# DESIGN OF MULTI-CHANNEL RADIO-FREQUENCY FRONT-END FOR 200MHZ PARALLEL MAGNETIC RESONANCE IMAGING

A Dissertation

by

XIAOQUN LIU

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

December 2008

Major Subject: Electrical Engineering

# DESIGN OF MULTI-CHANNEL RADIO-FREQUENCY FRONT-END FOR 200MHZ PARALLEL MAGNETIC RESONANCE IMAGING

A Dissertation

by

### XIAOQUN LIU

### Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

| Co-Chairs of Committee, | Takis Zourntos     |

|-------------------------|--------------------|

|                         | Steven M. Wright   |

| Committee Members,      | Jim Ji             |

|                         | Mary P. McDougall  |

| Head of Department,     | Costas Georghiades |

December 2008

Major Subject: Electrical Engineering

#### ABSTRACT

# Design of Multi-Channel Radio-Frequency Front-End for 200MHz Parallel Magnetic Resonance Imaging. (December 2008) Xiaoqun Liu, B.S., Zhejiang University

Co-Chairs of Advisory Committee: Dr. Takis Zourntos Dr. Steven M. Wright

The increasing demands for improving magnetic resonance imaging (MRI) quality, especially reducing the imaging time have been driving the channel number of parallel magnetic resonance imaging (Parallel MRI) to increase. When the channel number increases to 64 or even 128, the traditional method of stacking the same number of radio-frequency (RF) receivers with very low level of integration becomes expensive and cumbersome. However, the cost, size, power consumption of the Parallel MRI receivers can be dramatically reduced by designing a whole receiver front-end even multiple receiver front-ends on a single chip using CMOS technology, and multiplexing the output signal of each receiver front-end into one channel so that as much hardware resource can be shared by as many channels as possible, especially the digitizer.

The main object of this research is focused on the analysis and design of fully integrated multi-channel RF receiver and multiplexing technology. First, different architectures of RF receiver and different multiplexing method are analyzed. After comparing the advantages and the disadvantages of these architectures, an architecture of receiver front-end which is most suitable for fully on-chip multi-channel design is proposed and a multiplexing method is selected. According to this proposed architecture, a four-channel receiver front-end was designed and fabricated using TSMC 0.18µm technology on a single chip and methods of testing in the MRI system using parallel planar coil array and phase coil array respectively as target coils were presented. Each channel of the receiver front-end includes an ultra low noise amplifier (LNA), a quadrature image rejection down-converter, a buffer, and a low-pass filter (LPF) which also acts as a variable gain amplifier (VGA). The quadrature image rejection downconverter consists of a quadrature generator, a passive mixer with a transimpedance amplifier which converts the output current signal of the passive mixer into voltage signal while acts as a LPF, and a polyphase filter after the TIA. The receiver has an over NF of 0.935dB, variable gain from about 80dB to 90dB, power consumption of 30.8mW, and chip area of 6mm<sup>2</sup>.

Next, a prototype of 4-channel RF receiver with Time Domain Multiplexing (TDM) on a single printed circuit board (PCB) was designed and bench-tested. Then Parallel MRI experiment was carried out and images were acquired using this prototype. The testing results verify the proposed concepts.

#### ACKNOWLEDGEMENTS

My journey of pursuing knowledge has been a long road filled with obstacles. These obstacles can not be conquered and my goal in each stage can not be turned into reality without the contributions of many people. Although it is so difficult, even impossible to reward them as much, I do acknowledge so many people who I learned from, who aided me in my work, and who I shared my happiness and sadness with from the beginning, especially during these years at Texas A&M University.

First, I would like to express my sincere gratitude to my advisor, Dr. Takis Zourntos, for his guidance, support and constant encouragement all these years. His open thought as a pioneering explorer led me omit from the research field of pure analog circuit design to MRI, seeking the applications of analog circuit design from communications to biomedical. His encouragement, support, trust, and his guidance gave me great confidence and inspiration in my research. His supervision and guidance all these years in my study in Texas A&M University has been invaluable.

I would like to express my special thanks to my co-advisor, Dr. Steven M. Wright for his invaluable help, instruction and guidance. His wealth of knowledge and insight in research have not only showed me the art of the wonderful NMR/MRI world, but also assisted and guided me effectively in exploring my research in this field. I am grateful to him and respect him not only for his pioneering expertise as an advisor, but also as a great human being. His great attitude toward research and his great personality have become the model of me and other students.

I would also like to thank Dr. Jim Ji and Dr. Mary P. Mcdougall for spending their precious time being my committee members, patiently answering my questions, and giving me great suggestions. Their advice helped improve the quality of my research and this dissertation.

I want to thank Dr. Sebastian Magierowski for his effective help, discussion and instruction in RF/analog circuit design. I am deeply affected by his attitude toward his work, and his wealth of knowledge in RF/analog circuit design. I would also like to acknowledge Dr. Jose Silva-Martinez and other professors in electrical engineering for there good courses. I want to thank my friends Johnny Lee, Rain Lei, and many current and former graduate students in the Analog and Mixed Signal Group and Magnet Resonance System Lab. They gave me effective discussion and help in technical issues.

With a deep sense of feeling, I am indebted to my parents who I have not seen for five and a half years. They have always encouraged me in my education. They raised me, and supported me with their small amount of salary and their tremendous amount of love. With a deep sense of gratitude, I thank my wife, Dr. Joanne Wei. She has been giving me all her love and unconditional support all these years, helping me conquer difficulties and giving me the strength and encouragement to follow my dreams.

## NOMENCLATURE

| ADC             | Analog to Digital Converter             |

|-----------------|-----------------------------------------|

| BPF             | Band Pass Filter                        |

| CG LNA          | Common Gate Low Noise Amplifier         |

| CMFB            | Common Mode Feedback                    |

| CMOS            | Complementary Metal-Oxide-Semiconductor |

| CS LNA          | Common Source Low Noise Amplifier       |

| DSP             | Digital Signal Processing               |

| FDM             | Frequency Domain Multiplexing           |

| FID             | Free Induction Decay                    |

| FOV             | Field of View                           |

| GBW             | Gain-Bandwidth                          |

| GUI             | Graph User Interface                    |

| IC              | Integrated Circuit                      |

| IF              | Intermediate Frequency                  |

| IM <sub>3</sub> | Third Order Inter-Modulation            |

| IRF             | Image Rejection Filter                  |

| IRR             | Image Rejection Ratio                   |

| KCL             | Kirchhoff's Current Law                 |

| KVL             | Kirchhoff's Voltage Law                 |

| LCD             | Liquid Crystal Display                  |

| LHP          | Left Hand Plane                      |

|--------------|--------------------------------------|

| LNA          | Low Noise Amplifier                  |

| LPF          | Low Pass Filter                      |

| LO           | Local Oscillator                     |

| MESFET       | Metal Semiconductor FET              |

| MRI          | Magnetic Resonance Imaging           |

| MSL          | Micro Strip (Transmission) Line      |

| Opamp        | Operational Amplifier                |

| $P_{1dB}$    | 1dB Compression Point                |

| Parallel MRI | Parallel Magnetic Resonance Imaging  |

| РСВ          | Printed Circuit Board                |

| RF           | Radio Frequency                      |

| SAW          | Surface Acoustic Wave                |

| SDR          | Signal to Distortion Ratio           |

| SEA          | Single Echo Acquisition              |

| SNDR         | Signal to Noise and Distortion Ratio |

| SNR          | Signal to Noise Ratio                |

| SMT          | Surface Mount Technology             |

| TDM          | Time Domain Multiplexing             |

| TIA          | Transimpedance Amplifier             |

|              | 1 1                                  |

| THD          | Total Harmonic Distortion            |

| TTL | Transistor-Transistor Logic   |

|-----|-------------------------------|

| VCO | Voltage Controlled Oscillator |

VGA Variable Gain Amplifier

## TABLE OF CONTENTS

|                                                                                                                                                                                                                                 |                                                    | Page                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------|

| ABSTRACT                                                                                                                                                                                                                        |                                                    | iii                                              |

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                |                                                    | v                                                |

| NOMENCLATURE                                                                                                                                                                                                                    |                                                    | vii                                              |

| TABLE OF CONTENTS                                                                                                                                                                                                               |                                                    | х                                                |

| LIST OF FIGURES                                                                                                                                                                                                                 |                                                    | viii                                             |

| LIST OF TABLES                                                                                                                                                                                                                  |                                                    | xix                                              |

| CHAPTER                                                                                                                                                                                                                         |                                                    |                                                  |

| I INTRODUCTION                                                                                                                                                                                                                  |                                                    | 1                                                |

| 1.2 Time Domain Multipl<br>1.3 Research Goals                                                                                                                                                                                   | gn of MRI Receivers Using CMOS Technology<br>exing | 3<br>4<br>5<br>7                                 |

|                                                                                                                                                                                                                                 | O ARCHITECTURE AND MULTIPLEXING                    | 8                                                |

| <ul> <li>2.1.1 Superheterodyne</li> <li>2.1.2 Direct Conversion</li> <li>2.1.3 Low-IF</li> <li>2.1.4 Proposed Archite</li> <li>2.2 Multiplexing Technique</li> <li>2.2.1 Frequency Doma</li> <li>2.2.2 Time Domain M</li> </ul> | rchitecture                                        | 8<br>9<br>11<br>12<br>14<br>23<br>23<br>32<br>35 |

| III CMOS CIRCUIT DESIG                                                                                                                                                                                                          | N OF THE RF FRONT-END                              | 37                                               |

| 3.1 Low Noise Amplifier<br>3.1.1 CS LNA Noise I                                                                                                                                                                                 | Design                                             | 37<br>39                                         |

|    | 3.1.2 CS LNA Gain and Power Consumption                            | Λ   |

|----|--------------------------------------------------------------------|-----|

|    | 3.1.3 CMOS Design and Simulation Result of LNA                     |     |

|    | 3.2 Mixer Design and Simulation Result of ENA                      |     |

|    | 3.3 Quadrature Generator and Polyphase Filter Design               |     |

|    |                                                                    |     |

|    | 6                                                                  |     |

|    | 3.5 VGA/LPF Design                                                 |     |

|    | 3.6 Simulation and Layout of Front-End    85                       | 5   |

| IV | TESTING ARCHITECTURES OF FOUR-CHANNEL FRONT-END<br>IN MRI SYSTEM   | 4   |

|    |                                                                    |     |

|    | 4.1 Using Planar Coil Array in SEA as Target Coils                 |     |

|    | 4.1.1 Illustration of Planar Coil Array in SEA                     |     |

|    | 4.1.2 Proposed Testing Architecture Using Planar Coil Array        | 6   |

|    | 4.1.3 Specifications of the Parallel MRI Receiver System Using the |     |

|    | Proposed Architecture 10                                           |     |

|    | 4.1.3.1 Carrier Frequency, Phantom, and Bandwidth 10               | )() |

|    | 4.1.3.2 Signal to Noise Ratio                                      | )1  |

|    | 4.1.3.3 Bits of the Digitizer 10                                   | )4  |

|    | 4.1.3.4 Noise Figure of the Front-End 10                           | )5  |

|    | 4.1.3.5 Noise Performance Comparison between the Proposed          |     |

|    | Architecture and the Existing Architecture in SEA                  | )6  |

|    | 4.1.3.6 Linearity of the Front-End                                 | )7  |

|    | 4.1.3.7 Limit of Maximum Channel Number                            | )7  |

|    | 4.2 Using Phase Coil Array as Target Coils                         | )8  |

|    |                                                                    |     |

| V  | DESIGN OF A FOUR-CHANNEL FRONT-END PROTOTYPE                       |     |

|    | ON A PRINTED CIRCUIT BOARD                                         | 19  |

|    |                                                                    |     |

|    | 5.1 Main Targets of the Prototype                                  |     |

|    | 5.2 System Design                                                  |     |

|    | 5.2.1 System Gain 11                                               |     |

|    | 5.2.2 Noise Figure 11                                              |     |

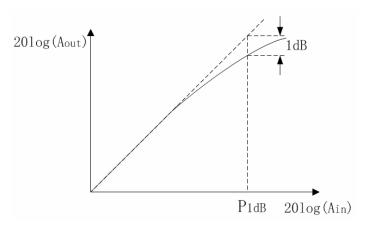

|    | 5.2.3 Input 1dB Compression Point 11                               | 2   |

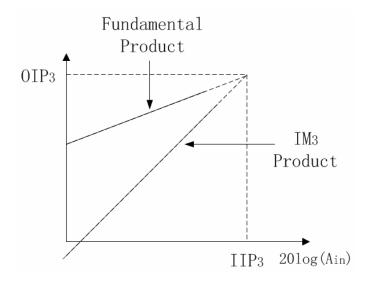

|    | 5.2.4 Input Third Intercept Point 11                               | 3   |

|    | 5.2.5 Slew Rate                                                    | 4   |

|    | 5.2.6 Input Resistance and Capacitance of each Block 11            | 4   |

|    | 5.2.7 Maximum Input Voltage 11                                     | 7   |

|    | 5.2.8 Power Supply 11                                              | 7   |

|    | 5.2.9 Package                                                      | 7   |

|    | 5.3 Circuit Design 11                                              | 9   |

|    | 5.3.1 MR Coil 11                                                   | 9   |

# CHAPTER

| 5.3.2 Preamplifier                                     | 120 |

|--------------------------------------------------------|-----|

| 5.3.3 Down-Converter                                   | 122 |

| 5.3.3.1 Quadrature Generator and Polyphase Filter      | 122 |

| 5.3.3.2 Mixer Setup and Down-Converter Gain            | 125 |

| 5.3.4 LPF and VGA                                      | 126 |

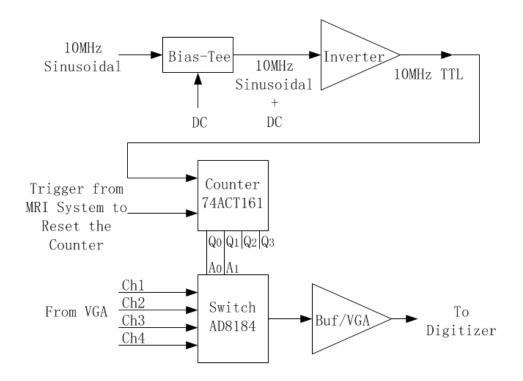

| 5.3.5 Multiplexing Switch and Switching Control        | 127 |

| 5.3.6 Power Supply                                     | 132 |

| 5.3.7 Ground Plane                                     | 133 |

| 5.4 Bench-Testing                                      | 133 |

| 5.4.1 Setup of the Bench Testing                       | 133 |

| 5.4.2 Gain of the Receiver Front-End                   | 135 |

| 5.4.3 Suppression of Thermal Noise at Image Frequency  | 136 |

| 5.4.4 Crosstalk among Channels                         | 137 |

| 5.4.5 Other Measurements                               | 139 |

| 5.4.5.1 Phase Shifts between each Quadrature LO Signal |     |

| from the Output of the Quadranture Generator           | 139 |

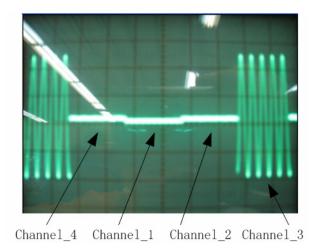

| 5.4.5.2 Multiplexed Signals Viewed at the              |     |

| Output of the Prototype                                | 140 |

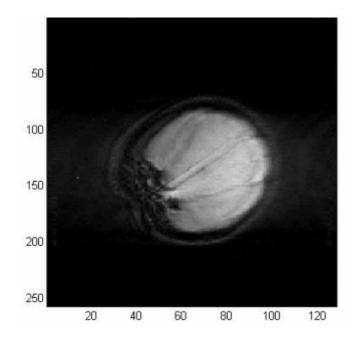

| 5.5 MRI Testing                                        | 141 |

| 5.5.1 MR Image Acquired Using a Single Channel         | 141 |

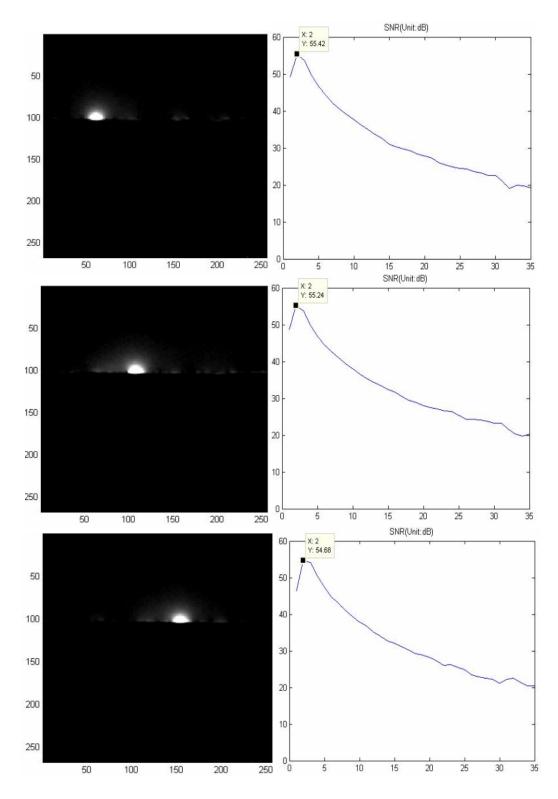

| 5.5.2 Parallel MR Imaging with the                     |     |

| Four-channel Receiver out of the Magnet                | 142 |

| 5.5.3 Parallel MR Imaging with the                     |     |

| Four-channel Receiver inside the Magnet                | 148 |

|                                                        |     |

| VI FUTURE WORK AND CONCLUSIONS                         | 152 |

| REFERENCES                                             | 155 |

| VITA                                                   | 168 |

# LIST OF FIGURES

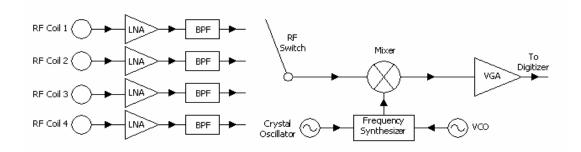

| Figure 2.1  | Superheterodyne Architecture                                        | 9  |

|-------------|---------------------------------------------------------------------|----|

| Figure 2.2  | Direct Conversion Architecture                                      | 11 |

| Figure 2.3  | Low-IF Architecture                                                 | 12 |

| Figure 2.4  | Thermal Noise Folding                                               | 14 |

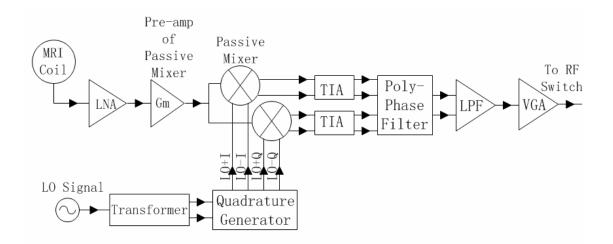

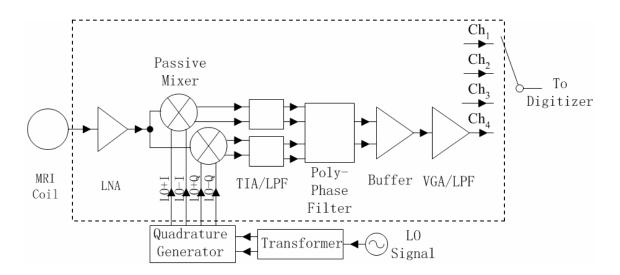

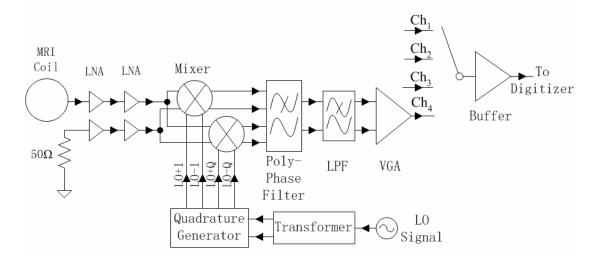

| Figure 2.5  | Proposed RF Receiver Front-End Architecture                         | 15 |

| Figure 2.6  | Quadrature Generator                                                | 16 |

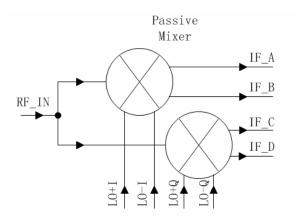

| Figure 2.7  | Quadrature Mixer                                                    | 17 |

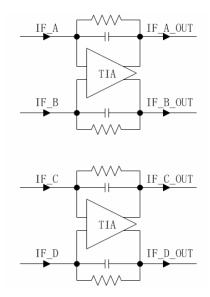

| Figure 2.8  | Transimpedance Amplifier                                            | 19 |

| Figure 2.9  | Polyphase Filter with Quadrature IF Input in Different Directions   | 20 |

| Figure 2.10 | Image Rejection                                                     | 20 |

| Figure 2.11 | Wide-Band Quadrature Generator                                      | 22 |

| Figure 2.12 | Wide-Band Polyphase Filter                                          | 22 |

| Figure 2.13 | Frequency Domain Multiplexing                                       | 24 |

| Figure 2.14 | Third Order Inter-Modulation                                        | 25 |

| Figure 2.15 | Dynamic Range Reduced by IM <sub>3</sub> Products                   | 25 |

| Figure 2.16 | Frequency Re-Arrangement                                            | 26 |

| Figure 2.17 | Effect of LO Frequency Phase Noise on the<br>Down-Converted Signals | 27 |

| Figure 2.18 | Illustration of Channel Spacing                                     | 28 |

| Figure 2.19 | Gradient Echo Sequence for MRI                                                                          | 30 |

|-------------|---------------------------------------------------------------------------------------------------------|----|

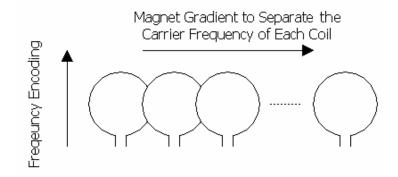

| Figure 2.20 | Simplified Illustration of Applying a Magnet Gradient across the Phase Array                            | 31 |

| Figure 2.21 | Simplified Illustration of Applying a Magnet Gradient<br>across the Planar Coil Array in SEA            | 31 |

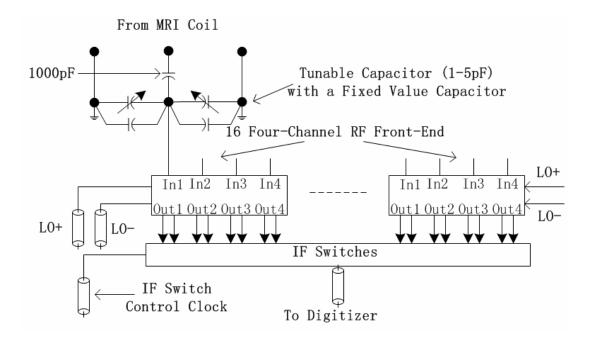

| Figure 2.22 | Multi-Channel RF Front-End with TDM                                                                     | 33 |

| Figure 2.23 | Proposed Architecture of the Four-Channel<br>Front-End with TDM                                         | 35 |

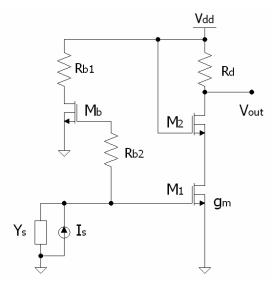

| Figure 3.1  | Common Source LNA                                                                                       | 39 |

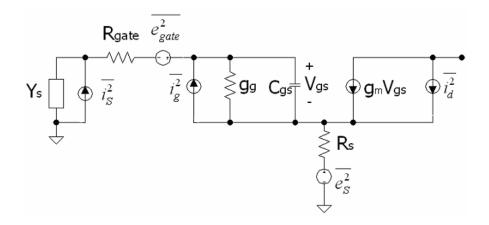

| Figure 3.2  | Small Signal Noise Performance Model of CS LNA                                                          | 41 |

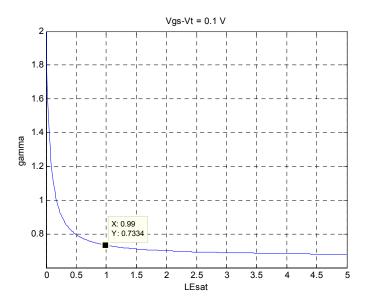

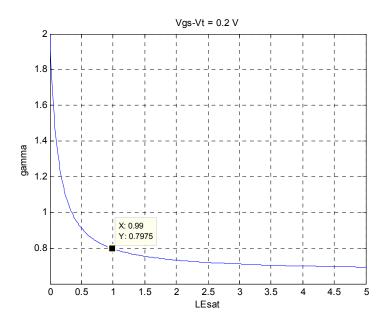

| Figure 3.3  | Plot of $\gamma$ as a Function of $LE_{sat}$                                                            | 43 |

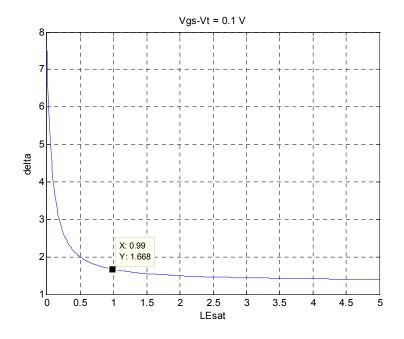

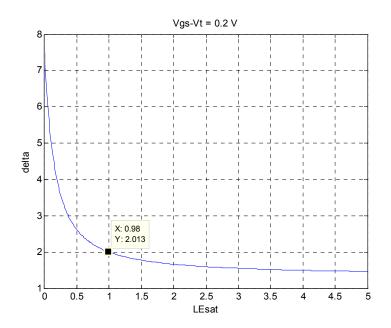

| Figure 3.4  | Plot of $\delta$ as a Function of $LE_{sat}$                                                            | 45 |

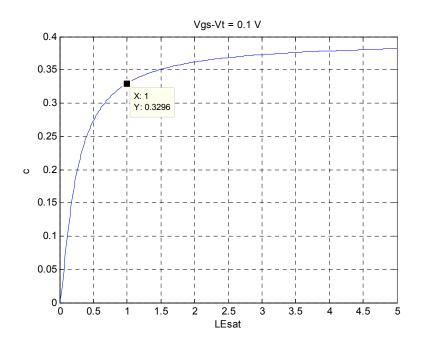

| Figure 3.5  | Plot of $c$ as a Function of $LE_{sat}$                                                                 | 47 |

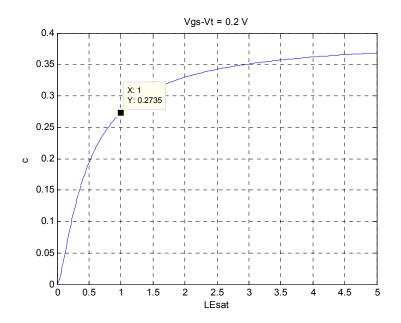

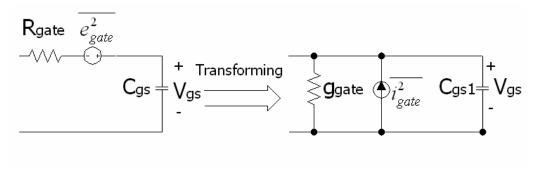

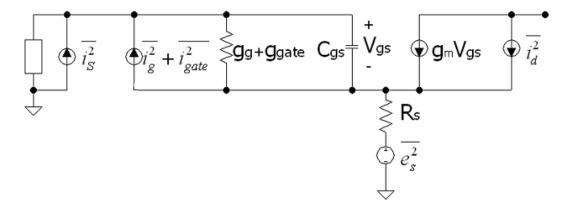

| Figure 3.6  | Equivalent Small Signal Noise Performance Model of CS LNA                                               | 48 |

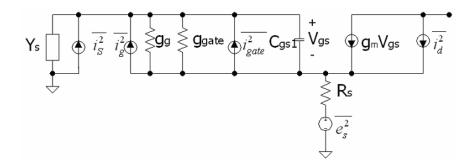

| Figure 3.7  | Conversion of Series $R_{gate}$ , $\overline{e_{gate}^2}$ to Shunt $g_{gate}$ , $\overline{i_{gate}^2}$ | 49 |

| Figure 3.8  | Rearranged Equivalent Small Signal Noise Performance<br>Model of CS LNA                                 | 50 |

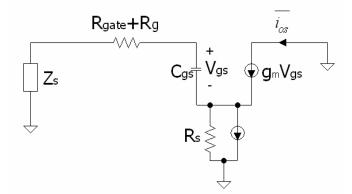

| Figure 3.9  | Equivalent Small Signal Model to Calculate $\overline{i_{os}^2}$                                        | 51 |

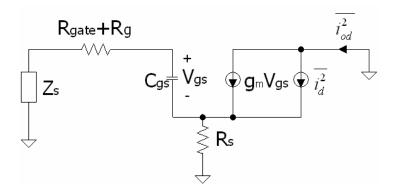

| Figure 3.10 | Equivalent Small Signal Model to Calculate $\overline{i_{od}^2}$                                        | 52 |

| Figure 3.11 | Equivalent Small Signal Model for Noise Factor Calculation                                              | 53 |

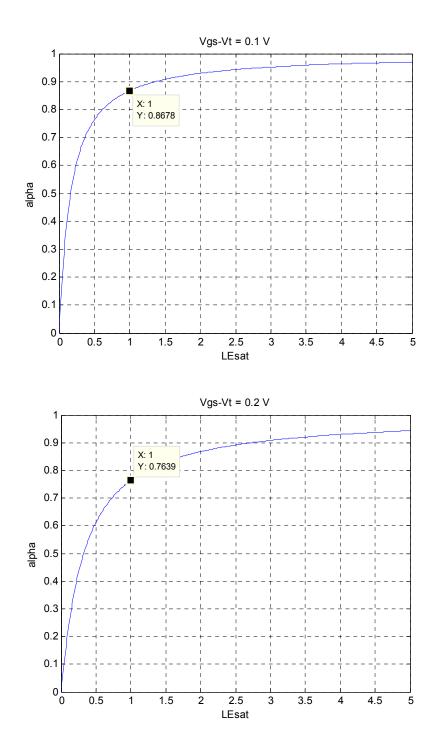

| Figure 3.12 | Plot of $\alpha$ as a Function of $LE_{sat}$                                                            | 55 |

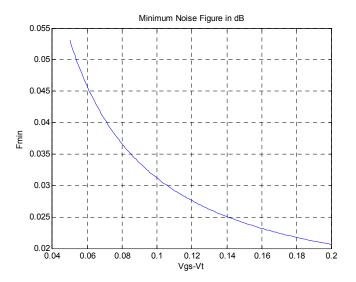

| Figure 3.13 | Plot of $F_{\min}$ as a Function of $V_{gs} - V_t$                                                      | 57 |

XV

| Figure 3.14 | CS LNA with an "Extra Capacitor" in Shunt with $C_{gs}$               | 58 |

|-------------|-----------------------------------------------------------------------|----|

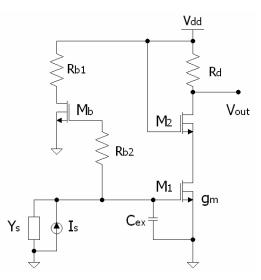

| Figure 3.15 | CS LNA Schematic with Equivalent circuit of MRI coil                  | 60 |

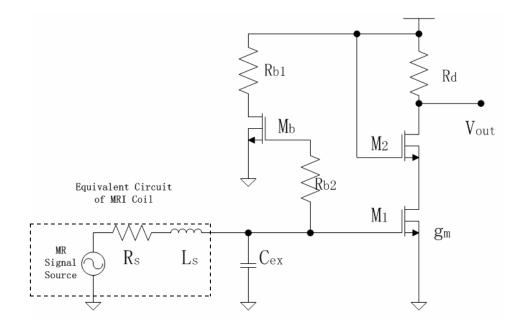

| Figure 3.16 | Schematic of CS LNA with Equivalent circuit of MRI coil               | 61 |

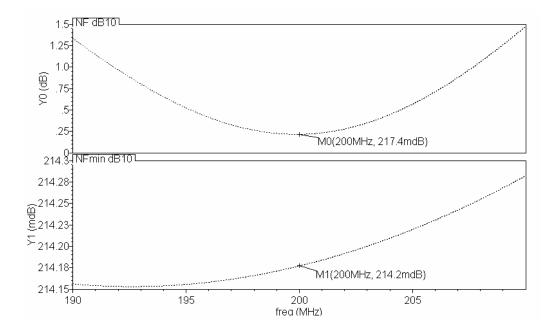

| Figure 3.17 | NF and NF <sub>min</sub> of LNA                                       | 63 |

| Figure 3.18 | Noise Summary of LNA                                                  | 63 |

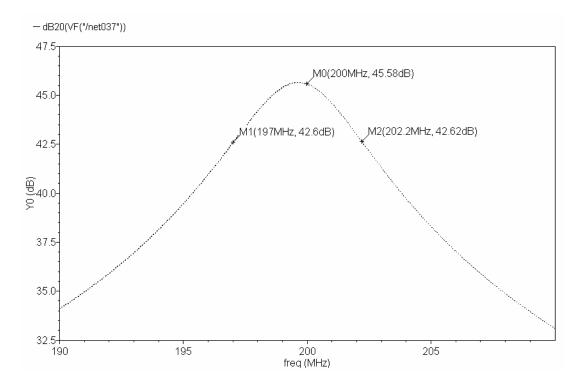

| Figure 3.19 | Conversion Gain of LNA                                                | 64 |

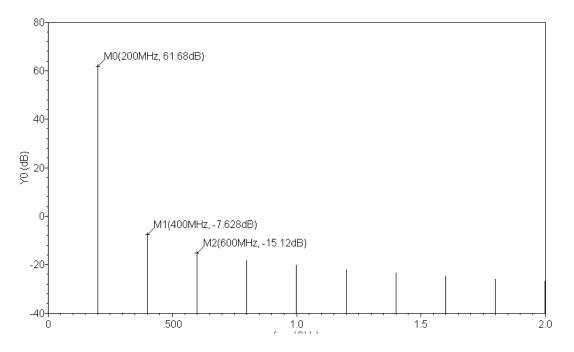

| Figure 3.20 | Harmonics of LNA                                                      | 64 |

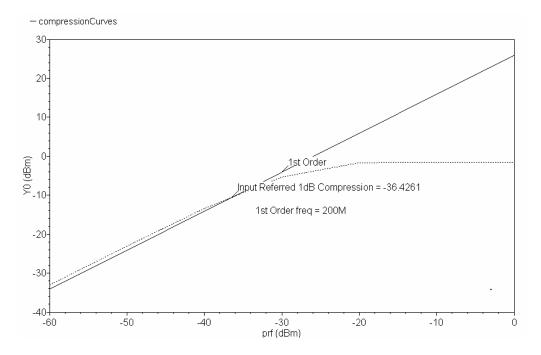

| Figure 3.21 | 1dB Compression Point of LNA                                          | 65 |

| Figure 3.22 | Power Consumption of LNA                                              | 65 |

| Figure 3.23 | Double-Balanced Passive Mixer Design<br>with Differential-Ended Input | 68 |

| Figure 3.24 | Double-Balanced Passive Mixer Design<br>with Single-Ended Input       | 69 |

| Figure 3.25 | Single-Balanced Passive Mixer Design<br>with Single-Ended Input       | 70 |

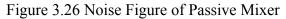

| Figure 3.26 | Noise Figure of Passive Mixer                                         | 71 |

| Figure 3.27 | Conversion Gain of Passive Mixer                                      | 71 |

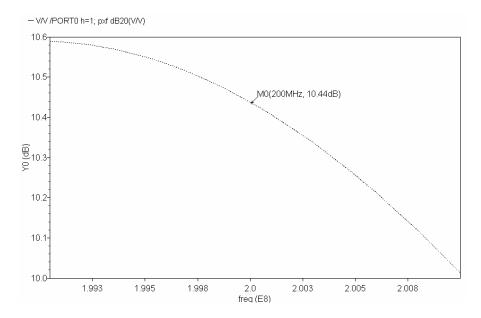

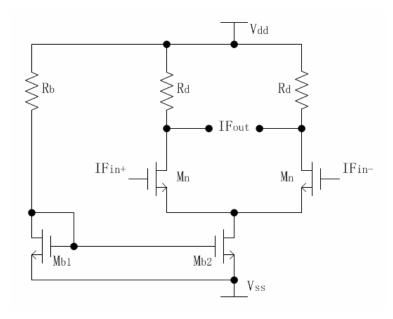

| Figure 3.28 | Schematic of Opamp                                                    | 72 |

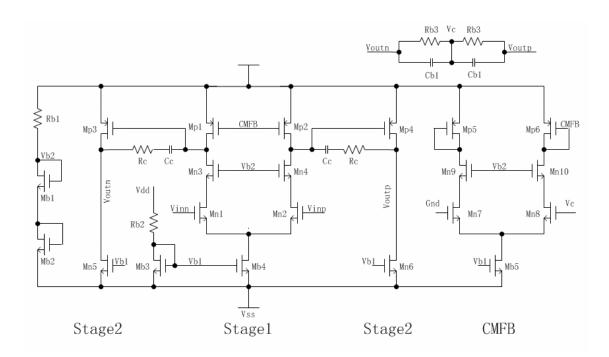

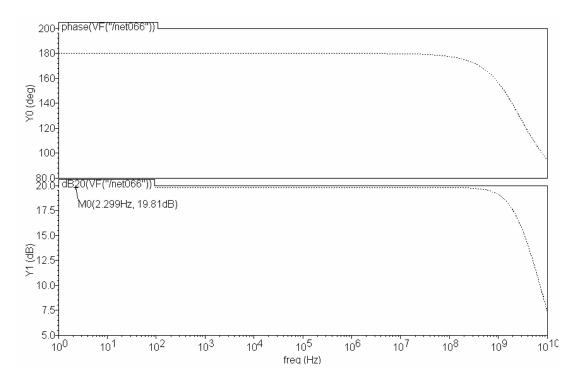

| Figure 3.29 | AC Simulation Results of Opamp                                        | 75 |

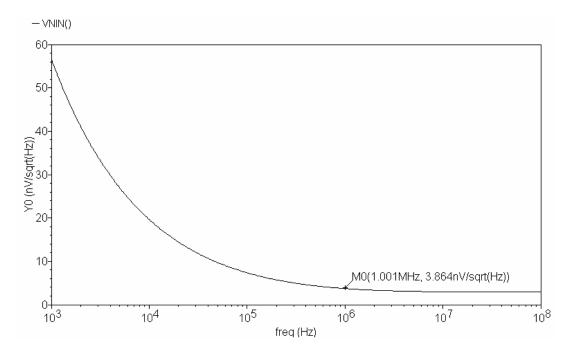

| Figure 3.30 | Input Referred Equivalent Noise of Opamp                              | 76 |

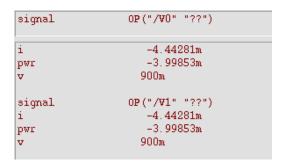

| Figure 3.31 | Power Consumption of Opamp                                            | 76 |

| Figure 3.32 | Schematic of Wide-Band Quadrature Generator                           | 78 |

| Figure 3.33 | Schematic of Wide-Band Polyphase Filter                                                                                          | 79 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.34 | Schematic of Buffer                                                                                                              | 80 |

| Figure 3.35 | AC Simulation Results of Buffer                                                                                                  | 81 |

| Figure 3.36 | Input Referred Equivalent Noise of Buffer                                                                                        | 81 |

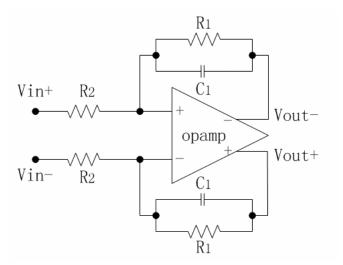

| Figure 3.37 | VGA/LPF                                                                                                                          | 82 |

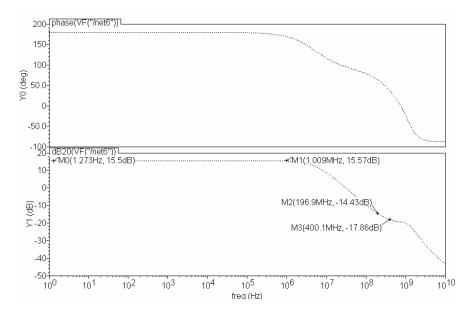

| Figure 3.38 | AC Simulation of VGA/LPF ( $R_2 = 1k\Omega$ )                                                                                    | 84 |

| Figure 3.39 | AC Simulation of VGA/LPF ( $R_2 = 6k\Omega$ )                                                                                    | 85 |

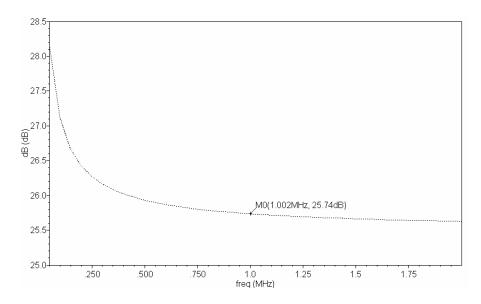

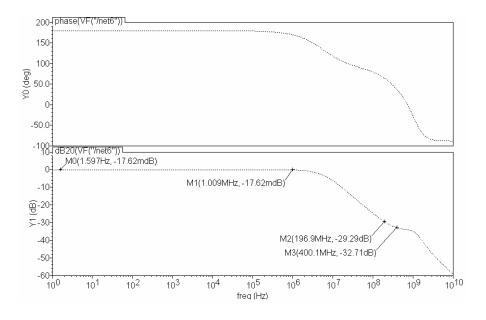

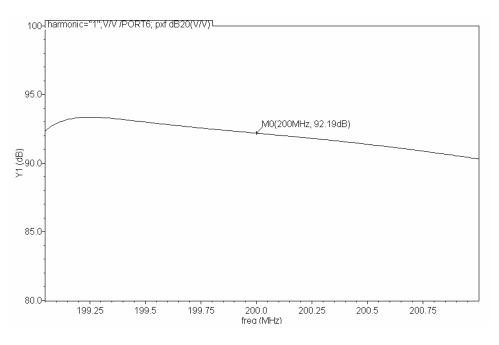

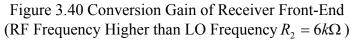

| Figure 3.40 | Conversion Gain of Receiver Front-End<br>(RF Frequency Higher than LO Frequency $R_2 = 6k\Omega$ )                               | 86 |

| Figure 3.41 | Conversion Gain of Receiver Front-End<br>(RF Frequency Lower than LO Frequency $R_2 = 6k\Omega$ )                                | 86 |

| Figure 3.42 | Conversion Gain of Receiver Front-End<br>(RF Frequency Higher than LO Frequency $R_2 = 1k\Omega$ )                               | 87 |

| Figure 3.43 | Conversion Gain of Receiver Front-End<br>(RF Frequency Lower than LO Frequency $R_2 = 1k\Omega$ )                                | 87 |

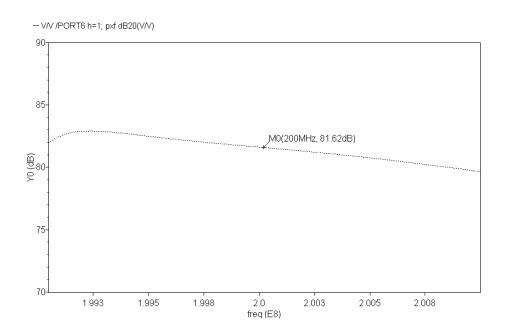

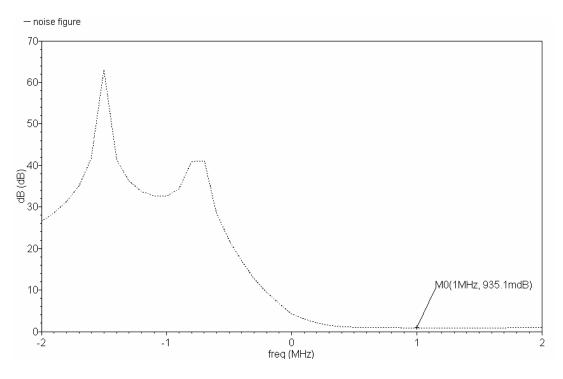

| Figure 3.44 | Noise Figure of Receiver Front-End                                                                                               | 88 |

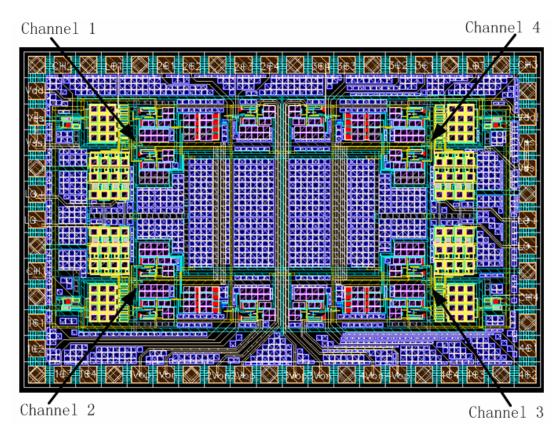

| Figure 3.45 | Layout of the Four-Channel Receiver Front-End                                                                                    | 89 |

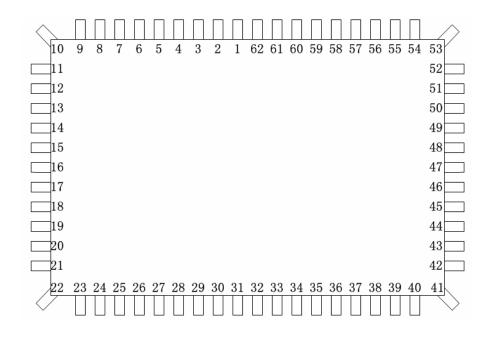

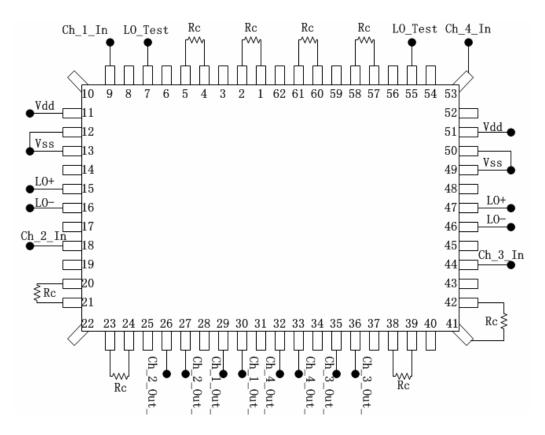

| Figure 3.46 | Pin Number (Upper) and Pin Connection (Lower)<br>of Four-Channel Receiver Front-End                                              | 90 |

| Figure 4.1  | Planar Coil Array Proposed in SEA                                                                                                | 96 |

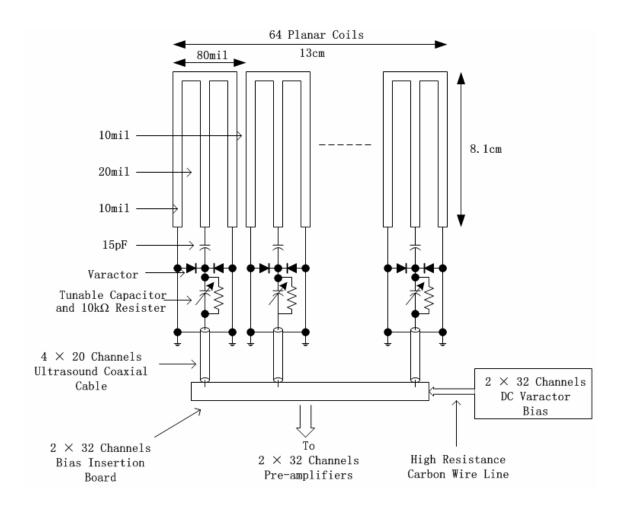

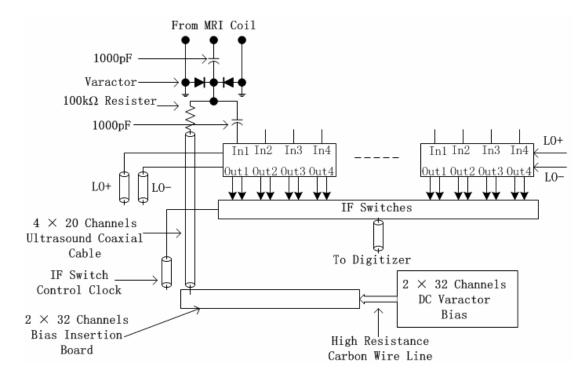

| Figure 4.2  | Proposed Architecture of Parallel RF Front-End Using<br>Parallel Planar Coil Array (Using Varactor as C <sub>ex</sub> )          | 99 |

| Figure 4.3  | Proposed Architecture of Parallel RF Front-End Using<br>Parallel Planar Coil Array (Using Tunable Capacitor as C <sub>ex</sub> ) | 99 |

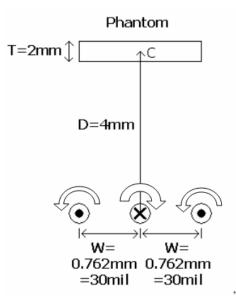

| Figure 4.4  | Cross Section View of a Coil; Field Produced by Each Wire;<br>And the Section of the Phantom on Its Top | 102 |

|-------------|---------------------------------------------------------------------------------------------------------|-----|

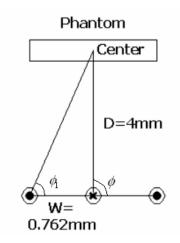

| Figure 4.5  | $\phi$ and $\phi_1$ in $\frac{B_1}{I}$ Calculation                                                      | 103 |

| Figure 4.6  | Simplified Illustration of the Phase Coil Array                                                         | 108 |

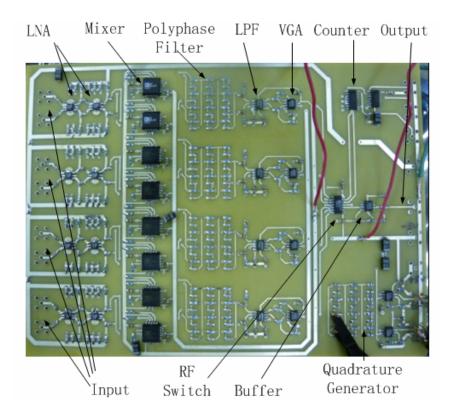

| Figure 5.1  | Architecture of the Four-Channel Front-End<br>with TDM on a Single PCB                                  | 110 |

| Figure 5.2  | Photograph of the Four-Channel Front-End<br>with TDM on a Single PCB                                    | 110 |

| Figure 5.3  | Definition of Input 1dB Compression Point                                                               | 112 |

| Figure 5.4  | Definition of Input Third Intercept Point                                                               | 113 |

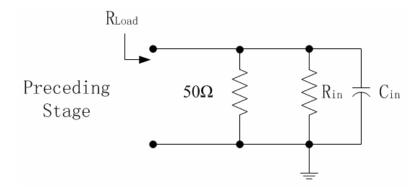

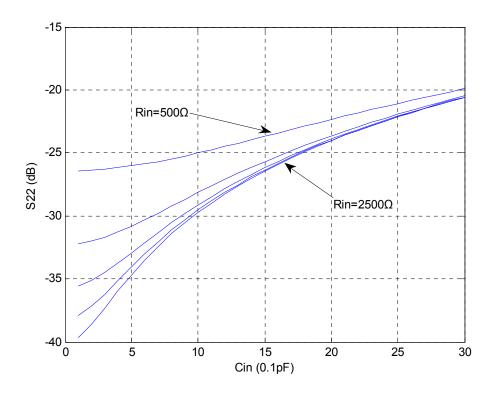

| Figure 5.5  | Input Matching Circuit of RF Block                                                                      | 115 |

| Figure 5.6  | MATLAB Evaluation of Input Resistance and Capacitance                                                   | 116 |

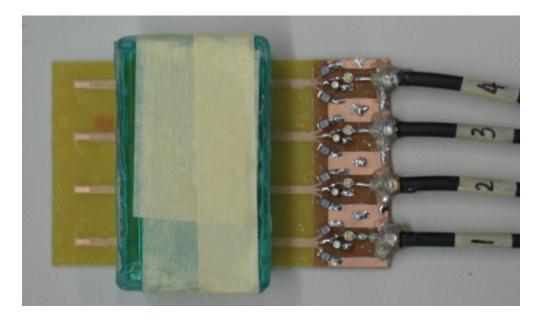

| Figure 5.7  | Four SEA Coil with Phantom on Top of It                                                                 | 120 |

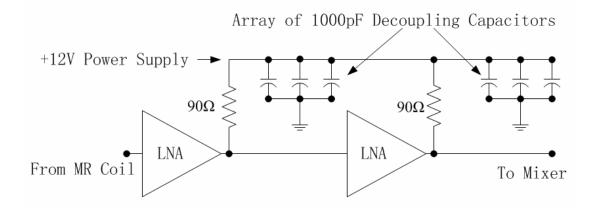

| Figure 5.8  | Power Supply and Decoupling of Preamplifiers                                                            | 121 |

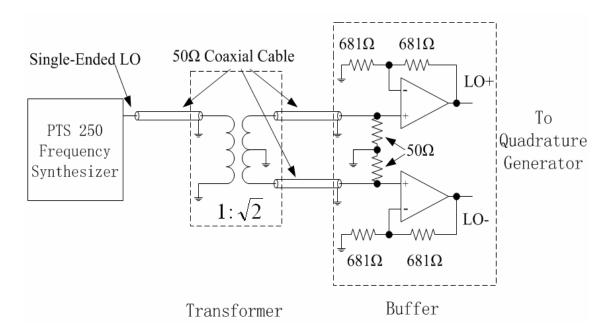

| Figure 5.9  | Single-Ended LO to Differential-Ended LO Conversion                                                     | 124 |

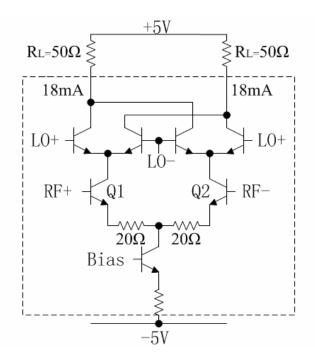

| Figure 5.10 | Setup of Mixer                                                                                          | 126 |

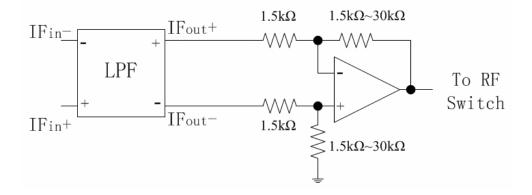

| Figure 5.11 | LPF and VGA                                                                                             | 127 |

| Figure 5.12 | Multiplexing Switch and Switching Control                                                               | 129 |

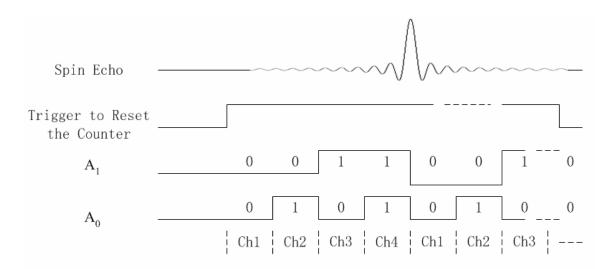

| Figure 5.13 | Timing of Switching Control                                                                             | 129 |

| Figure 5.14 | Setup of Bench-Testing                                                                                  | 134 |

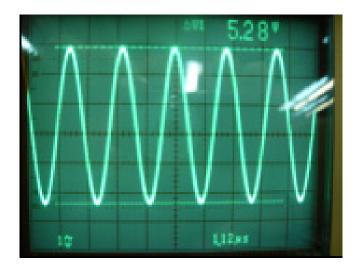

| Figure 5.15 | Measured Output Signal of Prototype                                                                     | 136 |

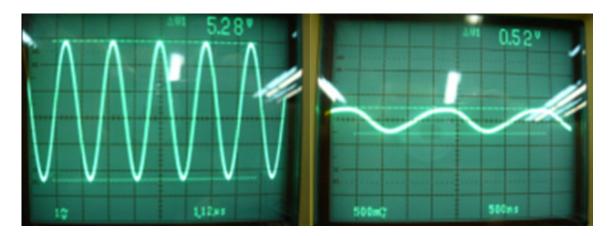

| Figure 5.16 | Suppression of the Noise at the Image Frequency                                                         | 137 |

| Figure 5.17 | Crosstalk                                                                                     | 138 |

|-------------|-----------------------------------------------------------------------------------------------|-----|

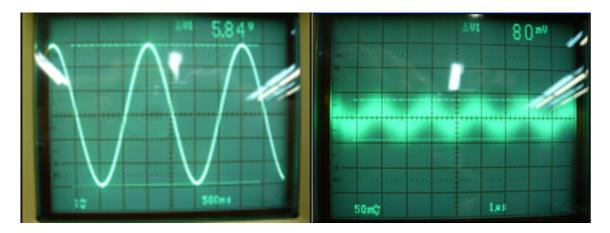

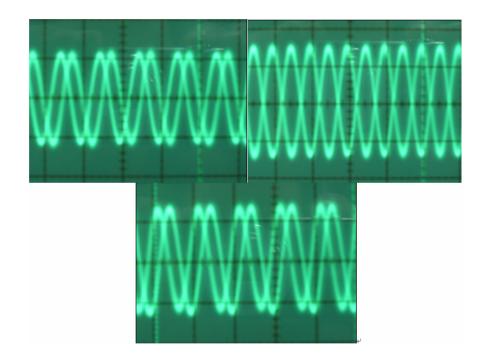

| Figure 5.18 | Phase Shifts between each Quadrature LO Signal from the Output of Quadranture Generator       | 139 |

| Figure 5.19 | Multiplexed Signals Viewed at the Output of Prototype                                         | 141 |

| Figure 5.20 | MR Image Acquired Using a Single Channel                                                      | 142 |

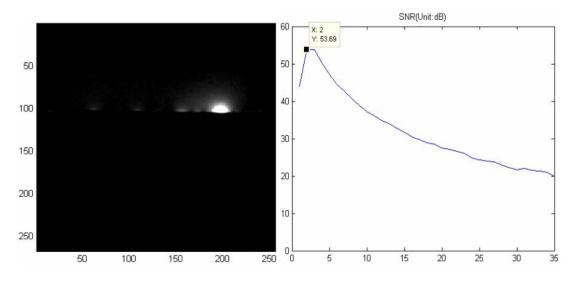

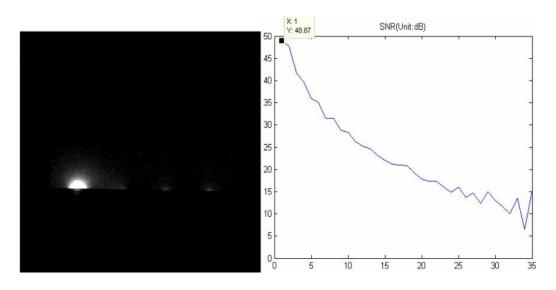

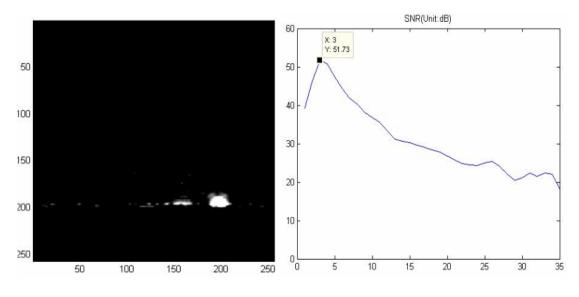

| Figure 5.21 | Images and SNR of the Images Acquired from the<br>Receiver Prototype before Being Multiplexed | 144 |

| Figure 5.22 | Images and SNR of the Images Acquired from the<br>Commercial MR System                        | 145 |

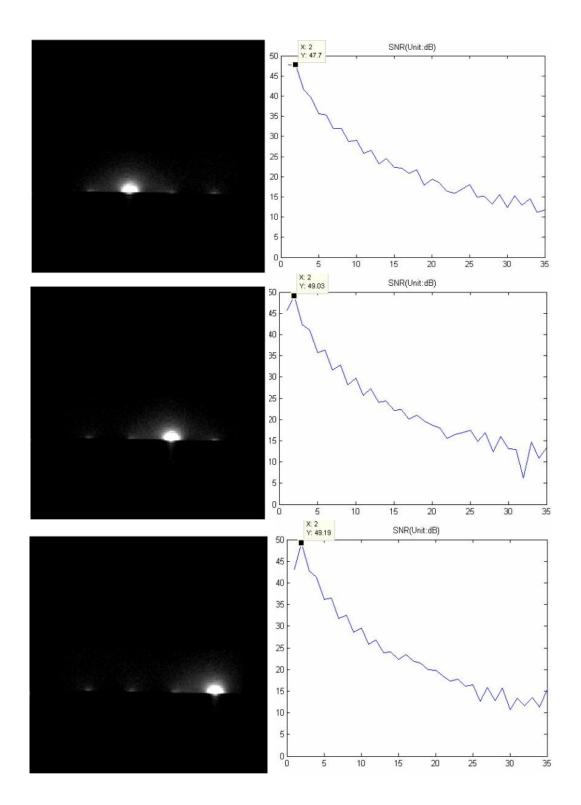

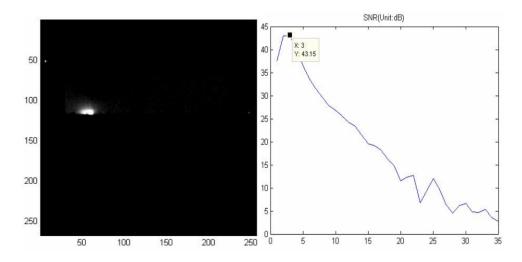

| Figure 5.23 | Images and SNR of the Images Acquired from the<br>De-Multiplexed Singles                      | 147 |

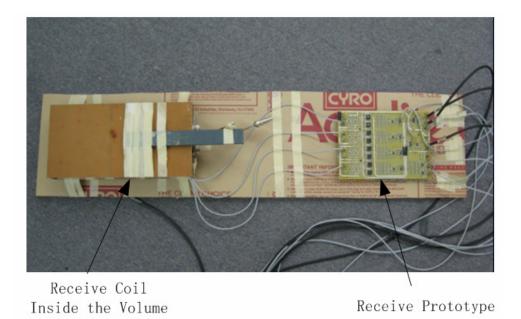

| Figure 5.24 | Receiver Prototype Mounted together with the Receive Coils<br>on a Plastic Board              | 149 |

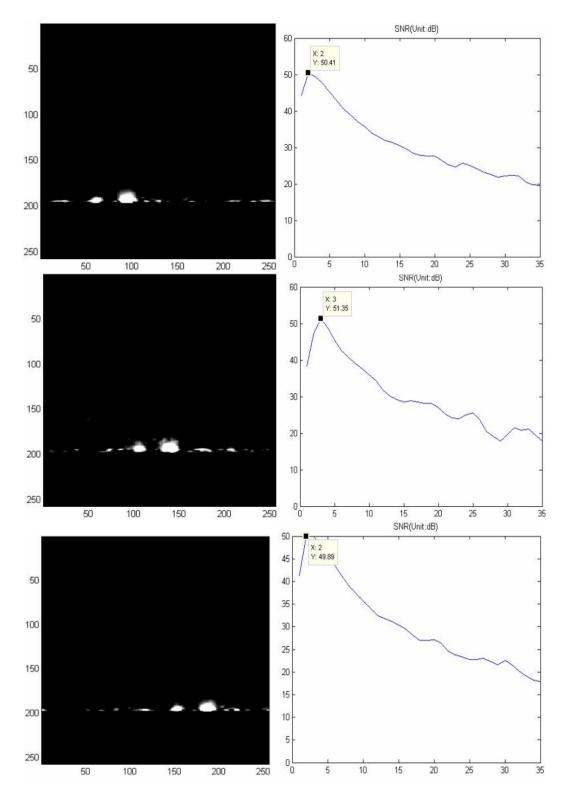

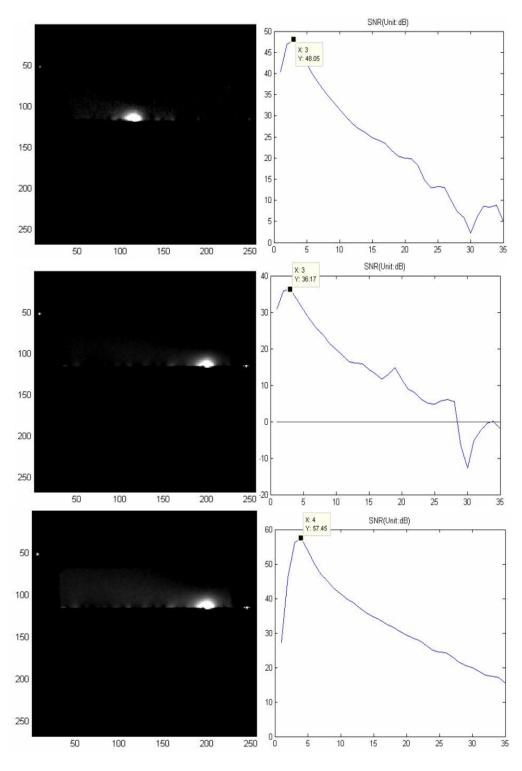

| Figure 5.25 | Images and SNR of the Images Acquired from the<br>Receiver Prototype inside the Magnet        | 149 |

# LIST OF TABLES

| Table 2.1 | SDR of Different Offset Frequency                                      | 29  |

|-----------|------------------------------------------------------------------------|-----|

| Table 3.1 | Summary of LNA Simulation Results                                      | 66  |

| Table 3.2 | Summary of Opamp Simulation Results                                    | 77  |

| Table 3.3 | Quadrature Generator Design Parameters                                 | 79  |

| Table 3.4 | Polyphase Filter Design Parameters                                     | 79  |

| Table 3.5 | Summary of Buffer Simulation Results                                   | 82  |

| Table 3.6 | Summary of Receiver Front-End Simulation Results                       | 88  |

| Table 3.7 | Summary of Receiver Front-End Pin Definition                           | 91  |

| Table 5.1 | List of the Selected Components and Specifications for each Stage      | 118 |

| Table 5.2 | Component Values of Quadrature Generator                               | 123 |

| Table 5.3 | Component Values Polyphase Filter                                      | 123 |

| Table 5.4 | True Values Table of the Switch                                        | 130 |

| Table 5.5 | Gain of each Channel                                                   | 136 |

| Table 5.6 | Suppression of Thermal Noise<br>at the Image Frequency of each Channel | 137 |

| Table 5.7 | Crosstalk between Channels                                             | 138 |

| Table 5.8 | Phase Shifts between Quadrature LO Signals                             | 140 |

#### CHAPTER I

#### INTRODUCTION

After first proposed and developed during early 1970s, magnetic resonance imaging (MRI) technique was dramatically developed and MRI equipments were built in experiment labs as well as in hospitals as a non-invasive tomographic imaging technique while suffering the disadvantages as the most expensive and slowest imaging method [1]-[3]. In the past decade, there have been considerable interests in parallel magnetic resonance imaging (Parallel MRI) to allow for simultaneous analysis of multiple biological samples, to improve other valuable factors, such as enlarging the field-of-view (FOV), increasing signal-to-noise ratio (SNR), and especially to facilitate faster image acquisition [4]-[7]. For example, a 64-channel coil array on a printed circuit board (PCB) was designed, constructed and successfully used by McDougall and Wright to test the method of single echo acquisition (SEA) imaging in which an independent image was acquired with only one echo by entirely replacing the phase encoding steps with the spatial information obtained from the coil array [3], [8], [9]. As another example, in order to increase the image SNR, a 23-channel and a 90-channel receive only phase array of small surface coils, which were arranged over the dome of head in a continuous array, were built by Wiggins and Wald et al. [6]. These phase array coils allow for significant imaging time and SNR improvement over conventional coils [6].

This dissertation follows the style of IEEE Journal of Solid State Circuits.

Parallel MRI demands the signals from each coil be acquired, pre-processed and digitized simultaneously. The most cost-effective approach to satisfy this requirement for parallel MRI is updating the existing conventional single-channel MRI equipment to its multi-channel counterpart by designing a multi-channel receiver, instead of designing and building a totally new set of parallel MRI equipment because of the prohibitively high-cost a new one introduces.

The most direct multi-channel receiver design simply duplicates a single channel receiver chain as many times as needed for the parallel MRI experiment [10]. However, this approach of simple duplication is expensive and cumbersome [5] because conventionally each receiver chain is built from integrated circuits (ICs) with low level of integration and other necessary discrete components, and these ICs and components increase to a large number after duplication, especially for experiment up to 128 channels. Moreover, each channel needs a single cable connecting the coil in the main magnet and the receiver front-end out of the main magnet, and still another cable is needed to connect the output of the front-end and the digitizer. The large number of cables continues to make the receiver more bulky. This high-cost and cumbersomeness make the receiver to be bottle-neck of parallel MRI experiment and limit its application in research labs and hospitals. Therefore, much recent effort has been devoted to seeking an effective approach to reduce the complexity and cost of the receiver. In this work, the limitation of reducing the size and cost of the multi-channel receiver has been explored by on-chip CMOS circuit design and multiplexing technique.

1.1 On-Chip Circuit Design of MRI Receivers Using CMOS Technology

As mentioned above, most of the existing MRI receivers were designed and assembled with very low level of integration making the receivers of Parallel MRI system expensive and cumbersome. On-chip circuit design becomes a most effective solution with additional advantages [11]. T. L. Peck et al. designed an integrated gallium arsenide metal semiconductor FET (MESFET) on the same substrate with a micro coil [11]-[14]. Although this design is a successful try of on-chip circuit design of MRI receiver, it is still in low level of integration because there is only one channel on a single chip and only the preamplifier stage was designed on the chip. Advances in lowcost CMOS technology inspire a solution that dramatically reduces the cost and complexity while providing outstanding imaging quality by using CMOS IC design. The key points of this design are low noise and high integration. In order to acquire low noise, first, the topology of LNA is explored and designed with high gain and ultra low noise figure. Second, a filter has to be designed before the down-converter in order to attenuate to thermal noise at image frequency. Otherwise, a threshold of 3dB exists for the noise figure of the receiver because of the thermal noise folding from the image frequency at the down-converter. In order to acquire high integration, the out-of-chip components such as surface acoustic wave (SAW) filter or crystal filter before the downconverter is avoided by introducing an image reject quadrature down-converter satisfying not only image noise rejection but also fully on-chip circuit design.

For demonstration purposes, a four-channel front-end was on-chip designed by the author using TSMC CMOS 0.18µm technology. This CMOS IC design is a small "chip" about the size of a finger nail after packaged and costs on the order of ten dollars with large volume production. The "chip" is even smaller about the size of a surface mounted technology (SMT) 0805-resistor if it is not packaged, and is small enough to be mounted on the same PCB of the coil array, and therefore the large bunch of cables originally connecting the coils and the receivers are avoided. This makes the multichannel receiver more economic and compact, moreover, the signal power lose of the MR signal along each of these cables is reduced and therefore the SNR at the output of each channel of receiver is increased as much as the reduced signal power loss.

The signals at the output of the multi-channel front-end can be multiplexed using a RF switch controlled by a time clock signal to realize the solution of time domain multiplexing (TDM).

### 1.2 Time Domain Multiplexing

TDM technique for MRI application was first proposed and prototypes were designed and proved to be a cost-effective multi-channel solution by Wright et al. using a RF multiplexing switch [4], [5], [15], [16]. Using the RF switch, the MR signal from each signal source was sampled in respective time-slot, and sent to a single receiver of the existing conventional MRI system for amplification, down-conversion, filtering and digitization. In this approach, the bandwidth and components of a single receiver is effectively used by multiple channels, so that the number of the components and the cables between the front-ends and the digitizer are largely reduced, and therefore the receiver is more compact and cost-effective. The TDM method proposed has its limitation. The bandwidth of the receiver is required to be *N* times that of the single channel. That is, at least *N* times Nyquist frequency of the down-converted MR signals, or in another word, the bandwidth of the MRI pulse sequence is required, where *N* is the number of the channels. Therefore, under the limitation of the bandwidth of the receiver of the existing conventional MRI system, the multiplexed channels are limited to a low number because of crosstalk. In the work of this dissertation, the TDM method is modified in order to eliminate the bandwidth limitation of the RF receiver by moving the RF switch to after the down-converter and the low-pass filter, right before the digitizer. Therefore the limitation of the bandwidth of the receiver is eliminated. After being multiplexed, the MR signals are sent to the digitizer for digitization. After the digitized MR signals are acquired, digital signal processing (DSP) technology is applied for separating the multiplexed signals and down-converting each channel of the MR signals.

#### 1.3 Research Goals

This research addresses the issues regarding the multi-channel receiver front-end integrated in CMOS technology for parallel MRI. The CMOS circuit design of each block of the receiver front-end, including the LNA, mixer, low-pass filter (LPF), and variable gain amplifier (VGA), is also analyzed and illustrated. Moreover, the multiplexing approaches of TDM and FDM, as well as various trade-offs of them are investigated. For demonstration purposes, as mentioned above, an experimental prototype of four-channel RF front-end based on the proposed concept was designed using TSMC CMOS 0.18µm technology to meet the 200MHz parallel MRI experiment. Moreover, also for demonstration purposes and verification, based on the analysis of this research, another experimental prototype of four-channel RF front-end together with a TDM circuit using commercial ICs and other necessary discrete components were designed in a single PCB and tested. Both prototype designs are frequency "universal", that is, suitable to a large range of MR signal frequency with only changing the local oscillator (LO) frequency provided.

The research goals and key contributions of this research are:

- Analysis of CMOS RF front-end architectures for MRI: Superheterodyne, Direct Conversion, and Low-IF architectures. And finally, proposing an architecture that is suitable for fully integration for MRI applications.

- 2. Investigation of TDM and FDM.

- The first CMOS multi-channel RF front-end design which dramatically decreases the cost and physical size of the multi-channel receiver.

- 4. The first house-made multi-channel RF front-end design with TDM technique.

- 5. Exploring the feasibility of the novel idea of "Digital Coil Array".

- 6. Low noise and high linearity circuit design of wide-band RF front-end which is also valuable for other wide-band application besides MRI.

- 7. Exploring the signal cross-talk and leakage among channels for multi-channel design on a single silicon substrate and on a single PCB.

- 8 Starting a new research field to explore the limitation of reducing the size, cost, and power consumption of receivers for parallel MRI.

### 1.4 Dissertation Organization

Chapter II reviews the existing RF receiver architectures and multiplexing methods. In order to achieve fully integrated design of multi-channel, a receiver frontend architecture is proposed in this chapter. Also a setup of multi-channel front-end with TDM is proposed.

Chapter III addresses the analysis and design of each building block of the fully integrated four-channel receiver front-end using CMOS TSMC 0.18µm. The front-end was designed to achieve ultra low noise figure, low power and high gain.

Chapter IV proposes architecture to setup 64-channel RF receiver front-end with TDM using parallel planar coil array in SEA as target coils, and analyzes the performance improvement of this architecture on MRI. Architecture using phase coil array as target coils is also proposed in order to prove the universality of the application of the multi-channel front-end with TDM on parallel MRI.

Chapter V addresses the design of a prototype of the first house-made multichannel front-end with TDM on a single PCB in the MRI society. Bench-testing and MRI experiment results of this prototype are also addressed.

In Chapter VI, future work and conclusions are presented.

#### CHAPTER II

#### RECEIVER FRONT-END ARCHITECTURE AND MULTIPLEXING METHOD

#### 2.1 Receiver Front-End Architecture

Although the MR signal from the output of the RF coil is theoretically possible to be digitized directly by analog to digital converter (ADC), due to the sampling frequency limitation and the trade-off between the sampling frequency and SNR of ADC, also due to the consideration of the data volume of the digitized MR signal and the computer resources to process this large volume of data if the MR signal is digitized at RF frequency, the MR signal has to be down-converted before digitization. When using down-conversion mixer, a LNA with enough gain is necessary to be placed before the mixer in order to overcome the noise of the mixer and the subsequent stages [17]. The LNA also has to be as low noise as possible in order to reduce the noise it introduces to the signal because no amplifier stage exists before the LNA and therefore the noise of the LNA is not suppressed. Moreover, filters are still needed before the mixer for thermal noise attenuation and signal selection if other signals exist at frequency nearby. After the mixer, low-pass filter is still necessary to attenuate the signal produced by the mixer at high frequency, and other gain stages are also needed to provide a proper signal power level for the input of the ADC. In conclusion, a RF/analog signal processing front-end is necessary before the ADC. Various RF front-end architectures exist [18]-[23]. The most common architecture is superheterodyne.

### 2.1.1 Superheterodyne

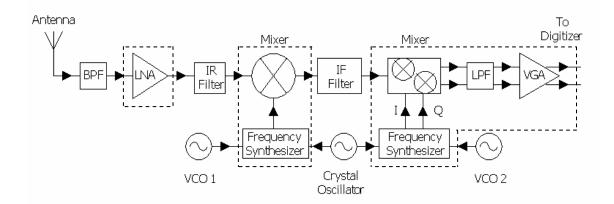

The superheterodyne architecture was first proposed by E. H. Armstrong in 1917 [17] as shown in Figure 2.1, and has been widely used in wireless communications, enjoying excellent sensitivity and selectivity [24]. In wireless communications applications, depending on different standard, the signal spectrum from the output of the antenna contains the signal band, which consists of a certain number of channels with certain bandwidth of each and certain channel spacing between the adjacent channels, and signals from other standards at frequencies out of the signal band (Out-of-band signals).

Figure 2.1 Superheterodyne Architecture (The blocks within the dashed line area are on-chip)

In this architecture, the band-pass filter (BPF), also called the band-selection filter, attenuates the out-of-band signals, and then the selected signal band is amplified by a LNA, which introduces as little noise as possible and provides enough gain to suppress the noise of the subsequent stages. A band-pass image rejection filter (IRF) after the LNA and before the mixer is used in order to attenuate the signal at the image frequency. The first mixer down-converts the RF signal to a certain intermediate frequency (IF), and the desired channel is selected by the band-pass IF filter, which is also called channel-selection filer. The IF is necessary to be high enough to relax the Q of the BPF and IRF. However, if the IF is too high, the Q of the IF filter has to be increased in order to effectively attenuate the out-of-channel signals. Therefore, a trade-off exists between the Q of IF filter and that of BPF and IRF. The selected desired channel, which is a complex signal in most cases, is then down-converted to base-band with real (Q) part and imaginary (I) part by a quadrature mixer. Next the base-band I, Q signals go through a LPF to further reject the out-of-channel signals. Now the signal is ready to be amplified by a VGA to proper value of amplitude for the input of the ADC.

Although the superheterodyne architecture enjoys excellent signal to noise and distortion ratio (SNDR), and acquires excellent SNR, this architecture suffers the following disadvantages:

- 1. The BPF, IRF and IF filter have to be out-of-chip because the Q of which is too high to be implemented in conventional CMOS technology [25].

- 2. The voltage controlled oscillator (VCO) has to be off-chip because of the low Q of the on-chip inductor [24].

- 3. This architecture is complicated and comprises many stages to be designed onchip [25].

- 4. The BPF, IRF and IF filter are passive and therefore reduce the signal power, and in turn degrade the SNR, especially the BPF before the LNA [25].

In the application of MRI, the MR signal is a very clean signal containing only a single signal band at Larmor frequency, and only thermal noise exists out of the Larmor frequency. Therefore, the BPF and the IRF can be removed because no large out of band signal is needed to be attenuated. Since no Q of the BPF and IRF is needed to be relaxed by the IF, the first stage of the down-conversion together with the IF filter can also be removed if the thermal noise at the image frequency is not considered. After removing all these stages, we can find that this architecture turns in to a direct conversion receiver.

Note that the thermal noise at the image frequency has to be suppressed in order to reduce the noise figure of the receiver front-end to be smaller than 3dB. This issue is being discussed later in this chapter.

#### 2.1.2 Direct Conversion

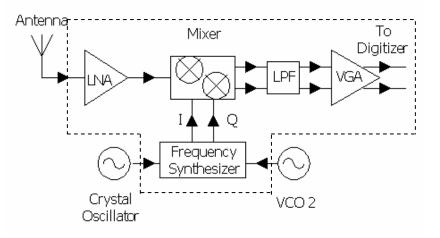

Figure 2.2 Direct Conversion Architecture (The blocks within the dashed line area are on-chip)

Direct conversion architecture, as illustrated in Figure 2.2, has an advantage of simplicity and enjoys fully integration [25], however, this architecture also suffer the following disadvantages:

- First and foremost, a small amount of energy at LO frequency radiates from the LO input port of the mixer and is received by the antenna, and/or leaks through the silicon substrate to the input of the LNA. These amount of energy at LO frequency are amplified by the LNA, and then "self-mixed" to the base-band in the mixer, causing a DC offset problem [17].

- 2. The leakage of the RF signal to the LO input port of the mixer is "self-mixed" with the RF signal, and also introduces DC offset problem [17].

- 3. Harmonics of RF and LO signals also have the same effect [25].

- 4. Flicker noise is large at low frequencies especially at base-band.In order to overcome these problems, a low-IF architecture is used in this design.

2.1.3 Low-IF

Figure 2.3 Low-IF Architecture (The blocks within the dashed line area are on-chip)

As illustrated in Figure 2.3, the signal from the output of the RF coil is downconverted to a low IF frequency, which is chosen to be low enough to accommodate the sampling frequency limitation of the ADC. On the other hand, this IF has to be high enough to avoid the large flicker noise. Normally, the IF is chosen to be a little larger than the noise corner frequency which is about 500 kHz to 1 MHz in CMOS technology [25].

Since the RF signal is not down-converted to DC, this architecture is free from the DC offset problem, as well as flicker noise as mentioned above.

The Low-IF architecture increases the requirement of the ADC, however, with the advances of the CMOS and the effort of the talented CMOS analog designers, nowadays, a 16-bit ADC is not difficult to be designed with sampling frequency up to 20MHz.

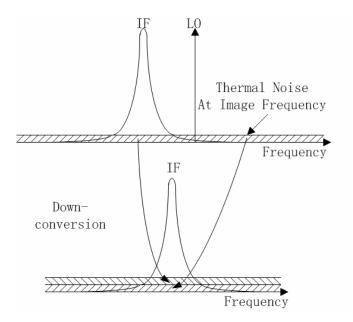

However, although there is not large signal power at the image frequency, if the IRF is removed as shown in Figure 2.3, the thermal noise at the image frequency is folded to the down-converted signal at IF by the down-converter as illustrated in Figure 2.4. The noise folding decreases the SNR of the MR signal by 3dB, that is, increase the noise figure of the receiver front-end by 3dB [25]. Therefore, a threshold of 3dB is set for the noise figure of the receiver front-end. In order for reducing the noise figure of the front-end to lower than 3dB, it is necessary to place an IRF before the down-converter. Normally, a surface acoustic wave (SAW) filter or a crystal filter is used as the IRF to satisfy the requirement of high Q of the IRF. However, the SAW filter or crystal filter is passive and out-of-chip. In order for fully on-chip design, one solution is using CMOS

active filter to replace the SAW or crystal filter. However, in order to acquire the necessary high Q for the IRF, the CMOS active filter has to be very high order and be a very large circuit and therefore not only increases the complication of the receiver design but also introduces much thermal noise.

Figure 2.4 Thermal Noise Folding

A solution to this problem is using a quadrature generator for the LO signal and a polyphase filter after the down-converter [26]-[30].

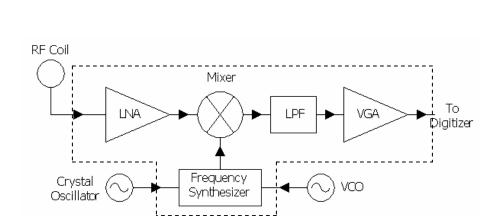

### 2.1.4 Proposed Architecture of RF Receiver Front-End

As discussed above, the Low-IF architecture is updated by using a quadrature generator for the LO signal and a polyphase filter after the mixer [26]-[30] in order to avoid noise folding and satisfy fully on-chip design.

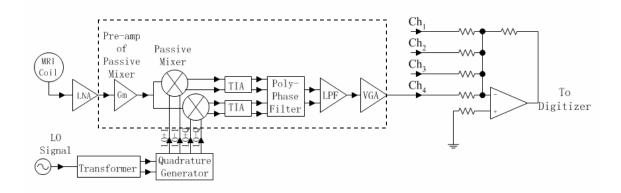

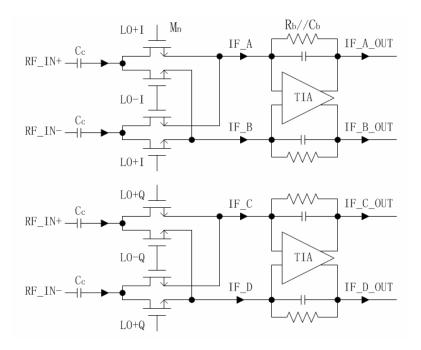

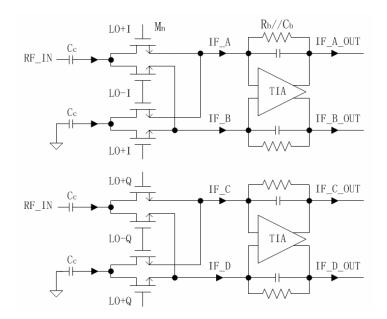

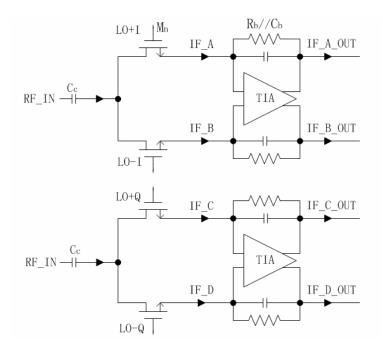

As shown in Figure 2.5, the MR signal from the MRI coil is amplified by the LNA and the pre-amp of the passive mixer in order to compensate the loss and suppress the noise of the passive mixer. Note that if the gain of the LNA is large enough, the pre-amp of the passive mixer can be ignored. After being amplified, the MR signal is sent to the mixer, which is a passive mixer in order for reducing the flicker noise, and mixed with the quadrature LO signals from the LO quadrature generator. After the down-converter, transimpedance amplifier (TIA) and the polyphase filter, the MR signal is down-converted to an intermediate frequency, and the thermal noise at the image frequency is attenuated. This down-converted MR signal still needs to be sent to a LPF in order to filter out the signal at the frequency of  $\omega_{LO+RF}$  generated at the mixer. Finally, after amplified by the variable gain amplifier to a proper value of amplitude, the MR signal is sent to the RF switch for multiplexing.

Figure 2.5 Proposed RF Receiver Front-End Architecture

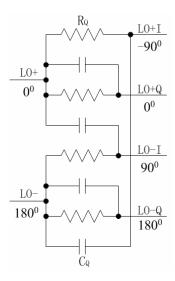

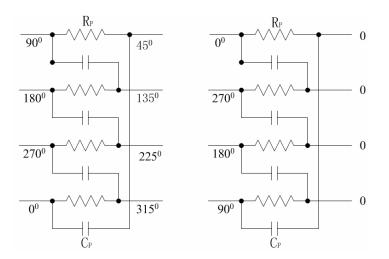

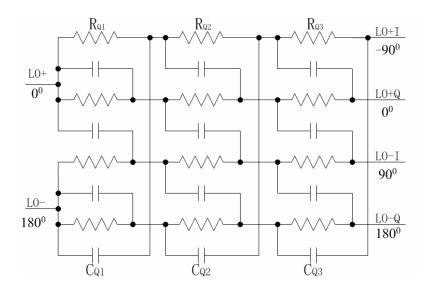

The key points of image rejection in this architecture are the quadrature generator and the polyphase filter. First, the LO signal from the frequency synthesizer is transformed from single-ended to differential-ended by a transformer. Then the differential-ended LO signal is sent to the quadrature generator illustrated in Figure 2.6 [26] according to the Kirchhoff's Voltage Law (KVL) and Superposition Principle, where  $R_{\varrho} = \frac{1}{\omega_{LO}C_{\varrho}}$ . Then the quadrature LO signals are sent to the quadrature mixer

shown as Figure 2.7.

Figure 2.6 Quadrature Generator

Figure 2.7 Quadrature Mixer

In order to analyze how the thermal noise at the image frequency is rejected, we can assume the input signal in Figure 2.7 is

$$S_{in}(t) = A_{RF} \cos \omega_{RF} t + A_{IM} \cos \omega_{IM} t$$

$$2.1$$

$$\omega_{RF} - \omega_{LO} = \omega_{LO} - \omega_{IM} > 0$$

where

According to the relative phase shifts of the quadrature LO signals between each other, we can get

$$LO + I = \sin \omega_{LO} t$$

2.2

$$LO - I = \sin(\omega_{LO}t + 180^\circ)$$

2.3

$$LO + Q = \sin(\omega_{LO}t + 90^{\circ})$$

2.4

$$LO - Q = \sin(\omega_{LO}t + 270^{\circ})$$

2.5

Note that in order for simplicity, the amplitudes of the LO signals are neglecting. Then the RF input signal mixers with the LO signals respectively, and we can get the following results neglecting the high frequency components which are filtered by the LPF.

$$IF_{-}A = \frac{A_{RF}}{2}\cos(\omega_{IF}t + 90^{\circ}) + \frac{A_{IM}}{2}\cos(\omega_{IF}t)$$

2.6

$$IF_{B} = \frac{A_{RF}}{2}\cos(\omega_{IF}t - 90^{\circ}) + \frac{A_{IM}}{2}\cos(\omega_{IF}t + 180^{\circ})$$

2.7

$$IF_{-}C = \frac{A_{RF}}{2}\cos(\omega_{IF}t + 0^{0}) + \frac{A_{IM}}{2}\cos(\omega_{IF}t + 90^{0})$$

2.8

$$IF \_ D = \frac{A_{RF}}{2} \cos(\omega_{IF}t + 180^{\circ}) + \frac{A_{IM}}{2} \cos(\omega_{IF}t + 270^{\circ})$$

2.9

In order for simplicity, equations (2.6)-(2.8) are rewritten as the following

$$IF_{A} = \frac{A_{RF}}{2} \angle 90^{0} + \frac{A_{IM}}{2} \angle 0^{0}$$

2.10

$$IF\_B = \frac{A_{RF}}{2} \angle -90^{\circ} + \frac{A_{IM}}{2} \angle 180^{\circ}$$

2.11

$$IF_{-}C = \frac{A_{RF}}{2} \angle 0^{0} + \frac{A_{IM}}{2} \cos \angle 90^{0}$$

2.12

$$IF_{D} = \frac{A_{RF}}{2} \angle 180^{\circ} + \frac{A_{IM}}{2} \angle 270^{\circ}$$

2.13

Next, the down-converted MR signals are sent to TIA, which is an opamp connected in negative feedback with a pair of shunt resistor and capacitor. The TIA transfers the IF signal from current to voltage, as shown in Figure 2.8.

Figure 2.8 Transimpedance Amplifier

Since the TIAs are connected in negative feedback, each output IF signal of the TIA has a 180<sup>o</sup> phase shift, therefore, we can get the IF signals at the TIA outputs

$$IF \_ A \_ OUT = \frac{A_{RF}}{2} \angle 270^{\circ} + \frac{A_{IM}}{2} \angle 180^{\circ}$$

2.14

$$IF \_ B \_ OUT = \frac{A_{RF}}{2} \angle 90^{\circ} + \frac{A_{IM}}{2} \angle 0^{\circ}$$

2.15

$$IF \_ C \_ OUT = \frac{A_{RF}}{2} \angle 180^{\circ} + \frac{A_{IM}}{2} \cos \angle 270^{\circ}$$

2.16

$$IF \_ D \_ OUT = \frac{A_{RF}}{2} \angle 0^0 + \frac{A_{IM}}{2} \angle 90^0$$

2.17

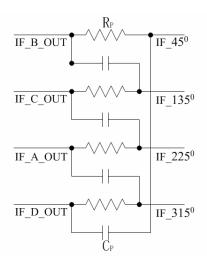

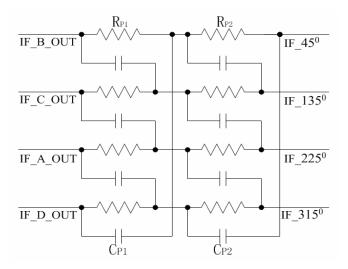

Then the IF signals at the TIA outputs are sent to the polyphase filter. As illustrated in Figure 2.9, according to the Kirchhoff's Voltage Law (KVL) and Superposition Principle, if the quadrature IF signals are connected in clockwise, we can get the output signals as shown in the left side of Figure 2.9. If the quadrature IF signals

are connected in counter clockwise, the signals are cancelled at the output as shown in the right side of Figure 2.9. Therefore with proper connection, we can get the IF signals while cancelling (rejecting) the thermal noise at the output of the polyphase filter as

shown in Figure 2.10, where  $R_P = \frac{1}{\omega_{IF}C_P}$

Figure 2.9 Polyphase Filter with Quadrature IF Input in Different Directions

Figure 2.10 Image Rejection

As shown in Figure 2.10, if the quadrature MR signals from the output of the TIAs are connected to the polyphase filter at the sequence of IF\_B\_OUT, IF\_C\_OUT, IF\_A\_OUT, IF\_D\_OUT, according to equations (2.14) – (2.17), the quadrature MR signals are connected in clockwise and the quadrature thermal noises down-converted from the image frequency are connected in counter clockwise. Therefore, according to Figure 2.9, at the output of the polyphase filter, the thermal noise from the image frequency is rejected while the down-converted quadrature MR signals are reserved. From Figure 2.10, we can get two pair of differential MR signals, one is IF\_45<sup>0</sup> and IF\_225<sup>0</sup>, the other is IF\_135<sup>0</sup> and IF\_315<sup>0</sup>. Either one of these two pairs can be used as the differential input of the LPF and next to the VGA.

In the analysis about, all of the values of resistance, capacitance are assumed to be ideal, and the mixer gain, mixer phase mismatch are also assumed to be zero, however, in actually circuit design, the above values vary because of variation of process and temperature. Therefore, the image rejection ratio (IRR) becomes finite, and given in equation 2.18 [25], [31],

$$IRR \approx \frac{1}{4} \left( \left( \frac{\Delta A}{A} \right)^2 + \left( \tan(\theta) \right)^2 \right)$$

2.18

where  $\Delta A$  and  $\theta$  are the overall mismatches of gain and phase respectively between the quadrature signal paths because of the mismatches of the quadrature generator, mixer, and the polyphase filter. And A is the normalized overall gain of the signal path. For careful layout design of the capacitors, resistors and mixer, as well as good design skill of mixer, the IRR can be reduced to – 40 dB [25], [31], For the target of thermal noise rejection, this IRR value is small enough.

Figure 2.11 Wide-Band Quadrature Generator

Figure 2.12 Wide-Band Polyphase Filter

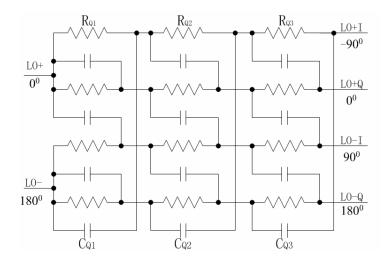

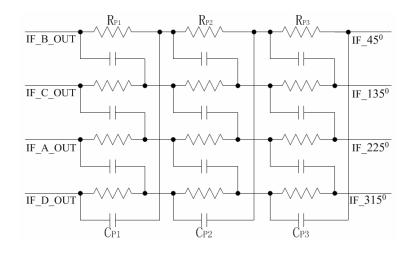

Still one other problem exists. As shown in Figure 2.6 and Figure 2.10, the quadrature generator and the polyphase filter are both narrow-band. That is, the quadrature generator can only work at frequency of  $\omega_{LO} = \frac{1}{R_Q C_Q}$ , while the polyphase

filter can only work at frequency  $\omega_{IF} = \frac{1}{R_P C_P}$ . In order for wide-band application, multi-stage topology is used as shown in Figure 2.11 for the quadrature generator and Figure 2.12 for the polyphase filter, where  $\frac{1}{R_{Q1}C_{Q1}} < \omega_{LO} = \frac{1}{R_{Q2}C_{Q2}} < \frac{1}{R_{Q3}C_{Q3}}$ , and

$$\frac{1}{R_{P1}C_{P1}} < \omega_{IF} = \frac{1}{R_{P2}C_{P2}} < \frac{1}{R_{P3}C_{P3}}$$

. The values of  $\frac{1}{R_{Q1}C_{Q1}}$ ,  $\frac{1}{R_{Q3}C_{Q3}}$ ,  $\frac{1}{R_{P1}C_{P1}}$  and

$\frac{1}{R_{P3}C_{P3}}$  are selected in consideration of the 30% variation of the RC time constant as well as ensuring the IRR smaller than -40dB in the whole bandwidth. Specific values of the resistance and capacitance of the quadrature generator and polyphase filter are discussed and selected in circuits design Chapter III.

With the optimal architecture is determined, a four-channel RF front-end is to be designed on-chip or on a PCB. In order to reduce the amount of hardware resources, multiplexing technique is applied after the RF front-ends so that one digitizer and other signal processing blocks can be shared by multiple channels. There exist two types of multiplexing technique, one is frequency domain multiplexing (FDM), and the other is time domain multiplexing (TDM) [4], [5], [15], [16].

# 2.2 Multiplexing Techniques

# 2.2.1 Frequency Domain Multiplexing

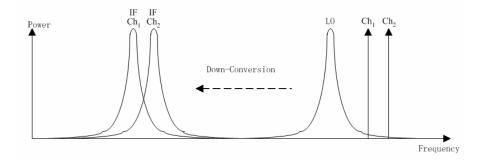

As illustrated in Figure 2.13, an operational amplifier (opamp) adds up the output voltages of each channel and sends them to the digitizer for digitization. After

digitization, each channel is separated by software (using digital filter) from the fourchannel digitized signals and is then ready for image reconstruction.

Figure 2.13 Frequency Domain Multiplexing (The blocks within the dashed line area are on-chip)

Compared with the RF front-ends in wireless communications application, which select a single desired channel from other signal channels and signal bands with different frequencies, the FDM, on the other hand, combines a certain number of channels with different frequencies into a multi-channel signal. Therefore, the FDM technique introduces the following two problems, which reduce the SNR of the MR signal.

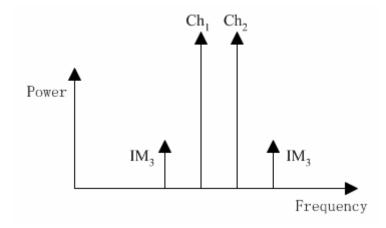

Problem 1: Signal to Distortion Ration (SDR) Reduced by Third Order Inter-Modulation (IM<sub>3</sub>) Products:

As shown in Figure 2.14, due to the nonlinearity of active components, when two signals, at different frequencies  $f_1$  and  $f_2$ , pass through the opamp, two IM<sub>3</sub> products are produced at the output of the opamp.

Figure 2.14 Third Order Inter-Modulation

Figure 2.15 Dynamic Range Reduced by IM<sub>3</sub> Products

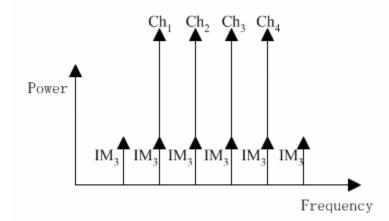

If four channels with the same channel spacing are added by the opamp, as illustrated in Figure 2.15, Ch<sub>1</sub> and Ch<sub>2</sub> produce IM<sub>3</sub> product on Ch<sub>3</sub>, while Ch<sub>2</sub> and Ch<sub>3</sub> produce IM<sub>3</sub> product on Ch<sub>1</sub> and Ch<sub>4</sub>, in addition, Ch<sub>3</sub> and Ch<sub>4</sub> produce IM<sub>3</sub> product on Ch<sub>2</sub>. These IM<sub>3</sub> products can be treated as noise and decrease the SNR of each channel of signal.

Therefore the linearity of the opamp has to be improved in order to decrease the effects of IM<sub>3</sub> products on the SDR. A term of "IIP<sub>3</sub>" is used in literature to denote the linearity according to the following equation

$$IIP_{3} = \frac{(P_{out} - IM_{3})}{2} + P_{in}$$

2.19

where  $P_{out}$  is the output signal power and  $P_{in}$  is the input signal power. We can assume that the SNR of a MR signal is 90dB for a 200MHz MRI experiment, and the gain of the opamp is 10dB, while the output signal power is 0dBm. We can easily compute that  $IIP_3 = 35dBm$  in order to ensure that the IM<sub>3</sub> products are smaller than the thermal noise, which is too high for an opamp design.

Solution of Problem 1: Frequency Re-Arrangement

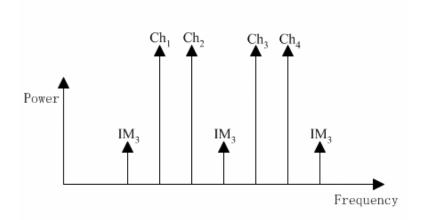

Figure 2.16 Frequency Re-Arrangement

If we re-arrange the frequency of each channel by increasing the channel spacing between Ch<sub>2</sub> and Ch<sub>3</sub>, from Figure 2.16, we can find that none of the IM<sub>3</sub> products is at

the same frequency of any channel. However, the total bandwidth of the multiplied signals is therefore increased, and the requirement of the sampling frequency of the ADC is tightened. Moreover, the channel spacing turns into un-even.

Problem 2: Effect of LO Frequency Phase Noise on the Down-Converted Signals

Figure 2.17 Effect of LO Frequency Phase Noise on the Down-Converted Signals

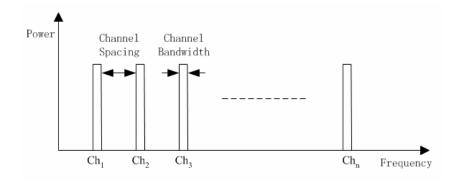

Because of the phase noise of the LO frequency, each down-converted IF signal contains the phase noise as illustrated in Figure 2.17. The phase noise of IF signal extends to adjacent channels, and therefore decreases the SNR of adjacent channels.

We can assume that the channel spacing (the frequency difference between the center frequencies of adjacent channels deducted by channel bandwidth a channel as illustrated in Figure 2.18.) is 100kHz, and the bandwidth of each channel is 20kHz. Normally, the LO frequency has a phase noise of  $-144 dBc/\sqrt{Hz}$ , at 100kHz offset for FLUKE 6080A [32] (The phase noise of another excellent frequency synthesizer HP

8656B is at the same level of FLUKE 6080A [33]), and therefore the phase noise energy of a certain channel on the adjacent channel is

$$-144 + 10 \times \log_{10}(2 \times 10^4) = -101 dBc$$

Figure 2.18 Illustration of Channel Spacing

If the channel spacing is smaller, for example, decreases to 20kHz, the phase noise of  $-141 dBc/\sqrt{Hz}$  at 20kHz offset for FLUKE 6080A, the phase noise energy of a certain channel on the adjacent channel is

$$-141+10 \times \log_{10}(2 \times 10^4) = -98 dBc$$

If the channel spacing continues to decrease, for example, decreases to 1kHz, the phase noise is  $-106 dBc/\sqrt{Hz}$  at 1kHz offset for FLUKE 6080A, and the phase noise energy of a certain channel on the adjacent channel is

$$-106+10 \times \log_{10}(2 \times 10^4) = -63 dBc$$

The following table is a summary of the calculated SNR of different offset frequency.

| Frequency Offset | 1kHz | 20kHz | 100kHz |

|------------------|------|-------|--------|

| SNR              | 63dB | 98dB  | 101dB  |

Table 2.1 SDR of Different Offset Frequency

From the calculation results, we can evaluate that the channel spacing needs to be close to about 20kHz in order to maintain the SNR larger than 90dB. Considering the channel bandwidth, the frequency spacing between the center frequencies of the adjacent channels has to be larger than about 20kHz plus channel bandwidth. That is 40kHz in this case.

The previous calculation is based on the assumption of 20kHz channel bandwidth. In order to generalize the calculation, we can denote the bandwidth as B. Therefore the equation of the SNR is

$$SNR = -(Phase\_noise + 10 \times \log_{10}(B))$$

2.20

That is, if the channel bandwidth is B, the SNR of a certain channel equals to the value in Table 2.1 deducted by  $10 \times \log_{10}(\frac{B}{2 \times 10^4})$ .

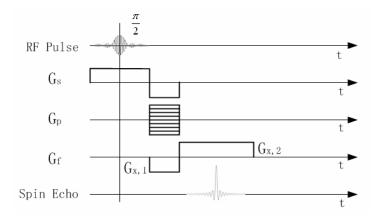

Based on the previous analysis, the application of the FDM approach on MRI is examined in the following. In parallel MRI experiments using phase array coils in [10], the spin echo signal is sensed and sampled by the RF front-end during the existence of the frequency encoding pulse, however, during this time interval, the phase encoding pulse does not exist as illustrated in Figure 2.19, therefore, the MR signal of each channel experiences the same frequency encoding and has the same carrier frequency. Therefore, the FDM approach can not be applied in parallel MRI experiments using phase array coils before the experiment is modified.

Figure 2.19 Gradient Echo Sequence for MRI

In another case, the SEA MRI experiment [3], [9], in which the coil array is placed parallel to the direction of main magnet field, and the slice selection gradient is orthogonal to the coil array plane, while the frequency encoding is along the direction of main magnet, the spatial localization provided by each phase encoding line is replaced by the spatial localization of each coil. In SEA, there is no phase encoding gradient and each coil experiences the same frequency encoding, and therefore, each MR signal from each coil has the same carrier frequency and FDM approach can not be applied in this case either before modification.

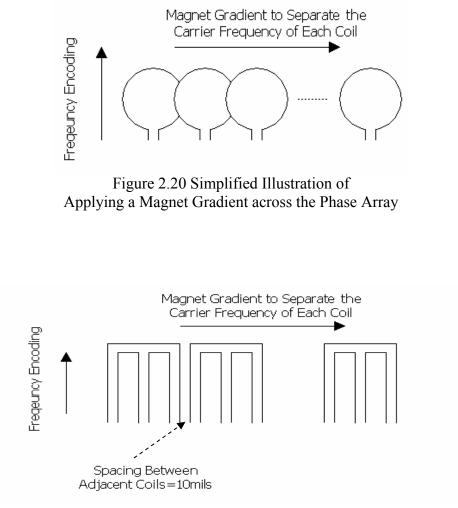

In order to explore the possibility of applying the FDM approach on parallel MRI experiments, an idea is proposed by applying a magnet gradient across the coil array, as

illustrated in Figure 2.20 and Figure 2.21 only to separate the carrier frequency of each coil.

Figure 2.21 Simplified Illustration of Applying a Magnet Gradient across the Planar Coil Array in SEA

As illustrated in Figure 2.20, each coil has a small part of its area overlapping its adjacent coils in order for decoupling, therefore, no matter how large the frequency separation magnet gradient is, frequency overlapping exists between adjacent channels

and therefore channel spacing is not larger than zero. Therefore the FDM approach can not be applied in this case although a magnet gradient is applied on the phase array to separate the center frequency of MR signal from each coil.

In the case of SEA, the spacing between the centers of the adjacent coils is 2mm, and the maximum frequency spacing between the center frequencies of the adjacent channels is 4kHz, therefore, using FDM, the SDR is limited. What is even worse, the channel bandwidth is mainly determined by the gradient of the frequency encoding because the length of each coil is much larger than the width of each coils. The bandwidth is possible to be much larger than the frequency spacing between the center frequencies of the adjacent channels. Therefore, frequency overlapping is possible to happen in this case.

Therefore, although the FDM approach provides a possible approach for parallel MRI experiment, based on the previous analysis, the approach is limited by bad SDR, and even can not be applied on parallel MRI experiments because of adjacent channel frequencies overlapping. As a possible method of overcoming these disadvantages, time domain multiplexing (TDM) technique is investigated.

# 2.2.2 Time Domain Multiplexing

The TDM receiver for MRI was first proposed and demonstrated as illustrated in Figure 2.12 by Wright et al. [4], [5], [15], [16]. (The down-conversion is dual-stage in [4], [5], [15], [16], and is simplified to single-stage in Figure 2.22 for the purpose of simplification.)

As illustrated in Figure 2.22, the RF switch is placed before the down-conversion mixer, and connects each signal source to the rest of the receiver chain in a sequence of time slots [16]. Each signal source is modulated by the switching waveform, and the resulting frequency spectrum of the modulated signal can be written as [16]

$$S_{mux}(f) = \sum_{n=-\infty}^{\infty} A_n S(f - nf_m)$$

2.21

where  $S_{mux}(f)$  is the modulated MR signal, and  $f_m$  is the switching frequency.  $A_n$  is given by

$$A_n = \frac{\sin(\frac{n\pi}{N})}{n\pi}$$

2.22

where N is the duty ratio of the switching waveform.

Figure 2.22 Multi-Channel RF Front-End with TDM

Investigating the frequency spectrum of the modulated signal, we can find that if a low-pass filter is placed anywhere after the RF switch, the high frequency part of the modulated signal is suppressed and crosstalk happens [16]. Therefore, the low-pass filter originally succeeding the mixer is removed, and instead, a band-pass filter is placed before the RF switch in order to attenuate the thermal noise.

Compared with its FDM counterpart, the TDM architecture solves the two problems described previously because the signals are time-multiplexed in TDM instead of being frequency-multiplexed. In addition, TDM also enjoys fewer numbers of mixers and needs only one VGA.

However, TDM architecture also has the following disadvantages:

- 1. Insertion loss is possible to be introduced by the RF switch.

- 2. The channel number is limited by the ADC sampling frequency.

- 3. Crosstalk is introduced by the limited time-constant,  $\tau = RC$ , or in other word, bandwidth, of the stages succeeding the RF switch. That is, the channel number is limited by the receiver bandwidth [5].

- 4. The band-pass filter before the mixer needs to be high order and therefore is expensive and lossy.

- 5. The band-pass filter is out-of-chip.

- 6. Because of 1 and 4, additional gain stage is necessary.

Moreover, if CMOS circuits are designed, the CMOS analog circuit designer has the following difficulties:

- 1. The circuit of high order band-pass filter is much more complex than the lowpass filter, and if designed on chip, the high order band-pass filter consumes a large chip area and introduces much noise.

- 2. The RF switch can be designed using CMOS switch, however, the large charge-

injection by the CMOS switch introduces voltage spike at the input of the mixer because the input capacitance of the mixer is required to be as small as possible in order to reduce the time-constant  $\tau = RC$ . If charge injection cancellation circuit is used, the complexity of the circuit increases, and thermal noise is introduced.

3. The conversion gain of the mixer is limited in order to reduce the input capacitance.

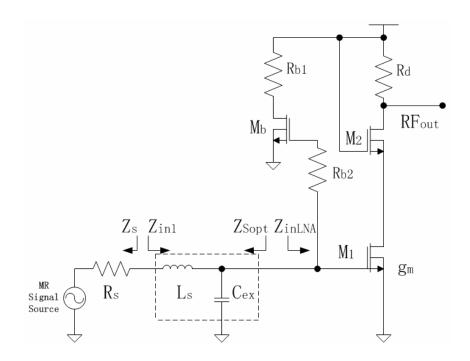

Therefore the following modified TDM architecture is proposed by moving the RF switch backwards to after the receiver front-end, as illustrated by Figure 2.23.

2.3 Proposed Multi-Channel RF Front-End with TDM

Figure 2.23 Proposed Architecture of the Four-Channel Front-End with TDM (The blocks within the dashed line area are on-chip)

As illustrated in Figure 2.23, the proposed architecture solves the originally TDM technique. First, the energy at frequency of  $f_{LO}+f_{RF}$  after the mixer is suppressed by the low-pass filter, and the bandwidth of this low-pass filter does not affect the crosstalk among the multiplexed channels because it is placed before the RF switch. Second, the band-pass filter in Figure 2.22 is removed. This makes it possible for fully on-chip design of the whole receiver because the high order band-pass filter is very difficult for on-chip design as discussed above. Third, the limited time constants of the mixer and the VGA do not cause crosstalk because the modulation of MR signal by the switching waveform happens after those stages.

#### CHAPTER III

#### CMOS CIRCUIT DESIGN OF THE RF FRONT-END

According to the discussion and the proposed architecture in Figure 2.23, a fourchannel RF front-end was designed using TSMC 0.18µm technology on a single silicon substrate. Each channel of the RF front-end includes an ultra low noise amplifier, a passive mixer with a TIA which also acts as a low-pass filter, a quadrature generator and a polyphase filter, another low-pass filter which also acts as a variable gain amplifier (VGA). The receiver has an overall NF of 0.935dB, variable gain from about 80dB to 90dB, power consumption of 30.8mW, and chip area of 6mm<sup>2</sup>.

### 3.1 Low Noise Amplifier Design

In MR experiment, the SNR of the MR signal from each planar coil is much smaller than the SNR of the MR signal from multi-turn solenoid coil because MR signal coupled by the planar coil is much smaller than that of multi-turn solenoid coil with the same size of its planar counterpart. Therefore, in order to maintain good image SNR, the NF of the RF front-end has to be as small as possible. In order to reduce the NF of the RF front-end, the NF of the LNA has to be as small as possible so that the noise introduced by the LNA is as low as possible, while the gain of the LNA has to be as large as possible in order to suppress the noise of the succeeding stages as much as possible.