# RADIO-FREQUENCY INTEGRATED-CIRCUIT DESIGN FOR CMOS SINGLE-CHIP UWB SYSTEMS

A Dissertation

by

YALIN JIN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2008

Major Subject: Electrical Engineering

# RADIO-FREQUENCY INTEGRATED-CIRCUIT DESIGN FOR CMOS SINGLE-CHIP UWB SYSTEMS

A Dissertation

by

## YALIN JIN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Cam Nguyen

Committee Members, José Silva-Martínez

Laszlo Kish Mark Everett

Head of Department, Costas N. Georghiades

May 2008

Major Subject: Electrical Engineering

#### ABSTRACT

Radio-Frequency Integrated-Circuit Design for CMOS Single-Chip UWB

Systems. (May 2008)

Yalin Jin, B.S., Xi'an Jiaotong University, China;

M.S., Chinese Academy of Sciences

Chair of Advisory Committee: Dr. Cam Nguyen

Low cost, a high-integrated capability, and low-power consumption are the basic requirements for ultra wide band (UWB) system design in order for the system to be adopted in various commercial electronic devices in the near future. Thus, the highly integrated transceiver is trended to be manufactured by companies using the latest silicon based complimentary metal-oxide-silicon (CMOS) processes. In this dissertation, several new structural designs are proposed, which provide solutions for some crucial RF blocks in CMOS for UWB for commercial applications.

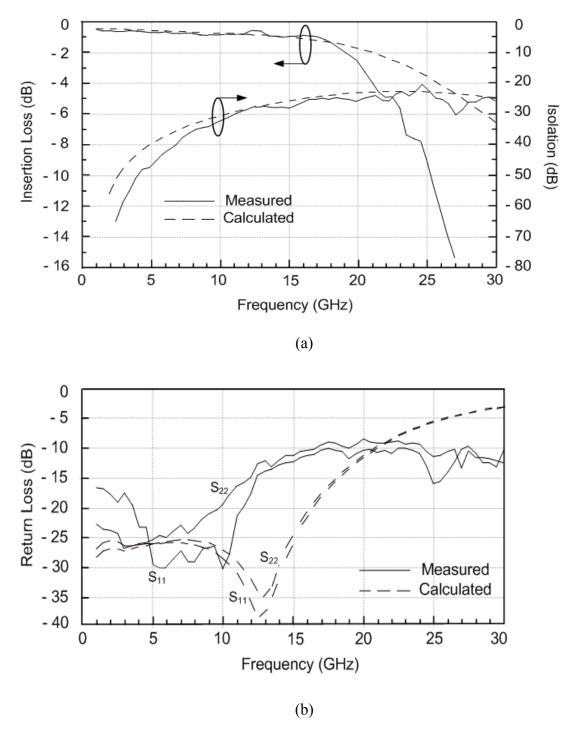

In this dissertation, there is a discussion of the development, as well as an illustration, of a fully-integrated ultra-broadband transmit/receive (T/R) switch which uses nMOS transistors with deep n-well in a standard 0.18-µm CMOS process. The new CMOS T/R switch exploits patterned-ground-shield on-chip inductors together with MOSFET's parasitic capacitances in order to synthesize artificial transmission lines which result in low insertion loss over an extremely wide bandwidth. Within DC-10 GHz, 10-18 GHz, and 18-20 GHz, the developed CMOS T/R switch exhibits insertion

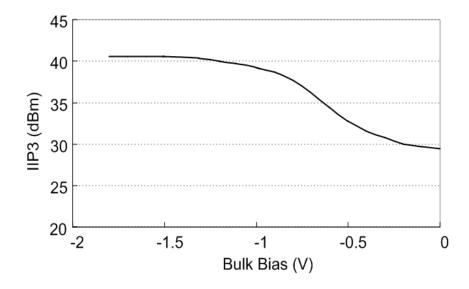

loss of less than 0.7, 1.0 and 2.5 dB and isolation between 32-60 dB, 25-32 dB, and 25-27 dB, respectively. The measured 1-dB power compression point and input third-order intercept point reach as high as 26.2 and 41 dBm, respectively.

Further, there is a discussion and demonstration of a tunable Carrier-based Timegated UWB transmitter in this dissertation which uses a broadband multiplier, a novel fully integrated single pole single throw (SPST) switch designed by the CMOS process, where a tunable instantaneous bandwidth from 500 MHz to 4 GHz is exhibited by adjusting the width of the base band impulses in time domain. The SPST switch utilizes the synthetic transmission line concept and multiple reflections technique in order to realize a flat insertion loss less than 1.5 dB from 3.1 GHz to 10.6 GHz and an extremely high isolation of more than 45 dB within this frequency range.

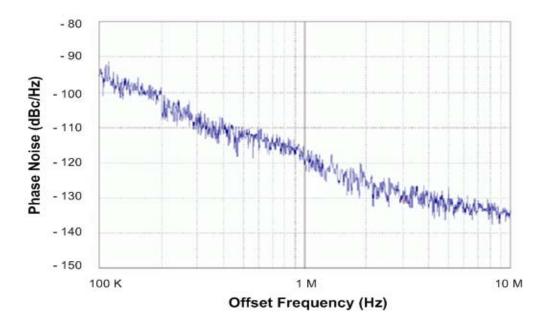

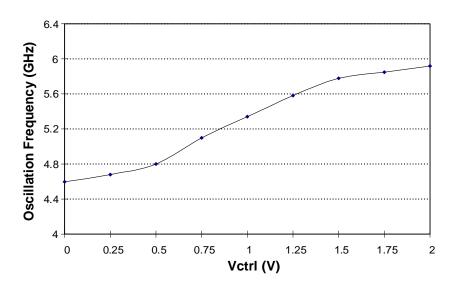

A fully integrated complementary LC voltage control oscillator (VCO), designed with a tunable buffer, operates from 4.6 GHz to 5.9 GHz. The measurement results demonstrate that the integrated VCO has a very low phase noise of –117 dBc/ Hz at 1 MHz offset. The fully integrated VCO achieves a very high figure of merit (FOM) of 183.5 using standard CMOS process while consuming 4 mA DC current.

#### **ACKNOWLEDGEMENTS**

This dissertation would not have been possible without the help and support of many people. First, I would like to thank Dr. Cam Nguyen, my dissertation advisor, and express my most sincere appreciation to him for directing me to this wonderful field of research and directing me. I am also indebted to him for helping me gain industry RFIC design practice that broadened my research knowledge and capability. His instruction and direction were instrumental in my efforts, as I pursued my research and experiments, by which I ultimately was able to produce through careful analysis the design for the world's first high-power, high-linearity, ultra-compact CMOS T/R switch for UWB applications and propose the new power-efficient UWB transmitter. He believed in me from the beginning and has been a constant source of encouragement throughout the duration of the dissertation process.

I sincerely thank my committee members, Dr. Silva and Dr. Kish, for their time, as well as for generously making themselves available to me and offering me many valuable suggestions during the course of my work. I am also very grateful to them for all that I learned from their courses on broadband systems and low noise circuitry. I am also indebted to Dr. Mark Everett who taught me about the many intricacies associated with EMI sensors.

The people at Alereon Inc. played important roles in the design of the first worldwide LO generator of all-band WiMedia MB-OFDM UWB and helped me with my work. Mark Cavin provided insights into the operations of the LO generator for a

direct conversion system. Bo Liang helped me avoid the pitfalls in electrical engineering that only experienced professors can understand. Oliver Werther and Angelika Schneider brought their insights to bear on my research and helped me understand the many difficulties in this field, which are a mystery to many engineers. Bob Renninger provided Verilog AD converters and helped me resolve the difficulties associated with band decoding.

My colleagues at Texas A&M University provided me with a great deal of technical assistance, enriched my experiences by their advice, and provided me with their friendship. Xin Guan shared with me his novel idea on broadband LNA. Rui Xu worked out with me the first carrier gated UWB covering 3.1 to 10.6 GHz, and Meng Miao helped with many practical matters, especially circuit layout and measurements. Mohan Chirala contacted the foundry and helped package the chip as well.

I would like to thank my parents and my elder brother for their love, support, and encouragement during my many years in the graduate schools. Finally, I would like to express my love and gratitude to my beloved wife, Jianli Wei, and my daughter, Grace Sicheng Jin, for the endless care and the happiness that they brought me throughout my graduate studies.

My work was also supported by the National Science Foundation, the Texas Advanced Research Program, and the Dell Computer Corporation. I thank them for their support and financial assistance.

# TABLE OF CONTENTS

|            |                                                             | Page |

|------------|-------------------------------------------------------------|------|

| ABSTRAC    | Γ                                                           | iii  |

| ACKNOWI    | LEDGEMENTS                                                  | v    |

| LIST OF FI | GURES                                                       | X    |

| LIST OF TA | ABLES                                                       | xiv  |

| CHAPTER    |                                                             |      |

| Ι          | INTRODUCTION                                                | 1    |

|            | 1.1 High Integration Trend of Wireless Product Circuitry    | 5    |

|            | 1.2 Direct Conversion Transceivers                          | 7    |

|            | 1.3 RFIC by CMOS Processes                                  | 9    |

|            | 1.4 Dissertation Organization                               | 13   |

| II         | CMOS RF SWITCH AND INTEGRATED INDUCTOR                      | 15   |

|            | 2.1 Switch Devices                                          | 15   |

|            | 2.2 MOSFET and MESFET                                       | 16   |

|            | 2.3 MOSFET with Floating Bulk                               | 19   |

|            | 2.4 Distributed Structure and Synthetic Transmission Line   | 22   |

|            | 2.5 Coplanar Spiral Inductor in CMOS                        | 24   |

|            | 2.5.1 First Order Planar Inductor Model                     | 26   |

|            | 2.5.2 Losses in Integrated Planar Inductors                 | 29   |

|            | 2.5.2.1 Metal Loss                                          | 29   |

|            | 2.5.2.2 Substrate Loss                                      | 33   |

|            | 2.5.3 Integrated Planar Inductor Design Guidelines          | 35   |

| III        | INTEGRATED BROAD BAND CMOS T/R SWITCH                       | 37   |

|            | 3.1 Integrated Transmit-Receive Switch for UWB Transceivers | 38   |

|            | 3.1.1 Performance Metrics for T/R Switch                    | 39   |

|            | 3.1.2 Previous Works                                        | 41   |

|            | 3.2 T/R Switch Design                                       | 43   |

|            | 3.2.1 Broad Band Topology                                   | 43   |

|            | 3.2.2 Linearity and Power Handling Enhancement              | 49   |

| CHAPTER |                                                                                          |

|---------|------------------------------------------------------------------------------------------|

|         | 3.2.3 Circuits Design                                                                    |

|         | 3.3 T/R Switch Performance                                                               |

|         | 3.3.1 Small Signal Measurements                                                          |

|         | 3.3.2 Linearity and Power Handling Measurements                                          |

|         | 3.3.3 Overall Performance Evaluation                                                     |

|         | 3.4 Summary                                                                              |

| IV      | INTEGRATED SINGLE- POLE SINGLE-THROW SWITCH AND TIME-GATED CARRIER-BASED UWB TRANSMITTER |

|         | 4.1 Carrier-based UWB                                                                    |

|         | 4.1.1 Carrier-based UWB Transmitter                                                      |

|         | 4.1.2 Broad Band Single Generation                                                       |

|         | 4.2 SPST Switch Design                                                                   |

|         | 4.2.1 On-state                                                                           |

|         | 4.2.2 Off-state                                                                          |

|         | 4.2.3 Fast Switching                                                                     |

|         | 4.3 SPST Switch Performance                                                              |

|         | 4.3.1 Measurements                                                                       |

|         | 4.3.2 Linearity Measurement                                                              |

|         | 4.4 UWB Signal Generations                                                               |

| V       | INTEGRATED LC VCO AND TUNABLE BUFFER                                                     |

|         | 5.1 Theory of Oscillators                                                                |

|         | 5.2 LC Oscillators                                                                       |

|         | 5.3 Voltage-Controlled Oscillators                                                       |

|         | 5.4 Phase Noise                                                                          |

|         | 5.4.1 Definition of Phase Noise                                                          |

|         | 5.4.2 Phase Noise Modeling                                                               |

|         | 5.5 CMOS LC VCO                                                                          |

|         | 5.5.1 Current-limited Regime and Voltage-limited Regime.                                 |

|         | 5.5.2 Complementary MOS vs. nMOS(pMOS)-only VCO                                          |

|         | 5.5.3 $1/f^3$ Phase Noise Mechanisms and Minimization                                    |

|         | 5.5.4 Figure of Merit (FOM) of VCO                                                       |

|         | 5.6 Complementary LC VCO Design                                                          |

|         | 5.6.1Design Strategy                                                                     |

|         | 5.6.2 Design Optimization                                                                |

|         | 5.6.3 Measurements                                                                       |

| VI      | SUMMARY AND CONCLUSION                                                                   |

|            | Page |

|------------|------|

| REFERENCES | 157  |

| VITA       | 168  |

# LIST OF FIGURES

| FIGURE |                                                                                                                                                                                                                                                                                                  | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1    | FCC UWB EIRP spectrum mask                                                                                                                                                                                                                                                                       | 2    |

| 1.2    | Simple RF transceiver architectures (a) Heterodyne or IF-based, and (b) Homodyne or direct conversion                                                                                                                                                                                            | 6    |

| 2.1    | Network to characterize a RF switch                                                                                                                                                                                                                                                              | 16   |

| 2.2    | Simplified MOSFET cross-section and physical origin of main RF small signal equivalent circuit elements                                                                                                                                                                                          | 18   |

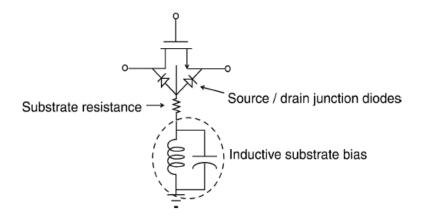

| 2.3    | MOSFET with inductive substrate bias                                                                                                                                                                                                                                                             | 20   |

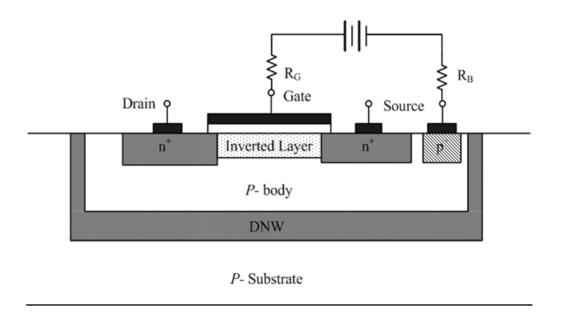

| 2.4    | Simplified physical structure of nMOS transistors with Deep N Well (DNW) under on state                                                                                                                                                                                                          | 20   |

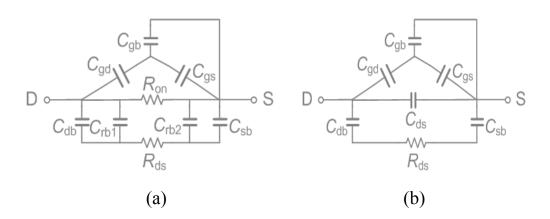

| 2.5    | Simplified small-signal equivalent-circuit models for MOSFETs with the bulk and gate floated under on-state (a) and off-state (b)                                                                                                                                                                | 21   |

| 2.6    | Lumped-element network representing one element of the artificial transmission line.                                                                                                                                                                                                             | 22   |

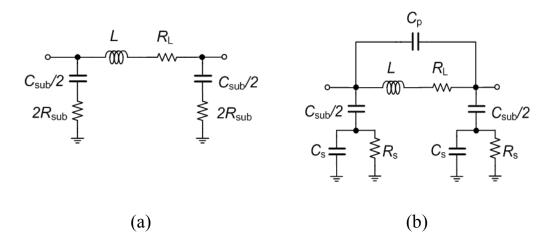

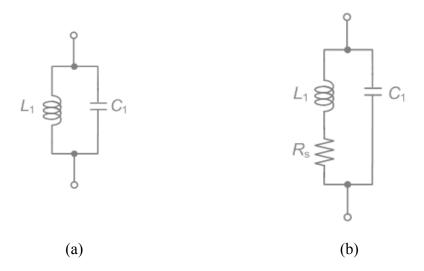

| 2.7    | First order models for passive integrated inductors: (a) simple and (b) extended                                                                                                                                                                                                                 | 28   |

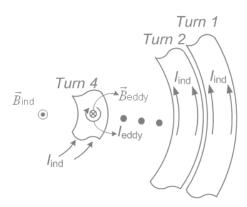

| 2.8    | Eddy current in the inner turns of planar inductors                                                                                                                                                                                                                                              | 32   |

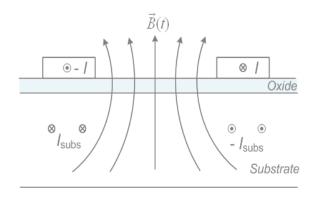

| 2.9    | Substrate currents underneath planar inductors                                                                                                                                                                                                                                                   | 33   |

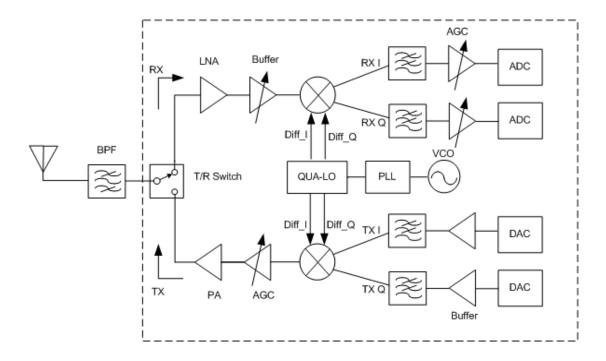

| 3.1    | Simple direct conversion transceivers for MB-OFDM UWB                                                                                                                                                                                                                                            | 38   |

| 3.2    | A series-shunt T/R switch topology using N type MOSFETs                                                                                                                                                                                                                                          | 41   |

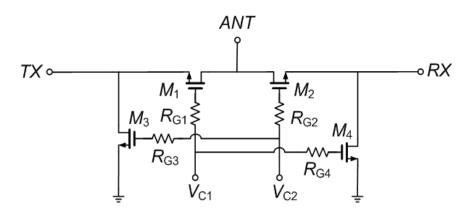

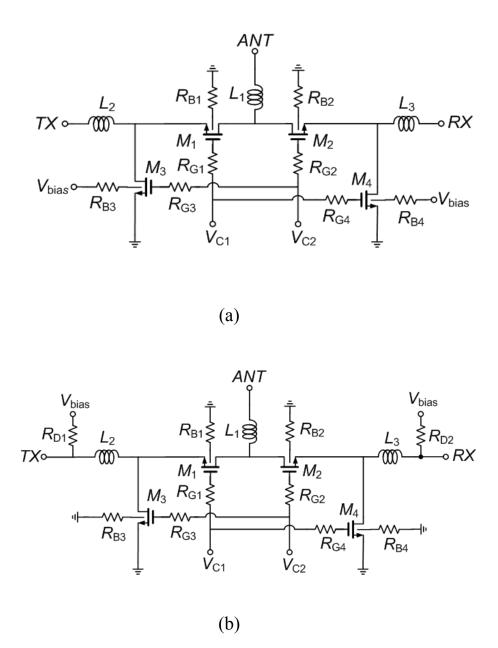

| 3.3    | Schematics of the CMOS T/R switch implemented using synthetic transmission lines with negative bias to the bulk (a) and positive bias to the drain (b) of the shunt nMOS devices. ANT, TX, and RX stand for the (input) antenna, (output) transmitter, and (output) receiver ports, respectively | 45   |

| FIGURE |                                                                                                                                                                                                               | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

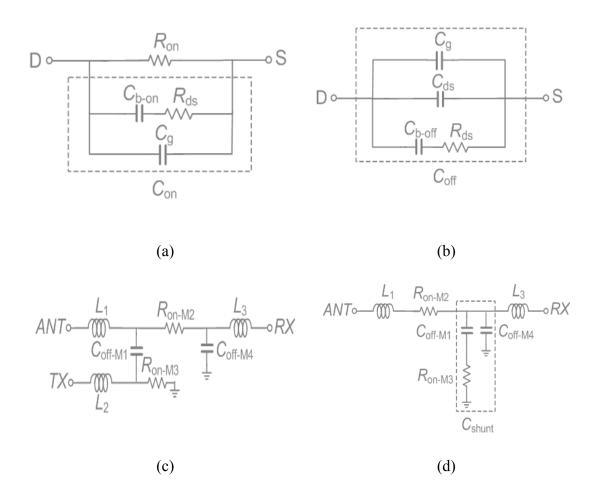

| 3.4    | Small-signal equivalent-circuit models of the MOSFETs under on (a) and off (b) conditions, the T/R switch with ANT-RX on and ANT-TX off (c), and the ANT-RX on-path (d)                                       | 47   |

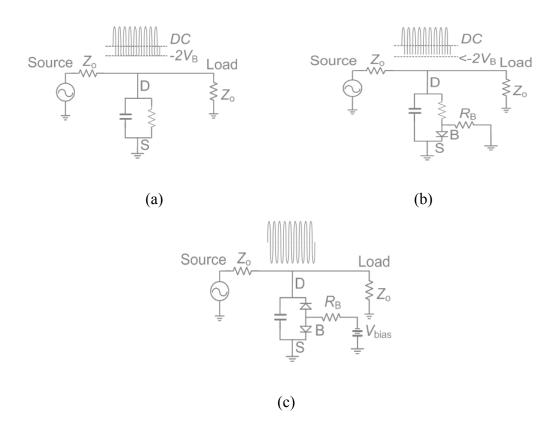

| 3.5    | Simplified large signal models for a shunt MOSFET with bulk grounded (a), floated (b), and negatively biased (c) for different linearity and power handling conditions. The sinusoidal signal is at the drain | 50   |

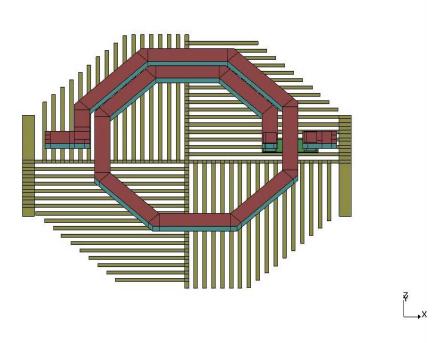

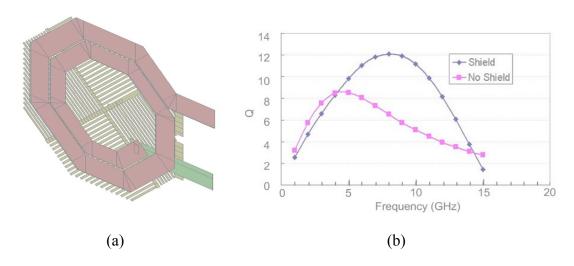

| 3.6    | Two-port S-parameter simulation of an inductor with PGS in IE3D                                                                                                                                               | 53   |

| 3.7    | 3-dimensional layout of the high Q inductor                                                                                                                                                                   | 54   |

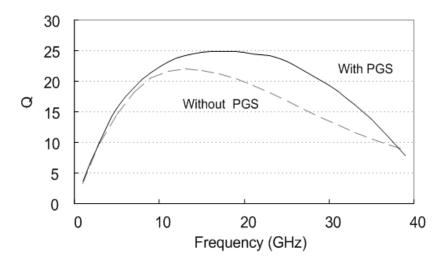

| 3.8    | Calculated Q of on-chip spiral inductors with and without PGS                                                                                                                                                 | 55   |

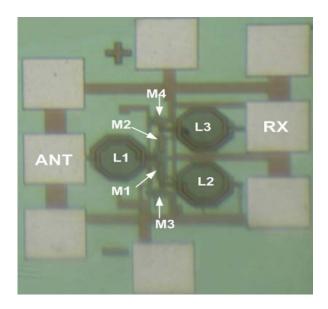

| 3.9    | Microphotograph of the CMOS T/R switch                                                                                                                                                                        | 58   |

| 3.10   | Measured and calculated insertion loss and isolation (a) and return loss at the antenna ( $S_{11}$ ) and TX/RX ( $S_{22}$ ) ports (b)                                                                         | 60   |

| 3.11   | IP3 measurements at 5.8 GHz by two-tone testing                                                                                                                                                               | 63   |

| 3.12   | Measured IIP3 at 5.8 GHz versus bulk bias voltage                                                                                                                                                             | 64   |

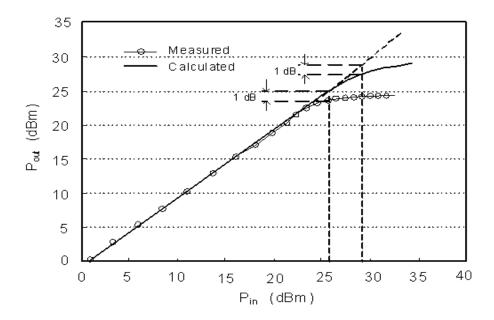

| 3.13   | P1dB testing at 5.8 GHz, the bulk bias voltage is -1.8 V                                                                                                                                                      | 64   |

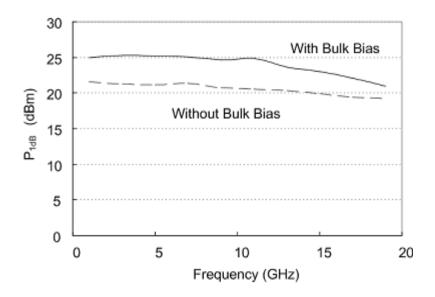

| 3.14   | Measured P <sub>1dB</sub> with 0- and –Bulk bias voltage                                                                                                                                                      | 65   |

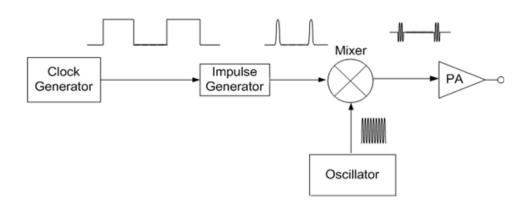

| 4.1    | Block diagram of a typical carrier-based UWB transmitter                                                                                                                                                      | 70   |

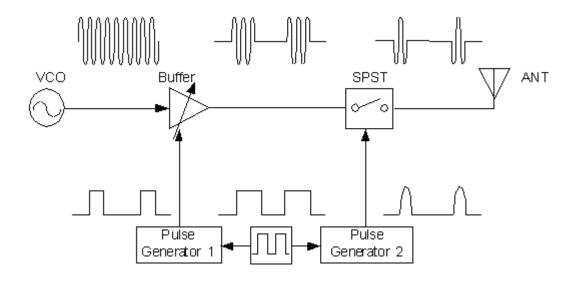

| 4.2    | The proposed carrier-based UWB transmitter topology                                                                                                                                                           | 72   |

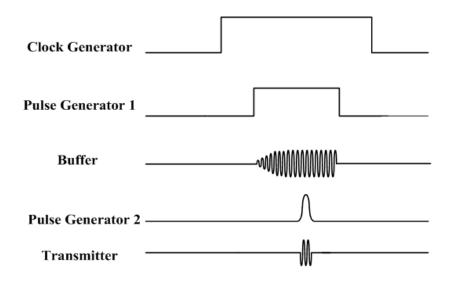

| 4.3    | Waveforms for the building blocks in the proposed UWB Transmitter                                                                                                                                             | 74   |

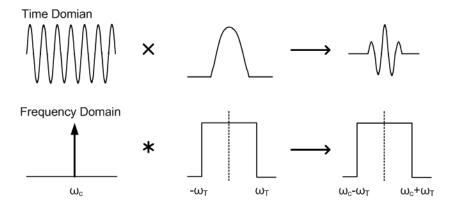

| 4.4    | Time-gated Carrier-based UWB single generation                                                                                                                                                                | 76   |

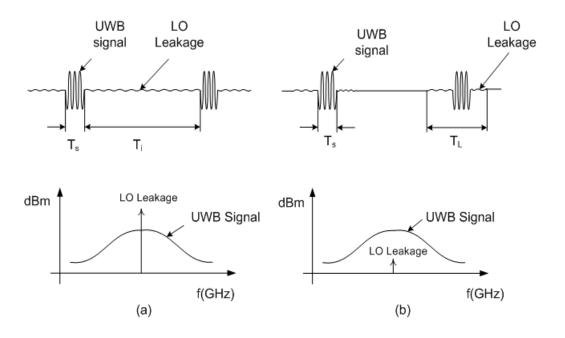

| 4.5    | Effects of power leakage using: (a) Single- and (b) double-stage switching                                                                                                                                    | 78   |

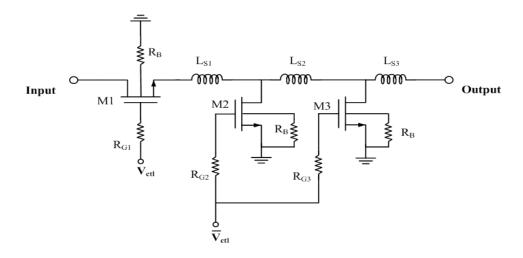

| 4.6    | Schematic of the broadband SPST switch                                                                                                                                                                        | 79   |

| FIG | FIGURE |                                                                                                                |     |

|-----|--------|----------------------------------------------------------------------------------------------------------------|-----|

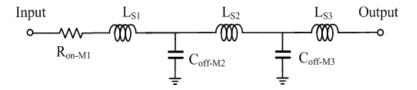

| ۷   | 4.7    | Equivalent network of the SPST switch working at on state                                                      | 81  |

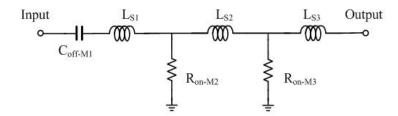

| ۷   | 4.8    | Equivalent network of the SPST switch working at off state                                                     | 83  |

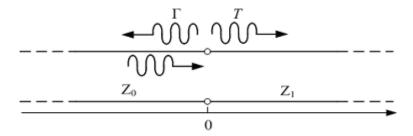

| ۷   | 4.9    | Reflection and transmission at the junction of two transmission lines with different characteristic impedances | 84  |

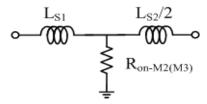

| 4   | 4.10   | T shape lump elements network consisting of two series inductors and a shunt MOSFET transistor                 | 85  |

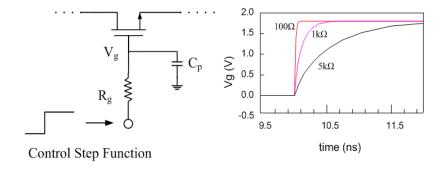

| ۷   | 4.11   | Schematic of the broadband SPST switch                                                                         | 88  |

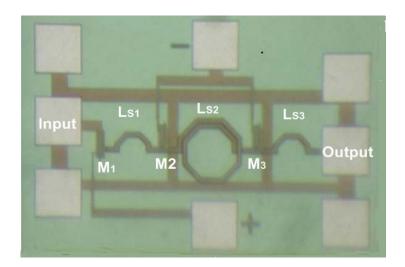

| ۷   | 4.12   | Microphotograph of the CMOS SPST switch                                                                        | 90  |

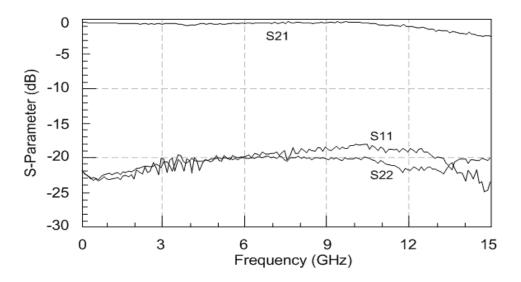

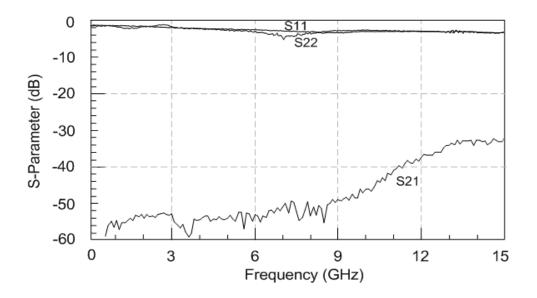

| ۷   | 4.13   | Measured S-parameters when the SPST switch is on                                                               | 93  |

| ۷   | 4.14   | Measured S-parameters when the SPST switch is off                                                              | 93  |

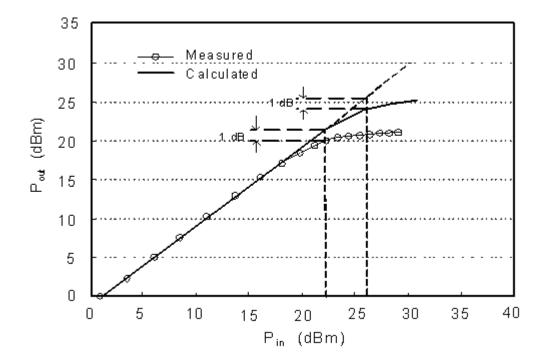

| ۷   | 4.15   | Simulated P1dB and measured P1dB of the SPST switch at 5.8 GHz                                                 | 94  |

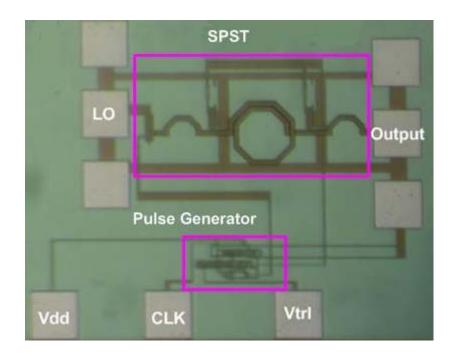

| ۷   | 4.16   | Microphotograph of the 0.18-um CMOS UWB demonstration chip integrating the pulse generator and the SPST switch | 97  |

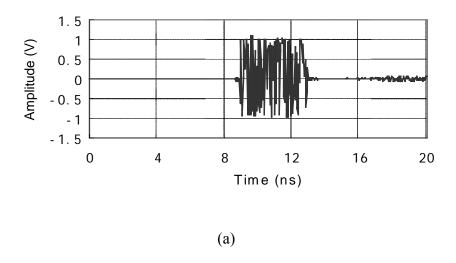

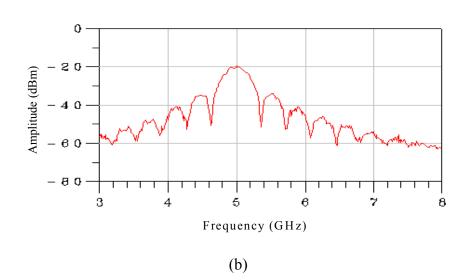

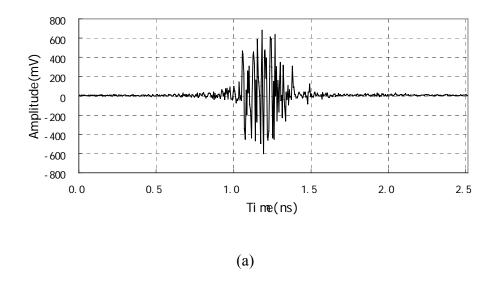

| ۷   | 4.17   | Measured UWB signal having 500MHz bandwidth                                                                    | 98  |

| ۷   | 4.18   | Measured UWB signal having 4GHz bandwidth                                                                      | 100 |

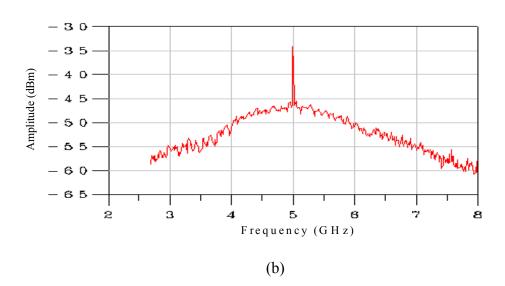

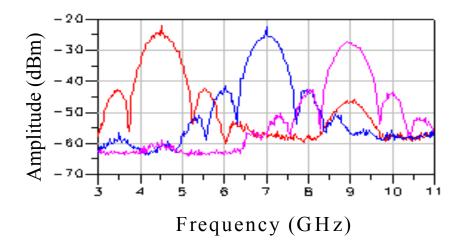

| ۷   | 4.19   | Measured spectrums of UWB signals covering the 3.1–10.6-GHz                                                    | 102 |

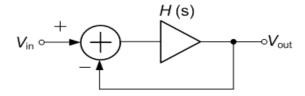

| 4   | 5.1    | A feedback system                                                                                              | 106 |

| 5   | 5.2    | (a) Ideal and (b) realistic LC tank                                                                            | 107 |

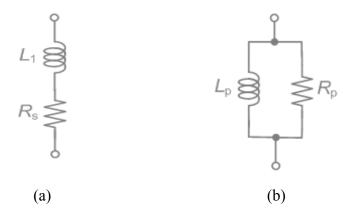

| 5   | 5.3    | Conversion of a series LR network (a) to a parallel LR network (b)                                             | 108 |

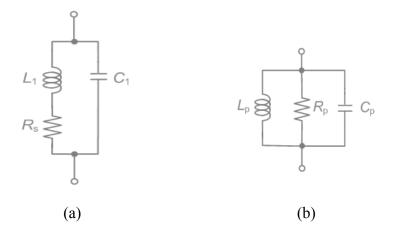

| 5   | 5.4    | Conversion of a tank (a) to a parallel LRC network (b)                                                         | 111 |

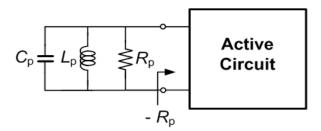

| 5   | 5.5    | Use of an active circuit to provide negative resistance                                                        | 112 |

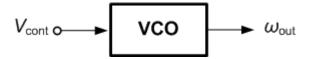

| 4   | 5.6    | Definition of a VCO                                                                                            | 115 |

| FIGURE |                                                                                                                                                     |     |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

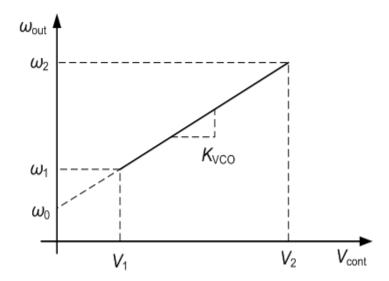

|        | The frequency (a) and time (jitter) (b) representation of phase noise in an oscillator at $\omega_0$                                                | 116 |

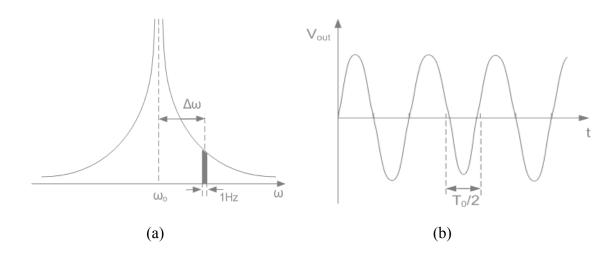

| 5.8    | From noise on the phase to the oscillator output spectrum                                                                                           | 119 |

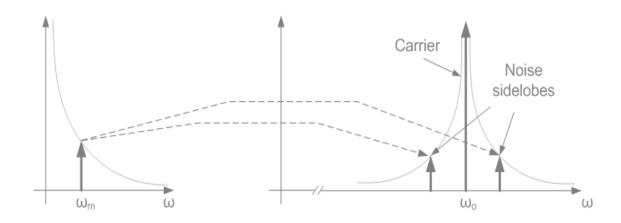

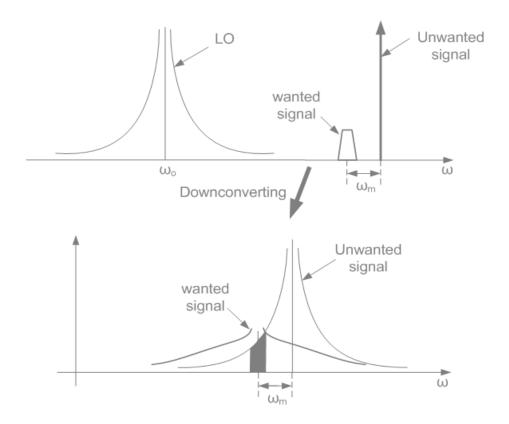

|        | The effect of phase noise on the reception quality of a communication system                                                                        | 122 |

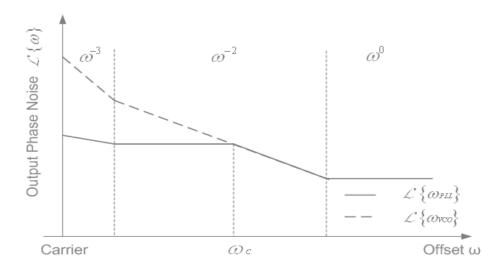

| 5.10   | The phase noise transfer functions in a PLL frequency synthesizer                                                                                   | 123 |

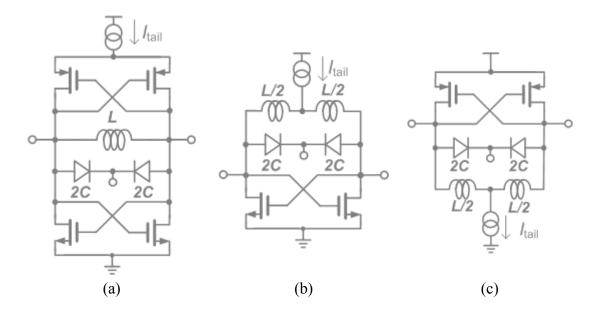

|        | VCO topologies. (a) complementary, (b) nMOS-only and (c) pMOS-only                                                                                  | 127 |

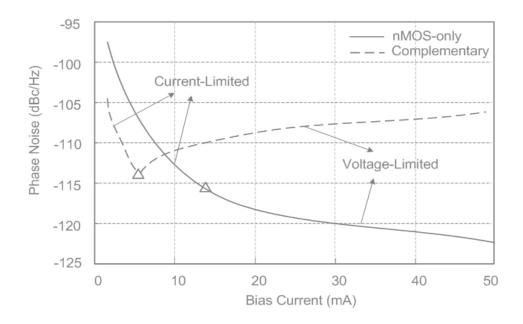

|        | Calculated phase noise at 1MHz offset versus the bias current for typical LC-tank and transistor parameters and $V_{DD} = 1.8 \text{ V}$ at 4 GHz   | 129 |

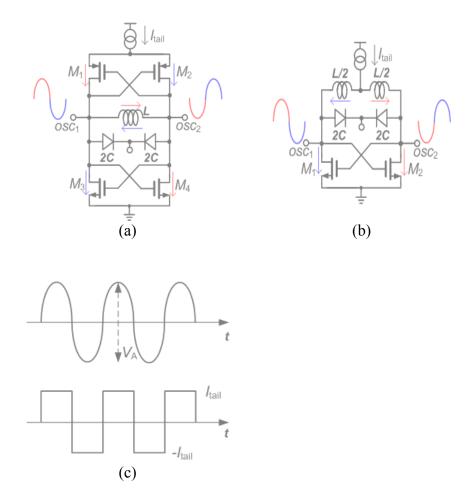

| 5      | (a) current switching in complementary LC VCO, (b) current switching in nMOS-only LC VCO, (c) output oscillation voltage and tank current waveforms | 132 |

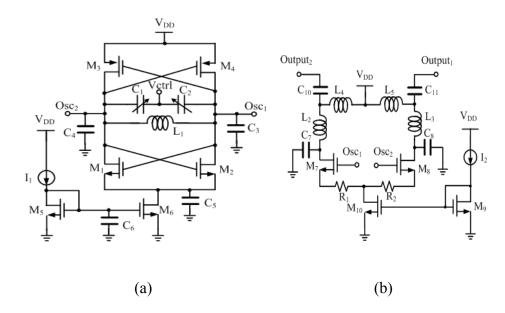

| 5.14   | Topologies of LC VCO and output buffer                                                                                                              | 139 |

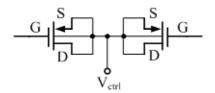

| 5.15   | Varactor pair                                                                                                                                       | 140 |

| 5.16   | (a) Tank inductor with PGS, (b) calculated quality factor of the inductor                                                                           | 141 |

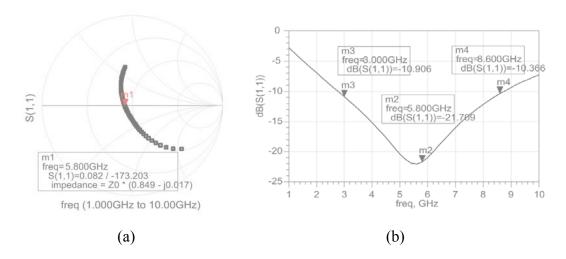

|        | (a) Output matching on Z-chart, (b) calculated return loss at the output port of the buffer                                                         | 147 |

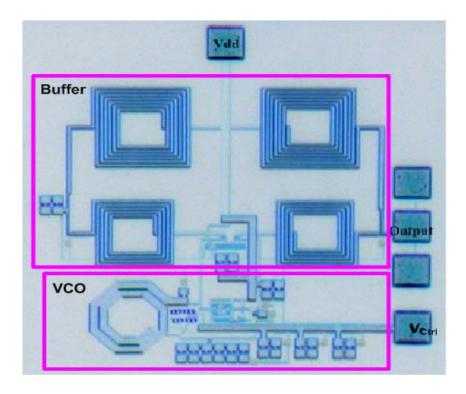

| 5.18   | Microphotograph of the complementary LC VCO and buffer                                                                                              | 148 |

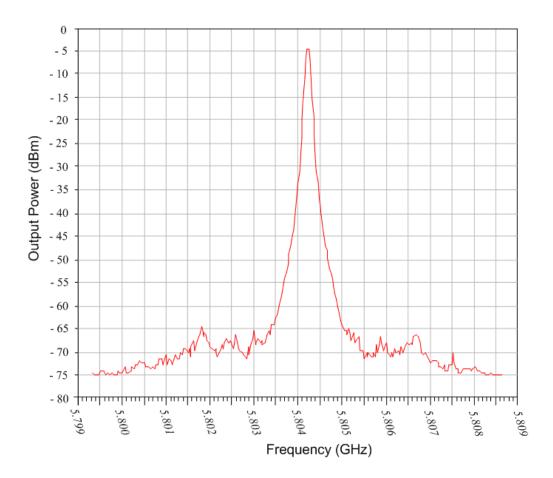

| 5.19   | Output spectrum with VDD = 1.8 V, Vctrl =1.75 V                                                                                                     | 149 |

| 5.20   | Measured phase noise at 5.8 GHz                                                                                                                     | 151 |

| 5.21   | Measured VCO tuning range versus control voltage                                                                                                    | 151 |

| 6.1    | UWB EIRP frequency mask regulation by Japan                                                                                                         | 154 |

# LIST OF TABLES

| TABLE |                                                      | Page |

|-------|------------------------------------------------------|------|

| 3.1   | Summary of the CMOS T/R Switch's Designed Parameters | 57   |

| 3.2   | Summary of CMOS T/R Switches                         | 68   |

| 4.1   | Summary of the Designed SPST's Components            | 89   |

| 5.1   | Summary of the CMOS VCO's Designed Parameters        | 144  |

| 5.2   | SpectreRF Simulations on the Noise Contributions     | 145  |

| 5.3   | Summary of the CMOS Buffer's Designed Parameters     | 146  |

## CHAPTER I

#### INTRODUCTION

When the Federal Communications Commission (FCC) agreed in February 2002 to allocate 7500 MHz of spectrum for unlicensed use of ultra-wideband (UWB) devices for communication applications in the 3.1-10.6 GHz frequency band [1], the move represented a victory in a long hard-fought battle that dated back decades. With its origins in the 1960s, when it was called time-domain electromagnetic, UWB came to be known for the operation of sending and receiving extremely short burst of RF energy. With its outstanding ability for applications that require precision distance or positioning measurements, as well as high-speed wireless connectivity, the largest spectrum allocation every granted by the FCC is unique because it overlaps other services in the same frequency of operation.

Previous spectrum allocations for unlicensed use, such as the Unlicensed National Information Infrastructure (UNII) band, have opened up bandwidth dedicated to unlicensed devices based on the assumption that "operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation." This means that the devices using unlicensed spectrum must be designed to coexist in an uncontrolled environment.

The style and format follow IEEE Transactions on Microwave Theory and Techniques.

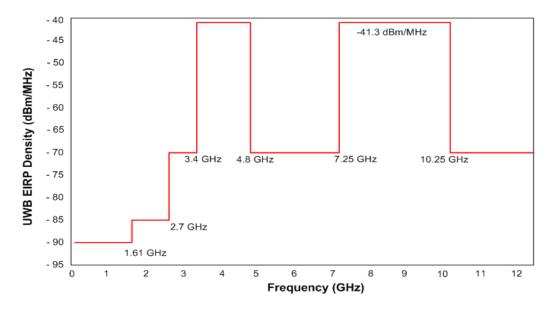

Devices utilizing UWB spectrum operate according to similar rules, but they are subject to more stringent requirements because UWB spectrum co-exists with other existing licensed and unlicensed allocations. In order to optimize spectrum use and reduce interference to existing services, the FCC's regulations are very conservative and require very low emitted power from UWB devices.

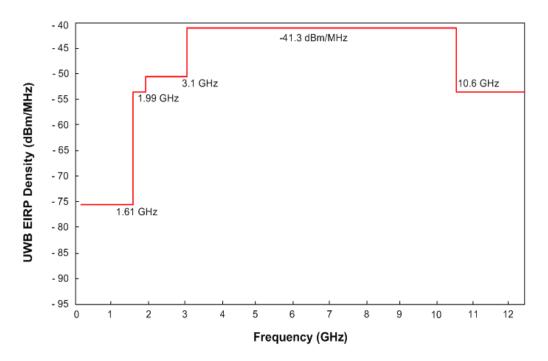

Figure 1. 1 FCC UWB EIRP spectrum mask. EIRP means Equivalent Isotropically Radiated Power from the transmitter antenna.

The FCC requires that UWB devices occupy more than 500 MHz of bandwidth in the 3.1-10.6 GHz band, according to the spectrum mask in Fig. 1.1. The power spectral density (PSD) measured in 1-MHz bandwidth must not exceed the specified - 41.24 dBm, which is low enough not to cause interference to other **services**, **such** as

Wireless Fidelity (WiFi) operating under different rules, but sharing the same bandwidth within the UWB frequency range.

This presents a serious challenge to any UWB system because other services sharing the same band of operation on licensed or unlicensed bands are likely to have a much higher transmit power and, therefore, would subject UWB receivers (RXs) to considerable interference.

This spectral allocation has initiated an extremely productive activity for industry and academia. Wireless communications experts now consider UWB an available spectrum to utilize with a variety of techniques, and not specifically related to the generation and detection of short RF pulse as in the past.

One of the most innovative techniques involves utilizing only 500-MHz instantaneous bandwidth (the minimum amount allowed by the FCC ruling) and dividing that frequency band into smaller simultaneously transmitted sub-carriers. Such systems present high regulatory flexibility for worldwide operation because they enable independent control of portions of the emitted spectrum to adapt for different environments. A design based on this idea is the most acceptable technical solution for very high bit-rate, low-cost, and low-power wireless networks for personal computing (PC), consumer electronics (CE), and mobile applications. These applications can be satisfied by relatively short-range systems, within a user's personal space, assuming that all other performance requirements is met. Systems developed to date, such as IEEE 802.11b, 11a, or 11g, do not address this market because they are designed to integrate longer-range wireless networks and are integrated on devices that can support higher

power consumption and cost. A specification is emerging today, led by the Multiband Orthogonal Frequency-Division Multiplexing alliance (MBOA), which is optimized to support these applications. The purpose of this standard is to provide a specification for wireless connectivity among devices within or entering the personal operating space. The data rate must be high enough (greater than 110 Mb/s) to satisfy a set of CE and multimedia industry needs for wireless personal area network (WPAN) communications. The standard also addresses the quality of service (QoS) capabilities required to support multimedia data types and mobile scenarios. There is also an extremely strong interest for even higher throughput and shorter range, up to 480 Mb/s, to support applications such as Wireless Universal Serial Bus (USB) or Wireless 1394 [2].

Devices included in the definition of personal area networks (PANs) are those that are carried, worn, or located near the body. Specific examples include devices that are thought of as traditionally being networked, such as computers, personal digital assistants (PDAs), handheld personal computers (HPCs), and printers. Also included are devices such as digital imaging systems, microphones, speakers, headsets, bar-code readers, sensors, displays, and pagers, as well as cellular and personal communications service (PCS) phones.

The long-term vision for these products is to enable personal devices with integrated wireless connectivity. Market considerations require that products be implemented in CMOS in order to achieve low-power and low-cost integration with other devices [3]. This is the best ticket to fulfilling the vision of integrated connectivity.

## 1.1 High Integration Trend of Wireless Product Circuitry

The synergism between economics and technological evolution, in hardware and software, drives wireless communication products to higher integration. If fact, the cost and ease of implementation of handsets becomes more critical, requiring aggressive reduction of the number of components. This evolution continues ultimately towards the radio frequency system on single-chip (RF-SoC) or the radio frequency system in singlepackage (RF-SiP) for all wireless products. The high integration trend requires architectural and technological innovations. For instance, the RF part of mobile phone has already move from super heterodyne to direct conversion architecture and in 2006 direct conversion has taken over 95% of the handsets. Technology has already moved from Gallium arsenide (GaAs) to silicon and is moving towards the most cost-effective solution using Complementary Metal-Oxide-Semiconductor (CMOS) process at RF frequencies (CMOS-RF or RF-CMOS). Although disbelievers claim that CMOS-RF will only be chosen for low-end, low-cost systems, while the much more powerful SiGe BiCMOS technology remains the choice for high-end systems, it has already been shown that CMOS has become the major process for most current wireless products, such as Global System For Mobile Communication (GSM), Code-Division Multiple Access (CDMA) and WiFi.

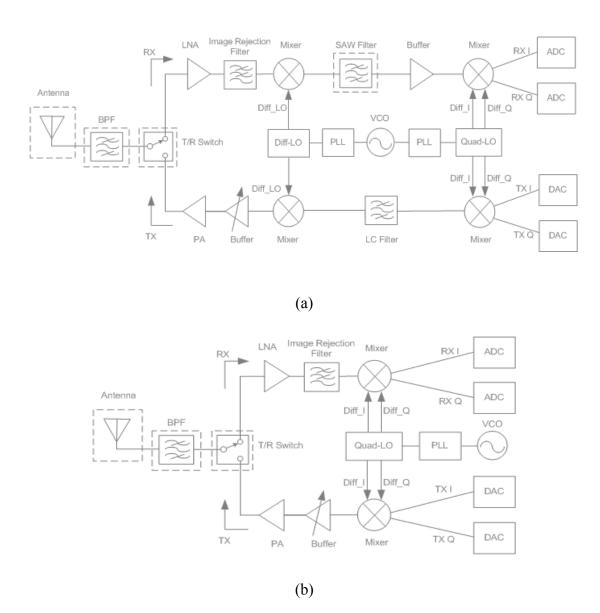

Figure 1.2 Simple RF transceiver architectures (a) Heterodyne or IF-based, and (b) Homodyne or direct conversion. The component count is significantly lower for homodyne system. The dashed blocks are currently external parts of integrated transceivers.

#### 1.2 Direct Conversion Transceivers

The wireless products consist of functionally two parts: the radio-frequency (RF) and analog front-end and base band digital back-end. The back-end of modern wireless products is already highly integrated. The RFIC design industry is increasingly looking at direct conversion architecture to facilitate higher integration by reducing the number of external components, which are, on the other hand, required by the traditional heterodyne RF architecture.

A sample heterodyne RF transceiver front-end is shown in Fig. 1.2 (a). In this architecture, the receive RF signals are first passed through a band pass filter, and then switched to a low-noise amplifier (LNA). Due to its gain, the LNA essentially sets the signal-to-noise ratio of the receiver chain. The amplified signals are filtered for improved image-rejection and down converted to an intermediate frequency (IF) with a mixer. The signals at IF are then filtered for channel-selection and shifted in frequency to baseband by a second mixer. The transmit process is complementary to the receive process. During transmission, the signals at baseband are upconverted to the RF frequency using an IF stage. A power amplifier (PA) is used to drive the antenna. A transmit-receive (T/R) switch is used to connect/disconnect the antenna during the transmit and receive processes respectively.

In the direct conversion or homodyne architectures, as in Fig. 1.2 (b), the receiver mixes the incoming RF signals with the carrier frequency to generate signals directly at

baseband. Similarly, the signals are directly upconverted to the RF carrier using only one mixing step during transmission.

Recently, the RF front-end has switched from conventional 90 years old superheterodyne receiver topology to direct conversion receiver. It is indicated that by 2007 a direct conversion receiver was used in 95% of all GSM cellular phones up from 40% in 2001. This is due to the fact that switching to direct conversion in GSM handsets and CDMA cellular phones reduces component costs as much as 30% and 70%, respectively [4].

Different flavors of direct conversion architectures exist in the receive as well as the transmit patch. Direct conversion receivers are zero-IF [5] and low-IF receivers [6]. Both architectures feature single-stage quadrature downconvesion without high Q filters. The architectures also fully exploit the digital circuitry capability of CMOS to include specially designed digital circuits in the chip to help improve the analog functions, such as image rejection, channel selection and demodulation. For instance, a digital circuit may adjust the phase of the I and Q channels of an image rejection mixer to help improve the image rejection. The bottlenecks of zero-IF receivers are  $^{1/f}$  noise, process mismatch-related offset, and self-mixing related offset that corrupt the wanted signal at low frequencies. The low-IF receiver alleviates this problem by setting the IF frequency to typically half the channel bandwidth [6]. If the external high Q, area expensive filters are removed, then higher demands on the analog building block performance are required, thus increasing the power consumption. For instance, if the filter is removed, then the differential mixer needs to be replaced with a quadrature

mixer so that good image rejection can be obtained, which leads to higher current consumption.

Direct conversion transmitters are mostly Cartesian I/Q modulators, which are in fact the equivalent of the zero-IF receive architecture. Quadrature up-conversion alleviates the need for high Q filters. Another direct conversion transmitter that is emerging is the direct modulation of a fractional-N synthesizer by the digital data, which presents an elegant and highly integrated solution [7].

## 1.3 RFIC in CMOS Processes

In the early 1980s, the GHz spectrum was mainly the territory of III-V compound semiconductors. Since the cost of silicon wafers is much lower than that of GaAs, silicon technologies become increasingly utilized in the market in the late 80s. Nowadays, SiGe bipolar transistor improved its current gain cut off frequency,  $f_T$ , to more than 100 GHz in 0.13  $\mu$ m process. In the total semiconductor revenue for digital and RF, GaAs only takes up 1% while silicon (Bipolar and CMOS) takes up 99% [8].

Among the currently used processes for RF front-end, i.e. CMOS, SiGe BiCMOS, SiGe Biploar and GaAs, the cost of a CMOS wafer is the lowest. Meanwhile, CMOS can benefit from a high-volume market, which aggressively scales technology to improve the digital performance, which at the same time improves the RF performance. The International Technology Roadmap for Semiconductors (ITRs) [9] predicts a transition to another process technology every 3 years. In reality, this happens every 2

years! While industry has maintained Moore's law for almost 30 years, some saturation in the scaling is expected when fundamental limits are reached, e.g. gate oxide thicknesses at atomic level. But performance can still be increased by advanced techniques, i.e. new materials like Cu interconnects, materials with small dielectric constants relative to silicon dioxide (low-dielectric-constant dielectrics) and more metal layers, all of which are at the same time beneficial for the RF performance of CMOS technology.

The main reason to favor CMOS for RF integration is certainly the cost. It has been estimated that RF-CMOS increases the wafer cost compare to pure CMOS by around 15%, due to Metal-Insulator-Metal (MIM) capacitances, resistances, and etc. But SiGe-BiCMOS increases the wafer cost by more than 40% [10]. In SiGe-BiCMOS, performance with low power is more easily obtained, but because of the lack of competition in this industry compared to CMOS, the price is not likely to decrease. Together with the compatibility of CMOS with the digital back-end, CMOS is an attractive cost-effective solution for integration of RF front-ends, with as goal full RF-SoCs.

It is worth examining the historic road maps of the RFIC developing towards CMOS and Direct-Conversion. The trend towards higher degrees of integration in the most cost-effective technology can be retraced in the history of mobile transceiver, presented by key publications. In the early years of mobile communications, all RF front-end ICs for cellular and cordless phones were integrated in Si bipolar, with good

examples as [11] in 1993 and [5] in 1994, where people already thought of a highly integrated solution by using zero-IF architectures [5].

In the following years, publications emerged with transceiver building blocks in BiCMOS due to the continuing improvement of mainly the bipolar transistor. In 1995, the first GSM transceiver ICs were published, [12] in BiCMOS and [13] in Si bipolar, both with superheterodyne architectures with external Surface Acoustic Wave (SAW) filter and LC-tank, loop filters.

In the same year CMOS made its entry in the GHz range with a 900 MHz low-IF receiver [6] and a high performance 1.8 GHz VCO [14]. From then on research for RF-CMOS took off rapidly. In 1998, the first single-chip CMOS transceiver, demonstrating the feasibility of achieving cellular specifications in CMOS, was presented by KULeuven [15]. The integrated circuit (IC) was intended for Digital Cellular System at 1800 MHz (DCS-1800) and combined a highly integrated low-IF receiver with a direct conversion transmitter, using an up-converter with a very low input IF and an on-chip VCO. Meanwhile, [16] [17] presented a 900 MHz single-chip transceiver for the Industrial, Scientific and Medical (ISM) band by RF-CMOS. In 1999, [18] demonstrated a single-chip transceiver for 900 MHz spread-spectrum cordless telephone with a direct conversion transceiver. A 5 GHz Wireless Local Area Network (WLAN) CMOS chipset with direct conversion transceiver was published by Bell Labs in 2000 [19]

It was in 2000 that the highly demanded technical barrier of the GSM cellular phone was overcome by the use of RF-SOC in CMOS. [20] presented a 2 V supply voltage CMOS cellular transceiver front-end for DCS-1800. This IC was the first single-

chip CMOS transceiver front-end with a complete on-chip PLL, including VCO and loop filter, that achieved all the requirements of the stringent DCS-1800 cellular system. Industry, on the other hand, mainly employed Bi-CMOS and bipolar, but became convinced of the feasibilities of the RF-CMOS, which is reflected in the first commercial CMOS transceiver chip set for GSM [21] [22].

In parallel, the integration of RF WLAN transceivers in CMOS gained more and more attention with a full session at the International Solid-State Circuit Conference (ISSCC) in 2001 on WLAN, featuring two CMOS Bluetooth transceivers [23], [24] and one CMOS Bluetooth SoC [25]. In 2002, more Bluetooth transceivers and a CMOS IEEE 802.11a transceiver [26] were published and even Universal Mobile Telecommunications System Third Generation (UMTs 3G) [27] and Wideband CDMA (WCDMA) [28] transceiver blocks in CMOS, were presented, proving the increasing interest and belief in RF-CMOS for research as well as commercial use.

Becoming a full session at ISSCC from 2005, UWB research, including Direct Sequence UWB (DS-UWB), gated pulses, and MB-OFDM, is mainly credited by universities. Industry was simultaneously launching UWB RF front-ends by SiGe Bi-CMOS [29] and RF-CMOS [30]. It is fore casted that MB-OFMD will exhibit a very fast development at the beginning of 2008. Also, in 2008, the first worldwide MB-OFDM UWB transceiver was published by industry [31]. Though still built by SiGe Bi-CMOS, it is no doubt that RF-CMOS is the utmost goal for UWB for various consumer electronics products because of its low cost, high-integration capability, and fairly good performance.

## 1.4 Dissertation Organization

This dissertation aims to demonstrate some strictly required building blocks and investigate new methods of designing RF switches for UWB radar and communication applications, with very impressive performances, in conventional RF-CMOS processes. A new way to generate timing gated multiple pulses for UWB is also presented for sensing applications, which diversifies the current UWB regimes. Chapter II discusses the detailed specifications that integrated CMOS switches need to meet so that they would be a viable alternative to the existing GaAs MESFETs. Then we propose a broadband alternative using MOSFET in tripe well whose substrate is biased using resistors. The focus of Chapter III is the ultra-wide band transmit/receive switch (T/R switch) design. A broadband topology with low loss, high linearity and compact layout is presented in detail with simulation and experiment. The measured results shows the best overall performance among the reported CMOS switches to date, and it is the first CMOS switch able to provide less than 1 dB loss over the entire UWB frequency span. In Chapter IV, a Time-gated Carrier-based UWB generation is presented with very low power consumption, and it's feasible of meeting FCC regulations. The key block of the transmitter, a single pole single throw switch (SPST) functioning as a multiplier in time domain, is discussed from the point of view of topology, simulation and experimental testing. Also the UWB signal generation method is demonstrated. Another key block of the UWB transmitter, a low phase noise, low harmonic integrated CMOS VCO, is the main topic of Chapter V. The key parameters of VCO associated with the topologies are discussed in detail and a new transistor level optimization method is proposed. Lastly, conclusions are summarized in Chapter VI.

## CHAPTER II

#### CMOS RF SWITCH AND INTEGRATED INDUCTOR

RF switch is an important building block in wireless transceivers. Operating at deep triode region with a small channel resistance, MOSFET is a very feasible device to implement integrated switches for various applications. For instance, a Transmit-Receive switch is the first block in the UWB integrated transceiver connecting external components like BPF or Antenna. The main consideration of the RF switch design is extremely broadband impedance matching with very low insertion loss in ON path and high isolation in the OFF patch. In this chapter, starting with a review of MOSFET physics functioning as a switch, a synthetic transmission line concept is presented by lump elements. Finally, design of high quality integrated monolithic inductors in CMOS process is analyzed.

#### 2.1 Switch Devices

In digital application, a switch device is characterized by metrics such as its switching speed, and input capacitance, etc. It must be noted that the switching speed is also affected by the loading capacitance caused by the subsequent component to the switch. For RF application, a switching device is commonly characterized with the help of the circuits of Fig. 2.1 in a 50-Ohms network. When the switch is closed and the signal passes through, some power is lost in the switch due to its imperfections. This loss

is commonly referred to as the insertion loss (IL) of the switch. In the close-sate, the linearity of the switch is specified by its one dB compression point,  $P_{1dB}$ . In the open-state, the switch blocks the signal from passing to the load and the attenuation by the switch is characterized as the isolation (ISO) of the switch. Insertion loss, linearity, and isolation are key metrics of a RF switch. Moreover, the RF switch, like the other RF blocks, must provide good input and output matching over the specific frequency range.

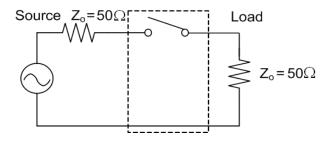

Figure 2.1 Network to characterize a RF switch. The impedances of the source and load are 50 Ohms. IL and linearity are measured when the switch is closed while the ISO is measured when the switch is open. The input and output matching are characterized by return losses.

## 2.2 MOSFET and MESFET

MESFETs are majority carrier devices, which make them suitable for high speed and high frequency operation. It can be implemented using silicon, GaAs, and InP. MESFETs implemented in silicon are incapable of handling large powers and typically are slower than those implemented using other materials, such as GaAs. MESFETs

implemented using GaAs are commonly used for high-power and high frequency applications. GaAs has a large band gap, and hence a large breakdown voltage that permits high-voltage operation without reliability concerns. Moreover, the high low-field mobility of GaAs enhances the usable bandwidth of the device. GaAs MESFETs also use a semi-insulating substrate, which further lowers loss in the device. The performance of GaAs switches currently achieves very low loss (< 1dB at 2 GHz) [32], high power (>1W) [32], and high frequency (20 GHz) [33].

The silicon-based MOSFET is currently the cheapest of all the switch options and it also enables to implement an RF switch integrated with other blocks to build a system on chip. The on-resistance of the silicon MOSFET, however, is significantly worse than a GaAs MESFET due to poor electron and hole channel-mobilities at low electric fields. Modern CMOS processes provide very small channel length MOSFETs with a good  $R_{on} \times C_{off}$  product, where  $R_{on}$  is the on-resistance while  $C_{off}$  is off-capacitance of the MOSFET respectively. Meanwhile, the thin gate oxide and small channel length permit a low voltage operation only, thus limiting the linearity and power handling capability. CMOS switches cannot be used for high-power RF applications. The normal performance of MOSFET switch at RF is poor compared to its GaAs counterparts. Various researches in CMOS switches have been widely pursued recently to improve the performance as the size of the MOSFET scaling down [34] [35].

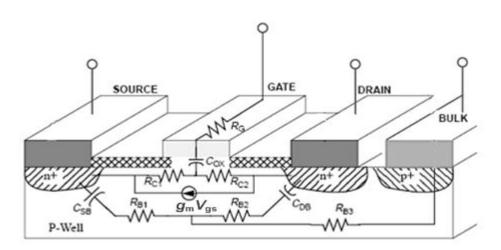

Fig. 2.2 shows an equivalent-circuit model of the MOSFET for RF applications. The gate resistance,  $R_G$ , is very small because of the multiple figure structure of MOSFET is normally implemented in the latest CMOS process resulting in a parallel

poly gate resistance. The channel resistances,  $R_{C1}$  and  $R_{C2}$ , and the substrate resistances,  $R_{B1}$ ,  $R_{B2}$  and  $R_{B3}$ , are the main sources of loss in the MOSFET. The substrate resistance,  $R_{B3}$ , can be reduced by grounding the substrate as close to the device as possible. The voltage controlled current source,  $g_m V_{gs}$ , stands for the capability of the MOSFET to convert the gate to source voltage,  $V_{gs}$ , into the current from drain to source, where  $g_m$  is the transconductance of the MOSFET. The low quality factor of the source and drain parasitic junction capacitors,  $C_{SB}$  and  $C_{DB}$ , can also lead to significant losses, especially as the frequency of operation increases. The linearity of the MOSFET switch is limited for large signal swings due to conductivity modulation caused by a changing gate-source (Vgs) and drain-source (Vds) voltage for a large signal input. Another cause of nonlinearity is the parasitic source and drain junction diodes which can clip the signal at about 0.7 V above the power supply (i.e., 0.7 V + Vdd) or 0.7 V below ground.

Figure. 2.2 Simplified MOSFET cross-section and physical origin of main RF small signal equivalent circuit elements.

## 2.3 MOSFET with Floating Bulk

In order to reduce the loss of the MOSFET switch, much work was done to optimize the size of MOSFET devices to compromise the on resistance and parasitic capacitance [34] [35]. Moreover, for a given size device, it might be noted that the loss caused by the substrate can be reduced by making the substrate resistance, R<sub>B3</sub>, very small, or making it extremely large [34]. The former idea induced the practice of shorting the substrate by paralleling hundreds of vertical contacts connecting bulk and P substrate [34]. The later thought is realized by making the substrate float at RF frequency [35].

Floating the bulk also helps to improve the linearity. In the MOSFET switch the gate is normally biased by a large resistor and hence the gate becomes a floating node. The gate voltage  $V_{\rm gs}$  remains approximately constant and is always higher than the source and drain voltages, which are equal, by the control voltage applied to the gate. The source/drain junction diodes can still turn on and distort the incoming signal with large voltage swings. When the source/drain diodes are turned on, the bootstrapping fails. While the floating bulk can be realized by an inductive bulk bias as shown in Fig. 2.3, [35], the parallel integrated LC tank connecting the substrate resistance, shown in Fig. 2.3, provides a high impedance at resonant frequency of the tank and thus enables the bulk floating at this frequency. The DC potential, on the other hand, is the same as the ground because there is no DC current flowing through the external bias inductor and the internal substrate resistor. Apparently, this technique is not acceptable for a

broadband switch as the LC tank resonates at a fixed frequency, thus limiting this to a very narrow band use.

Figure 2.3 MOSFET with inductive substrate bias.

Figure 2.4 Simplified physical structure of nMOS transistors with Deep N Well (DNW) under on state.

Resistively floating the bulk is made practical for broadband switch by using the triple well device provided by majority of commercial CMOS foundries [36]. Fig. 2.4 shows a simplified geometry of these nMOS transistors with the gate biased so that the devices are operated under on-state. The deep N well (DNW) separates the bulk of the nMOS transistors from the p-substrate. The p-n junctions between the p-bulk and n+regions form a pair of parasitic drain-bulk (or drain) and source-bulk (or source) diodes. With DNW, large resistors can be applied directly to the bulk of nMOS devices, making it float at high frequencies without latch-up problems that would result in RF ICs consisting of both nMOS and pMOS without DNW.

Figure 2.5 Simplified small-signal equivalent-circuit models for MOSFETs with the bulk and gate floated under on-state (a) and off-state (b). D and S stand for the drain and source, respectively.

Floating the bulk forces the bulk resistance,  $R_{B3}$  in Fig. 2.2, underneath the source and drain junctions open with respect to the ground, leading to a much smaller resistive loss in the conductive p-bulk than with the bulk grounded. Fig. 2.5 shows simplified small-signal equivalent-circuit models for the on and off states of floating-bulk MOSFETs when the gate is floated with a large resistor.  $R_{ds}$  represents the resistive loss in the p-bulk between the source and drain. Using large gate widths for advanced sub-micron CMOS devices can produce  $R_{ds}$  within several ohms, thereby resulting in low loss in the bulk.  $C_{gs}$  and  $C_{gd}$  represent the gate-source and gate-drain capacitances due to the overlapping between the gate and diffusion areas.  $C_{gb}$  represents the gate-bulk capacitance.  $C_{db}$  and  $C_{sb}$  are the junction capacitances between the drain-bulk and source-bulk, respectively.  $C_{rb1}$  and  $C_{rb2}$  in Fig. 2.5 (a) represent the distributed capacitances between the inversion layer and bulk.  $C_{ds}$  in Fig. 2.5 (b) is the source-drain diffusion capacitance in a multi-finger MOSFET.

## 2.4 Distributed Structure and Synthetic Transmission Line

Synthetic transmission lines can be used to alleviate the bandwidth limitation in

Figure 2.6 Lumped-element network representing one element of the artificial transmission line.

RFICs [37]. A synthetic transmission line can be created by cascading multiple sections of an identical series inductor and shunt capacitor, shown in Fig. 2.6, whose inductance and capacitance can be properly chosen to realize a particular characteristic impedance and velocity. Such a synthetic transmission line approximates a transmission line over a finite bandwidth. The characteristic impedance of the artificial transmission line and its phase velocity can be found, respectively, as

$$Z_0 = \sqrt{\frac{L}{C}} \tag{2.1}$$

Where  $Z_0$  is the characteristic impedance of the artificial transmission line.

$$v_P = \sqrt{LC} \tag{2.2}$$

Where  $v_P$  is the phase velocity of the artificial transmission line.

For  $f \ll f_C$ , where  $f_C$  is the cut-off frequency of the artificial transmission line, which normally determines the bandwidth of the distributed structures, given as

$$f_c = \frac{1}{\pi \sqrt{L \cdot C}} \tag{2.3}$$

If the desired characteristic impedance  $Z_0$  of the transmission line is fixed, the cut-off frequency  $f_C$  can be expressed as

$$f_c = \frac{1}{\pi \cdot C \cdot Z_0} \tag{2.4}$$

(2.4) shows that the bandwidth of an artificial transmission line decreases as the value of the capacitance C increases.

Distributed amplifier is well known to have broadband gain flatness by using the artificial transmission lines [38]. The basic design principle of distributed amplifiers is based on forming two artificial transmission lines at the input and output ports of the constituting gain cells by periodically combining serial inductive components with the parasitic capacitors of the gain cells. Essentially, the input and output capacitances are absorbed into the artificial transmission lines, resulting in an extremely wideband performance.

This concept inspires the design of the broadband RF switch in CMOS, where the MOSFET transistor normally has various parasitic capacitances, such as  $C_{gb}$ ,  $C_{gs}$ ,  $C_{gd}$ ,  $C_{db}$  and  $C_{sb}$ , is shown in Fig. 2.5.

# 2.5 Coplanar Spiral Inductor in CMOS

The high-quality inductor is one of the important passive structures for RFIC design. One way to realize high quality inductors with large inductances is gold bonding

wires [14], which are readily available in the IC assembly process. Since gold is highly conductive, the resistive loss of the bonding wire is very low. The parasitic capacitance is limited and mainly due to the bonding pads. However, due to lack of yield and repeatability (variations of  $\pm$  6%) the technique is less popular for mass production.

For monolithic integration, planar spiral inductors laid out in standard metal routing levels of the IC remain the desired topology of designer looking for inductors. The cost of this solution is lower that that of bonding wire inductors and the die area is reduced with an order of magnitude. Most importantly, the yield and repeatability is almost perfect since processing accuracy (< 0.1  $\mu$ m) is negligible with respect to the inductor size (100  $\times$  100  $\mu$ m<sup>2</sup>). Although the integrated planar inductor is the most elegant solution, its quality is limited by several parasitics. The most important one is the metal resistance, which increases for higher frequency due to the skin effect and eddy currents, and substrate losses, especially for highly doped CMOS substrates. To decrease the series resistance, multi-level and extra thick metallization, which is a standard feature in most modern deep-submicron processes, are used. To eliminate substrate losses, the substrate is selectively etched away underneath the inductor [39]. However, the extra post-processing steps associated with the etching undermine the main advantage of the planar integrated inductor, i.e. its low cost.

Therefore, the following section focuses on the integration and analysis of optimal high-quality planar inductors in standard CMOS technology, without tuning, trimming, or extra post-processing steps.

### 2.5.1 First-Order Planar Inductor Model

Integrated planar inductors are mostly designed using a spiral-shaped metal connection routed in one or more of the standard available metal levels. A general reference for extensive calculations of planar rectangular micro-electronic inductors is given in [40]. The famous Greenhouse article presents a method for accurately calculating the inductance value, based on summing or subtracting of the appropriate self- and mutual inductance values of the different segments of the inductor. Calculation of the total inductance value of a full spiral inductor involves the calculation of every mutual inductance between every possible couple of segments. Due to the large number of calculations, the formulas can be embedded in a custom computer program, yielding quite accurate results for the calculated inductance value. Unfortunately, the Greenhouse method does not support segments with 45° angles and does not provide calculation for the parasitic losses in the inductor.

In [37], several crude (0th order) calculations are given for integrated spiral inductors. These formulas are only useful for quick hand-calculations as a starting point for inductor design prior to verification with a field solver. This formula is used for the construction of a square spiral inductor:

$$L \approx \mu_0 n^2 r = 4\pi \cdot 10^{-7} n^2 r \tag{2.5}$$

With  $\mu_0$  the magnetic permeability of free space, n the number of turns and r the radius of the spiral in m. Again, the calculations are only valid for rectangular inductors.

Quality factor,  $\mathcal Q$  , is normally used to describe the quality of the inductor and is generally defined as:

$$Q = 2\pi \cdot \frac{\text{Energy stored}}{\text{Energy dissipated per cycle}}$$

(2.6)

Where the energy stored in the magnetic field is of importance, not the electrical energy, which is counterproductive for an inductor. The higher the  $\mathcal Q$ , the better the inductor.

It is known that the circular shape inductor has the best  $\mathcal Q$  among the various shapes of spiral inductors because it has the shortest winding metal and hence smallest series resistance. But to today, any 0th order formula does not provide accurate calculations to the circular spirals. On the other hand, today's CMOS processes support  $45^{0}$  angles winding, enabling the integration of octagonal inductors, which better approximate the  $\mathcal Q$  of a circular inductor.

Generally, a complete passive inductor can be modeled by the simple equivalent circuits shown in Fig. 2.7 (a). The inductor L has a parasitic resistance  $R_L$  and a capacitance  $C_{\text{sub}}$  to ground, mainly the oxide capacitance, in series with the substrate resistance  $R_{\text{sub}}$ . An extension to the simple model is shown in Fig. 2.7 (b). Shunt capacitance  $C_p$  over the inductor mainly takes into account the capacitance of the cross-

under metal line to connect the inner turns to the outside world. This capacitance is alleviated by balanced or differential inductor design.  $C_{ox}$  is the actual oxide capacitance between the inductor and the substrate.  $C_{s}$  and  $R_{s}$  are the capacitance and the losses of the actual substrate, including loss current through the oxide and eddy currents induced in the substrate by magnetic fields. This extended model can be fitted onto the measured data of almost every integrated spiral inductors up to 20 GHz [41].

Figure 2.7. First order models for passive integrated inductors: (a) simple and (b) extended.

Based on the first order model of the inductor shown in Fig. 2.7, the formula of quality factor of the inductor,  ${\cal Q}$  , is given by

$$Q = \frac{\omega L}{R_L} \cdot \left[ 1 - \left( \frac{\omega}{\omega_0} \right)^2 \right]$$

(2.7)

Where L is the inductance,  $R_{\rm L}$  is the series resistance, and  $\omega_0$  is the self-resonance frequency of the inductor. Note that Q is zero at the DC and self-resonance frequency, and has a peak value at one midrange frequency. By making the derivative of (2.7) as zero, the peak Q value,  $Q^{\rm max}$ , and the frequency giving a peak Q,  $\omega^{\rm max}$ , can be derived as

$$Q_{\text{max}} = \frac{2}{3} \cdot \frac{\omega_0 L}{R_L} \text{ and } \omega_{\text{max}} = \frac{\omega_0}{\sqrt{3}}$$

(2.8)

Though the losses mechanisms are more complicated and will be described in the following section, the first order model helps in designing high Q planar inductor by optimizing the layout for low loss and high self-resonance frequency.

# 2.5.2 Losses in Integrated Planar Inductors.

## 2.5.2.1 Metal Loss

For lower operating frequencies, the series resistance of the inductor is the DC resistance of the metal tracks, i.e. the product of the sheet resistance of the metal and number of squares of the metal tracks. Therefore, multiple metal layers should be used as much in parallel as possible to reduce the DC resistance of the metal. But this stacked parallel does lower the self-resonance frequency due to lower layers bringing larger

parasitic capacitance. At high frequencies, there are two effects causing a non-uniform current distribution in the metal tracksresulting in increased metal losses: the skin effect and eddy currents. The skin effect pushes the current to the outside of the conductor, such that 63% of the current is contained within a skin depth,  $\delta$ , defined by (2.9), where  $\sigma_M$  is the conductivity of the metal and  $\mu_0$  is the magnetic permeability of free space which is very close to that of aluminum and copper. The effective area of the conductor is reduced so that the current flows and hence the resistance increases. Due to the skin effect, the current density is  $J = J_s \cdot e^{-x/\delta}$ , where J is the current density of at the depth x and Js is the surface current density. So the effective depth with uniform Js density can be estimated as Eq. (2.10), where d is the effective depth and T is the actual thickness of the metal.

$$\delta = \sqrt{\frac{2}{\omega \mu_0 \sigma_M}} \tag{2.9}$$

$$d = \int_0^T J_s \cdot e^{-x/\delta} dt / J_s$$

(2.10)

The effective depth can then be calculated roughly as  $\delta(1-e^{-T/\delta})$ . The effective resistance of the metal can then be described by Eq. (2.11).

$$R_{L,\delta} \approx \frac{L}{W \cdot \sigma_M \cdot \delta \left(1 - e^{-T/\delta}\right)}$$

(2.11)

Where L and W are the length and width of the metal and  $R_{L,\delta}$  is the effective resistance of the metal due to the skin effect. For aluminum used for IC interconnects,  $\sigma_{Al} = 3.33 \cdot 10^{-7} \ 1/(\Omega \cdot m)$ , such that the skin depth is approximately  $\delta_{Al} \approx 1.95 \,\mu m$  at 2 GHz and  $0.87 \,\mu m$  at 10 GHz. For copper,  $\sigma_{Cu} = 5.95 \cdot 10^{-7} \ 1/(\Omega \cdot m)$ , such that the skin depth is approximately  $\delta_{Cu} \approx 1.46 \,\mu m$  at 2 GHz and  $0.65 \,\mu m$  at 10 GHz. It is apparent that due to the skin effect very wide metal tracks are useless in high-frequency inductors, since only a small part of the conductor is actually used, especially for better conductive material.

A second effect is eddy currents generated in the metal by the magnetic field of the inductor. The situation is depicted in Fig. 2.8 for one side of the inductor with 4 turns carrying a counter-clockwise current  $I_{ind}(t)$ . This current generates a magnetic field  $\overset{1}{B}_{ind}(t)$ , which is most intensive in the center of the inductor. The magnetic field is perpendicular to the page and pointing out in the center  $\overset{e}{e}$ . For an inductor with traces in the inner turns, the magnetic field goes through the inner turns instead of through the center of the inductor. It induces eddy currents in these inner turns, which induce an opposite magnetic field  $\overset{1}{B}_{eddy}(t)$ . The counteracting field decreases the inductance significantly at higher frequencies. Moreover, the eddy current  $I_{eddy}$  causes a non-uniform current distribution dramatically in the inner conductors: At the outer side of the conductor, the eddy currents cancel the inductor current, i.e. the total current is pushed to the inside of the conductor. As a result, at higher frequencies, the resistance of the inner

turns increases dramatically. To maintain the inductor quality, "hollow" inductors should be designed with no inner turns.

Since the losses with these two effects are too complex to calculate analytically, a full Electromagnetic (EM) Simulator is necessary for high frequency inductor optimization.

Figure 2.8 Eddy current in the inner turns of planar inductors.

Figure 2.9 Substrate currents underneath planar inductors.

### 2.5.2.2 Substrate Loss

Previous CMOS technologies use epi-wafers with a heavily doped and low resistive substrate. Although beneficial for digital design, it is a killer for analog and GHz RF circuits' design. In highly conductive substrates, current induced by the magnetic field of the inductor are free to flow, causing extra resistive losses in the substrate and degradations of both inductance and quality factor. Fig. 2.9 gives a typical cross section of a one turn planar inductor on a silicon substrate. The inductor carries a current I at one moment in time (direction denoted by  $^{\rm e}$ , out of page and  $^{\odot}$  into the page), inducing a magnetic field  $^{\rm h}$ . According to Daraday-Lenz, this field induces counteracting currents in the substrate,  $I_{subs}$ . The larger the inductor, the larger the magnetic field penetration in the substrate and the more currents, and thus losses are

induced. In addition, these substrate currents induce a magnetic field opposite to the magnetic field of the inductor, and as a result, the total inductance of the inductor is reduced.

Fortunately, most of today's CMOS processes use relative high-resistive substrate. The magnetic field causes much less substrate currents in these substrates, greatly reducing the effect on the losses in the substrate and the reduction of the inductance. Again, an analytic calculation of the substrate losses is cumbersome, and simulations by EM simulators are thus unavoidable.

There are some techniques that can be applied to reduce the substrate losses, but each of them should be verified by EM simulation since the modeling of the influences is very challenging. First, when substrate losses are an issue, it is best to stay away from the substrate by using only the top metal years, if possible. Secondly, especially in the case of highly-conductive substrates, the metal layers of the technology can be laid out in series instead of parallel (stacked multiple layer inductor). As a result, the area of the inductor and thus the substrate losses is greatly reduced for the same inductance. The disadvantage is that the DC series resistance of the inductor increases seriously compared to a single layer structure with the same inductance. A third, more elegant solution is the use of patterned ground shields [42]. To cancel energy dissipation in the substrate a short or an open must be realized. The open is using high-resistive substrates or etching out the substrate, the short is realized by shielding the substrate from the inductor. Highly conductive shields on aluminum layer (solid or patterned) present low electrical losses, but decrease the inductance because of the counteracting eddy current.

A patterned poly-silicon ground shield is better than a solid Al shield for increasing the quality factor, Q, with 33% (at optimal frequency) [42]. The ground shield replaces the lossy, frequency-variant  $C_{\text{sub}}$ , shown in Fig. 2.7 (b), with a larger, but lossless and frequency-invariant capacitance. This reduces the self-resonance frequency of the inductor, but also decreases the losses in the substrate, resulting in higher Q.

## 2.5.3 Integrated Planar Inductor Design Guidelines

The optimization process of designing integrated frequency inductors on silicon is done normally by EM simulations, but some design guidelines can be offered by distilling and summarizing the discussions in the previous sections.

The shape of the winding track: For a given inductance, circular shape spiral gives the best  $\mathcal{Q}_L$  and thus the closer to circular shape is more preferable. Typically, an octagonal inductor is available in latest CMOS processes.

The width of the metal tracks: For higher frequencies, the width of the metal tracks must be limited; wider tracks means that the inner turns of the inductor become smaller in diameter and contribute less to the inductance, but more to the resistance. To counter this effect, the radius must be increased, which also increases the DC metal resistance. Secondly, the skin effect limits the area use of the track, so that wide inductors lose their advantage. For intermediate frequencies, wide metal lines can still be more effective than narrower ones.

**Spacing between adjacent tracks:** the smaller the spacing, the larger the mutual inductance of the inductor and hence the larger the overall inductance.

**Hollow inductor design:** At high frequencies, eddy currents blow up the resistance of inner turns of the inductor, while the inductance contribution is small. They should be omitted and this results in a hollow inductor. At intermediate frequencies and high substrate resistance, filling the inductor has only a minor effect on the performance.

The loss of the substrate: For low-resistive substrates, the area of the inductor must be limited, since the penetration depth of the magnetic field is proportional to the inductor area. The area can be limited by using series connections of the metal layer. The loss caused by substrate can be further reduced by shielding the inductor from the substrate by poly-Si patterned ground shields. The inductor, using only top metal layers, can push the structure far away from the substrate and thus minimize the coupling losses.

#### CHAPTER III

#### INTEGRATED BROAD BAND CMOS T/R SWITCH

Silicon-based CMOS technology has fast become one of the most favorable processes for RF ICs due to its low cost and highly integrative capacity. Owing to low mobility, high substrate conductivity, low break-through voltage, and various parasitic parameters of CMOS processes, it is very challenging to design CMOS switches to achieve low insertion loss, high isolation, wide bandwidth, and high power handling comparable to their GaAs counterparts [34][43]. Various CMOS Transmit/ receive switches (T/R switches) have been developed at different frequencies within 900 MHz to 15 GHz [34], [35], [44]-[48]. Fully integrated CMOS T/R switches, operating over extremely wide bandwidths up to tens of GHz with high linearity and power handling, have not yet been reported. As the bandwidths of radar and communication systems are pushed wider or required to cover multi-bands to address newly emerging applications, the need of these ultra-wideband CMOS T/R switches becomes more critical.

In this chapter, a fully integrated DC-20 GHz T/R switch is presented and several new techniques are discussed to improve the switch's bandwidth, Insertion Loss (IL), Isolation (ISO), and linearity. The designed switch exhibits the best overall performance among the reported CMOS switches, e.g. the widest bandwidth, the lowest loss, and the highest isolation. Moreover, the topology is very feasible for application with fully UWB integrated transceivers as the first stage within the chip boundary connecting with the Electrostatic Discharge (ESD) structures and packages.

# 3.1 Integrated Transmit-Receive Switch for UWB Transceivers

Figure 3.1 Simple direct conversion transceivers for MB-OFDM UWB. The effect of integrating the T/R switch is to push the chip-to-board boundary closer to the antenna.

A fully integrated homodyne (direct conversion) RF transceiver architecture contains very few blocks, which are routinely implemented off-chip using alternative technologies, as shown in Fig.3.1, where those in dashed blocks are built in a single die. This is different, as illustrated in with Fig. 2.2, by an integration of a high performance T/R switch. Addressed in [49], the design of every block in the dashed blocks is challenging for 3.1 GHz to 10.6 GHz wide frequency span, particularly integrated in a

single CMOS die. To present, excluding this work [50], no other broad band T/R switch is reported to meet strict MB-OFDM UWB requirements.