# PERFORMANCE ANALYSIS OF FAULT-TOLERANT NANOELECTRONIC MEMORIES

A Dissertation

by

AYODEJI O. COKER

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2008

Major Subject: Computer Engineering

# PERFORMANCE ANALYSIS OF FAULT-TOLERANT NANOELECTRONIC MEMORIES

#### A Dissertation

by

#### AYODEJI O. COKER

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

## Approved by:

Chair of Committee, Valerie E. Taylor

Committee Members, Eun Jung Kim

Hank Walker

Lazlo Kish

Head of Department, Valerie E. Taylor

May 2008

Major Subject: Computer Engineering

#### **ABSTRACT**

Performance Analysis of Fault-Tolerant Nanoelectronic Memories. (May 2008) Ayodeji O. Coker, B.S. State University of New York at Albany; M.S. Northwestern

#### University

Chair of Advisory Committee: Dr. Valerie E. Taylor

Performance growth in microelectronics, as described by Moore's law, is steadily approaching its limits. Nanoscale technologies are increasingly being explored as a practical solution to sustaining and possibly surpassing current performance trends of microelectronics. This work presents an in-depth analysis of the impact on performance, of incorporating reliability schemes into the architecture of a crossbar molecular switch nanomemory and demultiplexer. Nanoelectronics are currently in their early stages, and so fabrication and design methodologies are still in the process of being studied and developed. The building blocks of nanotechnology are fabricated using bottom-up processes, which leave them highly susceptible to defects. Hence, it is very important that defect and fault-tolerant schemes be incorporated into the design of nanotechnology related devices.

In this dissertation, we focus on the study of a novel and promising class of computer chip memories called crossbar molecular switch memories and their demultiplexer addressing units. A major part of this work was the design of a defect and fault tolerance scheme we called the Multi-Switch Junction (MSJ) scheme. The MSJ

scheme takes advantage of the regular array geometry of the crossbar nanomemory to create multiple switches in the fabric of the crossbar nanomemory for the storage of a single bit.

Implementing defect and fault tolerant schemes come at a performance cost to the crossbar nanomemory; the challenge becomes achieving a balance between device reliability and performance. We have studied the reliability induced performance penalties as they relate to the time (delay) it takes to access a bit, and the amount of power dissipated by the process. Also, MSJ was compared to the banking and error correction coding fault tolerant schemes. Studies were also conducted to ascertain the potential benefits of integrating our MSJ scheme with the banking scheme. Trade-off analysis between access time delay, power dissipation and reliability is outlined and presented in this work.

Results show the MSJ scheme increases the reliability of the crossbar nanomemory and demultiplexer. Simulation results also indicated that MSJ works very well for smaller nanomemory array sizes, with reliabilities of 100% for molecular switch failure rates in the 10% or less range.

# **DEDICATION**

To my family!

#### **ACKNOWLEDGEMENTS**

This has been a long journey, and I did not get to this point purely on my own strength; there have been many people along the way that have encouraged and aided me along this arduous journey. Firstly, although this may sound cliché, it does not take away from the truth that accomplishing this feat would have been a virtual impossibility, if not for the grace of God. My parents, Ayo and Sade Coker, where do I start? They have always believed in me, even when I doubted myself. They have given me more than any son could ask for, and this degree is as much theirs as it is mine. Mum and Dad, I am eternally in your debt. I would also like to thank three of the greatest and most caring sisters that ever existed: Toyin, Tumi and Dami. You guys took it upon yourselves to bear the burden of my struggles with me. You have no idea how grateful I am. Thanks, Girls!

There are many people to thank in my academic life, first and foremost is my advisor and mentor, Dr. Valerie Taylor, who has stood by me all these years, all the way from Northwestern University to Texas A&M. Thanks for all the opportunities and for never letting me settle for less than my best. I would also like to thank Dr. Xingfu Wu for teaching me what it means to be hard working and dedicated. To my research group members, Charles Lively and Sameh Sharkawi, thanks a lot for putting up with all my antics, and for all the valuable research discussions and insights. Thanks are also in order for my past research group members Seung-Hye Jang, and Yue Zuo for all their help. To all my friends, too numerous to mention, you all know who you are; thanks for all the encouragements and prayers.

## **TABLE OF CONTENTS**

|                                                       | Page |

|-------------------------------------------------------|------|

| ABSTRACT                                              | iii  |

| DEDICATION                                            | v    |

| ACKNOWLEDGEMENTS                                      | vi   |

| TABLE OF CONTENTS                                     | vii  |

| LIST OF FIGURES                                       | xi   |

| LIST OF TABLES                                        | xxii |

| CHAPTER                                               |      |

| I INTRODUCTION: NANOTECHNOLOGY MOLECULAR ELECTRONICS  | 1    |

| 1.1 Challenges and Opportunities                      | 3    |

| 1.1.1 Reliability                                     | 4    |

| 1.1.2 Interconnects and Parasitics                    | 4    |

| 1.1.3 Charge Transportation                           | 5    |

| 1.1.4 Power and Heat Dissipation                      | 7    |

| 1.1.5 Molecular Electronic Devices                    | 8    |

| 1.2 Nanowires                                         | 9    |

| 1.2.1 Building Blocks                                 | 10   |

| 1.2.2 Carbon Nanotubes                                | 10   |

| 1.2.3 Geometrical Structure                           | 11   |

| 1.2.4 Carbon Nanotubes as Interconnects               | 11   |

| 1.2.5 Signal Propagation in Carbon Nanotubes          | 12   |

| 1.2.6 Memory Applications for Carbon Nanotubes        | 13   |

| 1.2.7 Semiconductor Nanowires                         | 15   |

| 1.2.8 Synthesis of Semiconductor Nanowires            | 15   |

| 1.2.9 Electrical Transport in Semiconductor Nanowires | 17   |

| 1.3 Objectives and Contributions of This Dissertation | 18   |

| СНАРТ | TER                                                                        | Page |

|-------|----------------------------------------------------------------------------|------|

| II    | CROSSBAR NANOMEMORIES                                                      | 19   |

|       | 2.1 Introduction                                                           | 19   |

|       | 2.2 Memory Architecture                                                    | 22   |

|       | 2.2.1 Memory Organization                                                  | 22   |

|       | 2.2.2 Memory Architecture                                                  | 24   |

|       | 2.2.3 Nanocomputer Architecture                                            | 28   |

|       | 2.3 Crossbar Molecular Switch Nanomemories                                 | 30   |

|       | 2.3.1 Trends in Nanoscale Molecular-Switch Crossbar                        |      |

|       | Circuit Fabrication                                                        | 33   |

|       | 2.3.2 Design and Fabrication of a 160 kilobit Crossbar                     |      |

|       | Nanomemory                                                                 | 35   |

|       | 2.3.3 Crossbar Nanomemory Operation                                        | 36   |

|       | 2.4 A Survey of Other Nanomemory Devices                                   | 37   |

|       | 2.4.1 Quantum Cellular Automata (QCA)                                      | 37   |

|       | 2.4.2 Nanocells                                                            | 41   |

|       | 2.5 Hybrid Microelectronic/Nanoelectronic Devices: Design and              |      |

|       | Architecture                                                               | 43   |

|       | 2.5.1 CMOL                                                                 | 45   |

|       | 2.5.2 Field Programmable Nanowire Interconnect (FPNI)                      | 49   |

| III   | CROSSBAR NANOMEMORY DEMULTIPLEXERS                                         | 52   |

|       | 3.1 Introduction: Defect-Tolerant Crossbar Demultiplexers                  | 52   |

|       | 3.2 Demultiplexer Architecture and Operation                               | 55   |

| IV    | RELIABILITY ARCHITECTURES FOR NANO AND MOLECULAR ELECTRONIC MEMORY DEVICES | 58   |

|       |                                                                            |      |

|       | 4.1 Introduction                                                           | 58   |

|       | 4.2 Defects and Faults Classifications                                     | 59   |

|       | 4.3 N-tuple Modular Redundancy Techniques                                  | 61   |

|       | 4.3.1 Von Neumann's Multiplexing Method                                    | 62   |

|       | 4.3.2 Reconfigurable Computer Technique                                    | 62   |

|       | 4.4 Defect and Fault Tolerance in Molecular Electronic Devices             | 64   |

|       | 4.5 Defect Tolerance                                                       | 65   |

| HAPTER         |                                                              |  |

|----------------|--------------------------------------------------------------|--|

| V MULTI-SWITCH | JUNCTION RELIABILITY ARCHITECTURES                           |  |

| 5.1 Introducti | on: Multi-Switch Junction Crossbar Architecture              |  |

| 5.1.1          | Multi-Switch Junction Circuit Model                          |  |

| 5.1.2          | Scaled Multi-Switch Junction Crossbar Circuit Model Approach |  |

| 5.2 Nanomem    | nory Decoders                                                |  |

|                | Defect-Tolerant Crossbar Demultiplexers                      |  |

|                | Effects of Demultiplexer Defects                             |  |

| 5.2.3          | Multi-Switch Junction Resistor Logic                         |  |

|                | Demultiplexers                                               |  |

| 5.2.4          | ECC Resistor Logic Demultiplexers                            |  |

| 5.2.5          | Enhanced Multi-Switch Junction ECC Resistor                  |  |

|                | Logic Demultiplexers                                         |  |

| 5.3 ECC Arch   | nitecture Implementation                                     |  |

| 5.3.1          | Crossbar Main Memory                                         |  |

| 5.3.2          | Decoder Probability Analysis Methodology                     |  |

| 5.3.3          | Banking Architecture Scheme                                  |  |

| 5.3.4          | Area Analysis Methodology                                    |  |

| AND POWER AN   | NOMEMORY AND DEMULTIPLEXER DELAY ALYSIS RESULTS              |  |

|                | Nanomemory: Parameterized Circuit Model Analysis.            |  |

|                | Circuit Analysis                                             |  |

| 6.1.2          | Performance Analysis Results                                 |  |

| -              | exer Model Implementation: Bundled Single-Wall s Approach    |  |

| 6.2.1          | 11                                                           |  |

| 0.2.1          | Demultiplexers                                               |  |

| 6.2.2          | SWNT Transmission Line Model                                 |  |

| 6.2.3          | Demultiplexer Delay and Power Analysis Results               |  |

|                | alti-Switch Junction Crossbar Nanomemory and                 |  |

|                | exer Circuit Model Analysis                                  |  |

| 6.3.1          | Simulation Engine Set-up.                                    |  |

| 6.3.2          | Results                                                      |  |

|                | exer Model Implementation: ECC Demultiplexer                 |  |

|                |                                                              |  |

|                |                                                              |  |

| CHAPT | ER                                                                    | Page |

|-------|-----------------------------------------------------------------------|------|

| VII   | CROSSBAR NANOMEMORY AND DEMULTIPLEXER                                 |      |

|       | RELIABILITY ANALYSIS RESULTS                                          | 132  |

|       | 7.1 Parameterized Circuit Reliability Analysis                        | 132  |

|       | 7.1.1 Reliability Results                                             | 134  |

|       | 7.2 Reliability of a Single-Wall Nanotube Demultiplexer:              |      |

|       | Introduction                                                          | 137  |

|       | 7.2.1 Probability Analysis                                            | 137  |

|       | 7.3 Reliability: Scaled Analysis Results                              | 140  |

|       | 7.3.1 Crossbar Nanomemory Reliability Analysis                        |      |

|       | Results                                                               | 143  |

|       | 7.4 Demultiplexer Nanowire Stuck-Open Faults Reliability              |      |

|       | Analysis Results                                                      | 149  |

|       | 7.5 Demultiplexer Broken Nanowire Defects Reliability Analysis        |      |

|       | Results                                                               | 155  |

|       | 7.6 Demultiplexer MSJ vs. Banking Scheme Reliability Analysis Results | 162  |

|       | 7.7 ECC Demultiplexer Reliability Analysis                            | 163  |

| VIII  | SUMMARY AND FUTURE WORK                                               | 173  |

|       | 8.1 Summary                                                           | 173  |

|       | 8.2 Future Work                                                       | 179  |

| REFER | ENCES                                                                 | 180  |

| VITA  |                                                                       | 196  |

## LIST OF FIGURES

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

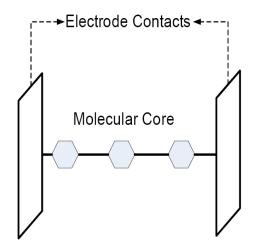

| Figure 1 | Electrode-Molecule-Electrode contact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6    |

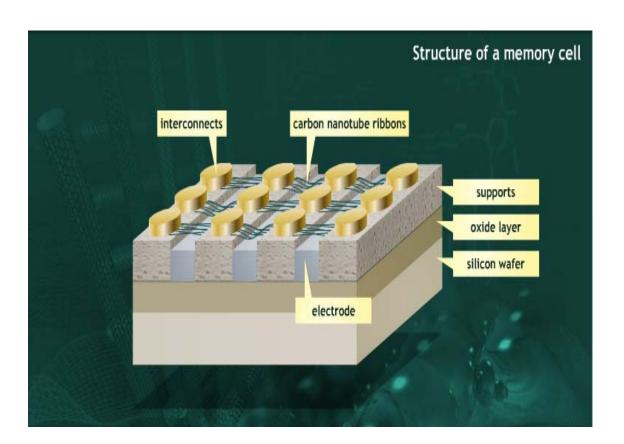

| Figure 2 | An NRAM (Nanotube-based/Non-volatile RAM) [22].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14   |

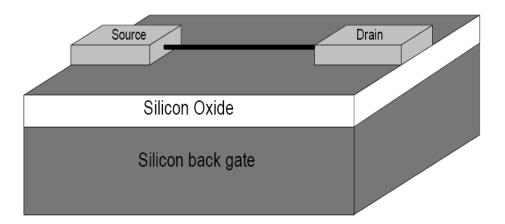

| Figure 3 | Nanowire Field Effect Transistor (NW-FET) schematic. A nanowire is placed between two electrodes which fuction as the source and drain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17   |

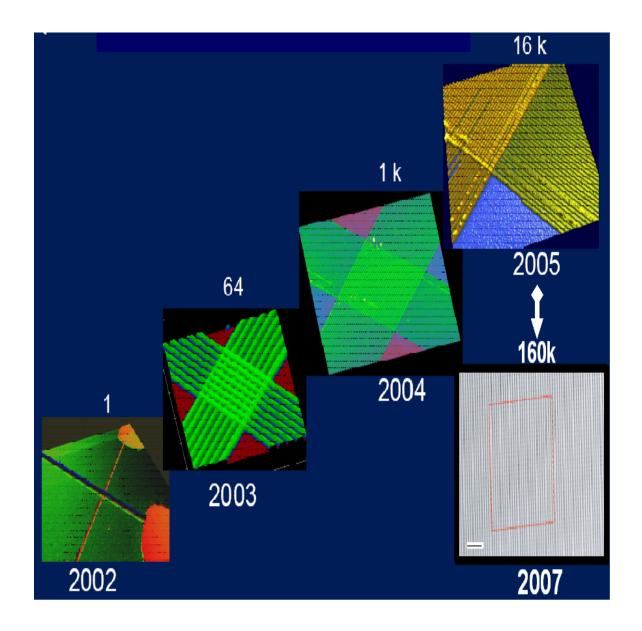

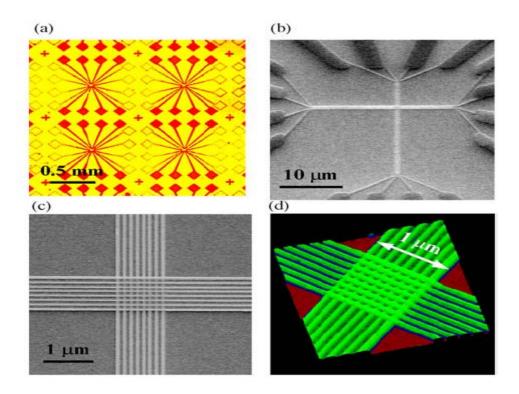

| Figure 4 | Development of crossbar nanomemory technology from 2002 – 2007. The image illustrated in the figure labeled 2002 image, is a proof of concept Atomic Force Microscope (AFM) image of intersecting nanowires. In 2003, nanotechnological fabrication processes improved, and scientists and engineers reported [1] the fabrication of a 64 bit crossbar molecular switch memory. In 2004 and 2005 more strides were made and a 1 kilobit [46] and 16 kilobit respectively, crossbar molecular switch nanomemory were fabricated. Recently, in 2007, the fabrication of the largest crossbar nanomemory to date, with a potential storage capacity of 160 kilobit was demostrated and reported in [31]. Elements of this figure were taken from [1, 31]. | 21   |

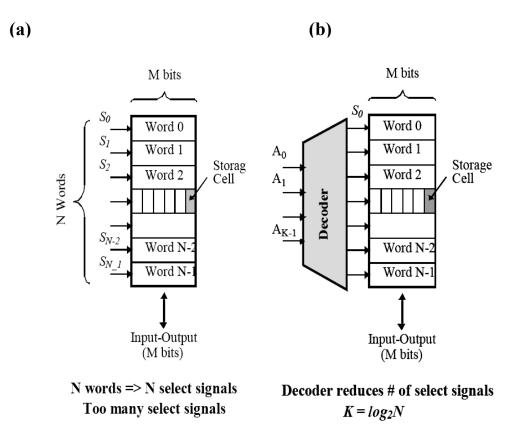

| Figure 5 | (a) Illustrates a memory that uses a single input port for assessing each word. Memory capacities can typically possess over a million words, hence, their configuration is optimized by implementing equal word-line and bit-line dimensions. (b) Multiple words are typically stored on the same word line; each word is distinguished via a column decoder. This aids in preserving a close to unity aspect ratio. Diagram was taken from [36].                                                                                                                                                                                                                                                                                                     | 27   |

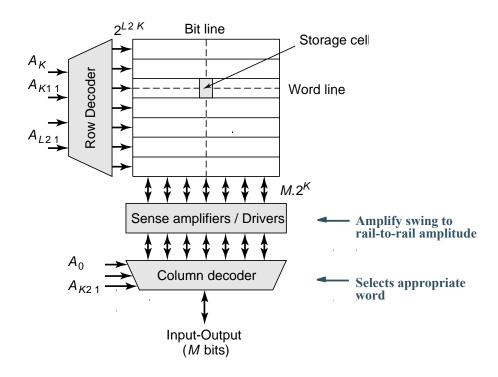

| Figure 6 | Array structured memory architecture [36]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28   |

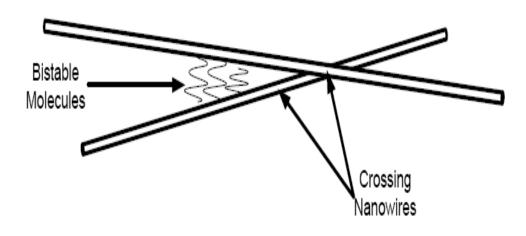

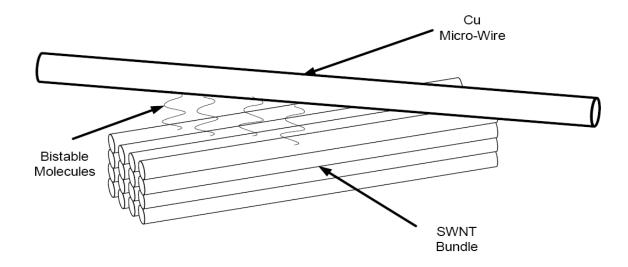

| Figure 7 | The intersection of two nanowires, with bistable molecules deposited at their intersection. This forms the building block molecular switches of the nanoelectronic memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31   |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Page |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 8   | Detailed illustration of the crossbar molecular switch memory [6]. (a) shows an Optical microscope image of an array of 4 crossbar molecular switch circuits, each having 16 contact pads with micron-scaled scaled connections to nanoscale circuits in the center. (b) is a Scanning Electron Microscope (SEM) image showing two nanowire arrays, oriented perpendicularly to each other, and connected to their micron-scaled connections. (c) is an SEM image showing intersection nanowire arrays crossing each other at the central area and thus forming a crossbar. (d) is an Atomic Force Microscope (AFM) image of the cossbar molecular switch memory. |      |

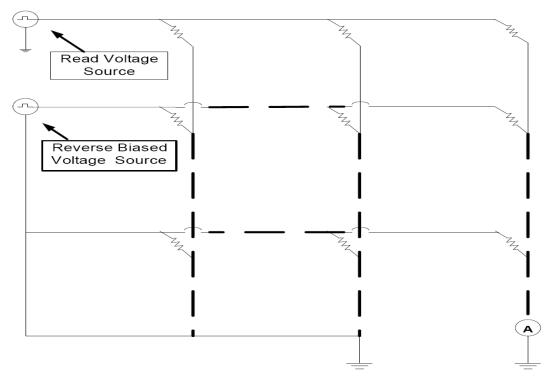

| Figure 9   | Write operation for a crossbar molecular switch nanomemory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 37 |

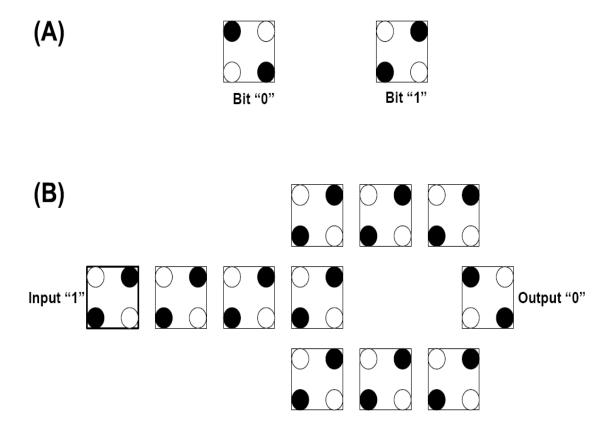

| Figure 10  | (A) Two QCA cells with four quantum dots in their two possible ground-state configurations representing binary "0" and "1" bits. (B) QCA cells used to demonstrate an inverter which takes an input logic "1" and yields an output logic "0"                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

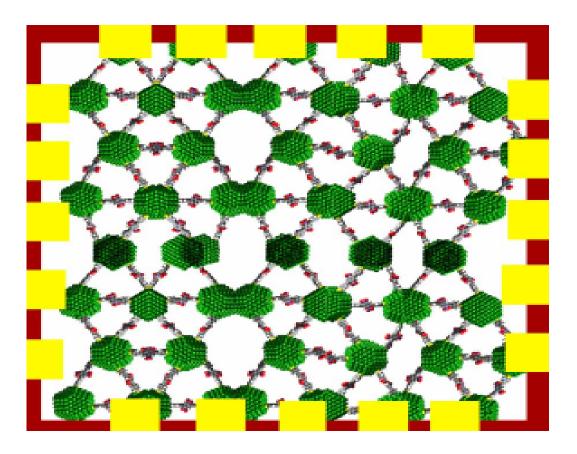

| Figure 11. | Image of a nanocell from [67] showing interconnected active molecules (green). The active molecules are accessed and programmed through the I/O leads (yellow squares)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

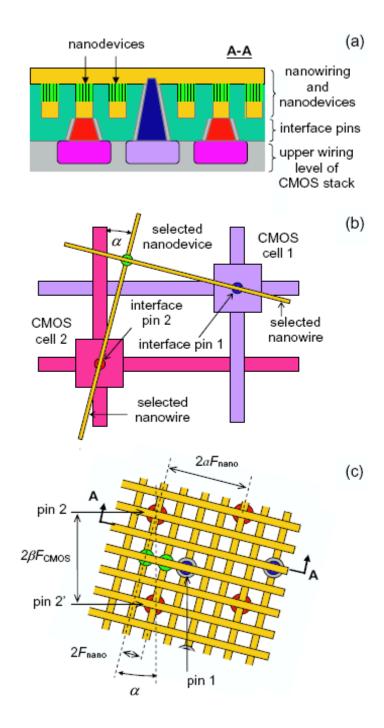

| Figure 12  | Illustration describing the lower level structure of the CMOL circuit architecture. (a) shows a cross sectional side view schematic. (b) illustrates two single pin contacts with two intersecting nanowires, used in addressing the molecular devices. (c) shows only two devices, as well as CMOS cells and wirings [83].                                                                                                                                                                                                                                                                                                                                       |      |

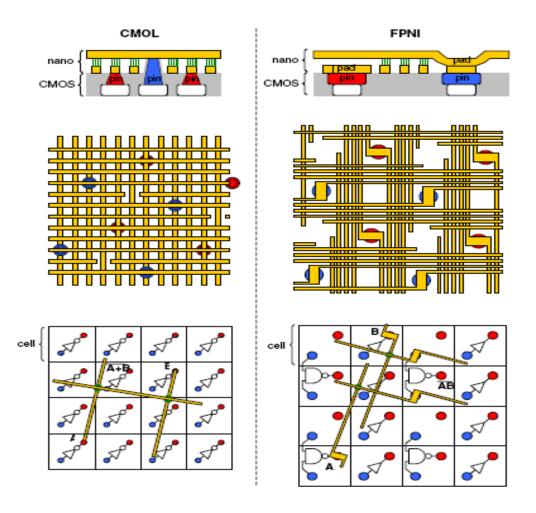

| Figure 13  | Description of the key differences between the CMOL and the FPNI architecture. The CMOL on the left shows the crossbar nanowires array placed above a layer of CMOS inverters. The crossbar has an angled orientation so that contact is made with only a single pin. The FPNI, shown on the right column, shows a sparse crossbar nanowires array placed over a layer of CMOS gates and buffers. The crossbar array also has an angled orientation for the same reasons as the CMOL case. Configured junctions in the FPNI are used for programmable interconnects only, with all logic implemented in CMOS [84].                                                |      |

|           | Pag                                                                                                                                                                                                                                                                                                                 | зe |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

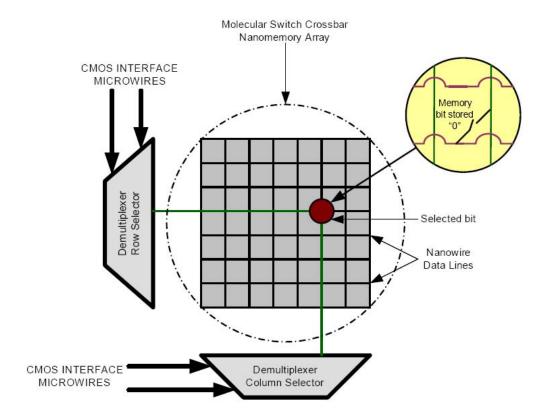

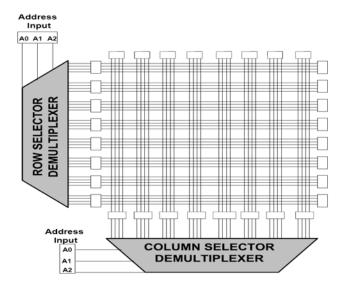

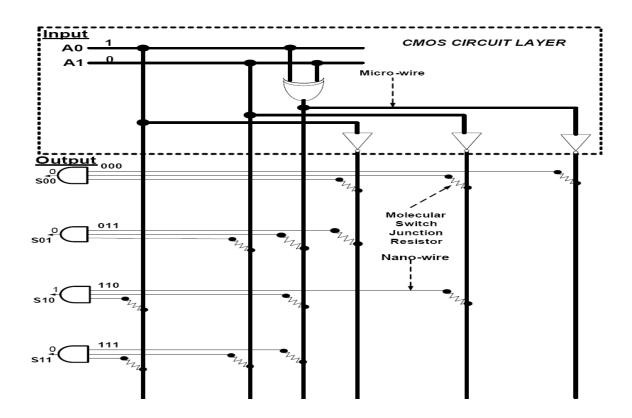

| Figure 14 | Crossbar nanomemory and demultiplexer organization. The important role played played by the demultiplexer can be inferred by its location at the interface of the crossbar nanomemory and CMOS interface addressing microwires.                                                                                     | 56 |

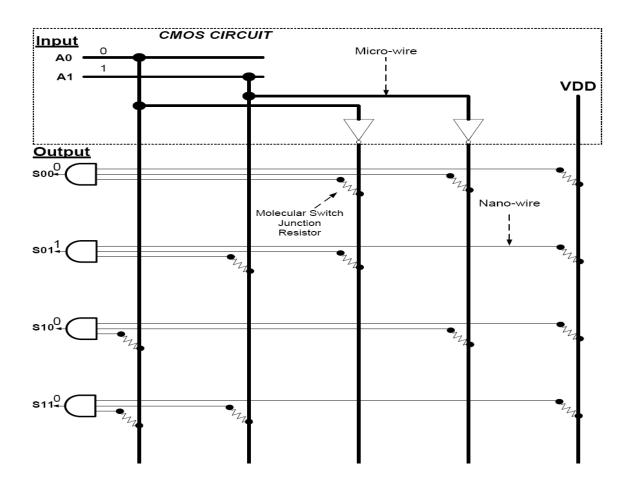

| Figure 15 | A molecular RAM demultiplexer that requires only m input signals to select 2 <sup>m</sup> nanowires.                                                                                                                                                                                                                | 57 |

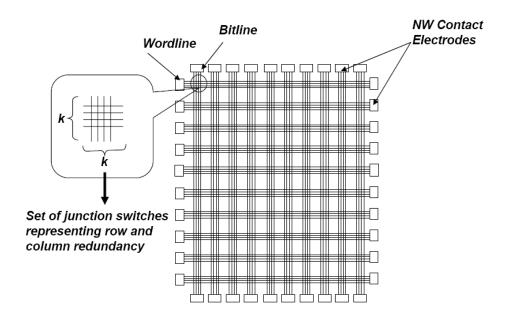

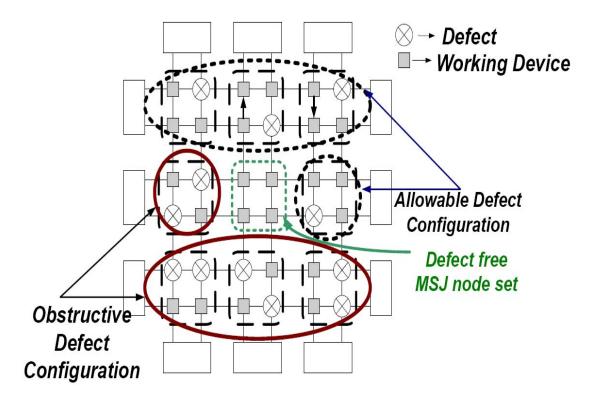

| Figure 16 | A crossbar molecular switch array, with a redundancy of $k = 4$                                                                                                                                                                                                                                                     | 67 |

| Figure 17 | Illustration of some allowed defect configuration in a 3×3 memory crossbar array, having a row and column redundancy of 2                                                                                                                                                                                           | 58 |

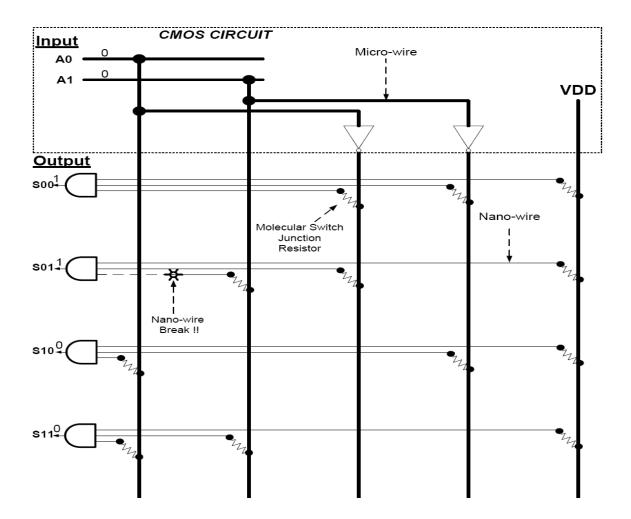

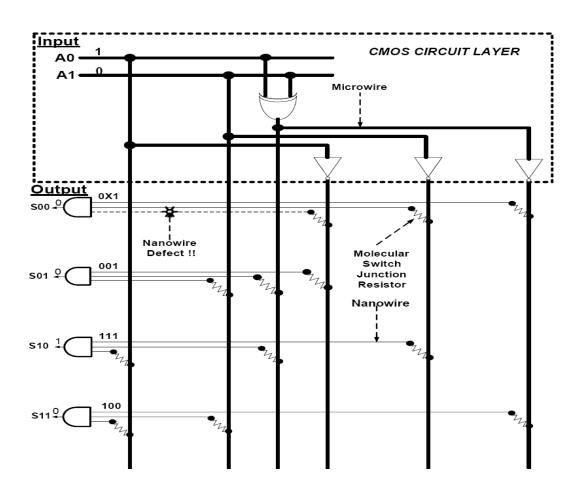

| Figure 18 | Resistor logic demultiplexer. When there is a break in the <i>S01</i> address-line, an attempt to select address <i>S00</i> will result in the selection of both addresses <i>S00</i> and <i>S01</i> . This is an undesirable effect that must be tolerated in order to achieve an effective demultiplexer decoder. | 72 |

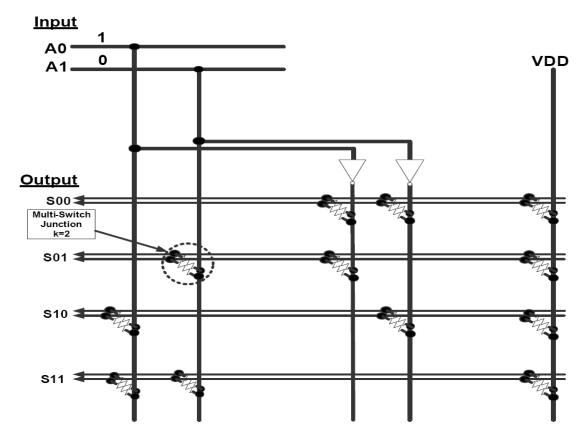

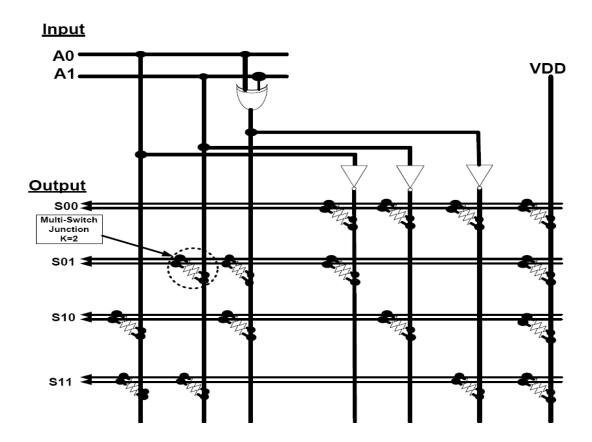

| Figure 19 | Demultiplexer circuit layout, illustrating the implementation the MSJ scheme using a redundancy of 2.                                                                                                                                                                                                               | 73 |

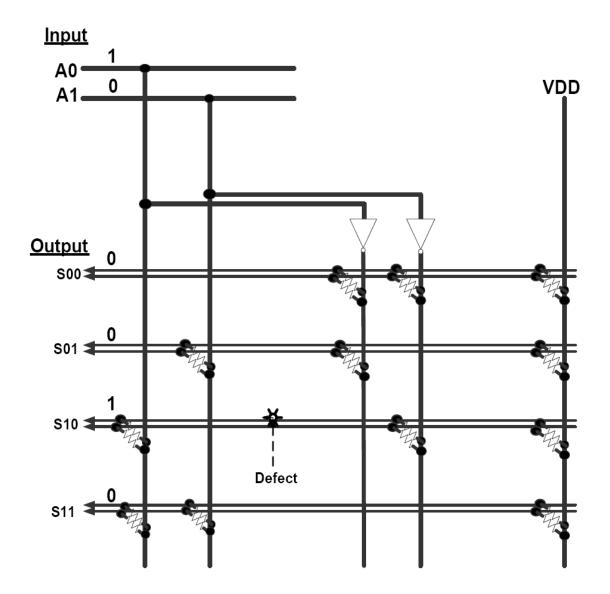

| Figure 20 | When a MSJ redundancy of 2 is implemented in the demultiplexer, A defect can be tolerated. In the illustration the S10 line contains a defect, but when the S10 address is input, the correct address-line is still selected.                                                                                       | 74 |

| Figure 21 | A molecular RAM demultiplexer with an additional EX-OR gate and inverter for ECC implementation. When a stuck open fault occurs in address line S11, a there is no conflict between addresses S11 and S10 because ECC helps to tolorate the fault.                                                                  | 76 |

| Figure 22 | A molecular RAM demultiplexer with an additional EX-OR gate and inverter for ECC implementation. An additional nanowire is added to each row to implement the multi-switch junction scheme.                                                                                                                         | 7  |

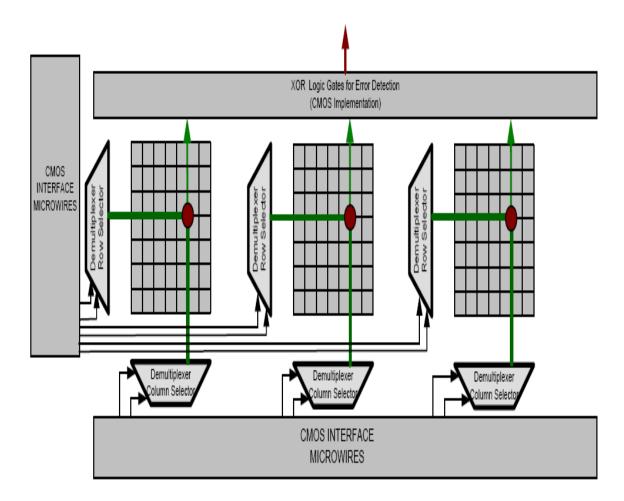

| Figure 23 | Error detection configuration of a triple modular redundant nanomemory block                                                                                                                                                                                                                                        | 79 |

|            |                                                                                                                                                                                                                                                                            | Page |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

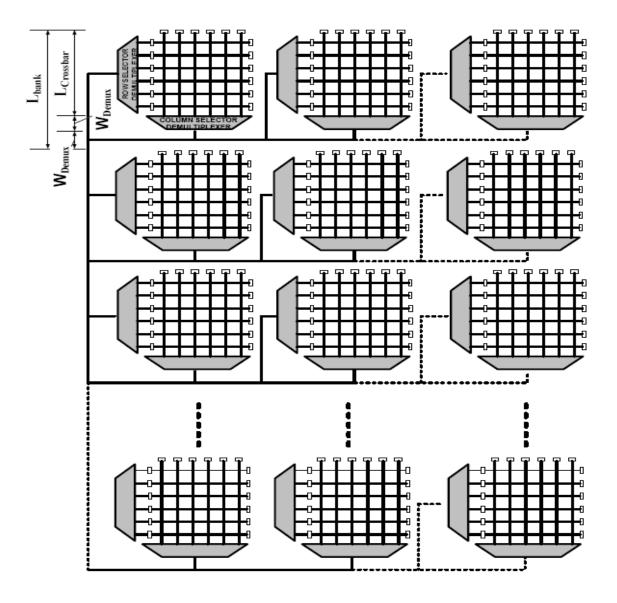

| Figure 24  | Area configuration of a crossbar nanomemory banking scheme used to implement fault tolerance.                                                                                                                                                                              | 82   |

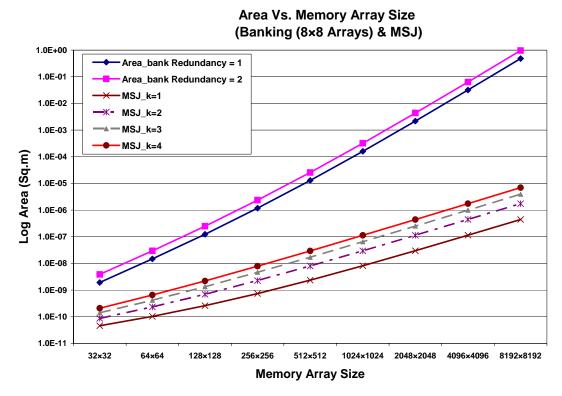

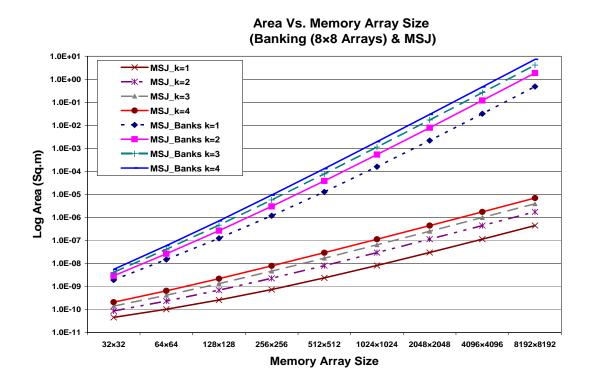

| Figure 25  | Comparison of area utilization of the MSJ scheme and the banking scheme. 8×8 array sized banks were utilized in this analysis.                                                                                                                                             | 86   |

| Figure 26  | Comparison of area utilization of the MSJ scheme and an integrated MSJ-banking scheme. 8×8 array sized banks were utilized in this analysis.                                                                                                                               | 87   |

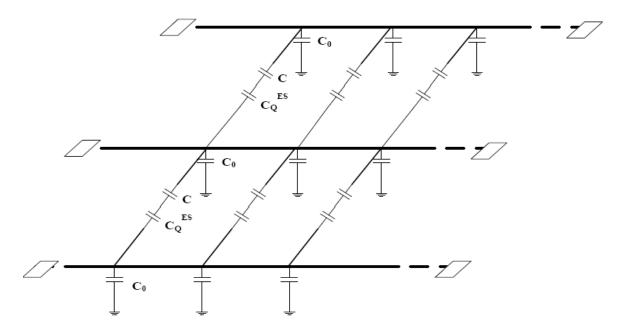

| Figure 27  | Capacitor network between two parallel nanowires. The number of nanowires at each electrodes scales with redundancy. For simplicity we show only a $3 \times 3$ network, with no redundancy at the electrode. The column network is not shown in this diagram for clarity. |      |

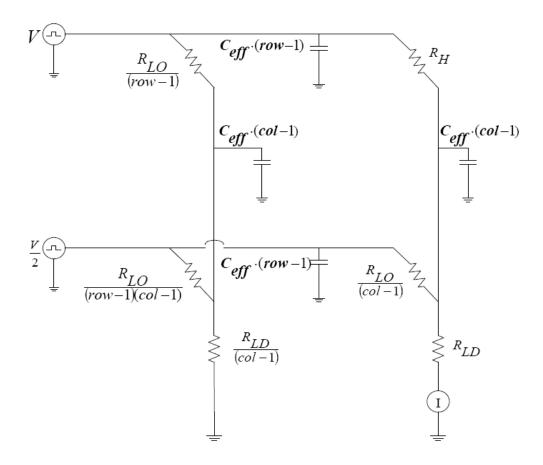

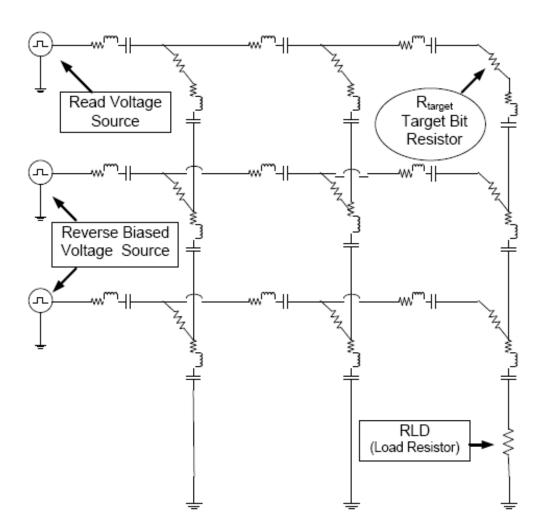

| Figure 28  | Capacitor parameterized circuit model used to simulate the MSJ crossbar                                                                                                                                                                                                    | 93   |

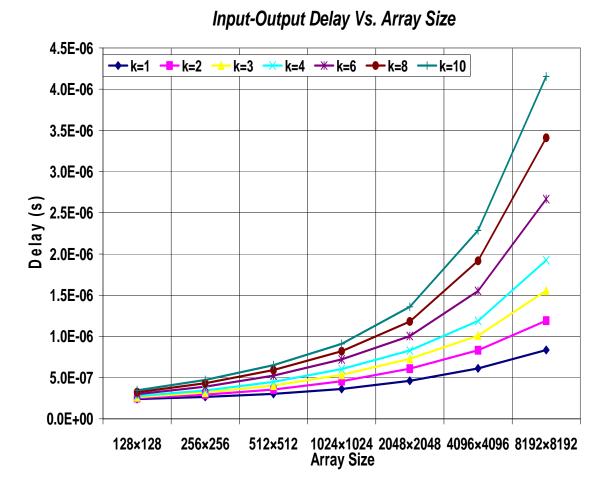

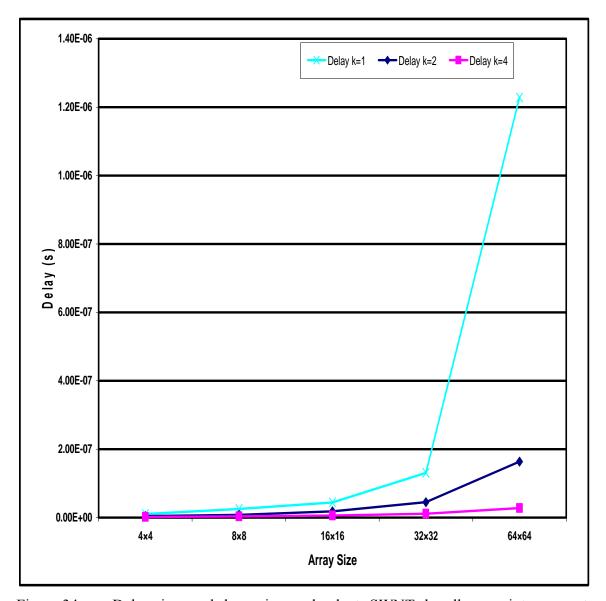

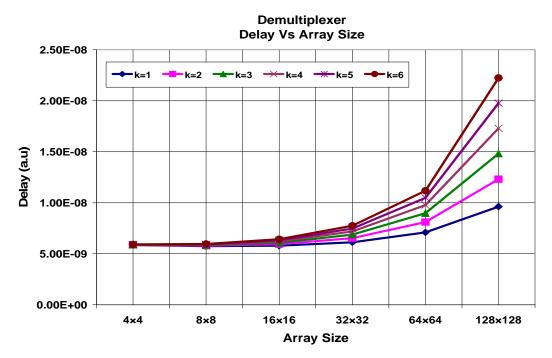

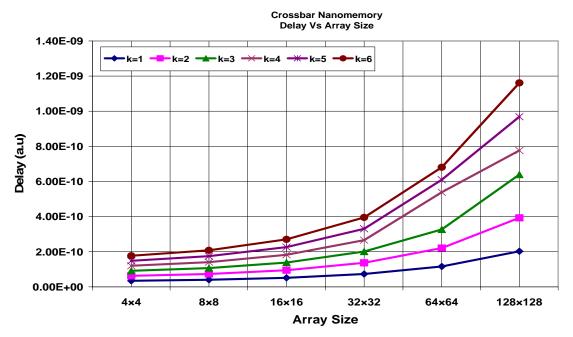

| Figure 29  | Delay realized when $k$ is varied with memory array sizes                                                                                                                                                                                                                  | 98   |

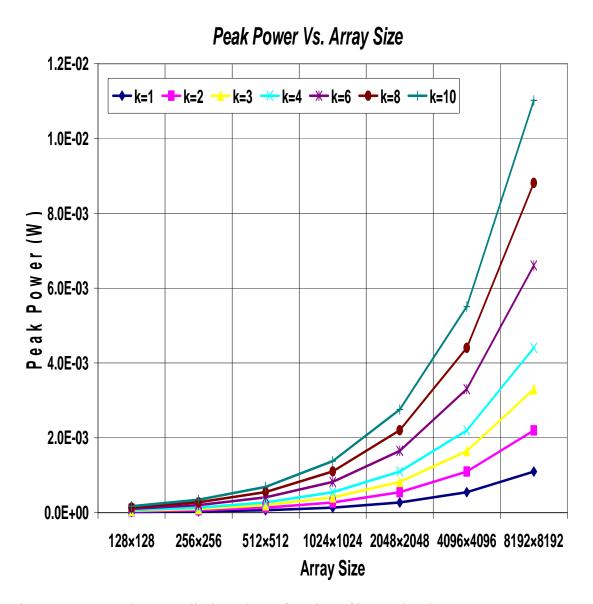

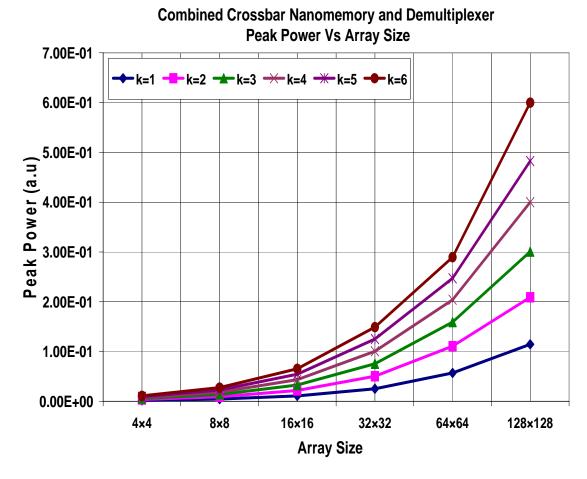

| Figure 30  | Peak power dissipated as a function of increasing k                                                                                                                                                                                                                        | 99   |

| Figure 31  | Analysis of delay change between two levels of k, e.g k4-k1 shows difference in delay between k=4 and k=1. All data is normalized with respect to k =1 and the maximum delta delay value.                                                                                  | 100  |

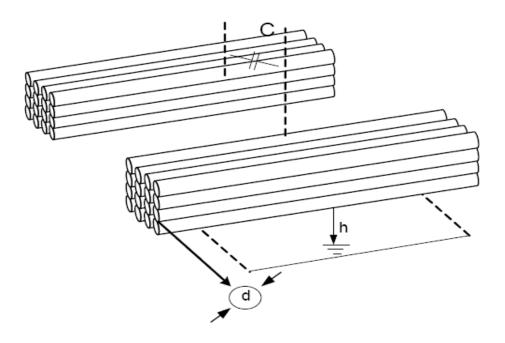

| Figure 32. | Schematic of adjacent nanotubes bundle showing their parameters.                                                                                                                                                                                                           | 106  |

| Figure 33  | Diagram showing the SWNT-microwire junction with redundancy of $k = 4$ . The redundancies in the bistable molecular junctions are also illustrated.                                                                                                                        | 107  |

|           |                                                                                                                                                                                                                                                                                                                                                       | Page |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

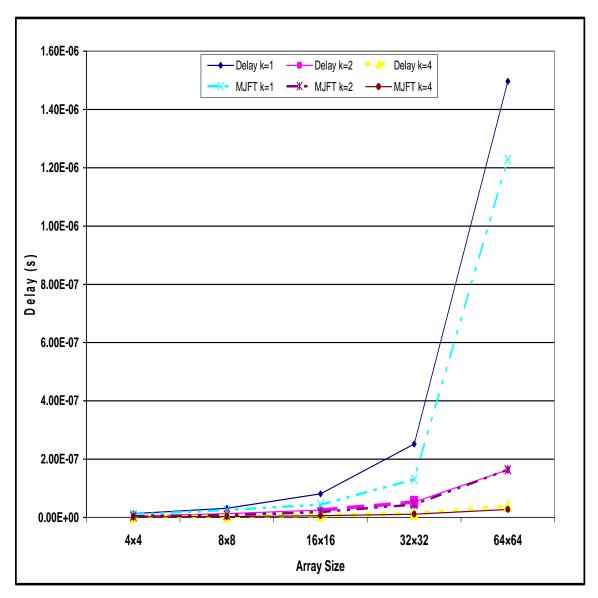

| Figure 34 | Delay incurred by using redundant SWNT bundles as interconnect address-lines.                                                                                                                                                                                                                                                                         | 110  |

| Figure 35 | Delay comparison between the multi-junction fault-tolerance scheme and the multi-junction enhanced ECC fault-tolerance scheme.                                                                                                                                                                                                                        | 111  |

| Figure 36 | MSJ crossbar and demultiplexer nanomemory; this illustration shows, as an example, an MSJ implementation of $k = 4$                                                                                                                                                                                                                                   | 112  |

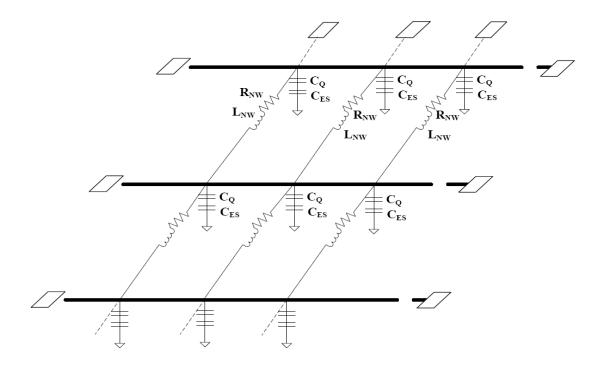

| Figure 37 | RLC network schematic for crossbar nanomemory                                                                                                                                                                                                                                                                                                         | 113  |

| Figure 38 | Circuit layout of a crossbar nanomemory demultiplexer with error correction coding. In this demultiplexer, the (S10) address-line is selected as indicated by the high (1) output on the S10 addressline. The extra bit on the address-line outputs are derived by the "1" parity bit added by implementing error correction coding into the circuit. | 115  |

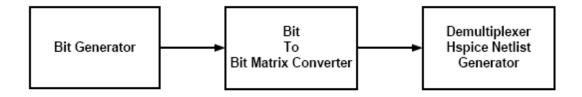

| Figure 39 | Simulator module process chart.                                                                                                                                                                                                                                                                                                                       | 117  |

| Figure 40 | Scaled 3×3 model of the crossbar nanomemory.                                                                                                                                                                                                                                                                                                          | 118  |

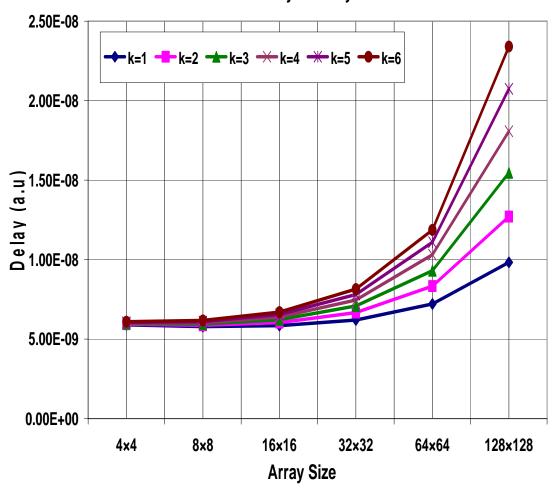

| Figure 41 | The access time delay penalty incurred by increasing the redundancy (k) in the demultiplexer                                                                                                                                                                                                                                                          | 119  |

| Figure 42 | The access time delay penalty incurred by increasing the redundancy (k) in the crossbar nanomemory.                                                                                                                                                                                                                                                   | 119  |

| Figure 43 | Signal delay measurement of selecting the memory address with the demultiplexer and reading a bit with the crossbar nanomemory. Specifically, graph describes the access time delay of the nanomemory and demultiplexer when increasing levels of <i>k</i> are implemented.                                                                           |      |

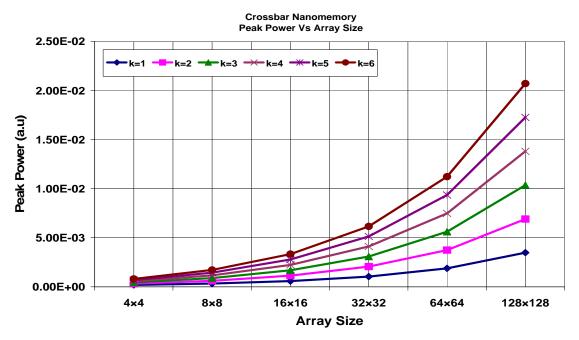

| Figure 44 | Peak power dissipation penalty incurred by increasing the redundancy (k) in the crossbar nanomemory.                                                                                                                                                                                                                                                  | 121  |

|           |                                                                                                                                                                                                                                                                                                                                                                                                         | Page |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

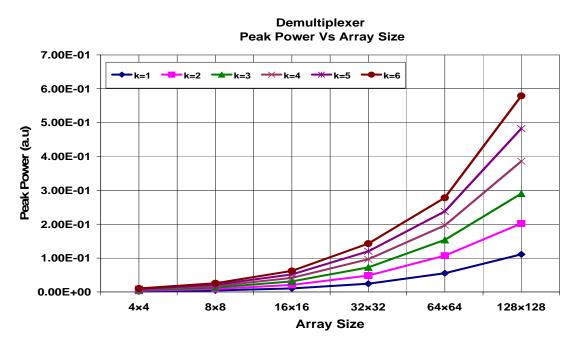

| Figure 45 | Peak power dissipation penalty incurred by increasing the redundancy (k) in the demultiplexer                                                                                                                                                                                                                                                                                                           | 121  |

| Figure 46 | Signal delay measurement of selecting the memory address with the demultiplexer and reading a bit with the crossbar nanomemory. Specifically, graph describes the peak power dissipation trend with increasing degrees of $k$ .                                                                                                                                                                         | 122  |

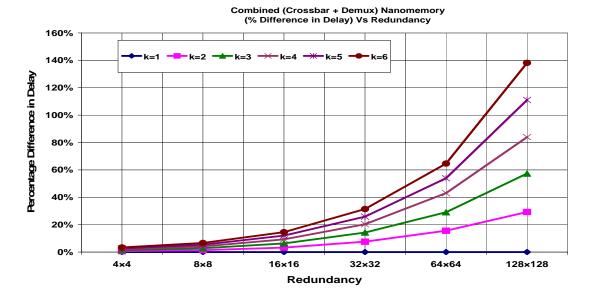

| Figure 47 | Percentage increase in access time delay as a function of increasing redundancy $(k)$ in the combined demultiplexer and crossbar nanomemory device. Percentage increase refers to the additional penalty paid by adding one extra level of redundancy. Example, the delay at $(k = 3)$ – delay at $(k = 2)$ , computes the penalty of going from a redundancy of two to three.                          | 123  |

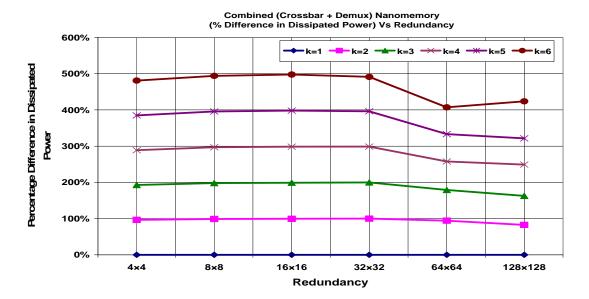

| Figure 48 | Percentage increase in power dissipated as a function of increasing redundancy $(k)$ in the combined demultiplexer and crossbar nanomemory device. Percentage increase refers to the additional penalty paid by adding one extra level of redundancy. For example, the power dissipated at $(k = 3)$ – power dissipated at $(k = 2)$ , computes the penalty of going from a redundancy of two to three. | 124  |

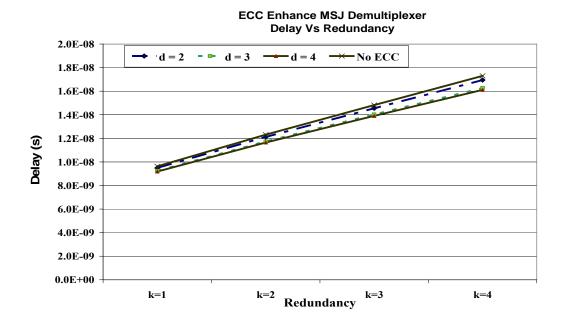

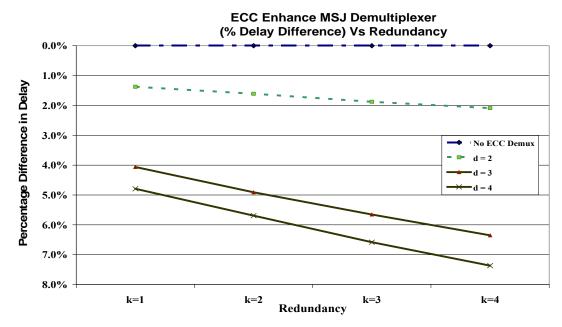

| Figure 49 | Relative increase in access time delay with increasing redundancy (k) and increasing error correction code parity bits, in the crossbar demultiplexer.                                                                                                                                                                                                                                                  | 128  |

| Figure 50 | Percentage difference increase in access time delay (as measured from the No ECC baseline case) with increasing redundancy (k) and increasing error correction code parity bits, in the crossbar demultiplexer.                                                                                                                                                                                         | 128  |

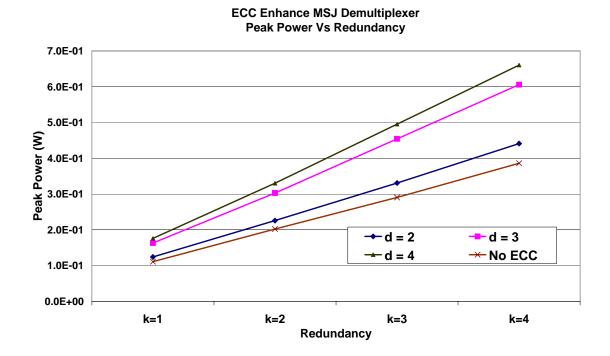

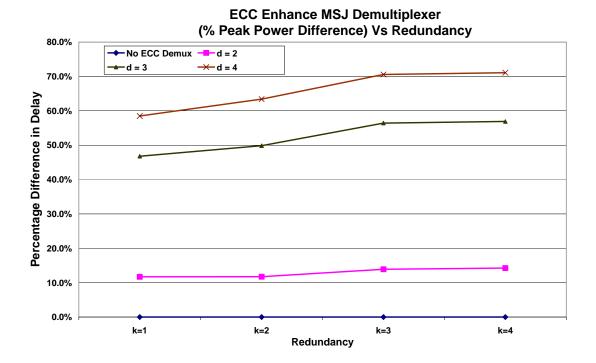

| Figure 51 | Relative increase in peak power dissipated with increasing redundancy $(k)$ and increasing error correction code parity bits, in the crossbar demultiplexer.                                                                                                                                                                                                                                            | 129  |

| Figure 52 | Relative increase in peak power dissipated with increasing redundancy (k) and increasing error correction code parity bits, in the crossbar demultiplexer.                                                                                                                                                                                                                                              | 130  |

|           |                                                                                                                                                                                                                                                                                                          | Page |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

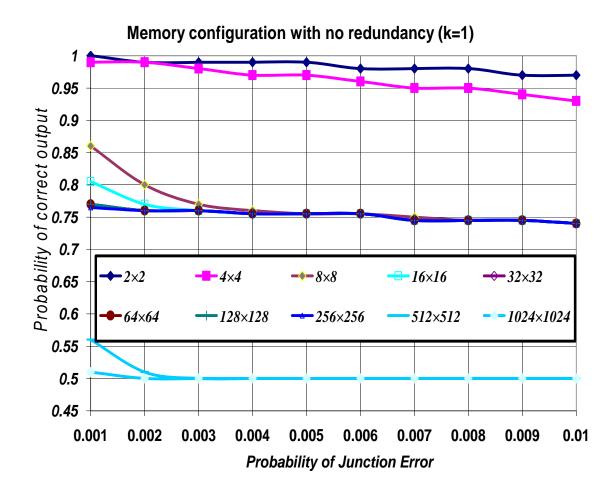

| Figure 53 | Probability of obtaining correct output from the molecular switch crossbar memory, when no redundancy is implemented in the device.                                                                                                                                                                      |      |

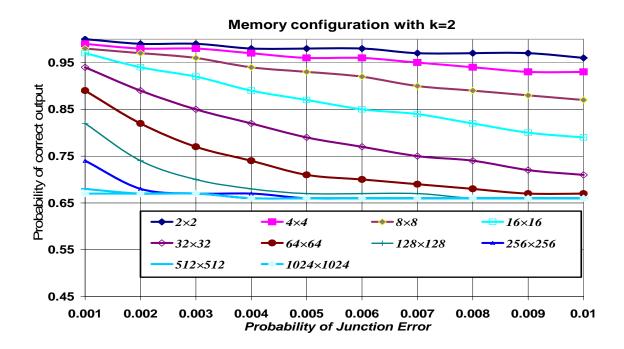

| Figure 54 | Probability of obtaining the correct output for $k = 2$ .                                                                                                                                                                                                                                                | 136  |

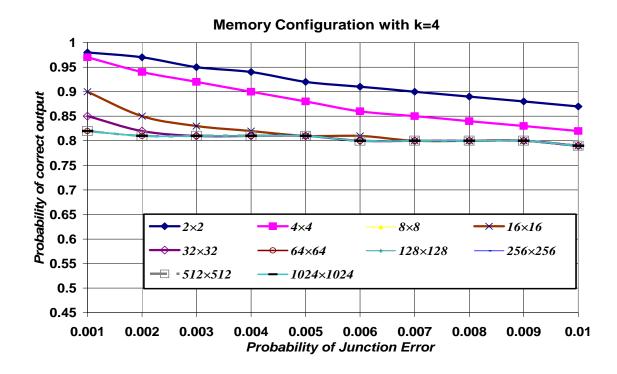

| Figure 55 | Probability of obtaining the correct output for $k = 4$ .                                                                                                                                                                                                                                                | 136  |

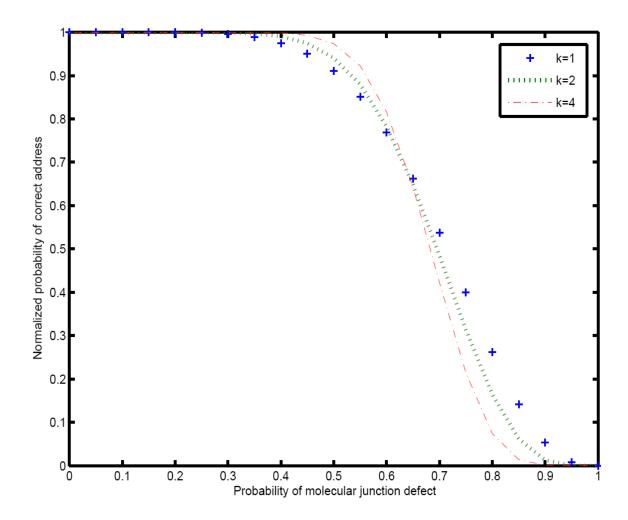

| Figure 56 | Probability analysis graph showing the normalized probability of selecting the correct input address given range of defects probability. $k = 1$ is the benchmark case indicating an ECC only demultiplexer.                                                                                             |      |

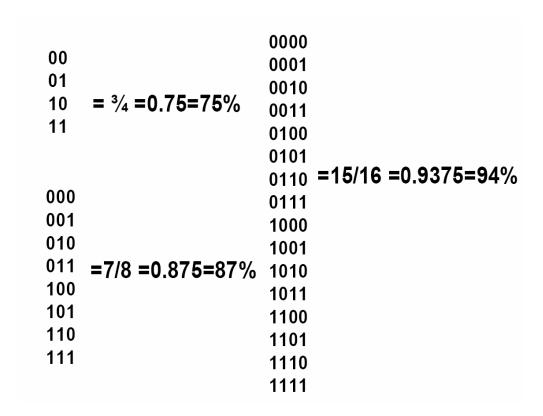

| Figure 57 | Probability analysis using binary numbers. All possible configurations of a one, two and three bit sequence were used. At least one of the binary bits in a configuration of a sequence must be "1" for it to be considered a success. Each bit is comuted as having a 50% chance of being a "1" or "0". |      |

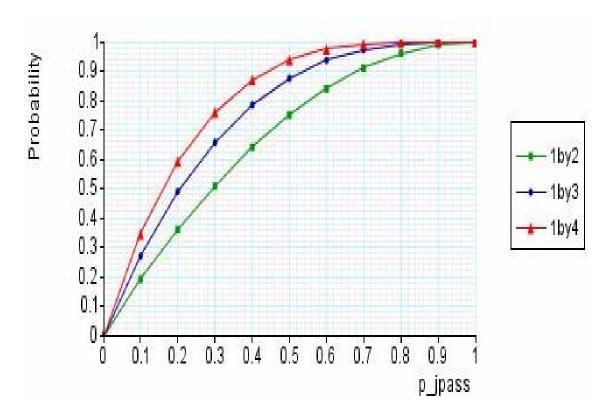

| Figure 58 | Validation results using PRISM. 1by2, 1by3 and 1by4, represent the 2, 3 and 4 bits sequence shown in Figure 57                                                                                                                                                                                           |      |

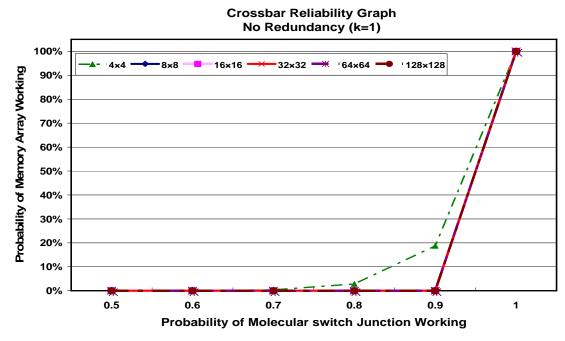

| Figure 59 | Simulation results showing the the reliability of a crossbar nanomemory with no implemented fault-tolerance.                                                                                                                                                                                             |      |

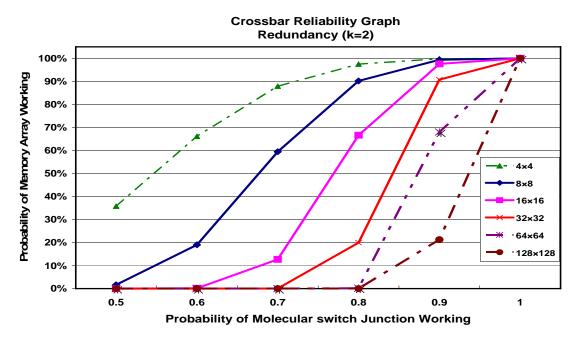

| Figure 60 | Simulation results showing the the clear improvement in the reliability of the nanomemory at redundancy $k = 2$ , especially with regards to the smaller array sizes.                                                                                                                                    |      |

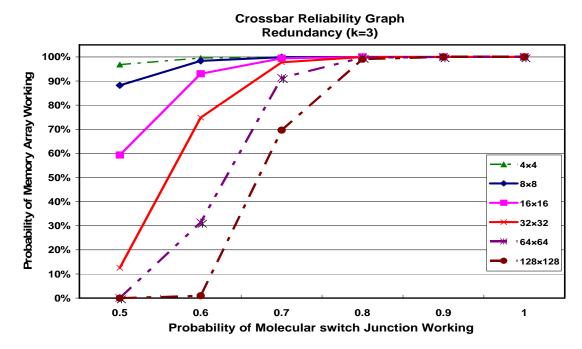

| Figure 61 | Simulation results showing the improved reliability over the $k = 2$ case when the nanomemory redundancy is increased to $k = 3$ . Also increased reliability is noticable for the larger array sizes                                                                                                    |      |

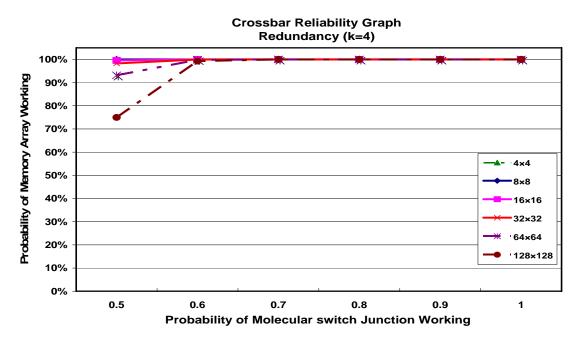

| Figure 62 | Graph shows the clear improvement in the reliability of the nanomemory at redundancy $k = 4$ .                                                                                                                                                                                                           |      |

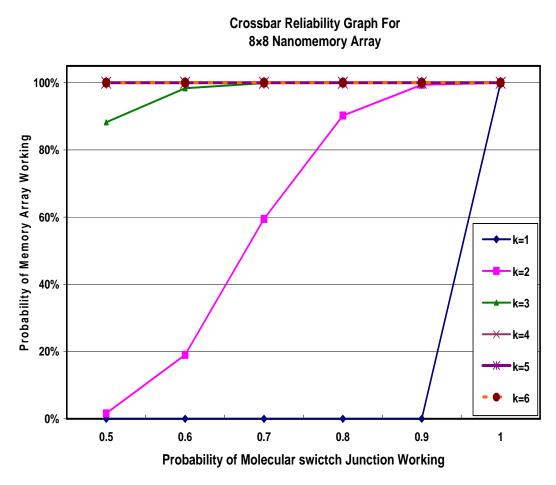

| Figure 63 | Simulation results showing the trend in reliability improment with increasing $k$ for a $8\times8$ nanomemory array                                                                                                                                                                                      |      |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

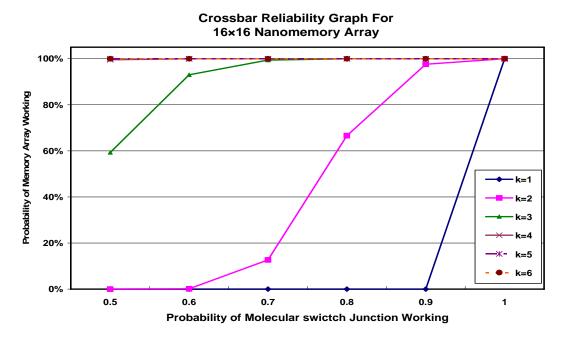

| Figure 64 | Simulation results showing the trend in reliability improvment with increasing $k$ for a $16 \times 16$ nanomemory array                                                                                                                                                                                                                                                                                                                                   | 147  |

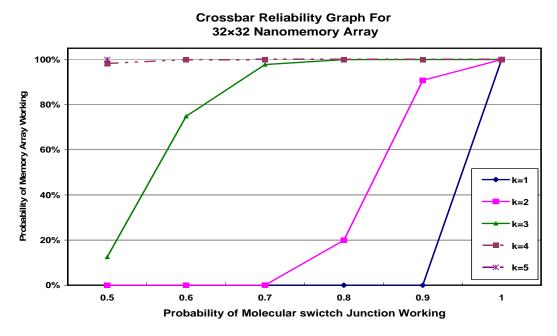

| Figure 65 | Simulation results showing the trend in reliability improvment with increasing $k$ for a 32×32 nanomemory array                                                                                                                                                                                                                                                                                                                                            | 147  |

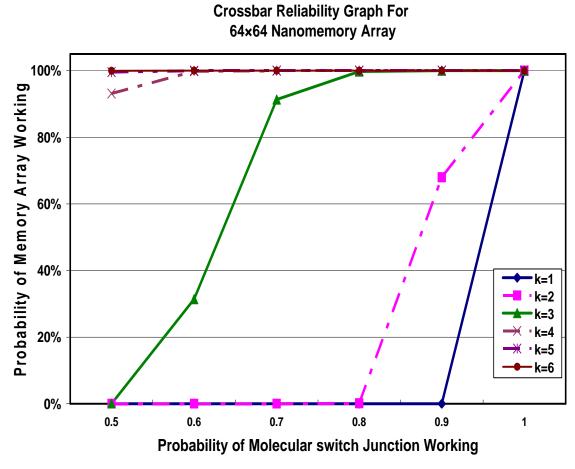

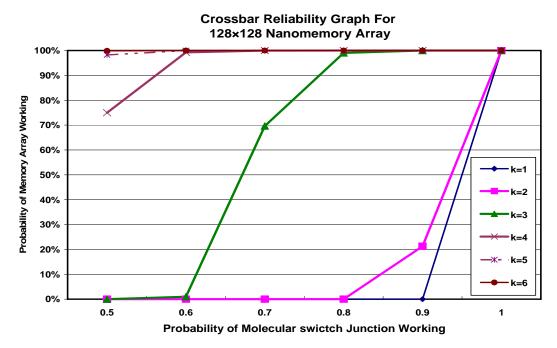

| Figure 66 | Simulation results showing the trend in reliability improvment with increasing $k$ for a 64×64 nanomemory array                                                                                                                                                                                                                                                                                                                                            | 148  |

| Figure 67 | Simulation results showing the trend in reliability improvment with increasing $k$ for a 128×128 nanomemory array                                                                                                                                                                                                                                                                                                                                          | 149  |

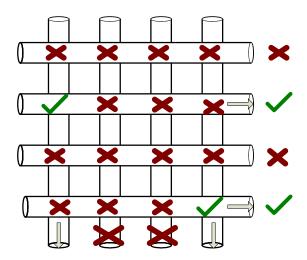

| Figure 68 | Stuck-open fault defect model illustrating conditions under which current woud be allow to pass to the row and column outputs in the presence of defective molecular switch junction. The <b>X</b> mark, symbolizes a defective molecular switches as well as a failed output, and the checks ( $\sqrt{\ }$ ) and arrows symbolize the successful transsmision of current to the row and column outputs. This model represents a $k=4$ MSJ implementation. | 150  |

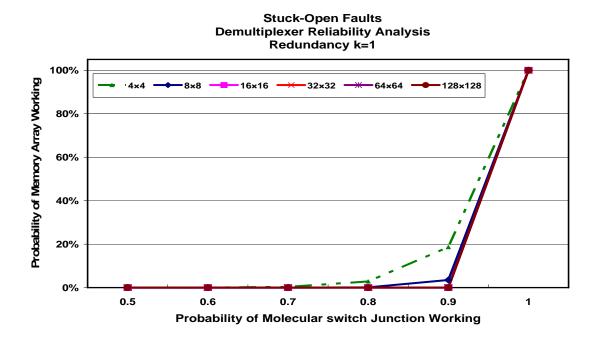

| Figure 69 | Demultiplexer reliability under stuck-open fault conditions when no redundancy is implemented. The high degree of device unreliability is clearly observed.                                                                                                                                                                                                                                                                                                | 152  |

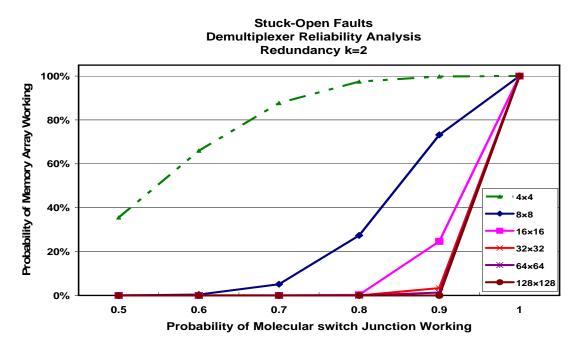

| Figure 70 | Demultiplexer reliability under stuck-open fault conditions, when redundancy $k = 2$ is implemented and array size is varied                                                                                                                                                                                                                                                                                                                               | 152  |

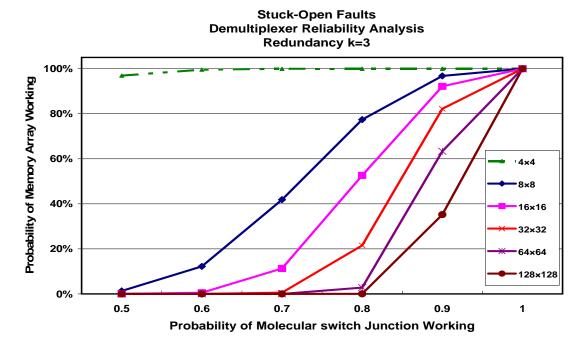

| Figure 71 | Demultiplexer reliability under stuck-open fault conditions, when redundancy $k = 3$ is implemented and array size is varied                                                                                                                                                                                                                                                                                                                               | 153  |

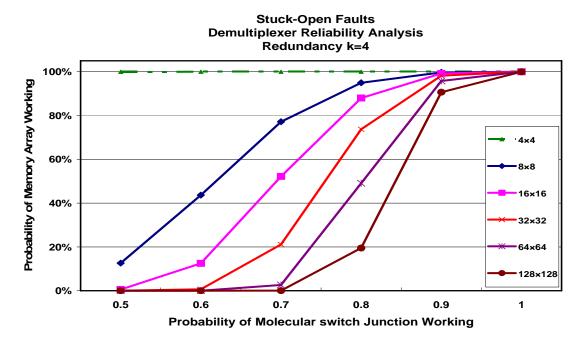

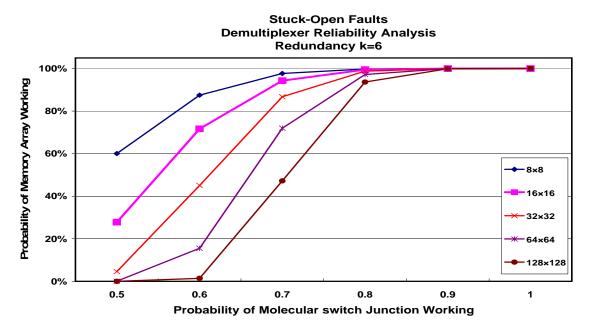

| Figure 72 | Demultiplexer reliability under stuck-open fault conditions, when redundancy $k = 4$ is implemented and array size is varied                                                                                                                                                                                                                                                                                                                               | 153  |

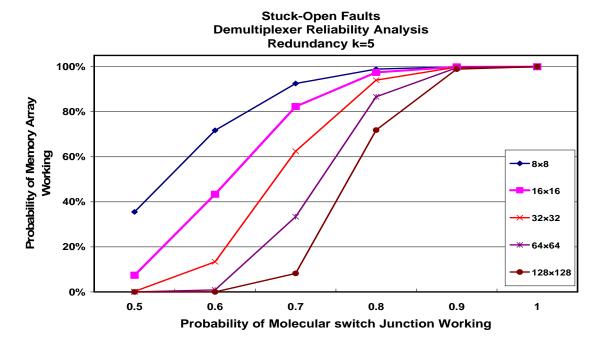

| Figure 73 | Demultiplexer reliability under stuck-open fault conditions, when redundancy $k = 5$ is implemented and array size is varied                                                                                                                                                                                                                                                                                                                               | 154  |

| Figure 74 | Demultiplexer reliability under stuck-open fault conditions, when redundancy $k = 6$ is implemented and array size is varied                                                                                                                                                                                                                                                                                                                               | 154  |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

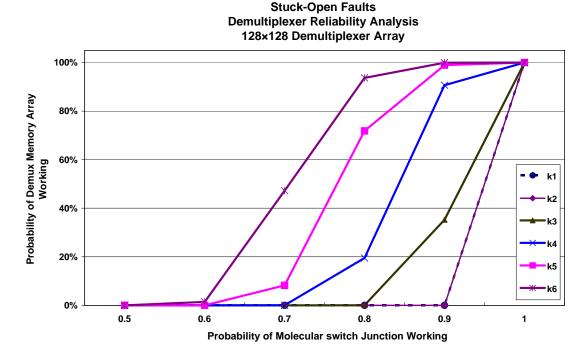

| Figure 75 | Demultiplexer reliability in a 128×128 demultiplexer array, measured as a function of the probability of the molecular switch junction working and increasing redundancy. Results demonstrates a clear improvement in demultiplexer reliability due to the implementation of the MSJ scheme.                                                                                                                                                                                                                                                                                                                                                                                                                           | 155  |

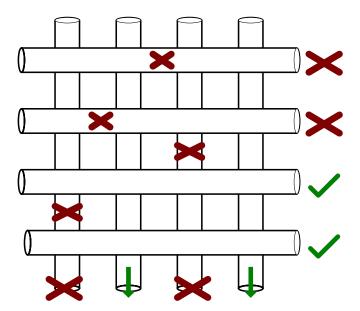

| Figure 76 | Broken nanowire defect model illustrating condition under which current woud be allow to pass to the row and column outputs in the presence of defects. The <b>X</b> mark, symbolizes a break or defect as well as a failed output, and the green check ( $\sqrt{\ }$ ) and arrow symbolize successful current output transmission. This model represents a $k=4$ MSJ implementation.                                                                                                                                                                                                                                                                                                                                  | 157  |

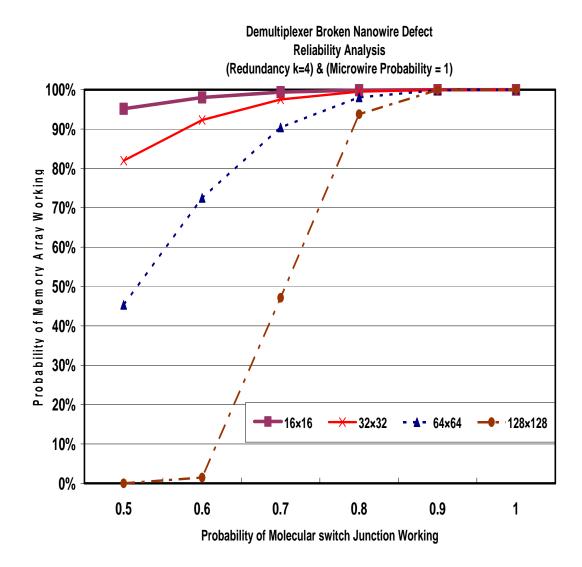

| Figure 77 | Demultiplexer reliability under broken nanowire defect conditions, when no redundancy $k = I$ is implemented, and as a function of the probability of the molecular switch junctions working, and the array sizes are varied in increasing order                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 158  |

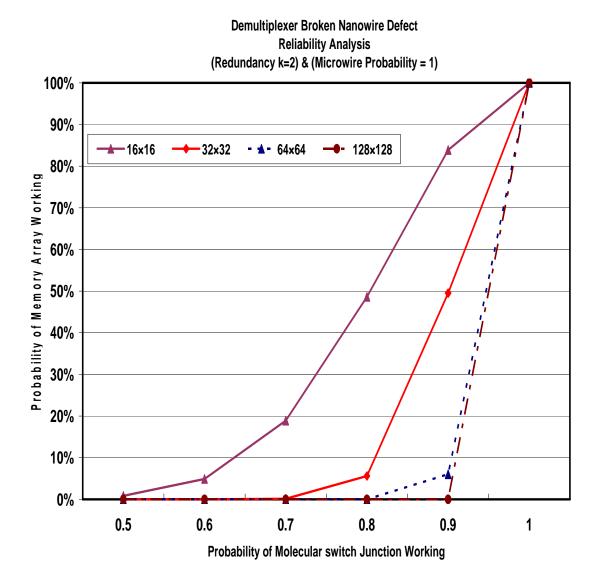

| Figure 78 | Demultiplexer reliability under broken nanowire defect conditions, when redundancy $k = 2$ , under the same conditions as Figure 77. Results show better reliability improvements in the smaller arrays. In particular, the reliability trend lines improve sharply with decreasing array sizes.                                                                                                                                                                                                                                                                                                                                                                                                                       | 159  |

| Figure 79 | Demultiplexer reliability under broken nanowire defect conditions, when redundancy $k=2$ , under the same conditions as Figure 77. Results show better reliability improvements in the smaller arrays. In particular, the reliability trend lines improves with decreasing array sizes as was the case in the $k=2$ implementation of Figure 77. In this case a sharper rise in the trend lines can be observed as indicated by the approximately 78% improvement when the probability of the molecular switch junction working is 0.9 (or 90%) for the $128 \times 128$ array. Contrast this with the 0% reliability achieved by implementing $k=2$ under the same conditions and parameters as observed in Figure 78 | 160  |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 80  | Demultiplexer reliability under broken nanowire defect conditions, when redundancy $k=4$ , under the same conditions as Figure 77. Results show better reliability improvements in the smaller arrays. In particular, the reliability trend lines improves with decreasing array sizes. In this case the $128 \times 128$ array was not simulated because of tool constraints. The reliability improvements are however, clearly visible, as reflected by the $100\%$ reliability observed for working molecular junction probabilities greater thn $0.8$ or $80\%$ . A feat no achieved for $k=2$ and $k=3$ | 161  |

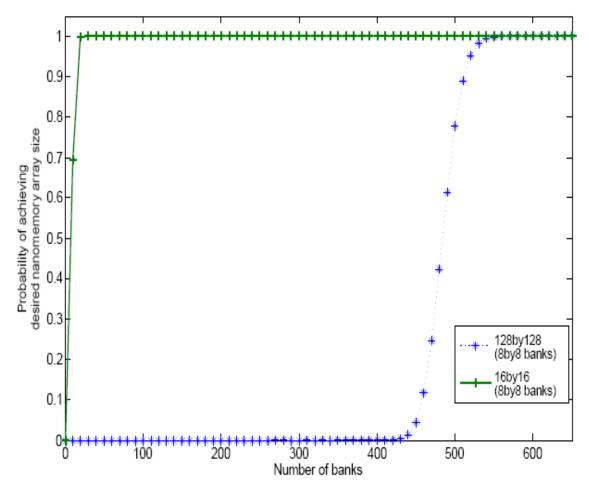

| Figure 81  | Data showing the number of 8×8 banks required to fabricate a 128×128 and 16×16 nanomemory array with a 1% molecular junction failure probability.                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 163  |

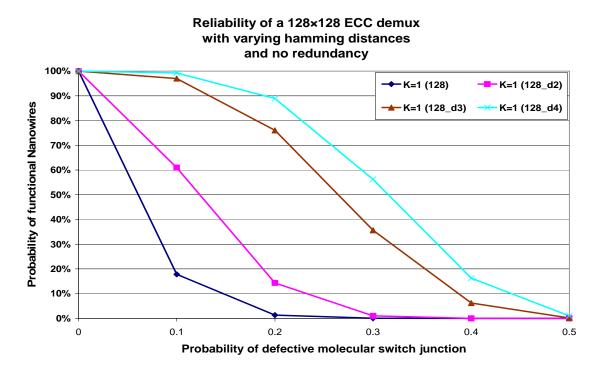

| Figure 82  | Shows the improvement in the reliability of the nanomemory demultiplexer when only ECC is implemented with no redundancy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 166  |

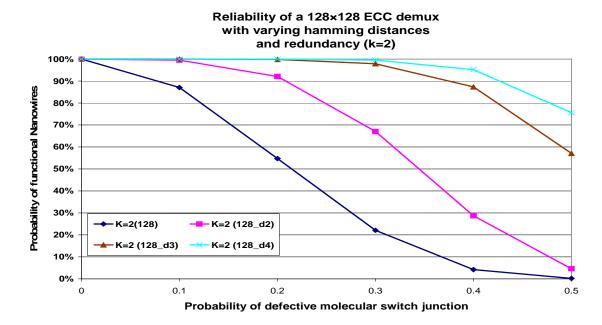

| Figure 83. | Shows the improvement in the reliability of the nanomemory demultiplexer when only ECC is implemented with with a redundancy of $k = 2$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 167  |

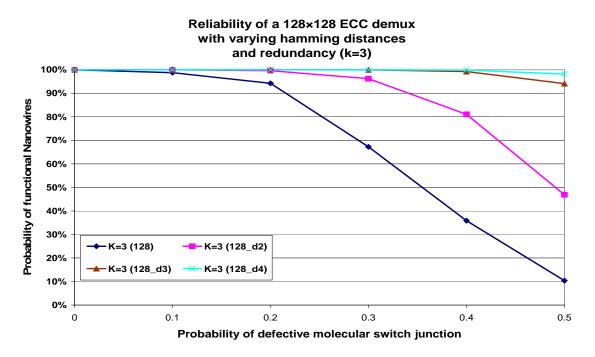

| Figure 84  | Shows the improvement in the reliability of the nanomemory demultiplexer when only ECC is implemented with with a redundancy of $k = 3$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 167  |

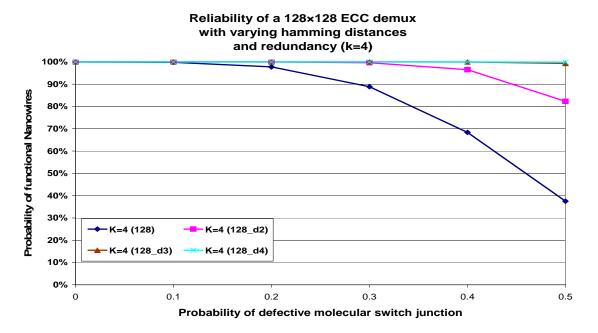

| Figure 85  | Shows the improvement in the reliability of the nanomemory demultiplexer when only ECC is implemented with a redundancy of $k = 4$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 168  |

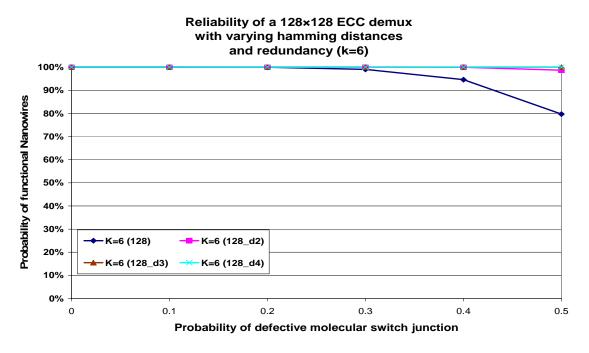

| Figure 86  | Shows the improvement in the reliability of the nanomemory demultiplexer when only ECC is implemented with with a redundancy of $k = 6$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 168  |

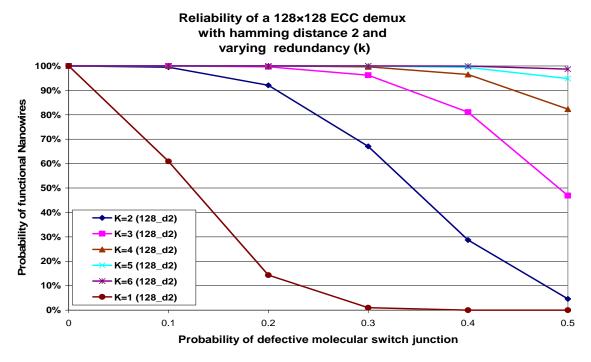

| Figure 87  | Shows the reliability improvement in a $128 \times 128$ nanomemory demultiplexer at an ECC hamming distance of 2 and increasing degrees of redundancy $k$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 171  |

|           |                                                                                                                                                             | Page |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

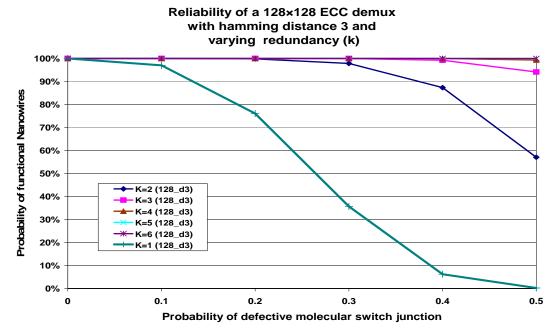

| Figure 88 | shows the reliability improvement in a $128 \times 128$ nanomemory demultiplexer at an ECC hamming distance of 3 and increasing degrees of redundancy $k$ . | 171  |

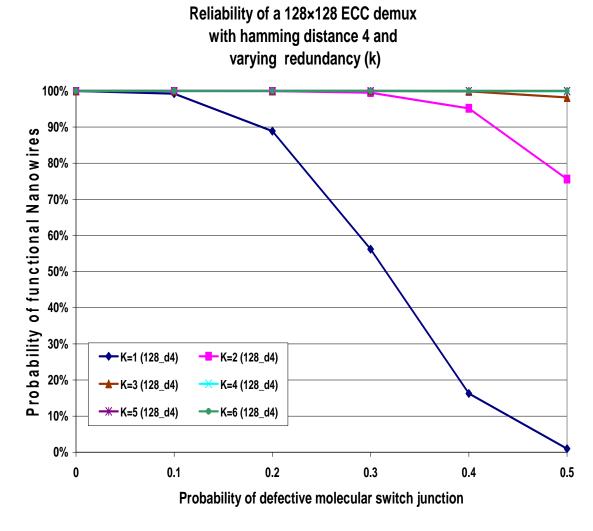

| Figure 89 | Shows the reliability improvement in a $128\times128$ nanomemory demultiplexer at an ECC hamming distance of 4 and increasing degrees of redundancy $k$ .   | 172  |

# LIST OF TABLES

|         |                                                                                                                                                                                                                            | Page   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Table 1 | Parameters used in the parametric analysis SPICE model                                                                                                                                                                     | . 94   |

| Table 2 | Parameters used for the scaled SPICE model analysis.                                                                                                                                                                       | . 117  |

| Table 3 | Results from the plot of Figure 46, showing the percentage difference in the increase in access time delay with respect to the baseline $k = I$ case for a combined crossbar and demultiplexent nanomemory.                | e<br>r |

| Table 4 | Results from the plot of Figure 46, showing the percentage difference in the increase in power dissipated with respect to the baseline $k = 1$ case for a combined crossbar and demultiplexen nanomemory                   | e<br>r |

| Table 5 | Results from the plot of Figure 48, showing the percentage difference in access time delay with respect to the base line k = 1 case for a 128×128 demultiplexer implemented with both ECC and MSJ schemes.                 | -<br>1 |

| Table 6 | Results from the plot of Figure 50, showing the percentage difference in the increase in power dissipated with respect to the baseline $k = I$ case for a 128×128 demultiplexer implemented with both ECC and MSJ schemes. | e<br>I |

| Table 7 | Results from the plots of Figures 85 to 87, showing the improvements in demultiplexer reliability with increasing redundancy (k), and increasing hamming distance (d).                                                     | 5      |

| Table 8 | Trade-off between reliability and performance for the nanomemory demultiplexer (A), and the crossbar nanomemory (B) for a 32×32 array                                                                                      | 7      |

| Table 9 | Trade-off between reliability and performance for the nanomemory demultiplexer (A), and the crossbar nanomemory (B) for a 128×128 array                                                                                    | 7      |

### **CHAPTER I**

## INTRODUCTION: NANOTECHNOLOGY MOLECULAR

#### **ELECTRONICS**

Microelectronics is fast approaching its scaling limits due to physical and economic constraints. Molecular electronics is promising technology that is poised to continue the advances of microelectronics. The idea is to use single molecules as the building blocks to create logic circuits. These molecules will function as electronic switches and storage elements. These molecules have dimensions that are several orders of magnitude smaller than silicon based components. They are synthesized to carry out specific functions, and they can be coaxed via a self assembly process into forming regular two dimensional patterns as well as well defined three dimensional supramolecular objects. This makes them the ideal building blocks for future high density memory devices. With the concepts that underline the molecular self assembly process, one can envision entire computational processing units designed and grown from the bottom-up into practical working devices. Already molecular transistors with bistable switching properties have been developed and demonstrated for use in high-density non-volatile memories [1, 2].

This dissertation follows the style of *IEEE Transactions on Nanotechnology*.

Molecular electronics is still very much in its infancy, and as such many of the experiments, simulations and theories required to understand this subject this field are still being developed. This makes molecular electronics a difficult area to research, but albeit an interesting one. The primary contributions of this work are as follows;

- Studied and assessed the performance and reliability of crossbar or gridlike nanoelectronic memories.

- Developed and simulated a defect and fault-tolerant scheme called the Multi-Switch Junction scheme for achieving reliability in nanoelectronic memories.

- Trade-off analysis of the performance, reliability and area utility of crossbar or grid-like nanoelectronic memories.

The outline of this dissertation is as follows; in this chapter, the emerging nanotechnology field of molecular electronics is first discussed. In chapter II crossbar nanomemories are introduced along with their circuit model, architecture and operation; literature reviews on the most current research and development on crossbar nanomemories are also discussed. Also included in chapter II, is an overview and literature review of competing nanomemory technologies. In chapter III, crossbar nanomemory demultiplexers used to address the main crossbar nanomemory are presented along with accompanying circuit models and operational procedures. Chapter IV presents a detail study of the fundamental reliability techniques being researched and implemented in nanotechnology driven devices. The Multi-Switch Junction architecture

we developed is presented in chapter V, along with a detailed description of its design and implementation in crossbar nanomemories and demultiplexers.

The later chapters are focused on the simulation results. In chapter VI, the steps employed in modeling and simulating the performance of the nanomemory and demultiplexers access time delay and power dissipation; graphs and comparison tables of the simulation results, as well as result analysis, are also presented in chapter VI. The following chapter, VII, introduces and expands upon the reliability techniques and simulators—PRISM and Matlab—used in determining the defect and fault tolerance capabilities of the crossbar nanomemory and demultiplexers; simulation result graphs and comparison tables are also presented and analyzed. In conclusion, chapter VIII summarizes the research work presented in this dissertation, and concluding remarks on the simulation results and findings are discussed.

## 1.1 Challenges and Opportunities

Microelectronics is facing an array of challenges. They include developing lithographic patterning technology capable of producing sub-micron scale line widths, scaling power supply voltages, improving contact resistance, increasing gate capacitance and at the same time reducing gate dielectric tunneling leakages and sustaining device performance. These challenges are the driving force behind discovering new and better technologies. However, there are also obstacles that have to be scaled if molecular electronics is to be realized. They can be divided into the following categories [3]; Reliability, Interconnects and Parasitics, Charge Transportation, Power and Heat Dissipation and Molecular Electronic Devices. These categories are further expanded

upon in sections 1.1.1 through 1.1.5.

#### 1.1.1 Reliability

Molecular electronic devices are fabricated using self assembly processes, As discussed earlier, this is a bottom-up process which means there will be a high occurrence of defects in the fabricated devices. As time progresses it is expected that better techniques will be developed to lessen the amounts of defect that are present in nanoelectronic or molecular electronic devices. In the interim, defect-tolerant architecture will be a necessity if reliable molecular electronic devices are to be realized. The regularity and array nature of the self assembly process make grid or crossbar schemes [1], the architecture of choice for defect tolerance. Several fault tolerance schemes [4-6] are being considered as potential solutions to the quandary of reliably interconnecting a large number of molecular devices to each other. The Teramac computer [7] where a large number of faults were reliably tolerated is an example of such a scheme. A more in-depth look at reliability is presented in chapter VII.

#### 1.1.2 Interconnects and Parasitics

Interconnects will also pose a major obstacle in molecular electronics. The difficulty lies in the fabrication and manipulation of nano wires. The nanometer dimensions of the wires limit the conducting cross-sectional area available for electron transport.

Scientists have been able to synthesize CNT wires nano scale width and lengths in the micrometer dimension [8]. On the other hand, controlling the electrical properties of CNT, to synthesize conducting or semi-conducting CNTs is still a major obstacle for scientists. There are techniques [9, 10] for growing silicon and germanium nanowires which are presently being developed, and are already showing promising results. The electrical properties of the wires can be controlled by using dopants to yield semi-conducting nanowires [11].

The difficulties of interconnection in an ultra dense memory array are significant. Starting with the issue of isolating nanowires from each other to prevent such parasitic as cross-talk, RC signal decay during transmission between molecular devices in the chip as well as between chips. Another problem that arises is that of connecting Nanowires to individual molecules. Scientists are experiencing difficulties in reducing the high resistance encountered at the metal/molecule interface. This problem is a result of the conformational change that occurs to the molecules at the metal/molecule interface. This amounts to a change in shape of the molecules, which results in a distortion of its atomic orbital configurations thereby causing a change in the charge transfer characteristics at the metal-molecule interface [12].

### 1.1.3 Charge Transportation

Understanding charge transportation in nanoscale wires is an important step towards realizing molecular electronic devices. A fundamental requirement for molecular electronics is a mode by which they can be connected to other devices or circuitry. In order to drive current through individual molecules, it is necessary that we have an electrode pair with nanometer sized spacing to contact them [13]. Charge transportation can occur either by quantum transportation, where conduction is determined by the

tunneling of electrons through well defined energy levels, or by coulomb blockade where conduction is attained when potential is sufficient to overcome the energy barrier of charge correlation. Charge transportation in molecular electronics can be broken down conceptually into three discrete parts [14] – the molecular core and the electrode-molecule contacts on both sides of the core, an illustration (Figure 1) is provided below.

Figure 1. Electrode-Molecule-Electrode contact.

The nature of the electrode – molecule interface is determined by the choice of the metal electrode as well as the chemical functionality, or the "alligator clip" which connects the molecules to the metallic contacts [13]. The chemical structure and the electronic transport properties of integrated molecules are intertwined. Hence the advantage to scientists is that the electronic properties of devices may be adjusted by engineering the chemical structures of the molecules.

Electron transport between the electrode-molecule interfaces is dependent on the

coupling strength of the molecules to the contact electrode. The coupling is weak when the molecules are attached to the surface only by weak van der Waals forces [13]. In this case, electron transportation is manifested by a tunneling process in an electron travels from the electrode to the molecule, stays there for a while before making its way to the other electrode; thus yielding poor electron conduction. However, in the case where the coupling is strong, the molecular orbital hybridizes with the metallic state in the electrodes, thus yielding a broadening of the energy levels and a higher conductance [13].

## 1.1.4 Power and Heat Dissipation

Heat generation in a circuit is a function of the product of current and voltage. The steady state formula for the current needed to charge a capacitor one cycle time is given by equation (1-1), where f is the operating frequency of the device, C is the charge capacitance and  $V_{dd}$  is the applied voltage. As earlier stated, the power (P) required for a transistor or on/off device to switch, is given by the product of current flowing through the device and the voltage applied. The switching power is shown in equation (1-2).