## DESIGN OF A 20MHZ TRANSIMPEDANCE AMPLIFIER WITH EMBEDDED LOW-PASS FILTER FOR A DIRECT CONVERSION WIRELESS RECEIVER

A Thesis

by

CHARLES PROF SEKYIAMAH

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

August 2011

Major Subject: Electrical Engineering

## DESIGN OF A 20MHZ TRANSIMPEDANCE AMPLIFIER WITH EMBEDDED LOW-PASS FILTER FOR A DIRECT CONVERSION WIRELESS RECEIVER

A Thesis

by

#### CHARLES PROF SEKYIAMAH

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE

Approved by:

Chair of Committee, Aydin Karsilayan Committee Members, Jose Silva-Martinez

> Henry Pfister Rainer Fink

Head of Department, Costas Georghiades

August 2011

Major Subject: Electrical Engineering

#### **ABSTRACT**

Design of a 20MHz Transimpedance Amplifier with Embedded Low-pass Filter for a Direct Conversion Wireless Receiver.

(August 2011)

Charles Prof Sekyiamah, B.Sc., Kwame Nkrumah University of Science and Technology Chair of Advisory Committee: Dr. Aydin Karsilayan

Accelerated growth in wireless communications in recent years has led to the emergence of portable devices that employ several wireless communication standards to provide multiple functionality such as cellular communication, wireless data communication and connectivity, entertainment and navigation, within the same device.

Industry drive is towards reduction of the number of radio frequency (RF) front-end receivers required to cater to the various standards/bands within a single device to reduce cost, size and power consumption. The current trend is to use broadband/multi-standard or reconfigurable RF front-ends to cater to two or three standards at a time for cost-effective RF front-end solutions. The direct conversion receiver architecture has become attractive as it offers a full on-chip front-end solution without the need for expensive external components. Passive current-mode mixers are used in these receivers to eliminate mixer flicker noise. The in-band current signals are typically in the micro-amp range after mixer downconversion.

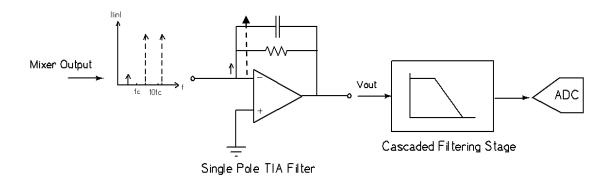

Transimpedance amplifiers are used to convert the downconverted current signals to voltage, and they provide amplification in the process. Because of the co-existence of multiple-radios within each device, large blocker currents downconvert close to the channel bandwidth after the mixer. Conventionally, single-pole transimpedance amplifier (TIA) filters are used to provide out-of-band (OOB) signal filtering. This requires high resolution analog-to-digital converters (ADCs) later in the receiver chain for signal processing. Providing higher order filtering before the ADC relaxes its specifications and this reduces the ADC and ADC calibration cost and complexity.

Typically, an extra filtering stage is provided in the form of a cascaded filtering block after the single-pole TIA.

In this work, higher order filtering is embedded within the TIA in the form of active feedback. In addition to relaxing the ADC specifications, this proposed TIA provides improved large signal linearity such as P1dB compression point. Furthermore, since the extra-circuitry is not in the signal path, in-band flicker noise and linearity are not degraded.

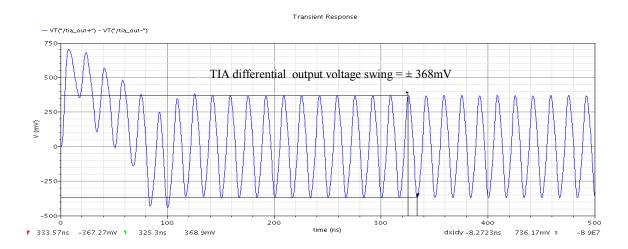

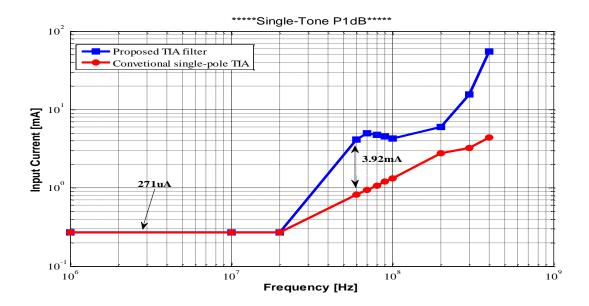

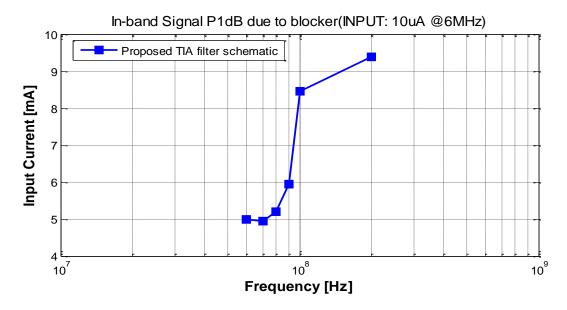

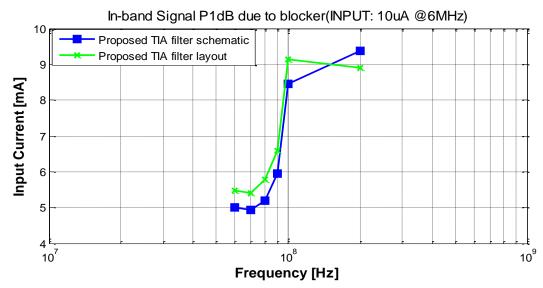

The proposed TIA filter has been designed in IBM 90nm technology with a supply voltage of 1.2V. It can tolerate close-in blocker magnitudes of 4.5mA at 60MHz and higher before in-band 1dB compression is reached.

#### **DEDICATION**

To my wonderful mother, Mrs. Cynthia Asabea Osei-Kofi

To the memories of my late grandfather and great-grandmother

#### ACKNOWLEDGEMENTS

To God be the glory for a successful journey through my master's program; in my darkest hours, his light shone brightly through (Psalm 23).

I would like to express many thanks to my advisor, Dr. Aydin Karsilayan, for guiding me through my master's program. His valuable input into making this thesis possible cannot go without mention.

Secondly, I would like to thank Dr. Jose Silva-Martinez, Dr. Henry Pfister and Dr. Rainer Fink for serving on my committee.

Thirdly, I would like to express my profound gratitude to Texas Instruments Inc. (TI) for the opportunity provided me through the TI African Analog University Relations Program (AAURP), which enabled me to pursue my master's program under the full-sponsorship of a TI fellowship. Particular thanks go to Tuli Dake, Ben Sarpong, Dee Hunter, Rod Wetterskog, and Art George, all of TI, who are directly involved with the TI-AAURP.

Also, my deep thanks go to my mother, Cynthia, my brothers, Luther and Kojo, and my girlfriend, Lorraine. Their thoughts and prayers have been with me throughout the duration of my master's.

And finally, I am deeply indebted to my roommates, friends and colleagues of the Analog & Mixed Signal Center (ASMC), and TAMU as a whole for making my master's program the experience of a lifetime.

#### **TABLE OF CONTENTS**

|     |            |                                                                         | Page     |

|-----|------------|-------------------------------------------------------------------------|----------|

| ΑE  | STRAC'     | Γ                                                                       | iii      |

| DE  | EDICATI    | ON                                                                      | v        |

| AC  | CKNOWI     | LEDGEMENTS                                                              | vi       |

| TA  | BLE OF     | CONTENTS                                                                | vii      |

| LIS | ST OF FI   | GURES                                                                   | ix       |

| LIS | ST OF TA   | ABLES                                                                   | xiii     |

| 1.  | INTRO      | DUCTION                                                                 | 1        |

| 2.  | THE BA     | ASIC TRANSIMPEDANCE AMPLIFIER FILTER                                    | 9        |

|     | 2.1        | Transimpedance Amplifier Parameters                                     | 9        |

|     | 2.2        | The Conventional Single-Pole Transimpedance Filter                      | 11       |

| 3.  | PROPO      | SED TIA FILTER                                                          | 17       |

|     | 3.1        | Conventional Filter Approximations                                      | 18       |

|     | 3.2        | System Level Design of 3 <sup>rd</sup> Order Inverse Chebyshev Feedback | 21       |

|     | 3.3        | Filter with Bandwidth of 20MHz and Notch at 60MHz                       | 21<br>31 |

|     | 3.4        | Macro-Modeling of Proposed TIA Filter in Cadence                        | 32       |

|     | 3.5        | Transistor Level Design Specifications and Considerations               | 38       |

| 4.  | TRANS      | ISTOR LEVEL DESIGN                                                      | 46       |

|     | 4.1        | Amplifier Design                                                        | 46       |

| 5.  | SIMUL      | ATION RESULTS                                                           | 63       |

|     | 5.1<br>5.2 | Schematic Simulation Results  Layout Simulation Results                 | 63<br>71 |

|                | Page |

|----------------|------|

| 6. CONCLUSIONS | 79   |

| REFERENCES     | 81   |

| VITA           | 83   |

#### LIST OF FIGURES

| FIGURE |                                                                        |    |

|--------|------------------------------------------------------------------------|----|

| 1.1    | Heterodyne RF Front-End Receiver                                       | 3  |

| 1.2    | Homodyne RF Front-End Receiver                                         | 4  |

| 1.3    | (a) Simplified Schematic of a Single-Balanced Passive Mixer. (b)       |    |

|        | Direct-Conversion Wireless Receiver with Current-Mode Passive          |    |

|        | Mixer                                                                  | 5  |

| 1.4    | Single-Pole TIA with $60dB\Omega$ In-Band Gain and a Bandwidth of      |    |

|        | 20MHz                                                                  | 7  |

| 2.1    | The Basic Transimpedance Amplifier                                     | 9  |

| 2.2    | Fully-Differential Direct-Conversion Wireless Receiver Block Diagram . | 11 |

| 2.3    | TIA Input Impedance Plotted for $Z_f = R_f$ and $Z_f = R_f    C_f$     | 13 |

| 2.4    | Comparison of TIA Input Impedance for Different Values of Op-amp       |    |

|        | GBW                                                                    | 14 |

| 2.5    | Extra OOB Blocker Attenuation through Cascading                        | 15 |

| 3.1    | Conceptual View of the Proposed TIA Using Active Feedback              | 17 |

| 3.2    | Idealized Brick-Wall Filter                                            | 18 |

| 3.3    | Practical Lowpass Filter Design Parameters                             | 19 |

| 3.4    | Comparison of Filter Approximations; All Filters are Fifth Order       | 20 |

| 3.5    | The General Feedback Structure                                         | 21 |

| 3.6    | Trade-Off between Bandwidth and Stop-Band Attenuation for a Fixed      |    |

|        | Notch Frequency                                                        | 22 |

| 3.7    | Magnitude and Phase Plot of the Synthesized 3rd Order Inverse          |    |

|        | Chebyshev Filter                                                       | 23 |

| 3.8    | Synthesized Inverse Chebyshev Magnitude Plot with a Passband Gain      |    |

|        | of $60dB\Omega$ , a Bandwidth of $20MHz$ with a $60MHz$ Notch          | 25 |

| 3.9    | Magnitude and Phase Plot of $H(s)$ .                                   | 26 |

| FIGUR | E                                                                             | Page |

|-------|-------------------------------------------------------------------------------|------|

| 3.10  | Pole-Zero Map of $H(s)$ and $H'(s)$                                           | 27   |

| 3.1   | Matlab Frequency Response of $H(s)$ and $H'(s)$                               | 28   |

| 3.12  | 2 TIA Step Response Obtained by Substituting $H(s)$ and $H'(s)$ into $(3.1)$  | 28   |

| 3.13  | 3 Comparison of Original Inverse Chebyshev Filter, Modified Filter and        |      |

|       | Single-Pole Filter Functions                                                  | 30   |

| 3.14  | Fully-Differential Tow-Thomas Biquad for Implementing Second                  |      |

|       | Order Functions with Arbitrary Transmission Zeros                             | 31   |

| 3.13  | Macro-Model of Proposed TIA Filter Using Ideal Opamps in Cadence              | 32   |

| 3.10  | 6 Proposed TIA Filter Magnitude Response in Using Ideal Op-amps with          |      |

|       | Infinite GBW                                                                  | 33   |

| 3.1   | 7 Proposed TIA Filter Response for the Following Op-amp GBW                   |      |

|       | Conditions: OpampA - 1GHz, OpampC - Infinite, OpampB-250MHz,                  |      |

|       | 500MHz, 1GHz, 2GHz                                                            | 35   |

| 3.18  | Proposed TIA Filter Response for the Following Op-amp GBW                     |      |

|       | Conditions: OpampA - 1GHz, OpampB - Infinite, OpampC - 250MHz,                |      |

|       | 500MHz, 1GHz, 2GHz                                                            | 36   |

| 3.19  | Proposed TIA Filter Loop Gain Magnitude and Phase Response                    |      |

|       | Using Op-amps with 60dB Gain and Infinite GBW                                 | 37   |

| 3.20  | Loop Gain Magnitude and Phase Response for a Parametric Sweep                 |      |

|       | of OpampB and OpampC GBWs : 250MHz - 2GHz                                     | 37   |

| 3.2   | Variation of Proposed TIA Filter OOB Attenuation with C <sub>IN</sub>         | 39   |

| 3.22  | 2 Single-Ended Representation of Output Loading of OpampB                     | 40   |

| 3.23  | Proposed TIA Filter $\alpha_{MIN}$ Reduction for a Change of $C_{IN}$ to 30pF | 42   |

| 3.24  | Targeted TIA Filter Magnitude Response                                        | 43   |

| 3.23  | 5 Transimpedance Gain from the Proposed TIA Input to Each Op-amp              |      |

|       | Output                                                                        | 44   |

| 4.1   | Block Diagram of a Two-Stage Amplifier with No-Capacitor                      |      |

|       | Feed-Forward (NCFF) Compensation                                              | 47   |

| FIGURE |                                                                               | Page |

|--------|-------------------------------------------------------------------------------|------|

| 4.2    | Schematic of Two-Stage Amplifier Using NCFF Compensation                      | 50   |

| 4.3    | Simple PMOS Differential Pair Input Stage                                     | 53   |

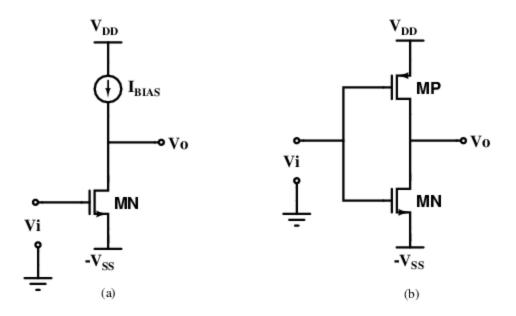

| 4.4    | A Class A Common-Source Output Stage. (b) A Class B Common-                   |      |

|        | Source Output Stage                                                           | 54   |

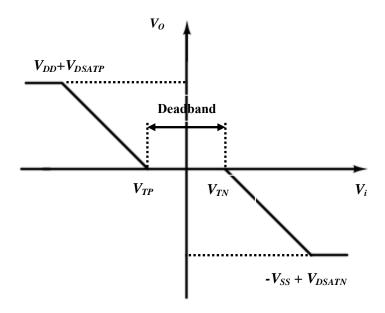

| 4.5    | Class B Output Characteristic Plot.                                           | 56   |

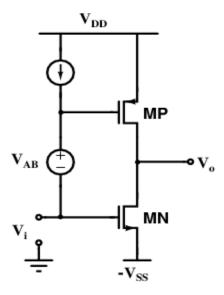

| 4.6    | The Class AB Output Stage [10]                                                | 56   |

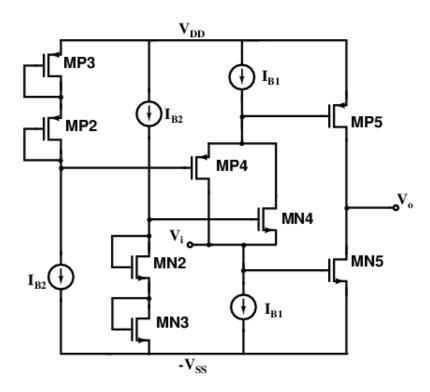

| 4.7    | Monticelli Class AB Output Stage                                              | 58   |

| 4.8    | Schematic of Miller-Compensated Two-Stage Op-amp with Class                   |      |

|        | AB Output Stage                                                               | 59   |

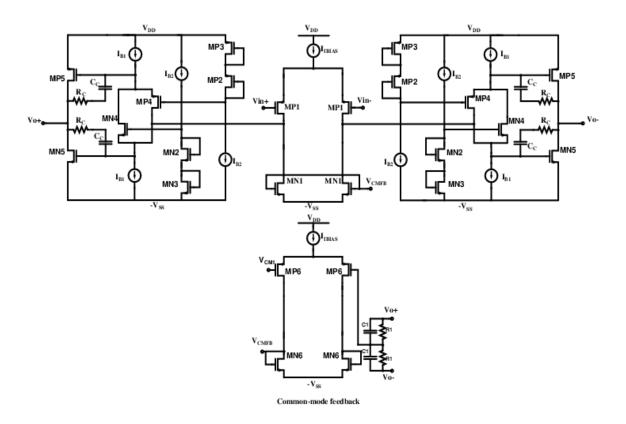

| 4.9    | Top Level TIA Filter Transistor Implementation                                | 61   |

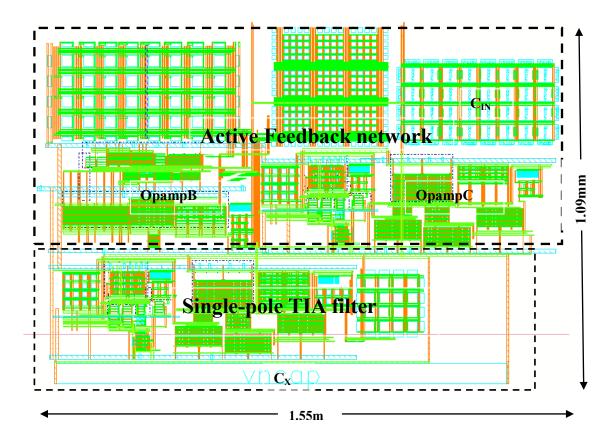

| 4.10   | Layout of the Proposed TIA Filter                                             | 62   |

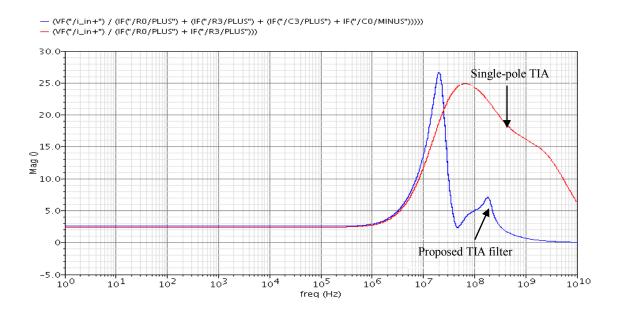

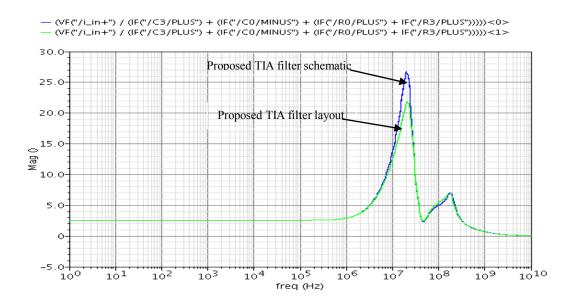

| 5.1    | Schematic Level AC Magnitude Response of the Proposed TIA Filter              | 65   |

| 5.2    | Schematic Level Small-Signal Input Impedance                                  | 65   |

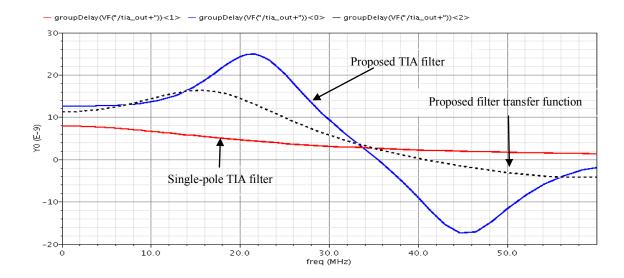

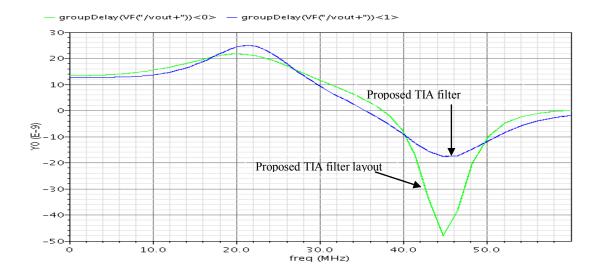

| 5.3    | Schematic Level In-Band Group Delay Variation                                 | 67   |

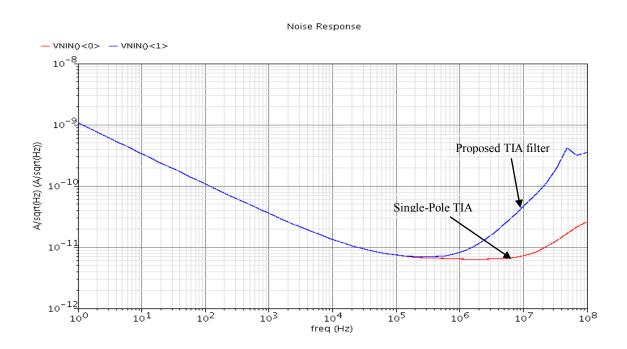

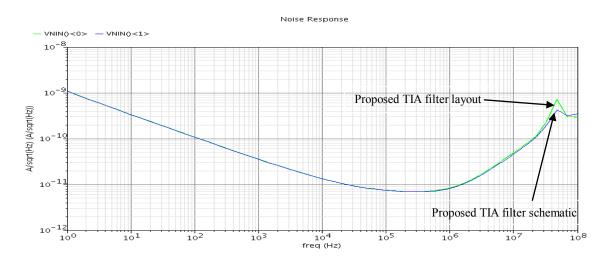

| 5.4    | Schematic Level Input-Referred Noise Current Density                          | 67   |

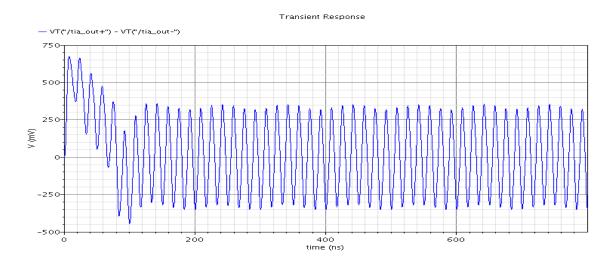

| 5.5    | Schematic Transient Response of Proposed TIA Filter to OOB Blocker            |      |

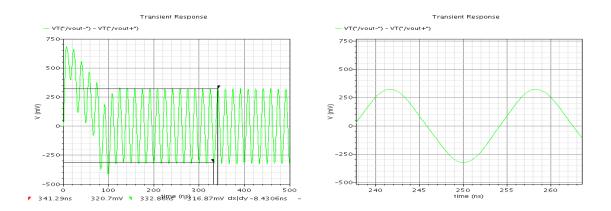

|        | of 4.5mA at 60MHz                                                             | 68   |

| 5.6    | Schematic Transient Response of Proposed TIA Filter to an In-Band             |      |

|        | Signal of $10\mu A$ at $10 MHz$ in the Presense of an OOB Blocker of $4.5 mA$ |      |

|        | at 60MHz                                                                      | 68   |

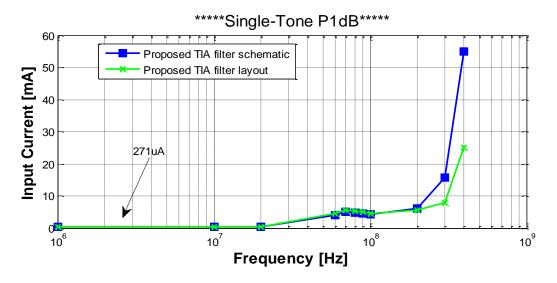

| 5.7    | Schematic Level Single-Tone 1dB Compression Point                             | 70   |

| 5.8    | Schematic Level In-Band Signal 1dB Compression due to OOB                     |      |

|        | Blocker Signal                                                                | 71   |

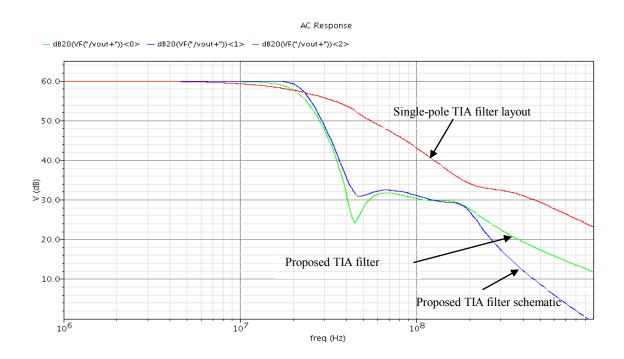

| 5.9    | Layout AC Magnitude Response of the Proposed TIA Filter                       | 72   |

| 5.10   | Layout Input Impedance of Proposed TIA Filter                                 | 73   |

| 5.11   | Layout In-Band Group Delay Variation                                          | 74   |

| 5.12   | Layout Input-Referred Noise Current Density                                   | 74   |

| FIGURE Page                                                                |    |

|----------------------------------------------------------------------------|----|

| 5.13 Layout Transient Response of Proposed TIA Filter to OOB Blocker of    |    |

| 4.5mA at 60MHz                                                             | 75 |

| 5.14 Layout Transient Response of Proposed TIA Filter to an In-Band Signal |    |

| of $10\mu A$ at $10MHz$ in the Presence of an OOB Blocker of $4.5mA$ at    |    |

| 60MHz                                                                      | 76 |

| 5.15 Layout Single-Tone 1dB Compression Point                              | 76 |

| 5.16 Layout In-Band Signal 1dB Compression due to OOB Blocker Signal       | 77 |

#### LIST OF TABLES

| TABLE |                                                                     | Page |

|-------|---------------------------------------------------------------------|------|

| 3.1   | Component Values for Macro-Model Simulations                        | 33   |

| 3.2   | Amplifier Loading                                                   | 38   |

| 3.3   | Summary of TIA Transistor Level Design Target Specifications and    |      |

|       | Op-amp Target Specifications                                        | 42   |

| 3.4   | Amplifier Slew-Rate Specifications                                  | 45   |

| 3.5   | Full Summary of TIA Transistor Level Design Specifications and      |      |

|       | Op-amp Target Specifications                                        | 45   |

| 4.1   | Transistor Dimensions, Device Values and Bias Conditions for OpampA |      |

|       | and OpampC                                                          | 52   |

| 4.2   | Transistor Dimensions, Device Values and Bias Conditions for        |      |

|       | OpampB                                                              | 60   |

| 4.3   | Summary of Amplifier Performance Parameters                         | 60   |

| 5.1   | TIA Input-Referred Integrated Noise Current                         | 66   |

| 5.2   | Proposed TIA Performance Summary                                    | 78   |

#### 1. INTRODUCTION

RF Front-end receivers find widespread application in this age of tremendous growth in wireless communication: from smartphone platforms, notebook computers, PDAs to handheld portable games such as the Playstation Portable (PSP). Several wireless communication standards have emerged as a result, adding to the traditional standards that already existed. Now we have GSM900, DCS1800, PCS1900 and WCDMA standards for cellular communication; WLAN a/b/g/n + WiMax , UWB Bluetooth standards for wireless data connectivity and communication; GPS for navigation; and FM/XM radio standards for entertainment [1], [2].

Usually in the aforementioned platforms- smartphones, notebook computers, PDAs - multiple wireless communication standards/radios coexist, resulting in the coined term multi-radio (multi-standard) platforms, e.g., today's smartphone will require GSM for cellular communications, Wi-fi/WLAN for internet connectivity, Bluetooth for short range connectivity and data transfer between itself and another phone, and GPS for navigation. The challenge is to find a way to integrate all these radios in these multi-radio platforms for cost-effective solutions; a reduction in the number of front-end receivers per device is the way to go.

There is the widespread notion that a single reconfigurable front-end architecture could be the ultimate cost-effective solution to cater to all standards in these multi-radio platforms. However, the argument in [3] is that the huge compromises which will have to be made in terms of performance and power dissipation makes this an unacceptable solution. The authors in [3] further contend that, multiple radios/standards will need to operate simultaneously for some period of time thus nullifying this solution as plausible, e.g., in a smartphone, a user can be surfing the internet (making use of WLAN radio)

This thesis follows the format of *IEEE Journal of Solid State Circuits*.

while talking on the phone (making use of GSM).

What is practical and is the current trend now, is to use broadband/multi-standard or reconfigurable front-ends that cater to two or three standards/bands at a time, thus reducing the number of front-end receivers in a practical manner, e.g., a dual-standard RF front-end receiver is built for W-LAN 802.11b/g (2.4-2.48 GHz) and W-CDMA-FDD (2.11-2.17 GHz) wireless standards in [2], a multi-standard direct-conversion RF front-end receiver is designed to cater to the WiMax and WiFi standards in the 4.9-6GHz range in [4], and a dual-band CMOS transceiver is designed for use in both IEEE 802.16e (mobile WiMAX) standard and WLAN standards in [5]. These multi-standard receivers suffer from out-of-band (OOB) interferer problems. Simply, when one standard is being utilized, signals in an adjacent standard/band, become OOB interferers or what is known as blockers, e.g., Bluetooth signals become interferer signals (blocker signals) when employing the GSM standard for communication between one cellphone user and another. Blockers are simply interferers that are large enough to de-sensitize the receiver chain. In addition, these multi-radio platforms suffer from other interference mechanisms such as OOB transmitter noise and limited switch isolation [3]. Some of these interferers down-convert as large blocking signals near the desired channel through the mixer.

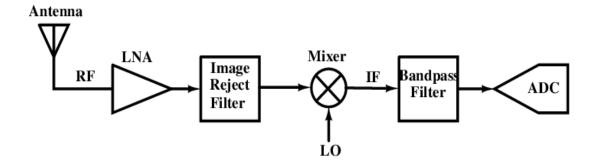

The homodyne receiver, otherwise known as the zero-IF architecture, is the RF front-end architecture of choice in these multi-standard front-end receivers because of its many advantages over the heterodyne architecture in terms of cost and complexity. A heterodyne RF front-end receiver conversion flow is shown in Fig. 1.1 [6].

Figure 1.1 Heterodyne RF Front-End Receiver.

Heterodyne receivers convert the RF signal to an intermediate frequency (IF). This architecture gives rise to what is known as the image problem [6] and the half-IF problem [6], thus the inclusion of an image reject (IR) filter in the front-end path to stem this issue. The IR filter is implemented as an external discrete passive component and this increases size and cost of the front-end receiver. Also, since the RF signal is converted to IF, a baseband bandpass filter is required after the mixer. In practice this filter is implemented using high Q off-chip SAW filters due to its stringent OOB attenuation requirements [6].

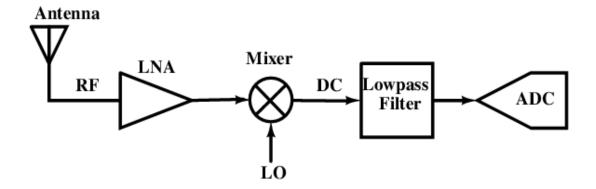

The homodyne receiver circumvents the aforementioned problems encountered in the heterodyne architecture. Firstly, the RF signal is converted directly to DC by the mixer and this solves the image problem [6]. Thus, the off-chip IR filter is not needed. Secondly, since the RF signal is directly converted to DC instead of IF by the mixer, an on-chip active low-pass filter can be used in the baseband path instead of the high Q off-chip SAW filter used for baseband filtering in the heterodyne architecture. This allows for a full monolithic (on-chip) RF front-end solution without the need for expensive discrete external devices and ultimately culminates in cost savings, thus making the homodyne receiver more amenable to multi-standard front-end receiver design.

Figure 1.2 Homodyne RF Front-End Receiver.

The disadvantage with the homodyne receiver topology shown in Fig. 1.2 is that it is hugely impacted by device flicker noise owing to the conversion of the RF input signal directly to DC after the mixer. Since the mixer is the first block in baseband, its flicker noise contribution is the most important. If flicker noise in the mixer can be reduced or eliminated altogether, the sensitivity of the receiver can be improved significantly.

Flicker noise of a MOS transistor is proportional to its DC bias current as [7]:

$$V_{n_{1/f}}^{2} = \frac{K_{f} I_{ds}^{af}}{C_{ox} L^{2}} \frac{1}{f^{ef}}$$

(1.1)

where  $C_{ox}$  is the unit oxide capacitance,  $K_f$  is a device specific constant, L is the length of the device,  $I_{ds}$  is the DC bias current, af and ef are current and frequency indices respectively.

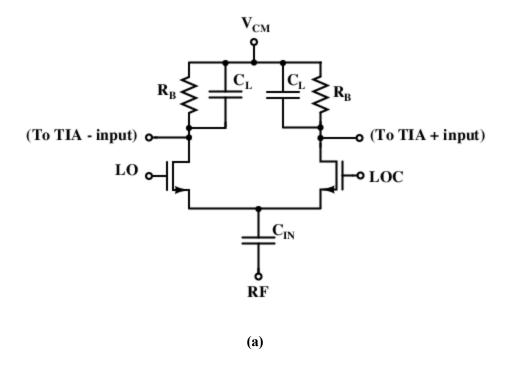

Figure 1.3 (a) Simplified Schematic of a Single-Balanced Passive Mixer. (b) Direct-Conversion Wireless Receiver with Current-Mode Passive Mixer.

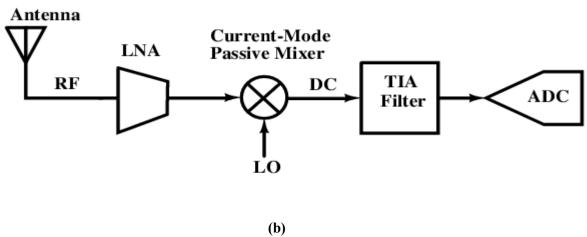

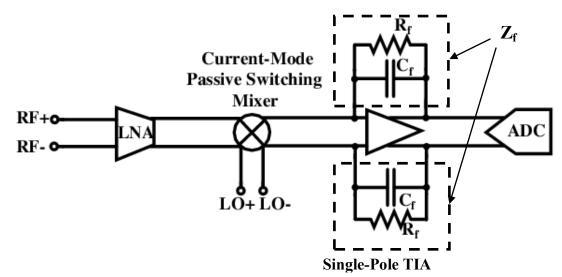

From (1.1), by adopting a passive mixer, flicker noise can be removed during frequency conversion because there is no DC biasing current. A mixer configuration that achieves this is the current-mode passive switching mixer [7] shown in Fig. 1.3(a). It eliminates the DC biasing current in the conventional Gilbert cell active mixer [8]. Using the

current-mode mixer, this leads to a different configuration for the homodyne receiver architecture, and this is shown in Fig. 1.3(b). The LNA becomes a transconductance, converting RF voltage input from the antenna into current, which is fed to the passive current-mode mixer and after down-conversion, a transimpedance amplifier (TIA) is used to convert this base band current to voltage which is eventually fed to the ADC or other succeeding blocks.

Usually the in-band signal current (wanted signal) from the mixer can be anywhere from a few micro-amps to hundreds of micro-amps. It is the job of the TIA to amplify this small in-band current signal to a large enough output voltage, which can be accurately detected and processed by the ADC or any other block following the TIA. The TIA must also be capable of rejecting the large OOB blockers that exist at close-in frequencies. These blockers can be as large as 20dB greater in magnitude than the in-band signal current from the mixer.

While the TIA provides amplification for small in-band signals and attenuation for OOB blockers, its input voltage swing must be very small, and its input impedance must ideally approach zero. This is because the transistors in the current-mode mixer shown in Fig. 3(a) are operated in triode region. As long as the drain-source voltage  $(V_{DS})$  of the mixer transistors is small, the channel resistance is very linear. However, as  $V_{DS}$  increases, the transistors approach the saturation region and the channel resistance becomes very non-linear. The drains of the MOS switching devices in the current-mode mixer are connected directly to the input of the TIA. Thus it is necessary to keep the voltage swing at the TIA input at a minimum to preserve the linearity of the mixer, and this means the TIA's input impedance must be kept at a minimum.

Traditionally, TIAs in the receiver chain have been implemented as single-pole filters since it is assumed that large OOB blockers will be handled by the ADC, e.g., in [4] a single-pole RC filter characteristic is used for the TIA because the blockers are accommodated by an oversampling, high dynamic range ADC later in the receiver chain.

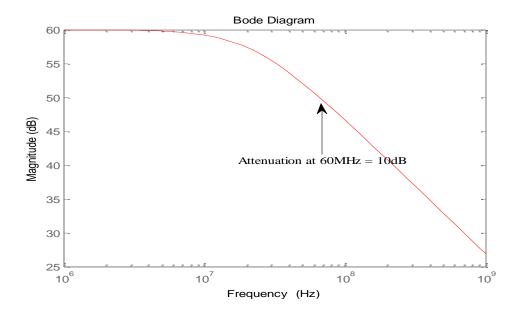

An example of a conventional single-pole response for a TIA having an in-band gain of 60dB and a 20MHz bandwidth is shown in Fig. 1.4.

Figure 1.4 Single-Pole TIA with  $60dB\Omega$  In-Band Gain and a Bandwidth of 20MHz.

The focus of this work is to provide higher order filtering before the ADC, and specifically to embed this filtering within the TIA. Higher order filtering before the ADC has the following advantages:

- a) It reduces the resolution of the ADC required in the frontend receiver, resulting in a lower number of bits for the ADC, reduced cost and complexity of the ADC.

- b) It reduces the cost and complexity of the ADC calibration circuitry

- c) It can potentially reduce the RF front-end receiver cost

In this work a  $3^{rd}$  order feedback TIA filter is proposed for multi-standard/reconfigurable/ broadband direct conversion RF receiver front-ends with a  $60dB\Omega$  in-band gain and a bandwidth of 20MHz. It offers 17.5dB more OOB attenuation

over the conventional single-pole TIA for close-in blockers at 60MHz and beyond. This feedback topology at the same time offers improved large signal linearity performance over the conventional single-pole TIA. Because the additional feedback circuitry is not in the signal path, the in-band performance of the single-pole TIA is not degraded; input impedance, flicker noise and in-band linearity are not sacrificed. The advantages of using a feedback topology for the proposed TIA filter are further explained in Section 2.

#### 2. THE BASIC TRANSIMPEDANCE AMPLIFIER FILTER

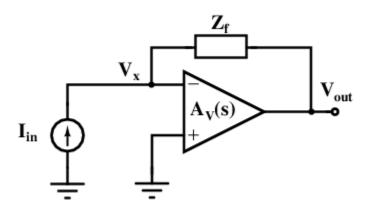

The basic single-ended transimpedance amplifier is shown in Fig. 2.1. The input current  $I_{in}$  is converted to voltage at its output,  $V_{out}$  through the feedback impedance  $Z_f$ . This conversion is linear due to the fact that  $Z_f$  is implemented as a passive impedance.

Figure 2.1 The Basic Transimpedance Amplifier.

#### 2.1 Transimpedance Amplifier Parameters

The basic parameters that characterize the transimpedance amplifier shown in Fig. 2.1 are the transimpedance gain and the input impedance. A brief discussion of these parameters is given as follows.

#### 2.1.1 Transimpedance Gain

This parameter characterizes the output voltage to input current gain and has the unit of ohms  $(\Omega)$ . For the circuit of Fig. 2.1 and with an op-amp open-loop gain of  $A_{\nu}$  (s), writing the nodal equation at the op-amp inverting input node gives:

$$I_{in} = \frac{V_x - V_{out}}{Z_f} \tag{2.1}$$

where:

$$V_{x} = -\frac{V_{out}}{A_{v}(s)} \tag{2.2}$$

Substituting (2.2) into (2.1) gives :

$$I_{in} = -\frac{V_{out}/A_{v}(s) + V_{out}}{Z_{f}}$$

(2.3)

After algebraic manipulation, the transimpedance gain is obtained as:

$$\frac{V_{out}(s)}{I_{in}(s)} = -Z_f \left[ \frac{A_v(s)}{1 + A_v(s)} \right]$$

(2.4)

For  $|A_v(j\omega)| \gg 1$ , the transimpedance gain reduces to :

$$\frac{V_{out}(s)}{I_{in}(s)} \approx -Z_f \tag{2.5}$$

which shows that the transimpedance gain is simply given by the value of the feedback impedance  $Z_f$  for sufficiently large values of op-amp open-loop gain  $A_V(s)$ .

#### 2.1.2 Input Impedance

The input impedance of the TIA is critical for preserving mixer linearity, as discussed in Section 1. Substituting  $V_{out} = -A_v(s) V_x$  into (2.1), we obtain:

$$I_{in} = \frac{V_x(1 + A_v(s))}{Z_f} \tag{2.6}$$

The input impedance is obtained as:

$$Z_{i,TIA}(s) = \frac{V_x}{I_{in}} = \frac{Z_f}{(1 + A_v(s))}$$

(2.7)

Ideally, the Opamp gain  $A_v(s) \to \infty$  and thus  $Z_{i,TIA} \to 0$  implying  $V_x \to 0$  from (2.7), which is what is desired. It can be recalled that a small TIA input impedance is desirable to keep the voltage swing  $V_x$ , which appears across the non-linear channel resistance of the mixer switching transistors at a minimum to preserve the mixer linearity. In practice, op-amps are not ideal and have finite open-loop gain,  $A_v(s)$  with a number of poles. Representing the op-amp in Fig. 2.1 as a single-pole op-amp for simplicity, its voltage gain can be expressed as:

$$A_{\nu}(s) = \frac{A_{\nu o}}{1 + s/\omega_p} \tag{2.8}$$

where  $A_{vo}$  is the DC gain and  $\omega_p$  is the -3dB frequency of the op-amp. When (2.8) is substituted into the input impedance expression obtained in (2.7) the following is obtained:

$$Z_{i,TIA}(s) = \frac{Z_f \ s + Z_f \ \omega_p}{s + \omega_p(1 + A_p(s))}$$

(2.9)

#### 2.2 The Conventional Single-Pole Transimpedance Filter

TIAs are employed as both an amplifier for in-band signals and a filter for OOB interferers in RF-front-end direct-conversion receiver chains as shown in Fig. 2.2.

Figure 2.2 Fully-Differential Direct-Conversion Wireless Receiver Block Diagram.

In Fig. 2.2 the feedback impedance  $Z_f$ , is implemented as a parallel combination of a capacitor  $C_f$  and resistor  $R_f$  thus forming a single-pole filter with a cut-off frequency (-3dB bandwidth) given by :

$$\omega_{tia} = \frac{1}{R_f C_f} \tag{2.10}$$

This conventional TIA topology is employed in [3] where it provides current-to-voltage conversion in a multi-standard receiver chain. As stated in the previous section, interference mechanisms inherent in multi-standard/broadband receivers produce large close-in OOB blockers. In [4] this first-order TIA filter is used because the blockers produced are accommodated by an oversampled, high dynamic range ADC later in the receiver chain.

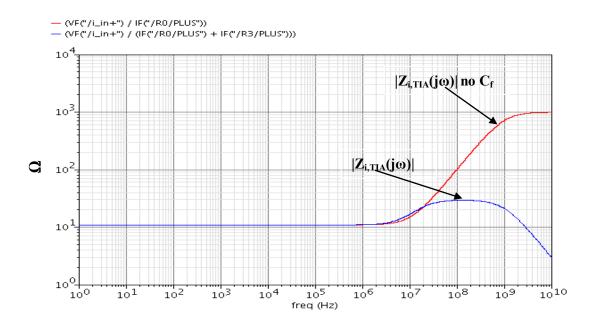

#### 2.2.1 Input Impedance of the Conventional Single-Pole TIA Filter

As discussed before, a low TIA input impedance is desirable for good mixer linearity. In conventional TIA filters,  $Z_f$  is made up of a resistor in parallel with a capacitor. Substituting (2.10) into the input impedance expression from (2.9) we obtain:

$$Z_{i,TIA}(s) = \frac{\left(\omega_{tia}R_f\right)s + \omega_p\omega_{tia}R_f}{s^2 + \left(\omega_{tia} + \omega_p(1 + A_{vo})\right)s + \omega_{tia}\omega_p(1 + A_{vo})}$$

(2.11)

$Z_{i,TIA}(s)$  has two poles, a dominant pole,  $\omega_d = \omega_{tia}$  and a high frequency pole  $\omega_{nd} = \omega_p(1+Av)$ ; and one zero,  $\omega_z = \omega_p$ . The DC input impedance is given by:

$$Z_{i,TIA,DC} = \frac{R_f}{(1 + A_{vo})} \tag{2.12}$$

Fig. 2.3 shows the input impedance plot,  $Z_{i,TIA}(s)$  of a single-pole TIA filter. The TIA has a DC transimpedance gain of  $1k\Omega$  ( $R_f = 1k\Omega$ ) and a bandwidth,  $\omega_{tia}$  of 20MHz. The TIA op-amp has a low frequency gain,  $A_{\nu o}$  of 1000V/V and a Gain-Bandwidth Product (GBW) of 1GHz. The op-amp -3dB frequency  $\omega_p$  is calculated to be 1MHz from the following:

$$GBW = A_{\nu o} \,\omega_{\nu} \tag{2.13}$$

Also shown in Fig. 2.4 is a plot of  $Z_{i,TIA}(s)$  for a TIA with a feedback impedance  $Z_f = R_f = 1k\Omega$ .

Figure 2.3 TIA Input Impedance Plotted for  $Z_f = R_f$  and  $Z_f = R_f || C_f$ .

From Fig. 2.3, the TIA input impedance magnitude starts at  $1\Omega$  at DC and remains at this value until 1MHz. The zero of  $Z_{i,TIA}(s)$  is located at this frequency and it causes  $|Z_{i,TIA}(s)|$  to increase/rise with a 20dB/decade slope. This rise in  $|Z_{i,TIA}(s)|$  from 1MHz onwards is cancelled out by the dominant pole,  $\omega_d$  of  $Z_{i,TIA}(s)$  at 20MHz and  $|Z_{i,TIA}(s)|$  flattens out until the higher frequency pole of  $Z_{i,TIA}(s)$  is encountered at 1GHz. From this point onwards  $|Z_{i,TIA}(s)|$  decreases with a -20dB/decade slope. It can be noted from Fig. 2.4 that with just resistive feedback  $R_f$ , the input impedance continues to increase from 1MHz frequency until it eventually reaches the value of  $R_f$  at high frequencies since in this case the dominant pole of  $Z_{i,TIA}(s)$  formed by  $\omega_{tia}$  ceases to exist and  $Z_{i,TIA}(s)$  will have only one pole at high frequency.

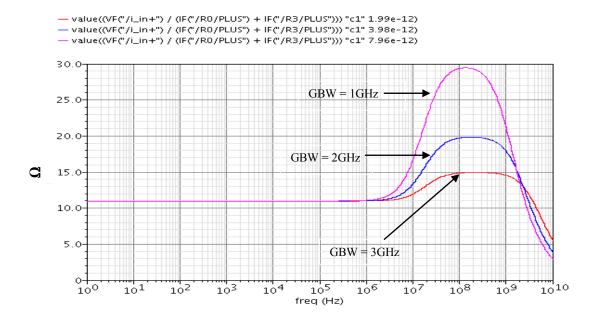

For the same TIA op-amp DC gain, the higher the GBW of the op-amp, the higher the zero frequency of  $Z_{i,TIA}(s)$  and the lower the rise in  $Z_{i,TIA}(s)$  before  $\omega_d$  takes effect to flatten the magnitude response of  $Z_{i,TIA}(s)$ . Thus the higher the GBW value of the TIA op-amp, the lower the TIA filter input impedance and this is demonstrated in Fig. 2.4 where GBW figures of 1GHz, 2GHz and 3GHz are used for the TIA op-amp

Figure 2.4 Comparison of TIA Input Impedance for Different Values of Op-amp GBW.

In this work a GBW of 1GHz is used for the TIA op-amp. This GBW value gives an acceptable input impedance value (comparable to input impedance levels in published works) across the full-spectrum of signals expected to be processed while keeping power consumption low.

#### 2.2.2 Drawbacks of the Conventional Single-Pole TIA

The transfer function of the conventional single-pole response for a TIA having an inband gain of 60dB and a 20MHz bandwidth was shown in Fig. 1.4. For close-in OOB

blockers at 60MHz, this filter produces 10dB of attenuation. Typically blockers of up to  $\pm 10$ mA can be expected at such frequencies. Using a single pole TIA filter, this produces a TIA output voltage swing of  $\pm 2.8$ V. Assuming a maximum in-band signal level of  $\pm 1$ mA is to be expected from the mixer, the output voltage swing of the TIA will be  $\pm 1$ V. If no additional filtering is done before the ADC, the in-band signal will represent 36% of the full-scale ADC input level. With additional OOB filtering before the ADC, the in-band signal level will represent a greater percentage of the full-scale ADC input voltage. The advantage in this is that, a lower resolution ADC which has lower number of bits will be required for processing of the baseband signals in the receiver chain. This will reduce the ADC and ADC calibration circuitry cost and complexity and offer a potential savings in power and cost of the receiver chain.

A number of publications have sought to provide extra OOB blocker attenuation (higher order filtering) by cascading filtering blocks to the single-pole TIA as shown in Fig. 2.5. In [5] a filter is cascaded to a gain-programmable TIA and in [9] a biquadratic transimpedance response is implemented as a cascade of two stages.

Figure 2.5 Extra OOB Blocker Attenuation through Cascading.

While cascading can provide the extra OOB attenuation required before the ADC to relax its specifications, it offers no relaxation for the large signal linearity requirements

of the single-pole TIA. This is because the same signal swings will appear at the output of the single-pole TIA filter op-amp with or without an additional cascaded filtering stage. And since the TIA op-amp is the source of non-linearity of the single-pole TIA filter, there will be no improvement in its large signal linearity performance.

If we can embed the extra filtering within the TIA filter in the form of feedback, we can achieve the task of relaxing the ADC specifications while at the same time providing improved TIA large signal linearity performance. This will improve receiver linearity and sensitivity and can potentially provide a savings in power and cost of the receiver chain. This argument assumes that the additional power required for the active feedback will be offset by the savings in power of employing a lower resolution ADC for signal processing. Also, since the added feedback block is not in the signal path, the in-band performance of the single-pole TIA is not degraded; input impedance, flicker noise and in-band linearity are not sacrificed. Additionally, it allows for design of the baseband section of the RF front-end receiver at lower supply voltages.

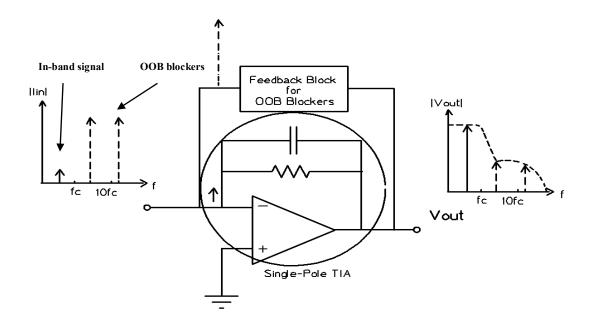

#### 3. PROPOSED TIA FILTER

The proposed TIA filter employs an inverse Chebyshev 3<sup>rd</sup> order filter approximation in a feedback topology and is shown conceptually in Fig. 3.1. The main idea is to divert large OOB signals that appear at the input nodes of a single-pole TIA filter into an active feedback circuit. This topology provides improved OOB blocker attenuation over the single-pole TIA filter without degrading the in-band performance of the single-pole TIA. Furthermore, this feedback topology allows for design of the baseband section of the front-end receiver chain with low supply voltages and offers improved large-signal linearity over the single-pole TIA filter.

Figure 3.1 Conceptual View of the Proposed TIA Using Active Feedback.

#### 3.1. Conventional Filter Approximations

An inverse Chebyshev filter approximation is chosen for the proposed TIA filter realization. Its features make it the ideal choice over other conventional filter approximations for the purpose of this work.

#### 3.1.1. Lowpass Filter Design Fundamentals

Fig. 3.2 shows an idealized brick-wall low-pass filter. It has full transmission of signals in the pass band, characterized by the bandwidth,  $\omega_p$ , and has complete attenuation in the stop-band, with an abrupt pass to stop band transition. The pass band denotes the -3dB bandwidth of the desired signal band while the stop band denotes OOB signals (unwanted interferer signals) that the filter is required to attenuate.

Figure 3.2 Idealized Brick-Wall Filter.

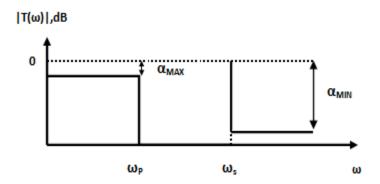

In practice a brick-wall response cannot be achieved and thus OOB signals close to the bandwidth  $\omega_p$  are not completely attenuated. In practical filter design, specifications are given to define the passband frequency,  $\omega_p$ ; maximum attenuation that can be tolerated within the passband,  $\alpha_{MAX}$ ; closest out-of-band signal frequency,  $\omega_s$ ; and the minimum attenuation desired at this frequency and beyond,  $\alpha_{MIN}$ . This is illustrated by Fig. 3.3. It should also be noted that a non-abrupt transition band exists for the practical filter given by the frequency range  $\omega_s$  to  $\omega_p$ , something which is non-existent in the brick-wall filter.

Figure 3.3 Practical Lowpass Filter Design Parameters.

#### 3.1.2. Comparison of Lowpass Filter Approximations

The conventional practical filter approximations that exist are:

- a. Butterworth

- b. Chebyshev

- c. inverse Chebyshev

- d. Elliptic

In addition to the practical filter design specifications given in the previous section, a parameter which is often used to compare these filter approximations is group delay. Ideally a linear phase response within the pass band is desirable in analog filters to avoid distortion of the in-band signals. However in practical filter approximations such as the above, the phase deviates from this linear response. The group delay, which is defined as the derivative of the phase response of the filter with respect to angular frequency, can be used to quantify the distortion in the desired in-band signal introduced by phase differences for different frequencies within the filter.

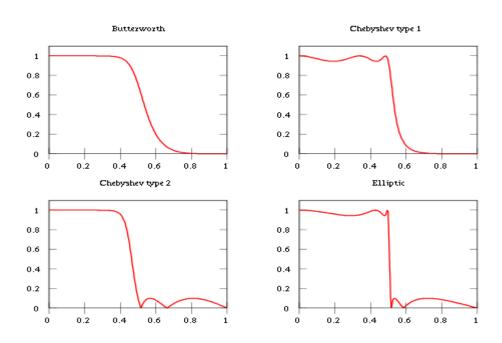

For the same order of filtering, stop-band attenuation at close-in frequencies increases in the following order:

Butterworth< Chebyshev/inverse Chebyshev < Elliptic.

Whereas for the same order of filtering, in-band group delay variation decreases in the following order:

Elliptic Chebyshev < inverse Chebyshev < Butterworth.

Fig. 3.4 shows a comparison of the magnitude plots of the aforementioned filter approximations. From the discussion in Section 1, a filter is required which is capable of providing maximum attenuation at close-in frequencies. For the same order of filtering, the elliptic filter would be the best possible choice with regards to stop band attenuation only. However, the inverse Chebyshev filter represents the best possible combination of stop band attenuation (desired for OOB blocker attenuation) and in-band group delay (small group delay variation is desirable for minimal in-band signal distortion arising from non-linear phase). Since the inverse Chebyshev filter has no in-band ripples, it is chosen over the elliptic filter in the design of the proposed TIA filter. A third order filter design is targeted to provide adequate close-in OOB blocker attenuation.

Figure 3.4 Comparison of Filter Approximations; All Filters are Fifth Order.

### 3.2 System Level Design of 3<sup>rd</sup> Order Inverse Chebyshev Feedback Filter with Bandwidth of 20MHz and Notch at 60MHz

The block diagram for the proposed feedback TIA is shown in Fig. 3.5. The transfer function of this system is given by :

$$T(s) = \frac{I(s)}{V(s)} = \frac{A(s)}{1 + A(s)H(s)}$$

(3.1)

where A(s) represents the single-pole TIA filter and H(s) represents the active feedback network required for improved OOB attenuation. The closed-loop system transfer function, T(s), is obtained from a 3<sup>rd</sup> order inverse Chebyshev filter approximation. Since the filter approximation equations are stable, ideally T(s) will be inherently stable.

# Mixer Single-Pole TIA Vout ADC Feedback Network H(s)

Figure 3.5 The General Feedback Structure.

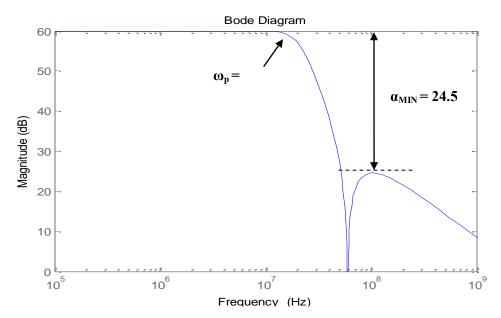

A  $3^{rd}$  order inverse Chebyshev filter is synthesized using MATLAB. Generally for a fixed notch frequency (in this case 60MHz), the greater the  $\alpha_{MIN}$ , the lower the -3dB bandwidth of the filter as shown in Fig. 3.6.

Figure 3.6 Trade-Off between Bandwidth and Stop-Band Attenuation for a Fixed Notch Frequency.

For a bandwidth of 20MHz with a 60MHz notch, the largest  $\alpha_{MIN}$  achievable is 35.5dB as shown in Fig. 3.7. The corresponding normalized inverse Chebyshev transfer function is given as :

$$T(s) = A \cdot \frac{1}{s + 0.425} \left( \frac{s^2 + 1.333}{s^2 + 0.3743 \, s + 0.1591} \right) \tag{3.2}$$

where:

$$A = \frac{0.1591 \times 0.425}{1.333} \tag{3.3}$$

Figure 3.7 Magnitude and Phase Plot of the Synthesized 3rd Order Inverse Chebyshev Filter.

Note that (3.3) is required to scale the passband gain of (3.2) to 0dB. The coefficients in (3.2) are replaced with variables as follows:

$$T(s) = \frac{A}{s+D} \left( \frac{s^2 + n}{s^2 + B \, s + C} \right) \tag{3.4}$$

where n = 1.333; B = 0.3743; C = 0.1591; D = 0.4250

Magnitude and frequency scaling of T(s) to give a low frequency gain of  $60\text{dB}\Omega$  (1000  $\Omega$ ), a bandwidth of 20MHz and a notch frequency of 60MHz gives :

$$T(s) = \left(\frac{s^2 + n\omega_o^2}{s^2 + B\omega_0 s + C\omega_o^2}\right) \left(\frac{A_\omega}{s + D\omega_0}\right)$$

(3.5)

where  $A_{\omega}$ = -1000CD $\omega_{o}/n$  and  $\omega_{0} = \sqrt{n} \times 60e6$ . Note that the magnitude scaling factor  $A_{\omega}$  is negative since the TIA has a negative gain as derived in (2.4). The frequency response of (3.5) is shown in Fig. 3.8.

In (3.5), the  $2^{nd}$  term in brackets represents the single-pole TIA filter function, A(s). From (3.5):

$$T(s)|_{s=0} = -1000\Omega \tag{3.6}$$

$$A(s)|_{s=0} = -\frac{1000C}{n} = -R_f \tag{3.7}$$

Clearly (3.6) and (3.7) are different, meaning that for a closed-loop TIA DC gain  $T(s)/_{s=0}$  of  $60dB\Omega$  the feedback resistor,  $R_f$ , of the single-pole TIA will need to be  $119\Omega$  from (3.7). This value of  $R_f$  will increase the input referred noise current density of the single-pole TIA filter by the ratio  $(C/n)^2 A^2 / Hz$ . Also, since we do not want to alter the small-signal in-band characteristics of the conventional single-pole TIA,  $R_f$  is kept at  $1K\Omega$ . This requires us to introduce a scaling factor, X into (3.5) such that (3.6) will equal (3.7):

$$T(s) = \left(\frac{1}{X} \frac{s^2 + nw_0^2}{s^2 + B w_0 s + C w_0^2}\right) \left(\frac{-A_w K X}{s + D w_0}\right)$$

(3.8)

where X = n/C. (3.8) gives the desired transimpedance function we want to synthesize. Thus (3.8) is equated to (3.1) as shown:

$$T(s) = \left(\frac{1}{X} \frac{s^2 + n w_o^2}{s^2 + B w_0 s + C w_o^2}\right) \left(\frac{-A_w KX}{s + D w_0}\right) = \frac{A(s)}{1 + A(s)H(s)}$$

(3.9)

As stated before, A(s) represents the conventional single-pole TIA filter and forms the forward path of the closed-loop system. What remains then, is to derive the feedback transfer function H(s) from (3.9) as:

$$H(s) = \frac{I(s)}{V(s)} = \frac{as^3 + bs^2 + cs + d}{s^2 + p}$$

(3.10)

where:

$$a = (X - 1) Y (3.11)$$

$$b = (XB + D(X - 1))Y\omega_0$$

(3.12)

$$c = (C - n + DB) XY \omega_0^3$$

(3.13)

$$d = D(XC - n)Y\omega_0^3 \tag{3.14}$$

$$p = n\omega_0^2 \tag{3.15}$$

$$Y = A_{\omega} \tag{3.16}$$

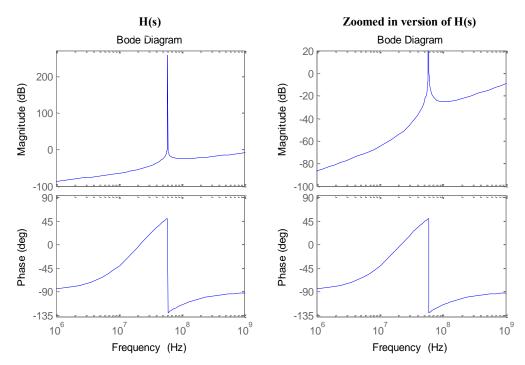

(3.10) gives the feedback function we need to implement. H(s) in essence is a high pass transfer function as shown in Fig. 3.9. It can be thought of as being transparent to inband signals and only being active when OOB signals are present.

Figure 3.8 Synthesized Inverse Chebyshev Magntiude Plot with a Passband Gain of  $60dB\Omega$ , a Bandwidth of 20MHz with a 60MHz Notch.

Figure 3.9 Magnitude and Phase Plot of H(s).

#### 3.2.1 Approximation of H(s) for Practical Circuit Implementation

It is possible to implement H(s) in several different ways, however the choice of implementation may introduce low frequency poles into the feedback loop thus making the proposed TIA unstable. For our application, we want to be able to implement H(s) as a voltage input, voltage output biquad (two pole function with 2 zeros) in which the voltage to current conversion is done through a capacitor. Thus we factor out 'as' from (3.10) to obtain:

$$H(s) = H_1(s)H_2(s) = \frac{I}{V}\frac{V}{V} = as\left(\frac{s^2 + b/as + c/a + d/as}{s^2 + p}\right)$$

(3.17)

where 'as' is realised by a capacitance. The term in brackets constitutes the voltage in, voltage out biquad, which is denoted as  $H_2(s)$ . It is not in a form that can be readily implemented at circuit level. By eliminating the last term in the numerator of  $H_2(s)$ , we obtain a biquad function which can be easily implemented:

$$H'(s) = H_1(s) H_2'(s) = \frac{I}{V} \frac{V}{V} = as \left( \frac{s^2 + b/a s + c/a}{s^2 + p} \right)$$

(3.18)

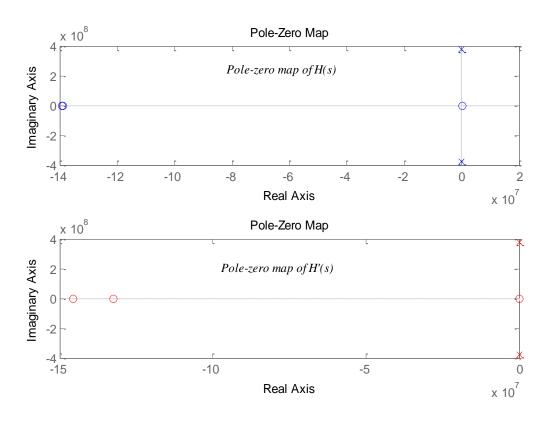

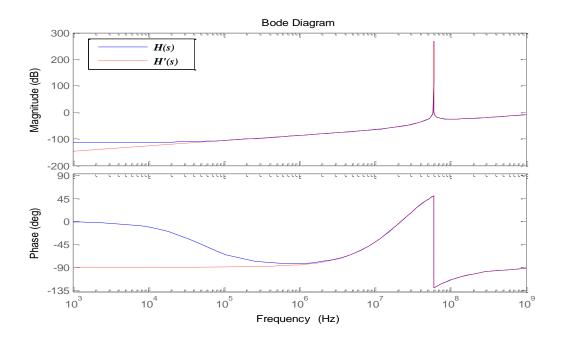

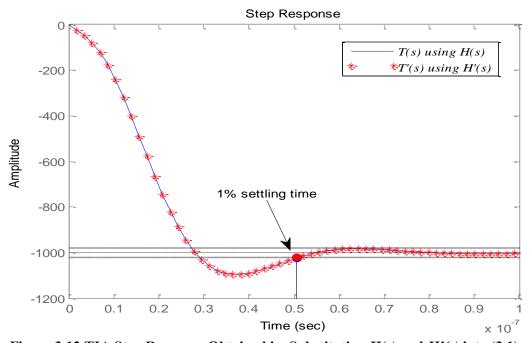

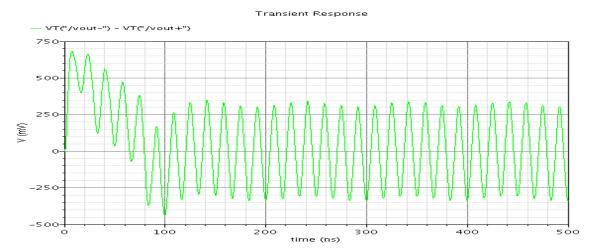

Now (3.18) is in a form which is amenable to circuit implementation. Matlab pole-zero plots in Fig. 3.10 show that the zero locations of (3.17) and (3.18) are different. However, a look at the frequency response plots of (3.17) and (3.18) in Fig. 3.11 show that they are the same. A step response in Fig. 3.12 obtained after substituting (3.17) and the modified form in (3.18) into (3.1) shows that the TIA filter stability is not affected. Thus from this point on, (3.18) is used.

Figure 3.10 Pole- Zero Map of H(s) and H'(s).

Figure 3.11 Matlab Frequency Response of H(s) and H'(s).

Figure 3.12 TIA Step Response Obtained by Substituting H(s) and H'(s) into (3.1).

Substituting the values of the variables a,b,c, and p into (3.18) gives :

$$H'(s) = H_1(s) H_2'(s) = 53 \times 10^{-12} s \left( \frac{s^2 + 2.78 \times 10^8 s + 1.93 \times 10^{16}}{s^2 + 1.42 \times 10^{17}} \right)$$

(3.19)

The general form of a biquadratic transfer function with arbitrary zeros is given by:

$$B(s) = \frac{a s^2 + b s + c}{s^2 + \frac{w_0}{Q} s + {w_0}^2}$$

(3.20)

Comparing (3.19) to the general form in (3.20) shows that H'(s) is an infinite Q function. This is evident in the plots of Fig. 3.11 where we see that there is infinite peaking in (3.19). This peaking is due to the 60MHz notch of the inverse Chebyshev filter. In the front-end receiver, OOB blockers are not confined to a single frequency and what we seek to do in this work is to provide attenuation to OOB blockers from 60MHz and beyond. What is important is that the designed filter provides adequate attenuation for the full-scale blocker signal magnitudes expected at 60MHz and higher frequencies. Thus, the 60MHz notch is not necessary. By removing this notch, the peaking in H'(s) can be eliminated. Ultimately, the entire feedback function, H'(s), with the peaking removed becomes:

$$H''(s) = \frac{I(s)}{V(s)} \frac{V(s)}{V(s)}$$

(3.21a)

$$H''(s) = H_1(s) H_2''(s)$$

(3.21b)

$$H''(s) = 53 \times 10^{-12} \, s \, \left( \frac{s^2 + 2.78 \times 10^8 s + 1.93 \times 10^{16}}{s^2 + 3 \times 10^8 s + 1.42 \times 10^{17}} \right)$$

(3.21c)

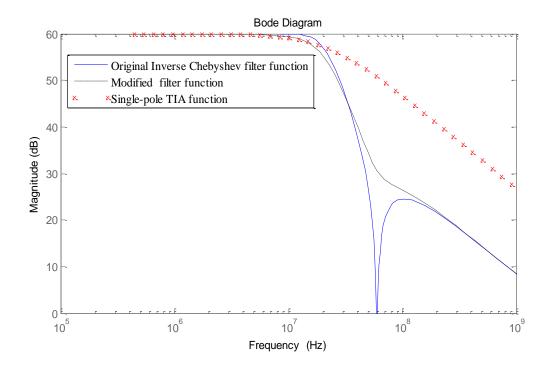

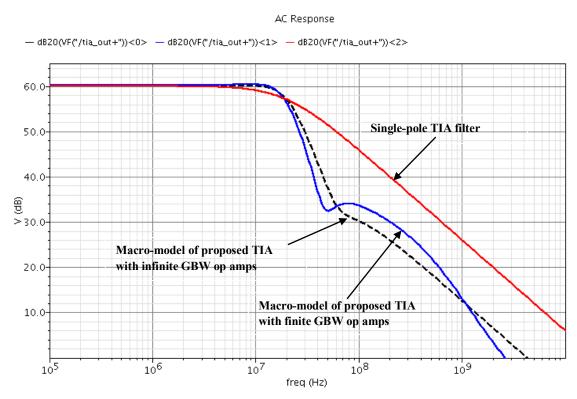

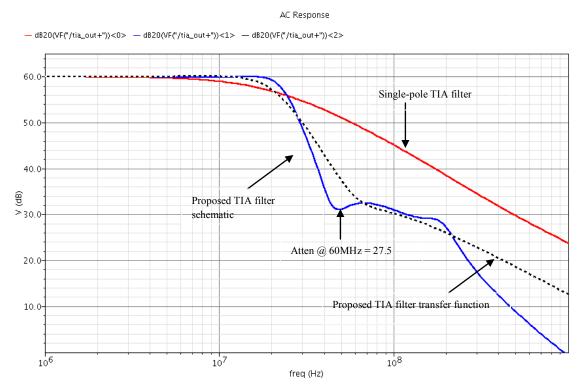

MATLAB plots of the closed-loop system magnitude responses, T''(s) and T(s), are shown in Fig. 3.13. Also superimposed is the transfer function of the single-pole TIA filter for comparison. It will be shown in later sections that though the notch at 60MHz is removed, the modified TIA filter provides adequate attenuation for the close-in OOB blockers (full-scale magnitude of 4.5mA) that this design targets. Although by removing

the notch, the bandwidth of the TIA is reduced, it is trivial to extend the bandwidth back to 20MHz by frequency scaling or to compensate for this loss by adjusting the value of the TIA feedback capacitor,  $C_{\rm f}$ .

Figure 3.13 Comparison of Original Inverse Chebyshev Filter, Modified Filter and Single-Pole Filter Functions.

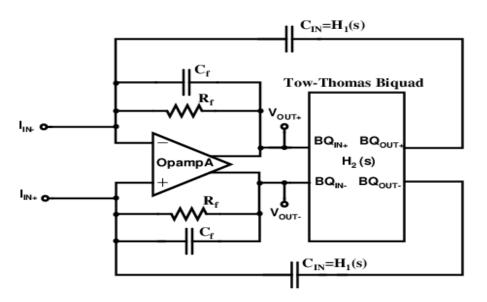

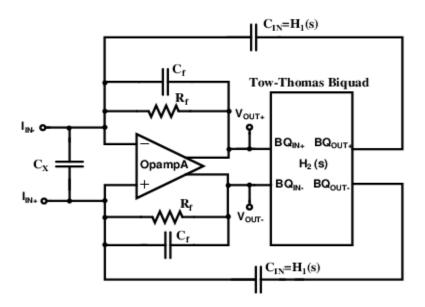

H''(s) in (3.21) is essentially a biquad which is divided into  $H_I(s)$  and  $H_2''(s)$ .  $H_I(s)$  represents a voltage-to-current converter and its form means it can readily be implemented with a 53pF capacitor.

In the circuit realization of  $H_2$  ''(s), the first target is to minimize its power consumption. This means utilizing a biquad topology with a minimal number of op-amps. Also, the biquad architecture chosen must be capable of implementing arbitrary transmission zeros

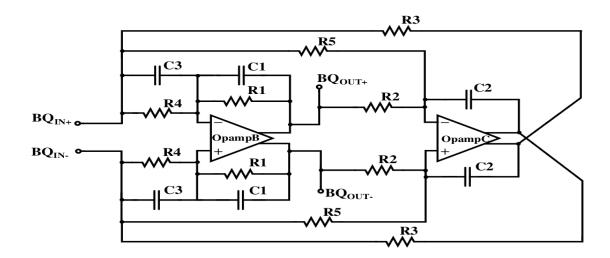

as the numerator of  $H_2$ ''(s) demands. A biquad topology that uses the lowest number of op-amps possible and at the same time implements arbitrary transmission zeros is a feedforward Tow-Thomas biquad.  $H_2$ ''(s) is thus implemented with this biquad topology.

## 3.3. Tow-Thomas Based Implementation of $H_2$ "(s)

The Tow-Thomas fully-differential biquad is shown in Fig. 3.14 .  $H_2$  ''(s) from (3.21c) is given as:

$$H_2''(s) = \frac{s^2 + 2.78 \times 10^8 s + 1.93 \times 10^{16}}{s^2 + 3 \times 10^8 s + 1.42 \times 10^{17}}$$

(3.22)

Figure 3.14 Fully-Differential Tow-Thomas Biquad for Implementing Second Order Functions with Arbitrary Transmission Zeros.

The transfer function for the feedforward Tow-Thomas of Fig. 3.14 is given as :

$$H_2''(s)_{TT} = -\frac{(C_3/C_1) s^2 + s/R_4C_1 + 1/R_5 R_3 C_2 C_1}{s^2 + s/R_1 C_1 + 1/R_2 R_3 C_2 C_1}$$

(3.23)

## 3.4 Macro-Modeling of the Proposed TIA Filter in Cadence

Equating the constant terms in the denominators of (3.20), (3.22) and (3.23) gives :

$$\omega_0 = \frac{1}{R_2 R_3 C_2 C_1} = 1.42 \times 10^{17} \tag{3.24}$$

A choice of  $1K\Omega$  is made for  $R_2$  and  $R_3$ . Also,  $C_1$  and  $C_2$  are chosen to have the same value and their value is calculated from (3.24) to be 2.65pF. Now equating the other coefficients of the numerator and the denominator terms of (3.20), (3.22) and (3.23) gives the values of  $R_1$ ,  $R_4$ ,  $R_5$ , and  $C_3$ .

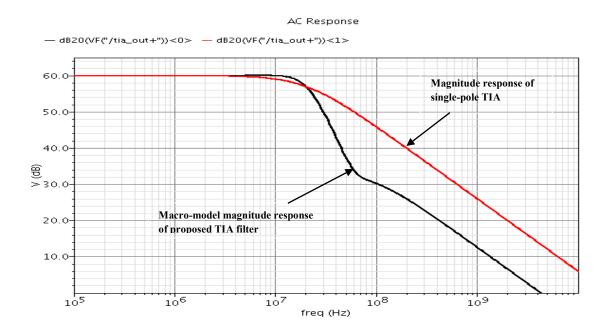

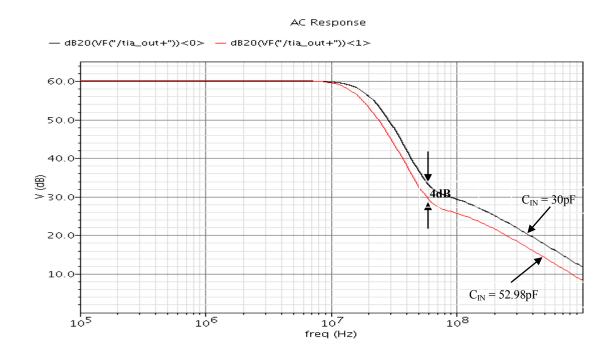

The proposed TIA filter is implemented in Cadence using ideal op-amps with capacitors and resistors. The top-level system is shown in Fig. 3.15. Fig. 3.16 shows the AC response of the TIA and this response is compared with that of the single-pole TIA filter, which is superimposed in the plot. The list of component parameters calculated from (3.20), (3.22) and (3.23) is given in Table 3.1.

Figure 3.15 Macro-Model of Proposed TIA Filter Using Ideal Op-amps in Cadence.

**Table 3.1 Component Values for Macro-Model Simulations.**

| Simulation Condition | Simulation Conditions:OpampA, OpampB and OpampC have 60dB DC Gain, GBW = |                |         |  |  |  |

|----------------------|--------------------------------------------------------------------------|----------------|---------|--|--|--|

|                      | infinite                                                                 |                |         |  |  |  |

| Component            | Component Value Component                                                |                |         |  |  |  |

| $C_{\mathrm{F}}$     | 7.2pF                                                                    | $R_1$          | 1.26ΚΩ  |  |  |  |

| $R_{\mathrm{F}}$     | 1ΚΩ                                                                      | R <sub>2</sub> | 1ΚΩ     |  |  |  |

| C <sub>IN</sub>      | 52.98pF                                                                  | R <sub>3</sub> | 1 ΚΩ    |  |  |  |

| $C_1$                | 2.65pF                                                                   | R <sub>4</sub> | 1 ΚΩ    |  |  |  |

| $C_2$                | 2.65pF                                                                   | R <sub>5</sub> | 7.39 ΚΩ |  |  |  |

| C <sub>3</sub>       | 2.65pF                                                                   |                |         |  |  |  |

Figure 3.16 Proposed TIA Filter Magnitude Response Using Ideal Op-amps with Infinite GBW.

# 3.4.1 Macro-Modeling Using Single-Pole Op-amps with Finite Gain and Finite GBW

In the previous section, macro-modeling was done in Cadence using op-amps with finite gain of 60dB and infinite GBW. However, practical op-amps have GBW limitations and this leads to deviation from the ideal filter frequency response, especially at high frequencies. Although the rule of thumb is to use GBW values of  $10 \times f_{3dB}$ , we note that for the proposed TIA filter, it is important to determine how much the high frequency response deviates from the ideal response in Fig. 3.16, since the filter is required to process high frequency OOB blockers in addition to the in-band signals. Also, since we are dealing with a feedback system, it is important to examine how the loop stability will be affected by the finite GBW of the op-amps within the loop.

A detailed look at the op-amp GBW limits in this section then is important to prevent over-design since the higher the GBW, the greater the power consumption. Thus, we can use the minimum possible GBW values for the op-amps to keep power consumption at a minimum without distorting the filter shape at high blocker frequencies. It will be recalled from section 2 that the GBW of OpampA is important for keeping the input impedance of the TIA at a minimum, and a minimum of 1 GHz GBW was determined for this op-amp. Therefore, the GBW of OpampA is fixed at 1GHz. What remains is to determine the acceptable GBW values for OpampB and OpampC. A single-pole model is used for the op-amps.

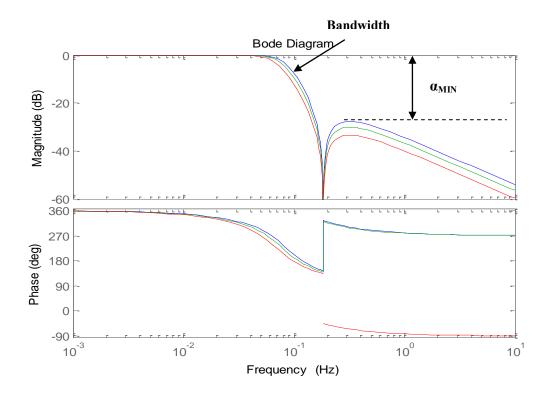

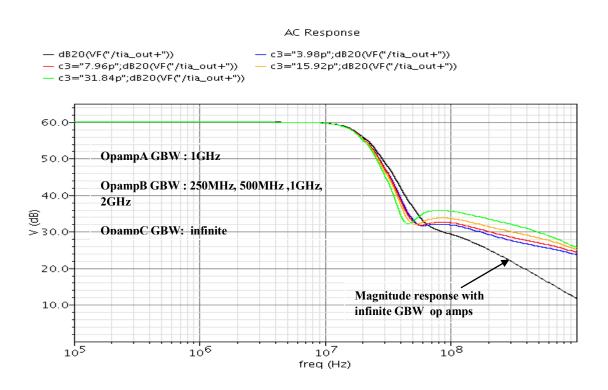

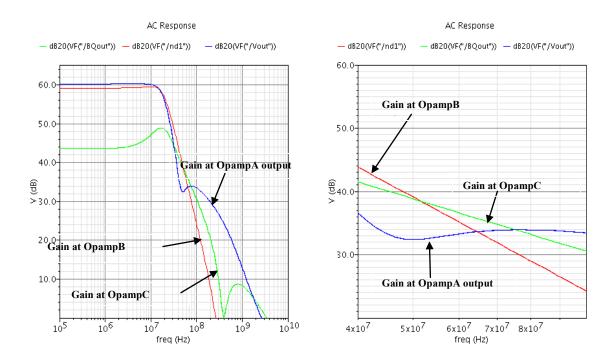

Firstly, we look at the effect of finite GBW of OpampB on the filter shape. An infinite GBW is used for OpampC and the GBW of OpampB is varied from 250MHz – 2GHz and the resulting TIA magnitude response is plotted in Fig. 3.17.

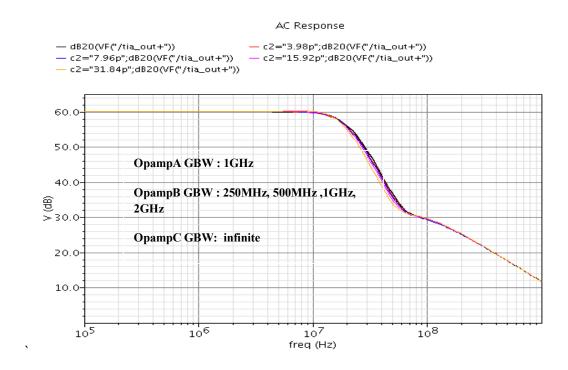

Secondly, we look at the effect of finite GBW of OpampC on the filter shape. An infinite GBW is used for OpampB and the GBW of OpampC is varied from 250MHz – 2GHz and the resultant filter magnitude response is plotted in Fig. 3.18.

Two observations can be made from the simulation plots of Fig. 3.17 and Fig. 3.18:

- a) Decreasing the GBW of OpampB in the biquad has the primary effect of decreasing  $\alpha_{MIN}$ . As a secondary effect, the bandwidth of the filter decreases as OpampB GBW is decreased .

- b) As the GBW of OpampC is decreased, the bandwidth of the filter decreases. GBW variation in OpampC does not have a significant effect on the OOB attenuation of the filter.

Figure 3.17 Proposed TIA Filter Response for the Following Op-amp GBW Conditions: OpampA - 1GHz, OpampC - Infinite, OpampB - 250MHz, 500MHz, 1GHz, 2GHz.

Figure 3.18 Proposed TIA Filter Response for the Following Op-amp GBW Conditions: OpampA -1GHz, OpampB - Infinite, OpampC - 250MHz, 500MHz, 1GHz, 2GHz.

#### 3.4.2 Effect of Finite Op-amp GBW on Stability

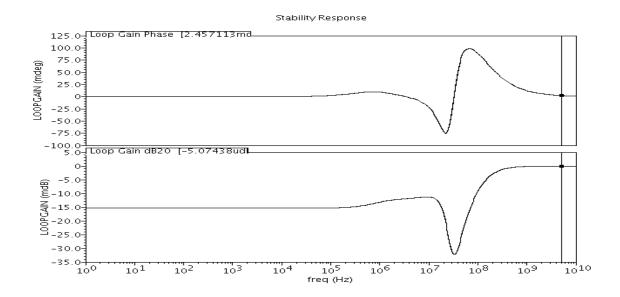

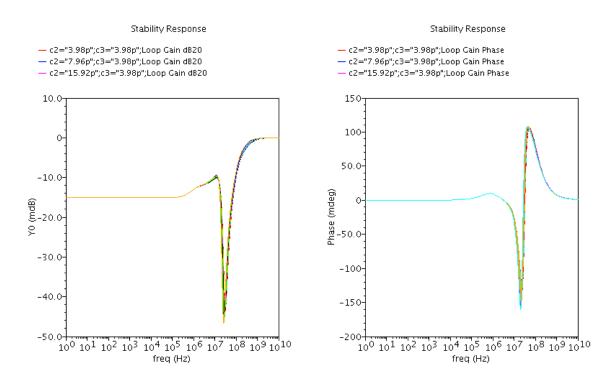

Fig. 3.19 shows the loop gain of the proposed TIA filter for op-amp gain of 60dB and infinite GBW. It can be seen that the loop gain does not exceed 0dB and thus we have a stable system.

Next we look at the effect of finite op-amp GBW on the loop gain and stability of the proposed TIA filter. As stated before a GBW of 1GHz is chosen for OpampA. In the previous section we varied the GBWs of both OpampB and OpampC from 250MHz-2GHz independently using single-pole models for the amplifiers. These GBW values are typical, and can be easily achieved in sub-micron processes such as IBM 90nm. In this section, both OpampB and OpampC GBWs are swept from 250MHz-2GHz and Fig. 3.20 plots the variation in the loop gain.

Figure 3.19 Proposed TIA Filter Loop Gain Magnitude and Phase Response Using Opamps with 60dB Gain and Infinite GBW.

Figure 3.20 Loop Gain Magnitude and Phase Response for a Parametric Sweep of OpampB and OpampC GBWs: 250MHz-2GHz.

We see from Fig. 3.20 that for the range of GBW values that can be achieved in IBM 90nm process, the loop gain phase response does not vary by more than 1degree and hence the TIA filter is stable for these typical GBW values. Therefore stability is not critical in the implementation of the proposed TIA filter in this work. However, it must be noted that the single-pole amplifier macro-models used in this study of stability is a bit too simplistic. Real op-amps have higher frequency poles. But transient simulations done at transistor level provided in Section 5 show a stable system, thus the single-pole amplifiers used in macro-modeling offer a good approximation for stability.

## 3.5. Transistor Level Design Specifications and Considerations

Macro-modeling has been done in the previous section to determine the op-amp GBW limits that can be tolerated in the design. In this section transistor level design specifications and considerations will be outlined.

This work is implemented in IBM 90nm CMOS process with a supply voltage of 1.2V. The maximum output voltage swing requirement for the TIA filter is  $\pm 200$ mV single-ended. The target OOB blocker magnitude to be processed by this filter is  $\pm 4.5$ mA single-ended at 60MHz and higher frequencies. Table 3.2 shows the loading for OpampA, OpampB, and OpampC.

**Table 3.2 Amplifier Loading.**

| Amplifier | Loading                                 |

|-----------|-----------------------------------------|

| OpampA    | $R_f//C_f = 1K\Omega//7.2pF$            |

| OpampB    | $R1  C1  C_{IN} = 1.26K\Omega//55.63pF$ |

| OpampC    | C2 = 2.65 pF                            |

As determined before, OpampA GBW is 1GHz. OpampC GBW is also selected to be 1GHz. We notice from Fig. 3.14 and Fig. 3.15 that OpampB's capacitive load of 55.63pF is close to 8 times the capacitive loading of OpampA. To obtain similar GBW

values for OpampB with its capacitive load specification, significant amount of power needs to be dissipated. We therefore look at ways of reducing the loading on this amplifier.  $C_{IN}$  can be reduced to reduce the loading on OpampB. Fig. 3.21 shows the effect of  $C_{IN}$  on the filter response. A reduction of  $C_{IN}$  by half (from 52.98pF to 26.49pF) reduces the TIA OOB attenuation by 6dB. Reducing  $C_{IN}$  increases the filter bandwidth as well, but this can be compensated for easily by increasing the value of  $C_{f}$ .

Figure 3.21 Variation of Proposed TIA Filter OOB Attenuation with C<sub>IN</sub>.

To determine how low the value of  $C_{IN}$  can be set, one needs to look at two issues. Firstly, the loss in OOB attenuation that can be tolerated by the system and secondly the increase in voltage swing at the output of OpampB as a result of the reduction of  $C_{IN}$ .

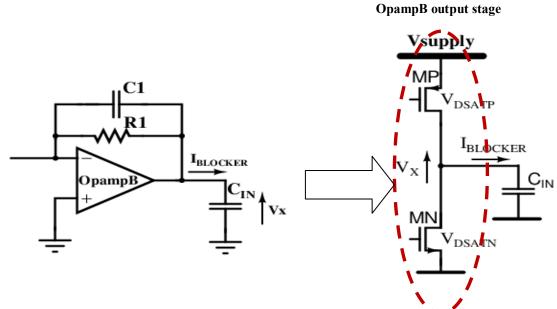

We note that a fullscale blocker current of 4.5mA needs to be tolerated at 60MHz. OpampB needs to be able to source/sink this blocker current through  $C_{\rm IN}$ . It can be seen

from Fig. 3.14 and Fig. 3.15 that while one terminal of  $C_{IN}$  is connected to the output of OpampB the other terminal of  $C_{IN}$  connects to the input of OpampA which is a virtual ground and therefore OpampB can considered as driving a  $\pm 4.5$ mA current through a shunt capacitor,  $C_{IN}$ . A single-ended representation of OpampB within the TIA is shown in Fig. 3.22.

Figure 3.22 Single-Ended Representation of Output Loading of OpampB.

The voltage swing at the output of OpampB when it sources/sinks a full-scale blocker current of 4.5mA at 60MHz can be calculated as:

$$V_{\chi} = \frac{I_{BLOCKER}}{\omega C_{IN}} \tag{3.23}$$

where  $\omega = 2\pi \, x \, 60 \, x 10^6 \, rad/s$  and  $I_{BLOCKER} = 4.5 mA$ . If  $C_{IN}$  is reduced by half to 26.49pF then  $V_x = \pm 460 mV$ . Since we have a supply voltage of 1.2V, this voltage swing leaves only 280mV across the drain-source of the output transistors. OpampB's output stage will consist of both NMOS and PMOS transistors, MN and MP as shown in Fig. 3.23. This effectively leaves a  $V_{DS}$  of 140mV across each device (MN/MP). Large devices

will need to be used to reduce  $V_{DSATN/P}$  to below 140mV to ensure the devices stay in saturation, and this will add more parasitic capacitance at the output node, a situation which is undesirable as we already have a large output capacitance which we are trying to reduce to decrease power consumption. Also a  $V_{DSATN/P}$  of less than 140mV simply does not provide enough margin across process and temperature. We desire to have a  $V_{DSATN/P}$  of at least 200mV to keep MN and MP in saturation across process and temperature during the processing of fullscale blocker currents of 4.5mA. Since we have a supply voltage of 1.2V,

$$V_{x,max} = V_{supply} - V_{DSATN} - |V_{DSATP}| = 1.2V - 200mV - 200mV = \pm 400mV$$

(3.24)

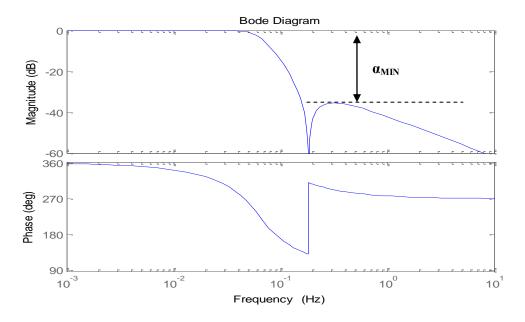

From (3.23), for  $V_{x,max} = \pm 400 mV$ ,  $C_{IN,MIN} \approx 30 pF$ . From here on,  $C_{IN} = 30 pF$  is used in the design and this gives 27dB of attenuation at the closest OOB blocker frequency of 60MHz and a plot of the corresponding filter magnitude response is shown in Fig. 3.23. This attenuation value of 27dB translates to  $\pm 400 mV$  differential output voltage swing for the TIA for a full-scale blocker current of 4.5mA. With  $C_{IN}$  of 30pF the loading on OpampB is approximately 5 times that of OpampA. A 500MHz GBW is targeted for OpampB to minimize its power consumption.

Table 3.3 provides a summary of the TIA filter specifications along with op amp specifications to be used for the transistor level design of the TIA filter. Fig. 3.24 shows the macro-model magnitude plot of the proposed TIA filter AC response obtained using these specifications and compares it to the single-pole TIA filter response.

Figure 3.23 Proposed TIA Filter  $\alpha_{MIN}$  Reduction for a Change of  $C_{IN}$  to 30pF.

Table 3.3 Summary of TIA Transistor Level Design Target Specifications and Op-amp Target Specifications.

| Parameter                           |                     | Value  | Unit               |  |  |

|-------------------------------------|---------------------|--------|--------------------|--|--|

| DC Transimpedance Gain              |                     | 60     | dB                 |  |  |

| Output Voltage Swing (single-ended) |                     | ±200   | mV                 |  |  |

| Closest OOB BI                      | Closest OOB Blocker |        | ±4.5mA at 60MHz    |  |  |

| Amplifier Target Specifications     |                     |        |                    |  |  |

| Amplifier                           | Gain                | GBW    | Loading            |  |  |

| OpampA                              | 50-60dB             | 1GHz   | 7.2pF  1KΩ         |  |  |

| OpampB                              | 50-60dB             | 1GHz   | 2.65pF             |  |  |

| OpampC                              | 50-60dB             | 500MHz | 30pF  2.65pF  1K Ω |  |  |

Figure 3.24 Targeted TIA Filter Magnitude Response.

## 3.5.1 Determination of Amplifier Slew-Rate Specifications

Slew-rate is an important parameter that needs to be considered for processing of high frequency signals by amplifiers. As the frequency of the input current signals to the TIA increases, the voltage at each op-amp output is slew-limited, leading to heavy distortion. For this reason, the op-amps used in the TIA must be designed such that they have enough slewing capability to accommodate the high frequency signals to be processed (60MHz and higher).

For a sinusoidal voltage signal given by:

$$V_O = \hat{V}_{MAX} sin\omega t \tag{3.25}$$

the minimum slew rate of the op amps required to process such a signal is equal to the maximum slope of (3.25) which is given by:

$$\frac{dV_O}{dt}|_{max} = \hat{V}_{MAX}\omega \tag{3.26}$$

As stated before, the full-scale blocker current expected at the TIA inputs is 4.5mA at 60MHz and beyond. The maximum output voltage swing of each of the op-amps occurs for this input blocker magnitude. In Fig. 3.25, the transimpedance gain from the TIA input to each op-amp output is plotted as a function of frequency, which shows a low-pass response. We consider the maximum OOB transimpedance gain at each op-amp output, and multiply this gain by 4.5mA to give the op-amp maximum output voltage swing,  $\hat{V}_{MAX}$ , for a full-scale blocker magnitude. Noting the frequency at which  $\hat{V}_{MAX}$  the maximum at the output of each op-amp occurs, the minimum slew-rate is calculated using (3.26).

Figure 3.25 Transimpedance Gain from the Proposed TIA Input to Each Op-amp Output.

Table 3.4 shows each amplifier slew-rate specification calculated from (3.26) and Table 3.5 provides a summary of the proposed TIA filter specifications along with op-amp specifications from macro-modeling to be used for the transistor level design of the proposed TIA filter.

**Table 3.4 Amplifier Slew-Rate Specifications.**

|        | Maximum output voltage<br>swing (for I <sub>BLOCKER</sub><br>=4.5mA) | Frequency at which maximum output voltage swing occurs | SR <sub>MIN</sub> |

|--------|----------------------------------------------------------------------|--------------------------------------------------------|-------------------|

| Units  | Mv                                                                   | MHz                                                    | V/µs              |

| OpampA | 200                                                                  | 85                                                     | ± 107             |

| OpampB | 400                                                                  | 60                                                     | ± 150             |

| OpampC | 250                                                                  | 60                                                     | ± 94              |

Table 3.5 Full Summary of TIA Transistor Level Design Specifications and Op-amp Target Specifications.

| Parameter                    |           | Value      | Unit                 | Unit            |                    |

|------------------------------|-----------|------------|----------------------|-----------------|--------------------|

| DC Transimpedance Gain       |           | 60         | dBΩ                  | dBΩ             |                    |

| Maximum Output Voltage swing |           | ±200 mV    |                      |                 |                    |

| (single-ended)               | )         |            |                      |                 |                    |

| Closest OOB Blocker          |           |            |                      | ±4.5mA at 60MHz |                    |

|                              | An        | nplifier T | arget Spec           | ifications      |                    |

| Amplifier                    | Gain (dB) | GB         | GBW (GHz) SR Loading |                 |                    |

|                              |           |            |                      | (V/µs)          |                    |

| OpampA                       | 50-60     | 1          |                      | 104             | 7.2pF  1KΩ         |

| OpampB                       | 50-60     | 1          |                      | 150             | 2.65pF             |

| OpampC                       | 50-60     | 0.5        |                      | 94              | 30pF  2.65pF  1K Ω |

#### 4. TRANSISTOR LEVEL DESIGN

Using the specifications obtained in the last section, a transistor level design of the proposed TIA filter is implemented in this section.

## 4.1 Amplifier Design

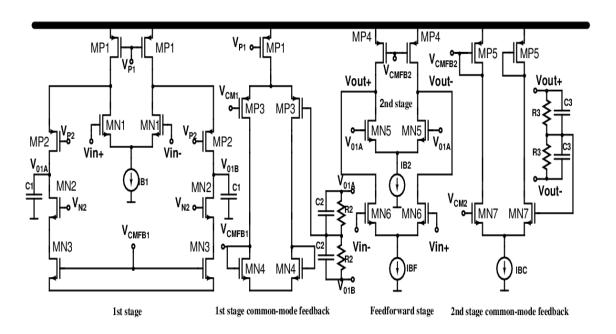

We recognize the need for high speed, high gain amplifiers in the design of the TIA as shown by macro-modeling in Table 3.5 from the previous section. Also, we recognize the high OOB blocker current which will need to be sourced/sunk by OpampB. Thus class AB biasing will be employed in the output stage of OpampB so as to maximize its power efficiency. OpampA and OpampC will be implemented with class A output stages since they are not required to provide large load currents.

In [10], a high gain, high bandwidth class A amplifier topology is presented that makes use of feedforward compensation for stability. This obviates the need for large Miller compensation capacitors. The trade-off is that while power consumption is increased area is reduced. OpampA and OpampC employ the architecture in [11] (trade off power for smaller area) while OpampB employs a conventional two-stage Class AB topology with Miller compensation (trades off area for reduced power), thus providing a balance of area and power consumption.

#### 4.1.1 High Gain, High Bandwidth Operational Amplifier - OpampA and OpampC

Table 3.5 in the previous section shows the gain and GBW target specifications for OpampA and OpampC. These op-amps are essentially high gain, high GBW amplifiers. In the design of a high gain and high GBW amplifier, the designer is presented with a fundamental design trade off. While high gain amplifiers require cascode (vertical approach) and/or multi-stage (cascade approach) architectures with long channel devices and low bias currents, high bandwidth amplifiers use single stage architectures, large bias currents and short channel devices. The signal swing in cascode amplifiers is constrained by the power supply voltage which is a problem for low voltage designs, and particularly in this work where a supply of 1.2V is used. In cascaded amplifiers which

are the alternate option for high gain, each amplifier stage contributes a pole and Miller compensation schemes are required for stability. These schemes however, are based on the fundamental principle of creating a dominant pole with 20dB/decade roll-off to the unity gain frequency, trading off bandwidth for stability.

To achieve high gain without sacrificing bandwidth, a two-stage op amp with a feedforward compensation scheme which does not use Miller capacitors is used [10]. This feedforward compensation technique is known as no-capacitor feedforward (NCFF) compensation. The technique uses the positive phase shift of left-half-plane (LHP) zeros caused by a feedforward path to cancel the negative phase shift of poles to achieve a good phase margin. A two-stage (cascade) design gives high, low-frequency gain and the feedforward stage makes the circuit faster. The amplifier bandwidth is not compromised due to the absence of the traditional pole-splitting effect of Miller compensation, resulting in a high-gain, wide-band (large GBW) amplifier with a fast step response. However, in practical circuits the pole-zero cancellation may not be exact and this leads to the formation of pole-zero pairs (doublets) which may degrade the settling time of the amplifier. In this work, the settling time requirement is not critical since we are dealing with a continuous-time filter.

Figure 4.1 Block Diagram of a Two-Stage Amplifier with No-Capacitor Feed-Forward (NCFF) Compensation.

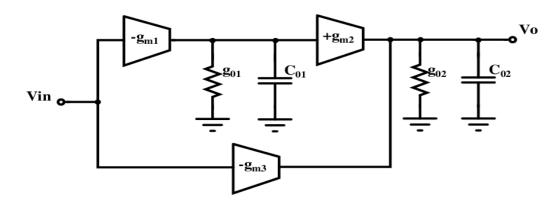

The block diagram of the feedforward compensation scheme is shown in Fig. 4.1.  $A_{VI}$ ,  $A_{V2}$  and  $A_{V3}$  define the dc gains of the first, second and feedforward stages of the amplifier. The first stage pole is located at  $\omega_{p1} = (go1/C_{01})$  and the second and feedforward stages have a common pole at  $\omega_{p2} = (go2/C_{02})$ . The overall amplifier voltage gain is given by:

$$A_{VT}(s) = \frac{-(A_{V1}A_{V2} + A_{V3})\left(1 + \frac{A_{V3}s}{(A_{V1}A_{V2} + A_{V3})\omega_{p1}}\right)}{\left(1 + \frac{s}{\omega_{p1}}\right)\left(1 + \frac{s}{\omega_{p2}}\right)}$$

(4.1)

which has two poles and a LHP zero created by the feedforward path. The DC gain is given by:

$$A_{VTO} = A_{V1}A_{V2} + A_{V3} (4.2)$$

and the dominant pole is located at  $\omega_{pl}$ . The location of the LHP zero is :

$$\omega_z = -\omega_{p1} \left( 1 + \frac{A_{V1} A_{V3}}{A_{v2}} \right) \cong -\frac{g_{m1}}{C_{01}} \frac{g_{m2}}{g_{m3}}$$

(4.3)

The second and feedforward stages are designed such that the negative phase shift due to  $\omega_{p2}$  is compensated by the positive phase shift of  $\omega_z$ .

#### 4.1.2 High Gain, High Bandwidth Operational Amplifier Design Procedure

The design procedure of the two-stage NCFF amplifier is discussed next. The design equations, which form the basis for the design procedure, are given as follows:

$$GBW = A_{VT}\omega_{p1} \tag{4.4}$$

$$A_{V1} = g_{m1} r_{01} (4.5)$$

$$A_{V2} = g_{m2} r_{02} (4.6)$$

$$A_{V3} = g_{m3}r_{02} (4.7)$$

$$\omega_{p1} = \frac{1}{r_{01}C_{01}} \tag{4.8}$$

$$\omega_{p2} = \frac{1}{r_{02}C_{02}} \tag{4.9}$$

$$\omega_Z = -\frac{g_{m1}}{C_{01}} \left( \frac{g_{m2}}{g_{m3}} \right) \tag{4.10}$$

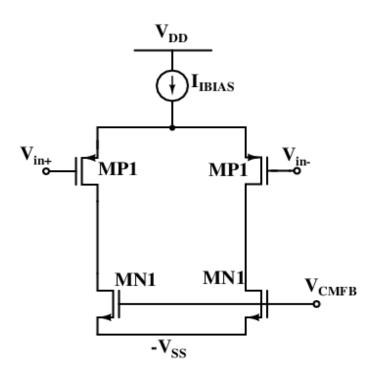

- i) The GBW specification for both OpampA and OpampC is 1GHz. A DC gain,  $A_{VT0}$  of 50-60dB is also targeted. The dominant pole frequency,  $\omega_{p1}$ , is determined from (4.3). Given  $\omega_{p1}$ ,  $C_{01}$  is determined using (4.7) based on the process technology values of  $r_{01}$  which is the effective parasitic resistance lumped at the output of the first stage.

- ii) The first gain stage is required to be a high gain stage. The gains of the first and second stages are apportioned as :  $A_{VI} = 40$ dB and  $A_{V2} = 10$ dB. From (4.5) and (4.6),  $g_{mI}$  and  $g_{m2}$  are determined.

- iii)  $C_{02}$  is equal to the output load capacitor  $C_{LOAD}$  ( $C_{LOAD}$  is 7.2pF for OpampA and 2.65pF for OpampC). With  $g_{m1}$ ,  $g_{m2}$ ,  $C_{01}$  and  $C_{02}$  known,  $g_{m3}$  is determined by equating the zero frequency,  $\omega_Z$  to the second stage pole frequency,  $\omega_{p2}$ . Thus (4.9) is equated to (4.10) to obtain  $g_{m3}$ .

- iv) For the amplifiers in this work, the load capacitor  $C_{LOAD}$  is larger than the capacitance at the output of the first stage,  $C_{0I}$ . Since the second stage is implemented as a differential pair with a tail current, it is the slew limiting stage of the amplifier. Hence from the slew rate specification of the amplifiers, the minimum bias current of the second stage is determined as follows:

$$I_{B2} \geq g_{m2} \times C_{LOAD} \tag{4.11}$$

where  $I_{B2}$  is the tail current source of the second stage input differential pair.

#### 4.1.3 High Gain, High GBW Operational Amplifier Circuit Implementation

The two-stage amplifier using the NCFF compensation has the following design considerations:

i) The second and feedforward stages should not have any non-dominant pole before the overall unity gain frequency of the amplifier [10].

ii) The pole–zero cancellation should occur at high frequencies for best settlingtime performance [10].