## COMMUNICATION RELIABILITY IN NETWORK ON CHIP DESIGNS

A Thesis

by

## REESHAV KUMAR

### Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

August 2011

Major Subject: Electrical Engineering

## COMMUNICATION RELIABILITY IN NETWORK ON CHIP DESIGNS

A Thesis

${\rm by}$

## REESHAV KUMAR

### Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

Approved by:

| Chair of Committee, | Seong Gwan Choi       |

|---------------------|-----------------------|

| Committee Members,  | Jiang Hu              |

|                     | Jose Silva Martinez   |

|                     | Eun Jung Kim          |

| Head of Department, | Costas N. Georghiades |

August 2011

Major Subject: Electrical Engineering

#### ABSTRACT

Communication Reliability in Network on Chip Designs. (August 2011)

Reeshav Kumar, B.E., Birla Institute of Technology & Science, India

Chair of Advisory Committee: Dr. Seong Gwan Choi

The performance of low latency Network on Chip (NoC) architectures, which incorporate fast bypass paths to reduce communication latency, is limited by crosstalk induced skewing of signal transitions on link wires. As a result of crosstalk interactions between wires, signal transitions belonging to the same flit or bit vector arrive at the destination at different times and are likely to violate setup and hold time constraints for the design. This thesis proposes a two-step technique: TransSync- RecSync, to dynamically eliminate packet errors resulting from inter-bit-line transition skew. The proposed approach adds minimally to router complexity and involves no wire overhead. The actual throughput of NoC designs with asynchronous bypass designs is evaluated and the benefits of augmenting such schemes with the proposed design are studied. The TransSync, TransSync-2-lines and RecSync schemes described here are found to improve the average communication latency by 26%, 20% and 38% respectively in a 7X7 mesh NoC with asynchronous bypass channel.

This work also evaluates the bit-error ratio (BER) performance of several existing crosstalk avoidance and error correcting schemes and compares them to that of the proposed schemes. Both TransSync and RecSync scheme are dynamic in nature and can be switched on and off on-the-fly. The proposed schemes can therefore be employed to impart unequal error protection (UEP) against intra-flit skewing on NoC links. In the UEP, a larger fraction of the energy budget is spent in providing protection to those parts of the data being transmitted on the link which have a higher priority, while expending smaller effort in protecting relatively less important parts of the data. This allows us to achieve the prescribed level of performance with lower levels of power. The benefits of the presented technique are illustrated using an H.264 video decoder system-on-chip (SoC) employing NoC architecture. We show that for Akyio test streams transmitted over 3mm long link wires, the power consumption can be reduced by as much as 20% at the cost of an acceptable degradation in average peak signal to noise ratio (PSNR) with UEP. To My Parents

#### ACKNOWLEDGMENTS

It is a pleasure to thank the many people who made this thesis possible.

I owe my deepest gratitude to my advisor, Dr. Seong Gwan Choi, for his support and direction over the last two years of my master's study. Without his continued encouragement and sound advice, this work would not have been possible.

I would also like to thank Drs. Hu, Silva and Kim for serving on my committee and for being excellent teachers.

I am indebted to many of my student colleagues for providing a stimulating and fun environment in which I had the opportunity to learn and grow. I am especially grateful to Yoon Seok Yang for teaching me the basics of Networks on Chip. I really enjoyed working with him.

A number of colleagues and friends have made my stay in College Station memorable. I would like to thank Ayush, Ravindra, Akshay, Anurag, Sapan, Dibakar and Hrishikesh for their constant support and affection.

Lastly, and most importantly, I wouldn't have been able to compile this work without the unconditional love and support of my family.

# TABLE OF CONTENTS

## CHAPTER

| Ι   | INTRODUCTION                                                                                        |

|-----|-----------------------------------------------------------------------------------------------------|

| II  | INTRA FLIT SKEW                                                                                     |

|     | A. The Problem of Intra-Flit Skew                                                                   |

|     | B. Crosstalk Coupling on Link Wires                                                                 |

|     | C. Combating Crosstalk                                                                              |

|     | 1. Physical Techniques to Combat Crosstalk 13                                                       |

|     | 2. Crosstalk Avoidance Codes                                                                        |

|     | 3. Variable Cycle Transmission and Re-transmission 14                                               |

|     | 4. Error Correcting Codes                                                                           |

|     | 5. TransSync $\ldots$ 15                                                                            |

|     | 6. TransSync 2 Lines                                                                                |

|     | 7. RecSync $\ldots \ldots 20$ |

|     | D. Results and Discussion                                                                           |

|     | 1. Simulation Environment                                                                           |

|     | 2. Performance Analysis                                                                             |

|     | 3. Overhead Analysis                                                                                |

|     | 4. System Level Results                                                                             |

| III | INTERCONNECT BER IN THE PRESENCE OF CROSSTALK                                                       |

|     | AND VARIATIONS                                                                                      |

|     | A. Sources of Variation                                                                             |

|     | 1. Device Variations $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 33$                          |

|     | a. Film Thickness                                                                                   |

|     | b. Lateral Device Dimensions                                                                        |

|     | c. Doping $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 34$                       |

|     | 2. Interconnect Variations                                                                          |

|     | a. Line Width (W) and Space (S) $\ldots \ldots \ldots 35$                                           |

|     | b. Metal Thickness $(T)$                                                                            |

|     | c. ILD Thickness (H) $\ldots \ldots \ldots \ldots \ldots 36$                                        |

|     | d. Contact Via Size and Resistance                                                                  |

|     | e. Metal Resistivity                                                                                |

|     | 3. Environmental Variations                                                                         |

|     | a. Supply Voltage                                                                                   |

| Page |

|------|

|------|

|          | b. Temperature                                  | 37 |

|----------|-------------------------------------------------|----|

|          | B. BER Analysis                                 | 37 |

|          | 1. Crosstalk Failure Mechanism                  | 39 |

|          | a. Timing Failure                               | 39 |

|          | b. Functional Failure                           | 40 |

|          | 2. Average BER                                  | 41 |

|          | C. Results and Discussion                       | 42 |

|          | 1. Simulation Environment                       | 42 |

|          | 2. Schemes Studied                              | 43 |

|          | 3. Results                                      | 45 |

| IV       | UNEQUAL ERROR PROTECTION (UEP) ON LINK          | 49 |

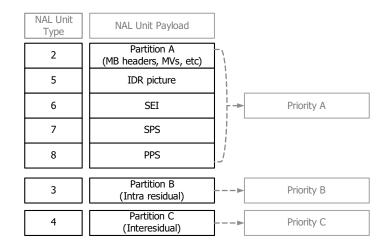

|          | A. UEP for H.264/AVC Video Streams on NoC Links | 50 |

|          | B. Results and Discussion                       | 52 |

|          | 1. Performance Metric                           | 52 |

|          | 2. Simulation Environment                       | 53 |

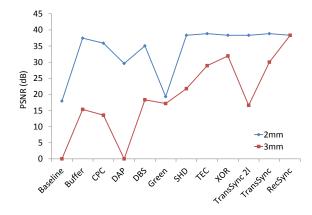

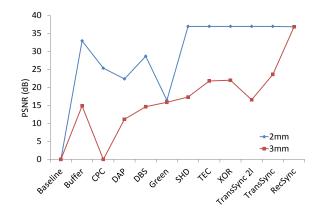

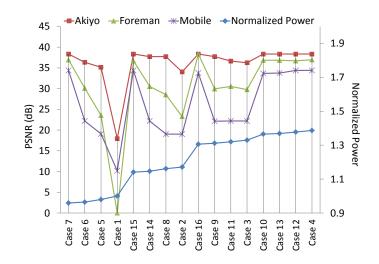

|          | 3. PSNR and Merit                               | 54 |

|          | 4. UEP Results                                  | 57 |

| V        | CONCLUSION                                      | 61 |

| REFERENC | CES                                             | 63 |

| VITA     |                                                 | 74 |

# LIST OF FIGURES

| FIGURI | E                                                                                                                                                   | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1      | ITRS 2009 projections for future SOC networking driver MC/AE platform performance.                                                                  | 2    |

| 2      | GALS topology with bypassing of flits on hops between source<br>and destination.                                                                    | 7    |

| 3      | The problem of intra-flit skew on links                                                                                                             | 8    |

| 4      | Plot of transmission delay and intra-flit skew vs. wire length for<br>interconnects that have repeaters driving optimal length wire segments.       | 9    |

| 5      | Plot of intra-flit skew vs. wire length for with different driving repeater strengths when repeaters are present every 1mm length of wire segments. | 10   |

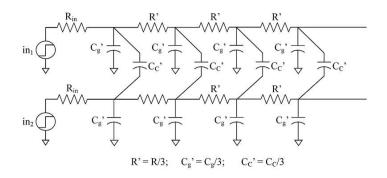

| 6      | Wire model for flits that are bypassed asynchronously over inter-<br>vening hops                                                                    | 11   |

| 7      | Timing diagram showing the operation of TransSync module                                                                                            | 16   |

| 8      | Circuit schematic of TransSync scheme.                                                                                                              | 17   |

| 9      | Circuit schematic of TransSync-2-lines scheme.                                                                                                      | 19   |

| 10     | Timing diagram for the operation of RecSync scheme.                                                                                                 | 20   |

| 11     | Circuit schematic of RecSync logic.                                                                                                                 | 21   |

| 12     | Signal diagram explaining the working of RecSync logic                                                                                              | 22   |

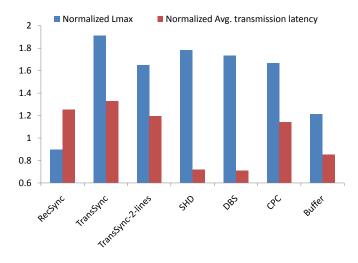

| 13     | Comparison of $L_{max}$ and transmission delay for the different schemes studied.                                                                   | 25   |

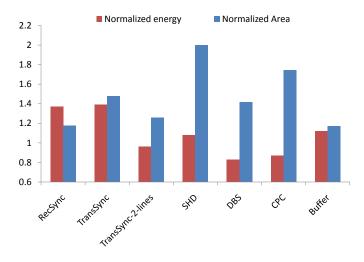

| 14     | Comparison of area and energy overhead of the different schemes studied.                                                                            | 26   |

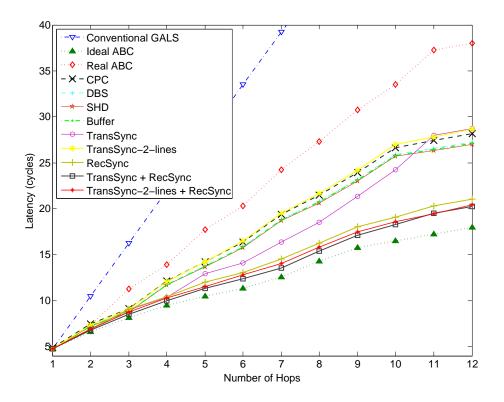

| 15     | Plot of transmission latency vs. number of hops traveled by flits for different schemes                                                             | 28   |

## FIGURE

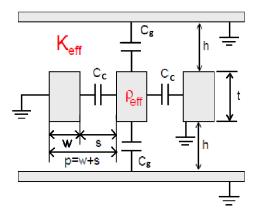

| 16 | Interconnect structure                                                                                                       | 34 |

|----|------------------------------------------------------------------------------------------------------------------------------|----|

| 17 | Three segment wire model for crosstalk coupling                                                                              | 35 |

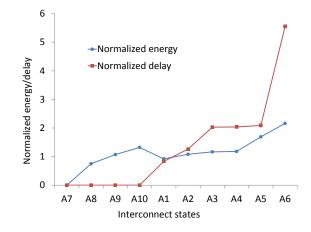

| 18 | Energy and delay for different states for 2mm long interconnect wires.                                                       | 39 |

| 19 | Sensitivity of delay and glitch amplitude to individual parameters to on repeater inserted links.                            | 45 |

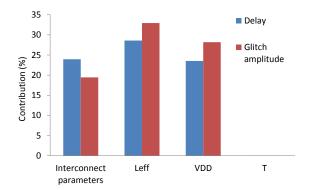

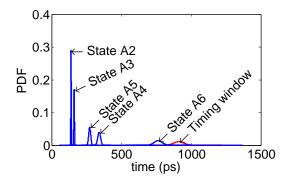

| 20 | Probability distribution function (PDF) of timing window and delay of different delay states for 1mm long interconnect wires | 46 |

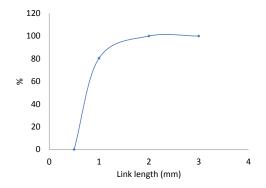

| 21 | Contribution of timing errors to BER vs. link length                                                                         | 46 |

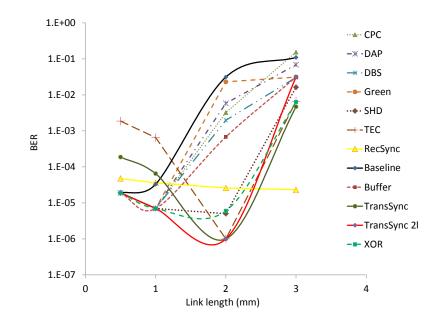

| 22 | BER vs. link length for different design                                                                                     | 47 |

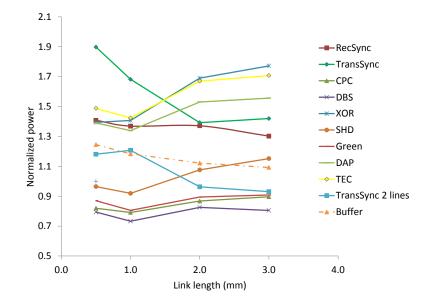

| 23 | Power overhead for different schemes                                                                                         | 48 |

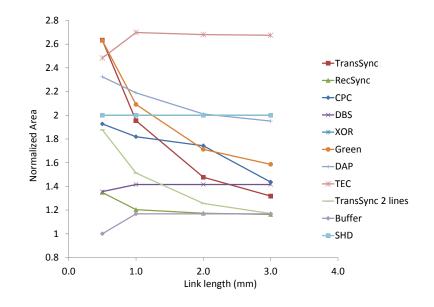

| 24 | Area overhead for different schemes                                                                                          | 48 |

| 25 | H.264 data partition and prioritization                                                                                      | 51 |

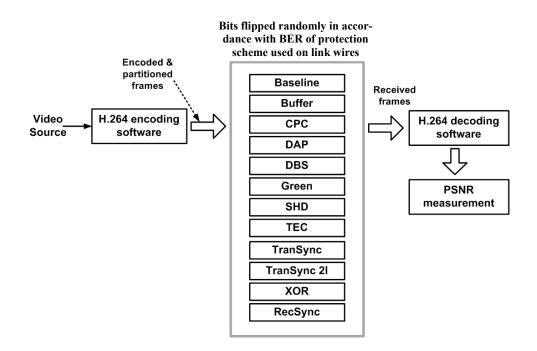

| 26 | Simulation setup for evaluating the quality of reconstructed frames with different protection schemes on links.              | 53 |

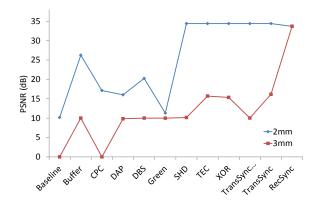

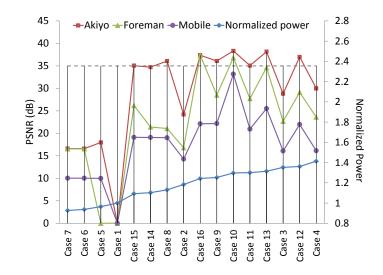

| 27 | PSNR results for Akiyo test streams with different protection schemes on 2mm and 3mm long links.                             | 54 |

| 28 | PSNR results for Foreman test streams with different protection schemes on 2mm and 3mm long links.                           | 54 |

| 29 | PSNR results for Mobile test streams with different protection schemes on 2mm and 3mm long links.                            | 55 |

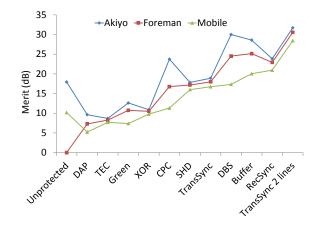

| 30 | Merit of different protection schemes on 2mm long link wires. $\ldots$                                                       | 56 |

| 31 | Merit of different protection schemes on 3mm long link wires                                                                 | 57 |

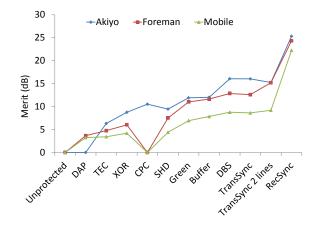

| 32 | Results for 2mm long link wires for the UEP schemes analyzed                                                                 | 59 |

| 33 | Results for 3mm long link wires for the UEP schemes analyzed                                                                 | 60 |

Page

# LIST OF TABLES

| TABLE |                                                                                                                                                                    | Page |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Ι     | Interconnect states                                                                                                                                                | 12   |

| II    | Output of TransSync Module for different crosstalk interaction cases.                                                                                              | 18   |

| III   | Output of TransSync-2-lines logic.                                                                                                                                 | 19   |

| IV    | Interconnect parameters used in the simulations.                                                                                                                   | 30   |

| V     | Number of hops that a flit can travel without requiring syn-<br>chronization, latency overhead and latency formula for different<br>schemes for 'n' hops of travel | 31   |

| VI    | Interconnect states                                                                                                                                                | 38   |

| VII   | Nominal values and variations for circuit parameters                                                                                                               | 42   |

| VIII  | CCD analysis points.                                                                                                                                               | 43   |

| IX    | Distribution of priority parts in test video streams                                                                                                               | 57   |

| Х     | Protection schemes employed on link with data partitions for dif-<br>ferent UEP configurations studied.                                                            | 58   |

#### CHAPTER I

#### INTRODUCTION

Advances in technology have nurtured growth in the performance of integrated circuits in keeping with the predictions of Moore's law over the last three decades. Increase in integration density has for long sustained increased microprocessor performance through higher clock rates and micro-architectural innovations. However, the dramatic increase in power density with device scaling in deep-Deep Sub-micron (DSM) technologies has made it infeasible to scale operating frequencies any more. The fundamental limitations to power dissipation in circuits, diminishing returns from the super-scalar execution model exploiting instruction level parallelism, increasing gate density and cost of wires in advanced integrated circuit technologies require that we look for new ways to harness their capabilities effectively.

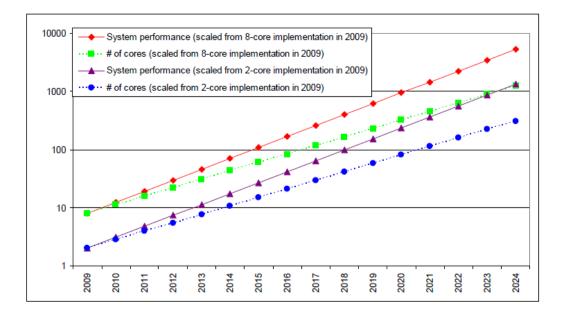

Many-core and multi-core micro-architectures constructed from several simpler processing elements (PEs) have been touted as the way forward to meet the ever increasing performance needs with manageable power levels and affordable costs. As a result, the development of complex Multi-Processor Systems-on-Chip (MPSoCs) and Chip-Multi-Porcessors (CMPs) has been receiving increasingly more and more attention lately [1], [2], [3]. Fig. 1 shows the International Technology Road-map for Silicon (ITRS) 2009 [4] projections for the anticipated growth over time in the performance and number of cores for the System on Chip (SoC) Networking Driver targeting the mid-range switching/routing workload segment of the embedded networking space, with 30W power envelope. As per these projections, the number of cores is expected to increases by  $1.4 \times$  every year for a constant die area. This implies

The journal model is IEEE Transactions on Automatic Control.

Fig. 1. ITRS 2009 projections for future SOC networking driver MC/AE platform performance.

that the performance of future 22nm system (with 80+ cores) would be >  $20\times$  times the performance of an 8-core implementation at 45nm in 2009.

Present day CMPs and MPSoCs encompass several intellectual property (IP) blocks and customized processing units (PUs). Traditional multi-drop buses do not scale sufficiently to meet the bandwidth demands of such many-core systems [5]. Networks on chip (NoC) designs offer large communication bandwidth and are therefore quickly substituting traditional bus based and ad-hoc on-chip interconnect implementations to become the design paradigm for CMPs/SoCs/MPSoCs [6] [7] [8]. NoCs are comprised of several nodes and each node can have one or more processing elements (PEs). These nodes, which may be placed several milli-metres apart on the die, are connected together by regular point to point links. Each node has a routing element that enables it to communicate with other nodes. The NoC infrastructure thus comprises physical layer, the data link layer and the network layer of the OSI protocol stack where the router plays the key role in facilitating on-chip communication be-

tween nodes [5, 9, 10]. The regular structure of NoCs makes them energy efficient and greatly simplifies the design of modular and reliable high performance systems. A comparison of the pros and cons of several popular NoC topologies can be found in [11][12].

In DSM technology nodes, with the reduced voltage swing, increasing clock frequencies and large propagation delays; signal transitions on interconnect wires have become increasingly susceptible to crosstalk induced performance degradation. Thus the integrity of signal transmitted on not just global wires but also intermediate and local wires also needs careful consideration. This is especially true of NoC designs employing globally asynchronous locally synchronous (GALS) clocking [13, 14, 15, 16], where network traversal latency is very high since flits might need to be synchronized at every hop between the source and the destination.

Several recent works have dwelt on improving network performance for GALS NoC designs by allowing flits to be asynchronously bypassed at intervening hops between the source and destination by incorporating some specialized clock routing [17, 18, 19, 20]. The presence of long distance traffic in 2-D mesh networks where a sizable fraction of the total traffic travels distances well over the mean topology hop distance for TRIPS [22], RAW [23] and cache coherent CMP applications [24] was established in [21].

In NoC designs employing fast bypass paths, sizable fractions of the traffic would therefore move over several hops, often even the entire network dimension, on these bypass paths without undergoing synchronization at any of the intervening hops. There may be considerable amounts of skew between the bits of the same flit or bitvector asynchronously bypassed over several hops in such low latency NoC designs. We refer to the problem of uncertainty in the delay experienced by different signal transitions of a bit vector on link wires and the consequent separation in their arrival times at the receiving node as the problem of "Intra-flit skew". Since GALS designs typically employ source synchronous communication strategies [25, 26, 27, 28] at clock boundaries, intra-flit skew can lead to timing and functional failures from the violation of setup and hold constraints, causing a large fraction of the received packets to be erroneous.

Signal errors that contribute to intra-flit skew can be classified into permanent, intermittent or temporary depending on their duration. Immutable malfunctions caused by permanent physical changes like manufacturing defects, aging or electromigration lead to permanent errors. Long-duration errors occurring in the same position, that are not permanent errors, are known as intermittent errors. Transient or soft errors result in short duration signal integrity loss and reliability degradation. Soft errors on link wires are caused by crosstalk coupling, external radiation, power supply fluctuations, process variations and temperature variations, electromagnetic interference and combinations of these sources. The aforementioned sources can affect signal integrity by inducing voltage glitches in the system and by causing transition delay uncertainty. Voltage glitches that exceed the noise margin and last for sufficient duration can lead to logical errors. Delay uncertainty is the uncertainty in the timing of a signal transition arrival at a node and leads to reduction in the frequency at which the system can operate to guarantee error-free operation.

Although it is not be possible to quantify the exact contribution of each of the above mentioned sources to signal integrity loss due to soft errors, crosstalk noise may be accredited as the most critical factor affecting reliability of on-chip interconnect in large NoC/SoC designs. Fault tolerance schemes like hardware, time and information redundancy which have been traditionally employed to mitigate permanent and intermittent error are often inadequate to deal with crosstalk induced soft errors. This work focuses on the impact of crosstalk on intra-flit skew and presents novel solutions, with minimal energy and area overhead, to improve signal integrity on link for NoC designs employing long bypass paths for low latency communication. The proposed "TransSync" scheme tries to preemptively minimize intra-flit skew by intelligently skewing signal transitions at the transmitting node on-the-fly so that they become aligned at the receiving node as a result of intra-flit skew on links. The "RecSync" scheme tries to eliminate the accrued intra-flit on link wires at the receiving node by forcing all the transitions to become aligned before they are relayed to the receiving buffers. The proposed schemes also provide the designers the liberty of dynamically implementing varying levels of protection against intra-flit skew induced errors on links for different priority data. Considerable amount of energy saving can be achieved at the cost of relatively small loss of system performance by using unequal error protection (UEP) where relatively lesser energy in expended in protecting less important portion of data.

The organization of the remainder of this thesis is as follows: Chapter II formulates the problem of intra-flit skew and explores the benefits of employing TransSync and RecSync schemes on low latency NoC designs. Chapter III presents a formal analysis of the bit error ratio (BER) performance of TransSync-RecSync and compares their performance to that of a host of crosstalk prevention and error correcting schemes. Chapter IV introduces the idea of unequal error protection (UEP) on link against crosstalk induced errors and evaluates the merit of UEP with TransSync and RecSync on a MPSoC video decoder design using a suite of H.264/AVC test video streams.

#### CHAPTER II

#### INTRA FLIT SKEW

We look at the problem of intra-flit skewing due to crosstalk on link wires and evaluate the solutions to this problem in this chapter. The performance of many-core NoCs, which have abundant processing resources, is limited by the latency of communication between PEs. Globally asynchronous locally synchronous (GALS) clocking strategy [13, 14, 15, 16] was proposed as a solution to the problem of ensuring the synchronization of the entire design with a single clock source which limits the development of large many core designs [6]. In a GALS NoC, each node may be running off a different clock source and therefore data flits need to be synchronized to the local clock domain of each intervening hop on their journey between the source and destination nodes. The latency overhead of synchronizations at intervening hops in inter-tile communication can account for a major portion of the communication latency exacerbating larger NoC designs' already substantial packet latency issues [29]. Thus communication latency seriously limits the overall network performance when more and more applications today are communication limited.

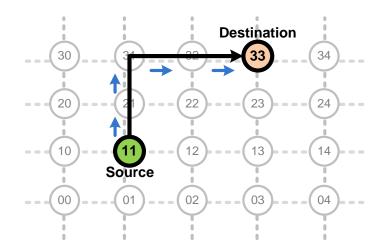

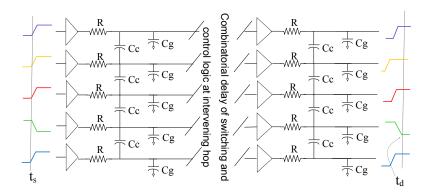

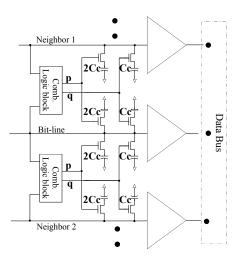

Several previous works have tried to reduces communication latency in NoCs by reducing the global hop count( [30] [31] [32] [33]). A popular approach that has been explored by recent NoC research tries to minimize communication latency by incorporating fast paths employing asynchronous bypass between nodes thereby reducing the per hop latency for traffic traveling on these fast paths. Fig. 2 shows an instance in a NoC with asynchronous bypass path where a flit bypasses four hops on its way from source to destination.

A regular k-ary n-cube interconnection network augmented with express channels that allow non-local messages to bypass nodes thereby resulting in network latency

Fig. 2. GALS topology with bypassing of flits on hops between source and destination.

and throughput improvement was proposed by Dally in [17]. Ogras et al. explore the possibility improving network latency and throughput by maximizing the value of the critical traffic workload in regular 2-D mesh NoCs via insertion of applicationspecific long-range links [18]. Krishna et al. in [19] propose express virtual channels (EVCs), which allow packets to virtually bypass intermediate routers along their path in a completely non-speculative fashion, thereby lowering the per-hop delay. Jain et al. propose an asynchronous bypass channel (ABC) router deign for GALS NoC that targets both hop count and per-hop latency to reduce network latency [20]. Improved latency and throughput figures in the above mentioned designs rely on flits being bypassed across intervening hops without suffering any synchronization latency.

#### A. The Problem of Intra-Flit Skew

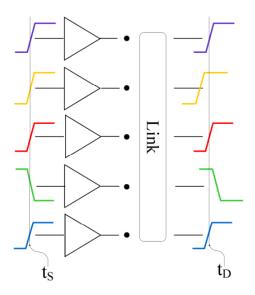

Not all the signal transitions of the bit vector being transmitted on the link arrive at the destination at the same time. As shown in Fig. 3, all the signal transitions are perfectly aligned when they are transmitted by the source node at time  $t_s$ but different bits on the link experience different amounts of skew to arrive at the

Fig. 3. The problem of intra-flit skew on links.

destination out of synchronization. We refer to this phenomenon as "intra-flit skew". The skewing of data transitions on the bus has to be accounted for in any source synchronous communication scheme with asynchronous bypass that assumes that the signals transitions for bits belonging to the same flit are always synchronized. The problem of intra-flit skew necessitates periodic synchronization of the bit vector on link thereby limiting the expected improvement in latency and throughput from asynchronous bypass in GALS NoCs.

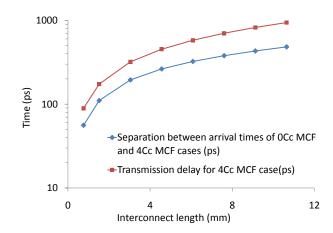

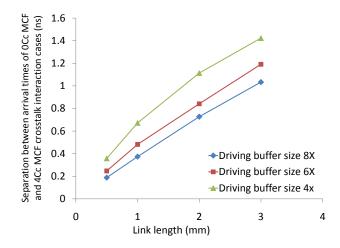

Fig. 4 and Fig. 5 plot the variations of intra-flit skew ( $\delta$ ) versus the length of link for interconnect wires that have been optimized for minimum propagation delay by insertion of optimal sized repeaters and for different driving repeater sizes respectively. From Fig. 4 and Fig. 5, it is evident that the value of maximum skew increases with wire length even with insertion of repeater between optimal length interconnects. The situation is much worse for NoCs since it is not feasible to insert repeaters between optimal length bus wires. In NoCs designs employing special clocking schemes and

Fig. 4. Plot of transmission delay and intra-flit skew vs. wire length for interconnects that have repeaters driving optimal length wire segments.

asynchronous bypass, where the separation between PEs is of the order of millimeters, the skew accumulating between bit lines for flits traveling several hops may be a considerable fraction of the cycle time itself. . Driving buffers may be inserted along the length of wire segments between nodes. As shown in Fig. 6, all the bits in a flit are transmitted by the source at the same time  $t_s$ . Different bits suffer different traversal delay on bus and arrive at the destination at different time. The flit becomes available at the destination at time  $t_d$  only after the last bit arrives. The transition skew and transmission delay accruing on wire segments between the PEs are further aggravated by combination delay incurred by the control and switching logic (multiplexers, etc) on each of the intervening hops, as shown in Fig. 6, which may be different for different bits of a flit. To prevent packet errors, flits which are supposed to be bypassed asynchronously at intervening hops would therefore need synchronization every time they travel a certain number of hops to eliminate the accumulated transition skew. Thus in practice, it is not possible to realize the figures of average network traversal latency expected with asynchronous bypass channels in NoC. Even with synchronization at regular interval, it might not be possible to

Fig. 5. Plot of intra-flit skew vs. wire length for with different driving repeater strengths when repeaters are present every 1mm length of wire segments.

completely eliminate packet errors resulting from skew between bit-lines. Some factors contributing to intra-flit skew on link wires are: crosstalk coupling between link wires, design irregularities/constraints in physical routing implementation, timing variations at switching and multiplexing logic, variations in process parameters, power supply fluctuation and noise, temperature variations, physical changes like electromigration and external radiation. While it may be difficult to quantify the exact contribution of each factor listed above to intra-flit skew, crosstalk coupling between adjacent wires can safely be attributed as the most significant contributor. Different bit transitions on links suffer different crosstalk interaction and therefore experience variable traversal delay to arrive at the destination at different times. We therefore intend to focus on crosstalk to deal with the problem of intra-flit skew on link for NoCs with long asynchronous bypass paths in this work.

Fig. 6. Wire model for flits that are bypassed asynchronously over intervening hops.

#### B. Crosstalk Coupling on Link Wires

Crosstalk noise is the result of unavoidable coupling capacitance between adjacent wires. With technology scaling, wire width and spacing scale at a higher rate than wire thickness to achieve higher integration. Increased aspect ratios in DSM have led to increased coupling capacitance between neighboring bit-lines such that coupling capacitances account for more than half of the total wire capacitance itself. Crosstalk coupling effects can induce significant voltage glitches on a victim line potentially inducing logic errors. Crosstalk-induced delay uncertainty is caused by the dependence of coupling capacitance on signal switching patterns. Besides engendering degradation in the reliability of on-chip interconnect, crosstalk coupling also leads to increased link power consumption. A first order coupling capacitance model shown in Fig. 6 takes into account the switching activity of the line and only its immediate adjacent neighboring lines has traditionally been used to model the crosstalk between bit-lines. In this model, the effective capacitance of a switching line varies with the switching activity of the neighboring wires in accordance with the Miller coupling factor (MCF). Based on this understanding, interconnects can be broadly classified into nine distinct states states [34] that differ from each other primarily in terms of

| Switching                                                                                                                                                                                           | Total wire    | Occurrence     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|

| Pattern                                                                                                                                                                                             | Capaciatnce   | Probability    |

| $(\uparrow,\uparrow,\uparrow),(\downarrow,\downarrow,\downarrow)$                                                                                                                                   | $0C_C + C_g$  | $\frac{1}{32}$ |

| $(-,\uparrow,\uparrow),(-,\downarrow,\downarrow), \\ (\uparrow,\uparrow,-),(\downarrow,\downarrow,-)$                                                                                               | $1C_C + C_g$  | $\frac{1}{8}$  |

| $ \begin{array}{c} (\uparrow,\downarrow,\downarrow),(\downarrow,\uparrow,\uparrow),(\uparrow,\uparrow,\downarrow),\\ (\downarrow,\downarrow,\uparrow),(-,\uparrow,-),(-,\downarrow,-) \end{array} $ | $2C_C + C_g$  | $\frac{3}{16}$ |

| $(\downarrow,\uparrow,-),(\uparrow,\downarrow,-),\\(-,\uparrow,\downarrow),(-,\downarrow,\uparrow)$                                                                                                 | $3C_C + C_g$  | $\frac{1}{8}$  |

| $(\uparrow,\downarrow,\uparrow),(\downarrow,\uparrow,\downarrow)$                                                                                                                                   | $4C_C + C_g$  | $\frac{1}{32}$ |

| (-, -, -)                                                                                                                                                                                           |               | $\frac{1}{16}$ |

| $(\uparrow,-,\downarrow),(\downarrow,-,\uparrow)$                                                                                                                                                   | $0C_C + 0C_g$ | $\frac{1}{8}$  |

| $(-,-,\uparrow),(-,-,\downarrow), ((\uparrow,-,-),(\downarrow,-,-))$                                                                                                                                | $1C_C + 0C_g$ | $\frac{1}{4}$  |

| $(\uparrow,-,\uparrow),(\downarrow,-,\downarrow)$                                                                                                                                                   | $2C_C + 0C_g$ | $\frac{1}{16}$ |

Table I. Interconnect states.

the total line capacitance that the signal transition on a wire experiences depending on the switching activity on the wire and its nearest neighbors. Different cross-talk interactions between the wires of an on-chip bus are listed in Table I. In this table  $\uparrow, \downarrow$  and- stand for  $0\rightarrow 1, 1\rightarrow 0$  and no transition on a wire respectively. The total line capacitance seen by a signal transition has two components:  $C_g$  which is due to the capacitance seen by the line with respect to ground and a second component  $C_C$ due to crosstalk coupling between with adjacent the wires, the magnitude of which varies in accordance with MCF. Depending on the switching behavior of a wire and its neighbors, the effective capacitance of a wire can change from  $C_g$  to  $C_g + 4C_C$ . The minimum coupling interaction (MCF = 0) is experienced by lines whose neighbors transmit transitions in the same direction with respect to the line transitions and the maximum crosstalk coupling (MCF = 4) is suffered by lines whose neighbors transmit transitions in the opposite direction. Therefore signal transitions which encounter  $4C_C$  MCF coupling experience largest wire delay while those that encounter  $0C_C$  MCF coupling suffer the smallest wire delay.

#### C. Combating Crosstalk

#### 1. Physical Techniques to Combat Crosstalk

Several techniques have been proposed to minimize or eliminate the impact of capacitive coupling on bus lines. [35, 36] present net ordering, wire segment reordering and buffer insertion techniques for the physical design of interconnect for noise and delay optimization. Hirose et al. in [37] propose intentional skewing of signal transition timing on adjacent wires of repeater inserted bus to minimize crosstalk noise. Such static skewing of signal transition on adjacent wires of a wide link can significantly increase packet transmission latency. Shielding of the wires and increasing the interwire spacing (DBS) are other options explored for reducing the impact of crosstalk by Arunachalam et al. in [38]. Active shielding method proposed by Kaul et al. employs two shielding wires on both sides of the target wire, and keeps the same transition direction as the target wire for fast propagation [39]. These layout level techniques incur a significant increase in link area which is unacceptable considering the dearth and outlay of routing resources in higher metal layers.

#### 2. Crosstalk Avoidance Codes

Victor et al. in [40] present the theory behind crosstalk-prevention codes (CPC) and the methods for generating these codewords. Pande et al. in [41] propose the use of crosstalk avoidance codes(CAC) and modification in the structure of the data packets to incorporate CAC schemes in the NoC data stream and reduction in the number of coding-decoding operations to address both crosstalk and energy dissipation in networks-on-chip (NoC). [42] presents the design of a reliable NoC which maps data into selected crosstalk avoidance code (SCAC) for message transmission and preserves state and controlling registers of routers with triple modular redundancy (TMR) to avoid large crosstalk-induced delay. These encoding schemes, however, require additional wires and circuitry to implement CODECs, thereby incurring sizable area overhead and increase routing requirement.

#### 3. Variable Cycle Transmission and Re-transmission

Lin et al. in [43] propose a crosstalk aware interconnect technique for on-chip processor buses where data is transmitted at different rates depending on data pattern classification and signaling is used on the bus to indicate start and end of transmission. A similar approach put forth by Sankaran et al. [44] detects worst case crosstalk interaction and postpones transmission of current data by one cycle by resetting the wires to ensure that the impact of signal transition pattern on coupling capacitance is always 2Cc or less. These designs employing variable cycle transmission and retransmissions may not be feasible for typical NoC architectures. Also, these approaches aim only at minimizing worst case coupling interactions and not so much at maximizing the time for which data is stable every cycle.

#### 4. Error Correcting Codes

Error correction schemes like Hamming and Cyclic Redundancy Check (CRC) have been traditionally employed to deal with soft-errors introduced into the system by the communication channel between the source and the destination. While the overhead involved in such traditional schemes is easily amortized in wireless communication architecture, they are too expensive to be adopted into the NoC framework. Error correction codes are able to detect and correct the error bits based on an information theoretic model [51]. Unified framework of coding schemes for system on-chip with crosstalk avoidance codes (CAC) and simple error control codes (ECC) to solve delay, power, and reliability problems jointly were proposed in [46], [47], [48]. A joint error correction coding scheme using duplication with parity (DAP) and triplication error correction (TEC) with Green bus coding for crosstalk avoidances to guard against crosstalk induced errors is presented in [49] and [50] respectively. Ying et al. in [42] present the design of a reliable NoC which maps data into selected crosstalk avoidance code (SCAC) for message transmission while preserving state and controlling registers of routers with triple modular redundancy (TMR) to avoid large crosstalk-induced delay. A solution to multiple logic errors and crosstalk-induced delay uncertainty in on-chip interconnects using the combination of Hamming product codes and type-II HARQ with skewed transition was presented in [52].

Now that we have reviewed the merits and shortcomings of the existing solutions to combat crosstalk on adjacent link wires, we present the novel TransSync-RecSync solution to intra-flit skew in the following sections.

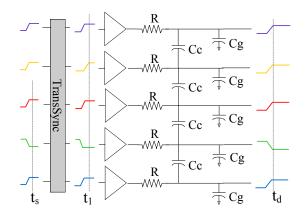

#### 5. TransSync

TransSync calculates the expected link traversal delay for each signal transition at the transmitting node before they are sent out and accordingly delays them so that their expected time of arrival at destination is the same as that of a transition suffering worst case (4Cc MCF) cross-talk interaction on link wires. Thus signal transition skew between the bit-lines of link are preemptively eliminated on the fly. At the sending node, the transmission of signal transitions which are likely to suffer the least cross-talk interaction on link wires (0Cc MCF), are delayed temporally so that they

Fig. 7. Timing diagram showing the operation of TransSync module.

reach the destination at the same time as transitions suffering 4Cc MCF interaction would. Signal transitions which are likely to suffer 4Cc MCF interaction on wires are not be delayed at all at the sending node. This scheme of dynamically delaying signal transitions at a sending node can be implemented with a simple combinational logic block added to the routers that uses the value of the current bit-vector on link wires and the value of the bit-vector transmitted in the previous cycle to estimate the expected wire delay for each signal transition. The TransSync scheme achieves this by employing a six-input combinational block for the current and previous values on a bit-line and its immediate neighbors to detect the type of cross-talk interaction (e.g.: 0Cc, 1Cc, 2Cc, 3Cc or 4Cc) for each bit of the bus. The state of each wire of the link is encoded onto the three outputs (p, q and r) of the TransSync module for the wire. Fig. 7 depicts the timing diagram of the working of the proposed TransSync design and Table II lists the output of the TransSync logic block for the different crosstalk interaction cases. A signal transition transmitted by a node at time  $t_s$  are actually transmitted on the link at time  $t_1$  by the TransSync module. It is to be noted that while we study the overhead of the logic to estimate the expected wire delay for every

Fig. 8. Circuit schematic of TransSync scheme.

signal of the bit-vector on link, this computation can be trivially performed by the PE at the sending nodes themselves.

Once the expected transmission delay for all the signal transition of the bit-vector on link has been figured out, their transmissions need to be delayed accordingly at the sending node. The transmission of a signal at the sending node can be delayed by a variety of ways. The transmission of different MCF cases can be delayed accordingly by varying the current available to charge/discharge the wire capacitance by modulating the current in the multi-stage radioed logic for the repeaters driving the link wires [59]. This is similar to the use of current-starved inverters in voltage-controlled oscillators. A simpler and more effective method of dynamically introducing the required delays would be to make all signal transitions charge/discharge shunt capacitors whose capacitance values are controlled by the "p, q, r" outputs of the TransSync logic before the signals are fed into the repeaters driving the link wires. We use this method delaying transmission by modulating load capacitances in our work here. The number and value of the capacitor employed for this purpose determines the accuracy with which de-skewing can be done. Since  $C_C$  and  $C_g$  associated with individual bit-

| Switching                                                                                                                         | Crosstalk      | Outputs |   |   |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------|---------|---|---|

| pattern                                                                                                                           | case           | р       | q | r |

| $(\uparrow,\uparrow,\uparrow),(\downarrow,\downarrow,\downarrow)$                                                                 | $0\mathrm{Cc}$ | 1       | 1 | 1 |

| $(-,\uparrow,\uparrow),(-,\downarrow,\downarrow),(\uparrow,\uparrow,-),(\downarrow,\downarrow,-)$                                 | 1Cc            | 1       | 1 | 0 |

| $(-,\uparrow,-),(-,\downarrow,-)$                                                                                                 | 2Cc            | 1       | 0 | 0 |

| $(\downarrow,\downarrow,\uparrow),(\downarrow,\uparrow,\uparrow),(\uparrow,\downarrow,\downarrow),(\uparrow,\uparrow,\downarrow)$ | 2Cc            | 1       | 0 | 0 |

| $(-,\downarrow,\uparrow),(-,\uparrow,\downarrow),(\downarrow,\uparrow,-),(\uparrow,\downarrow,-)$                                 | 3Cc            | 0       | 1 | 0 |

| $(\downarrow,\uparrow,\downarrow),(\uparrow,\downarrow,\uparrow)$                                                                 | 4Cc            | 0       | 0 | 0 |

Table II. Output of TransSync Module for different crosstalk interaction cases.

lines of links between hops change with process parameters and temperature, it may not possible to obtain a precise estimation of their values during different periods of operation of the NoC. However, a rough estimation of these capacitances, obtained during the design stage of the NoC, is sufficient to limit the intra-flit skew to an acceptable bound. Fig. 8 depicts the schematic of circuit implementing the proposed TransSync scheme.

The header flit can be used to determine the number of hops a particular packet is likely to bypass asynchronously on its way to the destination. To implement the TransSync scheme, every router only needs to incorporate the logic to enable TransSync during the transmission of only those flits which stand to gain from TransSync, i.e. only those flits which are likely to travel distances greater than those for which the skew between bit-lines remains within acceptable bounds.

Fig. 9. Circuit schematic of TransSync-2-lines scheme.

#### 6. TransSync 2 Lines

The overhead of TransSync design can be considerably reduced by taking into account the crosstalk coupling between only on two adjacent wires to predict the expected transmission delay for signal transition on a wire. This reduces the number of inputs to TransSync logic from six to four and the number of outputs from three to two. Table III lists the output of the modified TransSync: "TransSync-2-lines" scheme for different crosstalk interaction cases and Fig. 9 depicts the schematic of the modified TransSync-2-lines design.

Table III. Output of TransSync-2-lines logic.

| Switching pattern                                         | Crosstalk case | Output |   |

|-----------------------------------------------------------|----------------|--------|---|

|                                                           | (MCF)          | р      | q |

| $(\uparrow,\uparrow),(\downarrow,\downarrow)$             | 0Cc            | 1      | 1 |

| $(-,\uparrow),(-,\downarrow),(\uparrow,-),(\downarrow,-)$ | 2Cc            | 1      | 0 |

| $(\uparrow,\downarrow),(\downarrow,\uparrow)$             | 2Cc            | 0      | 0 |

With both TransSync and TransSync-2-lines schemes, the header flit can be used

to determine the number of hops a particular packet is likely to bypass asynchronously on its way to the destination. To implement the TransSync scheme, every router only needs to incorporate the logic to enable TransSync during the transmission of only those flits which stand to gain from TransSync, i.e. only those flits which are likely to travel distances greater than those for which the skew between bit-lines remains within acceptable bounds.

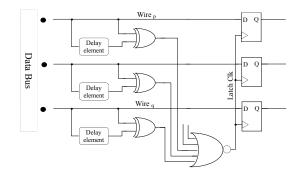

#### 7. RecSync

Fig. 10. Timing diagram for the operation of RecSync scheme.

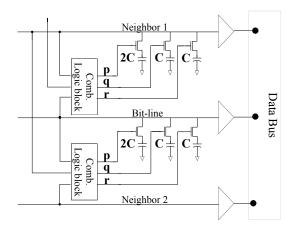

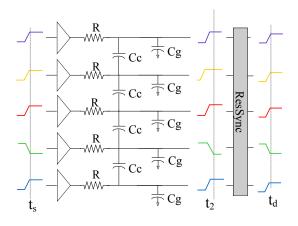

RecSync module eliminates the intra-flit skew accumulating between link wires at the receiving node by waiting for the last signal transition to arrive before relaying the flits further. The fastest arriving signal transition on link wires (OCc MCF case) triggers the RecSync module to enter a "wait" mode. The wait mode of Rec-Sync module precludes the destination node from receiving the incoming data. The RecSync module is allowed to wake up from the wait mode only after the slowest arriving signal transition suffering 4Cc MCF crosstalk interaction have arrived. Once the RecSync module is out of the wait state, the receiving node, it is guaranteed that all the signal transitions have already reached the destination and the receiving node is allowed to sample the incoming data.

Fig. 11. Circuit schematic of RecSync logic.

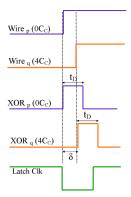

Fig. 10 explains the operation of RecSync scheme. A flit transmitted at time  $t_s$  arrives at the RecSync block at the destination hop at  $t_2$  and after the required processing is sampled by the destination node only at time  $t_d$  when the control signal to latch the incoming data is issued by the RecSync module. Fig. 11 shows a circuit implementing the RecSync scheme while Fig 12 depicts the timing diagram for the operation of RecSync. The signal arriving on every bit-line is passed through a delay element that delays the incoming signal by a preprogrammed interval of time  $t_D$ . The logical EXCLUSIVE OR of the current value on the bit-line and its delayed value from the delay element is generated. A logical high on the EXCLUSIVE OR output indicates a transition on the bit-line and the width of the EXCLUSIVE OR output pulse is proportional to the delay introduced by the delay element. If the delay  $t_D$  provided by the delay element on bit-lines (and consequently the width of pulse at the EXCLUSIVE OR outputs of all bit-line undergoing a transition) is greater that the temporal separation between signal transitions suffering 0Cc MCF crosstalk interaction and those suffering 4Cc MCF interaction on link wires, then the separation between the rising edges for the EXCLUSIVE OR output pulses for the

Fig. 12. Signal diagram explaining the working of RecSync logic.

two cases will be less than the width of these pulses. As shown in Fig 12, if the signal transition on wire-p suffers 0Cc coupling while that on wire-q suffers 4Cc crosstalk coupling and if the delay element is designed such that  $t_D$  greater than the separation between the arrival times of the signal on wire-p and wire-q for a given wire length, then the logical NOR of the corresponding EXCLUSIVE OR outputs is low until all signal transitions have arrived. If during every cycle, the destination node is allowed to sample the link wires for incoming data only when the NOR output is high, intra-flit skew induced errors can be avoided. This NOR signal can in fact be used as the clock to latch the incoming data.

Unlike TransSync, the RecSync scheme is also capable of handling transition skews on links resulting from sources other than just crosstalk coupling such as the wire length difference between bit-lines due to routing and other constraints. RecSync scheme needs be availed only when the number of hops that a flit has bypassed latching into FIFO queues is more than that for which the intra-flit skew on link wires is within acceptable bound. Like TransSync, the number of hops that the arriving data has been bypassed over can be inferred from the header flit.

The delay of the delay element in Fig. 11 can be programmed depending on the tolerance required and the number of hops over which flits are desired to be bypassed asynchronously without requiring synchronization. Greater the delay of the delay element, greater the skew between 0Cc and 4Cc interaction cases which can be eliminated by the RecSync module and hence greater is the number of hops over which the flits can be bypassed asynchronously. Increasing the delay of the delay element however increases the de-skewing latency of the RecSync module. To minimize the delay due to the wide NOR gate in RecSync design, a multi-stage logic implementing NOR function can instead be used. Also, for very wide links, RecSync scheme can be applied to overlapping subsets of wires to ensure that the delay of the wide NOR gate in the design does not become prohibitive.

#### D. Results and Discussion

#### 1. Simulation Environment

To obtain the timing information about signal transition skew using the first order wire model, transient analysis was carried out using Spectre in Cadence. The interconnect parameters for 65nm technology from Berkeley Predictive technology Model [45] used in the simulations are listed in Table IV. While the interconnect parameters (R,  $C_C$  and  $C_g$ ) used in the simulations are for PTM 65nm process, PTM 45nm bulk CMOS model [45] were used to construct static CMOS gates. All the gates used in the simulations have the minimum feature size as their transistor channel lengths while the width of the pull-up and pull-down transistors in the static gates were designed for equal rise and fall propagation delay. A power supply of 1.1V was used and simulations were performed for intermediate and global wires. A positive edge triggered system with clock period ( $T_{clk}$ ) of 1ns was simulated. The repeaters used for driving the link wires were taken to be six times the minimum sized inverter in this technology. Transmission delay for a signal transition was measured as the separation between 50% of the final value between the sending and receiving nodes. The transmission latency for a flit that is asynchronously bypassed over intervening hops is the sum of wire latency, combinational delay of the controlling and switching logic at the intervening nodes and the extra/synchronization latency.

The upper bound on intra-flit skew ' $\delta$ ' was obtained using the following formula:

$$\delta \le T_{clk} - (T_{setup} + T_{hold} + T_{Uncertainty}) \tag{2.1}$$

$T_{setup}$  and  $T_{hold}$  in Eqn. (2.1) are the setup and hold times respectively of the synchronous elements in the design while  $T_{Uncertainty}$  accounts for the uncertainty in the arrival times resulting from variations in process parameters, on-chip variation in temperature and supply voltage, constraints in physical routing implementation amongst other factors. Although it is difficult to precisely quantify the  $T_{uncertainty}$  component in Eqn. (2.1), it is known that this component is proportional to the length of wire  $L_{max}$  and consequently the wire delay. For the purpose of simulations, this component was assumed to be 10% of the clock period. We refer to the wire length for which the intra-flit skew is equal to the bounding value in Eqn. (2.1) as  $L_{max}$ . This is the maximum distance a flit can travel on the fast bypass paths without requiring to be synchronized. If a flit needs to travel a hop distance smaller than  $L_{max}$ , inter bit-line transition skew is within the tolerable limit and no synchronization is needed; whereas for distances of travel greater than  $L_{max}$  TransSync-RecSync schemes have to employed to ensure error-free operation. Link wires in baseline design as mentioned earlier are driven by 6X sized driving repeaters that are present every 1mm length of wire segment. We evaluate the performance of the proposed schemes and compare them with those of DBS [38], CPC [40], SHD and "Buffer" schemes. CPC is a crosstalk prevention coding scheme that encode three bits of information onto five adjacent wires to eliminate 4Cc crosstalk coupling on link wires. In DBS scheme, the

Fig. 13. Comparison of  $L_{max}$  and transmission delay for the different schemes studied.

inter-wire separation is doubled to reduce the coupling capacitance between adjacent wires. In SHD scheme, every bit-line is shielded by two GND lines on either side while in Buffer scheme, the size of the repeaters driving the links are doubled to 12X. While each of the schemes that we compare our designs against are radically different in their own right, they are also orthogonal to the proposed solutions since TransSync and RecSync can be used to reduce crosstalk noise in conjunction with any of these schemes.

#### 2. Performance Analysis

For the baseline design,  $L_{max}$  was found to be 2.23mm and the corresponding value of  $\delta$  was found to be 856.41ps. Fig. 13 compares values of  $L_{max}$  and the average transmission delay on 2mm long wires for the different schemes evaluated. The results presented in Fig. 13 have been normalized to the results obtained for the baseline design. Average delays for the different schemes reported in Fig. 13 have been obtained as the sum of the signal transmission delays for the different interconnect states weighted by their occurrence probabilities shown in Table I. As seen in Fig. 13, the

Fig. 14. Comparison of area and energy overhead of the different schemes studied.

largest  $L_{max}$  is to be achieved with TransSync scheme. The  $L_{max}$  of SHD and DBS greater than those achievable with CPC and SHD and DBS schemes also speed-up the transmission of signal transitions on wires because of the reduced coupling between adjacent wires. Also, it may be observed from Fig. 13 that while the  $L_{max}$  of TransSync-2-lines is lesser than that of TransSync, it is still comparable to that of CPC. The delay element of the RecSync scheme is programmed to eliminate the intra-flit skew accruing over the travel of data on 2mm long link wires. The average transmission latency is also reduced if the size and hence the drive strength of the driving repeaters is doubled (Buffer). However, the Buffer scheme provides very little improvement in  $L_{max}$  over the baseline design.

#### 3. Overhead Analysis

Fig. 14 shows the energy consumption and area of 2mm long links for the schemes studies normalized to those of the baseline design. CPC and DBS lead to a reduction of 13% and 17% respectively in the overall energy consumption on links when compared to the baseline design. The increased  $L_{max}$  with TransSync and RecSync

schemes come at the cost of increased energy consumption. TransSync-2-lines scheme leads to a 4% reduction in the overall link energy consumption. TransSync and Rec-Sync schemes have a small area overhead which is only greater than that of Buffer scheme.

## 4. System Level Results

We have worked with the assumption that the nodes on the chip are placed 1mm apart. Table V lists the summary of the simulation results. ABC in Table V stands for a heneric NoC architecture like [17, 18, 19, 20]) that incorporates asynchronous bypass to reduce communication latency. Flits that are bypassed over more than two hops in such designs therefore require synchronization every two hops, each synchronization costing 2.5 cycles [20], to eliminate the accrued intra-flit skew. TransSync allows this hop count to increase to 4 and incurs an extra latency of 0.37 cycles for every 4 hops of travel. If RecSync is employed every two hops, then the synchronization latency is reduced to 0.77 cycles. Table V summarizes the number of hops a flit can travel without synchronization and the extra latency incurred by the different schemes. The synchronization latency of RecSync is relatively high because of the wide NOR gate included in the design. This latency however, is still smaller than that incurred by synchronization using conventional bi-FIFIO schemes every two hops.

Fig. 15 represents the information listed in Table V as the plot of latency vs. the number of hops traveled by a flit under no load and no congestion network traffic on a 7X7 mesh NoC using the assumptions in [20]. The maximum number of hops that a flit can travel on the 7X7 mesh ix 12 and from [20] the sum of wire traversal latency and the delay of switching and forwarding logic is taken to be 0.75 cycle per hop of travel. The study has been carried out under no load and no congestion traffic conditions since the asynchronous bypass paths are more likely to help in

Fig. 15. Plot of transmission latency vs. number of hops traveled by flits for different schemes.

bringing down the down communication latencies under these conditions. In presence of congestion in the network or under high injection rates, the high-speed bypass paths would fail to serve their purpose since most of the data would have to be queued into to the FIFO buffers at intermediate nodes between source and destination nodes, while they wait for allocation of resources and are forwarded downstream. The communication latency on a conventional GALS NoC is very high since flits have to be synchronized to a new clock domain every hop. The asynchronous bypass paths in ABC designs promise to improve performance by eliminating the need for unnecessary synchronizations. The average network latency for an Ideal ABC design on 7X7 mesh was found to be 12.10 cycles. It is evident from Fig. 15 that the actual average communication latency in ABC is 22.20 cycles which is far from the expected value due to the problem of inter-bit-line skewing. CPC, DBS, SHD and Buffer schemes have similar performance with the average communication latencies in these schemes are in the vicinity of 17 clock cycles. The average communication latencies for TransSync and TransSync-2-lines schemes are 16.27 cycles and 17.74 cycles respectively. Although the performance of TransSync-2-lines is slightly worse than that of the original TransSync design, the overheads associated with it are much smaller. It may also be observed that the RecSync scheme is very effective as it helps in bringing down the average communication latency 13.79 cycles which is very close to that expected of an ideal ABC design. It may also be noted that there is no sizable improvement in latency when RecSync is coupled with either TransSync or TransSync-2-lines schemes.

| the simulations.                         |

|------------------------------------------|

| in t                                     |

| used                                     |

| parameters                               |

| Interconnect parameters used in the sim- |

| Ν.                                       |

| Table                                    |

| Wire type    | width( $\mu m$ ) | $space(\mu m)$ | thickness( $\mu m$ ) | height <sub>ILD</sub> ( $\mu m$ ) | $\mathbf{k}_{ILD}$ | $C_c(fF/mm)$ | $C_g(fF/mm)$ | $  R_l(\Omega/mm)  $ |

|--------------|------------------|----------------|----------------------|-----------------------------------|--------------------|--------------|--------------|----------------------|

| Local        | 0.1              | 0.1            | 0.2                  | 0.2                               | 2.2                | 53.683       | 19.419       | 1100                 |

| Intermediate | 0.14             | 0.14           | 0.35                 | 0.2                               | 2.2                | 57.649       | 26.888       | 448.979              |

| Global       | 0.45             | 0.45           | 1.2                  | 0.2                               | 2.2                | 73.222       | 82.031       | 40.74                |

Table V. Number of hops that a flit can travel without requiring synchronization, latency overhead and latency formula for different schemes for 'n' hops of travel.

| Latency Formula    | for 'n' hops of | travel                    | $0.75 \times n, if \ n < 3 \\ 0.75 \times n + 2.5 \times floor(\frac{n-1}{2}), \ n \ge 3$ | $0.75 \times n + 0.16, \ if \ n < 3$ $0.75 \times n + 0.16 \times floor(\frac{n}{3}) + 2.5 \times floor(\frac{n-1}{3}), \ n \ge 3$ | $0.63 \times n, if n < 3$ $0.63 \times n + 2.5 \times floor(\frac{n-1}{3}), n \ge 3$ | $0.61 \times n, \ if \ n < 3 \\ 0.61 \times n + 2.5 \times floor(\frac{n-1}{3}), \ n \ge 3$ | $0.71 \times n, if \ n < 3 \\ 0.71 \times n + 2.5 \times floor(\frac{n-1}{3}), \ n \ge 3$ | $0.75 \times n + 0.37 \times floor(\frac{n}{4}) + 2.5 \times floor(\frac{n-1}{4}), \ n \ge 4$ | $0, if n < 3 \\ 0.75 \times n + 0.22 \times floor(\frac{n}{3}) + 2.5 \times floor(\frac{n-1}{3}), n \ge 3$ | $\begin{array}{c} 0.75 \times n, \ if \ n < 3 \\ 0.75 \times n + 0.77 \times floor(\frac{n-1}{2}), \ n \geq 3 \end{array}$ | $0.75 \times n, \ if \ n < \frac{4}{1000} \\ 0.75 \times n + 0.37 \times floor(\frac{n}{4}) + 0.77 \times floor(\frac{n-1}{4}), \ n \ge 4$ | $0.75 \times n, if \ n < 3 \\ 0.75 \times n + 0.37 \times floor(\frac{n}{3}) + 0.77 \times floor(\frac{n-1}{3}), \ n \ge 3$ |

|--------------------|-----------------|---------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Synchronization    | latency (after  | $\mathcal{L}_{max}$ hops) | 2.5 cycles                                                                                | 2.5 cycles                                                                                                                         | 2.5 cycles                                                                           | 2.5 cycles                                                                                  | 2.5 cycles                                                                                | 2.5 cycles                                                                                    | 2.5 cycles                                                                                                 | 0                                                                                                                          | 0                                                                                                                                          | 0                                                                                                                           |

| Latency            | overhead of     | $\operatorname{scheme}$   | I                                                                                         | 0.16 cycles                                                                                                                        | I                                                                                    | I                                                                                           | I                                                                                         | 0.37 cycles                                                                                   | 0.22 cycles                                                                                                | 0.77 cycles                                                                                                                | RecSync +<br>TransSync                                                                                                                     | RecSync +<br>TransSync-2-lines                                                                                              |

| $\mathbf{L}_{max}$ | (# of           | hops)                     | 2                                                                                         | 33                                                                                                                                 | °.                                                                                   | 3                                                                                           | °                                                                                         | 4                                                                                             | 33                                                                                                         | 2                                                                                                                          | 4                                                                                                                                          | 3                                                                                                                           |

|                    | Scheme          |                           | ABC                                                                                       | CPC                                                                                                                                | CHS                                                                                  | DBS                                                                                         | Buffer                                                                                    | TransSync                                                                                     | TransSync-2-lines                                                                                          | $\operatorname{RecSync}$                                                                                                   | RecSync +<br>TransSync                                                                                                                     | RecSync +<br>TransSync-2-lines                                                                                              |

#### CHAPTER III

# INTERCONNECT BER IN THE PRESENCE OF CROSSTALK AND VARIATIONS

Crosstalk noise is the most critical factor affecting communication reliability in onchip interconnect in NoC/MPSoC designs. In Chapter II, we explored how intra-flit skew limits transmission of signal transitions on long parallel wires on chip. Maximum intra-flit skew which is the separation between transitions suffering 0Cc and 4Cc MCF interaction was used as a metric to study signal integrity on wires and the impact of crosstalk on packet errors. In this chapter, we present a formal methodology to estimate bit-error rate (BER) on interconnect wires in presence of crosstalk and variatios. Since variability greatly impacts the extent of crosstalk coupling between parallel wires, it is imperative to review the source of variability and their effect on the integrity of signal transitions in long wires.

## A. Sources of Variation

The performance of integrated circuits varies with any deviation in the circuits structural or electrical parameters from the desired values. Environmental factors that arise during the operation of a circuit and affect its performance are variations in power supply, switching activity and temperature. Physical factors brought about by limitations in processing and masking during manufacture result in randomly distributed spatial variations in device and interconnect structures. Variations in structural parameters affect both performance and yield in integrated circuits. These variations have both inter-die and intra-die components ([60], [61]). Inter-die variations are the difference in parameter values across similar dies on the same wafer while intra-die variations are randomly distributed spatial variations in parameters on the same die. The contribution of each component along with a model of each variation is presented by in [62] and [63]. A brief review of the sources of variation and their impact on interconnect reliability is given in the proceeding section.

# 1. Device Variations

Some important sources of variation relating to the geometric structure and internal material parameters of MOSFETs, resistors and capacitors in the circuit are:

a. Film Thickness

Oxide film thickness  $(t_o x)$  is very critical to a MOSFETs operation and any variations in the oxide thickness can lead variations in  $V_T$  which can in turn lead to large deviations from the MOSFETs nominal transfer characteristics. Oxide thickness, however, is a relatively well controlled parameter in most processes. In addition to geometric sources, the presence of any mobile charges in the gate oxide can introduce bias dependent variation in  $V_T$  which can be about 10% of the nominal device  $V_T$  for the technology [64].

#### b. Lateral Device Dimensions

Some factors which give rise to variations in length and width of devices are: photolithography proximity effects due systematic pattern dependencies; photo system variations due to mask errors; lens irregularities and plasma etch variations. The resulting variations may be spatially correlated. MOSFETs are particularly sensitive to effective channel length since this parameter directly impacts its output current characteristics [65].

Fig. 16. Interconnect structure.

#### c. Doping

Junction depth and doping profiles may vary with implant dose, energy or angle variations. This has a direct bearing on the effective channel length and therefore the threshold voltage of the devices. Random placement and dopant concentration fluctuations due to discrete location of dopant atoms in the channel and source/drain regions can also lead to variation of  $V_T$  across devices on the chip. Variations in  $V_T$  lead to variations in leakage currents and noise margins. Techniques like halo implant [66] and retrograde channel doping [67] employed in n deep sub-micron technologies further increase the impact of implant and diffusion variation. Variations in thermal anneal and gate doping can cause variation in effective gate oxide thickness which in turn can result in loss of matching.

## 2. Interconnect Variations

Like devices, deviations in material properties as well as vertical and lateral dimensions of interconnect structures give rise to variation in interconnect behavior. Some important source of interconnect variations are:

Fig. 17. Three segment wire model for crosstalk coupling.

# a. Line Width (W) and Space (S)