# CONCURRENT ONLINE TESTING FOR MANY CORE SYSTEMS-ON-CHIPS

A Dissertation

by

JASON DANIEL LEE

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

December 2010

Major Subject: Computer Engineering

Concurrent Online Testing for Many Core Systems-on-Chips

Copyright 2010 Jason Daniel Lee

# CONCURRENT ONLINE TESTING FOR MANY CORE SYSTEMS-ON-CHIPS

# A Dissertation

by

# JASON DANIEL LEE

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

# Approved by:

Chair of Committee, Rabi N. Mahapatra Committee Members, Duncan M. Walker

Eun Jung Kim

Seong G. Choi

Head of Department, Valerie E. Taylor

December 2010

Major Subject: Computer Engineering

#### **ABSTRACT**

Concurrent Online Testing for Many Core Systems-on-Chips. (December 2010)

Jason Daniel Lee, B.S., Texas A&M University

Chair of Advisory Committee: Dr. Rabi N. Mahapatra

Shrinking transistor sizes have introduced new challenges and opportunities for system-on-chip (SoC) design and reliability. Smaller transistors are more susceptible to early lifetime failure and electronic wear-out, greatly reducing their reliable lifetimes. However, smaller transistors will also allow SoC to contain hundreds of processing cores and other infrastructure components with the potential for increased reliability through massive structural redundancy. Concurrent online testing (COLT) can provide sufficient reliability and availability to systems with this redundancy. COLT manages the process of testing a subset of processing cores while the rest of the system remains operational. This can be considered a temporary, graceful degradation of system performance that increases reliability while maintaining availability.

In this dissertation, techniques to assist COLT are proposed and analyzed. The techniques described in this dissertation focus on two major aspects of COLT feasibility: recovery time and test delivery costs. To reduce the time between failure and recovery, and thereby increase system availability, an anomaly-based test triggering unit (ATTU) is proposed to initiate COLT when anomalous network behavior is detected. Previous COLT techniques have relied on initiating tests periodically. However, determining the

testing period is based on a device's mean time between failures (MTBF), and calculating MTBF is exceedingly difficult and imprecise.

To address the test delivery costs associated with COLT, a distributed test vector storage (DTVS) technique is proposed to eliminate the dependency of test delivery costs on core location. Previous COLT techniques have relied on a single location to store test vectors, and it has been demonstrated that centralized storage of tests scales poorly as the number of cores per SoC grows. Assuming that the SoC organizes its processing cores with a regular topology, DTVS uses an interleaving technique to optimally distribute the test vectors across the entire chip. DTVS is analyzed both empirically and analytically, and a testing protocol using DTVS is described.

COLT is only feasible if the applications running concurrently are largely unaffected. The effect of COLT on application execution time is also measured in this dissertation, and an application-aware COLT protocol is proposed and analyzed.

Application interference is greatly reduced through this technique.

# DEDICATION

This work is dedicated to the memory of my mother, Karen Culotta Lee.

#### **ACKNOWLEDGEMENTS**

Without the guidance and support of my advisor, Dr. Mahapatra, this work would not have been possible. The Ph.D. process is rarely a smooth endeavor; however, Dr. Mahapatra's encouragement was constant. Additionally, he provided great opportunities for my professional and personal growth beyond my own research. Highlights included a multi-year assistantship working for the FAA and various aerospace companies to make commercial avionics safer and a trip to India to discuss the need for greater American-Indian research collaboration.

The complimentary expertise of each of my committee members was also extremely valuable in creating this work. Drs. Walker, Kim and Choi each provided useful information and knowledge which improved the quality of my work greatly. They were always happy to discuss any aspect of research with me.

Maintaining a group of close friends and co-workers throughout my time here has also played a vital role in successfully completing this degree. Thank you to the following people: Praveen, Suman, Nikhil, Suneil, Aalap, Javier, Scott, Ron and Brad.

On a more personal level, my wife, Jennifer Nicks, deserves all the credit in the world for keeping me focused with a positive attitude during all of the emotional highs and lows attempting this degree has brought me. I look forward to our next challenge.

Finally, I would like to thank my father, Steven Lee, for instilling the importance of education throughout my life. From an early age, it was our plan for me to obtain a Ph.D. That goal has been fulfilled.

# NOMENCLATURE

ATE Automatic Test Equipment

ATTU Anomaly-Based Test Triggering Unit

BIST Built-in Self Test

COLT Concurrent Online Testing

CMOS Complementary Metal–Oxide–Semiconductor

CNI Core–Network Interface

DFT Design for Test

DTVS Distributed Test Vector Storage

ILP Instruction Level Parallelism

IMA Integrated Modular Avionics

IP Intellectual Property

MTBF Mean Time Between Failure

MTTR Mean Time to Repair

NoC Network-on-Chip

SoC System-on-Chip

TLP Thread Level Parallelism

# TABLE OF CONTENTS

|                                                                                                                                                          | Page           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| ABSTRACT                                                                                                                                                 | iii            |

| DEDICATION                                                                                                                                               | v              |

| ACKNOWLEDGEMENTS                                                                                                                                         | vi             |

| NOMENCLATURE                                                                                                                                             | vii            |

| TABLE OF CONTENTS                                                                                                                                        | viii           |

| LIST OF FIGURES                                                                                                                                          | xi             |

| LIST OF TABLES                                                                                                                                           | xiii           |

| CHAPTER                                                                                                                                                  |                |

| I INTRODUCTION                                                                                                                                           | 1              |

| A. Many Core SoC Preliminaries                                                                                                                           | 5<br>6         |

| II RELIABILITY AND TESTING OF SAFETY-CRITICAL SOC                                                                                                        | C 10           |

| A. Design and Analysis of Safety-Critical SoC                                                                                                            | 11<br>13<br>16 |

| Manufacturer Testing     Built-In Self Test C. Recent Proposals in Concurrent Online Testing     Test Infrastructure IP Cores     Software-Based Testing | 17<br>17<br>17 |

| III ONLINE DETECTION OF CORE FAILURE WITH ANOMALY-BASED TEST TRIGGERING UNITS                                                                            | 22             |

| CHAPTER |                                                      | Page |

|---------|------------------------------------------------------|------|

|         | A. Introduction                                      | 22   |

|         | B. Fault Tolerance and Anomaly-Based Error Detection |      |

|         | NoC-Based Fault Tolerance                            | 26   |

|         | 2. Anomaly-Based Error Detection                     | 27   |

|         | C. Test Triggering Mechanism                         | 28   |

|         | 1. ATTU Architecture                                 | 29   |

|         | 2. Message Monitoring Considerations                 | 30   |

|         | 3. ATTU Training Period                              |      |

|         | D. Experimental Setup                                | 33   |

|         | 1. Fault Model                                       |      |

|         | 2. NoC Configuration and Simulation                  |      |

|         | 3. Application Benchmarks                            |      |

|         | E. Experimental Results                              |      |

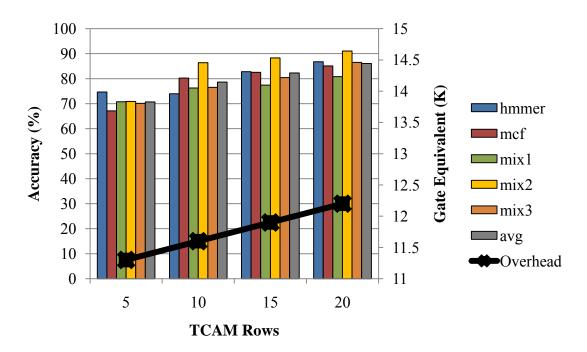

|         | Detection Rate                                       |      |

|         | 2. Effect of Error Distribution                      |      |

|         | 3. Effect of Error Rate                              | 39   |

|         | 4. Effect of L1 Cache Size                           |      |

|         | 5. Effect of ATTU Memory                             |      |

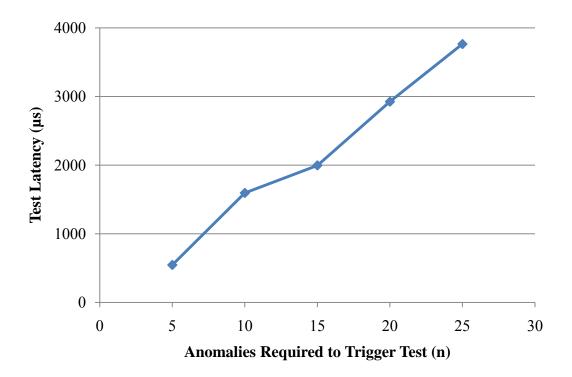

|         | 6. Effect of Trigger Sensitivity                     |      |

|         | 7. ATTU Overhead                                     |      |

|         | F. Conclusion                                        |      |

| IV      | DISTRIBUTED TEST VECTOR STORAGE                      | 44   |

|         | A. Introduction                                      | 44   |

|         | B. Mechanisms of Concurrent Online Test              |      |

|         | On-Chip Test Controllers                             |      |

|         | 2. ISA Testing Extensions                            |      |

|         | 3. Software-Based Self Test                          | 51   |

|         | C. Motivation for Distributed Test Vector Storage    |      |

|         | Test Delivery Costs Relative to Distance             |      |

|         | D. Distributed Test Vector Storage Analysis          |      |

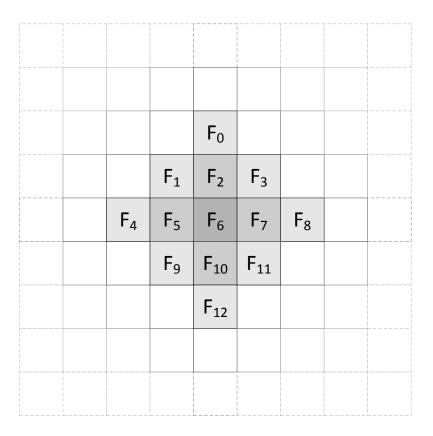

|         | Interleaving on Tori                                 |      |

|         | Interleaving Example                                 |      |

|         | 3. Applying Interleaving to Test Storage             |      |

|         | E. Distributed COLT Architecture                     |      |

|         | System Components                                    |      |

|         | Distributed COLT Scheduling Protocol                 |      |

|         | 3. Code-Division Core Test Scheduling                |      |

|         | F. Analytical Results                                |      |

|         | Anarytical Results     Network Load Analysis         |      |

|         | Energy Consumption Analysis                          |      |

|         | 2. Lifetgy Consumption Analysis                      | 07   |

| G. Experimental Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CHAPTER  |                                         | Page |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------|------|

| 1. NoC Simulator         7           2. System Architecture         7           3. System Cores         7           H. Experimental Results         7           1. System Test Latency         7           2. Energy Consumption of Test Delivery         7           3. Effect of Traffic Load on Testing         7           4. Effect of Core Test Scheduling         8           5. Distributed Test Controller Overhead         8           6. Test Vector Memory Overhead         8           1. Conclusion         8           V APPLICATION-AWARE ONLINE TESTING         8           A Introduction         8           B. Application-Aware Online Testing Architecture         8           1. Test Vector Delivery Blocking         8           2. Test Vector Storage Redundancy         9           3. Using These Methods in Combination         9           C. Experimental Setup         9           1. System Architecture         9           2. Test and Application Parameters         9           D. Experimental Results         9           1. Application Interference of COLT         9           2. Test Vector Storage Redundancy         9           4. Combination of Blocking and Redundancy         9 <t< td=""><td></td><td>3. Storage Redundancy</td><td> 69</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | 3. Storage Redundancy                   | 69   |

| 2. System Architecture       3. System Cores       7         H. Experimental Results       7         1. System Test Latency       7         2. Energy Consumption of Test Delivery       7         3. Effect of Traffic Load on Testing       7         4. Effect of Core Test Scheduling       8         5. Distributed Test Controller Overhead       8         6. Test Vector Memory Overhead       8         1. Conclusion       8         V APPLICATION-AWARE ONLINE TESTING       8         A. Introduction       8         B. Application-Aware Online Testing Architecture       8         1. Test Vector Delivery Blocking       8         2. Test Vector Storage Redundancy       9         3. Using These Methods in Combination       9         C. Experimental Setup       9         1. System Architecture       9         2. Test and Application Parameters       9         D. Experimental Results       9         1. Application Interference of COLT       9         2. Test Vector Storage Redundancy       9         4. Combination of Blocking and Redundancy       9         5. Test Controller Overhead       10         VI CONCLUSIONS       10         A. Future Work <td< td=""><td></td><td>G. Experimental Setup</td><td> 70</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | G. Experimental Setup                   | 70   |

| 3. System Cores   7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | 1. NoC Simulator                        | 70   |

| 3. System Cores   7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | 2. System Architecture                  | 72   |

| 1. System Test Latency         7           2. Energy Consumption of Test Delivery         7           3. Effect of Traffic Load on Testing         7           4. Effect of Core Test Scheduling         8           5. Distributed Test Controller Overhead         8           6. Test Vector Memory Overhead         8           1. Conclusion         8           A. Introduction         8           B. Application-Aware Online Testing Architecture         8           1. Test Vector Delivery Blocking         8           2. Test Vector Storage Redundancy         9           3. Using These Methods in Combination         9           C. Experimental Setup         9           1. System Architecture         9           2. Test and Application Parameters         9           D. Experimental Results         9           1. Application Interference of COLT         9           2. Test Vector Delivery Blocking         9           3. Test Vector Storage Redundancy         9           4. Combination of Blocking and Redundancy         9           5. Test Controller Overhead         10           VI CONCLUSIONS         10           A. Future Work         10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |                                         |      |

| 2. Energy Consumption of Test Delivery.       7         3. Effect of Traffic Load on Testing.       7         4. Effect of Core Test Scheduling.       8         5. Distributed Test Controller Overhead.       8         6. Test Vector Memory Overhead.       8         I. Conclusion.       8         V APPLICATION-AWARE ONLINE TESTING.       8         A. Introduction.       8         B. Application-Aware Online Testing Architecture.       8         1. Test Vector Delivery Blocking.       8         2. Test Vector Storage Redundancy.       9         3. Using These Methods in Combination.       9         C. Experimental Setup.       9         1. System Architecture.       9         2. Test and Application Parameters.       9         D. Experimental Results.       9         1. Application Interference of COLT.       9         2. Test Vector Storage Redundancy.       9         4. Combination of Blocking and Redundancy.       9         5. Test Controller Overhead.       10         E. Conclusion.       10         VI CONCLUSIONS.       10         A. Future Work.       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | H. Experimental Results                 | 74   |

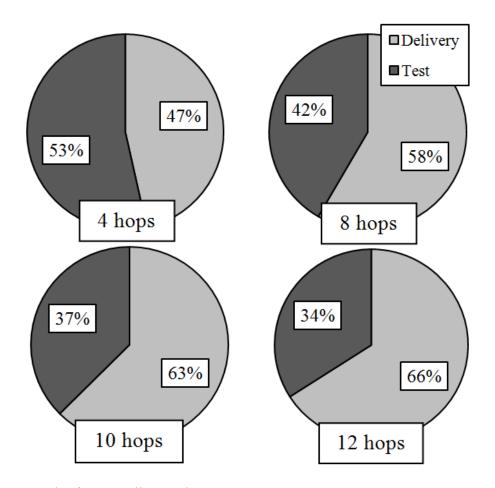

| 3. Effect of Traffic Load on Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | System Test Latency                     | 75   |

| 4. Effect of Core Test Scheduling       8         5. Distributed Test Controller Overhead       8         6. Test Vector Memory Overhead       8         I. Conclusion       8         V APPLICATION-AWARE ONLINE TESTING       8         A. Introduction       8         B. Application-Aware Online Testing Architecture       8         1. Test Vector Delivery Blocking       8         2. Test Vector Storage Redundancy       9         3. Using These Methods in Combination       9         C. Experimental Setup       9         1. System Architecture       9         2. Test and Application Parameters       9         D. Experimental Results       9         1. Application Interference of COLT       9         2. Test Vector Delivery Blocking       9         3. Test Vector Storage Redundancy       9         4. Combination of Blocking and Redundancy       9         5. Test Controller Overhead       10         E. Conclusion       10         VI CONCLUSIONS       10         A. Future Work       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |                                         |      |

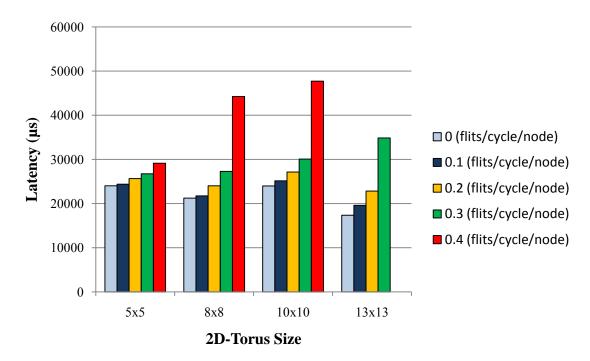

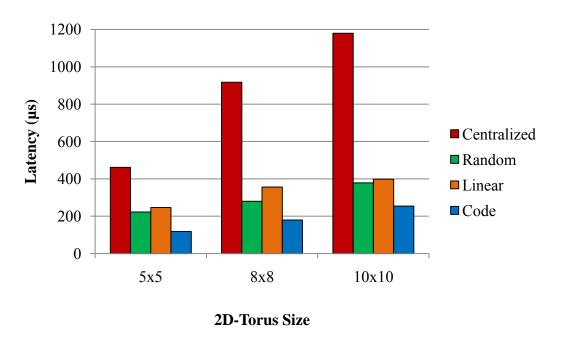

| 4. Effect of Core Test Scheduling       8         5. Distributed Test Controller Overhead       8         6. Test Vector Memory Overhead       8         I. Conclusion       8         V APPLICATION-AWARE ONLINE TESTING       8         A. Introduction       8         B. Application-Aware Online Testing Architecture       8         1. Test Vector Delivery Blocking       8         2. Test Vector Storage Redundancy       9         3. Using These Methods in Combination       9         C. Experimental Setup       9         1. System Architecture       9         2. Test and Application Parameters       9         D. Experimental Results       9         1. Application Interference of COLT       9         2. Test Vector Delivery Blocking       9         3. Test Vector Storage Redundancy       9         4. Combination of Blocking and Redundancy       9         5. Test Controller Overhead       10         E. Conclusion       10         VI CONCLUSIONS       10         A. Future Work       10         REFERENCES       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          | 3. Effect of Traffic Load on Testing    | 79   |

| 6. Test Vector Memory Overhead       8         I. Conclusion       8         V APPLICATION-AWARE ONLINE TESTING       8         A. Introduction       8         B. Application-Aware Online Testing Architecture       8         1. Test Vector Delivery Blocking       8         2. Test Vector Storage Redundancy       9         3. Using These Methods in Combination       9         C. Experimental Setup       9         1. System Architecture       9         2. Test and Application Parameters       9         D. Experimental Results       9         1. Application Interference of COLT       9         2. Test Vector Delivery Blocking       9         3. Test Vector Storage Redundancy       9         4. Combination of Blocking and Redundancy       9         5. Test Controller Overhead       10         E. Conclusion       10         VI CONCLUSIONS       10         A. Future Work       10         REFERENCES       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |                                         |      |

| I. Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | 5. Distributed Test Controller Overhead | 82   |

| V APPLICATION-AWARE ONLINE TESTING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | 6. Test Vector Memory Overhead          | 83   |

| A. Introduction  B. Application-Aware Online Testing Architecture  1. Test Vector Delivery Blocking  2. Test Vector Storage Redundancy  3. Using These Methods in Combination  C. Experimental Setup  1. System Architecture  2. Test and Application Parameters  D. Experimental Results  1. Application Interference of COLT  2. Test Vector Delivery Blocking  3. Test Vector Storage Redundancy  4. Combination of Blocking and Redundancy  5. Test Controller Overhead  E. Conclusion  10  VI CONCLUSIONS  10  REFERENCES  10  REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | I. Conclusion                           | 83   |

| B. Application-Aware Online Testing Architecture  1. Test Vector Delivery Blocking  2. Test Vector Storage Redundancy  3. Using These Methods in Combination  C. Experimental Setup  1. System Architecture  2. Test and Application Parameters  D. Experimental Results  1. Application Interference of COLT  2. Test Vector Delivery Blocking  3. Test Vector Storage Redundancy  4. Combination of Blocking and Redundancy  5. Test Controller Overhead  E. Conclusion  10  VI CONCLUSIONS  10  A. Future Work  11  REFERENCES  10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V        | APPLICATION-AWARE ONLINE TESTING        | 85   |

| B. Application-Aware Online Testing Architecture  1. Test Vector Delivery Blocking  2. Test Vector Storage Redundancy  3. Using These Methods in Combination  C. Experimental Setup  1. System Architecture  2. Test and Application Parameters  D. Experimental Results  1. Application Interference of COLT  2. Test Vector Delivery Blocking  3. Test Vector Storage Redundancy  4. Combination of Blocking and Redundancy  5. Test Controller Overhead  E. Conclusion  10  A. Future Work  11  CREFERENCES  12  A Future Work  13  Conclusion  14  CREFERENCES  15  CREFERENCES  16  CREFERENCES  17  CREFERENCES  18  Conclusion  19  Conclusion  10  CREFERENCES  10   |          | A. Introduction                         | 85   |

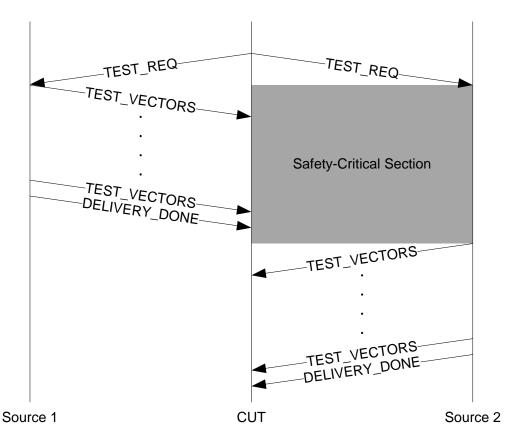

| 1. Test Vector Delivery Blocking 2. Test Vector Storage Redundancy 3. Using These Methods in Combination 5. C. Experimental Setup 5. 1. System Architecture 5. 2. Test and Application Parameters 6. D. Experimental Results 6. 1. Application Interference of COLT 6. 2. Test Vector Delivery Blocking 6. 3. Test Vector Storage Redundancy 6. 4. Combination of Blocking and Redundancy 6. 5. Test Controller Overhead 6. Conclusion 7. Conclusion |          |                                         |      |

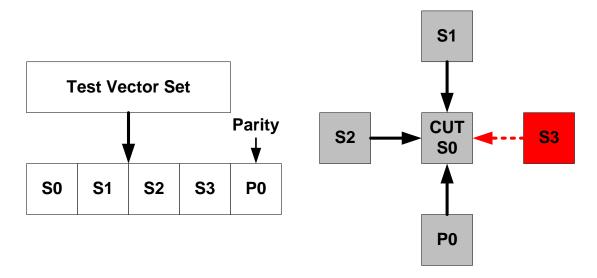

| 2. Test Vector Storage Redundancy 3. Using These Methods in Combination 5. C. Experimental Setup 5. 1. System Architecture 5. 2. Test and Application Parameters 5. D. Experimental Results 6. 1. Application Interference of COLT 6. 2. Test Vector Delivery Blocking 6. 3. Test Vector Storage Redundancy 6. 4. Combination of Blocking and Redundancy 6. 5. Test Controller Overhead 6. Conclusion 10. VI CONCLUSIONS 10. A. Future Work 10. CREFERENCES 10. CREFERENCES 10. Setup 10. Se |          |                                         |      |

| 3. Using These Methods in Combination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |                                         |      |

| C. Experimental Setup 99 1. System Architecture 99 2. Test and Application Parameters 99 D. Experimental Results 99 1. Application Interference of COLT 99 2. Test Vector Delivery Blocking 99 3. Test Vector Storage Redundancy 99 4. Combination of Blocking and Redundancy 99 5. Test Controller Overhead 100 E. Conclusion 100 VI CONCLUSIONS 100 A. Future Work 100 REFERENCES 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |                                         |      |

| 1. System Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | <u> </u>                                |      |

| 2. Test and Application Parameters 9 D. Experimental Results 9 1. Application Interference of COLT 9 2. Test Vector Delivery Blocking 9 3. Test Vector Storage Redundancy 9 4. Combination of Blocking and Redundancy 9 5. Test Controller Overhead 10 E. Conclusion 10 VI CONCLUSIONS 10 A. Future Work 10  REFERENCES 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | <u>.</u>                                |      |

| D. Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |                                         |      |

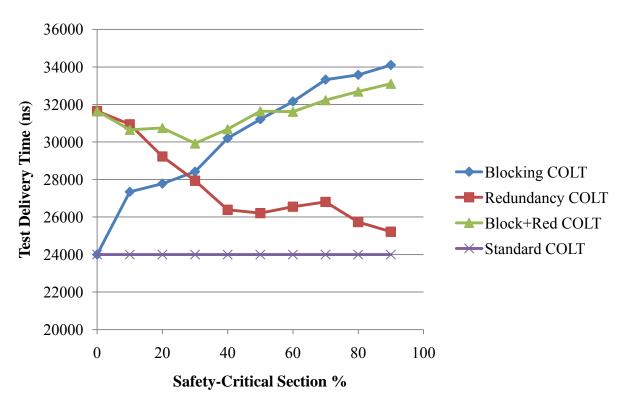

| 1. Application Interference of COLT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | • •                                     |      |

| 2. Test Vector Delivery Blocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |                                         |      |

| 3. Test Vector Storage Redundancy 9 4. Combination of Blocking and Redundancy 9 5. Test Controller Overhead 10 E. Conclusion 10  VI CONCLUSIONS 10  A. Future Work 10  REFERENCES 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                         |      |

| 4. Combination of Blocking and Redundancy 5. Test Controller Overhead 10 E. Conclusion 10 VI CONCLUSIONS 10 A. Future Work 10 REFERENCES 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |                                         |      |

| 5. Test Controller Overhead       10         E. Conclusion       10         VI CONCLUSIONS       10         A. Future Work       10         REFERENCES       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |                                         |      |

| E. Conclusion 10  VI CONCLUSIONS 10  A. Future Work 10  REFERENCES 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |                                         |      |

| A. Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |                                         |      |

| REFERENCES 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VI       | CONCLUSIONS                             | 103  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | A. Future Work                          | 105  |

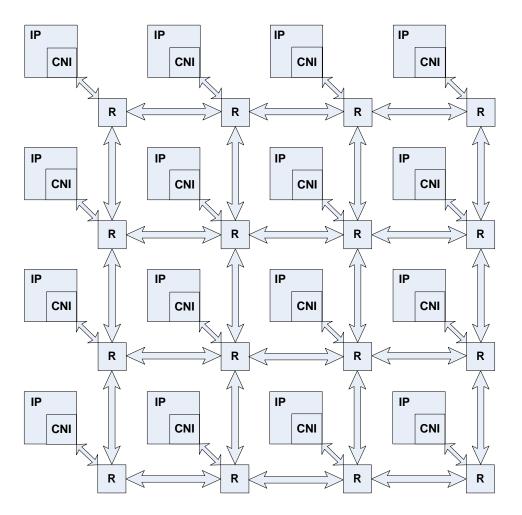

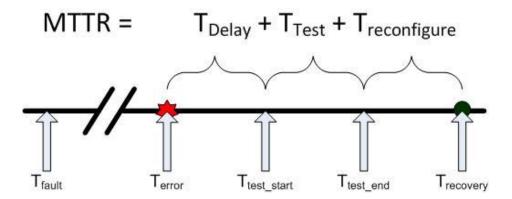

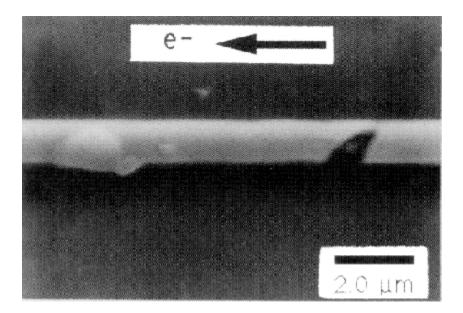

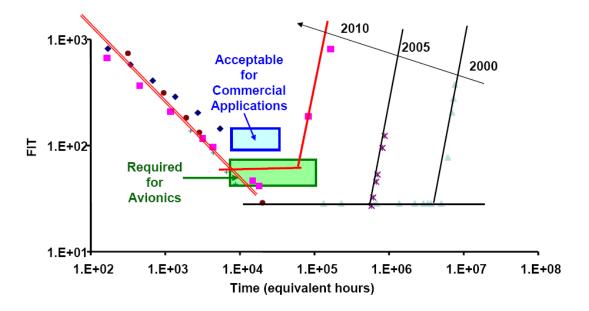

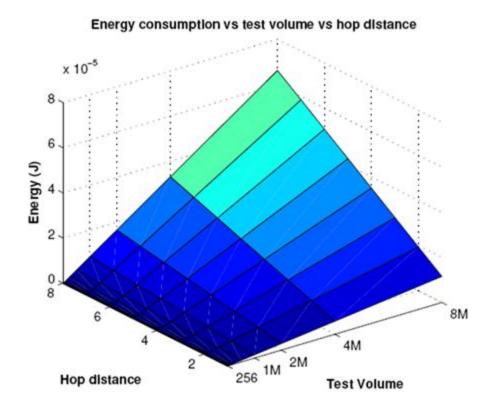

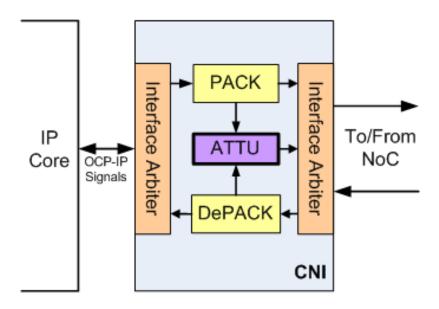

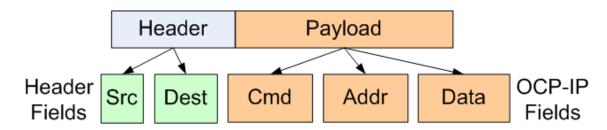

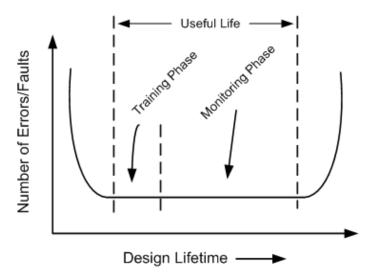

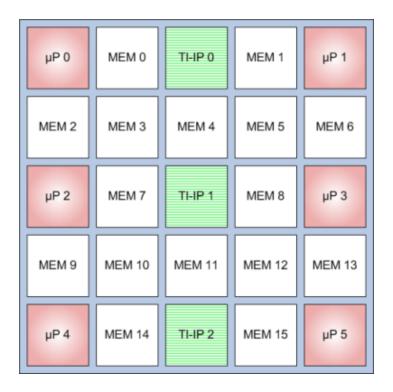

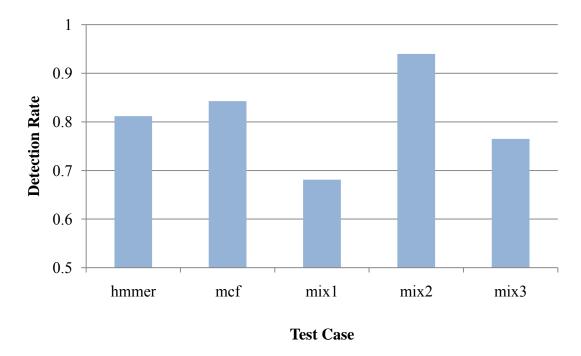

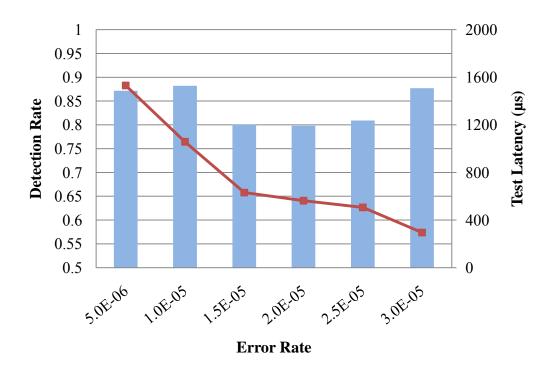

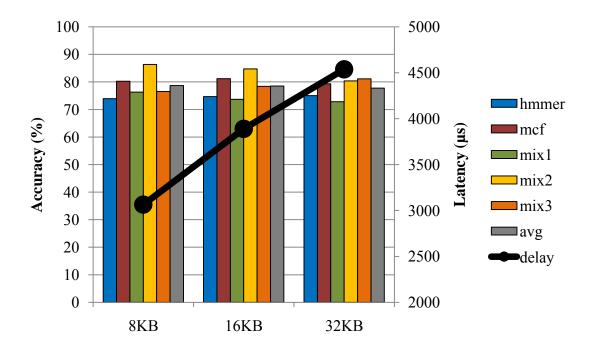

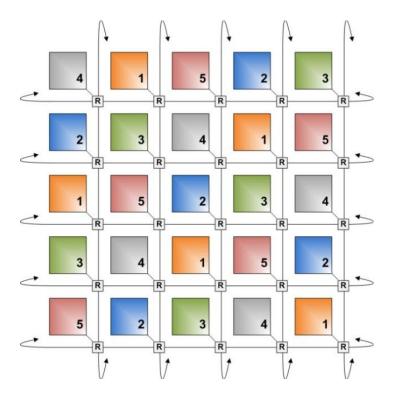

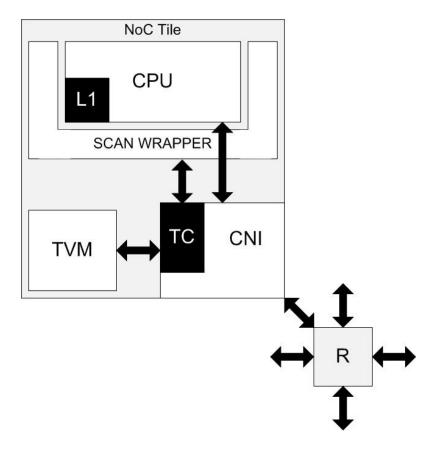

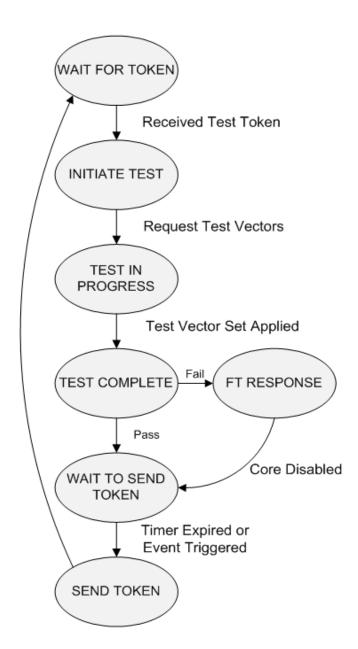

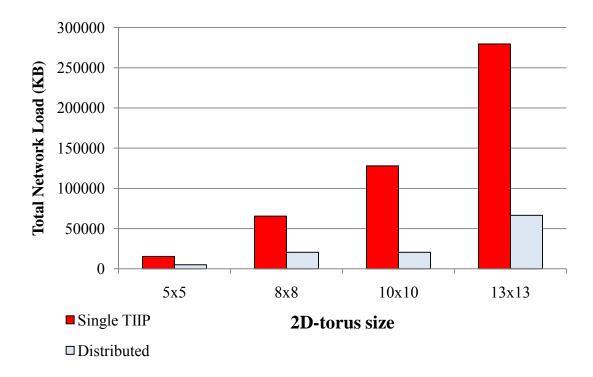

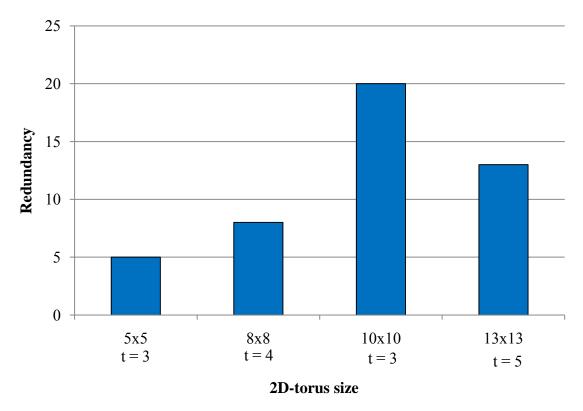

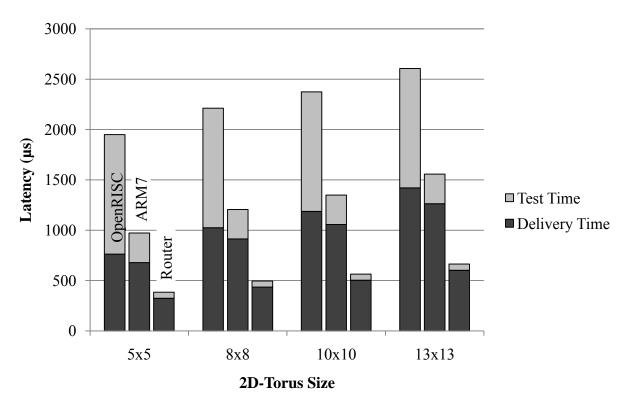

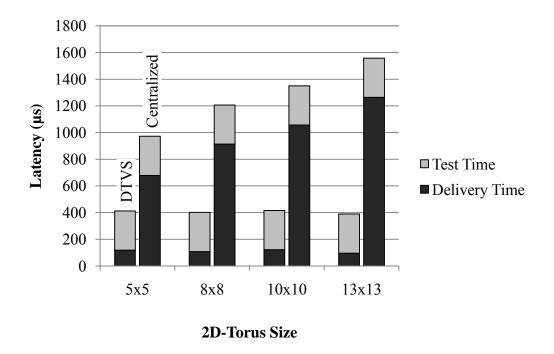

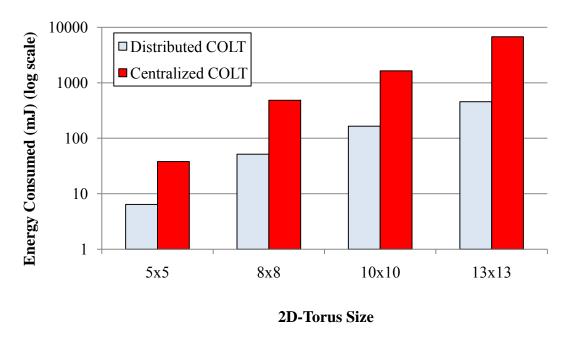

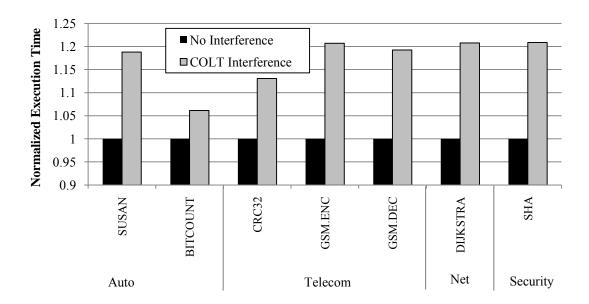

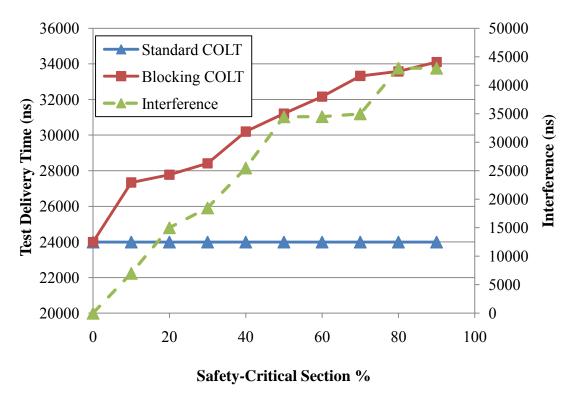

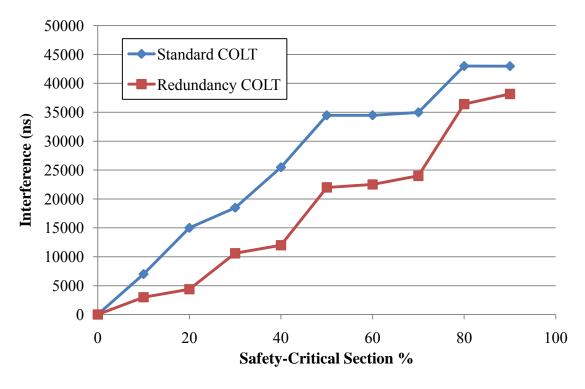

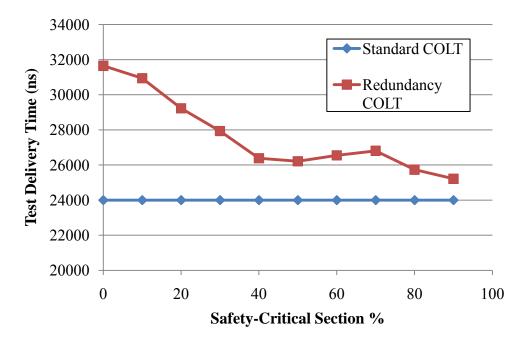

| VITA 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | REFERENC | CES                                     | 107  |