# CASE STUDIES ON CLOCK GATING AND LOCAL ROUTING FOR VLSI CLOCK MESH

A Thesis

by

## SUNDARARAJAN RAMAKRISHNAN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

August 2010

Major Subject: Computer Engineering

Case Studies on Clock Gating and Local Routing for

VLSI Clock Mesh

Copyright 2010 Sundararajan Ramakrishnan

# CASE STUDIES ON CLOCK GATING AND LOCAL ROUTING FOR VLSI CLOCK MESH

## A Thesis

by

## SUNDARARAJAN RAMAKRISHNAN

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

Approved by:

Chair of Committee, Jiang Hu Committee Members, S. Gwan Choi

Anxiao Jiang

Head of Department, Costas Georghiades

August 2010

Major Subject: Computer Engineering

#### ABSTRACT

Case Studies on Clock Gating and Local Routing for

VLSI Clock Mesh.

(August 2010)

Sundararajan Ramakrishnan, B.E., PSG College of Technology, Coimbatore, India

Chair of Advisory Committee: Dr. Jiang Hu

The clock is the important synchronizing element in all synchronous digital systems. The difference in the clock arrival time between sink points is called the clock skew. This uncertainty in arrival times will limit operating frequency and might cause functional errors.

Various clock routing techniques can be broadly categorized into 'balanced tree' and 'fixed mesh' methods. The skew and delay using the balanced tree method is higher compared to the fixed mesh method. Although fixed mesh inherently uses more wire length, the redundancy created by loops in a mesh structure reduces undesired delay variations. The fixed mesh method uses a single mesh over the entire chip but it is hard to introduce clock gating in a single clock mesh. This thesis deals with the introduction of 'reconfigurability' by using control structures like transmission gates between subclock meshes, thus enabling clock gating in clock mesh. By using the optimum value of size for PMOS and NMOS of transmission gate (SZF) and optimum number of transmission gates between sub-clock meshes (NTG) for 4x4 reconfigurable mesh, the

average of the maximum skew for all benchmarks is reduced by 18.12% compared to clock mesh structure when no transmission gates are used between the sub-clock meshes (reconfigurable mesh with NTG =0).

Further, the research deals with a 'modified zero skew method' to connect synchronous flip-flops or sink points in the circuit to the clock grids of clock mesh. The wire length reduction algorithms can be applied to reduce the wire length used for a local clock distribution network. The modified version of 'zero skew method' of local clock routing which is based on Elmore delay balancing aims at minimizing wire length for the given bounded skew of CDN using clock mesh and H-tree. The results of 'modified zero skew method' (HC\_MZSK) show average local wire length reduction of 17.75% for all ISPD benchmarks compared to direct connection method. The maximum skew is small for HC\_MZSK in most of the test cases compared to other methods of connections like direct connections and modified AHHK. Thus, HC\_MZSK for local routing reduces the wire length and maximum skew.

### ACKNOWLEDGEMENTS

First, I would like to thank my advisor, Dr. Jiang Hu, for his continuous support and guidance throughout my thesis. He showed me different ways for approaching research problem and the need to be persistent to accomplish any goal. He has always extended his help during different stages of my thesis and I shall always thank him for that.

I would also like to thank my committee members, Dr. Gwan Choi and Dr. Anxiao Jiang, for their support throughout the course of the thesis. Also I extend my gratitude and thanks to all the staff of the Electrical and Computer Engineering Department for taking care of the administrative issues.

Besides my advisors and committee members I would like to extend my gratitude to my friends for their continuous encouragement and support during the research.

Finally, I would like to thank my parents for their unconditional support and encouragement to pursue my interests.

# NOMENCLATURE

CDN Clock distribution network

HC\_DC Direct connection method from clock sinks to nearest clock grid

HC\_MZSK Modified zero skew method to form local distribution network

HC\_M\_AHHK Modified AHHK method to form local distribution network

HC\_DC\_EXT Direct connection after elongation for wire length balancing

# TABLE OF CONTENTS

|     |            |                                                                                                             | Page                            |

|-----|------------|-------------------------------------------------------------------------------------------------------------|---------------------------------|

| ΑE  | BSTRAC     | Γ                                                                                                           | iii                             |

| ΑC  | CKNOWI     | LEDGEMENTS                                                                                                  | v                               |

| NC  | OMENCL     | ATURE                                                                                                       | vi                              |

| ΤA  | BLE OF     | CONTENTS                                                                                                    | vii                             |

| LIS | ST OF FI   | GURES                                                                                                       | ix                              |

| LIS | ST OF TA   | ABLES                                                                                                       | xi                              |

| 1.  | INTROI     | DUCTION                                                                                                     | 1                               |

| 2.  | INTERO     | CONNECT MODELING AND DELAY ANALYSIS                                                                         | 4                               |

| 3.  | IMPOR'     | TANCE OF CLOCK GATING                                                                                       | 6                               |

| 4.  | CLOCK      | DISTRIBUTION USING H-TREE                                                                                   | 9                               |

|     | 4.1<br>4.2 | Methodology of Clock Routing in H-Tree  Clock Routing in H-Tree with Clock Gating                           | 10<br>14                        |

| 5.  | CLOCK      | DISTRIBUTION USING CLOCK MESH AND H-TREE                                                                    | 21                              |

|     | 5.1<br>5.2 | Methodology of Clock Routing using Clock Mesh and H-Tree<br>Clock Distribution Network Using Reconfigurable | 24                              |

|     | 5.3        | Clock Mesh and H-Tree  Impact of the Size of the Transmission Gate between the                              | 29                              |

|     | 5.4        | Sub-Clock Meshes                                                                                            | <ul><li>37</li><li>43</li></ul> |

| 6.  |            | ENGTH MINIMIZATION FOR BOUNDED SKEW FOR CLOCK                                                               | 49                              |

|                         | Page |

|-------------------------|------|

| 7. RESULTS AND ANALYSIS | 66   |

| 8. CONCLUSION           | 72   |

| REFERENCES              | 75   |

| APPENDIX                | 81   |

| VITA                    | 83   |

# LIST OF FIGURES

| FIC | GURE | 3                                                                                                                                     | Page |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------|------|

|     | 1    | Equivalent $\Pi$ -model representation of unit length wire with resistance ( $R_a$ ) and capacitance ( $C_a$ )                        | 4    |

|     | 2    | RC ladder for linear network                                                                                                          | 5    |

|     | 3    | Clock gating in a simple sequential logic                                                                                             | 7    |

|     | 4    | H-tree with 1 level                                                                                                                   | 9    |

|     | 5    | H-tree with 2 levels                                                                                                                  | 10   |

|     | 6    | H-tree routing with wires of Manhattan distance                                                                                       | 11   |

|     | 7    | Clock routing using H-tree of level 4 for '02.in' benchmark without clock gating                                                      | 13   |

|     | 8    | Two level H-tree with level 1 clock gating                                                                                            | 16   |

|     | 9    | Two level H-tree with level 2 clock gating                                                                                            | 18   |

|     | 10   | Simple clock mesh of different levels                                                                                                 | 25   |

|     | 11   | Clock distribution network using clock mesh and H-tree                                                                                | 26   |

|     | 12   | Clock routing using clock mesh of level 5 and H-tree of level 4 for '02.in' without clock gating                                      | 27   |

|     | 13   | Clock distribution network with 2x2 reconfigurable clock mesh of level 3 with H-tree of level 2                                       | 31   |

|     | 14   | Clock distribution network with 4x4 reconfigurable clock mesh of level 3 and H-tree of level 2                                        | 34   |

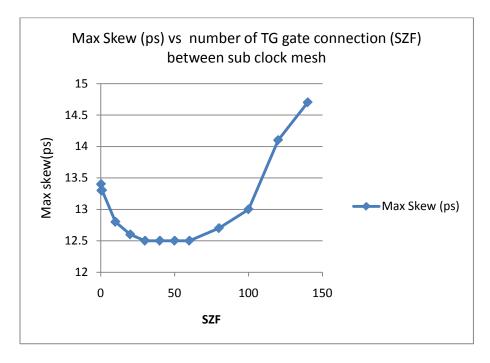

|     | 15   | Variation of the maximum skew with the change of the size of the transmission gate for 2x2 reconfigurable clock mesh for '02.in' case | 39   |

|     | 16   | Variation of the maximum skew with the change of the size of the transmission gate for 2x2 reconfigurable clock mesh for '01.in' case | 40   |

| FIGURI | E                                                                                                                                                   | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|

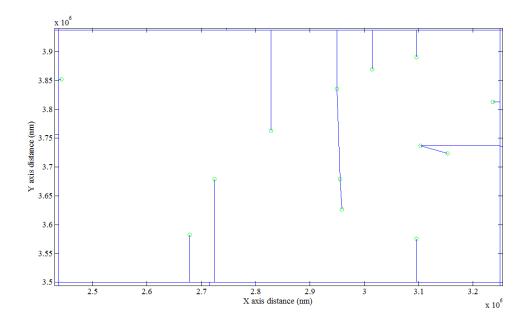

| 17     | Variation of the maximum skew with the change of the size of the transmission gate for 4x4 reconfigurable clock mesh for '02.in' case               | 42   |

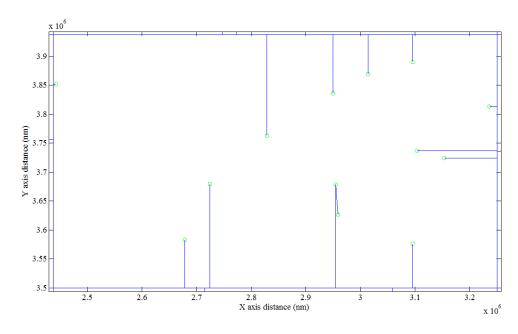

| 18     | Variation of the maximum skew with the change of the size of the transmission gate for 4x4 reconfigurable clock mesh for '01.in' case               | 42   |

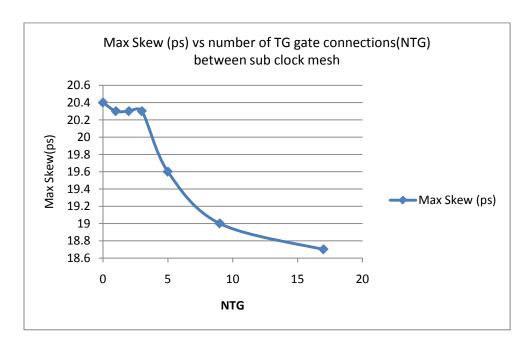

| 19     | Variation of the maximum skew with the change of the number of the transmission gate for 2x2 reconfigurable clock mesh for '02.in' case             | 44   |

| 20     | Variation of the maximum skew with the change of the number of the transmission gate for 2x2 reconfigurable clock mesh for '01.in' case             | 45   |

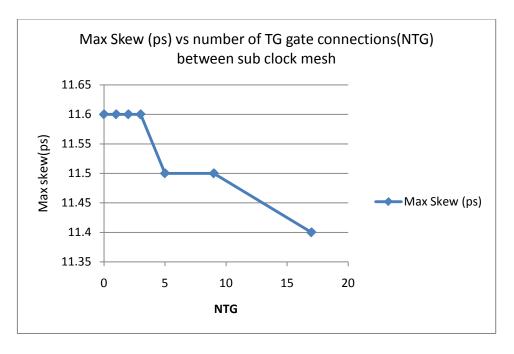

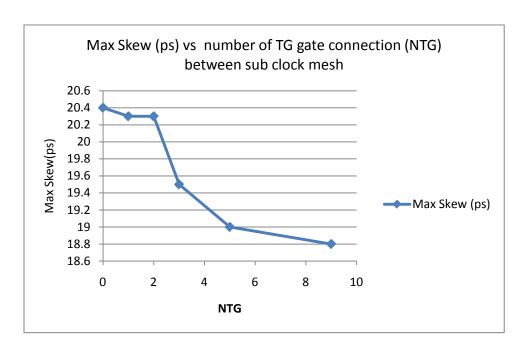

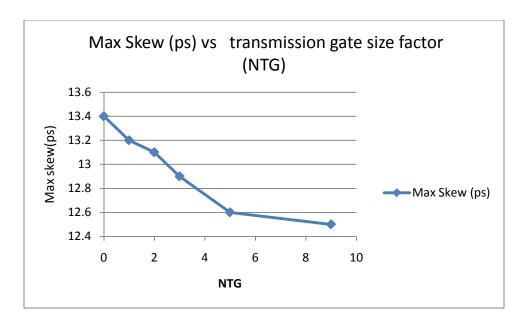

| 21     | Variation of the maximum skew with the change of the number of the transmission gate for 4x4 reconfigurable clock mesh for '02.in' case             | 46   |

| 22     | Variation of the maximum skew with the change of the number of the transmission gate for 4x4 reconfigurable clock mesh for '01.in' case             | 47   |

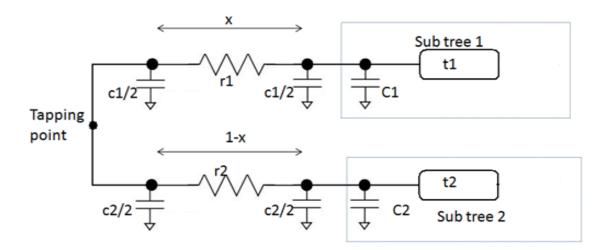

| 23     | Tapping point location between two sub-trees                                                                                                        | 50   |

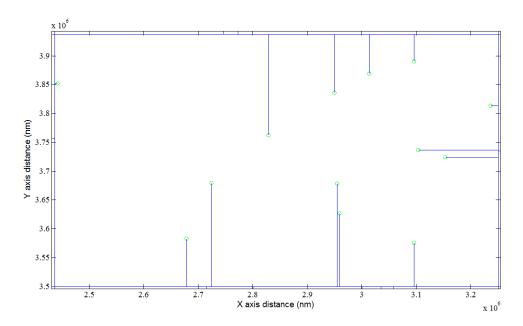

| 24     | Enlarged view of sub-block (b <sub>4,9</sub> ) of the clock mesh for ISPD '02.in' benchmark with local distribution connection using HC_DC method   | 63   |

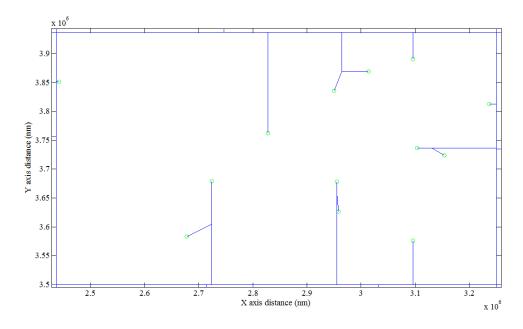

| 25     | Enlarged view of sub-block (b <sub>4, 9</sub> ) of the clock mesh for ISPD'02.in' benchmark with local distribution connection using HC_MZSK method | 64   |

| 26     | Enlarged view of sub-block (b <sub>4,9</sub> ) of clock mesh for ISPD'02.in' with local distribution connection using HC_M_AHHK method with c=0     | 64   |

| 27     | Enlarged view of sub-block (b <sub>4, 9</sub> ) of clock mesh for ISPD '02.in' with local distribution connection using HC_M_AHHK method with c=0.3 | 65   |

# LIST OF TABLES

| ΓABLE |                                                                                                                                                          | Page |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1     | Comparison of the maximum skew, average power for clock distribution network formed with only H-tree for different benchmarks of ISPD 2010               | 14   |

| 2     | Comparison of the maximum skew, average power for H-tree with level 1 clock gating                                                                       | 17   |

| 3     | Comparison of the maximum skew, average power for H-tree with level 2 clock gating                                                                       | 19   |

| 4     | Comparison of the maximum skew, average power for clock mesh with H-tree and single mesh without 'reconfigurability' for different ISPD benchmarks       | 29   |

| 5     | Comparison of the maximum skew, average power for clock mesh with H-tree for 2x2 reconfigurable mesh                                                     | 33   |

| 6     | Comparison of the maximum skew, average power for clock distribution network with H-tree and 4x4 reconfigurable clock mesh                               | 36   |

| 7     | The variation of the maximum skew, average power with the change in the size of the transmission gate for 2x2 reconfigurable clock mesh for '02.in' case | 38   |

| 8     | The variation of the maximum skew, average power with the change in the size of the transmission gate for 4x4 reconfigurable clock mesh for '02.in' case | 41   |

| 9     | Variation of the maximum skew and other parameters with the change of number of transmission gates for 2x2 reconfigurable clock mesh for '02.in' case    | 44   |

| 10    | Variation of the maximum skew and other parameters with the change of number of transmission gates for 4x4 reconfigurable clock mesh for '02.in' case    | 46   |

| 11    | Variation of the maximum skew, wire length and maximum fall time for the ISPD 2010 benchmarks 02.in, 03.in, 08.in                                        | 57   |

| ΓABLE |                                                                                                                                                              | Page |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 12    | Variation of the maximum skew, wire length and maximum fall time for the IBM benchmarks r1, r4, r5                                                           | 59   |

| 13    | Variation of the maximum skew, wire length and maximum fall time for the ISPD benchmark '02.in' by changing the density of clock mesh level and H-tree level | 60   |

| 14    | Variation of the skew, average power of the CDN formed using H-tree and single mesh with and without blockages                                               | 62   |

| 15    | Summary of comparative results                                                                                                                               | 70   |

#### 1. INTRODUCTION

Clock design is an important design step in the overall chip integration methodology and often a critical step in the fast design process. The clock is the important synchronizing element in synchronous digital system. The clock signal is distributed from an external pad to all the flip-flops and synchronizing elements through a clock distribution network (CDN). Global clock distribution networks with low difference in arrival time between different clock sinks are required in the high performance microprocessors. The difference in the clock arrival time between sink points is called the clock skew.

The clock skew is the maximum difference in the delay time from the clock source to the flip-flops. The clock skew is preferred to be less than 5% of the critical path delay time to build high performance systems, which is a very tight constraint [1]. The transistor delay used to be the main factor in affecting the performance of a system, but with the deep submicron technology, the interconnect delays makes up a large part of the overall delay [2]. Several clock routing techniques have been proposed till now which can be broadly categorized into balanced tree method and the fixed mesh method. One of the methodologies to realize the balanced tree method is to use H-tree which helps to achieve small skew [3]. The flip-flops of different sizes at different locations

This thesis follows the style of *IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems*.

increase the load at some particular H-tree leaf node and thus increases the clock skew. This restriction introduces the difficulty in keeping the H-tree symmetric and achieving small skew. In [4] by Jackson *et al.* the Method of Means and Medians (MMM) is used to divide the circuit recursively into two subsets and then connect the subset at their center of masses calculated based on the clock pin locations. This method aims at reducing the clock skew when the flip-flops are not placed symmetrically. The above method does not take into account the weight factor due to the value of capacitances each 'balanced tree method' leaf node is driving.

Further the balancing of clock routing for small skew can also be done for the two sub-clock trees based on the bottom-up approach where the skew is minimized as in the Path Delay Balancing Method [5]. The algorithms like the clustering-based algorithm reduces the total wire length used for routing along with the target of achieving smaller skew [6]. The delay and skew due to balanced tree method like H-tree is more than the fixed mesh method. Thus we can go for the fixed mesh method which uses a single mesh over the entire chip driven by a large buffer which also reduces the clock skew. However, it increases overall wire length used.

Clock routing method could use both 'balanced tree method' and clock mesh. The 'balanced tree method' will be at the higher level to distribute the clock to the lower level involving the fixed mesh. This helps to attain the advantage of both the methods. In order to provide the clock with small skew, the 'balanced tree method' like H-tree can be used at the top level and the fixed mesh can be used at the lower level. The fixed mesh is used to connect to the sink points in the clock distribution network. The work deals with

analysis of the global clock distribution using the clock mesh network and its effect on clock skew after the introduction of 'reconfigurability' in the clock mesh. The later part of the work deals with the analysis of the methods to connect the synchronous flip-flops or sink point in the circuit to the clock grids of the clock mesh in the clock distribution network.

## 2. INTERCONNECT MODELING AND DELAY ANALYSIS

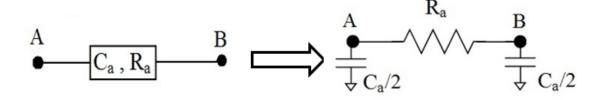

The modeling of the wires should be done with more accuracy for the correct evaluation of delay, skew and slew rate of the clock signal from the source terminal to the sink points [7]. The accuracy of the delay calculation heavily depends on the accurate modeling of the clock distribution network and the delay analysis model [8]. We have modeled the wires in the clock distribution network as distributed  $\Pi$ - model as shown in the following Figure 1.

If  $t_i$  is insulator thickness,  $\epsilon$  is dielectric permittivity and w is line width, then the capacitance per unit length (neglecting sidewall capacitance) is given by [9]

$$C_{a} = (\varepsilon * w)/t_{i}$$

(1)

Similarly if  $\rho$  is metal resistivity then the resistance per unit length is given by [9],

$$R_a = \rho / (w^*t_i) \tag{2}$$

Figure 1. Equivalent  $\Pi$ - model representation of unit length wire with Resistance ( $R_a$ ) and Capacitance ( $C_a$ )

The resistance per unit length and the capacitance of the wire are obtained based on the benchmark files and technology file being used. For example the test cases in the 'ISPD 2009' and 'ISPD 2010' benchmarks used resistance per unit length and capacitance per unit length values as 0.0001 Ohm/nm and 0.0002 fF/nm respectively. While for the IBM benchmarks, resistance per unit length and capacitance per unit length used are 0.003 Ohm/nm and 0.02 fF/nm respectively.

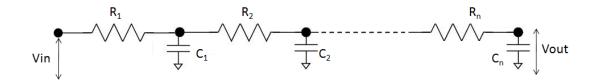

The Elmore delay of a linear network is defined as first moment of the network impulse response [10] [11]. For the RC ladder as shown in Figure 2, the Elmore delay is given by

Elmore Delay =

$$\int_0^\infty Vout(t) dt = R_1(C_1 + ... + C_n) + R_2(C_2 + ... + C_n) + ... + R_n C_n$$

(3)

Figure 2. RC ladder for linear network

The Elmore delay is used for calculating the estimate of the delay and skew while performing the local clock mesh routing using the modified zero skew routing method. However, the actual calculation of delay and skew were done using simulation of the SPICE model of the circuit using HSPICE.

#### 3. IMPORTANCE OF CLOCK GATING

The clock network distributes clock from the source to the sinks. The clock distribution network consumes a large percentage of power in modern microprocessors [12]. Major power consumption in the circuits may be due to combinational logic whose values are changing on each clock edge or power consumed by flip-flops. The latter case will have a non-zero value even if the inputs to the flip-flops and internal state of those flip-flops are not changing. Further the power consumed by clock buffers in the clock tree of the design also contributes to certain amount of power [13].

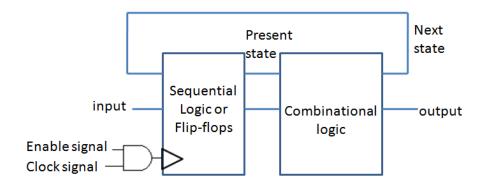

The power consumption can be reduced by using voltage scaling, reducing the load capacitance and reducing the switching activity. Since the first two are dependent mostly on technology the switching activity can be exploited to reduce the power at the logic design stage [14]. Gated clocks are better for reducing power by reducing the switching activity of logic in redundant cycles [15] [16]. The unneeded functional units at a particular time can be disabled to reduce power [17]. Clock gating has been used to reduce power by disabling the clock and thereby disabling value changes on unneeded functional units [18]. The methods like deterministic clock gating (DCG) suggests that for many of the stages in pipelined architectures of modern processors, usage of a block in a circuit is deterministically known a few cycles ahead and clock gating helps to reduce the power to a larger extent [19]. If the 'enable signals' are generated based on the switching activity then they can be used to realize clock gating to reduce power. For example in the simple sequential circuit with flip flops and combinational logic, the

clock gating can be introduced by using a simple logic 'AND' gate with inputs as clock signal and the enable signal. The output of the AND gate is the new gated clock signal. Figure 3 shows the clock gating for the simple sequential logic with enable signal.

Figure 3. Clock gating in a simple sequential logic

When the enable signal is made low then clock signal being fed to the flip-flops of the sequential logic will be disabled saving the power consumption. Similarly in order to implement clock gating for a group of flip-flops or sequential logic, they can be considered to be associated with a sub-block and enable signal can be used to realize clock gating for that sub-block. Thus the clock gating reduces the unnecessary value changes and hence reduces power consumption. The concept can be further extended to clock distribution network using H-tree and clock mesh. The global clock gating can be introduced in the H-tree by using 'AND' gate logic at the leaf nodes of the H-tree whose inputs will be the clock signal and corresponding enable signal. The clock gating in simple clock distribution network using H-tree will turn-off the flip-flops or clock sinks connected to a particular node of the H-tree. Clock mesh proves to be better in reducing

the skew and delay but introducing clock gating in a single mesh is difficult and the following sections deals with the introduction of clock gating in clock distribution network using H-tree and clock mesh in detail.

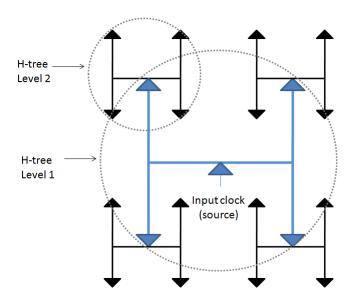

### 4. CLOCK DISTRIBUTION USING H-TREE

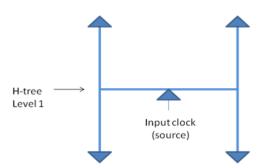

Minimization of clock skew is the main concern in the clock distribution network. H-tree structures have been used extensively for clock routing in regular systolic arrays. Single level consists of two vertical columns and one horizontal row forming an H-shaped structure is as shown in Figure 4. The k level H-tree is effective in achieving a balanced structure which helps to reduce the clock skew if the clock sinks are distributed on a  $2^k x 2^k$  array [20]. The H-tree reduces the wire length compared to the clock mesh. It also helps to achieves balanced structure at the top level unlike the rectilinear Steiner tree structure.

Figure 4. H-tree with 1 level

In order to achieve smaller skew multilevel H-tree can be used to provide the source signals to the local distribution network or the clock sinks [21]. With a single level H-tree the clock signal from the source is distributed to the four quarters of the chip. Similarly  $2^n x 2^n$  sub-blocks of the chip can be provided with the clock using n level H-tree. With increase in the number of levels the wire length required for local

distribution network is reduced and hence it helps to reduce the skew. The H-tree with '2 level' is shown in Figure 5.

Figure 5. H-tree with 2 levels

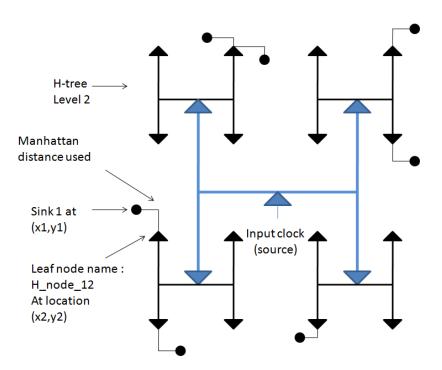

## 4.1. METHODOLOGY OF CLOCK ROUTING IN H-TREE

The H-tree structure as described can contain many levels and the leaf nodes of the final levels are used as source point for connecting the clock sinks to the H-tree. Normally the leaf nodes of the final level H-tree are connected individually to the chain of buffers whose outputs are then connected to the clock sinks or the local distribution network. Further in the description, leaf node of the H-tree usually refers to the H-tree leaf nodes which have the buffers connected to them. With n levels of H-tree we have  $2^n x 2^n$  sub-blocks. Clock sinks in the chip are connected to any leaf node of the H-tree which is nearer to them. The Manhattan distance is used to find the nearest leaf node of

the H-Tree to that particular clock sink. The distance between two points measured along axes at right angles is the Manhattan distance. In a plane with p1 at (x1, y1) and p2 at (x2, y2), the Manhattan distance is |x1 - x2| + |y1 - y2|. The length or cost of an edge in the tree is the Manhattan distance between the two endpoints of the edge and the total tree cost or length is the sum of all edge costs or length in the tree. The key idea behind connecting clock sinks to H-tree is to find the leaf node of that sub-block out of  $2^n x 2^n$  sub-blocks of H-tree which is nearer to the clock sink. The connection is made with the Manhattan distance. For instance consider the sample circuit with seven sink nodes. The clock routing using H-tree for this circuit would result in clock distribution network as shown in Figure 6.

Figure 6. H-tree routing with wires of Manhattan distance

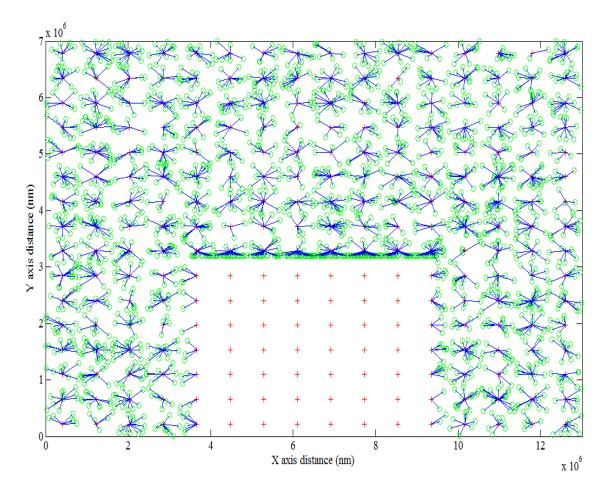

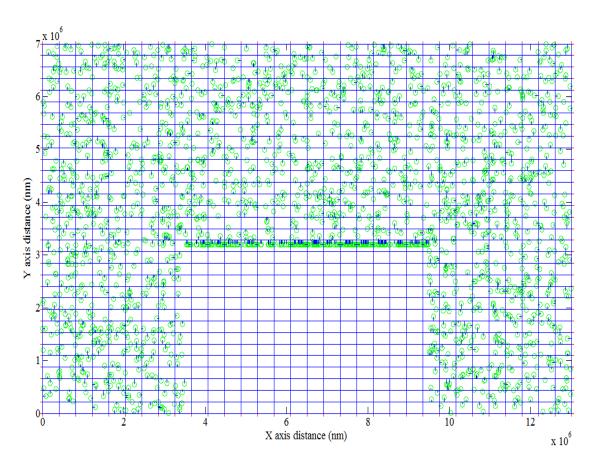

In Figure 6 sink 1 with coordinates (x1, y1) is connected to the H-tree node namely 'H\_node\_12' with coordinates (x2, y2), since 'H\_node\_12' is the leaf node which is nearer to it. The corresponding Manhattan distance is |x1 - x2| + |y1 - y2|. Similarly the local routing is done for other sinks by connecting them to nearest H-tree node. For example in the 'ISPD 2010' test cases the benchmark '02.in' has 2249 sink points. For each of the sink points the leaf node of the H-tree which is nearer to them is determined and the HSPICE file is created representing the entire clock routing using the H-tree alone. Later section deals with clock gating which can 'switch off/on' particular sub-blocks of the chip using H-tree method. Figure 7 shows the clock routing using H-tree alone without clock gating of any sub-blocks for the ISPD 2010 benchmark '02.in'.

In Figure 7 the symbol '+' represents the connection points of all the leaf nodes of the final level H-tree with local connections from the clock sinks. The clock sinks are represented by the symbol 'o'. Here we have used 4 levels of H-tree to make the connection from the clock sinks to the leaf nodes of the final level H-tree. Although the H-tree was used to form the SPICE file of the CDN, it is not shown graphically in the Figure 7. Also the connections from clock sinks to H-tree leaf node are shown as straight connections here, but the actual Manhattan distance value is used to calculate the distance while generating the SPICE netlist file. Equivalent Π– model of the wire is used to make the connection for the length which is calculated from clock sink to the nearest leaf node of the final level H-tree. The Manhattan distance is used for length calculation. The wire length used to connect clock sinks to H-tree changes if the H-tree level is changed. It affects slew rate, the maximum skew, average power consumed for the

particular configuration of clock routing. Also size of buffers which are used at the end of the H-tree has bigger impact on the above parameters. In Figure 7, the continuous white spaces where there are no clock sinks are indicating the blockages.

Figure 7. Clock routing using H-tree of level 4 for '02.in' benchmark without clock gating

Simulations have been performed for all the 'ISPD 2010' benchmarks after forming the clock distribution network (CDN) using H-tree of level 4. The clock frequency used for simulation is 1GHz for ISPD benchmarks with 50% duty cycle. The

45nm technology file from Predictive Technology Model (PTM) is used to form buffers within the clock distribution network for each of the 'ISPD' benchmarks. Equivalent Π– model of the wire with resistance per unit length and capacitance per unit length values as 0.0001 Ohm/nm and 0.0002 fF/nm respectively were used to model the wire of specific length for H-tree and local routing in the CDN for the benchmarks. Table 1 shows the variation of the maximum skew, maximum fall time, average power and wire length for different ISPD benchmarks for the CDN using only H-tree.

Table 1. Comparison of the maximum skew, average power for clock distribution network formed with only H-tree for different benchmarks of ISPD 2010.

|       |               | Clock distribution network            |           |         |        |         |

|-------|---------------|---------------------------------------|-----------|---------|--------|---------|

|       |               | With Only H-tree without clock gating |           |         |        |         |

|       | Number of     | Max                                   | Max       | Average | Wire   | Max     |

| Bench | sinks in each | Skew                                  | Fall time | Power   | length | latency |

| marks | benchmark     | (ps)                                  | (ps)      | (mW)    | (cm)   | (ns)    |

| 01.in | 1107          | 36.1                                  | 92.49     | 343.56  | 31.5   | 1.35    |

| 02.in | 2249          | 52                                    | 138.24    | 483.92  | 55.97  | 2.42    |

| 03.in | 1200          | 19.27                                 | 44.4      | 214.09  | 6.47   | 0.68    |

| 04.in | 1845          | 11.87                                 | 27.19     | 219.46  | 12.74  | 0.69    |

| 05.in | 1016          | 15.77                                 | 35.63     | 207.44  | 9.58   | 0.69    |

| 06.in | 981           | 31.07                                 | 77.4      | 161.77  | 4.92   | 0.44    |

| 07.in | 1915          | 25.12                                 | 59.66     | 221.06  | 9.87   | 0.69    |

| 08.in | 1134          | 25.58                                 | 62.66     | 167.79  | 6.92   | 0.44    |

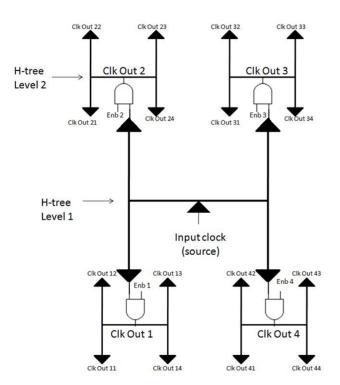

### 4.2. CLOCK ROUTING IN H-TREE WITH CLOCK GATING

The clock distribution system accounts for a large amount of power (20% to 50%) consumed by the systems [12]. Thus, in low power synchronous systems the power consumed must be reduced subject to the various constraints like keeping the

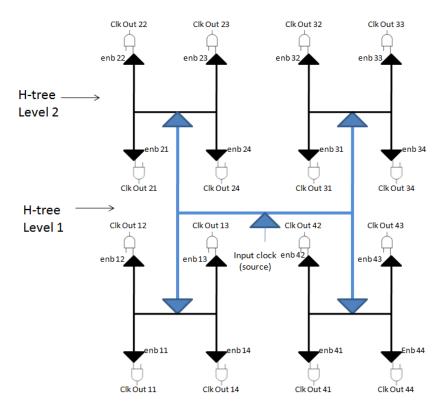

clock skew, clock slew rate under the required bounded values. In the global clock distribution using the H-tree the clock gating can be introduced at different levels of H-tree. Additional control signals and gates are required to perform clock gating which implies that there exists a tradeoff between the amount of clock tree gating and the total power consumption of the clock tree [12]. The activity-driven clock trees have been previously analyzed for performing the clock gating [12]. In our implementation the clock distribution network from H-tree of Figure 6 can be converted to a structure with level 1 clock gating by introducing the control signals enb1, enb2, enb3, enb4 with control logic for the four quarters of the chip. The control logic used here is a logic AND gate with enable signals. The 45nm technology file is used for constructing control logic and buffers for the 'ISPD' benchmarks. Figure 7 shows H-tree of two levels with level 1 clock gating.

With the level n clock gating there are 2<sup>n</sup>x2<sup>n</sup> sub-blocks which can be clock gated in an H-tree with n or more levels. For example in Figure 8, we have 2 level of H-tree and one level of clock gating. Hence the four quadrants of the chip, controlled by the control signals enb1, enb2, enb3, and enb4 can be clock gated. If the enb1 is made low then all the signals 'Clk out 21', 'Clk out 22', 'Clk out 23', 'Clk out 24' including the 'Clk out 2' signals are made low. All lower levels H-trees and clock sinks connected to the above terminals or the lower level H-trees (if the H-tree levels considered are greater than two) are also switched off. Thus the clock gating helps to switch off that particular sub-block controlled by that particular enable signal.

The granularities at which we can switch off the particular nodes are determined by the number of levels of clock gating. In Figure 8 four sub-blocks can be clock gated individually. The granularity can be increased by increasing the number of levels of clock gating. H-tree with one level of clock gating is shown in Figure 8. Therefore, there are 2x2 sub-blocks to clock gate (2 "x2" sub-blocks for n levels of clock gating). It can be referred to as H-tree with 2x2 clock gating.

The results for simulations performed for the test case '02.in' corresponding to 'ISPD 2010' benchmark are as shown in Table 2. Totally 4 levels of H-tree are used with level 1 clock gating (2x2 clock gating).

Figure 8.Two level H-tree with level 1 clock gating

From the results it can be seen that the maximum skew is in the range of 50ps, while there are reasonable decreases in the power value with increase in the number of sub-blocks which are clock gated or switched off. The power dissipation is still there when none of the sub-blocks are ON which is because of the power dissipation in buffers and the wire used for first level of the H-tree. It can be seen that variance in the value of the maximum skew is small with change in the number of sub-blocks which are switched ON. There is power saving with the number of blocks which are turned off. Also using enable signals there is greater flexibility in controlling the number of sub-blocks which are turned off. In order to get more flexibility/granularity in clock gating we can use clock mesh of higher clock gating levels.

Table 2. Comparison of the maximum skew, average power for H-tree with level 1 clock gating

| Benchmark               | Clock distribution network                    |                      |                  |             |                 |

|-------------------------|-----------------------------------------------|----------------------|------------------|-------------|-----------------|

| 02.in                   | Only H-tree with 2x2 clock gating (level = 1) |                      |                  |             |                 |

| Number of sub-blocks ON | Maximum<br>Skew (ps)                          | Maximum<br>Fall time | Average<br>Power | Wire length | Maximum latency |

|                         | bkew (ps)                                     | (ps)                 | (mW)             | (cm)        | (ns)            |

| 0                       | -                                             | -                    | 32.31            | 55.97       | -               |

| 1                       | 49.7                                          | 138.24               | 144.43           | 55.97       | 2.42            |

| 2                       | 49.7                                          | 138.24               | 258.68           | 55.97       | 2.42            |

| 3                       | 51.1                                          | 138.25               | 373.75           | 55.97       | 2.42            |

| 4                       | 52                                            | 138.24               | 483.92           | 55.97       | 2.42            |

The H-tree with two levels of clock gating is as shown in Figure 9. For the 2 level H-tree with two level of clock gating, the clock gating can be done with more

granularities since number of sub-blocks which can be clock gated increases. Also the size of the sub-block which can be clock gated decreases for a give benchmark with same level of H-tree.

In Figure 9 if 'enb 22' signal is made low then local distribution network connected to 'Clk Out 22' are switched off. Since there are more number of enabling signals to control clock gating hence the granularity of the clock gating is more. Similarly in Figure 9 the level 2 clock gating is shown and it can be referred to as H-tree with 4x4 clock gating. Simulations have been performed for the test case '02.in' corresponding to 'ISPD 2010' benchmark. The results are as shown, in Table 3.

Figure 9.Two level H-tree with level 2 clock gating

Table 3. Comparison of the maximum skew, average power for H-tree with level 2 clock gating

| Benchmark     | Clock distribution network                    |           |            |             |         |  |

|---------------|-----------------------------------------------|-----------|------------|-------------|---------|--|

| 02.in         | Only H-tree with 4x4 clock gating (level = 2) |           |            |             |         |  |

|               | Max                                           | Max Fall  | Average    | Wire length | Max     |  |

| Number of     | Skew                                          | time (ps) | Power (mW) | (cm)        | latency |  |

| sub-blocks ON | (ps)                                          |           |            |             | (ns)    |  |

| 0             | 1                                             | -         | 80.41      | 55.97       | 1       |  |

| 1             | 48.4                                          | 138.24    | 107.72     | 55.97       | 2.42    |  |

| 2             | 50.2                                          | 138.24    | 128.38     | 55.97       | 2.42    |  |

| 3             | 50.2                                          | 138.24    | 153.38     | 55.97       | 2.42    |  |

| 4             | 50.3                                          | 138.24    | 174.19     | 55.97       | 2.42    |  |

| 5             | 50.3                                          | 138.24    | 199.55     | 55.97       | 2.42    |  |

| 6             | 50.3                                          | 138.24    | 224.53     | 55.97       | 2.42    |  |

| 7             | 50.3                                          | 138.24    | 249.79     | 55.97       | 2.42    |  |

| 8             | 52                                            | 138.24    | 279.63     | 55.97       | 2.42    |  |

| 9             | 38.8                                          | 99.58     | 302.18     | 55.97       | 2.4     |  |

| 10            | 38.8                                          | 99.58     | 329.1      | 55.97       | 2.4     |  |

| 11            | 38.8                                          | 99.58     | 354.28     | 55.97       | 2.4     |  |

| 12            | 52                                            | 138.24    | 379.85     | 55.97       | 2.42    |  |

| 13            | 52                                            | 138.24    | 406.23     | 55.97       | 2.42    |  |

| 14            | 52                                            | 138.25    | 431.25     | 55.97       | 2.42    |  |

| 15            | 52                                            | 138.24    | 451.49     | 55.97       | 2.42    |  |

| 16            | 52                                            | 138.24    | 477        | 55.97       | 2.42    |  |

Since there are 16 sub-blocks, Table 3 shows variation of the maximum skew, the maximum fall time and average power with the number of sub-blocks which can be clock gated in the H-tree. The maximum skew corresponding to the values of 9, 10 and 11 in the 'number of sub-blocks ON' is less than skew for other values since the clock sink corresponding to the maximum skew is in the sub-block which is switched off for the above configurations. There is a variation in the maximum fall time for the above

cases because of the uneven loading due to the clock sinks at all the leaf nodes of the Htree for the present configuration.

For the values of 9, 10 and 11 in the 'number of sub-blocks ON', the maximum fall time is less since the H-tree leaf node with maximum loading is switched off. Thus the maximum fall time corresponding to these configurations does not include the clock sinks which would have, otherwise, contributed to the increase in the maximum clock fall time. Those clock sinks have been disabled by clock gating.

## 5. CLOCK DISTRIBUTION USING CLOCK MESH AND H-TREE

Although H-tree structure helps to reduce clock skew, it is efficient and applicable only when the clock sinks or synchronizing components are identical in size and are placed in a symmetric array. The clock mesh consists of the horizontal and vertical clock grids to which either local distribution network is connected or clock sinks are directly connected. The Manhattan distance can be used to connect local clock distribution network or clock sinks to the closest clock grid. Row clock grid in the clock mesh runs from left to right and column clock grid runs from bottom to top of the mesh. A 'mesh grid node' is the point where a column is connected to a row [22]. The top, bottom, left and right clock grids along with the four mesh grid nodes at corners form the sub-block/sub-grid of the clock mesh. Clock sinks found within the four 'mesh grid nodes' correspond to that particular sub-grid/sub-block. A local distribution network can be formed within sub-grids/sub-blocks in a clock mesh. For example if a clock mesh has number of rows and columns as 17 and 17 respectively then total number of sub-blocks is16x16. Since H-tree is considered to distribute the clock from the source to the clock grid, we can assume the clock mesh to be consisting of equal number of rows and columns.

The non-tree clock network has been recognized as a good approach to minimize the problems due to variation [23]. A mesh structure is better than a tree structure at coping with process variations, since the mesh has more local connections and the regenerated signals coming from different local connections help to smooth out the local delay variations and yield a smaller clock skew [21]. Thus, clock mesh-based structures like clock mesh, clock spines and cross links are more effective in reducing the variations on clock skew due to environmental variations effects [24]. Some of the commercial processors like first generation Itanium [25], IBM Power 4 [26], Sun Microsystems Dual Core Sparc V9 [27] and IBM Power 6 [28] microprocessors use clock mesh to reduce clock skew due to variations and design mismatch.

The microprocessor designs in many cases dissipate larger fraction of the microprocessor chip power in global clock distribution network [29] [12]. Also the interconnects haven't scaled as well as the devices hence it is necessary for the microprocessors to locally buffer the clock signals to maintain the required slew rate. In order to reduce most of power dissipation due to clock distribution network, efficient clock gating techniques are needed to turn off the local clock distribution networks when they are not being used. Most of the power dissipation is due to the gate capacitances of latches or clock sinks and due to the capacitances of the wire used for the local clock distribution. However, care must be taken to make sure that the clock skew is not increased by large amount after reducing the power using clock gating techniques.

Most of the clock distribution network designing techniques aims at reducing the clock skew, slew rate, and jitter. Undesired variations in cycle time period are called jitter. The jitter will reduce performance because the cycle time will be short and chip frequency must be slowed down to avoid long path errors [29]. Most of the clock distribution network is buffered at many levels. If these buffers are using relatively noisy Vdd and Gnd then much of the clock jitter will be from the buffer delay variations in

clock distribution network due to power supply noise [30]. In our analysis the clock signal is considered to be jitter free.

The normal clock distribution technique to get small skew consists of using a clock distribution network with many levels of H-tree connected to single clock mesh [31]. Clock network consists of buffered trees with the final level of trees driving a single common grid covering most of the chip. This combines the advantage of both the tree structure and the clock mesh. Clock tree has advantages like low power, low latency and minimal usage of wiring track. Without the grid, trees must often be rerouted whenever location of clock pins change or when value of the load capacitances change significantly [31]. Since the clock mesh provide a regular structure hence the routing would be easier from the clock sink to the nearest grid even if the position of the clock sink changes. Local routing track would be simpler with the clock mesh for clock sinks. Also when the single mesh is used the regenerated clock signals from the different parts of the mesh helps to improve the clock slew rate and the maximum clock skew.

Thus in the simplest form clock distribution network consist of symmetric H-tree driving a single mesh and local distribution network of the clock sinks within the sub-block of clock mesh. The grid reduces local skew by connecting nearby points directly. The tree wires are then tuned to minimize skew over longer distances [31]. The size of the buffers used at the leaf nodes of the H-tree driving the clock mesh also affects the global skew, local skew and clock slew rate. In our work the buffer sizes have been varied to find the optimum value which gives minimum slew rate and clock skew for all the benchmarks.

#### 5.1. METHODOLOGY OF CLOCK ROUTING USING CLOCK MESH AND H-TREE

Clock distribution network using clock mesh has got inherent routing redundancies which leads to improvement in clock skew and reliability [32]. The variation tolerance of a leaf-level mesh is a direct result of its high redundancy, with multiple sources to sink paths for every sink [31]. Thus clock mesh with local distribution network forms the lower level of the clock distribution network while the upper H-tree helps to distribute the signal to clock mesh from the clock input source.

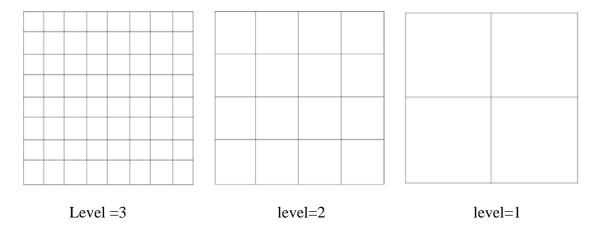

For forming the clock mesh and H-tree, Equivalent  $\Pi$ - model of the wire of specific length with resistance per unit length ( $R_a$ ) and capacitance per unit ( $C_a$ ) as shown in Figure 1 can be used for Spice simulation. Basic structure of clock mesh consists of horizontal rows and vertical columns of clock grids which are having connections at the 'mesh grid node'. The clock mesh is characterized based on the number of levels. The clock mesh is said to be of level n if it has  $2^n x 2^n$  sub-blocks/subgrids and there are ( $2^n+1$ ) rows of clock grids and ( $2^n+1$ ) columns of clock grids in the clock mesh.

For example the clock mesh structure with level 1, level 2 and level 3 are shown in Figure 10. Clock mesh with level 1 has 4 sub-blocks (2x2) while the clock mesh with level 3 has  $2^3x2^3$  (8x8) sub-blocks. With more levels in the clock mesh the local distribution network required for the clock sinks within the sub-blocks will be lower and it helps to improve clock slew rate and hence the clock skew. In order to assure a more uniform distribution of clock signals to clock grids, connection from H-tree to clock mesh is made at 'mesh grid nodes' in a more uniform fashion.

Figure 10. Simple clock mesh of different levels

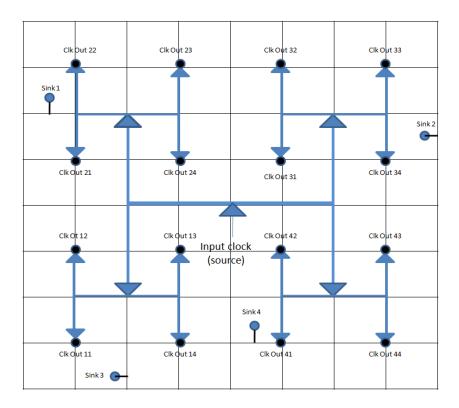

If the clock grid is of level 3 then there are 9 rows of clock grid and 9 columns of clock grids which are connected at the 81 specific nodes called mesh grid nodes. The above structure consists of 8x8 sub-blocks. The clock sinks within the sub-blocks can be connected to the nearest clock grids which form the local distribution networks. Clock distribution network considered have regular single clock mesh and top level H-tree. Thus, if the H-tree considered is of level n then clock mesh is considered to be of level (n+1) to make uniform connections from H-tree to clock mesh and it also helps to make the structure as a reconfigurable one when introducing clock gating for the sub-blocks in the clock mesh. Each clock sink receives signal from the nearby lowest level H-tree leaf nodes and also the regenerated signals from the other leaf nodes of the H-tree. Hence, this structure creates high redundancy with various paths from source to the sink for every sink [22]. Consider Figure 11 with clock grid of structure 8x8 sub-blocks (level 3) and H-tree of level 2. The connection of H-tree leaf nodes are made to the clock mesh at some of the 'mesh grid nodes' indicated by the black dots/marks in Figure 11. The

sample circuit is considered to have got 4 clock sinks. Local connection for clock sinks within sub-blocks is made using a direct connection from the clock grid to the clock sink.

Figure 11. Clock distribution network using clock mesh and H-tree

The method for forming the entire clock distribution network including H-tree, clock mesh, and local clock sink connections is done in Matlab which generates HSPICE compatible file. The HSPICE file represents the entire clock distribution network along with clock sinks. Simulations were performed to calculate the maximum clock skew, the maximum rise/fall time and latency for a given benchmark. The method designed to

form the clock mesh for the 'ISPD 2010' and 'ISPD 2009' benchmarks determines the optimum number of H-tree and clock mesh level required to achieve the required clock skew for that particular benchmark. Also concern is given to the minimum number of clock sinks which must be present within the particular sub-block. Hence the variation in the load distribution in each of the sub-blocks is small.

Figure 12. Clock routing using clock mesh of level 5 and H-tree of level 4 for '02.in' without clock gating

In 'ISPD 2010' test cases the benchmark '02.in' has 2249 sink points. For each of the sink points nearest clock grid is found along with distance. The connection is

made from that clock sink to the grid. Clock routing is done which has the H-tree, clock mesh and local distribution network from the clock sinks to the clock grid. Figure 12 shows the clock distribution network for the test case '02.in' in the ISPD 2010 benchmark. Although the H-tree was used to form the HSPICE netlist but it is not shown graphically in the Figure 12.

In Figure 12 the symbol '+' represents the connection points of all the leaf nodes of the final level H-tree to the clock grid and the local connections from the clock sinks to the nearest clock grid is done using direct connections. Clock sinks are represented by the symbol 'o'. Here we have used up to 4 levels of H-tree and clock mesh with 5 levels. Thus there are 32x32 sub-blocks in the clock mesh structure. This is a simple clock mesh without reconfigurable mesh. The clock gating can be done in these structures by using reconfigurable clock mesh as described in the following sections.

With the H-tree and single clock mesh forming the base structure of the clock distribution network it is not possible to clock gate the single sub-block since the regenerated signals from the neighboring clock grids will reach the clock sinks. The sub-blocks which have been clock gated haven't been disconnected from the connections with the neighboring clock grid's wires. Therefore, there is requirement of the introducing 'reconfigurability' in the clock mesh which enables clock gating in the clock mesh and at the same time tries to integrate the advantage of both the H-tree and clock mesh. Table 4 shows the variation of the maximum skew, the maximum fall time, average power, wire length and the maximum latency for different ISPD benchmarks for the clock distribution network using single clock mesh and H-tree.

Table 4. Comparison of the maximum skew, average power for clock mesh with H-tree and single mesh without 'reconfigurability' for different ISPD benchmarks

|           | Clock distribution network           |                       |                       |                  |                     |  |  |  |

|-----------|--------------------------------------|-----------------------|-----------------------|------------------|---------------------|--|--|--|

|           | With Single mesh and H-tree combined |                       |                       |                  |                     |  |  |  |

| Benchmark | Max<br>Skew<br>(ps)                  | Max Fall<br>time (ps) | Average<br>Power (mW) | Wire length (cm) | Max<br>latency (ns) |  |  |  |

| 01.in     | 11                                   | 45.31                 | 424.29                | 75.29            | 1.33                |  |  |  |

| 02.in     | 16.9                                 | 66.26                 | 542.04                | 96.84            | 2.39                |  |  |  |

| 03.in     | 2.52                                 | 17.75                 | 227.25                | 15.24            | 0.67                |  |  |  |

| 04.in     | 3.93                                 | 20.77                 | 238.58                | 23.86            | 0.68                |  |  |  |

| 05.in     | 2.85                                 | 18.04                 | 229.54                | 22.92            | 0.68                |  |  |  |

| 06.in     | 4.11                                 | 17.02                 | 174.75                | 12.75            | 0.41                |  |  |  |

| 07.in     | 5.75                                 | 21.37                 | 235.03                | 18.91            | 0.68                |  |  |  |

| 08.in     | 5.35                                 | 18.99                 | 183.23                | 16.27            | 0.42                |  |  |  |

# 5.2. CLOCK DISTRIBUTION NETWORK USING RECONFIGURABLE CLOCK MESH AND H-TREE

The mesh structure helps to achieve smaller skew compared to clock routing using H-tree only. Hence it is used at the lowest level of the clock tree. In the clock mesh when a signal is delayed in relation to the others, it is compensated by redundant paths [33]. In low power applications some parts of the clock tree can be turned off by clock gating some part of clock distribution network using H-tree only structure. In a clock distribution network with single clock mesh and multilevel H-tree the clock gating will have problem because the redundancy created by the loops will cause the signals from other parts of the mesh to reach the sub-block which is switched off after clock gating.

Thus, there is a need for changing the structure of single clock mesh which will exploit the advantage of redundancy of the signals in mesh structure and also isolate and

turn off some portions of the mesh when the clock gating is enabled (switched off) for that sub-block/sub-grid of the mesh. Similar to single clock mesh, reconfigurable clock mesh is distributed with clock signal from the top level H-tree. The main idea behind the 'reconfigurability' is to introduce control structures that will establish the connection with other neighboring sub-blocks of the clock mesh when clock gating is enabled for that sub-block and if clock gating is disabled later, then isolate and switch off that particular clock grid from other clock grids.

The PMOS or NMOS can be used as control unit. However, the usage of the transmission gate has advantage over the usage of the either NMOS or PMOS separately. Transmission gate consists of a NMOS transistor and a PMOS transistor in parallel with gates controlled by complementary signals. When transmission gate is ON, at least one of the two transistors is ON for any output voltage and hence it conducts both '0' and '1' well. If the transmission gate is used as the controlling structure between two sub-blocks then transmission gate normally acts as a voltage controlled resistor connecting the input and the output.

The clock mesh of level 3 has 8x8 sub-blocks in the clock mesh. With 2x2 'reconfigurability', we have 4 'sub-clock meshes' separated and controlled by the transmission gate. The resulting clock distribution network is as shown in Figure 13. H-tree with 'level 2' is used to distribute clock signal to clock mesh. Since H-tree has clock gating of level 1, a 2x2 reconfigurable mesh is formed with the control signals enb1, enb2, enb3, enb4. The sub-clock meshes in the four quadrants of the entire chip area are connected by control units (transmission gates) with control signal pairs like

'and\_enb1\_enb2' and 'nand\_enb1\_enb2' etc as shown in Figure 13. Extra control logic is needed to generate control signals. Signal pair like 'and\_enb1\_enb2' and 'nand\_enb1\_enb2' is generated by using the logic 'AND' and 'NAND' gates respectively with control inputs 'enb1' and 'enb2'. Similarly other signals like 'and\_enb2\_enb3', 'nand\_enb2\_enb3', 'and\_enb3\_enb4', 'nand\_enb3\_enb4', 'and\_enb4\_enb1', and 'nand\_enb4\_enb1' can also be generated.

Figure 13. Clock distribution network with 2x2 Reconfigurable clock mesh of level 3 with H-tree of level 2

For example when a sub-block controlled by 'enb1' signal is turned off then control signals corresponding to 'enb1' are 'and\_enb1\_enb2', 'nand\_enb1\_enb2', 'and\_enb4\_enb1' and 'nand\_enb4\_enb1' will have logic values of 0, 1, 0, 1 respectively. This will make corresponding transmission gates to be in switched off mode. Thus corresponding 'sub-clock mesh' is completely isolated from other sub-clock meshes. When there is a requirement to turn on the same sub-clock mesh then 'enb1' signal is made logic 1. The transmission gates will be switched ON again. And the 'sub-clock mesh' is now connected to the other sub-clock meshes using the transmission gate. In Figure 13 only an 8x8 clock mesh has been considered with 2x2 'reconfigurability', where each sub-clock meshes is connected to neighboring sub-clock meshes by only two transmission gates. In later sections the effect of changing the number of transmission gates (control units) will be discussed and also the effect of changing size of PMOS and NMOS of the transmission gate will be discussed.

Table 5 shows the comparison of the maximum skew, average power for clock distribution network with 2x2 reconfigurable clock mesh of level 5 with H-tree of level 4 for the test case '02.in' of ISPD 2010 benchmark. This is the largest benchmark in ISPD 2010 test cases with more number of sinks. It can be seen that there is not much variation in skew unlike clock routing structure with H-tree only. The maximum skew is in the range of 20 ps which is much less than the value for the structure with H-tree of similar configuration as shown in Table 2. Same configuration is used for simulating both the structures. Latency of both structures is very similar. However, the wire length used for clock mesh is greater than the wire length used for CDN with H-tree only.

In Table 5 it can be seen that there is reduction in the power with clock gating based on the number of sub-clock meshes being clock gated. For the value of 0 in the column of 'Number of sub-clock meshes ON' in Table 5 the power dissipation is due to the power accounting to first level of the H-tree which is consuming power even if all the clock meshes are turned off. The results calculated for the other benchmarks showed very similar trend.

Table 5. Comparison of the maximum skew, average power for clock mesh with H-tree for 2x2 reconfigurable mesh

| Benchmark | Clock distribution network |                                                                                            |         |       |      |  |  |  |  |  |

|-----------|----------------------------|--------------------------------------------------------------------------------------------|---------|-------|------|--|--|--|--|--|

| 02.in     | H-tree and 2               | H-tree and 2x2 reconfigurable mesh with clock gating (level =1) and SZF =1 and NTG=17/side |         |       |      |  |  |  |  |  |

| Number of | Max Skew                   | Max Fall                                                                                   | Average | Wire  | Max  |  |  |  |  |  |

| sub-clock | (ps)                       | (ps) time (ps) Power length latency                                                        |         |       |      |  |  |  |  |  |

| meshes ON |                            |                                                                                            | (mW)    | (cm)  | (ns) |  |  |  |  |  |

| 0         | 0                          | 0                                                                                          | 32.4    | 98.94 | 0    |  |  |  |  |  |

| 1         | 20.2                       | 76.75                                                                                      | 159.62  | 98.84 | 2.46 |  |  |  |  |  |

| 2         | 20.4                       | 76.75                                                                                      | 288.49  | 98.84 | 2.46 |  |  |  |  |  |

| 3         | 20.3                       | 20.3 76.33 417.7 98.84 2.46                                                                |         |       |      |  |  |  |  |  |

| 4         | 20.2                       | 76.3                                                                                       | 544.14  | 98.84 | 2.46 |  |  |  |  |  |

The above design deals with reconfigurable mesh with four 'sub-clock meshes' at the four quadrants of the chip area. They are connected to other sub-clock meshes and connection establishments are controlled using transmission gates. Hence only four sub-clock meshes can be turned on or turned off based on clock gating signals. Granularity

of controlling the clock gating can be increased by making the clock mesh as reconfigurable structure with 16 'sub-clock meshes' instead of only 4 sub-clock meshes.

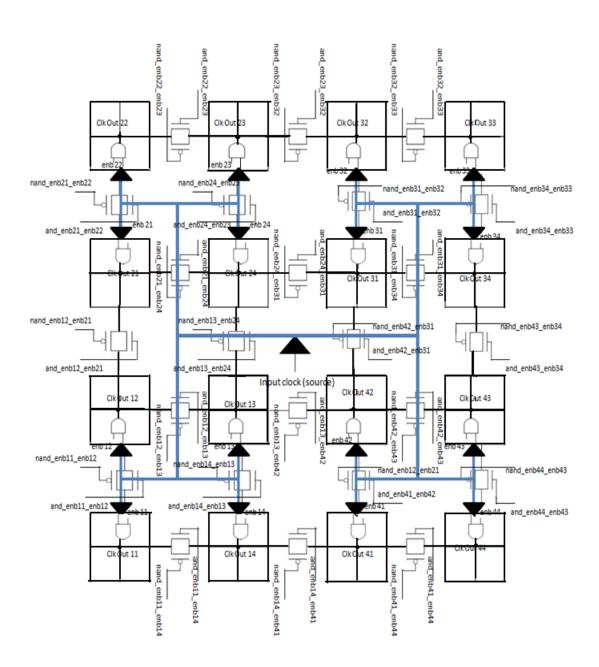

Figure 14. Clock distribution network with 4x4 reconfigurable clock mesh of level 3 and H-tree of level 2

Clock distribution network with 4x4 reconfigurable clock mesh of level 3 and H-tree of level 2 can be formed as shown in Figure 14 with 16 sub-clock meshes. Although the control logic required for creating the control signals have increased exponentially the clock gating can now be done with more granularity compared to the clock distribution network with 2x2 reconfigurable clock mesh. Here NTG is number of transmission gate connections for each sub-blocks and SZF is the transmission gate size factor which will be explained in the following sections.

In Figure 14 the clock mesh structure has 16 sub-clock meshes and there is a requirement of 16 enable signals. Also the number of transmission gates has increased. Transmission gate control signals are generated from logic 'AND' gates and 'NAND' gates. For example, control signals corresponding to the sub-clock mesh controlled by the output of H-tree 'Clk out 11' are 'and\_enb11\_enb14', 'nand\_enb11\_enb14', 'and\_enb11\_enb12' and 'nand\_enb11\_enb12'. If the 'enb 11' signal is at logic 0, then above control signals will switch off the transmission gate and will isolate corresponding 'sub-clock mesh' from the rest of the 'sub-clock meshes'. Similarly clock gating can be performed for the rest of the 'sub-clock meshes' to achieve reduction in power consumption.

There is possibility of increasing the granularity of clock mesh 'clock gating' from 4x4 to 8x8 which would give more flexibility in turning on or turning off particular sub-clock mesh of smaller size. For very low power applications, this might be of great use to reduce power. Table 6 shows the comparison of the maximum skew, average power for clock distribution network with H-tree and 4x4 reconfigurable clock mesh for

the test cases '02.in' of 'ISPD 2010' benchmark . H-tree level considered is of 'level 4' and the clock mesh considered has level 5 with 32x32 (2<sup>5</sup>x2<sup>5</sup>) sub-blocks. However, from Table 5 and Table 6 it can be inferred that the maximum fall time in Table 6 is greater than that of Table 5 by a small percentage. This is because of increase in 'reconfigurability' levels and introduction of more number of transmission gates, instead of direct connection of sub-clock meshes using wires as in single mesh.

Table 6. Comparison of the maximum skew, average power for clock distribution network with H-tree and 4x4 reconfigurable clock mesh

| Benchmark      |                                  | Clock distribution network                                 |        |        |         |  |  |  |  |  |  |

|----------------|----------------------------------|------------------------------------------------------------|--------|--------|---------|--|--|--|--|--|--|

|                | H-tree a                         | H-tree and 4x4 reconfigurable clock mesh with clock gating |        |        |         |  |  |  |  |  |  |

| 02.in          | (level =2) SZF =1 and NTG=9/side |                                                            |        |        |         |  |  |  |  |  |  |

| Number of sub- | Max Max Fall Average Wire M      |                                                            |        |        |         |  |  |  |  |  |  |

| blocks/sub-    | Skew                             | time (ps)                                                  | Power  | Length | latency |  |  |  |  |  |  |

| clock meshes   | (ps)                             |                                                            | (mW)   | (cm)   | (ns)    |  |  |  |  |  |  |

| ON             |                                  |                                                            |        |        |         |  |  |  |  |  |  |

| 0              | 0                                | 0                                                          | 80.55  | 102.84 | 0       |  |  |  |  |  |  |

| 1              | 17.4                             | 77.79                                                      | 110.53 | 102.84 | 2.46    |  |  |  |  |  |  |

| 2              | 19.2                             | 77.78                                                      | 137.05 | 102.84 | 2.46    |  |  |  |  |  |  |

| 3              | 20.3                             | 77.79                                                      | 166.13 | 102.84 | 2.46    |  |  |  |  |  |  |

| 4              | 20.3                             | 77.78                                                      | 192.77 | 102.84 | 2.46    |  |  |  |  |  |  |

| 5              | 20.3                             | 77.79                                                      | 222.07 | 102.84 | 2.46    |  |  |  |  |  |  |

| 6              | 20.4                             | 77.79                                                      | 251.16 | 102.84 | 2.46    |  |  |  |  |  |  |

| 7              | 20.4                             | 77.79                                                      | 280.44 | 102.84 | 2.46    |  |  |  |  |  |  |

| 8              | 20.3                             | 77.23                                                      | 312.51 | 102.84 | 2.46    |  |  |  |  |  |  |

| 9              | 16.3                             | 66.22                                                      | 340.11 | 102.84 | 2.45    |  |  |  |  |  |  |

| 10             | 16.4                             | 66.59                                                      | 370.63 | 102.84 | 2.46    |  |  |  |  |  |  |

| 11             | 16.4                             | 66.6                                                       | 399.82 | 102.84 | 2.46    |  |  |  |  |  |  |

| 12             | 20.4                             | 77.22                                                      | 429.04 | 102.84 | 2.46    |  |  |  |  |  |  |

| 13             | 20.3                             | 77.21                                                      | 458.99 | 102.84 | 2.46    |  |  |  |  |  |  |

| 14             | 20.4                             | 77.72                                                      | 488.16 | 102.84 | 2.46    |  |  |  |  |  |  |

| 15             | 20.3                             | 77.2                                                       | 514.37 | 102.84 | 2.46    |  |  |  |  |  |  |

| 16             | 20.3                             | 77.2                                                       | 544.84 | 102.84 | 2.46    |  |  |  |  |  |  |

Table 3 gives the results for the clock distribution network using H-tree with level 2 clock gating. Comparing Table 3 with Table 6, it can be inferred that the maximum skew value for the clock distribution network corresponding to Table 6 is very small compared to the maximum skew in Table 3.

Thus reconfigurable mesh combines both the advantage of clock mesh and H-tree with the capability of clock gating. Thus it guarantees small skew. However, average power for the clock distribution network using clock mesh with 4x4 "reconfigurability" is slightly higher than the power value for clock distribution network formed using H-tree with level 2 clock gating. The following sections deal with impact of the number of transmission gates (control units) between each of the sub-clock meshes and the impact of the size of the PMOS and NMOS of the transmission gate.

# 5.3. IMPACT OF THE SIZE OF THE TRANSMISSION GATE BETWEEN THE SUB-CLOCK MESHES

The transmission gates between sub-clock meshes in reconfigurable clock meshes provide controllability for isolating and clock gating particular sub-clock meshes from the others. In the above case, impact due to the size of the transmission gate will give more insight into the requirement for introducing transmission gates between the sub-clock meshes. In transmission gate structure we consider the size of PMOS to be twice the size of the NMOS. In our analysis the size of PMOS and NMOS is varied by changing the width of the PMOS and NMOS of the transmission gate.

Analysis is performed for various benchmarks of the ISPD 2010 benchmarks. For example Table 7 shows the comparison of the skew and slew rate for test case '02.in' in ISPD 2010 benchmark. The transmission gate size factor (SZF) determines the size (width) of the transmission gate. If SZF =1 then for ISPD benchmarks with 45nm technology, NMOS and PMOS of transmission gate will have size value as NMOS SIZE=SZF\*4\*45nm and PMOS SIZE=SZF\*8\*45nm respectively.

Table 7. The variation of the maximum skew, average power with the change in the size of the transmission gate for 2x2 reconfigurable clock mesh for '02.in' case

| Benchmark              | Clock distribution network                         |                                                       |         |        |         |  |  |  |  |

|------------------------|----------------------------------------------------|-------------------------------------------------------|---------|--------|---------|--|--|--|--|

|                        | H-tree wit                                         | H-tree with 2x2 reconfigurable mesh with clock gating |         |        |         |  |  |  |  |

|                        | (level =1) keeping the number of TG connections to |                                                       |         |        |         |  |  |  |  |

| 02.in                  |                                                    | (NTG) 17/side for each sub-blocks                     |         |        |         |  |  |  |  |

| Changing the           | Max                                                | Max Fall                                              | Average | Wire   | Max     |  |  |  |  |

| transmission gate size | Skew (ps)                                          | time (ps)                                             | Power   | Length | latency |  |  |  |  |

| factor (SZF) with      |                                                    |                                                       | (mW)    | (cm)   | (ns)    |  |  |  |  |

| NMOS=SZF*4*45nm &      |                                                    |                                                       |         |        |         |  |  |  |  |

| PMOS=SZF*8*45nm        |                                                    |                                                       |         |        |         |  |  |  |  |

| 0.25                   | 20.3                                               | 76.59                                                 | 544.13  | 98.84  | 2.46    |  |  |  |  |

| 0.5                    | 20.3                                               | 76.48                                                 | 544.13  | 98.84  | 2.46    |  |  |  |  |

| 1                      | 20.2                                               | 76.3                                                  | 544.14  | 98.84  | 2.46    |  |  |  |  |

| 10                     | 19.5                                               | 75.69                                                 | 544.35  | 98.84  | 2.46    |  |  |  |  |

| 20                     | 19                                                 | 76.63                                                 | 544.55  | 98.84  | 2.46    |  |  |  |  |

| 30                     | 18.8                                               | 77.05                                                 | 544.77  | 98.84  | 2.46    |  |  |  |  |

| 40                     | 18.7                                               | 77.23                                                 | 544.93  | 98.84  | 2.46    |  |  |  |  |

| 50                     | 18.7                                               | 77.37                                                 | 545.06  | 98.84  | 2.46    |  |  |  |  |

| 60                     | 18.7                                               | 77.5                                                  | 545.22  | 98.84  | 2.46    |  |  |  |  |

| 80                     | 18.8                                               | 77.75                                                 | 545.46  | 98.84  | 2.46    |  |  |  |  |

| 100                    | 19                                                 | 78                                                    | 545.7   | 98.84  | 2.46    |  |  |  |  |

| 120                    | 19.4                                               | 78.25                                                 | 545.93  | 98.84  | 2.46    |  |  |  |  |

| 140                    | 19.8                                               | 78.49                                                 | 546.15  | 98.84  | 2.46    |  |  |  |  |

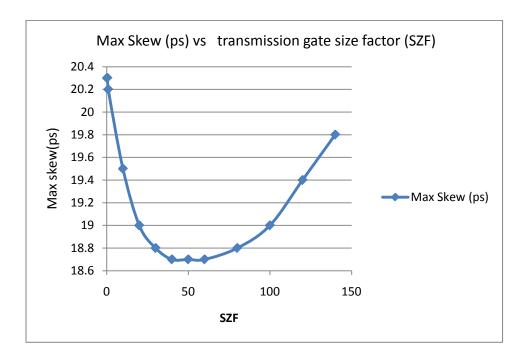

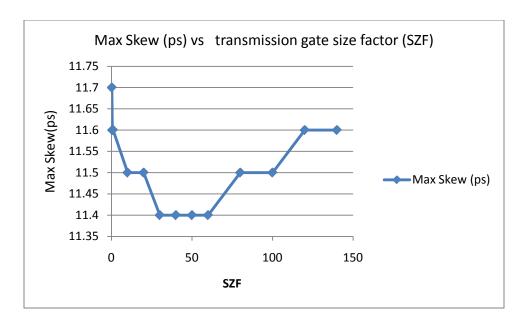

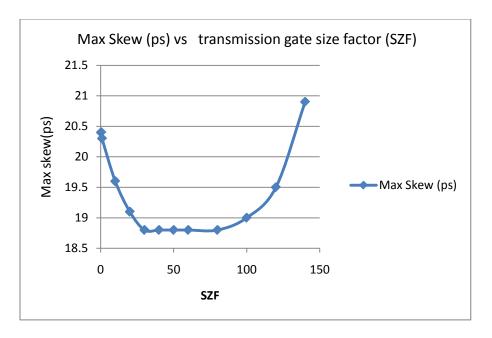

Variation in the skew with the size of transmission gate is given by Table 7 for the clock distribution network using 2x2 reconfigurable clock mesh of level 5 and H-tree of level 4. And the corresponding variation of the maximum skew with the change of the size of the transmission gate (SZF) has been plotted in Figure 15. Similarly, the variation of the maximum skew with SZF for 01.in benchmark corresponding to 2x2 reconfigurable mesh is shown in Figure 16. Transmission gate acts as voltage controlled resistor and its resistance decreases with increase in width of PMOS and NMOS when transmission gate is in conducting mode. Thus it can be seen that with the increase in the width of PMOS and NMOS of the transmission gate the maximum skew decreases.

Figure 15. Variation of the maximum skew with the change of the size of the transmission gate for 2x2 reconfigurable clock mesh for '02.in' case