# A PARTITIONING APPROACH FOR PARALLEL SIMULATION OF AC-RADIAL SHIPBOARD POWER SYSTEMS

A Dissertation

by

# FABIAN MARCEL URIARTE

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

May 2010

Major Subject: Electrical Engineering

# A PARTITIONING APPROACH FOR PARALLEL SIMULATION OF AC-RADIAL SHIPBOARD POWER SYSTEMS

A Dissertation

by

# FABIAN MARCEL URIARTE

# Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

Approved by:

| Chair of Committee, | K.L. Butler-Purry |

|---------------------|-------------------|

| Committee Members,  | S.P. Khatri       |

|                     | C.O. Malave       |

|                     | C. Singh          |

| Head of Department, | C.N. Georghiades  |

May 2010

Major Subject: Electrical Engineering

### ABSTRACT

A Partitioning Approach for Parallel Simulation of AC-Radial Shipboard Power Systems. (May 2010)

Fabian Marcel Uriarte, B. S. Virginia Tech;

M.S., Virginia Tech

Chair of Advisory Committee: Dr. Karen L. Butler-Purry

An approach to parallelize the simulation of AC-Radial Shipboard Power Systems (SPSs) using multicore computers is presented. Time domain simulations of SPSs are notoriously slow, due principally to the number of components, and the time-variance of the component models. A common approach to reduce the simulation run-time of power systems is to formulate the electrical network equations using modified nodal analysis, use Bergeron's travelling-wave transmission line model to create subsystems, and to parallelize the simulation using a distributed computer. In this work, an SPS was formulated using loop analysis, defining the subsystems using a diakoptics-based approach, and the simulation parallelized using a multicore computer.

A program was developed in C# to conduct multithreaded parallel-sequential simulations of an SPS. The program first represents an SPS as a graph, and then partitions the graph. Each graph partition represents a SPS subsystem and is computationally balanced using iterative refinement heuristics. Once balanced subsystems are obtained, each SPS subsystem's electrical network equations are

formulated using loop analysis. Each SPS subsystem is solved using a unique thread, and each thread is manually assigned to a core of a multicore computer.

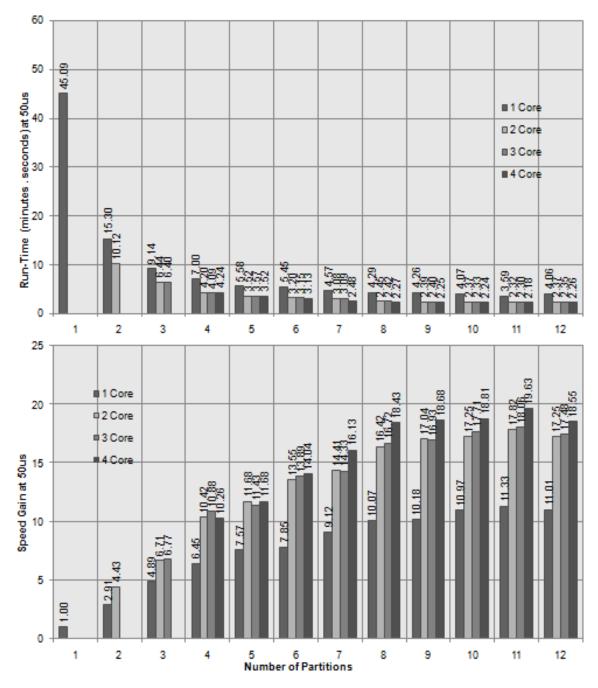

To validate the partitioning approach, performance metrics were created to assess the speed gain and accuracy of the partitioned SPS simulations. The simulation parameters swept for the performance metrics were the number of partitions, the number of cores used, and the time step increment. The results of the performance metrics showed adequate speed gains with negligible error.

An increasing simulation speed gain was observed when the number of partitions and cores were augmented, obtaining maximum speed gains of <30x when using a quadcore computer. Results show that the speed gain is more sensitive to the number partitions than is to the number of cores. While multicore computers are suitable for parallel-sequential SPS simulations, increasing the number of cores does not contribute to the gain in speed as much as does partitioning.

The simulation error increased with the simulation time step but did not influence the partitioned simulation results. The number of operations caused by protective devices was used to determine whether the simulation error introduced by partitioning SPS simulations produced a inconsistent system behavior. It is shown, for the time step sizes uses, that protective devices did not operate inadvertently, which indicates that the errors did not alter RMS measurement and, hence, were non-influential.

# DEDICATION

To my nuclear family. I thank them all for their immense patience, which was the only necessary and sufficient condition to complete this work.

### ACKNOWLEDGEMENTS

First and foremost I would like to acknowledge the effort, support, and trust bestowed upon me by my advisor Dr. K. L. Butler-Purry. I thank her for encouraging me through difficult times and believing in me. Without her guidance, far-sighted experience, and faith in the investigation this work could not have been completed.

The works of the following authors in the areas of modeling and simulation implementation was considered inspirational during the development of this dissertation: H. W. Dommel and J. R. Marti (University of British Columbia), K. Strunz (University of Washington), N. Watson (University of Canterbury), and T. Noda (Doshisha University). I would like to thank the aforementioned authors for the level of detail presented in their writings, which motivated the beginnings of this work.

I would thank Dr. A. Abur for teaching the course of Power System Electromagnetic Transient Analysis during his association with Texas A&M University in 2004. I would like to thank Dr. Khatri for his guidance in the area of computer engineering during the final stages of this dissertation. Additionally, I would like to thank Dr. P. Li, also from the department of Computer Engineering, for providing recommendations on this work. I would like to thank Dr. C. Malave for his friendship and, most importantly, for encouraging me to "stay put" in the doctoral degree program at Texas A&M.

# TABLE OF CONTENTS

| ABSTRACT   | Γ     |                                                                         | iii |

|------------|-------|-------------------------------------------------------------------------|-----|

| DEDICATIO  | ON    |                                                                         | V   |

| ACKNOWI    | LEDGE | MENTS                                                                   | vi  |

| TABLE OF   | CONT  | ENTS                                                                    | vii |

| LIST OF FI | GURES |                                                                         | X   |

| LIST OF TA | ABLES |                                                                         | XV  |

| CHAPTER    |       |                                                                         |     |

| Ι          | INTRO | DDUCTION                                                                | 1   |

|            |       | Introduction<br>Organization                                            |     |

| II         | LITER | ATURE REVIEW AND PROBLEM FORMULATION                                    | 6   |

|            | 2.1   | Introduction                                                            | 6   |

|            |       | Motivation of the Work                                                  |     |

|            |       | 2.2.1 AC-Radial Shipboard Power Systems                                 |     |

|            |       | 2.2.2 Power System Transient Simulators                                 |     |

|            | 2.3   | Existing Solutions to Reduce Simulation Run-Time                        |     |

|            |       | 2.3.1 Bergeron's Travelling-Wave Model                                  |     |

|            |       | 2.3.2 The Use of Time Step Delays                                       |     |

|            |       | 2.3.3 Diakoptics-based Partitioning Approaches                          | 29  |

|            | 2.4   | Differential-Algebraic Formulation of a Notional Shipboard              | •   |

|            |       | Power System                                                            |     |

|            |       | 2.4.1 Multi-Terminal Component Theory                                   |     |

|            |       | <ul><li>2.4.2 Component Models</li><li>2.4.3 Interconnections</li></ul> |     |

|            |       | 2.4.4 System Equation Formulation                                       |     |

|            | 2.5   | Problem Formulation                                                     |     |

|            |       |                                                                         |     |

|     | 2.6  | Chapter Summary                                             | 77  |

|-----|------|-------------------------------------------------------------|-----|

| III | SOLU | TION METHODOLOGY                                            | 78  |

|     | 3.1  | Introduction                                                |     |

|     | 3.2  | Mathematical System Representation                          | 80  |

|     |      | 3.2.1 Discretization of an Inductor                         | 83  |

|     |      | 3.2.2 Discretization of a Capacitor                         | 84  |

|     |      | 3.2.3 Discretization of Controllers and Relays              | 85  |

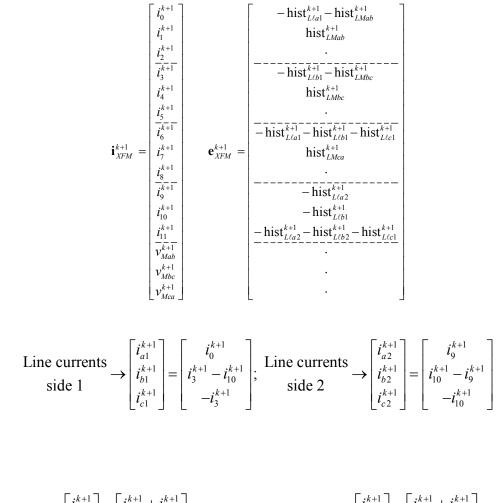

|     |      | 3.2.4 Formulation of Loop Currents for Electrical and Contr |     |

|     |      | Networks                                                    |     |

|     | 2.2  | 3.2.5 Electrical and Control Networks                       |     |

|     | 3.3  | $\mathbf{D}$                                                |     |

|     |      | 3.3.1 Diakoptics Theory and Capacitor Tearing               |     |

|     |      | 3.3.2 Flop Computations for Graph Vertices                  |     |

|     |      | 3.3.3 Creation of a Representative Graph                    |     |

|     |      | 3.3.4 Graph Balancing Heuristics                            |     |

|     | 2.4  | 3.3.5 Summary                                               |     |

|     | 3.4  |                                                             |     |

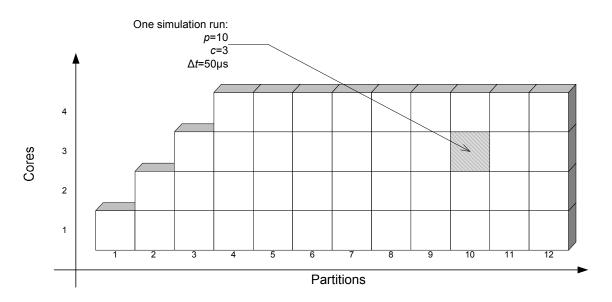

|     | 3.5  | Determining the Number of Partitions                        |     |

|     |      | 3.5.1 Cost of Step 1                                        |     |

|     |      | 3.5.2 Cost of Step 2                                        |     |

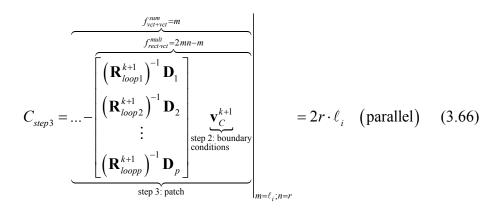

|     |      | 3.5.3 Cost of Step 3                                        |     |

|     | 2.0  | 3.5.4 Cost Function                                         |     |

|     | 3.0  | Chapter Summary                                             | 143 |

| IV  | STUD | IES AND PERFORMANCE ANALYSIS                                | 144 |

|     |      | Introduction                                                |     |

|     | 4.2  | Description of Performance Metrics                          |     |

|     |      | 4.2.1 Performance Metric 1                                  |     |

|     |      | 4.2.2 Performance Metric 2                                  |     |

|     | 4.3  | Description of Case Study                                   | 148 |

|     |      | 4.3.1 Simulation Waveforms                                  |     |

|     |      | 4.3.2 Performance Metric 1 Results                          |     |

|     |      | 4.3.3 Performance Metric 2 Results                          | 185 |

|     | 4.4  | Chapter Summary                                             | 207 |

| V   | CONC | CLUSIONS AND FUTURE WORK                                    | 210 |

|     | 5.1  | Conclusions                                                 | 210 |

|     |      | 5.1.1 Advantages of the Solution Methodology                | 210 |

| <ul><li>5.1.2 Limitations of the Solution Methodology</li><li>5.2 Future Work</li><li>5.3 Chapter Summary</li></ul> | 214 |

|---------------------------------------------------------------------------------------------------------------------|-----|

| REFERENCES                                                                                                          |     |

| APPENDIX A DISCRETIZED COMPONENT MODELS                                                                             |     |

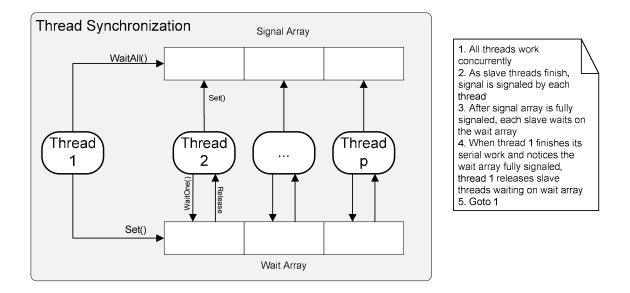

| APPENDIX B THREAD SYNCHRONIZATION                                                                                   |     |

| APPENDIX C COMPONENT DISTRIBUTION                                                                                   |     |

| APPENDIX D FAULT AND PROTECTIVE DEVICE EVENTS                                                                       | 277 |

| VITA                                                                                                                |     |

# LIST OF FIGURES

| Fig. 2.2.1. Motives and desired aspects of a solution                                   | 7  |

|-----------------------------------------------------------------------------------------|----|

| Fig. 2.2.2. General electrical layout of AC-Radial Shipboard Power Systems [12]         | 10 |

| Fig. 2.2.3. Illustation of fixed time step time domain simulation                       | 14 |

| Fig. 2.2.4 The simulation process at each time step (fixed $\Delta t$ assumed)          | 15 |

| Fig. 2.3.1. Classification of power system partitioning methods                         | 17 |

| Fig. 2.3.2 . A long transmission-line representation                                    | 21 |

| Fig. 2.3.3. Bergeron's equivalent circuit model for a long (lossless) transmission line | 22 |

| Fig. 2.3.4. Branch (left) and node (right) as modeled by the latency insertion method.  | 26 |

| Fig. 2.3.5. Two areas joined by an inter-area link (lumped resistances)                 | 33 |

| Fig. 2.3.6. Two areas decoupled by current source transportation [47]                   | 33 |

| Fig. 2.3.7. Two areas joined by ideal circuit breakers                                  | 37 |

| Fig. 2.4.1. A power apparatus enclosed inside a multi-terminal component (MTC)          | 39 |

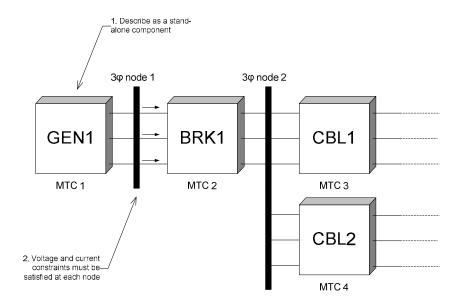

| Fig. 2.4.2. Radial connection of four MTCs                                              | 40 |

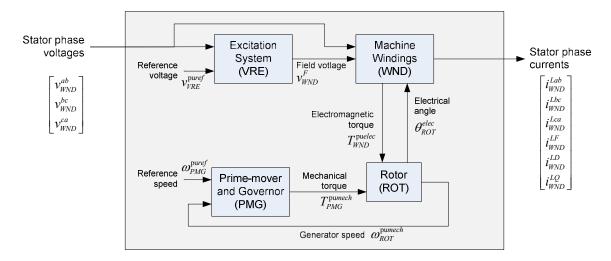

| Fig. 2.4.3. Electrical and mechanical subcomponents of a synchronous generator          | 42 |

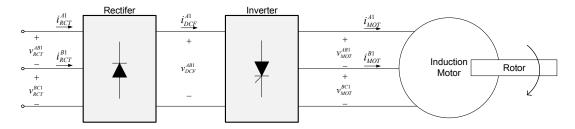

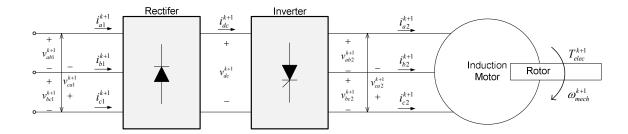

| Fig. 2.4.4. Induction motor and drive                                                   | 48 |

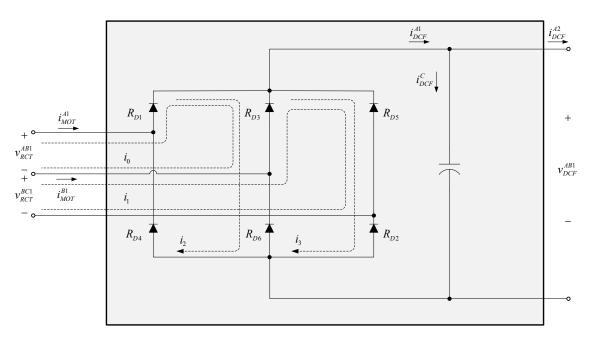

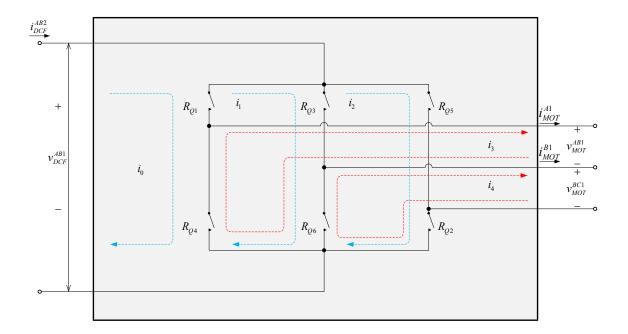

| Fig. 2.4.5. Motor drive's line-commutated rectifier                                     | 49 |

| Fig. 2.4.6. Motor drive's voltage-source inverter                                       | 50 |

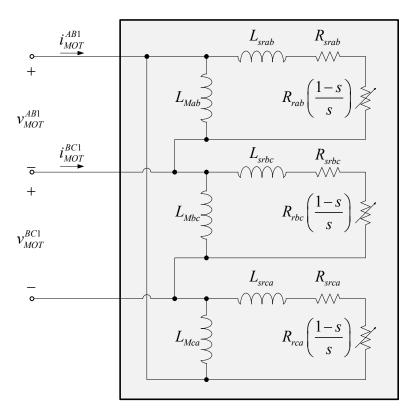

| Fig. 2.4.7. Induction motor stator and rotor windings                                   | 52 |

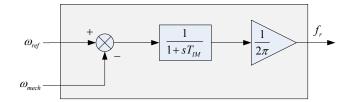

| Fig. 2.4.8. Speed controller for induction motor                                        | 54 |

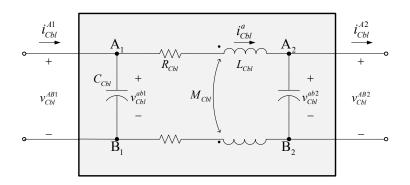

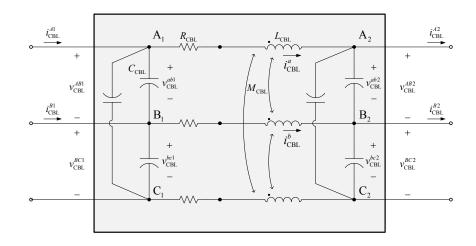

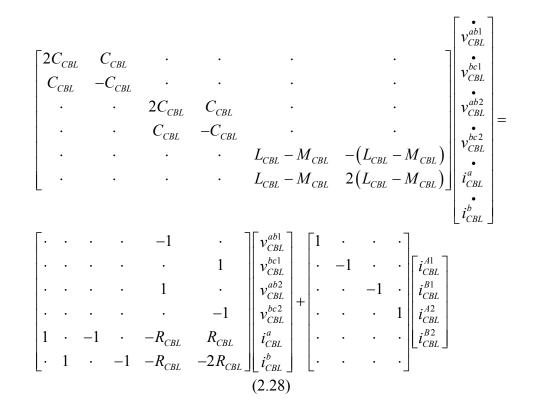

| Fig. 2.4.9. Single-phase cable model (current-in, voltage-out)                          | 54 |

| Fig. 2.4.10. Three-phase model (current-in, voltage-out)                                | 55 |

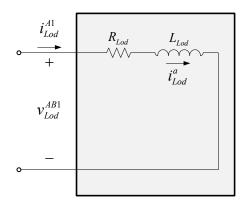

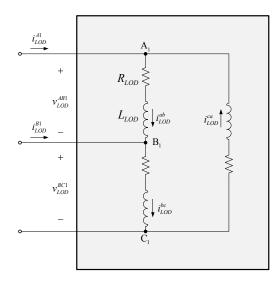

| Fig. 2.4.11. Single-phase load model (voltage-in, current-out)                           | 57  |

|------------------------------------------------------------------------------------------|-----|

| Fig. 2.4.12. Three-phase load model (voltage-in, current-out)                            | 58  |

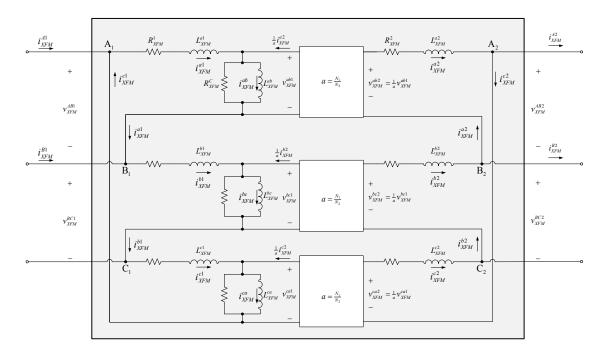

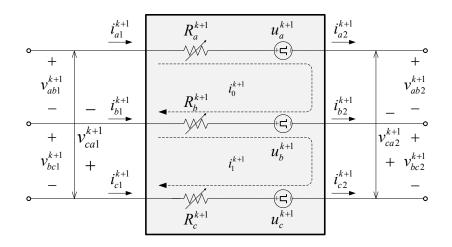

| Fig. 2.4.13. Three-phase transformer model (450/120V step-down)                          | 59  |

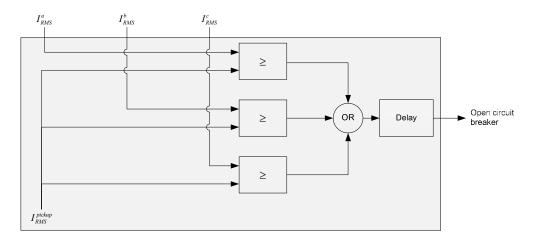

| Fig. 2.4.14. Over-current relay logic                                                    | 62  |

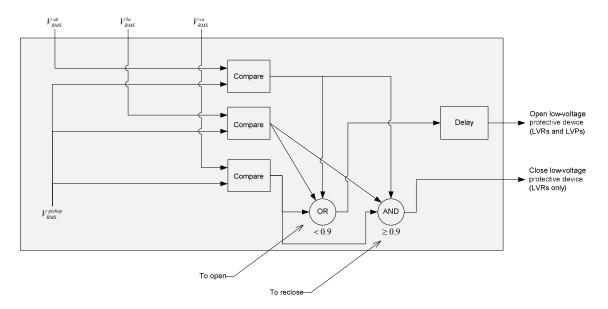

| Fig. 2.4.15. Under-voltage relay logic for low voltage protective devices (LVXs)         | 63  |

| Fig. 2.4.16. Over-current relay and low-voltage protective device model                  | 64  |

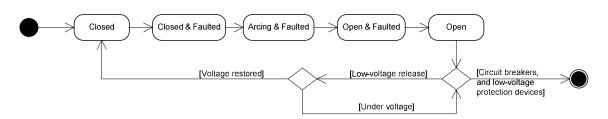

| Fig. 2.4.17. Over-current relay and low-voltage protection device states                 | 65  |

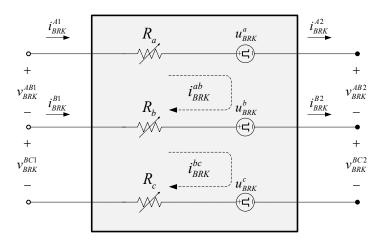

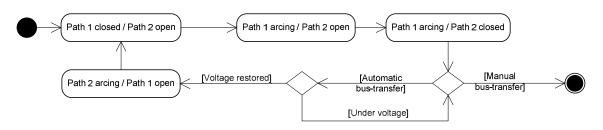

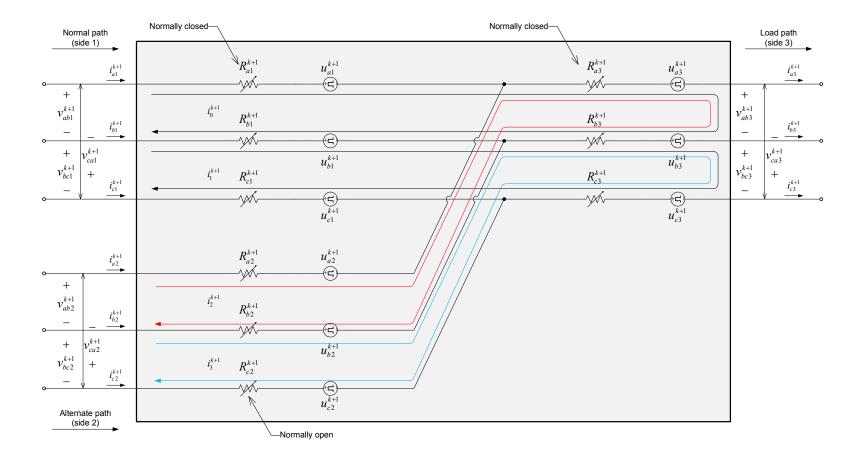

| Fig. 2.4.18. Bus transfer model                                                          | 67  |

| Fig. 2.4.19. Bus-transfer device states                                                  | 68  |

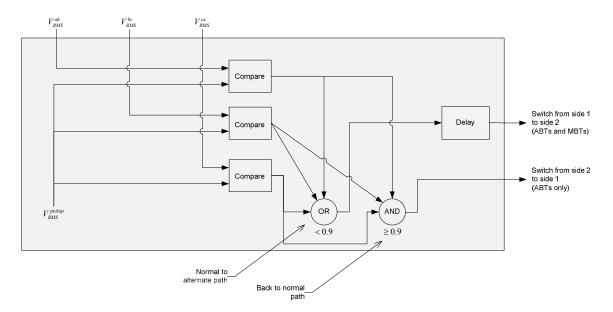

| Fig. 2.4.20. Under-voltage relay logic for bus transfers (XBTs)                          | 69  |

| Fig. 2.4.21 . Example connection of a cable and transformer                              | 71  |

| Fig. 2.4.22. Illustration of a notional AC-Radial SPS (repeated from Fig. 2.2.2)         | 74  |

| Fig. 3.2.1. Equivalent circuits for discretized inductors and capacitors                 | 85  |

| Fig. 3.2.2. Loop resistance matrix structure for an unpartioned AC-Radial SPS            | 92  |

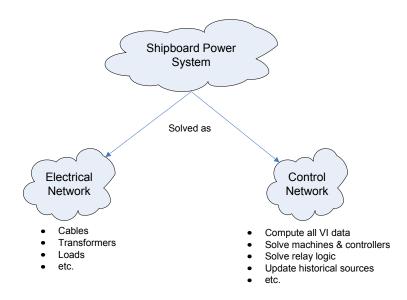

| Fig. 3.2.3. Overview of electrical and control network                                   | 95  |

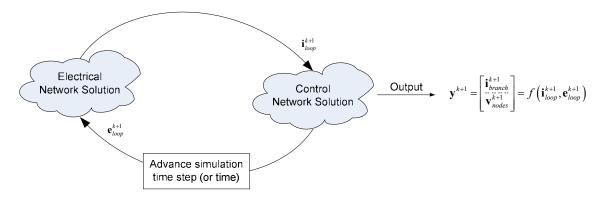

| Fig. 3.2.4. Solution of electrical and control networks [24]                             | 96  |

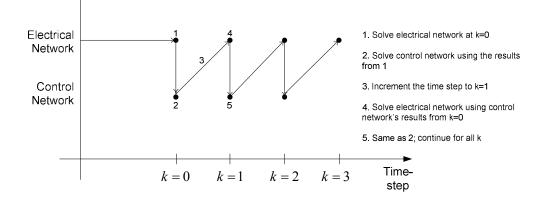

| Fig. 3.2.5. Time-line illustration of the electrical and control network interface [72]. | 97  |

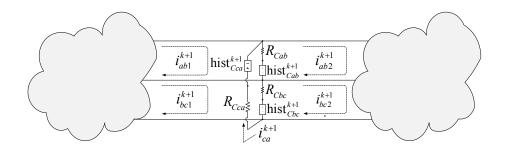

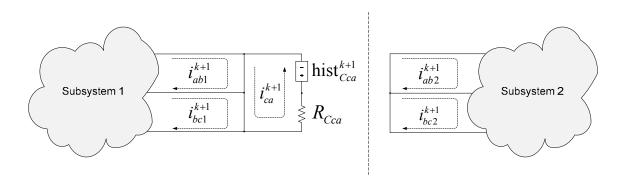

| Fig. 3.3.1. Generalized cable capacitor loop (at switchboards and load centers)          | 102 |

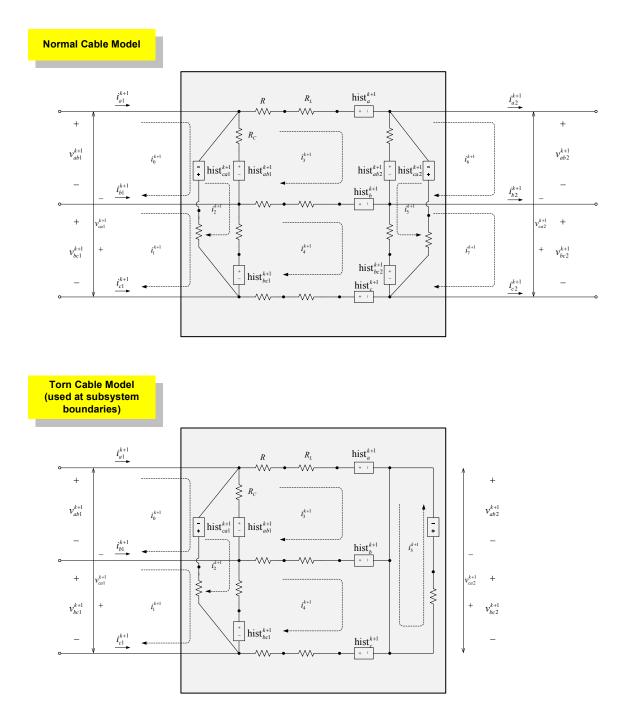

| Fig. 3.3.2. Three-phase cable model                                                      | 108 |

| Fig. 3.3.3. A discretized capacitor loop                                                 | 108 |

| Fig. 3.3.4. Torn cable forms two subsystems                                              | 108 |

| Fig. 3.3.5. Normal and torn cable model (replaced at boundaries)                         | 109 |

| Fig. 3.3.6. A group of components to illustrate the representative graph                 | 120 |

| Fig. 3.3.7. Representative graph of electrical network in Fig. 3.3.6                            | 120 |

|-------------------------------------------------------------------------------------------------|-----|

| Fig. 3.3.8. A graph divided into two partitions                                                 | 121 |

| Fig. 3.3.9. Subsystems corresponding to graph partitions                                        | 122 |

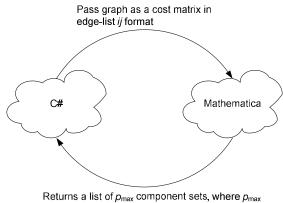

| Fig. 3.3.10. Interaction between C# and Mathematica                                             | 127 |

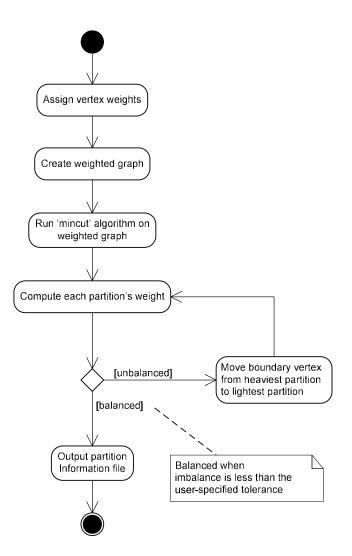

| Fig. 3.3.11. Activity diagram illustrating steps to balance graph                               | 128 |

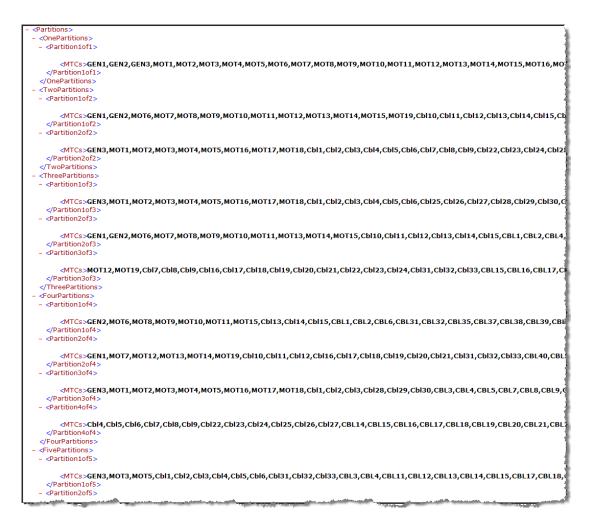

| Fig. 3.3.12. Component sets output file from Mathematica                                        | 129 |

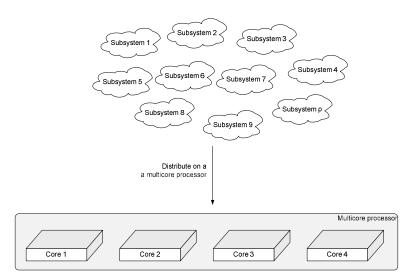

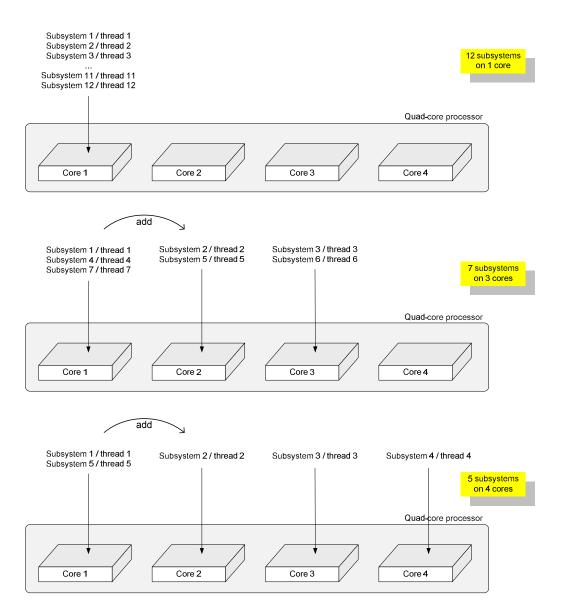

| Fig. 3.4.1. Illustration of subsystem simulation on a multicore processor                       | 131 |

| Fig. 3.4.2. Examples of various subsystem/thread distributions on four cores                    | 132 |

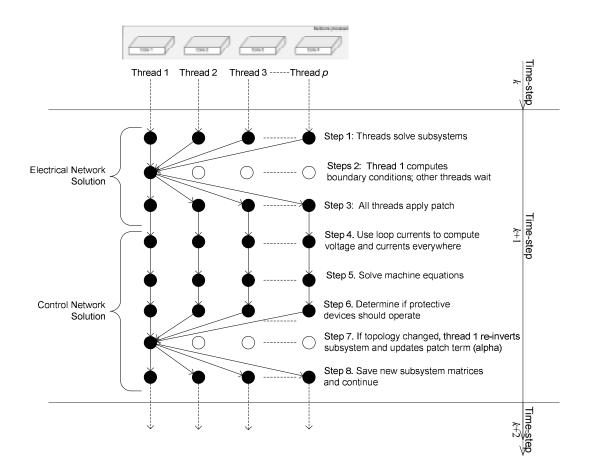

| Fig. 3.4.3. Thread swim-lane diagram: 1 thread-per-core shown                                   | 134 |

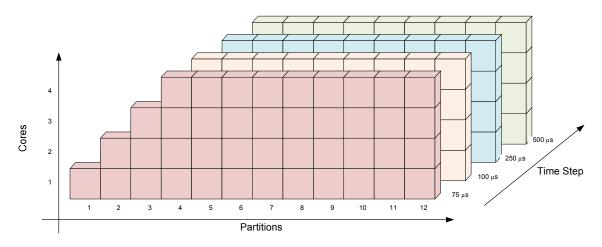

| Fig. 4.2.1. Number of simulation runs (42) to evaluate performance metric 1                     | 146 |

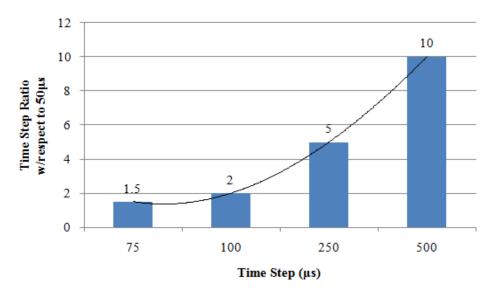

| Fig. 4.2.2. Time step sizes used for performance metric 2                                       | 147 |

| Fig. 4.2.3. Number of simulation runs (168) to evaluate performance metric 2                    | 148 |

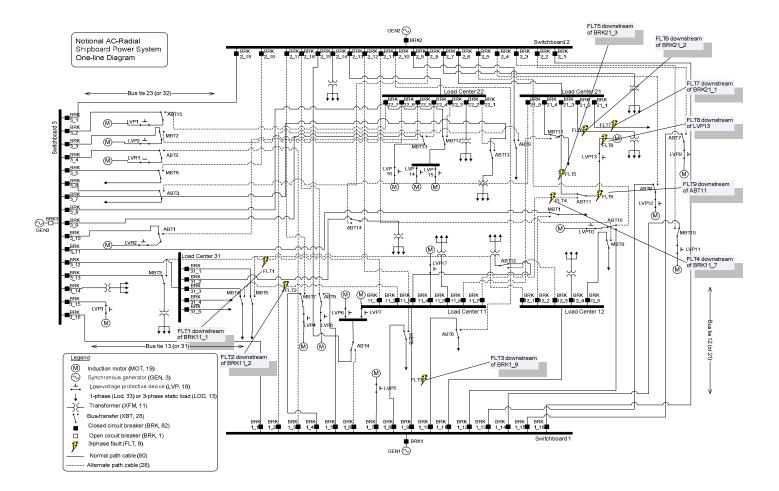

| Fig. 4.3.1. Schematic of SPS used for case studies showing locations of the 9 faults            | 151 |

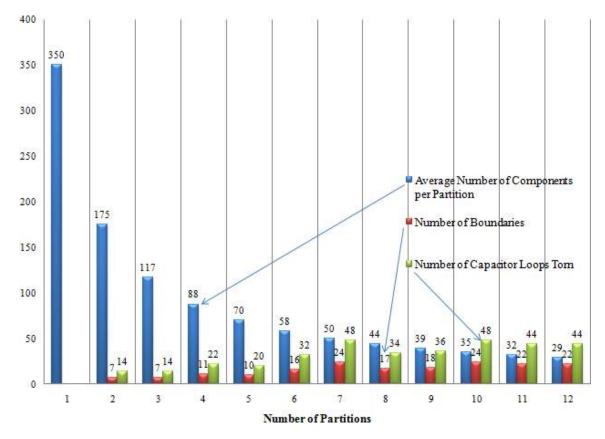

| Fig. 4.3.2. Average component distribution per number of partitions                             | 154 |

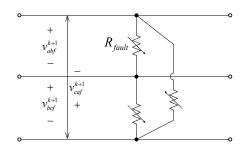

| Fig. 4.3.3. Three-phase fault model (inside three-phase cables)                                 | 155 |

| Fig. 4.3.4. Summary of switching events (1 of 2)                                                | 157 |

| Fig. 4.3.5. Summary of switching events (2 of 2)                                                | 158 |

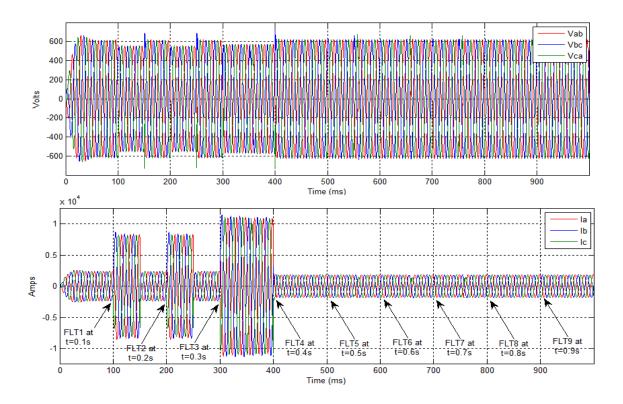

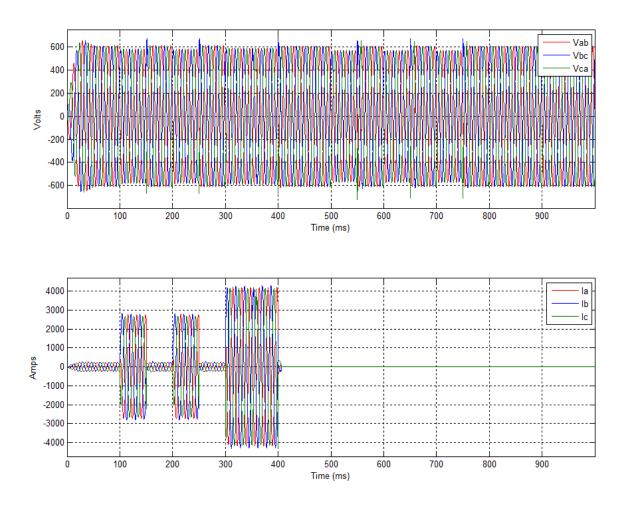

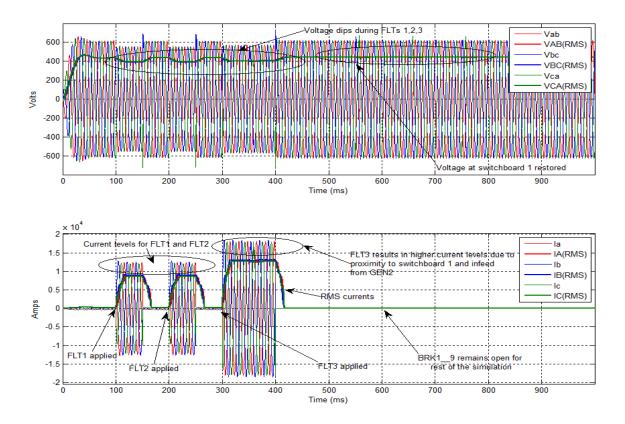

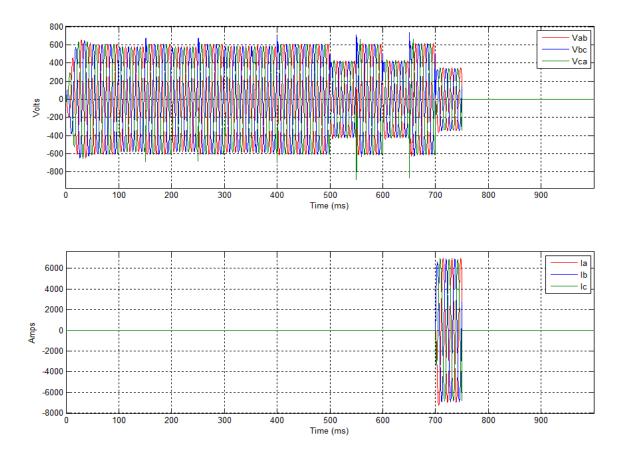

| Fig. 4.3.6. Voltage and current measured from generator 1 { $p=1$ ; $c=1$ ; $\Delta t=50\mu$ s} | 160 |

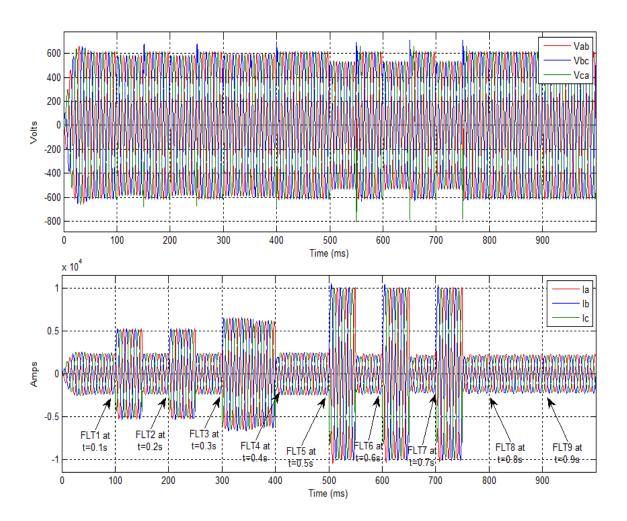

| Fig. 4.3.7. Voltage and current measured from generator 2 { $p=1$ ; $c=2$ ; $\Delta t=50\mu$ s} | 161 |

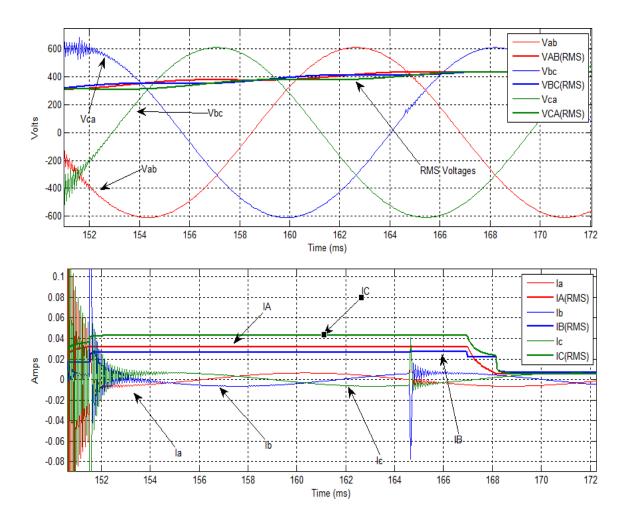

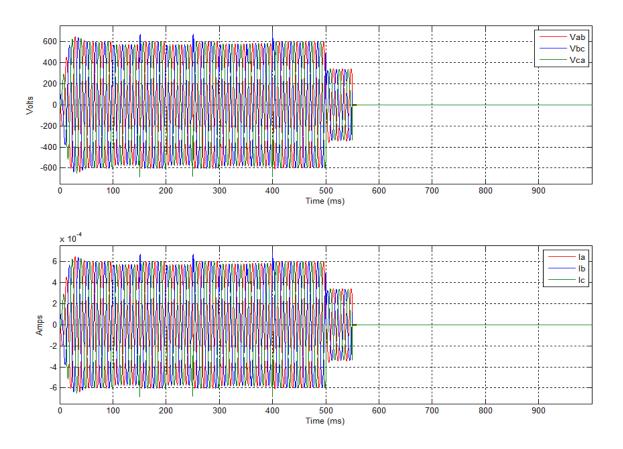

| Fig. 4.3.8. Voltage and current: BRK2_1 ( $p=1$ vs. $p=12$ ; $c=3$ ; $\Delta t=75\mu$ s)        | 162 |

| Fig. 4.3.9. Voltage and current: ( $p=1$ vs. $p=7$ ; $c=4$ ; $\Delta t=75\mu$ s)                | 163 |

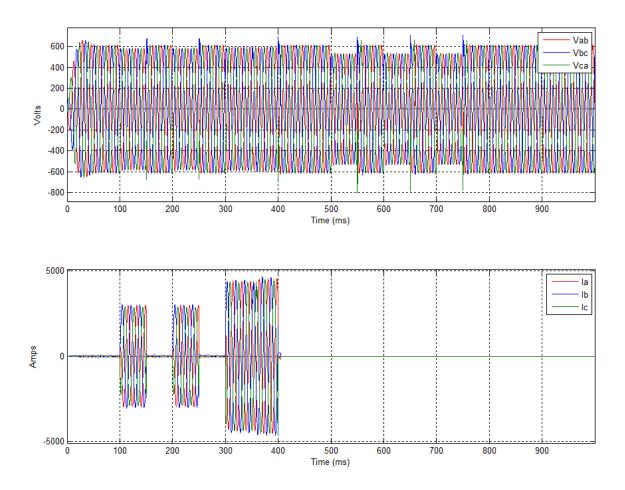

| Fig. 4.3.10. Voltage and current: BRK11_1 as FLT1 was cleared                                   | 164 |

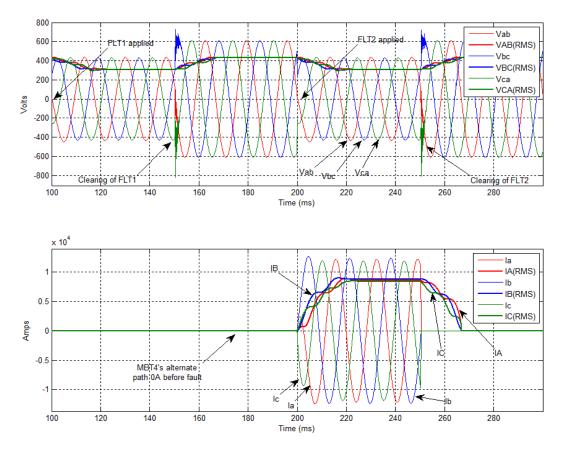

| Fig. 4.3.11. Voltage and current: BRK11_2 ( $p=1$ vs. $p=3$ ; $c=2$ ; $\Delta t=250 \mu$ s)     | 167 |

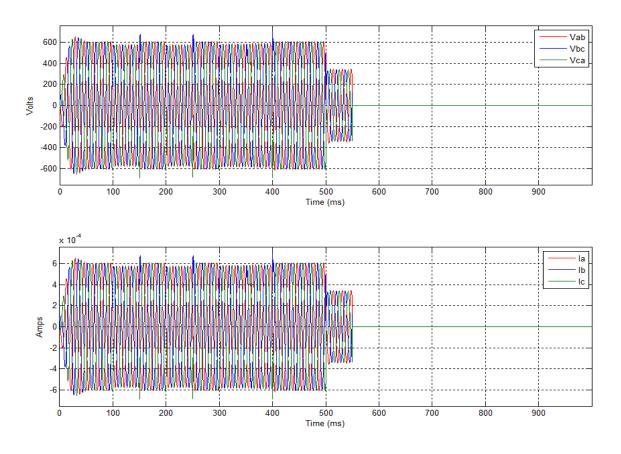

| Fig. 4.3.12. Voltage and phase current: FLT3's ( $p=1$ vs. $p=6$ ; $c=2$ ; $\Delta t=50\mu$ s)168              |

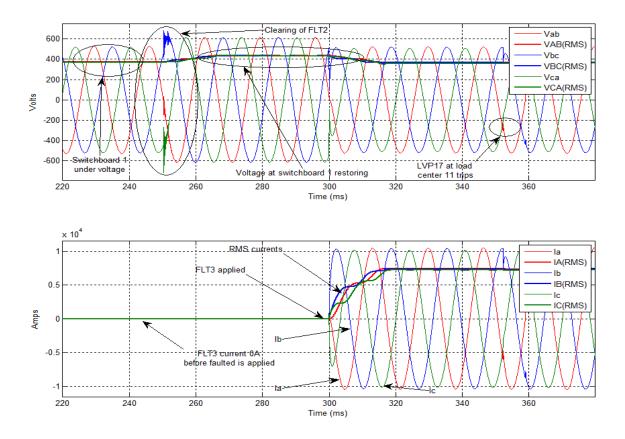

|----------------------------------------------------------------------------------------------------------------|

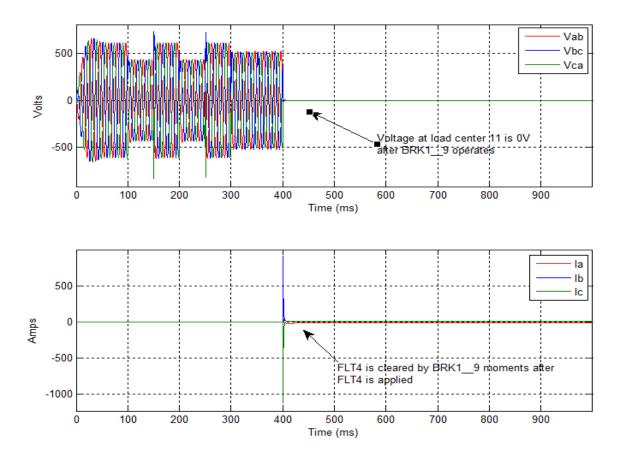

| Fig. 4.3.13. Voltage and current: BRK1_9 ( $p=1$ vs. $p=5$ ; $c=1$ ; $\Delta t=500\mu$ s)169                   |

| Fig. 4.3.14. Voltage and phase-current: FLT4's ( $p=1$ vs. $p=3$ ; $c=3$ ; $\Delta t=100\mu$ s)170             |

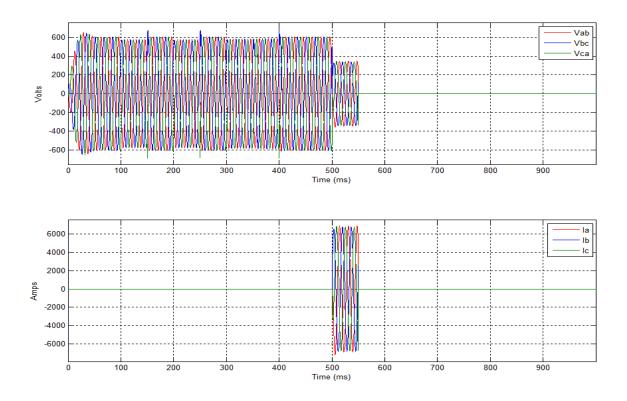

| Fig. 4.3.15. Voltage and phase-current: FLT5 ( $p=1$ vs. $p=2$ ; $c=2$ ; $\Delta t=100\mu$ s)171               |

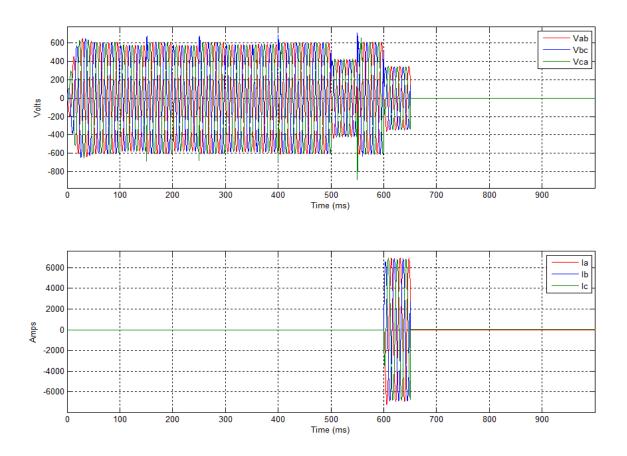

| Fig. 4.3.16. Voltage and phase-current: FLT6 ( $p=1$ vs. $p=3$ ; $c=1$ ; $\Delta t=75\mu$ s)172                |

| Fig. 4.3.17. Voltage and phase-current: FLT7 ( <i>p</i> =1 vs. <i>p</i> =6; <i>c</i> =3; Δ <i>t</i> =100μs)173 |

| Fig. 4.3.18. Voltage and phase-current FLT8: ( $p=1$ vs. $p=12$ ; $c=4$ ; $\Delta t=50\mu$ s)174               |

| Fig. 4.3.19. Voltage and phase-current: FLT9 ( $p=1$ vs. $p=3$ ; $c=1$ ; $\Delta t=250\mu$ s)175               |

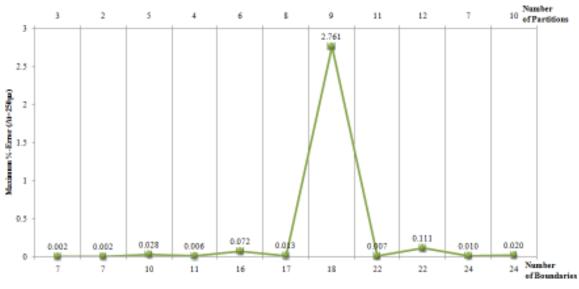

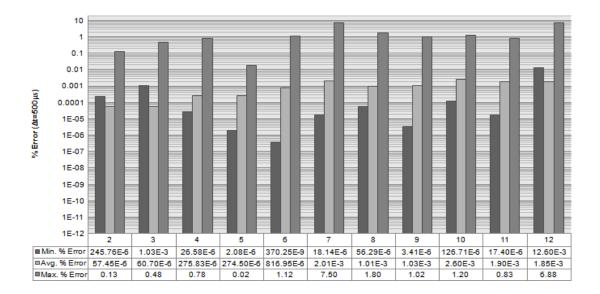

| Fig. 4.3.20 . Simulation run-time (top) and speed gain (bottom) for $\Delta t=50 \mu s$                        |

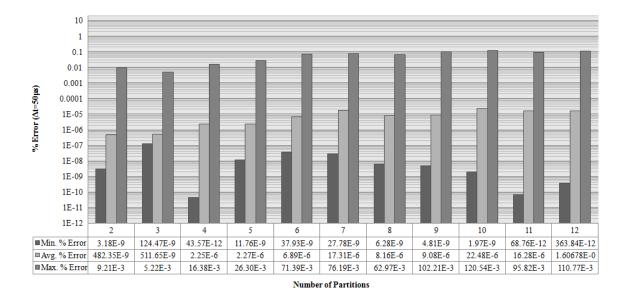

| Fig. 4.3.21 . Simulation errors for performance metric 1 ( $\Delta t$ =50µs)                                   |

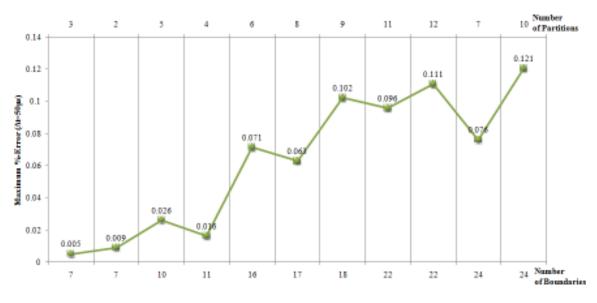

| Fig. 4.3.22 . Maximum simulation error for $\Delta t=50 \mu s$                                                 |

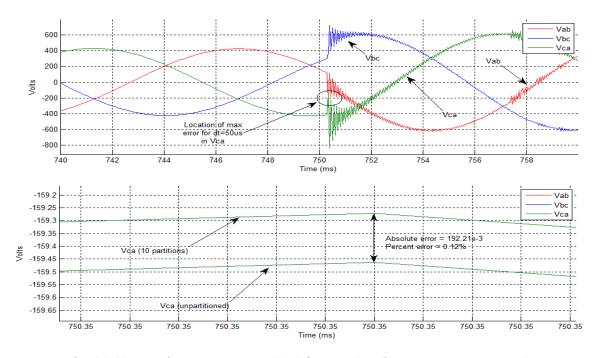

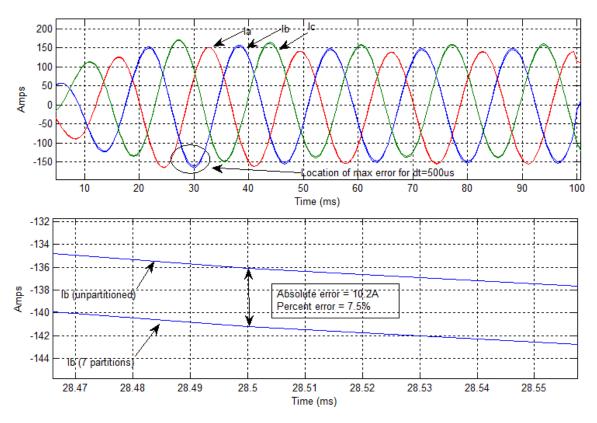

| Fig. 4.3.23 . Maximum error: BRK21_4 for $\Delta t=50\mu s$ (bottom curve zooms top)                           |

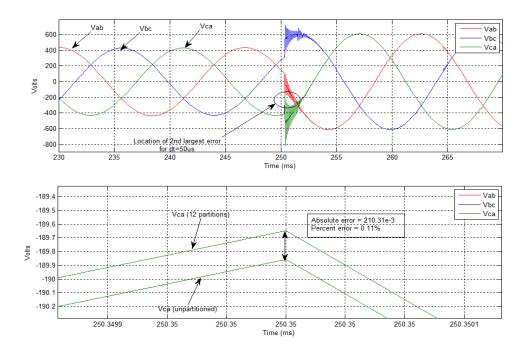

| Fig. 4.3.24 . Second largest error: MBT11 for $\Delta t$ =50µs (bottom curve zooms top)182                     |

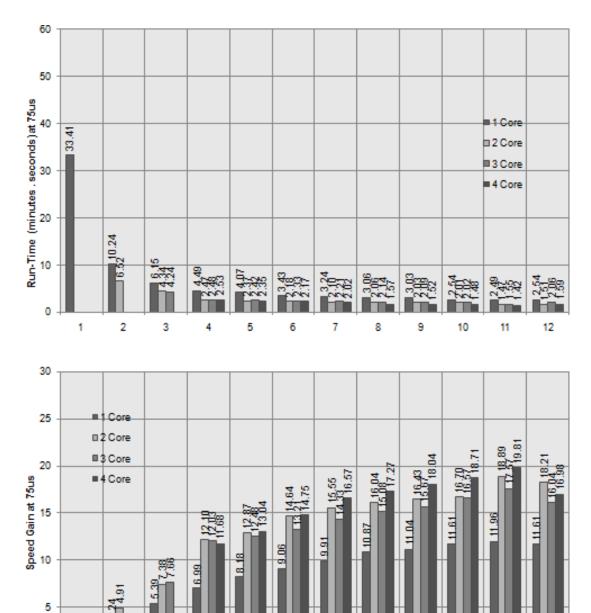

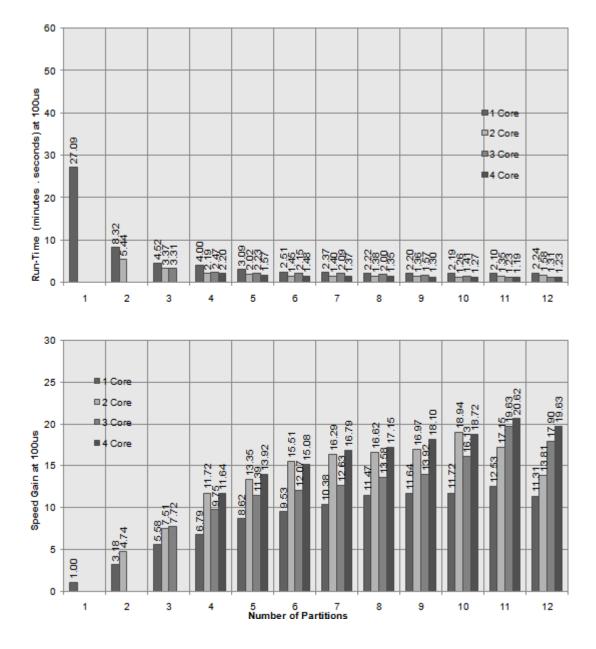

| Fig. 4.3.25 . Simulation run-time (top) and speed gain (bottom) for $\Delta t=75 \mu s$                        |

| Fig. 4.3.26 . Simulation errors for $\Delta t=75\mu s$                                                         |

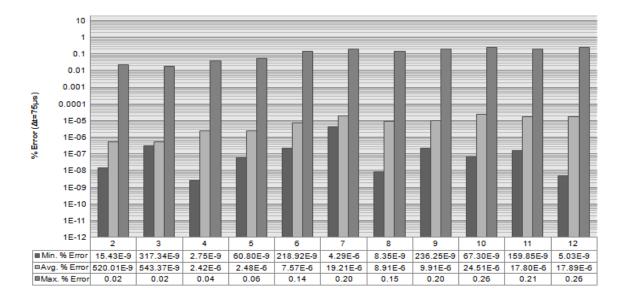

| Fig. 4.3.27 . Maximum simulation error for $\Delta t=75\mu$ s                                                  |

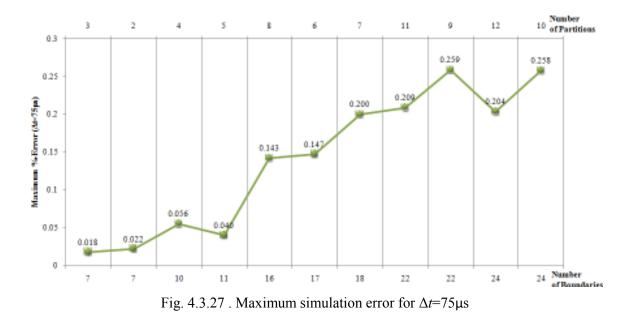

| Fig. 4.3.28 . Simulation run-time (top) and speed gain for $\Delta t=100\mu s$                                 |

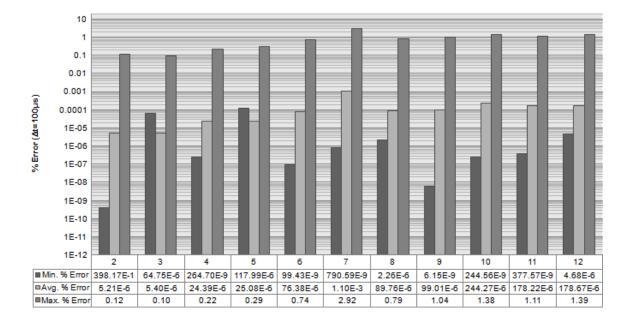

| Fig. 4.3.29 . Simulation errors for $\Delta t=100 \mu s$                                                       |

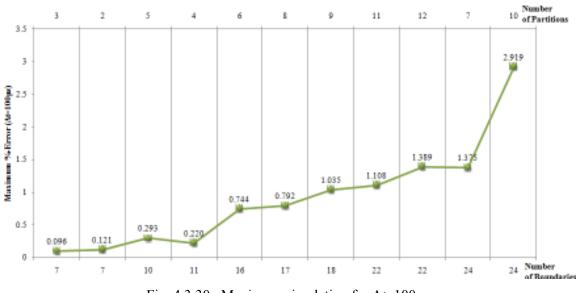

| Fig. 4.3.30 . Maximum simulation for $\Delta t=100\mu$ s                                                       |

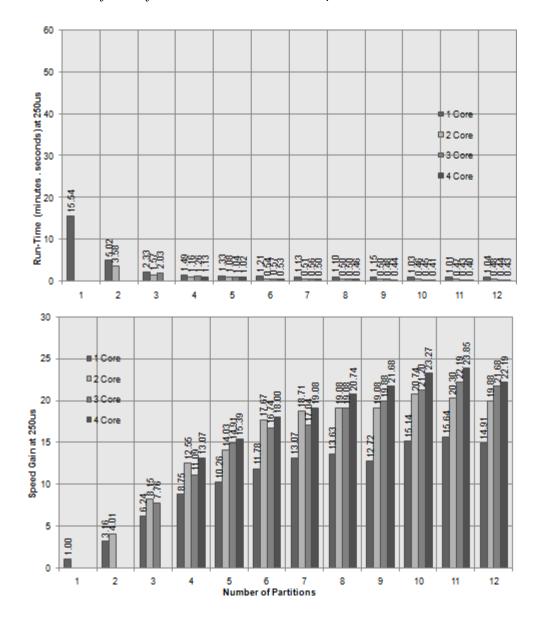

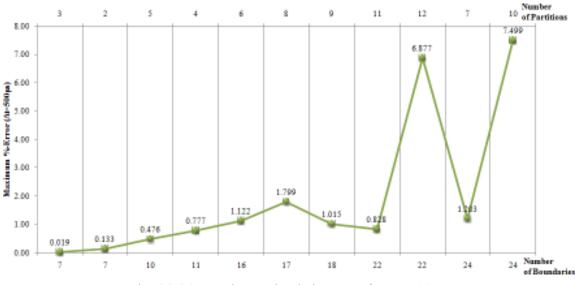

| Fig. 4.3.31. Simulation run-time (top) and speed gain (bottom) $\Delta t=250 \mu s$                            |

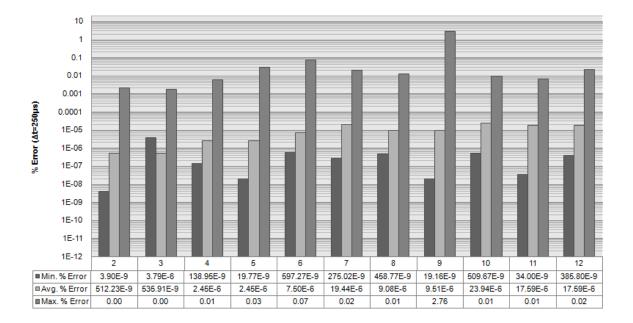

| Fig. 4.3.32 . Simulation errors for $\Delta t=250 \mu s$                                                       |

| Fig. 4.3.33 . Maximum simulation error for $\Delta t=250 \mu s$                                                |

| Р | a | g | e |

|---|---|---|---|

|   |   |   |   |

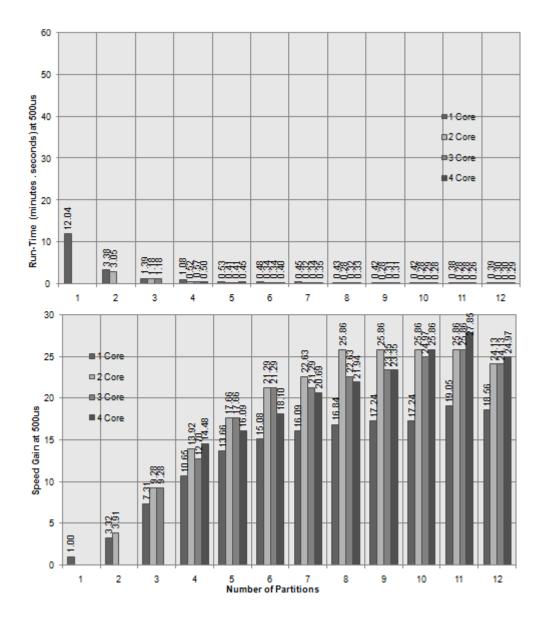

| Fig. 4.3.34. Simulation run-time (top) and speed gain (bottom) for $\Delta t$ =500µs |     |

|--------------------------------------------------------------------------------------|-----|

| Fig. 4.3.35 . Simulation errors for $\Delta t=500 \mu s$                             |     |

| Fig. 4.3.36 . Maximum simulation error for $\Delta t=500 \mu s$                      |     |

| Fig. 4.3.37 . Current overlay of BRK2_13 showing largest error for PM2               | 202 |

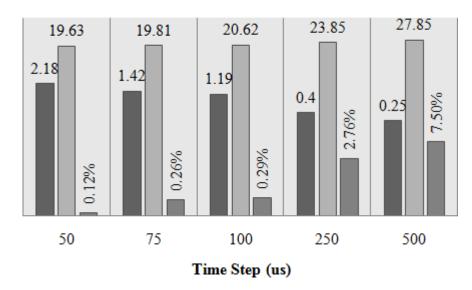

| Fig. 4.3.38 . Run-time, speed gain, and maximum error per time step                  | 204 |

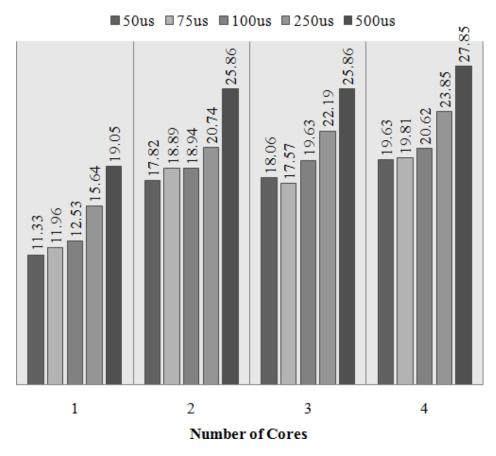

| Fig. 4.3.39 . Summary of speed gain for each $\Delta t$ and $c$                      |     |

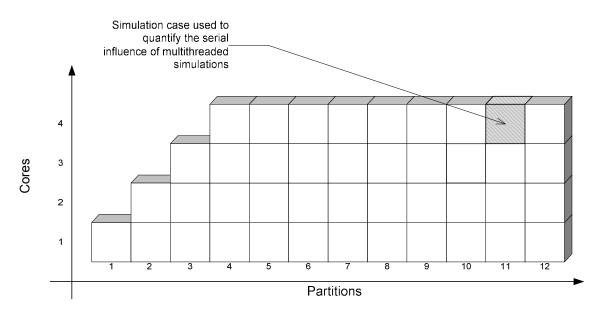

| Fig. 4.3.40 . Simulation case to determine computation time of serial steps          | 207 |

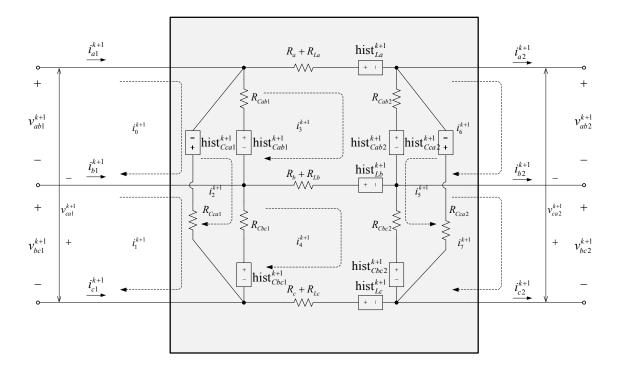

| Fig. 5.3.1. Discretized generator stator and rotor windings                          | 229 |

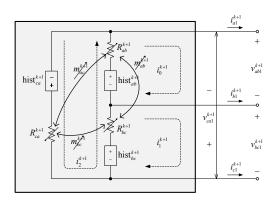

| Fig. 5.3.2. Induction motor and drive                                                | 234 |

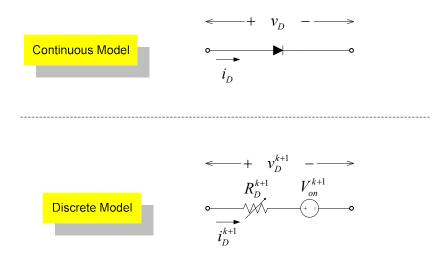

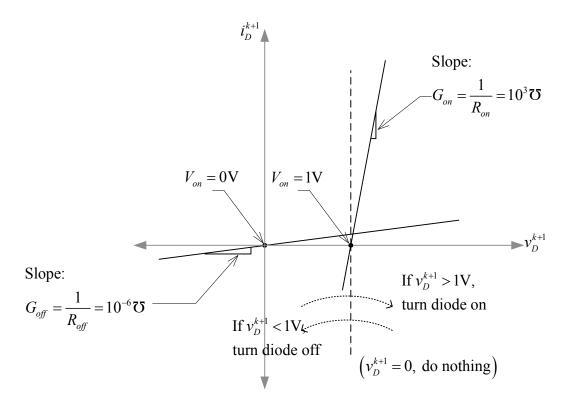

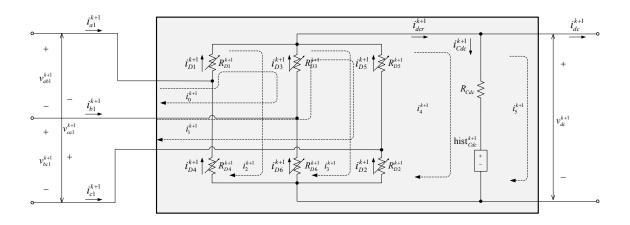

| Fig. 5.3.3. Continuous and discretized diode model                                   | 235 |

| Fig. 5.3.4. Discretized diode voltage and current characteristic                     | 236 |

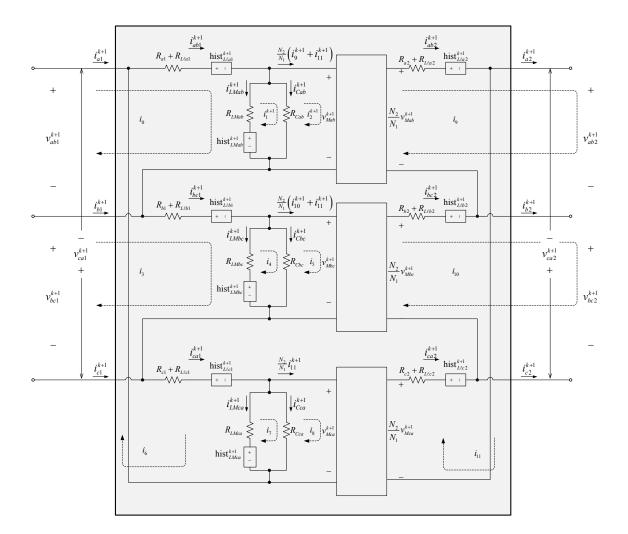

| Fig. 5.3.5. Discretized induction motor rectifier model                              | 236 |

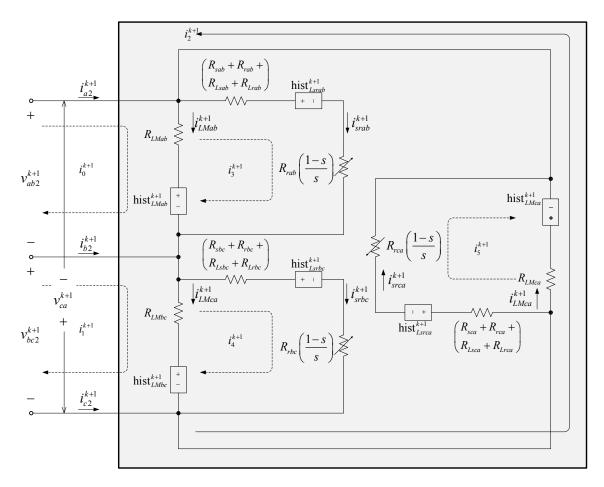

| Fig. 5.3.6. Discretized induction motor windings model                               | 239 |

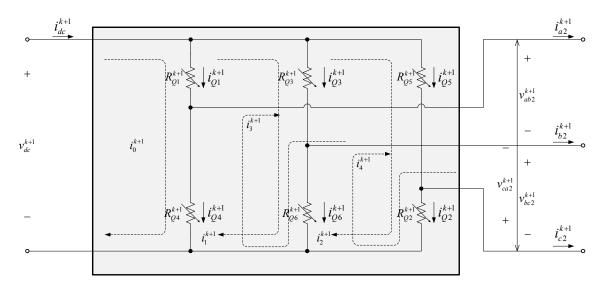

| Fig. 5.3.7. Discretized induction motor inverter model                               | 242 |

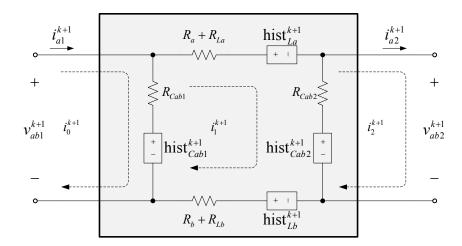

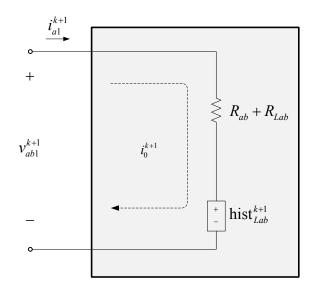

| Fig. 5.3.8. Discretized single-phase cable model                                     | 243 |

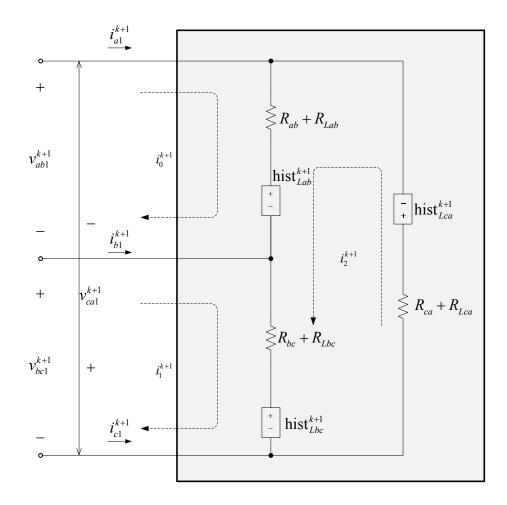

| Fig. 5.3.9. Discretized three-phase cable model                                      |     |

| Fig. 5.3.10. Discretized single-phase static load model                              |     |

| Fig. 5.3.11. Discretized three-phase static load model                               | 250 |

| Fig. 5.3.12. Discretized three-phase transformer model $(\Delta - \Delta)$           | 252 |

| Fig. 5.3.13. Over-current relay                                                      | 257 |

| Fig. 5.3.14. Bus transfer model                                                      |     |

| Fig. 5.3.15. Thread synchronization arrays and logic                                 |     |

# LIST OF TABLES

| Table II.1. Summary of commercial power system simulator partitioning abilities       | 13   |

|---------------------------------------------------------------------------------------|------|

| Table II.2. Induction motor types, ratings, and operating points                      | 47   |

| Table II.3. Induction motor parameters                                                | 47   |

| Table II.4. DAE formulation's state-variable count                                    | 75   |

| Table II.5. DAE formulation's algebraic equation count                                | 75   |

| Table III.1. Relationship between DAE and loop current formulations                   | 94   |

| Table III.2. Summary of common flop operations                                        | .115 |

| Table III.3. Example of weight calculation for a three-phase cable                    | .116 |

| Table III.4. Example of weight calculation for over-current relays                    | .117 |

| Table III.5. Summary of vertex weights per component                                  | .118 |

| Table III.6 . Comparison of graph balancing heuristics                                | .126 |

| Table IV.1 . Computer used to evaluate performance metrics                            | .148 |

| Table IV.2 . Notional AC-Radial SPS model base quantities                             | .153 |

| Table IV.3 . Protective device settings                                               | .153 |

| Table IV.4 . Column header descriptions for switching events output file              | .156 |

| Table IV.5.Simulation errors for performance metric 1 ( $\Delta t$ =50 microseconds)  | .179 |

| Table IV.6.Simulation errors for performance metric 2 ( $\Delta t$ =75 microseconds)  | .188 |

| Table IV.7.Simulation errors for performance metric 2 ( $\Delta t$ =100 microseconds) | .192 |

| Table IV.8.Simulation errors for performance metric 2 ( $\Delta t$ =250 microseconds) | .196 |

| Table IV.9.Simulation errors for performance metric 2 ( $\Delta t$ =500 microseconds) | .200 |

| Table IV.10.Influence of serial steps on run-time                                     | .207 |

## CHAPTER I

## **INTRODUCTION**

## 1.1 INTRODUCTION

Time domain computer simulations of Shipboard Power Systems (SPSs) are required to assess electric-service continuity under hostile conditions in advance of deployment [1]. Said simulations, however, are notoriously slow, limit the number of case studies that can be conducted in a day, and consume many machine hours. Time domain simulations are slow principally due to: the order of full-order SPS models, the quantity and time-varying nature of the component models, and the single-matrix approach taken by simulation programs to perform the simulations.

The purpose of this research is to reduce the run-time of AC-Radial SPS time domain simulation. Time domain simulation is a comprehensive simulation scheme that can be used for the following types of studies: steady-state analysis, short-circuit analysis, power flow analysis, protective device coordination studies, preventive and predictive topology reconfiguration studies, among others. To address the problem of slow SPS time domain simulations, the solution methodology presented in this work parallelizes the simulation of SPSs using multicore computers.

This dissertation follows the style of the IEEE Transactions on Power Systems.

Multicore computers are commercially available desktop computers containing a single processor with embedded (and independent) processing units called cores. The advent of multicore computers has reduced parallel computing costs to an all-time low and has become an attractive low-cost parallel computing option.

Presently, SPS simulation is conducted using either general purpose commercial power system simulation software or real-time simulators. Commercial software simulators are typically used to simulate reduced order SPSs in favor of timely results. The simulation of reduced order SPSs returns fast simulation results at the expense of not knowing the entire system's behavior. Real-time simulators [2-4] are an integrated hardware-software solution used to interface power apparatus and simulations in real-time, are extremely efficient, and are faster than commercial power system simulators. However, real-time simulators are also limited to power systems of small order.

The present-day inability to obtain timely simulation results of full-order SPS simulations has motivated to reducing the run-time of SPS simulation using multicore computers. The approach to parallelize the simulation of SPSs in this work is presented in three stages: discretization and formulation, partitioning, and simulation. A brief description of each stage ensues.

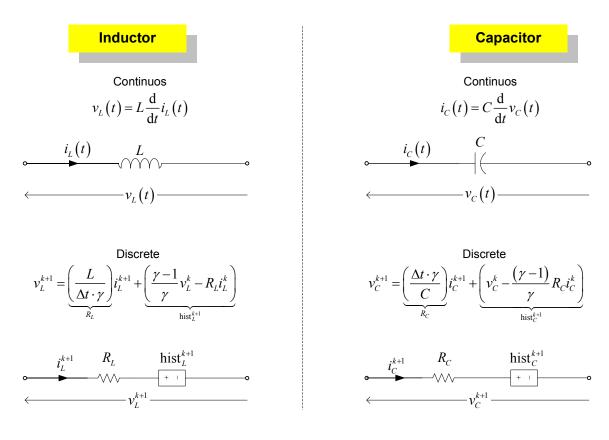

Discretization is the process of mathematically representing a system described in the time domain as a system modeled at discrete intervals of time. To discretize the SPS model used in this work, each SPS component model was discretized by replacing the inductors and capacitors with equivalent discretized branches. After each component model was discretized, the SPS was formulated in loop current as variables by interconnecting all of the discretized component models together. The resulting formulation is a system of equations solved at discrete intervals of time.

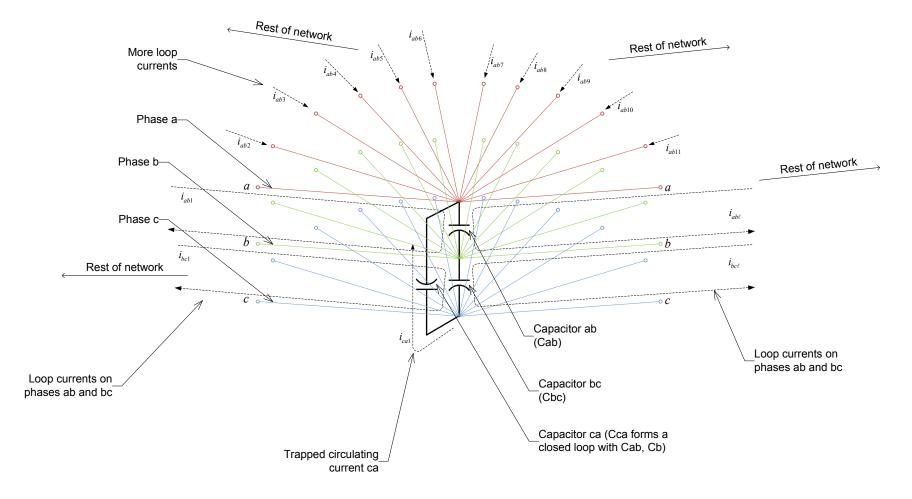

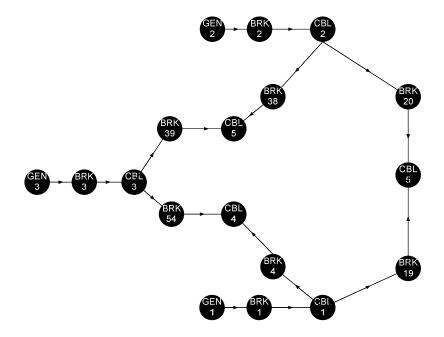

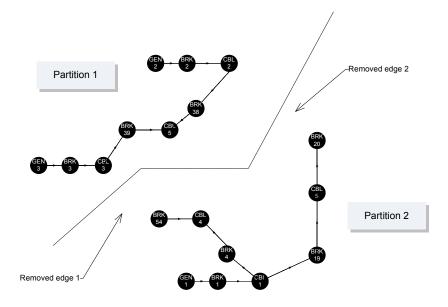

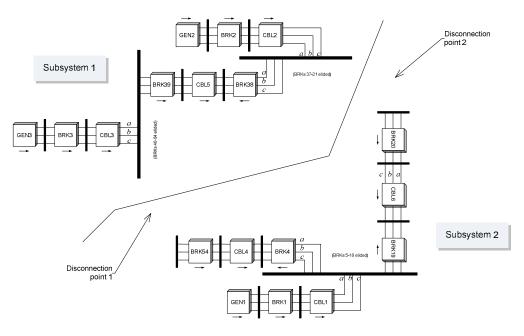

The partitioning stage consists of tearing a SPS into subsystems to parallelize time domain simulations. To determine where to tear the SPS, a weighted graph representative of an SPS was created. Each graph vertex represents a discretized SPS component model and each graph edge represents an electrical junction where two or more component models interconnect. The weight of each vertex is based on the estimated computational effort of solving the equations of the model a vertex represents. This stage begins by partitioning the representative graph using the mincut algorithm [1-2],[3] to produce an initial segregation. To balance the weighted graph partitions, balancing heuristics are used to move vertices across partitions. The edge-cut resulting from the balancing heuristics corresponds to the points of disconnection on the SPS where tearing occurs.

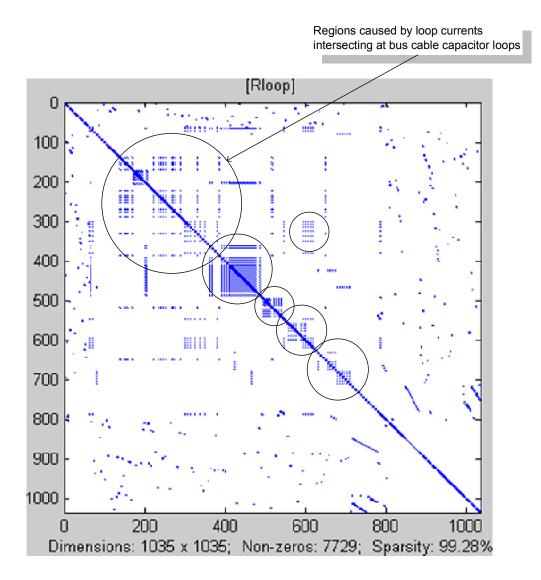

When the points of disconnection of the SPS have been determined, a partitioning approach motivated by diakoptics [4] is used to tear the SPS into subsystems. The partitioning approach presented in this work uses capacitor loops as the points of disconnection. By shorting two (out of three) capacitors on three-phase cables, a large portion of the network matrix's off-diagonal region is depleted producing subsystem decoupling. This rapid off-diagonal depletion is a direct result of the formulation approach taken, which concentrates loop currents at bus node capacitors where most of disconnection points are. Finally, the simulation stage consists of using threads to simulate the SPS subsystems, and manually assigning the threads to the cores of a multicore computer. A multithreaded program was developed in C# to solve SPS subsystems using the electromagnetic transients program (EMTP) solution approach [5], where each subsystem's electrical network is solved before its control network. After finding the loop currents in each subsystem, the branch currents and node voltages for all components are found. Select instantaneous voltages and currents from the electrical network are passed to the control network as inputs to solve controller equations, determine diode commutation times, calculate the root-mean-squared (RMS) voltages and currents, and determine if protective devices should operate.

To assess the performance and validity of the partitioning approach, the speed, accuracies, and time step variations are used as performance metrics. Speed is assessed by taking the ratio between unpartitioned and partitioned simulation run-times. Accuracy is determined by comparing the unpartitioned and partitioned simulation results at each time step of the simulation. The time step was varied to determine how the simulation error (if any) varies when using different time step sizes.

The contributions of this work are in four areas. The first lies in the formulation approach, where the loop currents are concentrated at bus node capacitor loops. This formulation approach is advantageous because tearing only a few capacitors depletes the off-diagonal structure of the network matrix and permits block-diagonalizing the network matrix. The second is related to the first in that after partitioning the representative graph using the mincut algorithm, the SPS subsystems are balanced with a minimal (if any) edge-cut increase. The edge-cut does not increase when vertices at bus nodes are moved to another partition adjacent at the same bus node. The third resides in the tearing of only two out of three capacitors in a loop. By tearing only two capacitors at each boundary, the number of constraint equations is two for each disconnection point regardless of how many graph edges are torn from the same boundary; having only a few constraint equations keeps the computation of the boundary condition low. And the fourth consists in the empirical determination that sequential-parallel SPS simulations (i.e., many threads per core and even with load imbalance) on multicore computers are computationally more efficient than purely parallel simulations. To note, the most important final result is that AC-Radial SPS simulation run-time is significantly reduced at bare cost since multicore computers are already (*virtually*) on every desktop if not all.

## 1.2 ORGANIZATION

This dissertation is organized into five chapters. The second chapter introduces the difficulty of large-scale SPS simulation, justifies the work discussing recent efforts in computational burden reduction, and presents a differential-algebraic (DAE) formulation of a notional AC-Radial SPS. The third chapter describes the solution methodology in three stages: discretization, partitioning, and simulation. The fourth chapter assesses the solution methodology's performance by evaluating three performance metrics. The fifth chapter concludes and examines future work.

#### **CHAPTER II**

#### LITERATURE REVIEW AND PROBLEM FORMULATION

## 2.1 INTRODUCTION

This chapter reviews common commercial power system simulators, introduces AC-Radial SPSs, common solutions to partitioning power systems, and presents the differential-algebraic equation (DAE) formulation of a notional SPS. Power system simulators are also introduced to discuss current simulation tools and simulation approaches. Time domain simulations are introduced to explain how computer resources can be rapidly depleted. A general description of AC-Radial SPSs is presented to introduce the topology and saliencies found on SPSs as the system that will be studied in this work. Since the approaches to parallelize power system simulation is fairly commonplace and well documented elsewhere, only those approaches that frequently appear in the literature are reviewed. The DAE formulation at the end of this chapter is used to assess the complexity of SPS time domain simulations and to estimate the order of a notional SPS.

#### 2.2 MOTIVATION OF THE WORK

Power system simulators rely on analytical methods programmed into desktop computers (e.g., PCs) to simulate behavior of electrical power systems. The drawback of simulators is the lengthy run-time in simulating large-scale electrical networks. The simulation of large-scale electrical networks imposes considerable computational burdens and can rapidly deplete available processing power and memory storage.

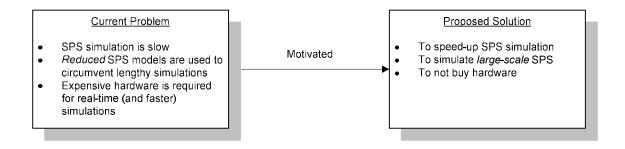

The result of simulations depleting computing resources is a limitation in the system order that can be simulated in a reasonable amount of time. The depletion of processing power and memory is especially true of time domain simulations, where the computational burden is pronounced and millions of data points are saved. Simulation of full order SPSs can take valuable hours, days, or even weeks to complete depending on the case study, order, and simulation end time  $(t_{end})$ . Such time dedication of computational resources may be detrimental to research budgets and has motivated the reduction of run-time by parallelizing SPS simulations. The considerations that motivated this work are summarized in Fig. 2.2.1, where the current problem is depicted on the left side and the aspects desired from a solution are shown on the right.

Fig. 2.2.1. Motives and desired aspects of a solution

In what follows of this chapter, the system order, complexity, and common characteristics found on SPSs are presented. The following subsection introduces AC-

Radial SPSs followed by a formulation that gives an ideal of the system order in the form of DAEs.

2.2.1 AC-Radial Shipboard Power Systems

This section presents a brief overview of AC-Radial SPSs. More details on AC-Radial SPSs are documented in [6-10]. The SPS examined here shares some characteristics of the U.S. CG 61 surface combatant [11].

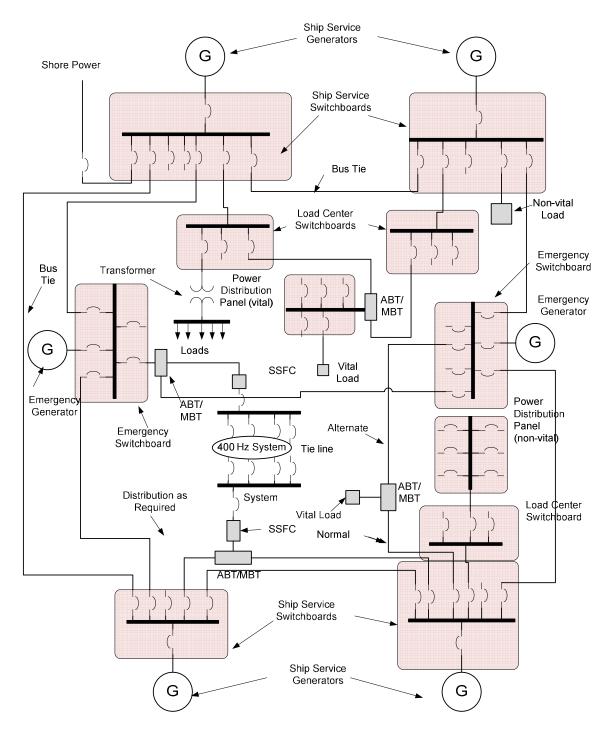

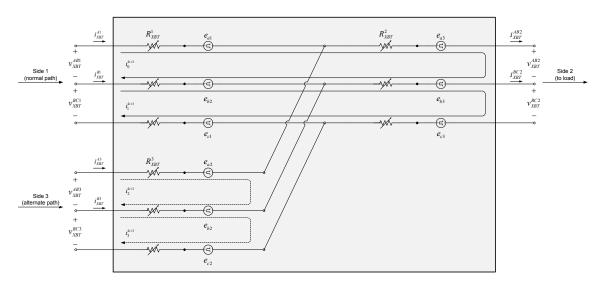

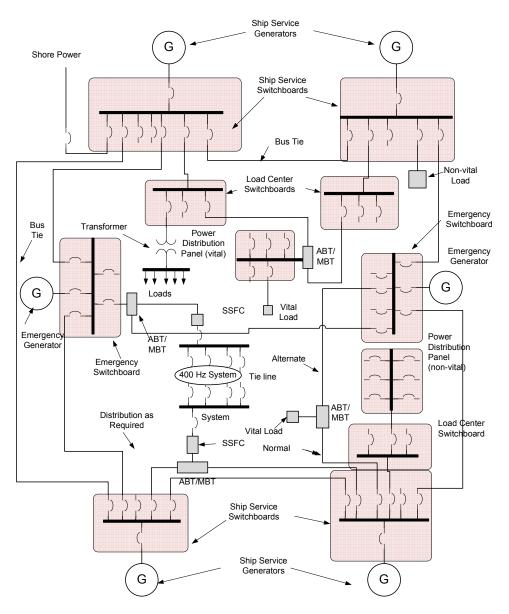

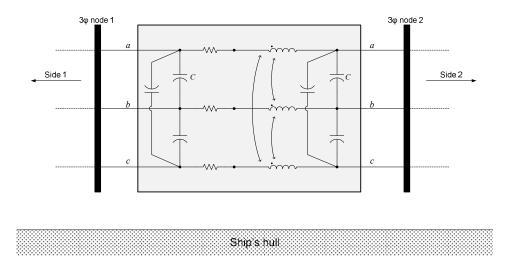

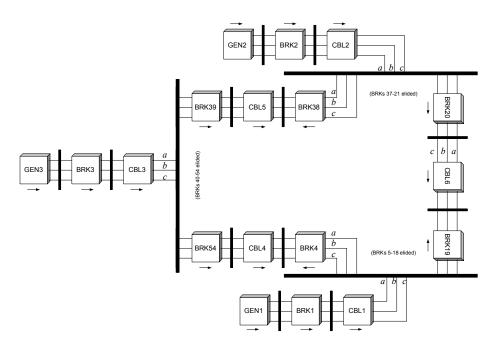

Generally, a combatant type ship consists of a three-generator system in a ring configuration; in typical operation, two generators are used, while the third serves as an emergency supply. Three-phase power is generated and distributed in an ungrounded delta fashion to ensure continued electrical supply despite single-phase to hull faults [9]. An illustration of a notional AC-Radial SPS is given in Fig. 2.2.2.

The voltage is generated at 450V at 60Hz and distributed to the system via switchboards. Generator switchboards are composed of one of more switchgear units and are located close to their associated generators. The switchboards, among themselves, are connected in ring topology so that loads can be fed from any generator. Bus tie circuits interconnect the generator switchboards, which allow for the transfer of power from one switchboard to another.

From each switchboard emanate radial paths to supply loads directly or from load centers. Load centers are distribution centers below the switchboard level and are used to supply power to load concentrations in various areas of the ship. There are two types of loads, non-vital and vital. The non-vital loads have only one supply path to a switchboard and are connected from the load centers. Vital loads have two supply paths

(normal and alternate) and are connected to switchboards or load centers via automaticor manual bus transfers (ABTs and MBTs, or XBTs to refer to either).

The major types of protective devices utilized in the U.S. Navy ship electrical power systems are fuses, circuit breakers, and relays [10]. The purpose of protective devices is to mitigate damage to electrical equipment during abnormal conditions. The fundamental characteristics of protective devices are to monitor system voltage and current levels, detect the presence of abnormalities, and to intelligently reconfigure the routing of power to maintain power continuity at loads vital to crew survival.

The vessel's load to generation ratio is high (i.e., stiffly-connected system); thus, there is not much of a reserve margin in case of severe faults or catastrophic conditions. The generation system is a finite inertia one, where, as opposed to terrestrial systems, generation has a limited capacity. A consequence of finite-inertia systems is that during disturbances the system is prone to pronounced under-frequencies, under-voltages, and inter-rotor oscillations.

A general description of AC-Radial systems was given in this subsection to highlight saliencies that distinguish SPSs from terrestrial power systems. The next section introduces commercial power system simulators.

Fig. 2.2.2. General electrical layout of AC-Radial Shipboard Power Systems [12]

### 2.2.2 Power System Transient Simulators

Available power systems simulators range from commercial ones to free ones [13]. Some well-known commercial simulators are EMTDC/PSCAD [14], ETAP [15], EMTP-RV [16], PLECS [17], SimPowerSystems [18], PowerFactory [19], and PowerWorld [20]. Some of free simulators include ATP [21], InterPSS [22], and VTB [23].

Most simulators solve power systems by implementing the electromagnetic transients program (EMTP) solution approach [5],[24]. The EMTP approach discretizes power system branches (i.e., inductors and capacitors) and forms a large nodal conductance matrix, which corresponds to writing Kirchhoff's current law (KCL) equations at each node. The set of nodal equations have the form  $\mathbf{A} \cdot \mathbf{x} = \mathbf{b}$ , where  $\mathbf{A}$  represents the nodal conductance matrix,  $\mathbf{x}$  represents the vector of node voltages, and  $\mathbf{b}$  represents the vector current injection at each node. The solution of the node voltages takes place in incremental time steps (i.e., at k = 0, k = 1, k = 2, ...) and rapidly becomes burdensome as the order of the system increases. The aforementioned simulators all experience the problem of burdensome time domain simulations and depletion of computational resources which lead to the problems listed in Fig. 2.2.1.

Albeit multicore technology in desktop computers, commercial power system simulators do not fully exploit their potential for parallelism. For example, PSCAD/EMTDC uses two cores: one core for PSCAD [25] to render the graphical interface and run-time meters, and the other for the solver (EMTDC [26]). Since the

solution produced by EMTDC is executed by only one core, the simulation is not a parallel one.

Other simulators such as EMTP-RV [16] have not yet implemented any parallel strategies. At InterPSS [22], a distributed power system simulation approach has been developed. Such approach uses grid-computing, where transient stability case studies for large-scale power systems can be ran simultaneously on different computers. The solution of *each* case study, however, is not divided. Each case study runs concurrently on a different machine. A limitation of distributed grid-computing is the linear speed gain limit, where if M computers are used, the maximum speed gain would be M.

Real-time simulators, such as RTDS<sup>®</sup> and Opal-RT<sup>®</sup>, can partition power systems only if Bergeron's traveling-wave line model can be used. That is, a transmission line of sufficient physical length must exist in order to partition power systems. If said line does not exist in the power system being modeled, short-lines (stublines [27]) with one time step delay can be used instead. The effects of inserting one time step delay stublines where none exist may introduce phase drifts and run longtime simulations unstable [28]. As of this writing, the largest system that can be simulated in real-time is by company Opal-RT<sup>®</sup>, which currently can solve 330 buses in real-time [29] using a cluster of quad-core computers ; however, hardware cost is significant and stublines would be required to partition the short cables on SPSs. A summary of partitioning capabilities (if any) of today's commercial power system simulators is reported in Table II.1.

| Program          | Partitioning Ability                                                               |

|------------------|------------------------------------------------------------------------------------|

| ATP              | Does not partition                                                                 |

| EMTP-RV          | Does not partition                                                                 |

| ETAP             | Does not partition                                                                 |

| InterPSS         | Transient stability case studies possible on a distributed computer                |

| PowerFactory     | Does not partition                                                                 |

| PSCAD/EMTDC      | One thread renders graphics (PSCAD); one thread solves power system (EMTDC)        |

| RSCAD            | Real-time simulation software power systems using Bergeron's travelling-wave model |

| RTLAB            | Real-time simulation software power systems using Bergeron's and/or stublines      |

| SimPowerSystems  | Uses MATLAB's engine which is multicore capable; power systems are not partitioned |

| Virtual Test Bed | Does not partition                                                                 |

TABLE II.1. SUMMARY OF COMMERCIAL POWER SYSTEM SIMULATOR PARTITIONING ABILITIES

\*Information based on in-person conversations and emails with technical support

The concepts of time domain simulation and how computing resources are depleted are presented next. After focusing on background information in time domain simulation, relevant solutions to ameliorate time domain simulations are described.

## 2.2.2.1 Time Domain Simulation

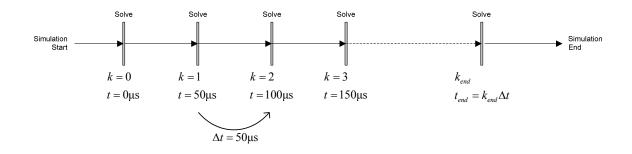

Time domain simulations are computer-based simulations of physical systems for an intended continuum of time (e.g., from  $t_{start} = 0$ s to  $t_{end} = 20$ s). Since computers actuate on clock pulses, computer simulations are inherently a discrete-time processes. To simulate physical systems for an intended continuum of time, said systems are discretized and solved at discrete instances with a time step increments of  $\Delta t$  seconds.

A time line illustrating the concept of time domain simulation is depicted in Fig. 2.2.3. The first time step (step, hereinafter) solved is k = 0, which represents t = 0s. After the system is solved at k = 0, the step advances to k = 1 and the system is solved again using part of the previous solution from k = 0. The integer increments of k are continued throughout the intended simulation time. As illustrated by Fig. 2.2.3, if  $\Delta t = 50 \mu s$ , a simulation of  $t_{end} = 20 s$  would require  $k_{end} = \frac{t_{end}}{\Delta t} = \frac{20}{50 \mu s} = 400,000$  solutions of  $\mathbf{A} \cdot \mathbf{x} = \mathbf{b}$ , which can take hours, days, or even weeks depending on how long the solution at each k takes.

Fig. 2.2.3. Illustation of fixed time step time domain simulation

### 2.2.2.2 Computational Burden

Simulation run-time is directly related to the solution time at each k as illustrated in Fig. 2.2.3. If the solution at step k takes 0.216s to complete, solving 400,000 steps would take  $0.216 \times 400,000/3,600 = 24$  hours. Spending 24 hours on a single casestudy is impractical in terms of the number of cases studies that can be ran in one day; hence, a motivation to reduce the computational burden exists.

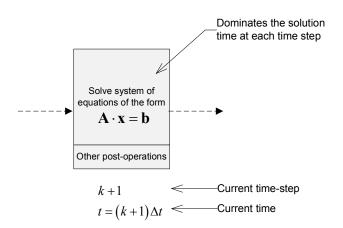

A close-up of the solution process at each k in Fig. 2.2.3 is given in Fig. 2.2.4. In Fig. 2.2.4, a few sub-processes occur at each k (details can be found in Fig. 12.23 in [30]). The solution to  $\mathbf{A} \cdot \mathbf{x} = \mathbf{b}$  at each k constitutes ~90% percent of the solution time, particularly when the order of the system is  $O(10^3)$ .

Fig. 2.2.4 The simulation process at each time step (fixed  $\Delta t$  assumed)

Lengthy run-time often leads researchers into buying costly equipment to speed-up simulation, or modeling reduced equivalent power systems at the expense of not being able to observe system-wide dynamics. An important argument may be made at this point: the main reason time domain simulation is slow is due to the solution of a large system of equations in the form  $\mathbf{A} \cdot \mathbf{x} = \mathbf{b}$  at every time step. If the solution to  $\mathbf{A} \cdot \mathbf{x} = \mathbf{b}$  can be sped up, run-time will be reduced dramatically.

### 2.2.2.3 Memory Depletion

Time domain simulations of power systems aim to capture node voltages and branch current in as many places as possible (i.e., preferably at every relay). To save system-wide voltage and current information, 12 quantities may have to be saved: 3 instantaneous voltages, 3 instantaneous currents, 3 RMS voltages, and 3 RMS currents. To store each of these 12 quantities in memory at each k, computer numbers of type *double* are typically used.

Each double requires 8KB (64 bits) of memory (RAM) on desktop computers. To illustrate how a computer's memory can be depleted, consider saving 12 values per relay and at each k. Supposing there are 100 relays in a system, and  $t_{end} = 20$ s, the total memory that must be allocated is computed in (2.1), which is a considerable amount considering that desktop computers (as of this writing) typically sell with 4GB of RAM (expansion capability to 8-16GB is typical).

$$\frac{\text{Memory}}{\text{Storage}} \rightarrow \underbrace{100}_{\text{relays}} \times \underbrace{12}_{\text{quantities}} \times \underbrace{400,000}_{\text{no. steps}} \times \underbrace{8}_{\text{bytes}} = 3.84 \times 10^9 \approx 3.8\text{GB}$$

(2.1)

If more than 12 quantities were saved at each k, 4GB could be exceeded. Simulations requiring 4GB of memory are impractical and slow down user-interface response times.

To avoid depleting computer memory, it may be possible to i) save numeric data using a different number type (e.g., *floats* instead of *doubles*), ii) save less data per relay (e.g., only instantaneous quantities), iii) reduce the number of relays, iv) simulated for less time, or v) move the data from memory to files on the hard-drive. The former may result in loss of accuracy. Reasons ii)-iv) hinder the ability to observe system-wide dynamic phenomena. The latter solution increases simulation timeas writing data to the file system introduces a new bottleneck.

This section presented the concept of time domain simulation and the main reasons they are slow. The next section reviews common partitioning approaches to reduce simulation run-time.

### 2.3 EXISTING SOLUTIONS TO REDUCE SIMULATION RUN-TIME

The tendency to reduce power system simulation run-time has been, and is, to parallelize power system simulations [31]. However, it is only recently that multicore computers have made this objective a closer and a low-cost possibility. To parallelize power system simulations, the power system models must be partitioned first. A review of power system partitioning methods is reported in this section, where a classification of said methods is shown in Fig. 2.3.1.

Fig. 2.3.1. Classification of power system partitioning methods

Direct methods divide power systems into subsystems, and solve each subsystem using factorization. After the solution of each subsystem takes place, there is an exchange of boundary variables to accountfor the influence of neighbor subsystems. Iterative [32-33] methods solve the subsystems by guessing their solution and then exchanging boundary information several times during the same time step until converge is reached. The present work uses a direct partitioning approach; hence, iterative methods are not considered here. The implementation of a partitioning method to parallelize a power system's simulation can be on a combination of a distributed computer, shared-memory computer, or a sequential computer.

A distributed computer is a group of computers networked together working towards a common goal [34]. Each computer in a distributed computer network is referred to as a computational node, which is a stand-alone computer having independent memory and processor. The communication among computational nodes requires a physical communication network where messages among computational nodes are synchronized by the master computer. The computational nodes may or may not be in physical proximity. The main disadvantage of distributed computers is the communication network's latency, and constitutes a bottleneck in parallel simulations when too many computers are used.

A shared-memory computer is a computer having multiple processing units sharing on-board memory [35]. The processing units communicate by writing/reading to/from on-board shared-memory, which is fast and does not require an external communication network for the processing units to exchange data. A modern day example of shared-memory computers are multicore computers, which have one processor with various internal independent processing units (cores) that can work concurrently. The main drawback of shared-memory computers is that the number of cores is fixed, and cannot be changed unless the computer is replaced.

An alternative form of shared-memory computer is the graphical processing unit (GPU). GPUs are graphical cards embedded in PCs (can be added after purchase) containing cores that also communicate with via shared-memory. GPUs are designed to be extremely fast at processing large graphics data. However, GPU use for non-graphic operations such as scientific computation has drawn much attention in recent years [36]. The main reasons to use GPUs are the performance/\$ or benefit-cost ratio, increasing performance growth (i.e., at a faster rate than PCs), faster on-board memory bandwidth, and outstanding performance: GPUs can outperform PCs in floating-point arithmetic . In this work, GPUs are not considered, because of the need for a user to own specialized hardware, low on-board memory [37], and the initial hardware investment requirement. Multicore computers remain an attractive option due to their larger on-board memory, ubiquity, and positioned market (in-place) infrastructure, which implies a zero-cost investment.

A sequential computer is a computer with one processing unit. Work carried out with single-processor computers is purely sequential and processing cannot be parallelized. Sequential computers are no longer commonplace desktop computers as the advent, low-price, and performance of multicore computers outweigh sequential computers. The work in this dissertation falls under the category of direct methods using a shared-memory (multicore) computer. The next subsection reviews direct partitioning methods relevant to this work.

### 2.3.1 Bergeron's Travelling-Wave Model

Long transmission lines naturally decouple power system areas due to wave propagation delays on transmission lines. This natural decoupling has motivated simulating each power system area on a different processor. The parallel simulation approach that exploits wave propagation delays is known as Bergeron's model [38].

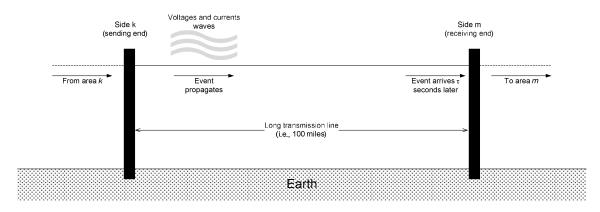

Consider the one-line diagram of a transmission-line shown in Fig. 2.3.2. Due to the line length, an event occurring in area k (sending-end) will not be perceived by area m (receiving-end) until  $\tau$  seconds later. In this regard, Bergeron's equations suggest the equivalent circuit in Fig. 2.3.3.

Fig. 2.3.2 . A long transmission-line representation

In Fig. 2.3.3, the current sources are delayed by  $\tau$  seconds and inject current for events that occurred in the neighbor area  $\tau$  seconds ago (noted as  $t - \tau$ ). The equations describing Bergeron's model are given in (2.2). In (2.2),  $Z_C$  is the characteristic impedance of the line, d is the line length, v is the propagation speed, and  $\{L', C'\}$  are the line's per-unit length inductance and capacitance.

Fig. 2.3.3. Bergeron's equivalent circuit model for a long (lossless) transmission line

$$I_{k} = i_{m} (t - \tau) + \frac{1}{Z_{c}} v_{m} (t - \tau)$$

$$I_{m} = i_{k} (t - \tau) + \frac{1}{Z_{c}} v_{k} (t - \tau)$$

$$\tau = \frac{d}{\upsilon} \quad \upsilon = \frac{1}{\sqrt{L'C'}} Z_{c} = \sqrt{\frac{L'}{C'}}$$

(2.2)

The advantage of Bergeron's model is that power systems can be formulated in block-diagonal form [39] and simulations easily parallelized. Bergeron's method appears frequently in power system partitioning literature and is introduced first.

J. A. Hollman and J. R. Marti [40] used a real-time PC-cluster to simulate terrestrial transmission systems. The inter-PC decoupling was based on Bergeron's model, where each power subsystem was solved on a different computational node. When using two PCs, speed gains of 32.89% and 37.05% were reported [41]. Four years later, the same authors published a paper [40] showing results from a five-computer PC-cluster as well as the expected results from a 19-computer cluster. The gains achieved with five computers neared 4, while the gains expected with 19

computers neared 19, which are close to linear speed-ups. It was shown that Bergeron's model was suitable for PC-cluster implementations which resulted in higher speed gains than when simulating subsystems on a single computer.

D. M. Falcao *et al.* [39] implemented Bergeron's method on a Inmos Transputer T800 connected in a hypercube topology. A speed gain of 4.92 was observed for a power system consisting of 1,026 nodes, 2,457 branches, and 146 lines, partitioned into 77 subsystems.

J. R. Marti and L. R. Linares [42] implemented Bergeron's traveling wave model to simulate small power systems in real-time using an IBM RISC System/6000 Model 560, also on a hypercube architecture. When using two processors, a 45% improvement of speed (gain of 2.22) was reported; 66% (gain 4.93) on four-processors, and gains of  $\leq$  1 beyond four processors. The loss of gain is attributed to the increasingly communication overhead from adding more processors (or when creating more subsystems).

Bergeron's model allows formulating power systems in block-diagonal form and is highly desirable in parallel simulations. However, there is a fundamental limitation intrinsic to Bergeron's model: the time step  $\Delta t$  must be an integer fraction N of the travel-time delay (i.e., must be smaller)  $\tau$  [43] as given by (2.3).

$$\Delta t = \frac{1}{N}\tau = \frac{1}{N}\frac{d}{\nu}$$

(2.3)

For example, for a line of d=10km, the maximum time step (N=1) is restricted to  $\Delta t=50\mu s$  [40] (assuming a phase velocity of  $\upsilon = 200 \times 10^6$  m/s). Application of Bergeron's model in SPSs would result in even a smaller time steps because the transmission lines on SPSs are cables of very short physical length. For example, in a SPS cable of d = 100m (assuming  $v = 200 \times 10^6$  m/s), the time step would be restricted to  $\Delta t \leq 50$ ns and would counter-act any speed gains obtained from parallelizing SPS simulations.

# 2.3.2 The Use of Time Step Delays

Discretization of differential equations results in difference equations with both present and previous time step terms. One approach to parallelize simulations is via explicit integration algorithms (e.g., inductors become historical current sourcesand capacitors become historical voltages sources). Discretization of (2.4) using the trapezoidal rule of integration yields (2.5), where appearance of v(t) on the LHS makes the integration implicit (i.e., the state-variable i(t) and input v(t) are solved simultaneously).

$$v(t) = L\frac{d}{dt}i(t) \tag{2.4}$$

$$\frac{v(t) + v(t - \Delta t)}{2} = \frac{L}{\Delta t} (i(t) - i(t - \Delta t)) \qquad \text{(implicit)} \qquad (2.5)$$

T. Noda and S. Sasaki [44] simulated a power distribution network on a PC-cluster by partitioning the network using explicit integration to create decoupling. The explicit integration presented in [44] is a modified version of the trapezoidal rule, which is given in (2.6). The advantage of explicit integration is that state-variables can be expressed as functions of previous time step (i.e., known) values. For example, in (2.6) if  $i_L(t)$  represents an inductor's current, an inductor branch can be modeled as a historical current source instead of in resistive-companion form [45].

Explicit integration permits partitioning inductors by current source transportation [46], and shunt capacitances by voltage splitting. In [44] the simulation speed gain resulting from explicit integration to partition distribution lines was the use of  $\Delta t=85\mu s$  at a real-time simulation speeds.

$$\frac{3}{2}v(t-\Delta t) - \frac{1}{2}v(t-2\Delta t) = \frac{L}{\Delta t}(i(t)-i(t-\Delta t)) \quad (\text{explicit}) \quad (2.6)$$

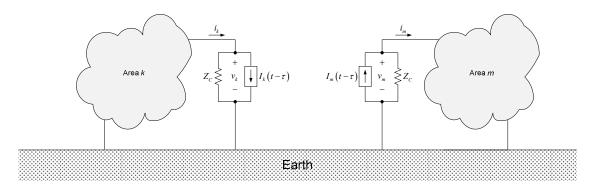

Another method to parallelize simulations based on time step delays is the latency insertion method (LIM) [47-48]. The LIM algorithm takes advantage of the inherent latency in inductors and capacitors to generate a leapfrog algorithm, which first solves for an electrical network's branch currents and then for the node voltages. In the LIM, if branches do not contain inductors, or if nodes do not contain capacitors, inductors and capacitors are artificially added to force the latency exploited by the leapfrog algorithm. When using the LIM, all branches and nodes are treated as shown in Fig. 2.3.4. The independent sources are non-zero only if they are physical present.

Fig. 2.3.4. Branch (left) and node (right) as modeled by the latency insertion method

In the LIM, which uses the backward Euler discretization, the branch currents and node voltages in Fig. 2.3.4 are discretized and solved as (2.7) and (2.8), respectively.

$$i_{ij}^{k+1} = i_{ij}^{k} + \frac{\Delta t}{L_{ij}} \left( v_{ij}^{k+\frac{1}{2}} - R_{ij} i_{ij}^{k} + E_{ij}^{k+\frac{1}{2}} \right)$$

(2.7)

$$v_i^{k+\frac{1}{2}} = \frac{\frac{C_i v_i^{k-\frac{1}{2}}}{\Delta t} + H_i^k - \sum i_k}{\frac{C_i}{\Delta t} + G_i}$$

(2.8)

At time step k + 1, the leapfrog algorithm first solves for all branch currents using (2.7). Once all branch currents are known, and before advancing the time step to k + 2, all node voltages are solved using (2.8). The notation  $k + \frac{1}{2}$  in (2.8) indicates that the node voltages are found from a post-computation following the branch current solution at k + 1. Once the time step is advanced to k + 2, the voltages found at  $k + \frac{1}{2}$  are used to compute the branch currents at k + 2 by using (2.7) again. The pattern of latency exploitation is clear as branch currents and node voltages are solved separately leaping back-and-forth between their solutions.

Watanabe *et al.* [49] used the LIM leapfrog method to parallelize the simulation of a power distribution network on a PC-cluster. The speed gains reported were between 20-100 times with an efficiency of 94% when using five computational nodes. The approach used to parallelize the simulations was to divide a large power distribution network into subsystems, where each subsystem was assigned to a different computational node.

At the subsystem boundaries there are a deliberate number of repeated (interface) branches and nodes considered the subsystem overlap. The subsystem overlap simultaneously exists on all subsystems created from the same boundary. At each time step of the simulation, each subsystem solves for its branch currents and node voltages using (2.7) and (2.8), respectively. Before advancing the time step, the subsystems exchange their branch current by sending them across the communication network. After receiving the currents from the adjacency subsystems, the boundary node voltages are updated by injecting the received current.

There are limitations in the LIM that prevent its application to SPSs. The first limitation is that datum nodes in SPS do not exist because when SPSs are modeled as purely ungrounded. Thus, the node model on the right of Fig. 2.3.4 cannot be formed. If said node model does not exist, the leapfrog algorithm cannot be used. Another limitation is the time step size requirement. In the case a fictitious (virtual) datum node were created for SPSs, shunt capacitors would have to be added to every node. Further, all branches containing capacitors would require inductors to be added to the same branches. Adding inductors to all branches containing capacitors, and adding capacitors to all nodes not containing capacitors, implies adding parasitic inductances and capacitances to the system. Parasitic reactance introduces fast transients that may not be physically presented and require a very small  $\Delta t$  to observe.

Moreover, to maintain numerical stability after introducing parasite reactance, it is recommended that the  $\Delta t \leq \sqrt{LC}$ , where *L* represents a branch inductance and *C* represents a node's shunt capacitance. In [49] time steps were in the order of  $O(10^{-12})$ , which does not make  $\Delta t \leq \sqrt{LC}$  a significant restriction. However, in power system simulation the typical time step is  $\Delta t = 50 \mu s$ . Unless the time step is decreased, unstable simulations are possible. If the time step is reduced to  $O(10^{-9})$ , run-time is significantly affected. If instead of using parasitic values for inductors and capacitors, larger values are were used instead, the physical significant of the results change. Other uncertainties regarding the application of LIM to SPSs are the suitability to time-varying and ungrounded networks, which have not been reported.

At Florida State University, a 9-rack RTDS® simulator [50] implements time step latency in two ways. The first is to create SPS subsystems by using transmission lines with travel-times of  $\Delta t$  [50-51]. It is noted that this line is not physically present on a SPS model; the line is intentionally placed in the SPS model to form subsystems from time step delays. The idea of placing (where physically not present) a  $\Delta t$  travel-time transmission line is to mimic Bergeron's travelling-wave model explained earlier.

The second method is to use a cross-rack transformer model to insert a latency and partition DC links. When partitioning DC links, the latency comes about inserting an

inductor of specified value such that simulation stability is warranted. Since partitioning by insertion of latencies is artificial, its impact on simulation results should be carefully studied [52] and, hence, is not considered in this work.

#### 2.3.3 Diakoptics-based Partitioning Approaches

Diakoptics (from Greek *kopto* meaning *to tear*, and English *dia* interpreted as *systems*) is a term associated with the work developed by G. Kron on tensorial analysis [53], which gave rise to a piecewise solution of large networks [4]. Between June 7, 1957 and February 22, 1959, G. Kron published a serial called "*Diakoptics*-The Piecewise Solution of Large-Scale Systems" in the *Electrical Journal*, London (formerly the *Electrician*), which later became available under one cover [4]. Kron's motivation was to obtain inter-area power flows knowing only intra-area power flows [54].

G. Kron's new partitioning theory was unique as it could solve large network problems using only the solutions of its component parts. Diakoptics was introduced before the digital computer, and did not receive attention until only after the sparse matrix ordering techniques suggested by Tinney [55], the discretization for computer simulation proposed by Dommel [5], and the modified nodal analysis formulation proposed by Ho [56], which became dominant and efficient digital computer methods. The introduction of Modified Nodal Analysis (MNA) by Ho and the reduction of computer size and cost led to believe that one computer alone was sufficient to solve power systems of moderate sizes during the 1970s. Diakoptics is not taught in academia and is rarely found in electrical engineering textbooks. Other approaches, asides from diakoptics, have become main stream in the recent decades and most of the literature on partitioning does not address diakoptics as a viable option; perhaps, for the same reason that it disappeared during its beginnings. Diakoptics lost popularity before it was well established, but those who used it did see and learnt from its efficient advantages [54],[57-59].

G. Kron showed that an electrical network represented as (2.9) and solution (2.10), where  $\mathbf{A}_{orig}$  is the original network (coefficient) matrix,  $\mathbf{x}$  the vector of unknown variables, and  $\mathbf{b}$  is the input vector, could be torn in *p* subsystems and reformulated as (2.11). Equation (2.11) leads to the parallelizable form in (2.12).

$$\mathbf{A}_{orig}\mathbf{x} = \mathbf{b} \tag{2.9}$$

$$\mathbf{x} = \mathbf{A}_{orig}^{-1} \mathbf{b} \tag{2.10}$$

$$\begin{bmatrix} \mathbf{A}_{block} & | \mathbf{D} \\ \mathbf{D}^{\mathrm{T}} & | -\mathbf{S}^{-1} \end{bmatrix} \begin{bmatrix} \mathbf{x} \\ \mathbf{u} \end{bmatrix} = \begin{bmatrix} \mathbf{b} \\ \mathbf{0} \end{bmatrix}$$

(2.11)

$$\mathbf{A}_{block} = \begin{bmatrix} \mathbf{A}_1 & & & \\ & \mathbf{A}_2 & & \\ & & \ddots & \\ & & & \mathbf{A}_p \end{bmatrix}; \qquad \mathbf{x} = \begin{bmatrix} \mathbf{x}_1 \\ \mathbf{x}_2 \\ \vdots \\ \mathbf{x}_p \end{bmatrix}_{n \times 1}; \qquad \mathbf{b} = \begin{bmatrix} \mathbf{b}_1 \\ \mathbf{b}_2 \\ \vdots \\ \mathbf{b}_p \end{bmatrix}; \qquad \mathbf{u} = \begin{bmatrix} u_1 \\ u_2 \\ \vdots \\ u_r \end{bmatrix};$$

$$\mathbf{D} = \begin{bmatrix} \mathbf{D}_1 \\ \mathbf{D}_2 \\ \vdots \\ \mathbf{D}_p \end{bmatrix}; \qquad \mathbf{S} = \begin{bmatrix} S_1 & \cdots & \\ & S_2 & \cdots & \\ & & \ddots & \\ & & & & S_r \end{bmatrix};$$

$$\mathbf{D}(i, j) \rightarrow \begin{cases} = 1, & \text{if } x_i \text{ is positively coupled to } \mathbf{u}_j \\ = -1, & \text{if } x_i \text{ is negatively coupled to } \mathbf{u}_j \\ = 0, & \text{if } x_i \text{ is not coupled to } \mathbf{u}_j \end{cases}$$

where

$\mathbf{b}_i$  = excitation vector of subsystem *i*

- $\mathbf{x}_i$  = unknown variable vector of subsystem *i*

- $\mathbf{A}_i$  = network matrix of subsystem *i*

$\mathbf{A}_{block} =$ block-diagonal matrix of all subsystems'  $\mathbf{A}_{i}$

- $\mathbf{D}_i$  = tensor relating network and boundary variables

- S = diagonal matrix of torn branch immitances

- $\mathbf{u}$  = vector of torn branch boundary variables

- $\cdot$  = zero matrix

- p = number of network partitions.

$$\mathbf{x} = \mathbf{A}_{block}^{-1} \mathbf{b} - \mathbf{A}_{block}^{-1} \mathbf{D} \Big( \mathbf{S}^{-1} + \mathbf{D}^{\mathrm{T}} \mathbf{A}_{block}^{-1} \mathbf{D} \Big)^{-1} \Big( \mathbf{D}^{\mathrm{T}} \mathbf{A}_{block}^{-1} \mathbf{b} \Big).$$

(2.12)

The power systems research group at the University of British Columbia (UBC) has a PC-based real-time simulator (OVNI [28],[60]) that uses a two-level partitioning approach. The first level of partitioning uses Bergeron's traveling wave model to form subsystems that can be solved on different PC-cluster computers. The second level of partitioning is to use a diakoptics-based formulation (called MATE [61]), which tears resistive lines (inter-area links) to create subdivisions from the first-level subsystems.

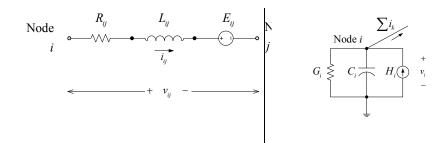

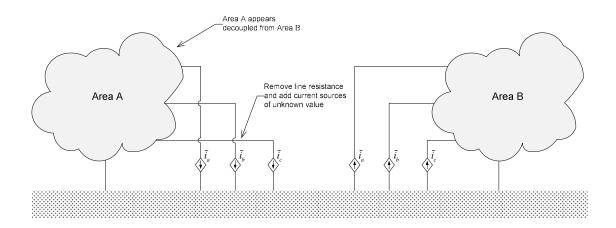

In [28],[60] J. R. Marti and L. R. Linares used diakoptics to tear the resistance of lumped lines as illustrated by Fig. 2.3.5-Fig. 2.3.6. In Fig. 2.3.5 the areas joined by the line resistance were decoupled by replacing the line resistance by current sources of unknown value. After replacing the resistance with current sources, from the principle of current source transportation [46], the current sources were torn as current sinks (left) and current sources (right) as shown in Fig. 2.3.6.

Fig. 2.3.5. Two areas joined by an inter-area link (lumped resistances)

Fig. 2.3.6. Two areas decoupled by current source transportation [46]

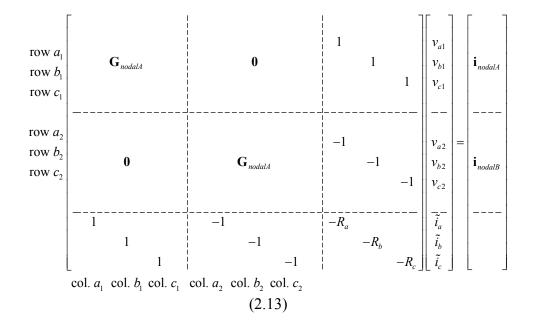

To solve the partitioned system shown in Fig. 2.3.6, the current source constraint equations are included in the system formulation (MATE). The network matrix for the system in Fig. 2.3.6 is given in (2.13), where  $G_{nodalA}$  is the nodal conductance matrix of Area A, **0** is a zero matrix, and  $i_{nodalA}$  is the current injection vector for Area A. The unknown current source values are included in the lower part of node voltage vector and

are part of the system's solution (i.e., solved simultaneously with the node voltages). Equation (2.13) has the form of (2.11), which is a diakoptical formulation.

K. W. Chan *et al.* [62] implemented a PC-based real-time simulator connected in a 4D-hypercube using diakoptics as the inter-processor partitioning scheme. The solution for an 811-busbar power system was measured in terms of speed gain and efficiency. The speed gain is the ratio between unpartitioned and partitioned simulation times. The efficiency is the ratio between speed gain and the number of processors used. When using two processors, the speed gain and efficiency were 1.76 and 88.2%, respectively. When using 16 processors, the speed gain and efficiency were 4.77 and 29.79%. The speed gains reported are sub-linear and show that inter-processor communication severely influences the overall performance of the parallel simulations. Another influential aspect is the computational imbalance among subsystems. The computation limbalance manifests itself as efficiency and is dominated by the processor finishing last

at each time step (i.e., ideally, all processors finish their solutions at the same time). The major bottleneck of diakoptics is the communication overhead in unifying the subsystem solutions to obtain the overall solution.

S. Jiwu *et al.* [63] implemented an eight-computer cluster using diakoptics as the inter-processor partitioning scheme for transient stability simulations. The authors improved the coarse-grained algorithm used by K. W. Chan in [62] by proposing a multilevel partitioning scheme and a hierarchical form of the bordered-block diagonal form power network algorithm. Cluster optimizations are also used to reduce the bottleneck of the partitioning scheme. The three case studies presented by the authors reported sub-linear and super-linear speed gains for transient stability studies. Speed-gains of near ten were attained for eight processors, and efficiencies of 180% were attained for four processors, which improved the results in [62]. The work in [63] addresses transient stability simulations, which is not the main endeavor of this work. However, it should be noticed that super-linear gains and good efficiencies are possible using diakoptics.

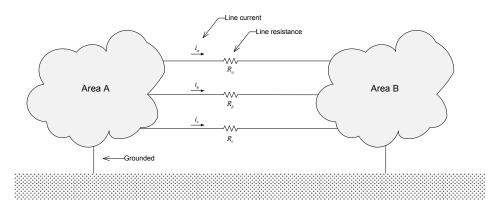

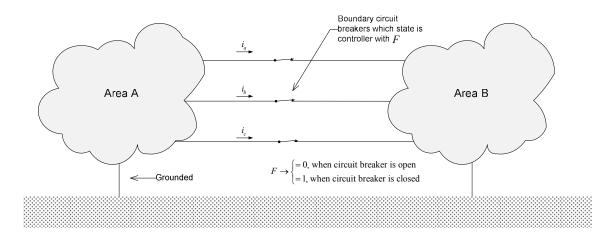

A. Kalantari [64] and S. Esmaeili [65] used a diakoptical formulation for inter-area steady-state fault studies. Ideal circuit breakers at the onset of subsystems were used to create boundaries of disconnection as shown in Fig. 2.3.7; if circuit breakers did not exist at the desired locations, they were inserted in place. The inter-area constraint equations include the circuit breakers' status (F=0 when open, and F=1 when closed). The diakoptical formulation used by A. Kalantari *et al.* is given in (2.14).

$$\begin{bmatrix} \mathbf{Y}_{1} & \cdot & \cdot & \cdot & \cdot & \mathbf{C}_{1} \\ \cdot & \mathbf{Y}_{2} & \cdot & \cdot & \mathbf{C}_{2} \\ \cdot & \cdot & \cdot & \cdot & \cdot & \mathbf{I}_{s} \\ \hline \mathbf{F}\mathbf{C}_{1}^{\mathrm{T}} & \mathbf{F}\mathbf{C}_{2}^{\mathrm{T}} & \cdots & \mathbf{F}\mathbf{C}_{p}^{\mathrm{T}} \begin{bmatrix} \mathbf{C}_{s} \\ \mathbf{C}_{s} \end{bmatrix} \begin{bmatrix} \mathbf{V}_{1} \\ \mathbf{V}_{2} \\ \vdots \\ \mathbf{V}_{p} \\ \mathbf{I}_{ex} \end{bmatrix} = \begin{bmatrix} \mathbf{I}_{1} \\ \mathbf{I}_{2} \\ \vdots \\ \mathbf{V}_{p} \\ \mathbf{I}_{ex} \end{bmatrix} = \begin{bmatrix} \mathbf{I}_{1} \\ \mathbf{I}_{2} \\ \vdots \\ \mathbf{I}_{s} \\ \mathbf{0} \end{bmatrix}$$

(2.14)

where:

- $\mathbf{I}_i$  = current injection vector of subsystem *i*

- $\mathbf{V}_i$  = vector of unknown voltages of subsystem *i*

- $\mathbf{Y}_i$  = admittance matrix of subsystem *i*

- $C_i$  = connection matrix relating subsystem *i*'s internal node currents to its boundary currents

- $\mathbf{I}_{ex}$  = boundary current injections

- F = variable parameter that determines that status

of boundary circuit breakers

*s* = number of network partitions.

Fig. 2.3.7. Two areas joined by ideal circuit breakers

The network equations in [64] were parallelized by first solving the network with the circuit breakers open, and then with the breakers closed. The fault study solution approach in [64] is computationally efficient because obtaining the new fault prevoltages does not require re-factoring the entire network matrix, only portions of each subsystem's bus impedance matrices (also called the Woodbury's method of inverting modified matrices [66-68]). The work in [64] was presented for steady-state results; the work in [65] for transient stability studies, grounded networks, use nodal analysis, and their breaker models did not exhibit arcing characteristics.

The main disadvantages of diakoptics are that branches must exist at the boundaries of disconnection for constraint equations to be written and that the computation of the patch term becomes computationally expensive as the number of partitions increases; more so in distributed computers having physical communication network delays. The former disadvantage poses a limitation on the number of places where a network can be torn, and limits the maximum number of partitions possible. The latter disadvantage is due to the sequential work required to compute the boundary conditions at each disconnection point. The larger the number of partitions, the larger the sequential work involved in said boundary condition computation. While the boundary conditions are computed, the solution to the subsystems is halted until the boundary conditions are known.

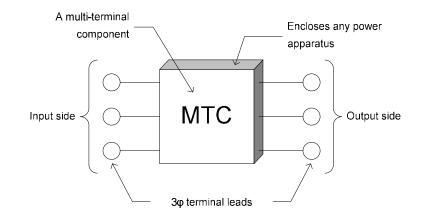

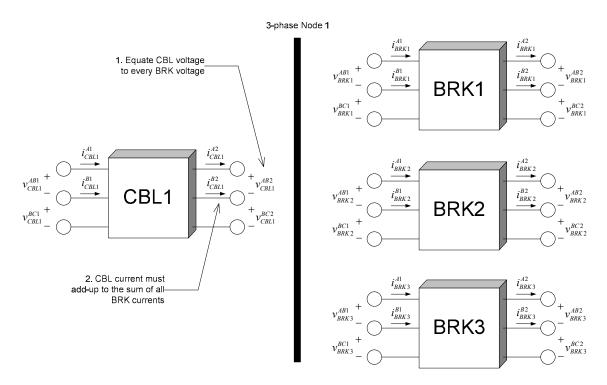

# 2.4 DIFFERENTIAL-ALGEBRAIC FORMULATION OF A NOTIONAL SHIPBOARD POWER SYSTEM