# CMOS INTEGRATED CIRCUIT DESIGN FOR ULTRA-WIDEBAND TRANSMITTERS AND RECEIVERS

A Dissertation

by

**RUI XU**

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

August 2009

Major Subject: Electrical Engineering

# CMOS INTEGRATED CIRCUIT DESIGN FOR ULTRA-WIDEBAND TRANSMITTERS AND RECEIVERS

A Dissertation

by

**RUI XU**

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Cam Nguyen Committee Members, Laszlo Kish

Anthony Cahill Andrew K. Chan

Head of Department, Costas N. Georghiades

August 2009

Major Subject: Electrical Engineering

#### ABSTRACT

CMOS Integrated Circuit Design for Ultra-Wideband

Transmitters and Receivers. (August 2009)

Rui Xu, B.S., Southeast University, China;

M.S., Southeast University, China

Chair of Advisory Committee: Dr. Cam Nguyen

Ultra-wideband technology (UWB) has received tremendous attention since the FCC license release in 2002, which expedited the research and development of UWB technologies on consumer products. The applications of UWB range from ground penetrating radar, distance sensor, through wall radar to high speed, short distance communications. The CMOS integrated circuit is an attractive, low cost approach for implementing UWB technology. The improving cut-off frequency of the transistor in CMOS process makes the CMOS circuit capable of handling signal at multi-giga herz. However, some design challenges still remain to be solved. Unlike regular narrow band signal, the UWB signal is discrete pulse instead of continuous wave (CW), which results in the occupancy of wide frequency range. This demands that UWB front-end circuits deliver both time domain and frequency domain signal processing over broad bandwidth. Witnessing these technique challenges, this dissertation aims at designing novel, high performance components for UWB signal generation, down-conversion, as well as accurate timing control using low cost CMOS technology.

We proposed, designed and fabricated a carrier based UWB transmitter to facilitate the discrete feature of the UWB signal. The transmitter employs novel two-stage -switching to generate carrier based UWB signal. The structure not only minimizes the current consumption but also eliminates the use of a UWB power amplifier. The fabricated transmitter is capable of delivering tunable UWB signal over the complete 3.1GHz -10.6GHz UWB band. By applying the similar two-stage switching approach, we were able to implement a novel switched-LNA based UWB sampling receiver frontend. The proposed front-end has significantly lower power consumption compared to previously published design while keep relatively high gain and low noise at the same time. The designed sampling mixer shows unprecedented performance of 9-12dB voltage conversion gain, 16-25dB noise figure, and power consumption of only 21.6mW(with buffer) and 11.7mW(without buffer) across dc to 3.5GHz with 100M-Hz sampling frequency.

The implementation of a precise delay generator is also presented in the dissertation. It relies on an external reference clock to provide accurate timing against process, supply voltage and temperature variation through a negative feedback loop. The delay generator prototype has been verified having digital programmability and tunable delay step resolution. The relative delay shift from desired value is limited to within 0.2%.

# DEDICATION

To my parents, my wife and those friends who supported me during this undertaking.

#### ACKNOWLEDGEMENTS

Along the journey towards this doctoral degree, it would never be possible to come up with this dissertation and all the work that was put into it, without the generous assistance and support of many people. At first, my most sincere appreciation goes to my academic advisor Professor Cam Nguyen. It has been a great experience to work under his mentoring. His extensive technical knowledge and keen insight have guided me into the field of RF circuit design. He showed me not only handy skills of conducting state-of-the-art research but also good working ethics leading to professional successfulness. All of these will benefit my entire life.

My thanks also goes to my fellow lab mates Xin Guan, Yalin Jin, Mohan Chirala and Meng Miao. Five years of working, studying and having fun with them have been one of my most memorable experiences during my Ph.D. study.

I would also like to express my appreciation to my committee member Dr. Laszlo Kish, Dr. Andrew K. Chan and Dr. Anthony Cahill for serving on my committee and their guidance during my Ph.D. study.

I also wish to thank the National Science Foundation, the Air Force Research Laboratory and the US Army for their support of my research work.

Lastly, I would like to save my deepest gratitude to my parents who always have faith in me during many up-and-downs in my life. I couldn't have done it without your support even it's from the other side of the ocean.

# TABLE OF CONTENTS

|                                                                                                                                                                                       | Page                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| ABSTRACT                                                                                                                                                                              | iii                        |

| DEDICATION                                                                                                                                                                            | v                          |

| ACKNOWLEDGEMENTS                                                                                                                                                                      | vi                         |

| TABLE OF CONTENTS                                                                                                                                                                     | vii                        |

| LIST OF FIGURES                                                                                                                                                                       | ix                         |

| LIST OF TABLES                                                                                                                                                                        | XV                         |

| CHAPTER                                                                                                                                                                               |                            |

| I INTRODUCTION                                                                                                                                                                        | 1                          |

| 1.1 Background and motivation                                                                                                                                                         |                            |

| II ULTRA-WIDEBAND TECHNOLOGY OVERVIEW                                                                                                                                                 | 5                          |

| 2.1 Brief history of UWB technology                                                                                                                                                   | 20<br>26<br>26<br>27<br>27 |

| III CARRIER BASED UWB TRANSMITTER DESIGN                                                                                                                                              |                            |

| 3.1 CMOS UWB pulse generator 3.2 Carrier based UWB transmitter architecture 3.3 The implementation of UWB transmitter 3.3.1 CMOS SPST switch design 3.3.2 CMOS pulse generator design | 33<br>39<br>39             |

| CHAPTER  |                                                       | Page |

|----------|-------------------------------------------------------|------|

|          | 3.3.3 Measurement results                             | 49   |

| IV       | UWB SAMPLING RECEIVER FRONT END DESIGN                | 56   |

|          | 4.1 The modeling of sample and hold circuit           | 56   |

|          | 4.2 Sampling switch design                            | 62   |

|          | 4.3 Integrated sampling mixer front-end architecture  | 64   |

|          | 4.4 Switching LNA design                              | 69   |

|          | 4.5 Time domain performance of the sampling mixer     | 74   |

|          | 4.6 Measurement results                               | 81   |

| V        | UWB ACCURATE DELAY GENERATOR                          | 87   |

|          | 5.1 Delay locked loop based delay generator (DLL)     | 90   |

|          | 5.1.1 Design of delay cell                            | 92   |

|          | 5.1.2 The design of reference DLL core                | 97   |

|          | 5.1.3 Simulation results                              | 99   |

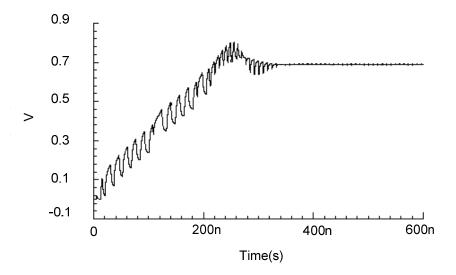

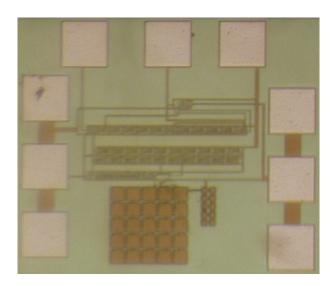

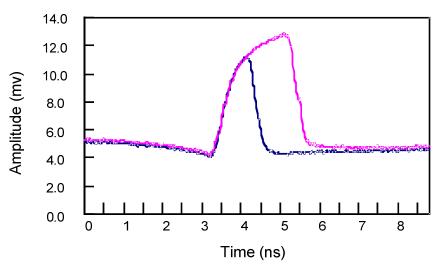

|          | 5.2 PLL based delay generator                         | 102  |

|          | 5.2.1 Phase detector design                           | 103  |

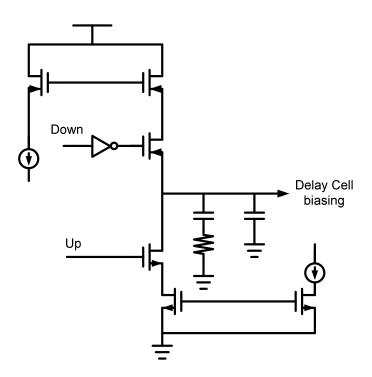

|          | 5.2.2 Charge pump and loop filter design              | 106  |

|          | 5.2.3 Experimental results                            | 106  |

| VI       | CONCLUSION                                            | 109  |

|          | 6.1 Summary of the research                           | 109  |

|          | 6.2 Recommended future work                           | 111  |

|          | 6.2.1 System integration                              | 111  |

|          | 6.2.2 LNA topology and switching scheme investigation | 111  |

|          | 6.2.3 Delay generator programmable divider            | 111  |

| REFERENC | CES                                                   | 112  |

| VITΔ     |                                                       | 117  |

# LIST OF FIGURES

|             |                                                                                                     | Page |

|-------------|-----------------------------------------------------------------------------------------------------|------|

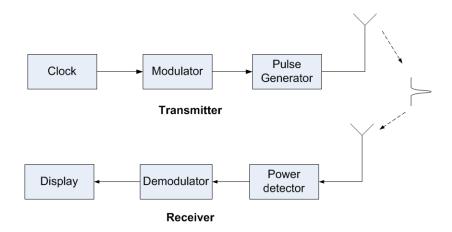

| Figure 2.1  | System diagram of base-band pulse communication from G. F. Ross[3]                                  | 5    |

| Figure 2.2  | Waveforms of different building blocks in based-band pulse radar systems                            | 6    |

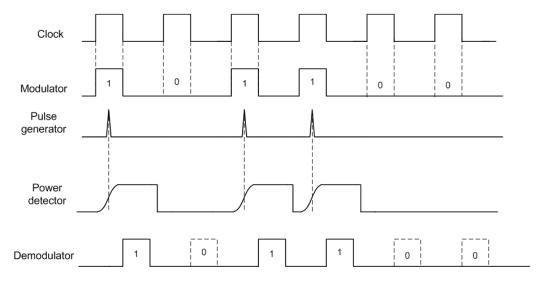

| Figure 2.3  | The configuration of pulse ground penetrating radar by Morey[5]                                     | 8    |

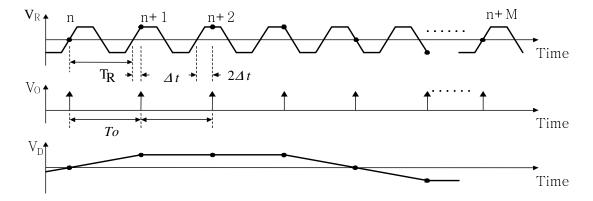

| Figure 2.4  | Illustration of synchronous sampling                                                                | 9    |

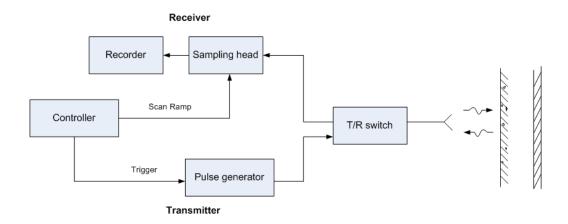

| Figure 2.5  | Simplified block diagram of MIR                                                                     | 10   |

| Figure 2.6  | Waveform of main components in MIR                                                                  | 10   |

| Figure 2.7  | Possible commercial applications for UWB technology                                                 | 12   |

| Figure 2.8  | Simplified construction of UWB system with coherent receiving                                       | 14   |

| Figure 2.9  | Signal timing diagram of coherent receiving based UWB system                                        | 14   |

| Figure 2.10 | Building blocks of non-coherent receiving based UWB system                                          | 15   |

| Figure 2.11 | UWB spectral mask for indoor communication by FCC                                                   | 17   |

| Figure 2.12 | 2 Frequency plan for multi-band OFDM based proposal                                                 | 18   |

| Figure 2.13 | Multiband signal transmitted at different time slot                                                 | 18   |

| Figure 2.14 | Direct conversion based MB-OFD UWB transceiver                                                      | 19   |

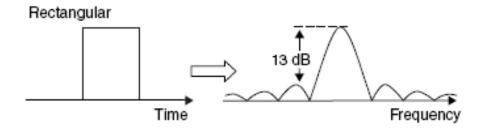

| Figure 2.15 | Time domain and frequency domain plot of a rectangular pulse                                        | 20   |

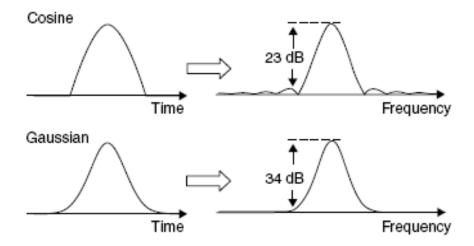

| Figure 2.16 | Time domain and frequency domain plot of a cosine and Gaussian based pulse                          | 21   |

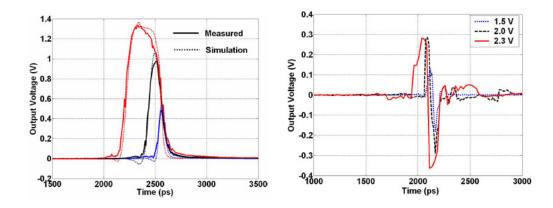

| Figure 2.17 | Measured time domain waveform of impulse at input and output of a wideband antenna proposed in [10] | 23   |

|             | ı                                                                                                                                           | age |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

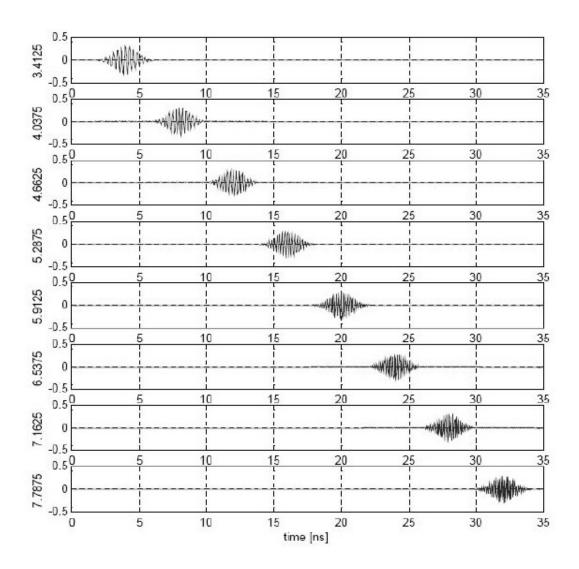

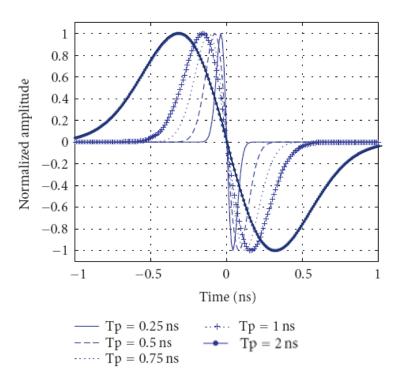

| Figure 2.18 | Time domain waveform of Gaussian mono-pulse with different $T_p$                                                                            | 24  |

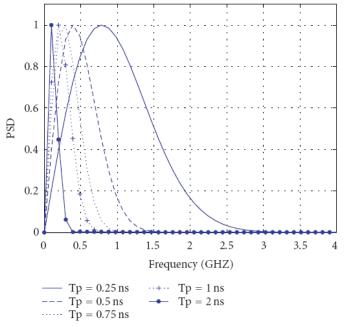

| Figure 2.19 | Spectrum of Gaussian mono-pulse with different $T_p$                                                                                        | 24  |

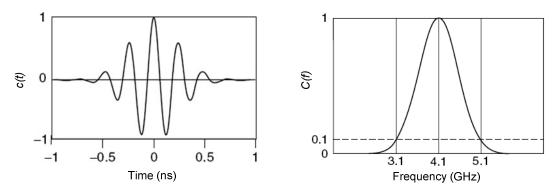

| Figure 2.20 | Time domain and frequency domain mapping of carrier-based UWB signal                                                                        | 25  |

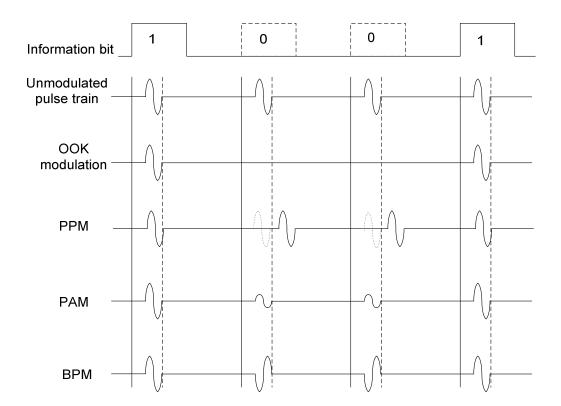

| Figure 2.21 | Comparison of different pulse modulation schemes for UWB communications                                                                     | 28  |

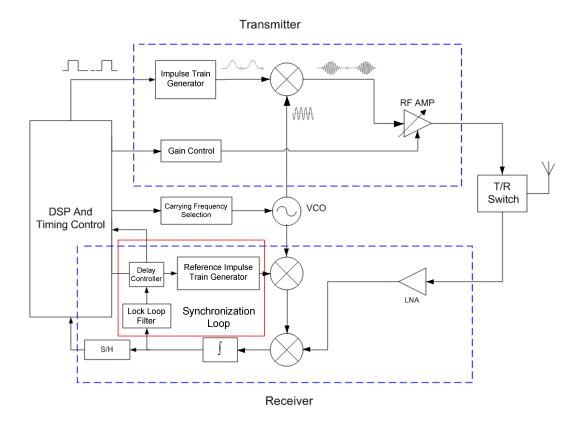

| Figure 2.22 | Multifunctional UWB system architecture                                                                                                     | 30  |

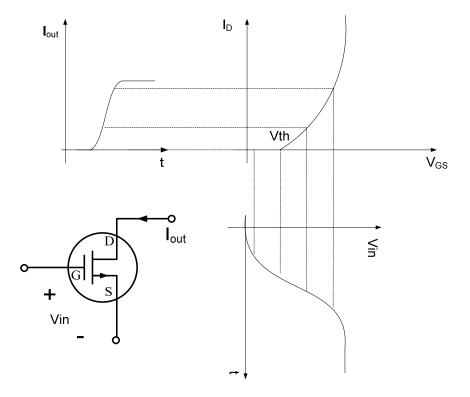

| Figure 3.1  | Step sharpening effect of MOSFET                                                                                                            | 33  |

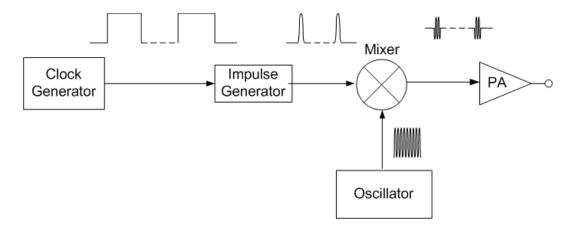

| Figure 3.2  | Block diagram of a typical carrier-based UWB transmitter.                                                                                   | 34  |

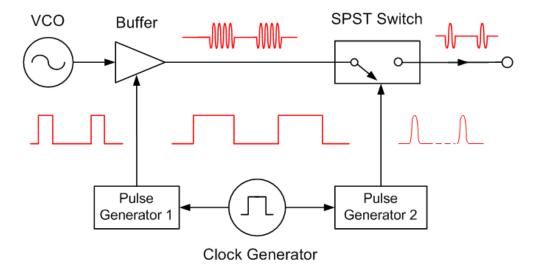

| Figure 3.3  | The proposed carrier-based UWB transmitter topology                                                                                         | 36  |

| Figure 3.4  | Waveforms of the building blocks in the proposed UWB transmitter                                                                            | 36  |

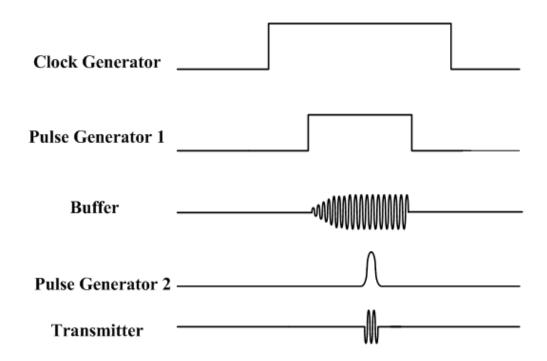

| Figure 3.5  | Effects of power leakage using (a) single-stage and (b) double-stage switching.                                                             | 38  |

| Figure 3.6  | Schematic of the CMOS SPST switch                                                                                                           | 40  |

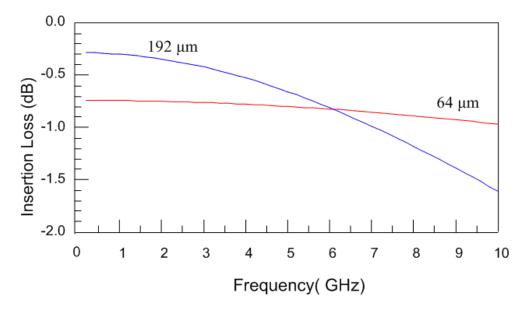

| Figure 3.7  | Insertion loss comparison of two 0.18-µm MOSFETs having different widths                                                                    | 41  |

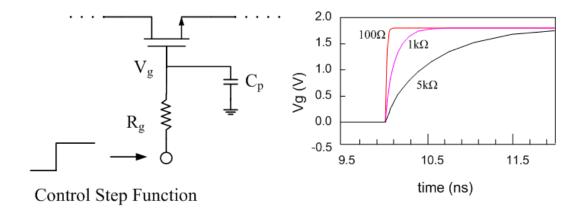

| Figure 3.8  | (a) MOSFET with a step function applied to the gate and (b) behavior of the gate voltage $V_{\rm g}$ for different gate bias resistances    | 42  |

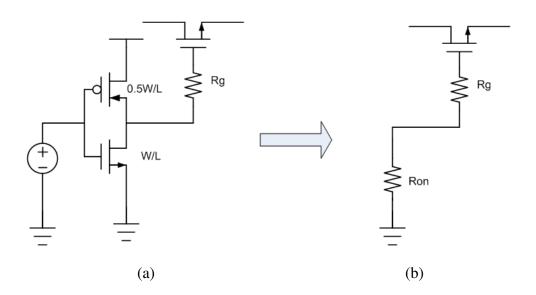

| Figure 3.9  | The inverter load that connect to the gate of the transistors in SPST switch (a) and its equivalent circuits (b).                           | 42  |

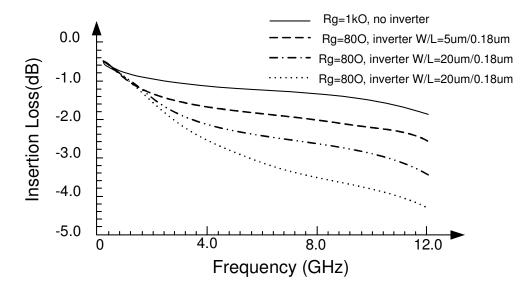

| Figure 3.10 | The effect of gate resistor and inverter transistor size.                                                                                   | 43  |

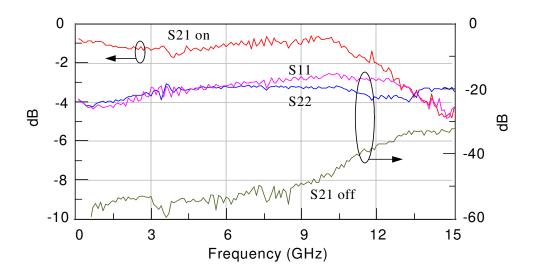

| Figure 3.11 | Measured insertion loss (S21 on), input return loss (S11), output return loss (S22) and isolation (S21 off) of the 0.18-µm CMOS SPST switch | 44  |

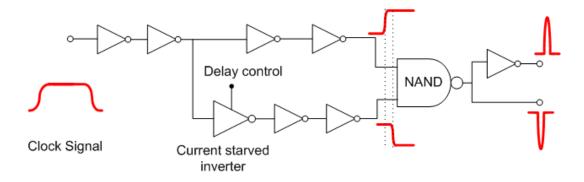

| Figure 3.12 | Impulse generation using digital NAND gate                                                                                                  | 45  |

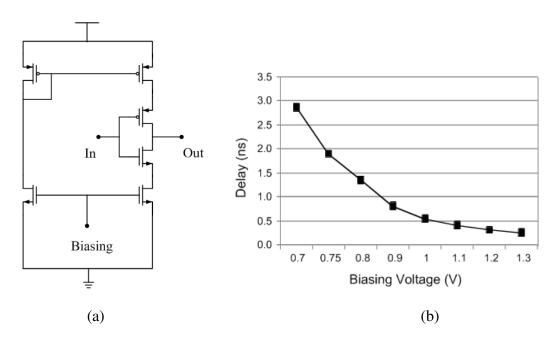

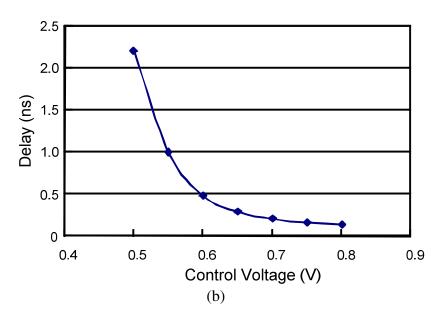

| Figure 3.13 | Current starving inverter structure (a) and its delay tuning range (b)                                                                      | 46  |

|             | Page                                                                                                                                                                                                 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

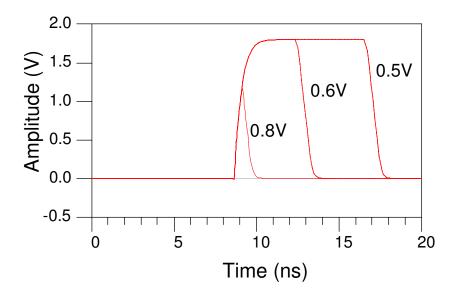

| Figure 3.14 | Different simulated pulse widths controlled by the bias voltage47                                                                                                                                    |

| Figure 3.15 | Rising edge compression of the SPST switch                                                                                                                                                           |

| Figure 3.16 | Microphotograph of the 0.18-µm CMOS chip integrating the pulse generator and the SPST switch                                                                                                         |

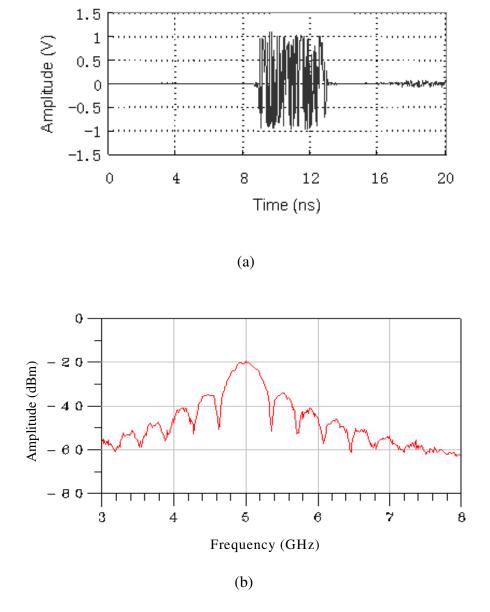

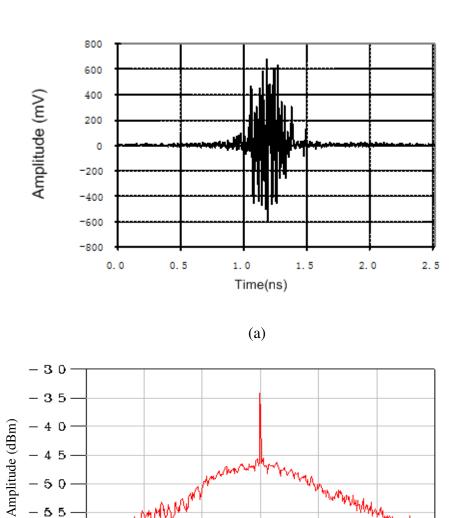

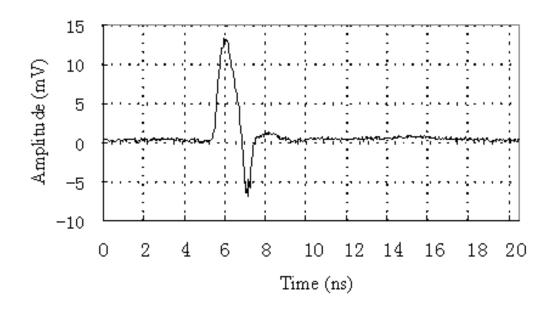

| Figure 3.17 | Measured UWB signal having 500-MHz bandwidth: (a) time domain waveform and (b) spectrum                                                                                                              |

| Figure 3.18 | Measured UWB signal having 4-GHz bandwidth: (a) time domain waveform and (b) spectrum. 52                                                                                                            |

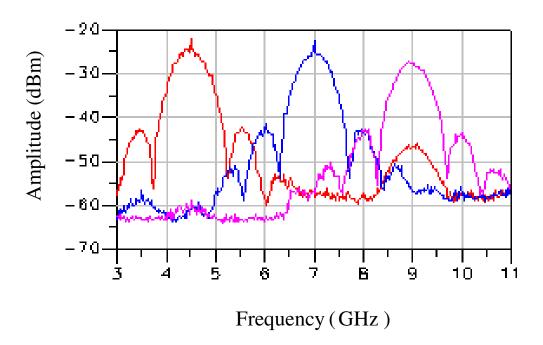

| Figure 3.19 | Measured spectrums of UWB signals covering the 3.1-10.6GHz UWB band                                                                                                                                  |

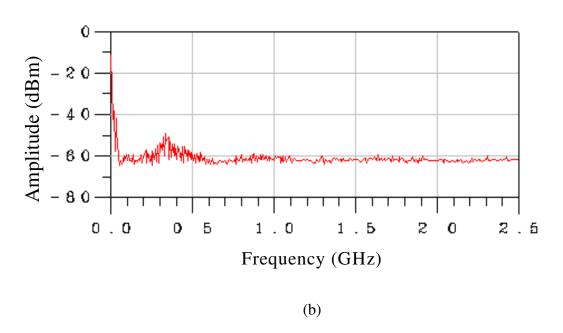

| Figure 3.20 | Measured output signal coupled from the impulse control signal (a) and its spectrum (b)                                                                                                              |

| Figure 4.1  | Sampling circuit model                                                                                                                                                                               |

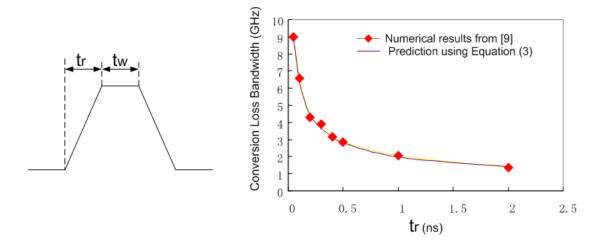

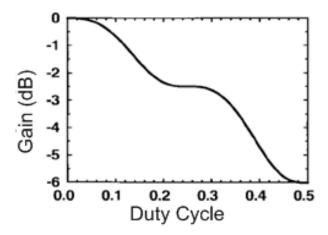

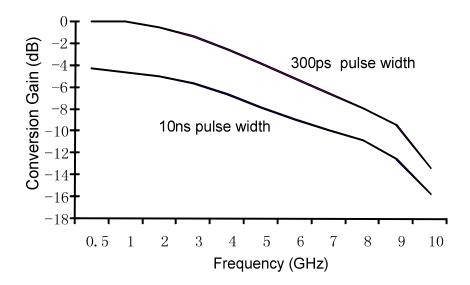

| Figure 4.2  | Pulse model of a sampling strobe (a) and its effect on sampling bandwidth (b). $t_w$ was set to 0 when calculating the conversion loss using (4-3) and results are similar for other values of $t_w$ |

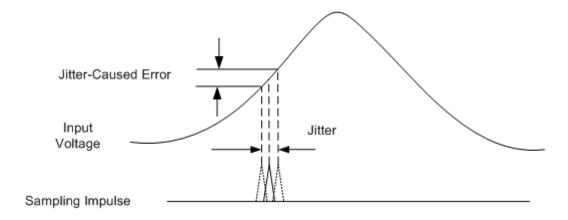

| Figure 4.3  | Derivation of jitter caused noise                                                                                                                                                                    |

| Figure 4.4  | The relationship between conversion gain and duty cycle for an ideal sampling circuit                                                                                                                |

| Figure 4.5  | Conversion gain comparison using different sampling pulse duration62                                                                                                                                 |

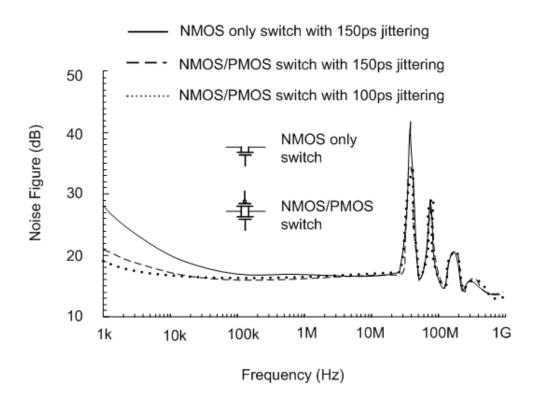

| Figure 4.6  | Noise figure of simple sampler with different switch structure63                                                                                                                                     |

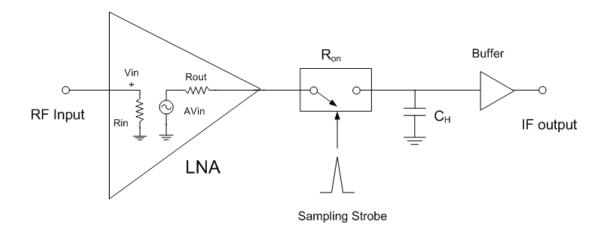

| Figure 4.7  | Diagram of an integrated LNA-sampling mixer. The schematic inside the LNA represents its simplified small-signal model                                                                               |

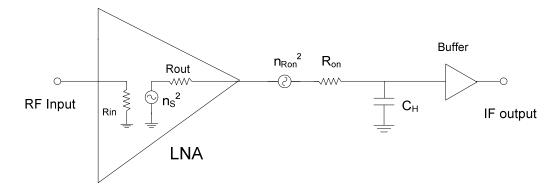

| Figure 4.8  | Equivalent circuit for calculating sampling mixer output noise65                                                                                                                                     |

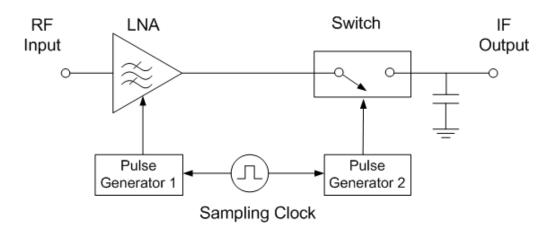

| Figure 4.9  | Block diagram of the integrated sampling mixer subsystem integrating a double-stage switching sampling mixer with a switching LNA67                                                                  |

|             | Page                                                                                                                                                                            |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

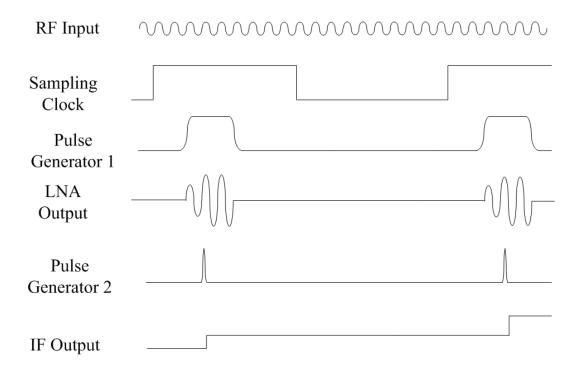

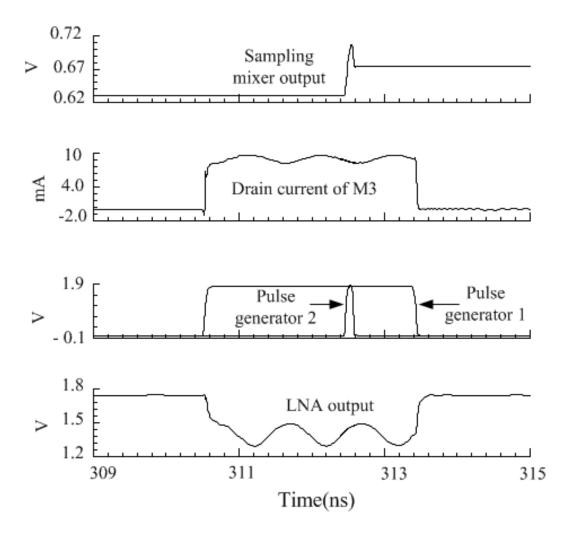

| Figure 4.10 | Waveforms of the building blocks in the proposed integrated sampling mixer subsystem                                                                                            |

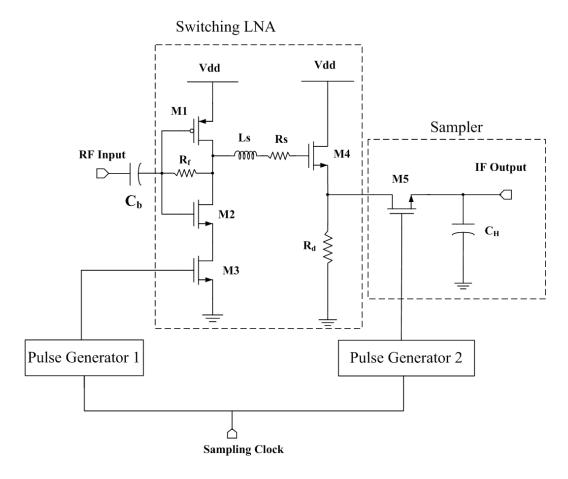

| Figure 4.11 | Schematic of the integrated sampling mixer subsystem. The pulse generators' schematics are shown in Fig. 969                                                                    |

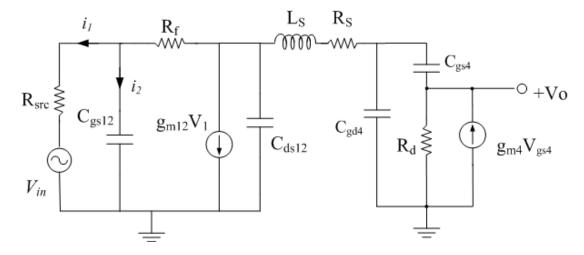

| Figure 4.12 | Small-signal equivalent circuit of the switching LNA with M3 turned on                                                                                                          |

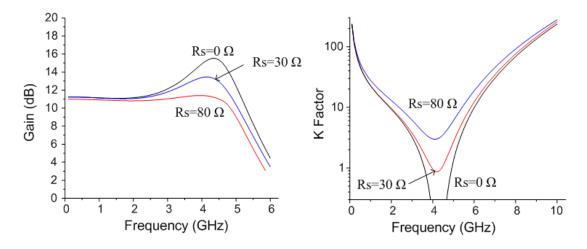

| Figure 4.13 | Effects of serial resistor Rs on gain (a) and stability factor K (b)72                                                                                                          |

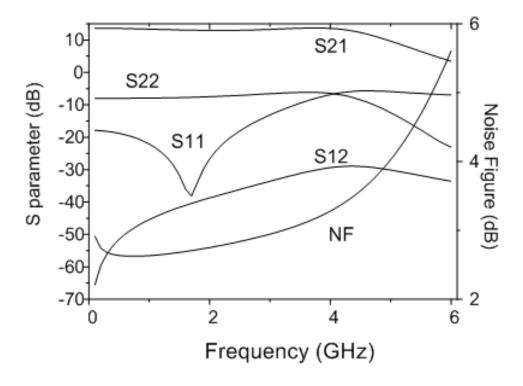

| Figure 4.14 | Simulated S-parameters and noise figure of the switching LNA73                                                                                                                  |

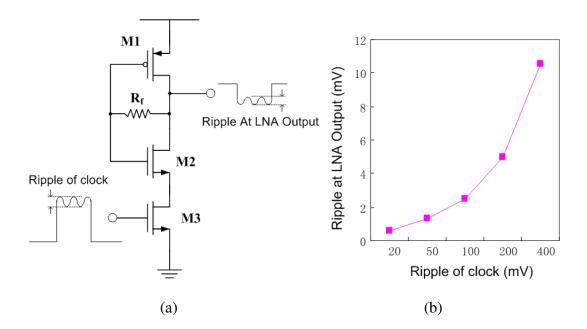

| Figure 4.15 | (a) The effect of sampling clock ripple and (b) simulated coupling results                                                                                                      |

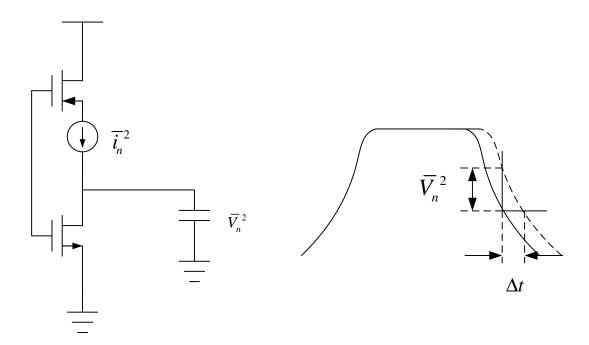

| Figure 4.16 | The transformation from thermal current noise to jitter                                                                                                                         |

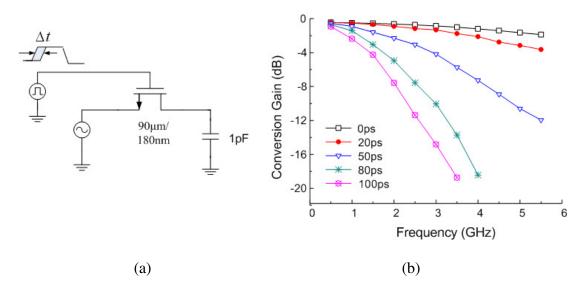

| Figure 4.17 | A basic sampler with a jittered clock (a) and the clock jitter's effects on the sampler's conversion gain (b). The NMOS has a width of 90 $\mu$ m and a length of 0.18 $\mu$ m. |

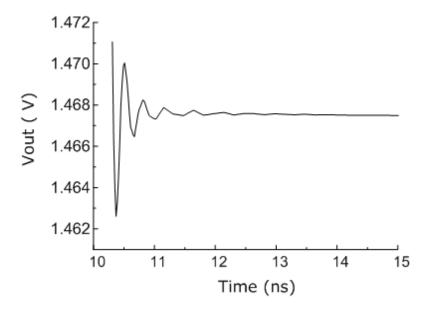

| Figure 4.18 | Transient response of the output of the switching LNA's first stage78                                                                                                           |

| Figure 4.19 | Time domain waveforms of different building blocks in the integrated sampling mixer subsystem                                                                                   |

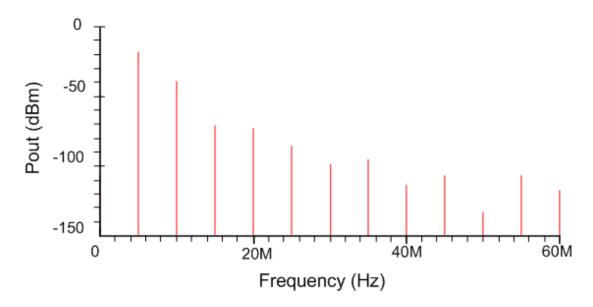

| Figure 4.20 | Output spectrum of the integrated sampling mixer subsystem80                                                                                                                    |

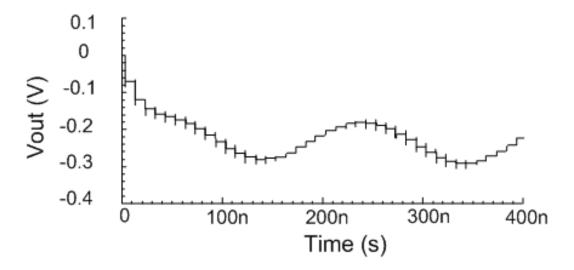

| Figure 4.21 | Output waveform of the integrated sampling mixer subsystem80                                                                                                                    |

| Figure 4.22 | Die microphoto of the integrated sampling mixer subsystem81                                                                                                                     |

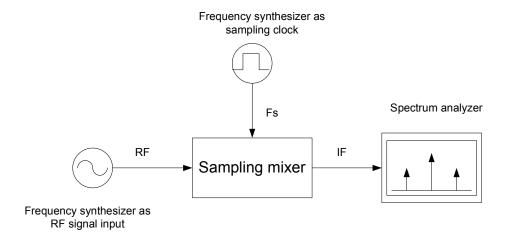

| Figure 4.23 | The setup for measuring conversion gain of the sampling mixer82                                                                                                                 |

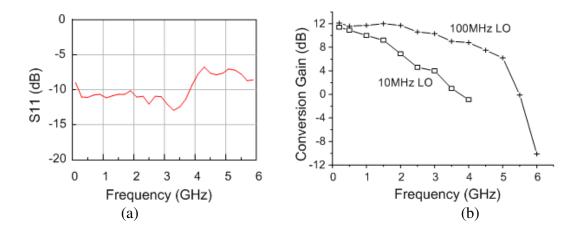

| Figure 4.24 | Measured input return loss (a) and conversion gain (b) of the integrated sampling mixer subsystem83                                                                             |

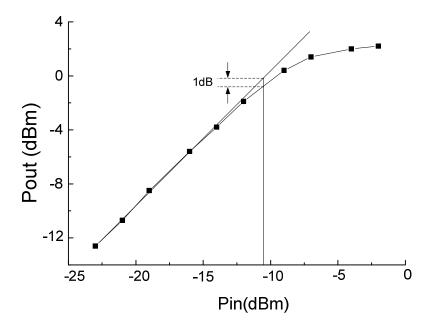

| Figure 4.25 | Measured 1-dB compression point of the integrated sampling mixer subsystem with 100-MHz sampling clock and 500-MHz RF frequency84                                               |

|             | Page                                                                                                                          |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|

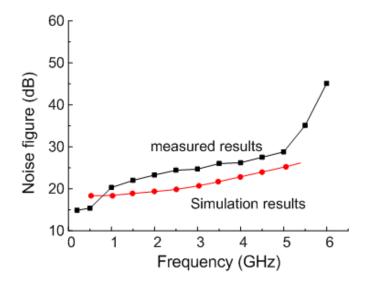

| Figure 4.26 | Measured and simulated noise figure of the integrated sampling mixer subsystem                                                |

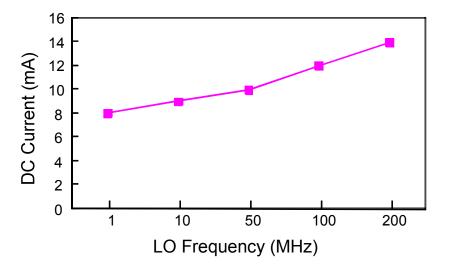

| Figure 4.27 | Current consumption of sampling mixer as LO frequency change85                                                                |

| Figure 5.1  | The diagram of a PPM based transmitter using delay generator87                                                                |

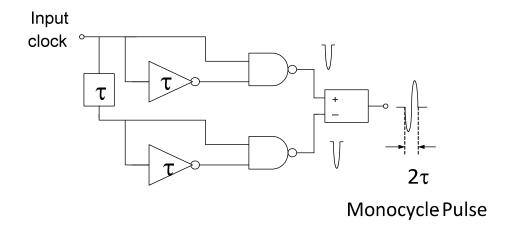

| Figure 5.2  | Generation of mono-pulse signal using delay generator                                                                         |

| Figure 5.3  | Block diagram of digital counter based delay generator in [45]89                                                              |

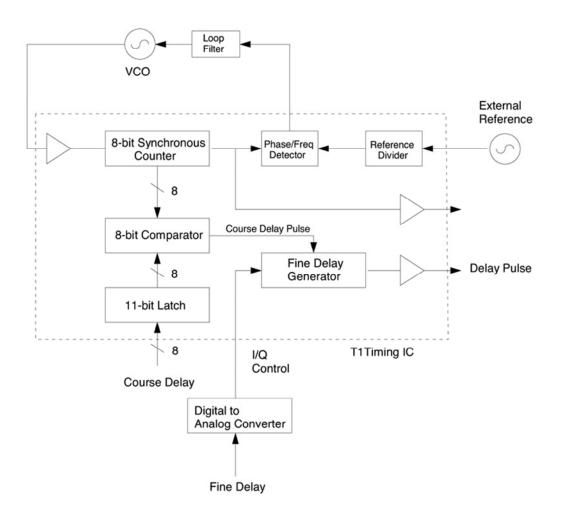

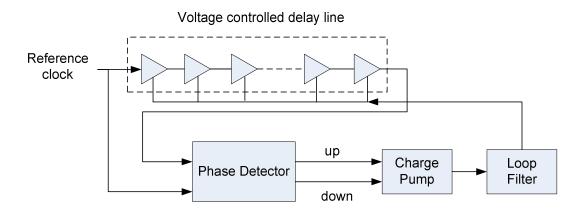

| Figure 5.4  | Block diagram of a delay locked loop90                                                                                        |

| Figure 5.5  | Delay generator that composed of a DLL and a replica delay line91                                                             |

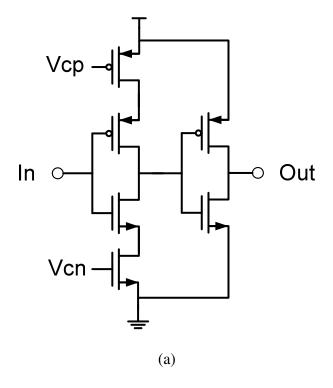

| Figure 5.6  | Delay cell structure in VCDL (a) and its tuning range (b)93                                                                   |

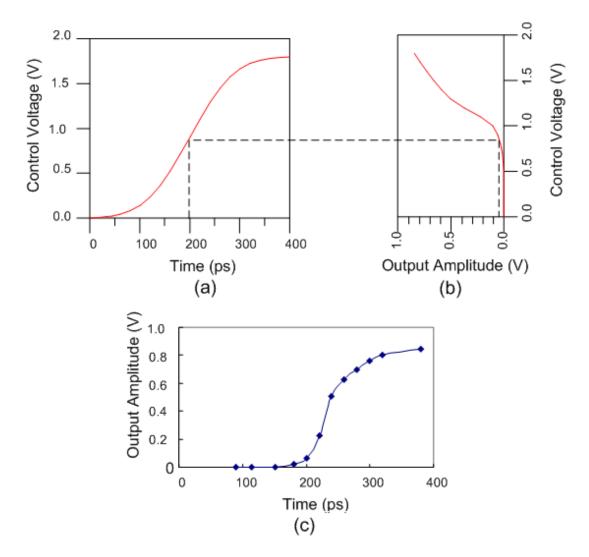

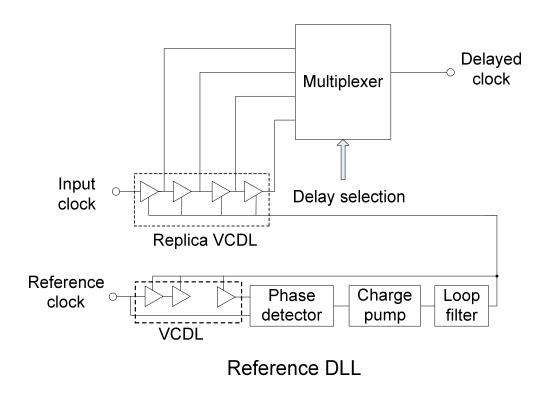

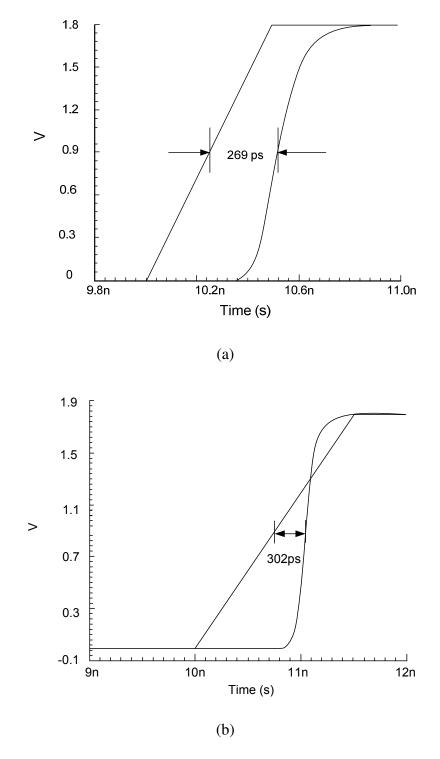

| Figure 5.7  | The delay generated by VCDL cell for (a) a clock signal with 0,5ns rising time and (b)a clock signal with 1.5ns rising time95 |

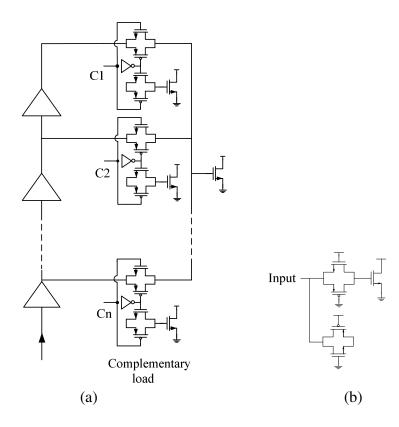

| Figure 5.8  | Schematic of (a) complementary load at multiplexer input and (b) dummy load for DLL delay cell                                |

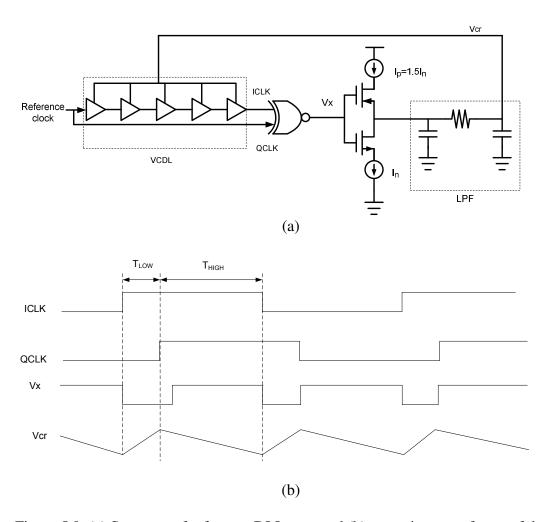

| Figure 5.9  | (a) Structure of reference DLL core and (b) operation waveforms of the reference DLL                                          |

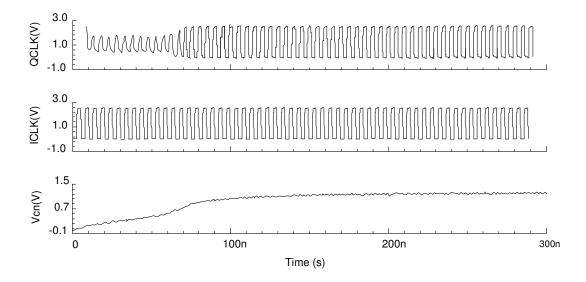

| Figure 5.10 | Simulated waveform in reference DLL core                                                                                      |

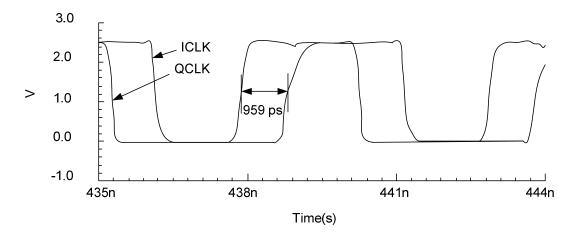

| Figure 5.11 | Waveform comparison between reference clock and delay clock100                                                                |

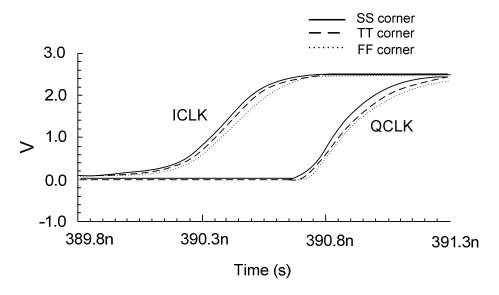

| Figure 5.12 | Delay over different process corner                                                                                           |

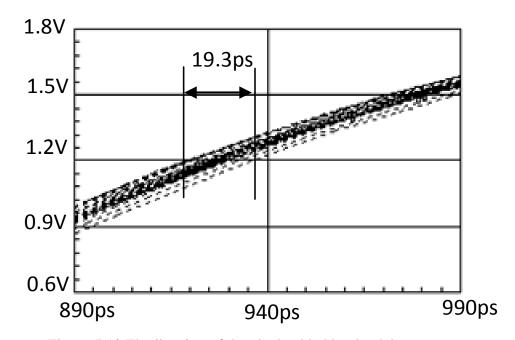

| Figure 5.13 | The jittering of the clock added by the delay generator101                                                                    |

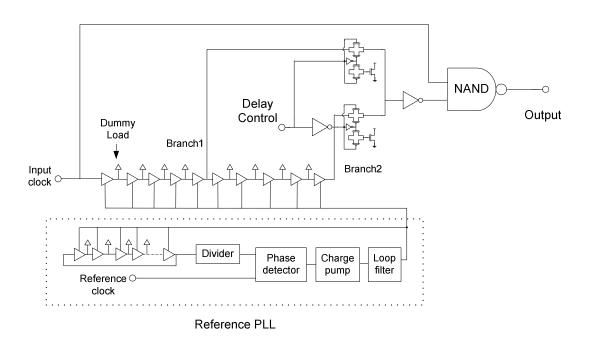

| Figure 5.14 | System diagram of PLL based delay generator                                                                                   |

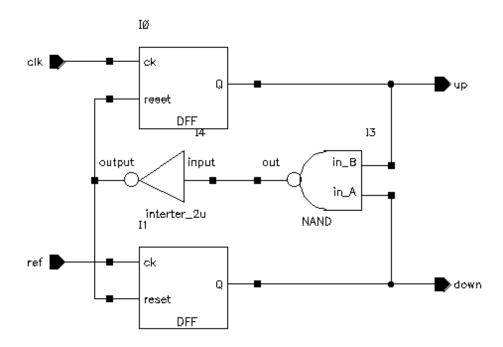

| Figure 5.15 | Structure of phase detector in PLL                                                                                            |

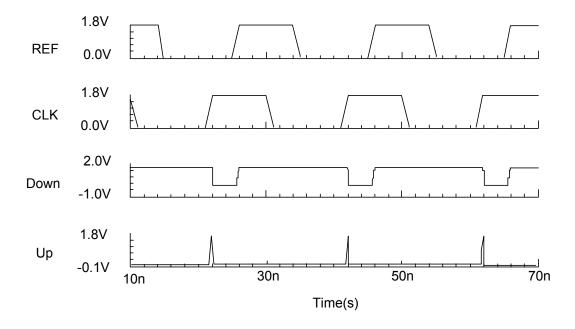

| Figure 5.16 | Operation waveform of phase detector when CLK is ahead of REF105                                                              |

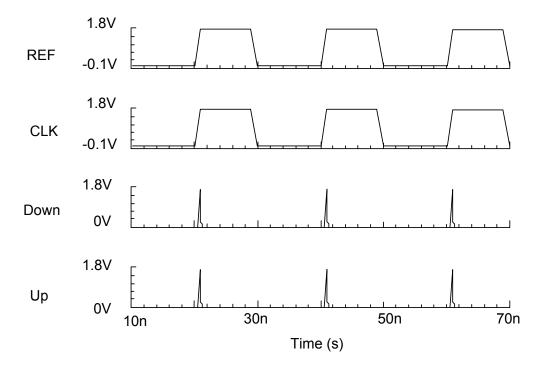

| Figure 5.17 | Operation waveform of phase detector when CLK and REF are in phase                                                            |

|                                                                | Page |

|----------------------------------------------------------------|------|

| Figure 5.18 Schematic of charge pump and low pass loop filter  | 106  |

| Figure 5.19 Time domain waveform of delay cell biasing voltage | 107  |

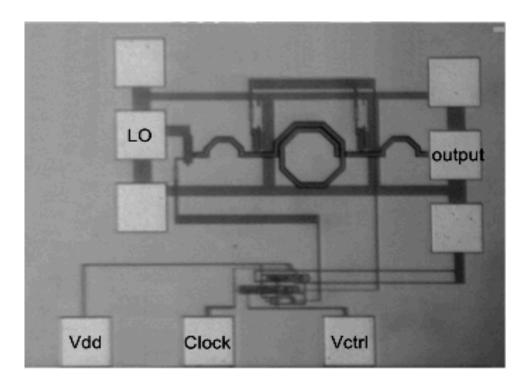

| Figure 5.20 Microphoto of fabricated PLL based delay generator | 108  |

| Figure 5.21 Measured impulse for selecting branch 1 and 2      | 108  |

# LIST OF TABLES

|                                                                                               | Page |

|-----------------------------------------------------------------------------------------------|------|

| Table 3.1 Summary of available semiconductor devices for UWB pulse generator before the 1990s | 31   |

| Table 3.2 Summary of the designed SPST's components                                           | 44   |

| Table 4.1 Performance comparison of published sampling mixers                                 | 86   |

#### CHAPTER I

#### INTRODUCTION

## 1.1 Background and motivation

According to Shannon's Formula, the maximum amount of information that can be transmitted in a wireless communication system is defined as

$$C = W \log_2(1 + SNR) \tag{1-1}$$

where *W* is the bandwidth of the transmitted signal and *SNR* is the signal to noise ratio in the communication system. The mathematical fact tells that higher transmission speed can be achieved by either increasing signal bandwidth or improving signal to noise ratio (SNR). In the past several decades, the evolution of wireless communication technology has been mainly focusing on improving SNR and modulation efficiency. This is mostly due to the fact that the bandwidth of wireless signal (spectrum) is a strictly limited resource. However the studies and applications of wideband signal have not been neglected. Early applications of ultra wideband signal (UWB) include specialized areas such as military communication, positioning/geolocation and ground penetrating. The wide bandwidth of UWB signal can be translated into ultra short pulse on time domain, which brings some advantages such as multipath immunity, high spatial resolution and low probability of interception. Most of these earlier specialized UWB systems are based on hybrid circuit and there was no imminent need for circuit integration.

This dissertation follows the style of *IEEE Transactions on Microwave Theories and Techniques*.

In 2002 FCC released the revised ruling to allocate the spectrum of 3.1GHz – 10.6GHz for UWB application provided that the power spectrum of which is below certain limit. The FCC ruling expedited the birth of the IEEE 802.15.4A standard which defined the standard of high speed short distance indoor communication employing UWB technology. The IEEE 802.15.4A standard turned out to be the main driving force to bring UWB technologies into consumer electronics because of its potential of connecting various home appliances at ultra fast speed. CMOS technology, which has become the dominant carrier for many wireless communication standards, is considered as first choice for implementing UWB technologies.

In the most of the earlier UWB systems, the front-ends were built on microwave hybrid circuits. These systems usually included components like step recovery diodes (SRD), avalanche transistors or schottky diodes, which are very difficult to be migrated onto CMOS process. Whereas the recent progress and achievement of CMOS wireless transceiver in cell phone, wireless LAN and Bluetooth are mostly narrow band based. To implement UWB technologies on CMOS imposes the development of CMOS front-end building blocks which can perform wideband signal processing such as amplifying, frequency conversion, frequency generation as well as timing control. Designing of these circuit modules while satisfying low power dissipation and high integration is a challenging issue and has yet to be fully studied. Interestingly, a divarication can be observed on the recently effort of integrating UWB technology on CMOS process. The approaches such as OFDM-UWB are based on the ideology of expanding the bandwidth of existing narrow band transceiver structure, which allow reuse of some proven designs

and technologies in narrow band systems. Some other implementations are more based on the impulse radio methodology. These attempts will introduce some new building blocks such as pulse generator, correlator and sliding integrator, which have not been extensively utilized in the mature narrow band transceiver structures. This dissertation tends to focus on the second approach and will present some novel topologies and designs to achieve low power, high performance by making use of the discrete nature of UWB pulse signal.

## 1.2 Dissertation scopes and organization

This dissertation will investigate and explore the designing of some key monolithic UWB building blocks on CMOS process. Both architecture trade-off and practical design issues will be discussed for each circuit module. Following this introduction chapter II will give an overview on the applications and structures of UWB systems in chronological manner to reveal the evolving of UWB technology and reasoning behind different architectures in UWB system. Chapter III presents a novel UWB carrier based transmitter design. This chapter will thoroughly address the subject of UWB signal generation. A two-stage-switching based configuration is proposed as a solution for low power, high efficiency and low complexity UWB transmitter. Chapter IV covers the designing of a UWB sampling mixer on CMOS process. As the front end in UWB sampling receiver, wideband sampler has not been realized on CMOS process previously. We are able to integrate a LNA with a sampling switch to complete the function of signal amplifying and down-conversion on a single chip while achieving low

power consumption, low noise and high gain at the same time. In Chapter V, the application and design procedure of delay generator in the UWB system will be discussed. The un-calibrated inverter based delay cell has significant process, supply voltage and temperature variations, which cause the timing control in UWB system unpredictable. The proposed delay generator will automatically calibrate the propagation delay in the delay cell through an external clock and a negative feedback loop. The last chapter summarizes the contribution of this dissertation and points out several potential improvements that can be completed in the future.

#### CHAPTER II

#### ULTRA-WIDEBAND TECHNOLOGY OVERVIEW

## 2.1 Brief history of UWB technology

The concept of Ultra-wideband (UWB) can be traced back to the 1960's when Harmuth published a series of papers to discuss non-sinusoid signal based communication systems [1]-[2]. Transmitting non-continuous signals to achieve time multiplexing is one of the motivations behind these discussions. In 1973 Ross filed a patent on so called based-band pulse communication system [3]. It was claimed that because of the wide spread spectrum of the base-band pulses, even the total energy content of the transmitted signal is considerably large it will place little interference on the relatively narrow pass band of other existing radios. The patent diagramed the implementation of transmitter, receiver and antenna which were capable of handling carrier-less pulse signal. The system structure has not changed radically for many UWB

Figure 2.1 System diagram of base-band communication from G.F. Ross [3]

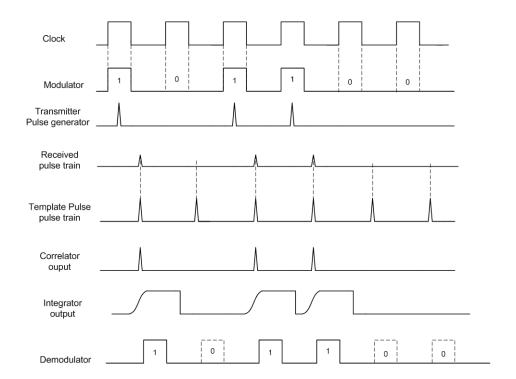

Figure 2.2 Waveforms of different building blocks in based-band pulse radar systems

system emerged later on. Figure 2.1 exhibits the diagram of such pulse system.

Distinct from sinusoid based communication system, the base-band pulse system in Figure 2.1 doesn't contain any frequency mixing.

Figure 2.2 depicts the time domain waveforms at output of different building blocks. In the transmitter, the modulation is directly applied to clock signal. We assume On-Off key modulation is used, e.g. the information bit "1" is represented by the presence of a pulse and no pulse is sent for bit "0". The modulated clock will be applied to pulse generator and produces a baseband pulse transmitted through the antenna. The receiver uses a power detector, in most cases a leading edge detector, to catch the arrival of pulses. If the pulse amplitude at the input of power detector reaches certain threshold, the power detector will assume there is a pulse signal instead of noise and generate a "high" voltage at the output, which signifies a "1". If there is no detected pulse found at designated time, it will be assumed that a "0" is received. Demodulator will sample this

output voltage, recover these modulated "1" "0" information bits and send to display device. Noticeably, all the signal processing is conducted on time domain. Consequently, such pulse systems sometime are referred as "time domain radio" systems. The time domain radio gets rid of the frequency up-conversion and down-conversion procedure therefore significantly reduces the circuit complexity. However the sensitivity of the power detector is far from satisfying for detecting weak signal. The pulse transmitter needs to have very large output power to assure a strong signal reception. The low receiver sensitivity will also limit the working range of the time domain radio when transmitted power through TX is limited. Wheareas the high power transmitter is the major impediment for making UWB system more compact and power efficient.

In 1977 Van Etten did an empirical testing on the impulse radar system following the topology in Figure 2.1 [4]. He studied the radiation and reception of impulse waveforms as well as the performance of some antenna structures when dealing with impulse signals. In his design, a high voltage was applied to a pressurized spark gap. When the voltage applied reaches the threshold the plasma within the gap will break down and ignite. The generated pulse can achieve 70ps of rising time and 100ps of pulse duration.

Based on similar idea, Morey invented the first ground penetrating pulse radar system which adopted synchronized sampling head in the receiver [5]. The radar system has the advantage of fine range resolution and deep penetration by making use of short pulse signal. It became a commercial success and brought many other followers since.

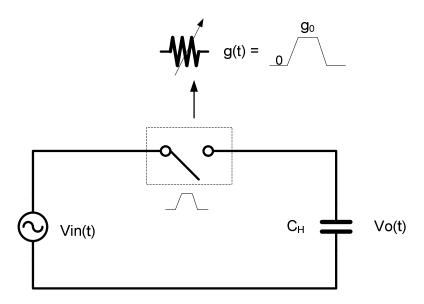

Figure 2.3 The configuration of pulse ground penetrating radar by Morey[5]

The configuration of such radar system is diagrammed in Figure 2.3. Comparing to the diagram in Figure 2.1 the transmitter and receiver of this system are both connected to the same controller. Also the pulse signal is generated periodically. These two features are important because the sampling head which is responsible for recovering the received waveform needs to be synchronized with transmitted signal. By observing the delay from signal transmission to signal reception the distance of reflection path can be accurately calculated. This sampling method is called synchronous sampling. Figure 2.4 illustrates the basic principle of the synchronous sampling method. In Figure 2.4  $V_R$  represents waveform of the input RF signal,  $V_O$  is the LO strobe pulse signal to trigger the sampling, and  $V_D$  is the down-converted output signal through the (ideal) sample-and-hold operation of the receiver. To achieve down-conversion of the RF input  $V_R$ , the frequency of  $V_R$  and the pulse repletion rate (PRF) of  $V_O$  should have a small difference between them. For impulse radar systems,  $V_R$  is actually a pulse signal having a small

Figure 2.4 Illustration of synchronous sampling

PRF( $f_R$ ) and an extremely large duty cycle. For down-converting or stretching of the RF pulse, the PRF of the LO strobe pulse,  $f_o$ , should have a small deviation from  $f_R$ . The designing details of sampling system will be further explored in Chapter IV. It's worth noticing that in Morey's ground penetrating radar (GPR), avalanche transistor was used for generating pulse with rising time of about 1ns. The employment of semiconductor component had greatly reduced the size of this radar system. By the 1970's the sampling head used in the receiver had undergone extensive studies and became commercially available thanks to the development of sampling oscilloscope. Pulse generation module, an indispensable part of sampling circuit, could also be purchased from companies like Hewlett Packard and Tektronix. The limited output power of pulse generator, however, made it difficult to be integrated into transmitter of pulse based systems.

In 1994 the term "Ultra-Wideband" was applied to all the pulse based systems by US department of defense for the first time. After decades of perfecting and especially rapid development of semiconductor technology, highly integrated pulse radar system finally became possible. In 1994, T.E. McEwan filed a patent on micro-power impulse

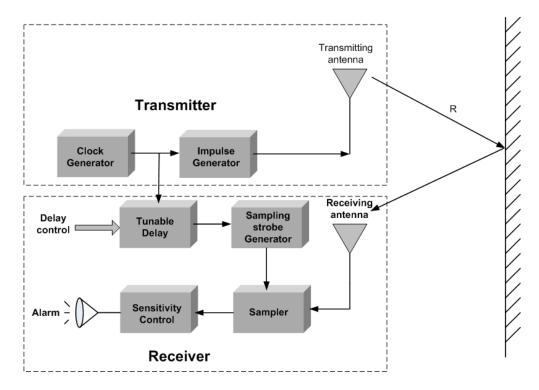

Figure 2.5 Simplified block diagram of MIR

Figure 2.6 Waveform of main components in MIR

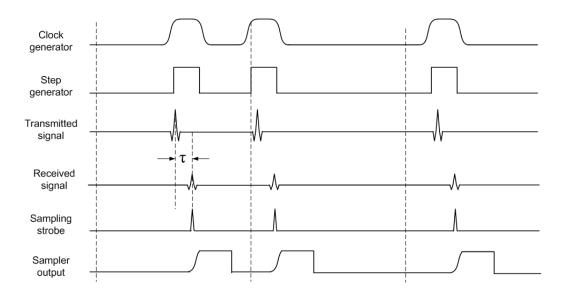

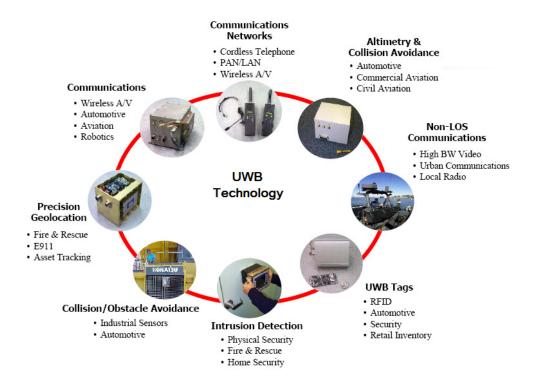

radar (MIR), an extremely low power, compact and low cost UWB radar system [6]. This ultra-wideband radar system was initially proposed as a motion sensor. The transmitter emits short duration impulses while receiver is only designed to accept signal echo from a fixed range R. Any motion on the reflector at range radius of R will cause a change on return signal level sensed by the receiver. In this case an alarm will be sent out. The main components of MIR are shown in Figure 2.5. The transmitter contains a clock generator and a step generator. The clock generator produces clocks that have random pulse repetition interval (PRI) rather than generating periodic clock signal. This helps to smooth the spectrum of the transmitted signal so that interference to other electronic systems can be minimized. The step generator utilizes a step recovery diode (SRD) to create a step signal with around 100ps rising time. Passing the signal through the antenna will differentiates the sharp edge and radiates Gaussian shaped impulse. The receiver is composed of a tunable delay generator, a sampling strobe generator, an ultrawideband sampler and a sensitivity control unit. The tunable delay determines the value of range R by adjusting the time delay between transmitted signal and received signal:  $R = c\tau/2$ , where c is light speed and  $\tau$  is the delay on time domain. The sampling strobes are generated by a delayed transmitted clock and will turn on the receiver when reflected signal is due after traveling distance of 2R. The receiver output can be averaged through integration for repeated sampling by sensitivity control unit. This will essentially improve the signal to noise ratio of the receiver. With clock frequency of 1 MHz, even with 1000 sampling point averaging, the MIR radar can still have 1 ms of responding time for motion detection. In Figure 2.6 the time domain waveforms of the main components are displayed to explain the transmitting and receiving operation of the MIR. Comparing to ultrasonic or passive infrared based motion sensors the pulse radar is not subject to restriction like line-of-sight limitations or degradation caused by fluorescent lighting or in direct sunlight. Although the application of MIR is limited, it signifies that the integration of UWB system has became feasible with advance in semiconductor technologies such as fast-transition SRD and high performance sampling diode. Since the late 1990s the move to commercialize UWB technology began to emerge. Companies such as Time Domain and XtremeSpectrum were founded to bring UWB based system into the field of consumer electronics. Figure 2.7 lists some of the possible applications for commercializing UWB technology. The lack of specified

Figure 2.7 Possible commercial applications for UWB technology

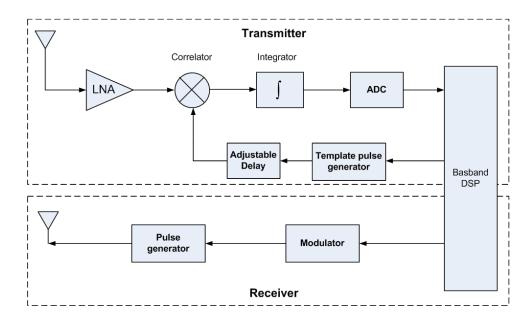

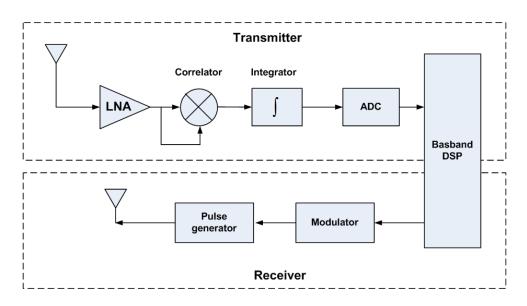

physical layer definition of UWB technology had left a very wide space for design innovation. There have been numerous variations and improvements on both concepts of UWB system and instantiation of subsystem blocks. The adoption of pulse shape, modulation scheme and receiver structure can all be implemented differently for each UWB application. We can categorize these UWB systems into two groups: Coherent receiving system and non-coherent receiving system. The coherent receiving based transceiver is illustrated in Figure 2.8. The transmitter comprises a modulator which applies information code to a clock signal generated by baseband DSP block. The clock can be modulated by a pseudo noise code (PN code) to spread the spectrum. For simplification purpose we can assume the clock is periodical and OOK modulation mentioned in

Figure 2.2 is used. On the receiver side the baseband DSP modulate will use a clock that is synchronized with transmitter to drive a pulse generator to produce a train of template signal pulse having the same waveform substantially equivalent to each pulse of the received pulse signal. The modulated template pulse train will be positioned to align with the received pulse train through the adjustable delay generator. Then successive correlation output will be integrated to recover the impulse radio signal out of noise. The demodulator will retrieve the information codes out of the integrator output. Comparing with the receiver structure in Figure 2.1 the coherent receiver knows "when the received signal will arrive" and will only turn on the reception during that small time window, which tremendously reduce the chance of "false alarm" caused by noise or interference in power detection based signal capturing method. Since the template

Figure 2.8 Simplified construction of UWB system with coherent receiving

Figure 2.9 Signal timing diagram of coherent receiving based UWB system

signals are generated locally in the receiver, it will have large enough amplitude that helps to increase the conversion gain during the correlation. The timing diagram of signals in different modules of transmitter and receiver is given in Figure 2.9.

Consequently the UWB system proposed by Ross in Figure 2.1 belongs to non-coherent receiving category. However, a more popular structure is often considered when a UWB system adopting a non-coherent receiver as shown in Figure 2.10. Instead of correlating received signal with template pulse train, the non-coherent receiver conducts a square operation for the received signal. The self-correlation is generally superior to peak power detection scheme in Figure 2.1.

Although coherent receiver usually outperforms non-coherent receiver by 3-7dB [7], the synchronization of template signal and received signal requires accurate timing precision and complicated feedback loop, which leads to the increase in power

Figure 2.10 Building blocks of non-coherent receiving based UWB system

consumption and circuit complexity. Therefore both coherent and non-coherent received structures are utilized in the recent UWB radar or communication designs based on the trade-off of each instantiation.

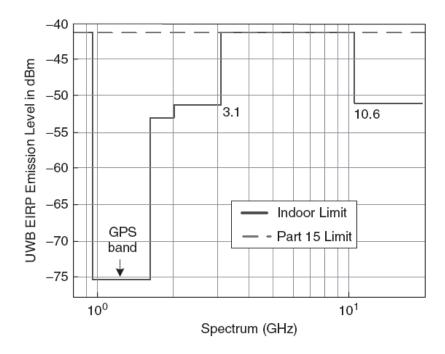

A substantial change occurred in February 2002, when FCC issued a ruling that provided official radiation limitations for UWB transmission and permitted the operation of UWB devices on unlicensed basis [8]. According to the regulation, the term 'UWB' is used to define any signal with fractional bandwidth of more than 20% if the central frequency of the spectrum is lower than 2.5GHz or -10dB signal bandwidth of more than 500MHz if central frequency of the signal spectrum is larger than 2.5GHz. UWB radio transmission can legally operate in the frequency range of 3.1GHz to 10.6GHz, with the power spectral density (PSD) satisfying a specific spectral mask assigned by the FCC. Figure 2.11 demonstrates the spectral mask for UWB indoor communications under Part 15 of FCC's ruling. According to this spectral mask the PSD of the UWB signal measured in the 1MHz bandwidth must not exceed -41.3 dBm. For sensitive band such as GPS band (0.96-1.61GHz), the PSD limit is even much lower. This ruling will allow UWB device to overlay with existing narrow band systems while ensuring sufficient attenuation to limit adjacent channel interference. Right after the spectrum resource became officially available, IEEE established the 802.15.3a study group to definite physical layer concept of wireless personal area network (WPAN) by employing UWB technology. WPAN aims to transmit data at rate ranging from 100Mbps to 500Mbps within the distance of 20m. Not surprisingly the impulse based radio transmission model became the immediate candidate for the new standard. At the same time an

Figure 2.11 UWB spectral mask for indoor communication by FCC

alternative approach that utilizes a combination of multiband approach and orthogonal frequency-division multiplexing (OFDM) techniques was also proposed and began to gain momentum during the competition [9].

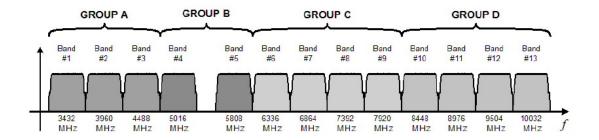

The MB-OFDM proposal chops the 7.5GHz UWB band into 13 sub-bands and does frequency hopping within at least three sub-bands as shown in Figure 2.12. In each sub-band, OFDM-QPSK modulation is used. Figure 2.13 shows a time domain representation of multiband UWB signals in which the signals at different center frequencies are transmitted at different discrete time slot. In the figure the center frequencies of the signals relative to the individual bands are shown in the Y axis. OFDM allows each sub-band to be divided into a set of orthogonal narrowband channels. The methodology behind this approach is extending the OFDM concept from

Figure 2.12 Frequency plan for multi-band OFDM based proposal

Figure 2.13 Multiband signal transmitted at different time slot

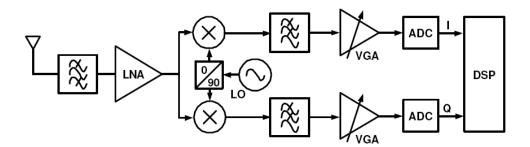

narrow band to ultra-wideband so that the waveform dispersion at the antenna and circuit interface is not critical anymore. Comparing with impulse radio based system, the multiband approach have more flexibility in regard to foreign spectral regulation which may limit their UWB spectral allocation to smaller range than that authorized by the FCC. Moreover, processing over a smaller bandwidth eases the requirement on A/D converter sampling rate. However the large frequency tuning range and stringent settling time imposed by multi-band approach put a tough challenge on the shoulder of frequency synthesizer designers. The transceiver structure of this proposal is quite similar to that in narrow band system as shown in Figure 2.14.

The argument between impulse based single band approach and MB-OFDM based approach eventually lands on employing different design trade-offs and is beyond the scope of this dissertation. However power consumption, circuit complexity and signal to noise ratio performance are always the most important factors when conducting optimization on both the system level and the component level.

Figure 2.14 Direct conversion based MB-OFD UWB transceiver

## 2.2 UWB signal characteristics

For any wireless signal, there is a one-to-one mapping between time domain and frequency domain. This mapping is mathematically expressed by the Flourier transform. Intuitively we know that a time limited signal can be transformed to spectrum with infinite frequency range and vice-versa. Impulse waveform becomes the convenient candidates for UWB signal to spreading spectrum. It is also the waveform adapted in the earlier UWB systems. A rectangular pulse with duration of T and amplitude of 1 can be expressed as

$$p(t) = 1 , -\frac{T}{2} < t < \frac{T}{2}$$

(2-1)

The Fourier transform will give its frequency domain representation:

$$P(f) = \frac{T\sin(\pi T f)}{\pi T f} \tag{2-2}$$

The waveform and spectrum of p(t) is plotted in Figure 2.15. On frequency domain the spectrum's main lobe is between -1/T and 1/T. It also has significant energy lobe outside this main lobe. This could be troublesome since these sidelobes may fall outside

Figure 2.15 Time domain and frequency domain plot of a rectangular pulse

Figure 2.16 Time domain and frequency domain plot of a cosine and Gaussian based pulse

the target UWB band and cause interference to other existing radios. Fortunately, actual impulse obtained by practical circuit doesn't have the ideal abrupt step. The smoother rising/falling edge of the impulse will help to reduce the sidelobe level. For a cosine-shaped pulse c(t) and a Guassian shaped pulse g(t), they can be modeled as:

$$c(t) = \cos(\frac{2\pi f_a t}{2}); \quad -\frac{1}{2f_a} < t < \frac{1}{2f_a}$$

(2-3)

$$g(t) = \exp(\frac{-0.5t^2}{u^2}) \tag{2-4}$$

where  $1/f_a$  denotes the pulse duration of the c(t). u is the constant that determines the slope of guassian pulse. Their Fourier transform are calculated to be:

$$C(f) = \frac{\cos(\pi \frac{f}{f_a})}{1 - (2\frac{f}{f_a})^2},$$

(2-5)

$$G(f) = \exp[-2(\pi f u)^2]$$

(2-6)

The time domain and frequency domain plots for these two pulses are shown in Figure 2.16. The cosine shaped pulse round at the top of the pulse but still have abrupt corners at the zero crossing point. It has smaller sidelobes comparing to rectangular pulse. While Gaussian shaped pulse has smooth transitions everywhere, its sidelobes are completely compressed, which is preferred for the UWB signal transmission. But notice that a large amount of spectrum of these three impulse signals concentrate in DC and low frequency area, which will be difficult to transmit through antenna. Applying an impulse signal directly to an antenna will cause pulse distortion e.g. spectrum variation even the antenna is very wideband. Figure 2.17 shows the measured impulse waveform at input and output of a wideband antenna proposed in [10]. Interestingly we can see that the antenna differentiate the impulse and generate a pulse shape that we called monopulse or mono-cycle pulse. If we take a differentiate for Gaussian pulse in (2-4) and do some normalization the mono-pulse can be expressed as

$$m(t) = 6\sqrt{\frac{e\pi}{3}} \frac{t}{T_0} \exp(-6\pi \frac{t^2}{T_0^2})$$

(2-7)

where  $T_p$  is the pulse duration of the mono-pulse. Its frequency domain expression can be obtained as

$$M(f) = -j\frac{fT_p^2}{3}\sqrt{\frac{e\pi}{2}}\exp(-\frac{\pi}{6}f^2T_p^2)$$

(2-8)

Figure 2.17 Measured time domain waveform of impulse at input and output of a wideband antenna proposed in [10]

The central frequency and the bandwidth of the mono-pulse is determined by  $T_p$ . The -3dB bandwidth is roughly 110% of the central frequency  $f_0 = 1/T_p$ . The time domain waveforms and spectrum of Gaussian mono-pulse with different duration are shown in Figure 2.18 and Figure 2.19 respectively. The ideal Gaussian mono-pulse has one zero crossing. If additional derivatives are taken for the mono-pulse the relative bandwidth decreases and the central frequency of the spectrum increases for a fixed  $T_p$ . Mono-cycle pulse UWB signal is a DC-free signal therefore doesn't suffer from significant pulse distortion through antenna. But it can be easily observed that the central frequency and bandwidth of the mono-pulse is correlated through  $T_p$ . It's not possible to design a mono-pulse UWB signal located at central frequency with variable bandwidth. This disadvantage will limit the ability of UWB system to efficiently utilize available spectrum.

Aiming at achieving more convenient spectrum management and less distortion through antenna, carrier based UWB signal became the late candidate for radar and

Figure 2.18 Time domain waveform of Gaussian mono-pulse with different  $T_p$

Figure 2.19 Spectrum of Gaussian mono-pulse with different  $T_p$

communication applications [11]. The principle of carrier based UWB signal generation is to conduct a frequency up-conversion for the baseband impulse signal to move its spectrum to desired operating central frequency. The up-converted impulse signal can be mathematically expressed as:

$$c(t) = \exp(-\frac{0.5t^2}{u^2})\cos(2\pi f_c)$$

(2-9)

where  $f_c$  is the frequency of the carrier. u is a constant that is related to pulse duration. The carrier is AM modulated by the baseband impulse. The bandwidth of the obtained UWB signal will be determined by the duration of baseband impulse. The UWB signal appeared in frequency domain as:

$$C(f) = \exp[-2\pi^2 (f \pm f_c)^2 u^2]$$

(2-10)

For a carrier based UWB signal with carrier frequency of 4.1GHz and impulse duration of 1ns, the signal mapping from time domain to frequency domain is illustrated in Figure 2.20. The signal spectrum has 10dB bandwidth of 1GHz and 20dB bandwidth of 2GHz. It has been mentioned earlier this chapter that for an impulse different rising edge shape

Figure 2.20 Time domain and frequency domain mapping of carrier-based UWB signal

will roughly have the same 10dB bandwidth. Therefore we are able to accurately place the UWB signal at any central frequency and control the bandwidth according to allocated spectrum. The expenses for choosing carrier based UWB signal are increased circuit complexity and possible higher power consumption due to the inclusion of an RF oscillator and an up-conversion mixer. Chapter III will discuss the solution for generating carrier based UWB signal effectively in detail.

# 2.3 UWB signal modulation

Similar to narrow band system, modulation schemes are also required for UWB communication and sensor systems in order to carry information. Noticeably some narrow band modulation approaches are not available to UWB pulse. For example, frequency modulation (FM) would be difficult to implement on UWB pulse since it needs to be applied to continuous wave (CW) signal. UWB pulse can be sent in discrete (as in GPR system) or near-continuous (as in MB-OFDM) manner. The information code can be applied to pulse position, shape or polarity. The most widely adopted modulation methods include On-Off-Key modulation (OOK), Pulse Position Modulation (PPM), Pulse Amplitude Modulation (PAM), Bi-phase modulation (BPM).

# 2.3.1 On-Off-Key modulation (OOK)

OOK is the simplest modulation method where presence or absence of a pulse is used to identify "1" or "0". The OOK scheme can be demodulated by power detection based UWB system as mentioned earlier. The modulation can be conducted for clock signal easily prior to the pulse generator. The major disadvantage of OOK is that it is

subject to noise interference and multipath because it will be difficult to determine if the detected signal is echo/noise or the received pulse.

## 2.3.2 Pulse Position Modulation (PPM)

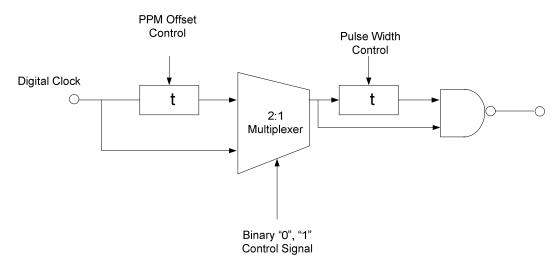

In PPM, information is distinguished by whether the pulse appeared in a delayed position from regular time or not. PPM is not necessarily a binary system, by specifying different delay values the pulse position can represent multiple possible symbols, e.g PPM can be a M-ary system in which two or more bits can be grouped together to form a symbol. Another advantage of PPM is that the pulse position will appeared to be random on the time domain, which translates into a smoothly spread spectrum on frequency domain. Like OOK modulation, the implementation of PPM can also be applied to digital clock signal provided that fine accurate timing control is required.

### 2.3.3 Pulse Amplitude Modulation (PAM)

Another way to realize M-ary modulation is using different pulse amplitude to define different symbol. This requires the gain of the pulse generator output driver be programmable. PAM can achieve high data rate since the pulses can be very close to each other. In general it is not the preferred way for UWB communication considering that smaller pulse will be susceptible to noise and interference while larger pulse will require more power for amplification. OOK actually can be considered as a subset of PAM.

### 2.3.4 Bi-Phase Modulation (BPM)

BPM can be easily understood as to create a binary system based on inversion of certain pulse shape, e.g. the polarity of the pulse. It also benefits from high data rate while not easily affected by noise and interference. The randomly appeared positive and negative pulse will have the benefit of removing spectral peaks. The requirement for accurate timing control is also not as stringent as PPM. Figure 2.21 summarizes and compares different modulation schemes mentioned in this chapter. The information bits to be transmitted are "1 0 0 1". The UWB signal is assumed to be mono-pulse. In a UWB system, the modulation scheme, the pulse shape and the configuration of

Figure 2.21 Comparison of different pulse modulation schemes for UWB communications

transceiver should be optimized altogether to achieve best trade-off between circuit complexity, power consumption and system performance.

# 2.4 Multifunctional UWB system

We have demonstrated that the UWB system architectures for radar and communication are quite similar. In coherent receiver structure based UWB communication system, the time of arrival (TOA) come as a byproduct that can be used for range sensing. Through careful design and arrangement, it is possible that a UWB system can accommodate the task of both exchanging data and detecting range. Figure 2.22 diagrams a possible multifunction UWB system that can work for both communication and radar purposes.

When the system works on communication mode, the transmitter sends out a PPM modulated pulse train. The receiver generates a series of pulses with exactly the same shape and intervals(template signal) to correlate with received pulse train in order to detect if the pulse is delayed from its position(stand for "1") or on time (stand for "0"). Because the received signal time delay is unknown, a synchronization process is needed to align the template pulse train and received signal, which will be the function of the synchronization loop.

When the system works on radar mode, the transmitter sends out periodic pulses with lower pulse repetition frequency (PRF). Same transmitted signal will be used as the template signal at receiver side. Basically the receiver performs the same as in communication mode except that the delay value of the delay generator inside the red block will be processed as the roundtrip traveling time of reflected signal. Notes that in

Figure 2.22 Multifunctional UWB system architecture

radar model, both transmitter and receiver use the same clock, which could provide us the transmitting – receiving time delay. The proposed system can use either carrier based UWB signal or carrier free UWB signal. The transmitter needs to have variable gain to serve for different power output level of communication and radar applications. A calibration algorithm is also required when calculating range since the clock prorogation delay in the circuit needs to be taken into account.

## CHAPTER III

## CARRIER BASED UWB TRANSMITTER DESIGN

# 3.1 CMOS UWB pulse generator

Although UWB technology is evolving rapidly, the fundamental structure of UWB transmitter has not experienced any radical change. Most design efforts of UWB transmitter are focusing on improving the design of pulse generator. The earlier design conception for pulse generator is to trigger a sharp step by applying a clock signal with large amplitude to an abruptly switching device, such as a step recovery diode (SRD). Then an impulse or mono-pulse can be synthesized from the sharp step signal. Table 3.1summarizes the available devices that can be used for UWB pulse generator before the 1990s. UWB technology mostly targeted for radar and sensing applications during this period. To maximize pulse amplitude, improve power efficiency while obtaining fast rising edge is the main design optimization goal for pulse generator at this stage.

Table 3.1 Summary of available semiconductor devices for UWB pulse generator before the 1990s

| Type                 | Step/Pulse       | Best available risetime |        | Notes                       |

|----------------------|------------------|-------------------------|--------|-----------------------------|

| <b>71</b>            | 1                | at amplitude            |        |                             |

| Mercury switch       | Step             | 70 ps                   | 300 V  | Max PRF = 200 Hz            |

| Avalanche transistor | Pulse            | 150 ps                  | 12 V   | Device selection necessary. |

| Tunnel diode         | Step             | 25 ps                   | 0.25 V | Fastest transition time.    |

|                      |                  | 100 ps                  | 1.0 V  |                             |

| Step recovery        | Step             | 60 ps                   | 20 V   | Commercially available.     |

|                      |                  | 100ps                   | 50 V   | Specially ordered four-     |

|                      |                  | 200 ps                  | 200 V  | stack.                      |

| Hertzian             | Impulse; also    | 100 ps                  | 1000 V | Limited lifetime, sparkgap. |

|                      | pulse modulated. | 1 ns                    | 1000 V |                             |

| Avalanche diode      | Impulse          | 400 ps                  | 125 V  | MHz rep. rate.              |

As UWB technology extends its reach into low power applications such as short range sensing, geolocation and communications, the integration of UWB pulse generator becomes more and more feasible and attractive. MOSFET has the essential nonlinear I-V characteristics that can be used to shape the fast rising edge required for generating subnanosecond UWB pulse. describes this edge sharpening effect of MOSFET. According to Berkeley Short-channel IGFET Model (BSIM) of a typical MOSFET, the drain current and gate source voltage have a nonlinear correlation:

$$I_{D} = \mu C_{ox} \frac{W}{L} [(V_{GS} - V_{TH})V_{DS} - \frac{1}{2}V_{DS}^{2}] \text{, when } V_{GS} < V_{th}$$

$$I_{D} = \mu C_{ox} \frac{W}{L} [(V_{GS} - V_{TH})V_{DS} - \frac{1}{2}V_{DS}^{2}] \text{, when } V_{th} < V_{GS} < V_{DS} - V_{th}$$

$$I_{D} = \frac{1}{2}\mu C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^{2} \text{, when } V_{GS} > V_{DS} - V_{th}$$

(3-1)

where W and L are the gate width and length of the transistor, respectively.  $\mu$  is the mobility of the charge carriers.  $C_{ox}$  is the gate oxide capacitance per unit area.  $V_{TH}$  is the threshold voltage.  $I_d$ ,  $V_{GS}$ ,  $V_{DS}$  are the drain current, gate-source voltage and drain-source voltage respectively. This  $I_D$  -  $V_{GS}$  relation is plotted in Figure 3.1. If we apply an input step signal to  $V_{gs}$  we can expect to obtain the waveform of output drain current  $I_{out}$  through a point-to-point  $I_D$  -  $V_{GS}$  mapping as shown in Figure 3.1. It can be observed that the attained output current  $I_{out}$  is also a step function only with much shorter rising time comparing with input voltage step  $V_{in}$ . By cascading several such sharpening stages, a slow-rising step signal can be transformed into step signal with sub-nanosecond rising time. Stemming from this characteristic, most of the recent CMOS UWB pulse generators utilize either analog or digital approaches to synthesize impulse or mono-

Figure 3.1 Step sharpening effect of MOSFET

pulse [12]-[16]. Usually adding a filter and an inverter-based driver amplifier following the pulse generator will be able to deliver the required output power to the antenna.

# 3.2 Carrier based UWB transmitter architecture

Carrier-based UWB transmitter will have to include more building blocks comparing with simple impulse/mono-pulse transmitter. Essentially, a carrier-based UWB signal is generated by multiplying an impulse signal with a single-tone carrier signal. Therefore, the bandwidth and central frequency of the generated signal can be manipulated by adjusting the pulse width of the impulse signal and the frequency of the

Figure 3.2 Block diagram of a typical carrier-based UWB transmitter

single tone. Figure 3.2 shows a typical carrier-based UWB transmitter. The clock generator is usually composed of timing-control digital circuits and sends out a clock signal that can contain modulation information. The impulse generator produces an impulse signal whose pulse width is inversely proportional to the bandwidth of the required signal. The mixer performs a multiplication between the impulse and a singletone signal generated by the oscillator. The up-converted signal is then sent to the wideband power amplifier (PA) to achieve required amplitude. In this approach, the oscillator is required to generate multiple tones if the transmitter needs to operate over multiple frequency bands. This carrier-based UWB transmitter suffers from two major disadvantages. First, the PA in the last stage of the UWB transmitter is a challenging design. This PA needs to supply enough gain, have reasonable power efficiency and provide good output matching over a wide frequency range. Second, in UWB radar applications, low pulse repetition frequency (PRF) is often utilized. Since the transmitted signal duration is usually very short, the resultant peak-to-average power ratio is

extremely high. This means no signal needs to be transmitted during most of the time. However, because the PA and other circuits of the transmitter are 'on' all the time, a large amount of power is wasted, rendering the approach power-inefficient. Based on this transmitter configuration various carrier-based UWB transmitters using CMOS and BiCMOS SiGe processes have been developed [17]-[19].

In order to overcome these issues, we proposed a modified UWB transmitter architecture similar to the concept of gated oscillator. Figure 3.3 shows the block diagram of the newly proposed carrier-based UWB transmitter, consisting of a voltagecontrol oscillator (VCO), a buffer, a SPST switch and two pulse generators. In this approach, power switching is used to perform the signal multiplication, instead of mixing as used in the typical UWB transmitter structure shown in Figure 3.2 and those in [17]-[19]. The transmitter's principle is based upon the concept of generating a carrier-based UWB signal by gating a single-tone signal with a small time window, thereby only producing signal during a small time period. A double-stage switching procedure, using two pulse generators of wide and narrow pulses, and two switches, is adopted in the proposed transmitter to remedy the switching speed limitation of the buffer, inherent in CMOS circuits and to achieve sub-nanosecond gating required in UWB signal generation. The VCO generates carrier signals that define the center frequencies of UWB signal to drive the buffer to achieve sufficient transmitted power and proper output impedance matching. The buffer is gated through its internal switch (first-stage switching) using a wide pulse produced by the pulse generator 1, which should be wide enough to allow the buffer to start and reach stabilization. The second-

Figure 3.3 The proposed carrier-based UWB transmitter topology

Figure 3.4 Waveforms of the building blocks in the proposed UWB transmitter

stage switching, performed by the SPST switch and the pulse generator 2 generating narrower pulses, is then used to reduce the pulse width of the generated signal, making it an UWB signal having spectrum bandwidth of at least 500 MHz as defined by FCC [8]. Pulse generator 1 and 2 are synchronized using a common clock generator as shown in Figure 3.3.

Figure 3.4 illustrates the time domain waveforms at the output of different blocks of the transmitter. It is noted that the SPST's gating signal from pulse generator 2 needs to fall behind the rising edge of the buffer's gating signal from pulse generator 1 to accommodate the slow switching time of the buffer. Using the first-stage switching to turn on/off the buffer not only saves power, particularly useful for battery-operated UWB devices, but is also needed to relax the isolation requirement for the second-stage switching. In low PRF UWB applications, the level of power leakage needs to be very small, imposing a very strict isolation requirement on the gating components, thus necessitating the use of two switching stages.

Figure 3.5 shows the effects of power leakage and demonstrates the need for two switching stages. In Figure 3.5 (a), only the second-stage switching is used. *Ts* stands for the pulse width of the UWB signal, while *Ti* is the interval between two consecutive pulses. During the time the second-stage switching is off, the LO signal (i.e., the VCO's signal) still manages to arrive at the transmit antenna due to limited SPST switch isolation. Although this LO leakage has much smaller amplitude than the transmitted UWB signal, it can still accumulate sufficiently large power over the duration *Ti* to overdrive the UWB signal on the transmitted spectrum. When such situation happens, a high-

Figure 3.5 Effects of power leakage using (a) single-stage and (b) double-stage switching

power single tone would be observed at the carrier frequency above the UWB signal spectrum. To avoid this problem, the signal-to-leakage ratio should be much higher than Ti/Ts. For instance, for a 1-ns UWB signal pulse to be transmitted at 10-KHz PRF with negligible power leakage, the ratio Ti/Ts is roughly about 105 and an isolation of much more than 50 dB is thus required to satisfy the leakage requirement if only one switching stage was used (i.e, the second stage). This level of isolation is very difficult to achieve in CMOS switches. In Figure 3.5 (b), both switching stages are applied. The LO leakage only appears during the time the buffer is on; i.e., within the time widow  $T_L$ , which is usually no longer than 10 ns. The isolation of the second-stage switching is only required to be larger than  $T_L/Ts$ . In this case, 30-dB isolation is sufficient to ensure small LO

leakage regardless of the PRF used. For CMOS switching, 30-dB isolation is a modest requirement and can be achieved by careful design.

# 3.3 The implementation of UWB transmitter

In order to verify the concept and feasibility of the proposed UWB transmitter topology a new carrier-based UWB transmitter covering the entire UWB band of 3.1-10.6 GHz is realized using a pulse generator-SPST switch CMOS chip, designed and fabricated using the TSMC 0.18-um CMOS process [20], and an external frequency synthesizer. The transmitter is based on the concept proposed in Figure 3.3 but implemented without the pulse generator 1 and the VCO and buffer replaced with an external frequency synthesizer.

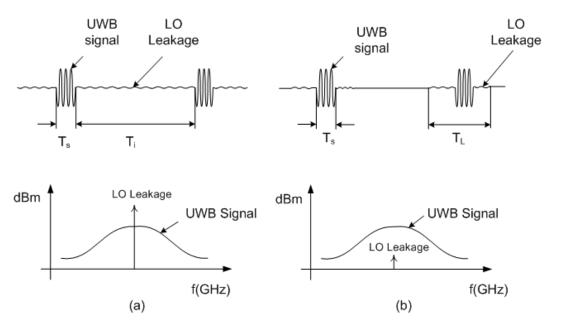

# 3.3.1 CMOS SPST switch design

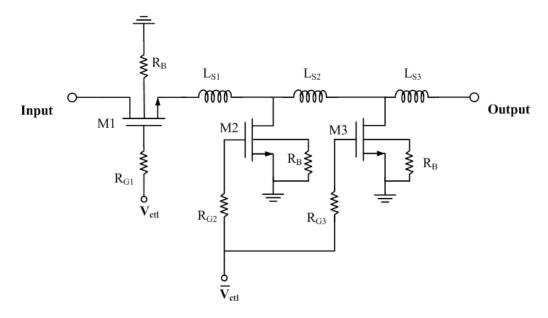

Figure 3.6 shows the schematic of the CMOS SPST switch. One serial and two shunt MOSFETs are used to provide compromise between insertion loss and isolation. In order to achieve an ultra-wide bandwidth, on-chip inductors between adjacent transistors are combined with the transistors' parasitic capacitances to form a synthetic transmission line between the input and output of the SPST switch. The bulk (or substrate) terminals of the transistors are floated to improve the power handling ability and insertion loss [21]. The SPST's on- and off-state are obtained when the control signals  $V_{ctl}/\bar{V}_{ctl}$  are set to Vdd/zero and zero/Vdd, respectively. To ensure wideband performance, the sizes of the serial and shunt transistors need to be carefully determined. The serial transistor

Figure 3.6 Schematic of the CMOS SPST switch

particularly plays an important role in the switch's insertion loss, while the shunt transistors enhance the isolation when the switch is off. Shunt devices, however, inadvertently aggravate the insertion loss due to their parasitics.

For serial-connected transistor the size needs to be carefully chosen, as the gate width is increased, the on-resistance reduces, resulting in low insertion loss in the low-frequency region. The gate-source parasitic capacitance, however, increases, and hence degrading the insertion loss at high frequencies. Figure 3.7 compares the insertion loss of two 0.18-μm MOSFETs, each in series configuration, having two different gate widths (64- μm and 192-μm). As can be seen, the smaller-size transistor has higher loss at lower frequencies but its insertion loss maintains relatively constant over a wide frequency range. For shunt-connected MOSFETs, a larger size provides higher isolation at lower frequencies.

Figure 3.7 Insertion loss comparison of two 0.18-µm MOSFETs having different widths

Typical SPST transistor switch structures are only suitable for slow switching due to the fact that the transistor's gate uses a large biasing resistor to make the gate open at RF so that the switch performance is not affected. This gate biasing resistor, however, leads to a large RC constant, which effectively slows down the control signal applied to the control terminal connecting to the gate via the resistor. Figure 3.8 demonstrates effect of the gate biasing resistor, assuming an ideal step-signal is applied to the control terminal. Due to the gate resistor  $R_g$  and gate-to-ground parasitic capacitance  $C_p$ , the rising edge of the resultant gate voltage  $V_g$  is slowed down. It can be concluded that, a larger gate resistor gives a slower rising edge, leading to slower switching speed. From Figure 3.8, it is apparent that in order to maintain the fidelity of the control sub-nanosecond pulse signals, the gate resistance should be less than a few

Figure 3.8 (a) MOSFET with a step function applied to the gate and (b) behavior of the gate voltage  $V_{\rm g}$  for different gate bias resistances

hundred ohms. Although this may aggravate the insertion loss and return loss of the switch, the switch is expected to have reasonably good performance by optimizing its other components, while maintaining the rising/falling edge of the control pulse signal.

The gate of each transistor in the SPST switch is in series with an inverter that

Figure 3.9 The inverter load that connect to the gate of the transistors in SPST switch (a) and its equivalent circuits (b)

Figure 3.10 The effect of gate resistor and inverter transistor size

has a non-zero output impedance as shown in Figure 3.9. This impedance is equal to the turn-on resistance ( $R_{on}$ ) of PMOS in the inverter. This resistor ( $R_{on}$ ), in series with the gate resistor, will actually improve the insertion loss of the SPST switch when gate resistor value is limited. Figure 3.10 compares the insertion loss of a serial transistor with four different loads at its gate. A large gate resistor of 1k ohms is preferred when designing slow switching SPST switch since it gives less loss. Using 80 ohms gate resistor alone to achieve fast switching increases insertion loss by as large as 2dB. While adding a small size inverter in series with 80 ohms gate resistor will only increase the insertion loss by 0.5dB. Table 3.2 summarizes the designed circuit elements in SPST switch.

The SPST switch has been measured on-wafer using a probe station and an automatic network analyzer. Figure 3.11 shows the measured results. The SPST switch

Table 3.2 Summary of the designed SPST's components

| Circuit Element   | Element Value     |  |  |

|-------------------|-------------------|--|--|

| M1                | 512-μm gate width |  |  |

| M2, M3            | 368-µm gate width |  |  |

| $L_{S1}$          | 0.3 nH            |  |  |

| $L_{S2}$          | 0.6 nH            |  |  |

| $L_{S3}$          | 0.3 nH            |  |  |

| $R_{G1}$          | 100 Ω             |  |  |

| $R_{\mathrm{G2}}$ | 100 Ω             |  |  |

| $R_{\mathrm{G3}}$ | 100 Ω             |  |  |

| $R_{\mathrm{B}}$  | 20 ΚΩ             |  |  |