# INTEGRATION OF MICRO PATTERNING TECHNIQUES INTO VOLATILE FUNCTIONAL MATERIALS AND ADVANCED DEVICES

A Dissertation

by

JUNG MOO HONG

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2009

Major Subject: Electrical Engineering

# INTEGRATION OF MICRO PATTERNING TECHNIQUES INTO VOLATILE FUNCTIONAL MATERIALS AND ADVANCED DEVICES

A Dissertation

by

### JUNG MOO HONG

## Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

| Chair of Committee, | Jun Zou                |

|---------------------|------------------------|

| Committee Members,  | Xing Cheng             |

|                     | Edgar Sanchez-Sinencio |

|                     | Hong Liang             |

| Head of Department, | Costas Georghiades     |

May 2009

Major Subject: Electrical Engineering

#### ABSTRACT

Integration of Micro Patterning Techniques into Volatile Functional Materials and Advanced Devices. (May 2009) Jung Moo Hong, B.S., Inha University; M.S., Inha University

Chair of Advisory Committee: Dr. Jun Zou

Novel micro patterning techniques have been developed for the patterning of volatile functional materials which cannot be conducted by conventional photolithography. First, in order to create micro patterns of volatile materials (such as bio-molecules and organic materials), micro-contact printing and shadow mask methods are investigated. A novel micro-contact printing technique was developed to generate micro patterns of volatile materials with variable size and density. A PDMS (Poly-dimethylsiloxane) stamp with 2-dimensional pyramidal tip arrays has been fabricated by anisotropic silicon etching and PDMS molding. The variable size of patterns was achieved by different external pressures on the PDMS stamp. A novel inking process was developed to enhance the uniformity and repeatability in micro-contact printing. The variable density of patterns could be obtained by alignment using x-y transitional stage and multiple stamping with a z-directional moving part.

Second, for direct patterning of small molecule organic materials (e.g. pentacene), a novel shadow mask method has been developed with a simple and accurate alignment system. To make accurate dimensions of patterning windows, a silicon wafer was used for the shadow mask since a conventional semiconductor process gives a great advantage for accurate and repeatable fabrication processes. A sphere ball alignment system was developed for the accurate alignment between the shadow mask and the silicon substrate. In this alignment system, four matching pyramidal cavities were fabricated on each side of the shadow mask and silicon wafer substrate using an anisotropic silicon bulk etching. By placing four steel spheres in between the matching cavities, the self-alignment system could be demonstrated with 2-3um alignment accuracy in x-y directions. For OTFT (Organic thin film transistor) application, an organic semiconducting layer was directly deposited and patterned on the substrate using the developed shadow mask method.

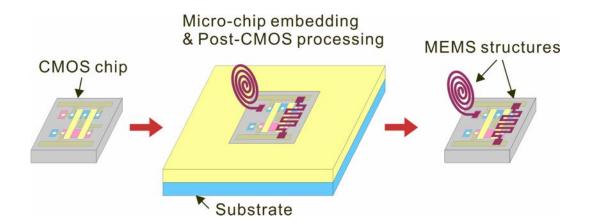

On the other hand, novel embedding techniques were developed for enabling conventional semiconductor processes including photolithography to be applied on the small substrate. The polymer embedding method was developed to provide an extended processing area as well as easy handling of the small substrate. As an application, post CMOS (Complementary metal–oxide–semiconductor) integration of a relatively large microstructure which might be even larger than the substrate was demonstrated on a VCO (Voltage-controlled oscillator) chip. In addition, micro patterning on the optical fiber was demonstrated by using a silicon wafer holder designed to surround and hold the optical fiber. The micro Fresnel lens could be successfully patterned and integrated on the optical fiber end.

To my parents

#### ACKNOWLEDGEMENTS

I would like to thank my committee chair, Dr. Jun Zou, and my committee members, Dr. Xing Cheng, Dr. Edgar Sanchez-Sinencio, and Dr. Hong Liang for their guidance and support throughout the course of this research.

Thanks also go to Mr. Robert Atkins and Mr. Jim Gardner for their technical training, support and collaboration throughout my entire research and fabrication steps. I also want to extend my gratitude to my friends and colleagues such as Murat, Lambi, Karthik, Alejandro, Pillip, Renato, Mehmet, RyoungHan, Jongen, Yongwook, Sungkyu, Myungjoon, Hyunchul, Hyungduk, Hyunsoo for their friendship and support in helping me through this toughest of times.

Finally, thanks from the deepest of my heart to my father, mother, and brother for their love, concern and encouragement, and for always believing in me throughout my life.

# **TABLE OF CONTENTS**

| ABS  | TRA   | .CT                                                                                                                                    | iii |

|------|-------|----------------------------------------------------------------------------------------------------------------------------------------|-----|

| ACK  | (NO   | WLEDGEMENTS                                                                                                                            | vi  |

| TAE  | BLE ( | DF CONTENTS                                                                                                                            | vii |

| LIST | Г OF  | FIGURES                                                                                                                                | ix  |

| LIST | Г OF  | TABLES                                                                                                                                 | xiv |

| 1.   | INT   | RODUCTION                                                                                                                              | 1   |

| 2.   |       | CRO-CONTACT PRINTING WITH VARIABLE DOT SIZE<br>D DENSITY                                                                               | 6   |

|      | 2.1.  | Introduction                                                                                                                           |     |

|      |       | <ul><li>2.1.1. Micro-contact Frinting</li><li>2.1.2. Failure Modes in Micro-contact Printing</li><li>2.1.3. Preliminary Work</li></ul> | 9   |

|      |       | 2.1.4. Motivation                                                                                                                      |     |

|      | 2.2.  | Modeling and Simulation                                                                                                                |     |

|      |       | 2.2.1. Modeling and Simulation of PDMS Tip Deformation                                                                                 |     |

|      |       | 2.2.2. Comparison with Columnar Pillar Structure                                                                                       |     |

|      | 2.3.  | Fabrication                                                                                                                            |     |

|      |       | 2.3.1. Fabrication of Silicon Master                                                                                                   |     |

|      |       | 2.3.2. Fabrication of PDMS Stamp                                                                                                       |     |

|      | 2.4.  | Experimental Results                                                                                                                   |     |

|      |       | 2.4.1. Micro-contact Printing with PDMS Stamp                                                                                          |     |

|      |       | 2.4.2. Contact Printing with Variable Dot Size                                                                                         |     |

|      | 2.5.  | 2.4.3. Contact Printing with Variable Density<br>Conclusions                                                                           |     |

| 3.   | DIF   | RECT PATTERNING OF VOLATILE MATERIALS                                                                                                  |     |

|      | USI   | NG SHADOW MASK METHOD                                                                                                                  |     |

|      | 3.1.  | Introduction                                                                                                                           |     |

|      | -     | 3.1.1. Shadow Mask Lithography (Stencil Lithography)                                                                                   |     |

|     | 3      | 1.2. Motivation                                       |    |

|-----|--------|-------------------------------------------------------|----|

|     | 3.2. D | Design of Shadow Mask System                          | 40 |

|     |        | 2.1. Design for Self-Alignment                        |    |

|     | 3.     | 2.2. Design for Gap Control                           |    |

|     | 3.3. F | abrication of Shadow Mask and Carrier Wafer           |    |

|     | 3.4. E | Experimental Characterization                         | 47 |

|     | 3.5. A | Application to Organic Thin Film Transistor           |    |

|     | 3.6. C | Conclusions                                           |    |

| 4.  |        | GRATION OF MICRO-PATTERNING TECHNIQUE                 |    |

|     | INTO   | THE SMALL SUBSTRATE                                   | 57 |

|     |        | ntroduction                                           |    |

|     |        | ost CMOS Integration with the Small VCO Circuit Chip  |    |

|     |        | 2.1. Polymer Embedding Technique                      |    |

|     |        | 2.2. CMOS VCO Circuit                                 |    |

|     |        | 2.3. Design of Ring Inductors                         |    |

|     |        | 2.4. Post CMOS Integration of Vertical Ring Inductors |    |

|     |        | 2.5. Testing                                          |    |

|     |        | Aicro Patterning onto the Optical Fiber End           |    |

|     |        | 3.1. Design of the Fresnel Zone Plate                 |    |

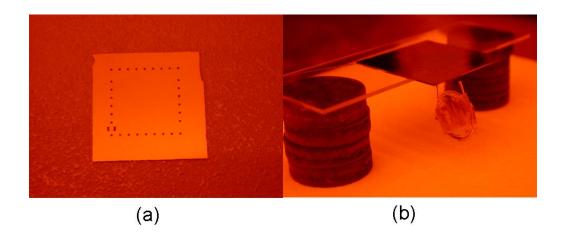

|     |        | .3.2. Optical Fiber Embedding with a Silicon Holder   |    |

|     |        | 3.3. Micro Patterning on the Optical Fiber            |    |

|     | 4.4. C | Conclusions                                           |    |

| 5.  | SUMN   | MARY AND CONCLUSIONS                                  |    |

| REF | ERENC  | CES                                                   |    |

| APP | ENDIX  | A ANISOTROPIC SILICON WET ETCHING                     |    |

| APP | ENDIX  | B LIFT-OFF PROCESS                                    | 93 |

| APP | ENDIX  | C ELECTROPLATING SETUP                                |    |

|     |        |                                                       |    |

| APP | ENDIX  | D ONE-PORT S-PARAMETERS ANALYSIS                      |    |

| VIT | 4      |                                                       | 97 |

## LIST OF FIGURES

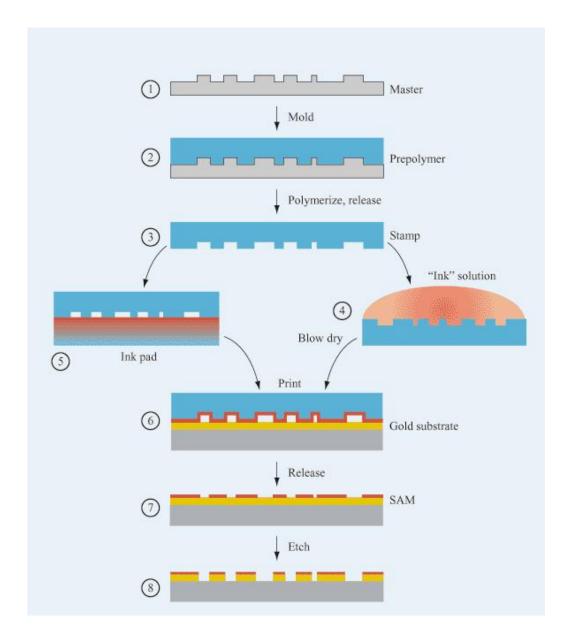

| Figure 1.  | Schematic diagram of micro-contact printing: A prepolymer (2) covering<br>the master (1) is cured by heat or light, and demolded to form an<br>elastomeric stamp (3). The stamp is inked by immersion (4) or contacted<br>with an ink pad (5), and printed onto the substrate (6), forming a SAM.<br>The ink pattern (7) is then transferred into the substrate by a selective<br>etch (8) |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

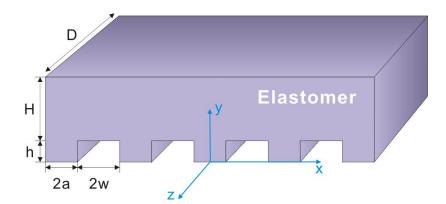

| Figure 2.  | Schematic diagram of an elastomeric stamp                                                                                                                                                                                                                                                                                                                                                  |  |

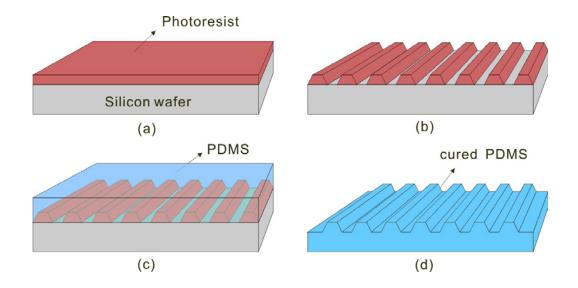

| Figure 3.  | The fabrication steps for PDMS molding. (a) Spin coating of photoresist<br>on the silicon wafer. (b) Photoresist was patterned by photolithography.<br>(c) PDMS solution was poured onto the silicon wafer. (d) PDMS was<br>cured and detached from the silicon wafer. 12                                                                                                                  |  |

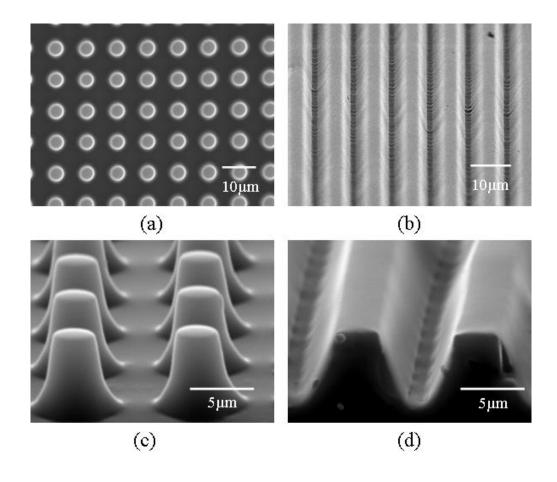

| Figure 4.  | Scanning electron microscope images of PDMS stamps (a), (c) cylindrical pillar array. (b), (d) parallel line structures                                                                                                                                                                                                                                                                    |  |

| Figure 5.  | Confocal microscope images of printed fluorescent dye                                                                                                                                                                                                                                                                                                                                      |  |

| Figure 6.  | An illustration of micro-contact printing with pyramidal PDMS tip<br>arrays: (a) Variable-dot-size printing by applying different pressures on<br>the tips; (b) Variable-density printing in a "step-print" manner by using a<br>transitional stage                                                                                                                                        |  |

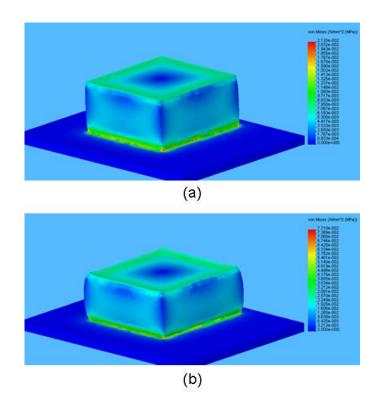

| Figure 7.  | FEA model of a PDMS pyramidal tip showing its deformation and stress distribution under applied pressures of (a) 80 g/cm <sup>2</sup> and (b) 320 g/cm <sup>2</sup> 18                                                                                                                                                                                                                     |  |

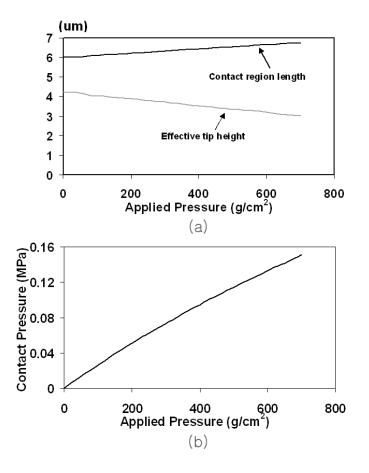

| Figure 8.  | (a) Simulated contact region size and height of the PDMS tip under different applied pressure; (b) Estimated contact pressure of the PDMS tip under different applied pressures                                                                                                                                                                                                            |  |

| Figure 9.  | FEA model of a PDMS square pillar showing its deformation and stress distribution under applied pressures of (a) 80 g/cm <sup>2</sup> and (b) 320 g/cm <sup>2</sup> 22                                                                                                                                                                                                                     |  |

| Figure 10. | (a) Simulated contact region size and height of the PDMS square stamp<br>under different applied pressures; (b) Estimated contact pressure of the<br>PDMS square stamp under different applied pressures                                                                                                                                                                                   |  |

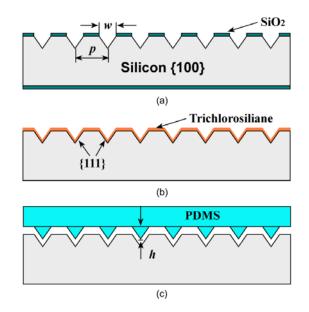

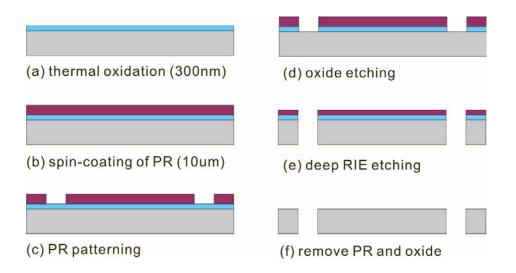

| Figure 11. | An illustration of the design and fabrication process of the pyramidal PDMS tip array (a) oxide layer patterning followed by anisotropic silicon etching, (b) anti-adhesive surfactant coating, (c) curing PDMS and detaching it from the substrate.                          | . 25 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

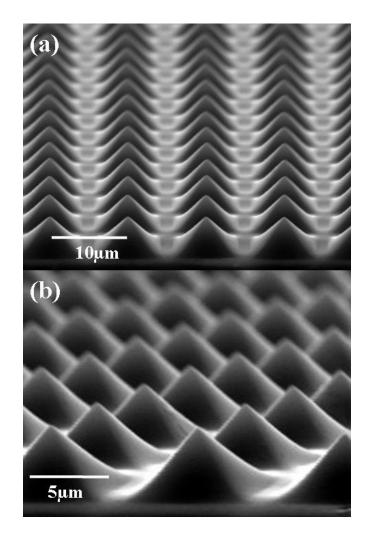

| Figure 12. | Scanning electron microscopic images of molded PDMS pyramid tips:<br>(a) front view; (b) prospective view.                                                                                                                                                                    | . 27 |

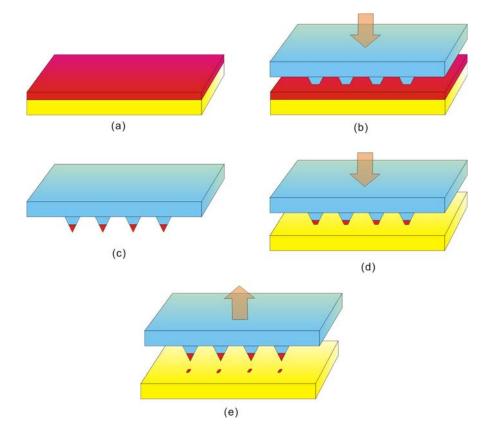

| Figure 13. | Micro-contact printing process using inking pad method; (a) spin-<br>coating of fluorescent dye solution on the slide glass, (b) inking PDMS<br>stamp, (c) inked PDMS tip array, (d) contact printing with external<br>pressure, (e) remove the PDMS stamp from the substrate | . 28 |

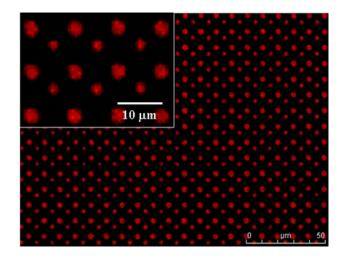

| Figure 14. | Micro-contact printing of fluorescent dyes using the inking pad process;<br>(a) Rhodamine B, (b) Fluorescein sodium salt                                                                                                                                                      | . 29 |

| Figure 15. | Optical microscopic images of deformed PDMS tips (left) and fluorescent images of printed Rhodamine B patterns (right) under different applied pressures: (a) 80g/cm <sup>2</sup> ; (b) 160g/cm <sup>2</sup> ; (c) 320g/cm <sup>2</sup>                                       | . 31 |

| Figure 16. | A schematic diagram of the multiple contact printing scheme with the x-<br>y alignment stage and z-directional moving control.                                                                                                                                                | . 32 |

| Figure 17. | Fluorescent image of double printed Rhodamine B dot patterns under different contact pressures.                                                                                                                                                                               | . 33 |

| Figure 18. | Atomic force microscope images of the printed fluorescent dye patterns;<br>(a) top view of the printed patterns, (b) height profile of the patterns                                                                                                                           | . 34 |

| Figure 19. | Schematic diagram of material deposition and patterning through a shadow mask.                                                                                                                                                                                                | . 36 |

| Figure 20. | A schematic process flow of the shadow mask lithography; (a) placing<br>and aligning the stencil with the substrate (b) deposition through the<br>stencil (c) remove the stencil from the substrate.                                                                          | . 38 |

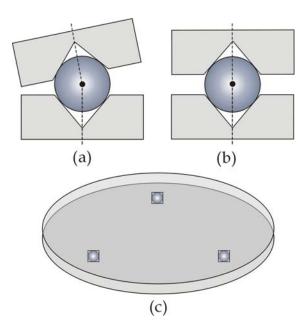

| Figure 21. | Schematic diagram of the new shadow mask system: (a) The fabrication substrate is fixed on the carrier wafer; and (b) the carrier wafer is directly used as the fabrication substrate.                                                                                        | . 40 |

| Figure 22. | Illustration of self-alignment of two silicon substrates using two bulk etched cavities and a steel sphere.                                                                                                                                                                   | . 41 |

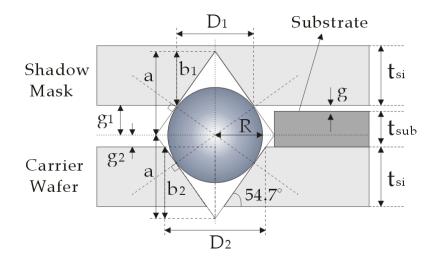

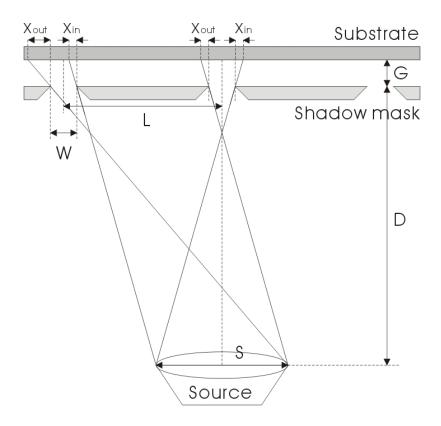

| Figure 23. | Design parameters for mask-substrate gap control.                                                                                                                                                                                                                                                                                                                    | 43 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

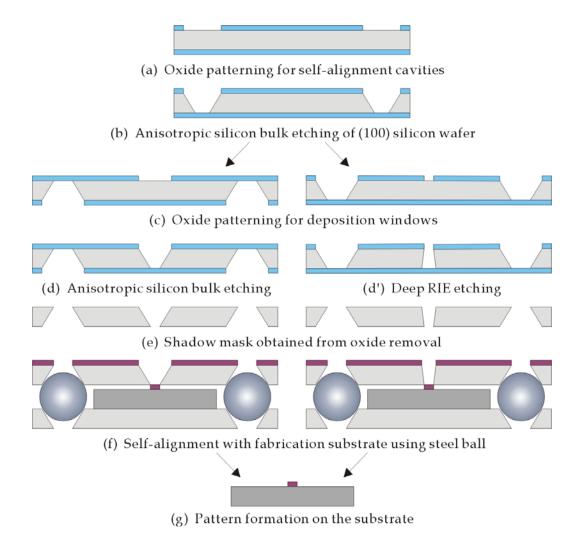

| Figure 24. | Schematic diagram of the fabrication process and application of the shadow mask system.                                                                                                                                                                                                                                                                              | 45 |

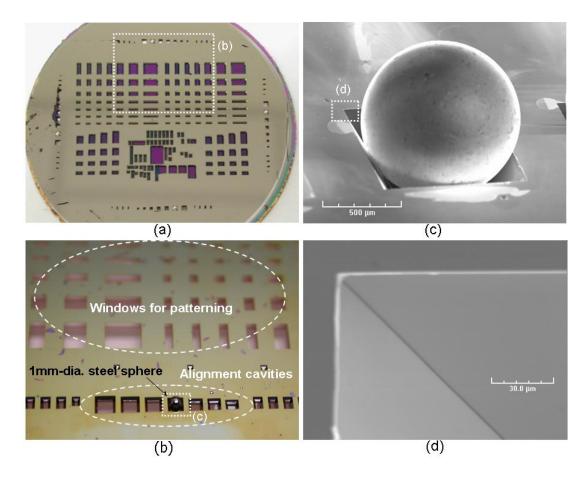

| Figure 25. | (a) The shadow-mask is seen from the front-side aligning with the carrier wafer by four steel spheres between; (b) A close-in view of a fabricated shadow mask seen from the back-side; (c) Scanning electron microscope (SEM) image of a steel sphere placed on the cavity; (d) SEM image of the cavity edge.                                                       | 46 |

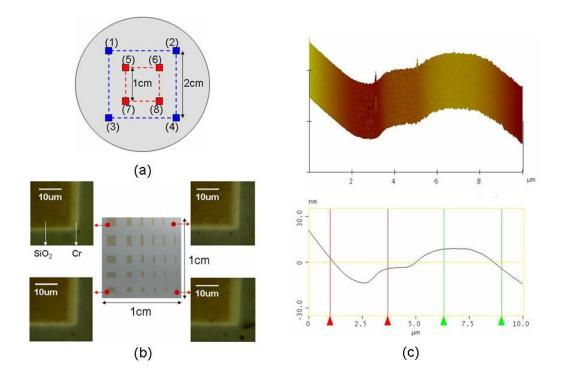

| Figure 26. | (a) 8 different patterns in $1 \times 1$ cm <sup>2</sup> and $2 \times 2$ cm <sup>2</sup> boxes for alignment accuracy estimation; (b) Optical microscopic image of four corner patterns of a $1 \times 1$ cm <sup>2</sup> box on the fabrication substrate. (c) 3-D topographic image and cross-section line plot of the (x) edge profile of a two layered pattern. | 49 |

| Figure 27. | Geometric parameters for the estimation of alignment accuracy in the developed shadow mask system.                                                                                                                                                                                                                                                                   | 51 |

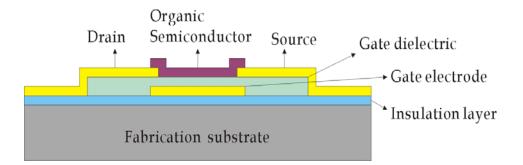

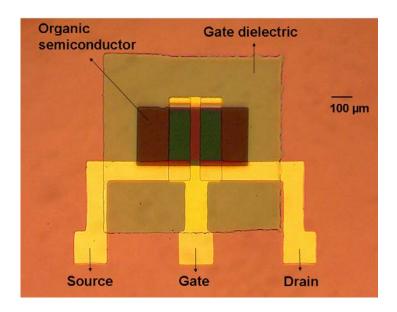

| Figure 28. | Schematic diagram of the OTFT.                                                                                                                                                                                                                                                                                                                                       | 53 |

| Figure 29. | Optical microscopic image of a fabricated OTFT.                                                                                                                                                                                                                                                                                                                      | 54 |

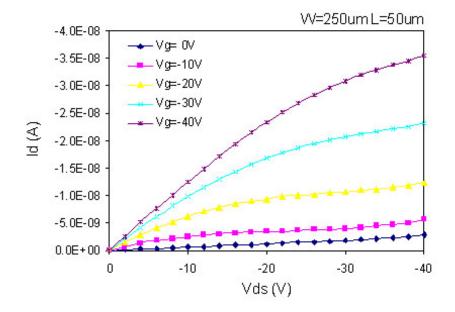

| Figure 30. | The Drain-source current $(I_{DS})$ as a function drain-source bias voltage $(V_{DS})$ and gate-source bias voltages $(V_{GS})$ for the OTFT shown in Figure 29.                                                                                                                                                                                                     | 55 |

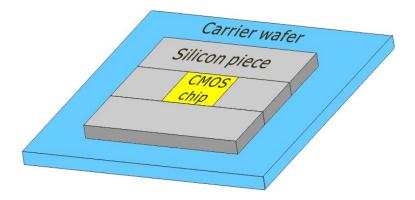

| Figure 31. | An example of the embedding technique for post processing on the small CMOS chip.                                                                                                                                                                                                                                                                                    | 58 |

| Figure 32. | Schematic diagram of post-CMOS integration technique using polymer embedding technique.                                                                                                                                                                                                                                                                              | 59 |

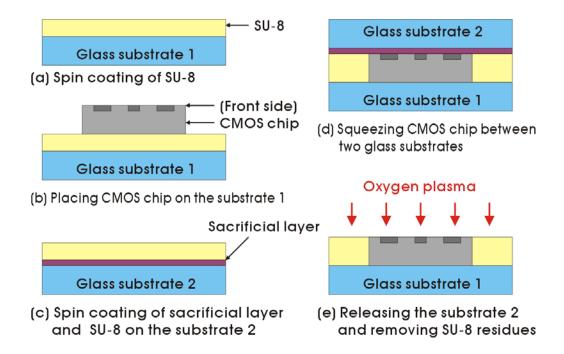

| Figure 33. | Schematic process flow of the new micro-chip embedding technique using SU-8 as the filling material                                                                                                                                                                                                                                                                  | 61 |

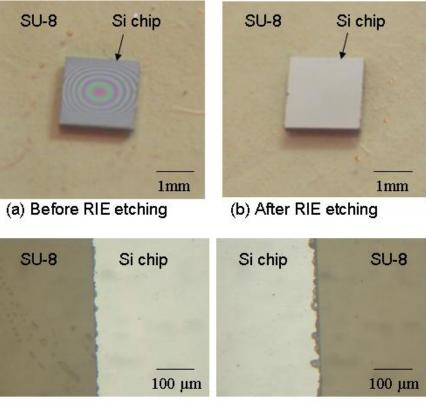

| Figure 34. | Optical images of a dummy silicon chip $(2 \times 2 \text{mm}^2)$ embedded in SU-8                                                                                                                                                                                                                                                                                   | 63 |

| Figure 35. | Surface profiles at the interface between the embedded silicon chip and SU-8 after plasma cleaning.                                                                                                                                                                                                                                                                  | 63 |

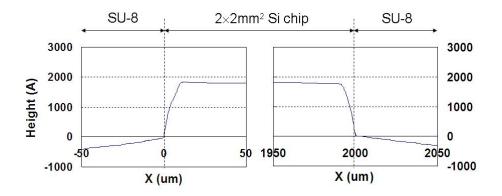

| Figure 36. | Schematic of the 5.8 GHz VCO circuit and output buffer.                                                                                                                                                                                               | . 65 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

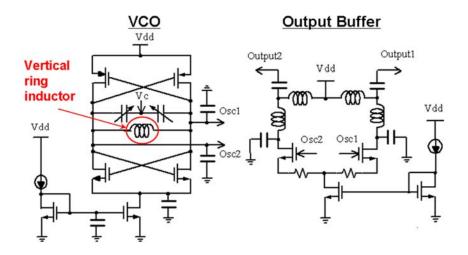

| Figure 37. | Schematic of vertical ring inductor.                                                                                                                                                                                                                  | . 66 |

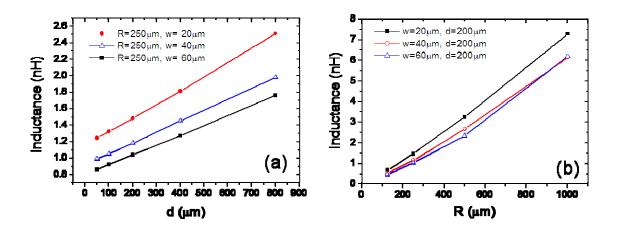

| Figure 38. | Simulated inductances according to the length of straight (a) and circular (b) portions.                                                                                                                                                              | . 67 |

| Figure 39. | Inductor performance according to structural design parameters.                                                                                                                                                                                       | . 68 |

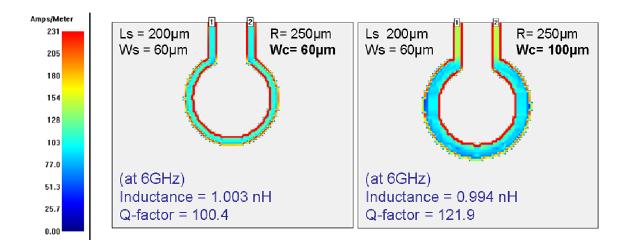

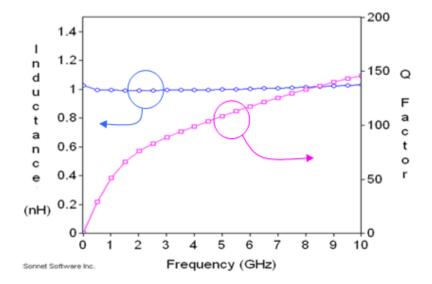

| Figure 40. | Simulated inductance value and quality factor of an optimal vertical ring inductor design.                                                                                                                                                            | . 69 |

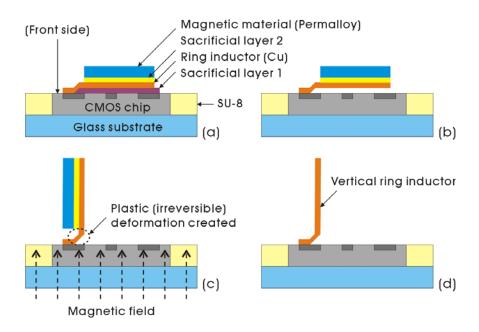

| Figure 41. | Schematic process flow for the fabrication of MEMS vertical inductors on CMOS substrates.                                                                                                                                                             | . 71 |

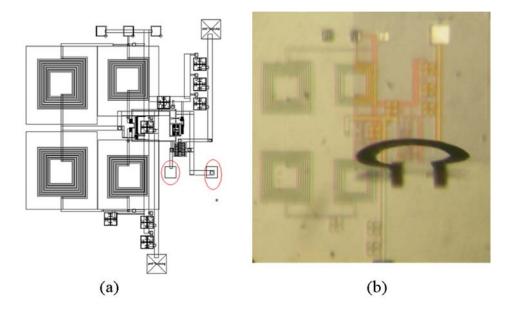

| Figure 42. | (a) Layout design of the 5.8 GHz VCO. The two contact pads circled in red were used to interface with the vertical ring inductor. (b) Optical microscopic image of the integrated vertical ring inductor on the $2\times 2$ mm <sup>2</sup> VCO chip. | . 72 |

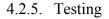

| Figure 43. | Comparison of Smith charts for measured S-parameter (a) and S-<br>parameter after De-embedding.                                                                                                                                                       | . 73 |

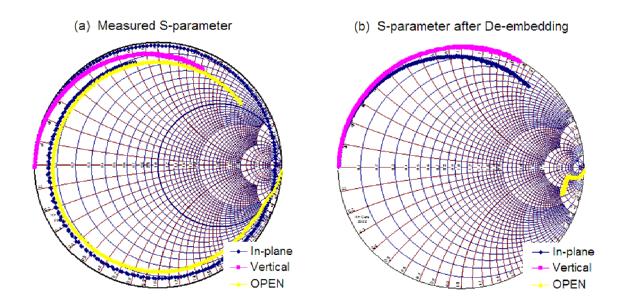

| Figure 44. | Inductance and quality factor of the in-plane and vertical ring inductors extracted from de-embedded $S_{11}$ parameters                                                                                                                              | . 75 |

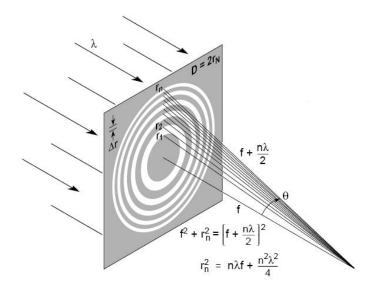

| Figure 45. | A Fresnel zone plate lens with plane wave illumination, showing only the convergent $(+1^{st})$ order of diffraction.                                                                                                                                 | . 76 |

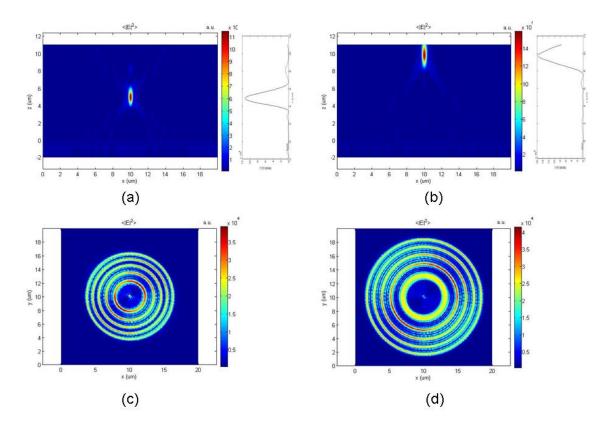

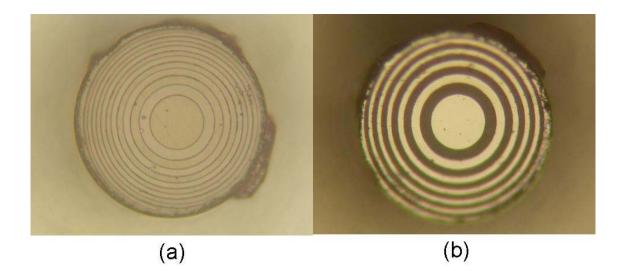

| Figure 46. | Simulated field distributions of the transmitted field in x-z plane: (a) $f = 5$ um and (b) $f = 10$ um, and simulated field distributions of Cr exit plane (x-y plane): (c) $f = 5$ um and (d) $f = 10$ um (Courtesy of Hyun-Chul Kim).              | . 78 |

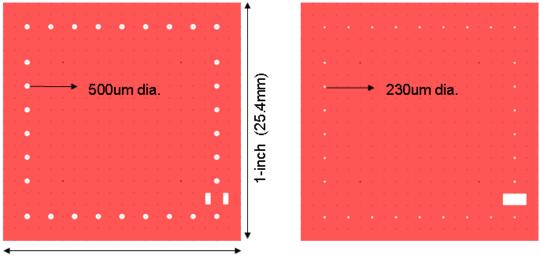

| Figure 47. | Mask layout designs for silicon wafer holders for fixing the optical fibers. (a) with 500um of hole diameter. (b) with of 230um of hole diameter.                                                                                                     | . 79 |

| Figure 48. | Fabrication steps of the optical fiber holder                                                                                                                                                                                                         | . 80 |

|            |                                                                                                                                                                                                                                                       |      |

| Page |  |

|------|--|

|------|--|

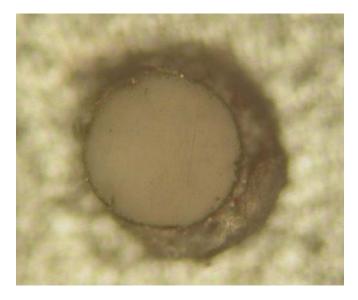

| Figure 50. | Optical image of the polished optical fiber with the silicon substrate                                                                                                                            | 81  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 51. | (a) Photoresist patterns of Fresnel zone plate on the optical fiber (b) Cr patterns after lift-off process                                                                                        | 82  |

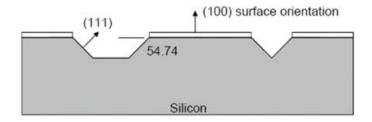

| Figure 52. | Schematics of anisotropically etched silicon substrate.                                                                                                                                           | 92  |

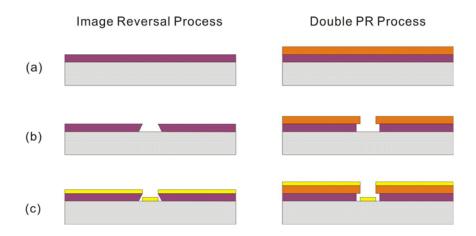

| Figure 53  | Schematic diagrams of Lift-off process; image reversal and double PR processes (a) Spin coating of PR, (b) Patterning PR with image reversal or double PR processes, (c) Deposition and lift-off. | .93 |

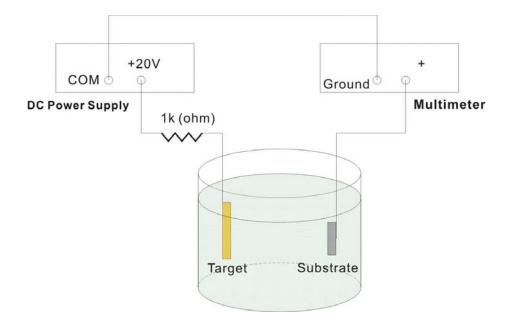

| Figure 54. | Schematic diagram of electroplating setup.                                                                                                                                                        | 94  |

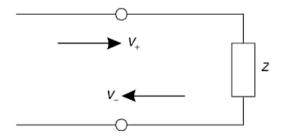

| Figure 55. | Transmission line terminated in a mismatched load.                                                                                                                                                | 95  |

## LIST OF TABLES

| Table 1. | Comparison among photolithography, micro-contact printing, and shadow mask lithography.                                                                                   | 4  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2. | Summary of failure modes in micro-contact printing [22].                                                                                                                  | 10 |

| Table 3. | Alignment error and its deviation at 8 different points of $1 \times 1$ cm <sup>2</sup> and $2 \times 2$ cm <sup>2</sup> boxes on three different fabrication substrates. | 50 |

| Table 4. | Comparison of anisotropic silicon etchants [30]                                                                                                                           | 92 |

#### 1. INTRODUCTION

Microfabrication, the generation of small-scale structures, is essential to much of modern science and technology [1-3]. Micro patterning is one of the most important fabrication steps in the micro devices to determine the critical dimension of desired patterns [4-6]. So far, several micro patterning techniques have been developed for various types of applications. Although photolithography is the most common micro-patterning technique and may be superior to other patterning techniques in general, it still has several disadvantages and limitations for certain applications.

First of all, the photolithography is an expensive and complex process since it is based on indirect patterning. In most case, the final patterns of the material (metal, dielectric, semiconductor, etc...) should be transferred from the photoresist. Therefore, it requires several process steps such as application of photoresist, exposure under UV light, development of resist, evaporation of film materials, wet/dry etching, and lift-off. Second, it cannot be used with a wide range of materials, especially when complex organic or biological functional groups are involved because the chemical and physical processes involved in photolithography could damage or contaminate volatile materials. Third, the surface of substrate should be flat in photolithography since the gap between the photomask and substrate causes diffraction of UV light, and thus non-uniform and lower resolution patterning.

This dissertation follows the style of Journal of Micromechanics and Microengineering.

In addition, handling and processing a small substrate are very difficult in conventional photolithography process. The spin coating of resist involved in photolithography cause the problematic "edge bead" which limits the resolution when applied on a small substrate. Alternatively, non-photolithographic micro patterning methods, which would complement the photolithography, such as micro-contact printing, shadow mask lithography (stencil lithography), nanoimprint lithography (NIL), and dippen nanolithography (DPN) have been developed and demonstrated [7-10]. These techniques would ideally circumvent the limitations of photolithography, which are applicable to three dimensional structures, inexpensive, experimentally convenient, and compatible with a wide range of materials and surface chemistries.

Among these non-photolithographic patterning techniques, micro-contact printing is superior to other methods with respect to compatibility with a wide range of materials and surface chemistries. It uses the relief pattern on the surface of a PDMS stamp to form patterns of self-assembled monolayers (SAMs) on substrates by conformal contact. Micro-contact printing differs from other printing methods in the use of self-assembly to form micro-patterns and microstructures of various materials. The contact printing also benefits from the low cost and fast process which consists of several essential steps [7]: (1) replication of master structures to the elastomeric stamp; (2) loading the elastomeric stamp with inking materials (alkanethiols or other surfactant-like molecules) and (3) forming a conformal contact with a solid substrate. During the contact time with the solid surface, the "ink" reacts with the surface, and a monolayer of molecules is transferred from the elastomeric stamp.

Shadow mask lithography (also called stencil lithography) is an emerging parallel, resistless, micro- and nano-patterning technique based on the deposition of material through apertures in a shadow mask onto a substrate [11]. Shadow mask lithography can greatly circumvent the damage or contamination which is especially important when volatile materials (e.g. organic or biological materials) are involved since it does not require resists, high-temperature processing, or chemical solvents. In addition, the shadow mask lithography is capable of patterning on top of free standing structures or three-dimensional topographies when the shadow mask and substrate are separated by a gap. Main challenges in current shadow mask technologies are the fine alignment and the mask-substrate gap control as well as the resolution for a correct pattern transfer from shadow mask to substrate. The characteristics of several micro and nano-patterning techniques are compared in Table 1 (modified from [7]).

On the other hand, several embedding methods have been introduced for the integration of microstructures into the small chip substrate [12-14]. In conventional photolithography, a residual resist remains on the edge of a substrate after resist spin-coating process, which is called "edge-bead". Although the "edge bead" can be removed by appropriate treatment (e.g. cotton swab), this greatly diminishes a possible processing area for the small substrate. An embedding system can effectively avoid this problem by extending processing area of the substrate, and thus, makes it possible to integrate complex MEMS (microelectromechanical system) components which may be even larger than the original substrate. In addition, it can be used for integration of microstructures onto the tip of fiber in micro optic application [15].

|                                                                                                                  | Photolithography                                                                     | Micro-contact<br>Printing                                                                                                              | Shadow Mask<br>Lithography                                                                        |

|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Definition of patterns                                                                                           | Rigid photomask<br>(patterned Cr<br>supported on a quartz<br>plate)                  | Elastomeric stamp or<br>mold (a PDMS block<br>patterned with relief<br>features)                                                       | Shadow Mask<br>(based on silicon<br>wafer)                                                        |

| Materials that can be patterned directly                                                                         | Photoresist (polymers<br>with photosensitive<br>additives)<br>SAMs on Au and<br>SiO2 | SAMs on Au, Ag, Cu,<br>GaAs, Al, Pd, and<br>SiO2<br>Colloidal materials<br>Organic and<br>inorganic<br>Polymer<br>Biological molecules | Any kinds of<br>materials that can be<br>evaporated (e.g. Au,<br>Ag, Cu, GaAs, Al,<br>Pd, SiO2, ) |

| Surfaces and<br>structures that can be<br>patterned<br>Current limits of<br>resolution (Minimum<br>feature size) | 2-D structures<br>Planar surfaces<br>< 50nm                                          | Both 2-D and 3-D<br>structures<br>Both planar and<br>nonplanar surfaces<br>< 50nm [16]                                                 | Both 2-D and 3-D<br>structures<br>Both planar and<br>nonplanar surfaces<br>< 50nm [17]            |

| Other advantages                                                                                                 | More reliable process<br>High accuracy of<br>alignment                               | Low cost and fast<br>process<br>Variable size of<br>patterns                                                                           | Available with fragile<br>or free standing<br>structures<br>No contamination                      |

Table 1. Comparison among photolithography, micro-contact printing, and shadow mask lithography.

In this study, micro patterning techniques such as micro-contact printing and shadow mask lithography have been researched for the direct patterning of volatile functional materials (e.g. biological, organic materials). In addition, the novel embedding techniques are developed for integrating conventional patterning technique into advanced devices such as the CMOS VCO chip and the optical fiber.

In section 2, a flexible and versatile micro-contact printing process using a micromachined elastomeric PDMS (Poly-dimethylsiloxane) stamp with two-dimensional arrays of pyramidal tips will be introduced. Two-dimensional arrays of dot patterns with different dot size (from sub-micron to a few microns) and density can be readily printed with a single stamp.

In section 3, a shadow mask technique with simple and accurate self-alignment system is designed and demonstrated for direct patterning of volatile materials. As an application, the shadow mask method is successfully integrated into the fabrication of OTFTs (Organic thin film transistors), and the electrical properties of the OTFTs are characterized.

In section 4, novel embedding techniques will be introduced for enabling conventional photolithography to be used with a small substrate. First, the polymer embedding technique is demonstrated for efficient post-CMOS integration of a high Q vertical ring inductor onto a  $2\times 2\mu m^2$  CMOS VCO chip. The performance of the vertical inductor was simulated numerically and experimentally characterized. In addition, silicon chip embedding technique is demonstrated for the integration of micro optical lens onto the tip of fiber.

# 2. MICRO-CONTACT PRINTING WITH VARIABLE DOT SIZE AND DENSITY\*

#### 2.1. INTRODUCTION

In many nano- and biotechnology applications, two dimensional (2D) arrays of dot chemical patterns with different dot size and density are necessary for parametric studies. For example, dot patterns of certain proteins can be used as "adhesive" for the attachment of cells and neurons on the target substrate. The shape, size and density of the dot patterns were found to significantly affect the morphology and functioning of the attached cells or neurons [18]. To generate such patterns, a commonly used method is micro-contact printing [7, 19]. Micro-contact printing utilizes an elastomer (e.g. PDMS) stamp to directly print chemical ("ink") patterns on a substrate, providing excellent material compatibility with a wide range of chemicals or biochemicals, e.g. DNAs (deoxyribonucleic acids) and proteins [20].

<sup>\*</sup> Reprinted with permission from "A micromachined elastomeric tip array for contact printing with variable dot size and density" by Jung Moo Hong, Fatih M Ozkeskin and Jun Zou, 2008. *J. Micromech. Microeng.* 18, 015003 (6pp), Copyright [2009] by IOP Publishing Ltd. (www.iop.org/journals/jmm)

#### 2.1.1. Micro-contact Printing

Micro-contact printing is categorized into soft lithography which includes replica molding (REM), microtransfer molding (TM), micromolding in capillaries (MIMIC), and solvent-assisted micromolding (SAMIM) [7]. All these methods have the common feature of using a patterned elastomer as the stamp, mold, or mask (rather than a rigid photomask) to generate micropatterns and microstructures. Likewise, micro-contact printing uses a PDMS stamp to create micro patterns of SAMs of inks on the substrate through conformal contact. Although photolithography is a dominant technology, it is not always the best option for all applications. For example, it is an expensive technology; it is poorly suited for patterning nonplanar surfaces or three-dimensional micro patterns; and it is directly applicable only to a limited set of photosensitive materials (e.g. photoresists). The characteristic of photolithography is such that it is relatively little used for microfabrication based on materials other than photoresists; to work with other materials it is necessary to attach chromophores or add photosensitizers.

To illustrate the micro-contact printing procedure, the entire printing process of alkanethiols on gold was described in Figure 1. Micro-contact printing relies on (1, 2) replication of a patterned elastomeric stamp from a master to form an elastic stamp (3) that can be inked with a monolayer-forming ink (7) using either wet inking (4) or contact inking (5). The inked stamp is then used to print (6) a pattern that selectively protects the noble-metal substrate during the subsequent etch (8).

Figure 1. Schematic diagram of micro-contact printing: A prepolymer (2) covering the master (1) is cured by heat or light, and demolded to form an elastomeric stamp (3). The stamp is inked by immersion (4) or contacted with an ink pad (5), and printed onto the substrate (6), forming a SAM. The ink pattern (7) is then transferred into the substrate by a selective etch (8) [21].

#### 2.1.2. Failure Modes in Micro-contact Printing

Stamp deformation can affect the dimensional stability of the micro-contact printing process. Since micro-contact printing uses soft elastomer as a stamp, several constraints might be imposed by stamp deformation according to the relief structures on the surface [22]. In order to explain the deformation of an elastomeric stamp, a simple stamp structure was assumed as shown in Figure 2.

Figure 2. Schematic diagram of an elastomeric stamp.

The lateral dimension of the stamp, D is assumed to be much greater than its thickness H. In turn, H is much larger than the dimension of the surface features. The surface relief consists of identical micro size punches which are prisms with a rectangular cross section. The axes of these prisms are parallel to the z axis. The punches are equally spaced with spacing 2w along the x axis. Let h be the height of the

punch and 2a be its width. In this condition, the common failure modes which can be occurred during contact printing are summarized in Table 2.

$$D \gg H \gg h, w, a \qquad (2.1)$$

Table 2. Summary of failure modes in micro-contact printing [22].

| Description                                             | Sketch | Result                                                                                                                  |

|---------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>Roof collapse:<br/>unwanted contact</li> </ol> | σ      | $\frac{4\sigma_{\infty}w}{\pi Eh}(1+\frac{a}{w})\cosh^{-1}\left[\left(\cos(\frac{w\pi}{2(w+a)})\right)^{-1}\right] < 1$ |

| 2. Buckling                                             | ¢σ∞    | $\frac{-3\sigma_{\infty}h^2}{4\pi^2 E^*a^2} < \frac{1}{1+w/a}$                                                          |

| 3. Lateral collapse                                     | Y      | $\frac{h}{2a} \left(\frac{2\gamma_s}{3E^*a}\right)^{1/4} < \sqrt{w/a}$                                                  |

| <ol> <li>Smooth surface<br/>asperities</li> </ol>       | k=2    | $\frac{-\pi E * h_a}{4\sigma_{\infty} a} < 1 + w/a$                                                                     |

| 5. Radius of an edge<br>rounded by surface<br>tension   | R      | $R \sim \frac{\gamma}{2E}$                                                                                              |

Where  $\sigma_{\infty}$  is the remote stress which is related to the compressive load P acting on a punch and N is the number of punches per unit length in the x direction.

$$N = \frac{1}{2(a+w)}$$

$$P = \sigma_{\infty} / N = 2(a+w)\sigma_{\infty}$$

(2.2)

The elastomer is assumed to be homogeneous and isotropic with Young's modulus E and Poisson's ratio v. Most elastomers are incompressible with v $\approx$ 0.5 and E between 0.1 and 10 MPa. Here  $\gamma_s$  is the surface energy, and E<sup>\*</sup> is defined by

$$E^* = \frac{E}{1 - v^2} \approx \frac{4}{3}E$$

.....(2.3)

As described above, if the aspect ratio of h to 2a is too low, all surfaces of the stamp can be deformed into contact with the substrate (roof collapse). On the other hand, when the aspect ratio is too large, the punches can collapse under their own weight (buckling). Also, neighboring punches may adhere to each other because of the capillary force experienced by the punches during the inking process (lateral collapse). In addition, surface tension forces can deform the sharp corners of the punches. This effect is particularly important for high resolution patterns less than 1um. Therefore, a stable and reliable elastomer stamp can be obtained by considering the conditions of failure modes.

#### 2.1.3. Preliminary Work

Micro-contact printing has been conducted by standard PDMS stamps with pillar arrays and line structures. In order to prepare PDMS stamps, silicon wafer with photoresist patterns was used for a master.

Figure 3. The fabrication steps for PDMS molding. (a) Spin coating of photoresist on the silicon wafer. (b) Photoresist was patterned by photolithography. (c) PDMS solution was poured onto the silicon wafer. (d) PDMS was cured and detached from the silicon wafer.

Figure 3 shows the fabrication process of PDMS stamp. The photoresist was first spin coated and patterned by photolithography (Figure 3a and Figure 3b). Second, the PDMS base and curing agent was mixed with the ratio of 10 to 1 uniformly, and poured on the silicon wafer with photoresist patterns (Figure 3c). Third, bubbles inside the PDMS were removed in the vacuum jar for 1hr. Next, the entire piece was baked in the oven at 90°C for 1hr for curing the PDMS. Finally, the PDMS mold was detached from the master of silicon wafer (Figure 3d). Figure 4 shows the SEM (scanning electromicroscope) images of cylindrical pillar arrays (Figure 4a and Figure 4c) and line structures (Figure 4b and Figure 4d). Here, the center to center distance between two near patterns (pillar or line structures) was designed to 10µm. The sidewall slopes of PDMS structures were caused by the original shape of the photoresist patterns.

Figure 4. Scanning electron microscope images of PDMS stamps (a), (c) cylindrical pillar array. (b), (d) parallel line structures.

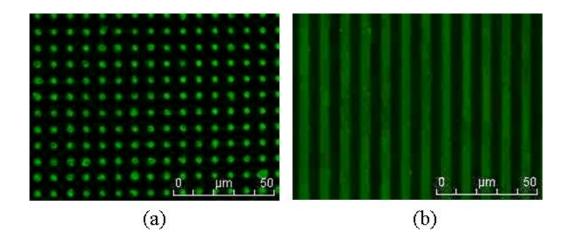

Micro-contact printing using fabricated PDMS stamp has been conducted with a fluorescent dye (fluorescein sodium salt; Sigma Aldrich, Saint Louis, MO), which has 460nm of excitation wavelength and 515nm of emission wavelength. The characteristics of fluorecein sodium salt have been described in APPENDIX 2 in detail. After the contact printing of fluorescent dye was performed on a slide glass substrate, the printed dye patterns were observed with a confocal microscope (Leica TCS SP5 Confocal Laser Scanning Microscopes). Figure 5 shows the fluorescent images of the printed dye patterns under the confocal microscope. The bright green area indicates the patterned fluorescent dye where the color corresponds to the emission wavelength of the dye.

Figure 5. Confocal microscope images of printed fluorescent dye.

#### 2.1.4. Motivation

Current micro-contact printing process generally follows a "one stamp for one pattern" paradigm. To print different patterns, multiple stamps have to be fabricated, which is not efficient and cost-effective. Also, to achieve submicron patterning, electron beam lithography is generally required to conduct stamp fabrication, which is a very expensive and slow process. During the past few years, certain effort has been made to address the above two intrinsic issues and extend the capability of micro-contact printing. To achieve different pattern size with single stamp, lateral stretching or compression, vertical compression (by applying different contact pressure) or swelling (by soaking in certain solvents) of the PDMS stamp was investigated [23]. However, these techniques can only generate small change of the dimensions and also requires special mechanical loading tool or chemicals, which would limited their application. Also, by using an AFM (atomic force microscope) testing grating as the master mold to make special Vshaped PDMS stamps, straight lines with sub-100 nm width was achieved without involving electron beam lithography process [24]. However, this method apparently lacks the generosity for contact printing of other shapes and density of patterns.

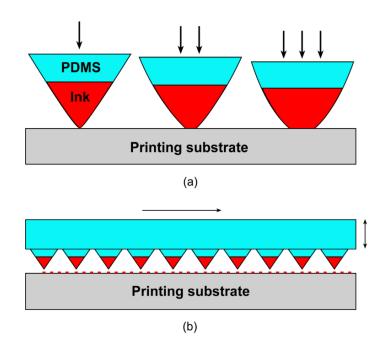

For the patterning with variable dot size and density, a novel micro-contact printing method was demonstrated using a single elastomeric stamp consisting of a 2D array of pyramidal PDMS tips. The PDMS tips were molded from a single-crystalline silicon master fabricated by photolithography and anisotropic bulk etching which are relatively easy and low cost IC fabrication processes. Variable-dot-size printing (from sub-micron to a few microns) was achieved by applying different contact pressure to induce variable mechanical deformation and thus contact area of PDMS tips (Figure 6a). Different from the columnar structures in conventional PDMS stamps, which are subject to limited lateral deformation and mechanical instability issues [25, 26], the pyramidal shape of the PDMS tip ensures a stable mechanical deformation for a controllable wide-range pattern generation.

Figure 6. An illustration of micro-contact printing with pyramidal PDMS tip arrays: (a) Variable-dot-size printing by applying different pressures on the tips; (b) Variable-density printing in a "step-print" manner by using a transitional stage.

Variable-density printing was also achieved in a "step-print" manner by using a mask contact aligner which has the up-and-down stage in z-direction for stamping and

the x-y transitional stage for aligning each step stamping (Figure 6b) [27, 28]. As a result, 2D arrays of dot patterns with different dot size and density can be readily printed with a single stamp. This technique eliminates the need for the fabrication of multiple stamps (for different pattern size) and electron beam lithography (for sub-micron printing) and thus is especially useful for parametric study applications.

#### 2.2. MODELING AND SIMULATION

#### 2.2.1. Modeling and Simulation of PDMS Tip Deformation

To predict the contact area of the PDMS tip (thus dot size of printing) under different applied pressure, the mechanical deformation and contact pressure of the PDMS tip was simulated with finite element analysis (FEA) tool (CosmosWorks Designer© add-in under SolidWorks©). Second order solid tetrahedral mesh elements were used in the simulation, which allow proper mapping to curvilinear geometry which distributes the stress effectively. Here, the applied pressure refers to the external pressure or force exerted on the stamp to induce the mechanical deformation of PDMS tips. The contact pressure means the actual pressure existing at the contact of the deformed PDMS tips on the printing substrate.

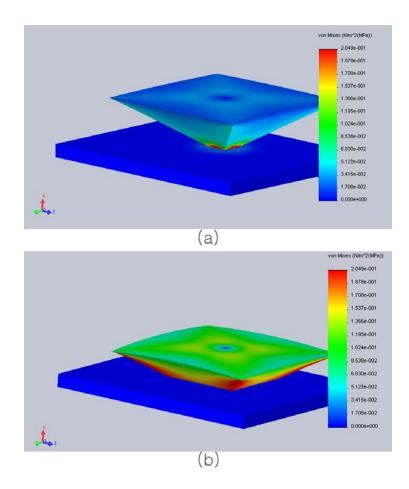

Figure 7a and Figure 7b show the FEA model used in the simulation, illustrating the deformation and stress distribution corresponding to an applied pressure of 80 g/cm<sup>2</sup> and 320 g/cm<sup>2</sup> on a rigid contacted substrate (e.g. glass), respectively.

Figure 7. FEA model of a PDMS pyramidal tip showing its deformation and stress distribution under applied pressures of (a)  $80 \text{ g/cm}^2$  and (b)  $320 \text{ g/cm}^2$ .

To ensure the accuracy of the simulation, the actual Young's modulus of the PDMS stamp was experimentally characterized. A "compression" test of a PDMS block was conducted by putting different weights (uniformly distributed on the PDMS block) and monitoring the deformation (in thickness) with a digital indicator. An elastic

modulus of 0.67MPa was obtained, which is close to the nominal value of 0.75MPa for PDMS with a mixing ration of 10:1 [29].

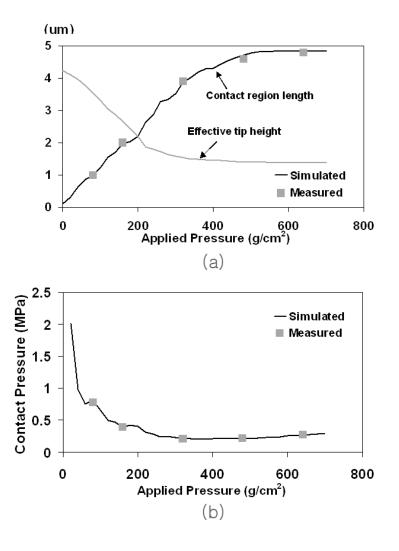

The size of the contact region and effective tip height of the PDMS tip were estimated from the simulated results (Figure 8a).

Figure 8. (a) Simulated contact region size and height of the PDMS tip under different applied pressure; (b) Estimated contact pressure of the PDMS tip under different applied pressures.

The size of the contact region first increases linearly with the applied pressure from 100 nm at zero applied pressure to 4.8  $\mu$ m at 400g/cm<sup>2</sup> (39.2 kPa) and then starts to saturate due to excessive deformation under higher applied pressure. This indicates a total tuning range (theoretical) of 4800% for the dot size for PDMS pyramidal tips with a  $6 \times 6 \mu m^2$  base area.

The average contact pressure of the PDMS tip on the printing substrate was also determined based on the applied pressure and the simulated contact area (Figure 8b). It reaches its maximum (around 2MPa) at very low applied pressure when the tip remains sharp with a very small contact area. As the applied pressure increases, the tip deforms and the actual contact pressure drops quickly as a result of the increased contact area. At high applied pressure, the contact pressure increases linearly with the applied pressure due to the saturation in the deformation of the PDMS tip. The overall extremely low contact pressure makes it feasible to apply the variable dot size contact printing technique even on soft substrates (e.g. polymer).

With the built FEA model, the maximum strain of the PDMS tip under different applied pressure was also obtained. A maximum strain of 13% occurs when an excessive applied pressure of 700g/cm<sup>2</sup> (the tip deformation goes deep into saturation under this pressure). This value is still much smaller than the 20~30% yield stain of elastomer material, such as PDMS. Therefore, the tip deformation is deemed to be completely elastic and fully reversible to ensure the reproducibility of contact printing with PDMS tip array. Still, fatigue of the PDMS stamp might affect the reproducibility

under excessive usage. However, we believe this will not occur in most contact printing applications where a light to medium usage of stamps are normally encountered.

One common issue in contact printing is that PDMS stamps tend to collapse under high applied pressure especially when the aspect ratio of the stamp structures is below a certain value. For the tip array stamp, the smallest tip which can be created faithfully with conventional photolithography should have a base area of  $1 \times 1 \text{ } \mu\text{m}^2$  and a corresponding height of 0.7  $\mu$ m. Assuming the tip-to-tip spacing is 2  $\mu$ m and the thickness of the stamp substrate is 2 mm, finite element simulation was conducted to study the possible stamp collapse. Under different applied pressure, the deformation of stamp substrate was negligible, compared with that of the PDMS tip. Stamp collapse doesn't happen because the dense pattern of the tips supports the substrate and distributes force uniformly. However, the possibility of stamp collapse increases with sparser tip pattern (larger tip-to-tip spacing) and thinner stamp substrate. For a given base size and height of the tips, the stamp collapse can be largely avoided when the tips are made dense enough. The thickness of the PDMS stamp substrate may also play a role in stamp collapse. For easy handling, the thickness of a PDMS stamp substrate is usually around  $2 \sim 5$  mm, which is much larger than the height of the PDMS tips (a few microns). In this case, most of the applying pressure and stamp deformation will be concentrated on the PDMS tips. Therefore, the thickness of the stamp substrate does not play a significant role in the tip-based contact printing process, as long as it is within the millimeter range. Only when the stamp substrate becomes very thin (comparable to the height of the tips), does the thickness start to affect the printing process.

#### 2.2.2. Comparison with Columnar Pillar Structure

The deformation and contact pressure of the columnar structures in conventional PDMS stamp under different applied pressure was also simulated for comparison. A square stamp structure with the same base area ( $6 \times 6 \ \mu m^2$ ) and height (4.24  $\mu m$ ) as those of the pyramidal tip was used in the simulation. As shown in Figure 9, the stamp structure was assumed to be pressed onto a rigid substrate with an applied pressure of 80 g/cm<sup>2</sup> and 320 g/cm<sup>2</sup>, respectively.

Figure 9. FEA model of a PDMS square pillar showing its deformation and stress distribution under applied pressures of (a)  $80 \text{ g/cm}^2$  and (b)  $320 \text{ g/cm}^2$ .

The size of the contact region and the effective height of the stamp structure were estimated from the simulated results (Figure 10a). It increases almost linearly with the applied pressure from 6  $\mu$ m at zero applied pressure to 6.7  $\mu$ m at 700 g/cm<sup>2</sup> (68.6 kPa), which indicates a total tuning range of only 11.6% for the dot size.

Figure 10. (a) Simulated contact region size and height of the PDMS square stamp under different applied pressures; (b) Estimated contact pressure of the PDMS square stamp under different applied pressures.

This result shows that conventional PDMS stamp structure does not facilitate the lateral deformation even under high applied pressure and thus is not effective for achieving variable pixel size. The average contact pressure of the PDMS tip on the printing substrate was also determined based on the applied pressure and the simulated contact area (Figure 10b). Since the contact area increases very slowly with the applied pressure, the contact pressure assumes almost linear relationship with the applied pressure.

### 2.3. FABRICATION

## 2.3.1. Fabrication of Silicon Master

The design and fabrication process of the PDMS tip array is illustrated in Figure 11. To form the PDMS tip array single crystalline silicon master mold was first fabricated. The silicon wafer was first cleaned with piranha solution (Sulfuric acid: Hydrogen peroxide= 3:1) and immersed into buffered oxide etchant to remove the initial oxide layer. For the silicon etch mask, 1000Å of oxide layer was grown by dry oxidation at 1100°C for 1hr. The grown silicon oxide layer was patterned for making square opening arrays by photolithography and buffered oxide etching. The four sides of the square windows were aligned to the <110> crystal direction of silicon. In order to make pyramidal cavities, the {100} silicon wafer was anisotropically etched by a solution of a concentration of 30% KOH by weight. The KOH etching was performed in the covered petri-dish (to maintain the concentration of KOH) on a magnetic stirring hotplate at 80°C, which terminated by itself when the {111} crystal surfaces was

exposed [30]. Thus, a silicon mold consisting of a 2D array of uniform pyramidal cavities with atomic apex sharpness (bounded by the four {111} crystal surfaces) can be readily obtained (Figure 11a). This fabrication of the silicon master mold does not require any complex process or special equipment, which results in a simple, straightforward and low cost fabrication process.

Figure 11. An illustration of the design and fabrication process of the pyramidal PDMS tip array (a) oxide layer patterning followed by anisotropic silicon etching, (b) antiadhesive surfactant coating, (c) curing PDMS and detaching it from the substrate.

### 2.3.2. Fabrication of PDMS Stamp

To make the stamp, PDMS solution was prepared from a mixture of Sylgard® 184 silicon elastomer base and silicon elastomer curing agent (from Dow Corning) with a ratio of 10:1. To ensure easy detachment of PDMS stamp from the silicon mold after

PDMS curing, Tridecafluoro-1,1,2,2,-tetrahydrocytyl-1-trichlorsilane (from Sigma-Aldrich) was coated on the silicon mold as an anti-sticking surfactant (Figure 11b). Ideally, only a mono layer of the surfactant is needed and thick coating of the surfactant can cover the end-point of pyramidal cavities and thus reduce the sharpness of the molded PDMS tips. In order to obtain a thin layer in the etched cavities, vapor coating of surfactant was conducted, instead of spin-coating. Several drops of the surfactant to evaporate and condense on the silicon surface. Next, the mixed PDMS solution was poured on the silicon mold and cured in the oven for 1hr at 90°C. Finally, the cured PDMS stamp was directly peeled off from the silicon master mold (Figure 11c).

Figure 12 shows the scanning electron microscopic (SEM) images of some molded PDMS tips. The radius of curvature of the PDMS tip is estimated to be around 100 nm from the zoom-in SEM image. In the current design, a base size of  $6 \times 6 \ \mu m^2$  and a tip-to-tip spacing of 10 $\mu$ m were chosen as a balance of the tip density and height. Based on the fixed taper angle of the PDMS tip (70.5°) defined by the pyramidal cavity, the height of the PDMS tip is determined as 4.24  $\mu$ m. Other combination of tip base size and spacing can be also selected to suit the needs of different applications. Increasing tip base size and spacing will provide a wide tuning range of the dot size, however at the cost of dot density. On the other hand, smaller base size and spacing will result in higher dot density with smaller tuning range of the dot size.

Figure 12. Scanning electron microscopic images of molded PDMS pyramid tips: (a) front view; (b) prospective view.

## 2.4. EXPERIMENTAL RESULTS

## 2.4.1. Micro-contact Printing with PDMS Stamp

To demonstrate the proposed contact printing concepts, a fluorescent dye (Rhodamine B; Sigma Aldrich, Saint Louis, MO) was used as an ink. Rhodamine B is

extensively used in biological applications and its pattern can be easily measured with fluorometer or confocal microscopes. Because of the good affinity of ethanol on PDMS surface, Rhodamine B was dissolved in ethanol with a concentration of 1 mg/ml. To ensure a uniform inking of the PDMS tips, a pre-cleaned glass slide was used as an inkpad [31, 32]. The schematic contact printing process was illustrated in Figure 13.

Figure 13. Micro-contact printing process using inking pad method; (a) spin-coating of fluorescent dye solution on the slide glass, (b) inking PDMS stamp, (c) inked PDMS tip array, (d) contact printing with external pressure, (e) remove the PDMS stamp from the substrate.

After spinning the Rhodamine B solution onto the glass slide (one inch square) at 2000 rpm for 15 seconds, the inking of the PDMS stamp was conducted by contacting

the stamp onto the glass slide with its own weight for 20 seconds (Figure 13a). To demonstrate variable-dot-size printing, the inked PDMS stamp was pressed onto another pre-cleaned glass slide with different applied pressure, which was controlled by putting different weights onto the PDMS stamp (Figure 13b). A contact time of 20 seconds was used for all the experiments.

Micro-contact printing of two types of fluorescent dyes (Rhodamine B and Fluorescein sodium salt) has been conducted with the inking pad method. The pressure of 100g/cm<sup>2</sup> was applied on the PDMS stamp after inking the PDMS tip arrays. Figure 14 shows the printed patterns of two fluorescent dyes with high contrast and uniformity. When the inking pad process was involved as shown above, the contrast and uniformity could be greatly improved with higher repeatability.

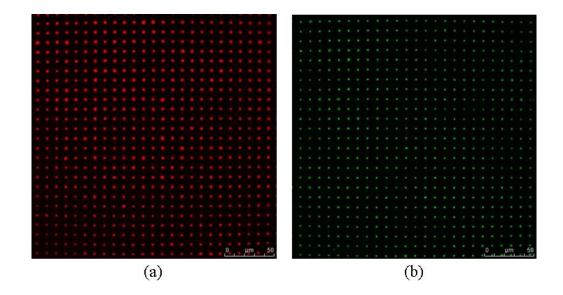

Figure 14. Micro-contact printing of fluorescent dyes using the inking pad process; (a) Rhodamine B, (b) Fluorescein sodium salt.

#### 2.4.2. Contact Printing with Variable Dot Size

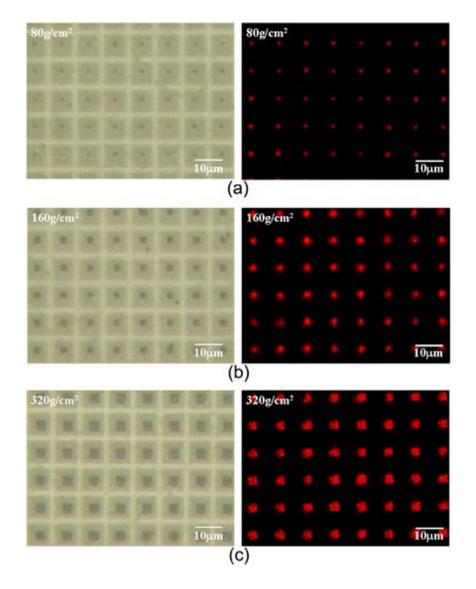

Since the PDMS is an elastomer, it can be easily deformed by external pressure. Especially the pyramidal tip array can be greatly deformed since the applying force is concentrated on the contact areas of the tip array. Therefore, the material characteristic of PDMS which is "soft" and the mechanical structure which has "smaller contact area" are considered to change the contact area, and thus the pattern size to be printed. The deformation and contact area of the PDMS tips were measured under an optical microscope. The printed Rhodamine B dot patterns were inspected under a confocal microscope (Leica<sup>®</sup> TCS SP5). As shown in Figure 15, the size of the (square) contact area of the PDMS tips on the glass slide is around  $1 \times 1 \mu m^2$ ,  $2 \times 2 \mu m^2$ , and  $4 \times 4 \mu m^2$  for an applied pressure of 80 g/cm<sup>2</sup>, 160 g/cm<sup>2</sup>, and 320 g/cm<sup>2</sup>, respectively, which closely match the size of printed Rhodamine B patterns.

In our work, all the experiments were conducted by manually putting the stamp (and the weight) onto the printing substrate. The method doesn't offer a good control of the contact pressure. The minimum pattern size was slightly smaller than  $1 \times 1 \,\mu\text{m}^2$ , which was obtained when there was not additional weight applied on the stamp. This corresponds to a tuning range of around 400%, which is still much wider than that obtained with conventional stamp. By "putting" the PDMS tip onto a scanning probe and using an atomic force microscope to provide an accurate control of the contact force (pressure), a minimum pattern size of 80nm was achieved, which approaches the radius

curvature of the tip [33]. Therefore, when a good contact control setup is used, a minimum pattern size of 100nm could be expected using the tip array stamp, with a tip radius of curvature around 100nm. In this case, a much wider tuning range could be expected.

Figure 15. Optical microscopic images of deformed PDMS tips (left) and fluorescent images of printed Rhodamine B patterns (right) under different applied pressures: (a) 80g/cm<sup>2</sup>; (b) 160g/cm<sup>2</sup>; (c) 320g/cm<sup>2</sup>.

By measuring the actual tip contact area under a microscope, the actual tip contact pressure can be determined. The measured tip contact area and contact pressure at different applied pressure is plotted in Figure 8 with the FEA simulated data, showing a good match between these two. This indicates the good accuracy of our FEA model and also the experimentally obtained value of the Young's modulus of PDMS. Also, to verify the excellent reliability of the tip array stamp predicted by FEA, a contact test was conducted when a tip array stamp was contacted a glass substrate with an applied pressure of 700g/cm<sup>2</sup> for 100 times. The tip array stamp was inspected under an SEM before and after the tests, with no visible change of tip shape observed.

## 2.4.3. Contact Printing with Variable Density

Figure 16. A schematic diagram of the multiple contact printing scheme with the x-y alignment stage and z-directional moving control.

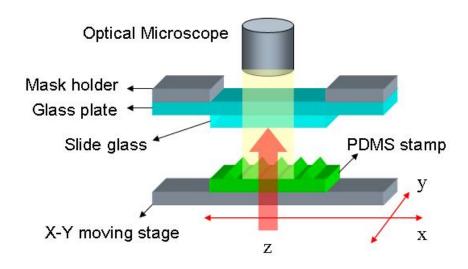

With the PDMS tip array, variable-density contact printing of dot patterns was also demonstrated in a "step-print" manner using the x/y transitional stage of a contact mask aligner (Karl Suss<sup>®</sup> MJB-3). Figure 16 shows a schematic diagram of the step-printing system. The printing substrate (glass slide) was mounted on the mask chuck of the contact aligner, while the inked PDMS stamp was mounted on the wafer chuck with the tips facing up. After the PDMS stamp and the glass slide was brought into contact for the first printing, the wafer chuck is lowered to separate the PDMS stamp from the glass slide and shift to a new location for a second contact printing.

Figure 17. Fluorescent image of double printed Rhodamine B dot patterns under different contact pressures.

Figure 17 shows the printing results of Rhodamine B dot patterns created with two times of printing. Because the contact aligner does not have any contact control, the contact pressure associated in the two contact printing is inevitably different, which causes the difference of the size of the printed patterns. It is expected that more uniform contact printing can be achieved when a better controlled pressure source is used.

## 2.5. CONCLUSIONS

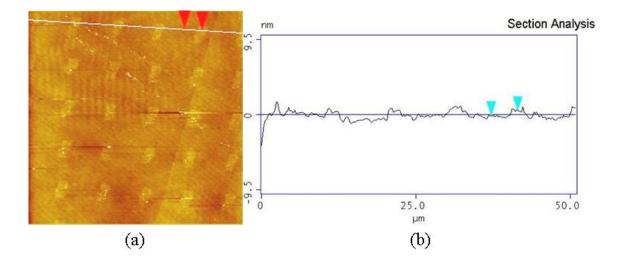

In conclusion, a flexible and versatile micro-contact printing process using a PDMS stamp consisting of a 2D array of pyramidal tips was demonstrated. When equipped with a fine resolution x/y/z translation stage and controlled pressure source, this technique is expected to provide a simple, efficient, and low-cost method to create variable 2D arrays of dot chemical patterns for nano- and biotechnology applications. In addition, as shown in Figure 18, the micro-contact printing developed in this study enables SAMs of functional materials to be printed and patterned with variable size and density.

Figure 18. Atomic force microscope images of the printed fluorescent dye patterns; (a) top view of the printed patterns, (b) height profile of the patterns.

# 3. DIRECT PATTERNING OF VOLATILE MATERIALS USING SHADOW MASK METHOD\*

## 3.1. INTRODUCTION

In microfabrication and micromachining, photolithography has been widely used for patterning thin-film materials for semiconductor device fabrication. However, the involvement of photoresist processing in a typical photolithography process makes it not suitable for patterning a wide range of organic materials. This is because the deposition, exposure, development and removal of photoresist would cause contamination, degradation or even damage to these materials. To address this issue, shadow masks are developed and used in vacuum deposition chambers to achieve direct material patterning without photolithography [34, 35] (Figure 19). A typical shadow mask consists of a thin flat substrate with open windows corresponding to the material patterns to be formed. After the vacuum deposition process starts, thin-film materials can be only deposited through the open windows.

<sup>\*</sup> Reprinted with permission from "A novel micromachined shadow mask system with self-alignment and gap control capability" by Jung Moo Hong and Jun Zou, 2008. J. *Micromech. Microeng.* 18, 055002 (7pp), Copyright [2009] by IOP Publishing Ltd. (www.iop.org/journals/jmm)

Figure 19. Schematic diagram of material deposition and patterning through a shadow mask.

Since the shadow mask technique can directly create a patterned thin-film layer in one process step, the possible material contamination, degradation and damage associated with photoresist handling can be largely avoided. This feature also makes the shadow-mask technique very useful for selective material deposition on micromachined substrates with delicate free-standing structures on the surface, such as micro cantilevers and membranes.

### 3.1.1. Shadow Mask Lithography (Stencil Lithography)

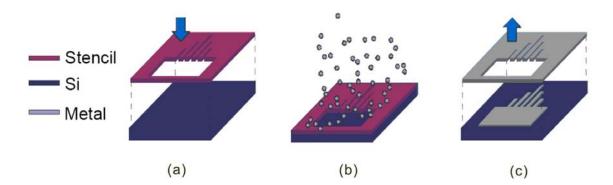

The shadow mask technique is a promising tool for micro- and nano-patterning of volatile functional materials. It is based on selective deposition of material through apertures in the shadow masks. The advantage of this technique is that it does not rely on photoresist processes. Although photolithography is still the main method used for creating micro- and nanostructures in thin films, it requires several process steps, for example, spin-coating of photoresist, thermal baking, mask alignment, exposure, development, evaporation of a thin film, and lift off. On the other hand, the shadow mask method can create a structured thin film in two process steps; alignment and deposition steps. The deposited structures can either be used directly, transferred into a sub-layer, combined by lift-off processes, or refined by self assembly or other growth processes.

The shadow mask method typically uses stainless steel or solid-state membranes with apertures from micro- to nano-meter range (< 100 nm). These patterns can be transferred to a substrate in a single process step, potentially in a non-contact mode. These characteristics make the shadow mask method applicable to surfaces that are either mechanically unstable free standing structures, such as cantilevers and membranes, or functionalized for organic and biological applications. Figure 20. shows a schematic process flow of the shadow mask lithography.

Figure 20. A schematic process flow of the shadow mask lithography; (a) placing and aligning the stencil with the substrate (b) deposition through the stencil (c) remove the stencil from the substrate.

The main advantages of stencil lithography are: (1) Clean process without involving resist, development, baking, and harmful chemicals, (2) Compatibility with pre-patterned, fragile, non-planar, functionalized, CMOS, MEMS substrates because of its non-contact process, (3) Re-usable, (4) Rapid and low-cost patterning, (5) Wide range of size features (micro and nanostructuring in a single step), (6) High flexibility of materials (metals, oxides, piezoelectrics, organic molecules, SAMs).

## 3.1.2. Motivation

Currently, shadow masks made of thin stainless-steel plates are most commonly used. However, their mechanically stability and resolution are generally not adequate for micron-size patterning, which limits their application mainly to the creation of large patterns (e.g. sub-millimeter). This is because the conventional machining techniques used for making the stainless-steel shadow mask are difficult to reach micron-size resolution. Also, the shadow mask will become very flexible and easy to deform when it

is thin (to facilitate its fabrication), causing distortion in the created patterns. To address the above issues, shadow masks made of silicon substrates have been investigated to benefit from the mechanical stability of silicon wafer and higher resolution provided by microfabrication and micromachining [36-39]. However, in order to use shadow masks to conduct layer-by-layer device fabrication, accurate alignment and gap control between the shadow mask and fabrication substrate will be also required, which otherwise has been a challenging issue in current shadow mask techniques. First, due to the unavailability of the optical alignment systems (similar to those used in photolithography), the alignment of shadow mask with the fabrication substrate largely has to rely on the use of mechanical fixtures, which are subject to issues such as complex alignment process, mechanical robustness, low repeatability or large alignment errors. Second, a proper mask-substrate gap is important to prevent loss of patterning fidelity (due to a large gap) and possible damage to any delicate structures (due to a hard contact caused by a small gap). Unfortunately, a straightforward and precise control of masksubstrate gap has not been obtained up to date.

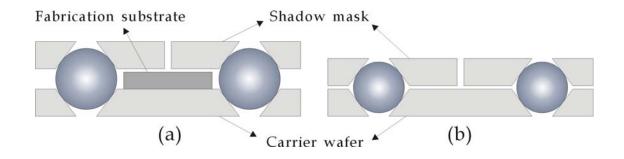

In this study, a new silicon shadow mask system was reported, which is capable of simple and accurate mask-substrate alignment and gap control. The shadow mask was fabricated with photolithography and anisotropic bulk etching of {100} silicon wafer. By using steel spheres and bulk-etched pyramidal cavities as alignment structures, accurate and robust self-alignment and gap control have been achieved. As an application of the new shadow mask technique, organic thin film transistor (OTFT) have been also fabricated and tested successfully.

## 3.2. DESIGN OF SHADOW MASK SYSTEM

### 3.2.1. Design for Self-Alignment