# GENERIC IMPLEMENTATION OF PARALLEL PREFIX SUMS AND THEIR APPLICATIONS

A Thesis

by

TAO HUANG

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

May 2007

Major Subject: Computer Science

# GENERIC IMPLEMENTATION OF PARALLEL PREFIX SUMS AND THEIR APPLICATIONS

A Thesis

by

### TAO HUANG

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

# Approved by:

Chair of Committee, Lawrence Rauchwerger

Committee Members, Nancy M. Amato

Jennifer L. Welch

Marvin L. Adams

Head of Department, Valerie E. Taylor

May 2007

Major Subject: Computer Science

#### ABSTRACT

Generic Implementation of Parallel Prefix Sums and Their Applications.

(May 2007)

Tao Huang, B.E.; M.E., University of Electronic Science and Technology of China Chair of Advisory Committee: Dr. Lawrence Rauchwerger

Parallel prefix sums algorithms are one of the simplest and most useful building blocks for constructing parallel algorithms. A generic implementation is valuable because of the wide range of applications for this method.

This thesis presents a generic C++ implementation of parallel prefix sums. The implementation applies two separate parallel prefix sums algorithms: a recursive doubling (RD) algorithm and a binary-tree based (BT) algorithm.

This implementation shows how common communication patterns can be separated from the concrete parallel prefix sums algorithms and thus simplify the work of parallel programming. For each algorithm, the implementation uses two different synchronization options: barrier synchronization and point-to-point synchronization. These synchronization options lead to different communication patterns in the algorithms, which are represented by dependency graphs between tasks.

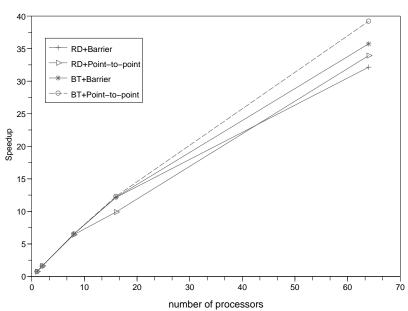

The performance results show that point-to-point synchronization performs better than barrier synchronization as the number of processors increases.

As part of the applications for parallel prefix sums, parallel radix sort and four parallel tree applications are built on top of the implementation. These applications are also fundamental parallel algorithms and they represent typical usage of parallel prefix sums in numeric computation and graph applications. The building of such applications become straighforward given this generic implementation of parallel prefix sums.

#### ACKNOWLEDGMENTS

My respect and gratitude go to my adviser Dr. Lawrence Rauchwerger and co-adviser Dr. Nancy Amato for their guidance, support, and generous help since the very first day I met them.

I want to thank Dr. Marvin L. Adams, who helped me in the Generic Particle Transport Code project.

I also want to thank Dr. Jennifer L. Welch, a great professor who gave me the knowledge of algorithms needed for this work.

I want to acknowledge the work of Tim Smith and Gabriel Tanase, both of whom spent a lot of time working on the implementation platform.

# TABLE OF CONTENTS

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page                 |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| CHAPTER |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |

| I       | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                    |

|         | A. Parallel Computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

|         | C. Contribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -<br>4<br>5          |

| II      | PRELIMINARIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6                    |

|         | A. Parallel Computation Models  B. Parallel Algorithmic Techniques  C. Parallel Algorithm Design Issues  C. Parallel Algorithm Design Issues                                                                                                                                                                                                                                                                                                                                                                                                                | 9<br>9               |

|         | D. Synchronization in Parallel Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12<br>12             |

| III     | COMMUNICATION PATTERNS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19                   |

|         | A. Communication Pattern I: Barrier Sequence B. Communication Pattern II  1. Recursive Doubling Pattern 2. STAPL FormulaDDG for Pattern II  C. Communication Pattern III  1. Balanced Binary-Tree Based Pattern 2. STAPL FormulaDDG for Pattern III  2. STAPL FormulaDDG for Pattern III  3. STAPL FormulaDDG for Pattern III  4. STAPL FormulaDDG for Pattern III  5. STAPL FormulaDDG for Pattern III  6. STAPL FormulaDDG for Pattern III  7. STAPL FormulaDDG for Pattern III  8. STAPL FormulaDDG for Pattern III  9. STAPL FormulaDDG for Pattern III | 21<br>23<br>29<br>29 |

| IV      | PREFIX SUMS ALGORITHMS IMPLEMENTATION A. 3-step Technique for $p < n$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |

|         | <ol> <li>Barrier Synchronization Implementation for RD Algorithm</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |

|         | RD Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |

| CHAPTER  | I                                                                                                                                                               | Page                             |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|          | <ol> <li>BT Algorithm and Theoretical Complexity</li> <li>Barrier Synchronization Implementation for BT</li> </ol>                                              | 54                               |

|          | Algorithm                                                                                                                                                       | 57<br>59<br>s 61                 |

| V        | PERFORMANCE OF IMPLEMENTATION                                                                                                                                   | 63                               |

|          | A. Optimization for Step 1 in the Implementation B. Experimental Results                                                                                        | 63<br>63                         |

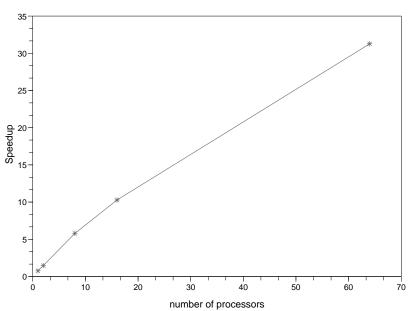

| VI       | APPLICATIONS                                                                                                                                                    | 66                               |

|          | A. Parallel Radix Sort  B. Tree Applications  1. Euler Tour Technique  2. Rooting a Tree  3. Three Other Tree Applications  4. Performance of Tree Applications | 67<br>72<br>73<br>76<br>81<br>82 |

| VII      | CONCLUSION AND FUTURE WORK                                                                                                                                      | 84                               |

|          | A. Conclusion                                                                                                                                                   | 84<br>85                         |

| REFERENC | CES                                                                                                                                                             | 86                               |

| VITA     |                                                                                                                                                                 | 89                               |

# LIST OF TABLES

| TABLE |                                                           | Page |

|-------|-----------------------------------------------------------|------|

| 1     | Theoretical Complexity of RD Algorithm with Sync. Options | . 62 |

| 2     | Theoretical Complexity of BT Algorithm with Sync. Options | . 62 |

# LIST OF FIGURES

| FIGURE |                                                                              | Page  |

|--------|------------------------------------------------------------------------------|-------|

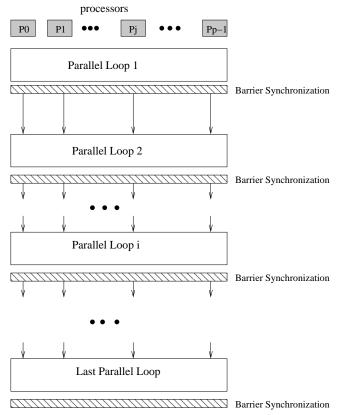

| 1      | Example communication structure using barrier synchronization                | 13    |

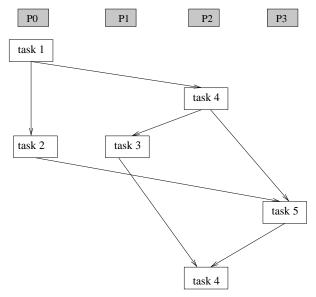

| 2      | Example communication structure using point-to-point synchronization         | on 14 |

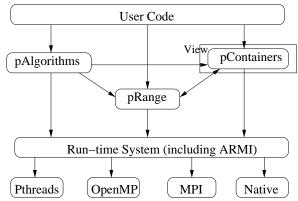

| 3      | STAPL components                                                             | 16    |

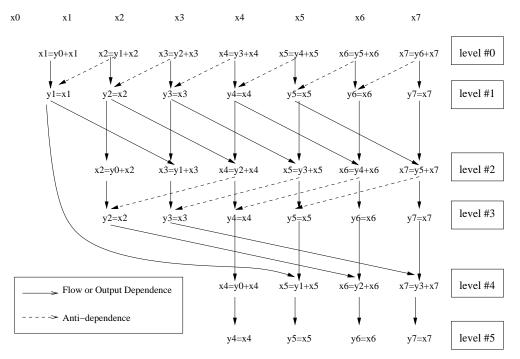

| 4      | Communication pattern II example                                             | . 22  |

| 5      | Communication pattern III in BT algorithm                                    | 30    |

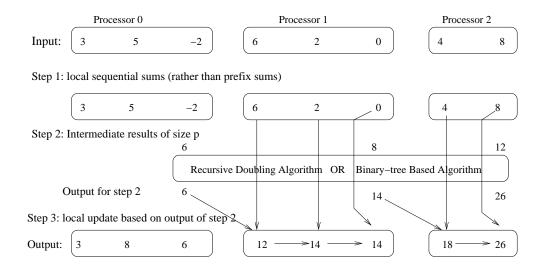

| 6      | Example of applying three-step technique                                     | 41    |

| 7      | Example of using the RD algorithm on 8 processors                            | 44    |

| 8      | Example using the BT algorithm on 8 processors                               | 56    |

| 9      | Processors' actions in the BT algorithm with barrier synchronization option  | 60    |

| 10     | Example of the generic implementation with optimization in step 1 (p=3, n=8) | 64    |

| 11     | Speedup of parallel prefix sums (input size: 512M integers)                  | 65    |

| 12     | Speedup of parallel radix sort (input size is 128M integers)                 | 70    |

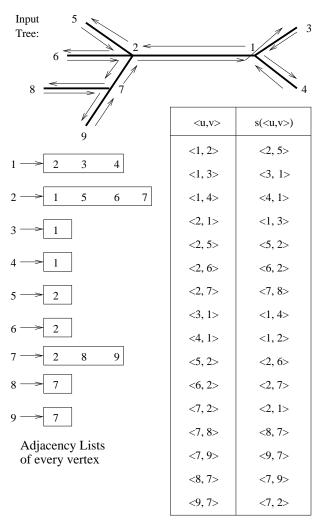

| 13     | Example of Euler circuit with successor function s [1]                       | 75    |

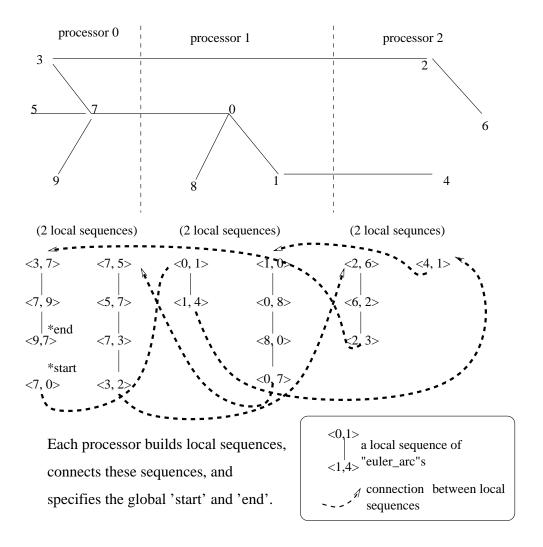

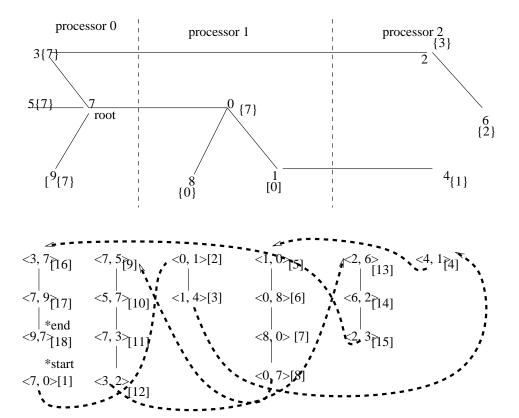

| 14     | Example of building an Euler tour in parallel                                | . 77  |

| 15     | Example of "rooting a tree"                                                  | 80    |

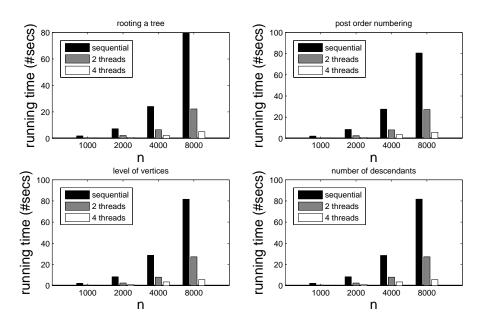

| 16     | Performance of Euler tour applications                                       | 83    |

#### CHAPTER I

#### INTRODUCTION

## A. Parallel Computation

As computers become ever faster, user demands for solving very large problems are growing at an even faster rate. Such demands include not only high-end scientific computing needs motived by numerical simulations of complex systems (e.g., weather, physics, and biological processes), but also emerging commercial applications that require computers to be able to process large amounts of data in sophisticated ways (e.g., video conferencing, computer-aided medical diagnosis, and virtual reality) [2].

At the same time, the speed of a uni-processor computer is limited by the physical size and speed of its transistors. To circumvent these limitations, computer hardware designers have been utilizing internal concurrency in chips, including pipelining, multiple function units, and multi-core processors.

Another important trend changing the face of computing is an enormous increase in the capabilities of the networks that connect computers, which enables applications to use physically distributed resources as if they were part of the same computer [2]. There is undeniable growing importance and interest in parallel computing.

However, most existing algorithms are designed specifically for single processor computers. In order to design and implement algorithms that can exploit multiple processors located inside a computer, and the additional processors available across

This thesis follows the style and format of *IEEE Transactions on Parallel and Distributed Computing*.

a network, the emphasis in algorithm designs has shifted from sequential algorithms to parallel algorithms, the algorithms in which multiple operations are performed simultaneously.

The basic idea behind parallel computing is to carry out multiple tasks simultaneously, thereby reducing execution time and handling larger scale problems. But the design and development of parallel algorithms are still far from well-understood. This is because there are some major issues in parallel algorithms that are not found in sequential algorithms. These include task decomposition, allocation, communication and synchronization, as well as performance issues such as scalability, speedup, and load balancing.

Fortunately, similar to sequential problems, many parallel problems can be solved based on a small set of essential parallel problems. Researchers have been working hard to design and develop the best parallel algorithms for these essential problems.

One of these essential problems is the parallel prefix sums problem. It has been shown that parallel prefix sums can be applied to a wide variety of parallel problems, as listed in Section B. This thesis deals with this problem by providing the generic implementation of two algorithms, handling the synchronization issues by building reusable communication patterns, and studying performance and applications.

#### B. Prefix Sums Problem

Parallel prefix sums might be the most heavily used routine in parallel algorithms [3]. They are one of the most important building blocks for parallel algorithms.

The definition of the prefix sums problem is [4]:

Given a binary associative operator  $\oplus$ , and an ordered set of n elements

$$[a_0, a_1, ..., a_{n-1}]$$

, return the ordered set  $[a_0, (a_0 \oplus a_1), ..., (a_0 \oplus a_1 \oplus a_{n-1})]$ .

For example, if the operator  $\oplus$  is addition, and the input set is [3, 5, -2, 6, 2, 0, 4, 8], then the prefix sums of this ordered set are [3, 8, 6, 12, 14, 14, 18, 26].

Even though the problem is called "prefix sums," the operator  $\oplus$  could be any binary associative operation that can be applied to two input elements. That is, prefix sums can be used for more than just addition. But for simplicity, the remainder of this thesis uses + to represent the operator, except in the pseudo-code where  $bin\_op$  is used.

Different applications of prefix sums problems are possible by using different operators and different types of input elements. The applications include, but are not limited to, the following [4]:

- Lexically compare strings of characters;

- Solve recurrences;

- Implement radix sort;

- Implement quick sort;

- Implement tree applications.

Given the simplicity and wide application, a generic implementation of a parallel algorithm that supports different input element types, different operators, and different physical distribution of input elements would be valuable for solving many other parallel problems.

Due to the importance of prefix sums problems in parallel computing, there has been considerable research devoted to building effective parallel prefix sums algorithms, including [5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15].

This thesis builds a generic implementation using two parallel prefix sums algorithms to build a generic implementation: a recursive doubling (RD) algorithm and a binary-tree based (BT) algorithm. The reason for selecting these two is that they utilize two important techniques widely used in parallel problems. Therefore, their implementation can be directly used to solve many other parallel problems.

#### C. Contribution

In order to make parallel programming efficient, portable, and reusable, a generic and efficient implementation of two important parallel algorithms for prefix sums in a parallel library is provided. These two algorithms, a prefix sums algorithm based on the recursive doubling technique (RD) and a balanced binary tree based prefix sums algorithm (BT), are implemented in C++ and analyzed using the Coarse Grained Multicomputer (CGM) model. This generic implementation supports a general linear sequence of any data structure as input, as long as the operation  $\oplus$  for prefix sums computation to be applied to the data structure is defined. There is no assumption about the distribution of input sequences across multiple processors.

Three pre-built reusable communication patterns are decomposed from these concrete parallel algorithms and they can be directly used by any parallel algorithm that follows the same communication pattern. These three pre-built communication patterns simplify the work of parallel algorithm implementation to a great extent. The usage of these communication patterns on the two prefix sums algorithms results in two different synchronization options used for each algorithm, thus producing four implementations for the two algorithms. All of them show reasonably good speedup in experimental results, while the point-to-point synchronization option has better performance than the barrier synchronization.

A few applications for parallel prefix sums are also implemented on top of the generic implementation, and they also perform well in experiments.

#### D. Thesis Structure

This chapter, Chapter I, introduces the prefix sums problem, motivates a generic implementation for parallel prefix sums algorithms, and summarizes this thesis' contributions.

Chapter II gives the preliminaries of parallel algorithm design, including some basic parallel computation models, parallel algorithmic techniques, and the major design phases and issues. For one of the main communication issue, synchronization, there are two typical techniques: barrier synchronization and point-to-point synchronization.

Chapter III introduces the three pre-built communication patterns.

Chapter IV presents the design and implementation of the two prefix sums algorithms using the three pre-built communication patterns. The implementations using the barrier synchronization use the first communication pattern with the global barrier operation supported by the library; the implementations using the point-to-point synchronization use communication patterns II and III to guarantee the minimal required synchronizations between tasks, represented by a directed graph.

Chapter V describes the performance study for the implementation of two algorithms with two different synchronization options.

Chapter VI provides a few other parallel problems' solutions through the application of parallel prefix sums. The performance results of these applications are also presented.

Chapter VII concludes this thesis and briefly discusses future work.

#### CHAPTER II

#### **PRELIMINARIES**

This chapter presents the basic ideas and issues in parallel algorithm design. The first two sections give a preliminary introduction to parallel computation models and important parallel algorithmic techniques. Section C briefly explains the major issues in parallel algorithm design. Section D introduces synchronization, the major issue in the design and implementation of parallel prefix sums this research deals with. The last section is a high level introduction of the implementation platform, a parallel / distributed standard template C++ library, STAPL.

#### A. Parallel Computation Models

A computation model is required to serve two major purposes. First, it is used to describe a computer. So, a computational model attempts to capture the essential features of a machine while ignoring the less important details of its implementation. Second, it is used as a tool for analyzing problems and expressing algorithms [16].

In the realm of sequential computation, the Random Access Machine (RAM) is a standard model that has succeeded in both of these purposes. It serves as an effective model for hardware designers, algorithm developers, and programmers alike.

However, when it comes to parallel computation, there is no such unifying standard model. This is due to the complex set of issues inherent in parallel computation.

Three important principles have emerged for successful parallel computation models: Work-Efficiency, Emulation, and Modeling Communication [17].

• Work-Efficiency: In sequential computation, an algorithm's work (or total number of operations) is equivalent to its execution time. On a parallel machine,

an algorithm taking t time on a p-processor machine performs work W=p\*t. An algorithm is work-efficient if it performs the same amount of work, within a constant factor, as the fastest known sequential algorithm.

- Emulation: A parallel computation model can be useful without mimicking any real or even realizable machine. Instead, it suffices that any algorithm that runs efficiently in the model can be translated into an algorithm that runs efficiently on real machines.

- Modeling Communication: To get the best performance out of a parallel machine, it is often helpful to explicitly model the communication capabilities of the machine, such as its latency.

One of the oldest parallel computation models is the PRAM model [18]. It assumes that the number of processors p is polynomial in the input size n, such that each processor only needs to work on partial input of a constant size. It is a simplistic model for parallel computation and is mainly of theoretical interest. Although it fails to capture the features of existing parallel computers by making the above unrealistic assumption, it does represent an upper bound for the performance of parallel algorithms. More importantly, any algorithm that runs efficiently in a p-processor PRAM model can be translated into an algorithm that runs efficiently on a p/L-processor machine with a latency L.

The BSP model [19] was proposed to serve as standard bridging model for hardware (machine architecture) and software (algorithm design and programming). As opposed to the PRAM model, parallel algorithms in the BSP model are organized in distinct computation and communication phases. Moreover, unlike the PRAM, the BSP model makes parallel computation coarse grained. In particular, it assumes that the number of processors and the input size are orders of magnitude apart. Due

to this assumption, the coarse grained model maps better on existing architectures where, in general, the number of processors is in the order of hundreds and the size of input data to be handled could be in the billions. This model uses four parameters: n, p, L and g. Parameter n is the input size; p is the number of processors; L is the minimal time between synchronous steps (measured in basic computation units); and g is the ratio of overall system computational capacity per unit time divided by the overall system communication capacity per unit time.

The introduction of the BSP model marks the beginning of increased research interest in coarse grained parallel computation. This model has been modified along different directions. For example, Culler et al. [20] suggest the LogP model as an extension in which asynchronous execution is modeled and a parameter is added to better account for communication overhead. In an effort to define a parallel computation model that retains the advantage of coarse grained models, while at the same time being simple to use (involving few parameters), Dehne et al. [21] suggest the CGM model.

The CGM model uses only two parameters: n and p. This model is a set of p processors, each with O(n/p) local memory, interconnected by a router that can deliver messages in a point-to-point fashion. A CGM algorithm consists of an alternating sequence of "computation rounds" and "communication rounds" separated by barrier synchronizations (barrier synchronizations are introduced in Section 1).

This thesis uses the CGM model. The input for the parallel prefix sums problem is a linear sequence of n elements, and each of the p processors gets O(n/p) input elements. How these elements are distributed to the processors is not assumed.

#### B. Parallel Algorithmic Techniques

There are some fundamental algorithmic techniques that are widely used in parallel algorithms. Some of these techniques are used by sequential algorithms as well, but they become much more important in parallel algorithms; others are unique to parallelism. Blelloch gives a brief description of three of the techniques in [17]:

- Divide-and-Conquer: By dividing a problem into two or more subproblems, the subproblems can be solved in parallel. Typically the subproblems are solved recursively and thus the next divide yields even more subproblems to be solved in parallel.

- Randomization: This is an algorithmic technique unique to parallel algorithms.

It allows processors to make local decisions which, with high probability, add up to good global decisions.

- Parallel Pointer Manipulations: Many of the traditional sequential techniques for manipulating lists, trees, and graphs do not easily translate into parallel techniques. But such techniques can be replaced by efficient parallel techniques such as recursive doubling, the Euler-tour technique, ear decomposition, and graph contraction.

The algorithms implemented in this work use recursive doubling and Eulertour techniques. Details of these techniques are introduced when the design and implementation are presented.

#### C. Parallel Algorithm Design Issues

Following the notation in [22], "task" represents a sequential program fragment that runs on a single processor together with its local storage. The basic point of parallel computing is to let two or more tasks execute concurrently. And "communication channel" means the logical link between two tasks over which they can exchange information (either through shared memory or explicit message).

The parallel algorithm design process is divided into four steps [22]:

- Partitioning: Decompose a problem into fine-grained tasks, maximizing the number of tasks that can be executed concurrently.

- Communicating: Determine the communication pattern among fine-grained tasks, yielding a "task graph" with nodes and communication channels as edges.

- Agglomerating: Combine groups of fine-grained tasks to form fewer, but larger, coarse-grained tasks thereby reducing communication requirements. This makes the algorithm execute efficiently on the physical target parallel computer.

- Mapping: Assign coarse-grained tasks to processors, subject to tradeoff between communication costs and concurrency.

The work presented in this thesis focuses mainly on the second step. Although a bad partitioning / agglomerating / mapping strategy may produce an imbalanced load and decrease performance, the correctness of the algorithm is not affected. However, if communication between tasks is not correctly designed and implemented, the whole program will fail.

In terms of communication, different problems have different inherent patterns:

• Local versus Global Communication: In local communication, each task communicates with a small set of other tasks (or "neighbors"). In global communication, each task is required to communicate with many tasks (if not exactly all others).

- Synchronous versus Asynchronous: In synchronous communication, producers and consumers of communicated data execute in a pair-wise fashion to perform the data transfer operations; while in asynchronous communication, producers and consumers are not required to cooperate in this way.

- Structured versus Unstructured: In structured communication, a task and its neighbors form a regular structure, e.g., a tree or a grid. Unstructured communication may form an arbitrary graph.

- Static versus Dynamic: In static communication, each task's communication partners do not change over time. Dynamic communication may decide communication partners at runtime and change them frequently.

In this thesis, all the algorithms have structured static communication patterns. This means all the communication channels are independent from the runtime context and can be represented in a pre-determined regular structure. In the following sections it is shown that such regular structures in the algorithms can be a sequence of global communication operations or a mathematically formulated graph. Additionally, asynchronous communication is used, i.e., producer tasks do not need to be aware when consumer tasks require data; hence, consumer tasks must explicitly request data from producer tasks.

The next section discusses the synchronization issue in parallel algorithm design, focusing on two different synchronization options using global and local communications, barrier synchronization and point-to-point synchronization.

#### D. Synchronization in Parallel Algorithms

Synchronization is the coordination of simultaneous tasks to ensure correctness and avoid unexpected race conditions. There are two types of synchronization, barrier

and point-to-point.

#### 1. Barrier Synchronization

A barrier is a point in parallel program code where a processor must wait until all the other processors participating the program have also reached the same point. After all of the processors reach the barrier, the processors continue issuing program code.

A typical place to use barriers is between parallel loop iterations which perform operations on the same set of data. These barriers guarantee that the processors associated with an iteration finish the operations in the iteration before any of them continue with other program instructions. This is necessary if one processor in a later iteration needs the results achieved on a process in a previous iteration.

Barrier synchronization is also useful for organizing the execution of a parallel program into a sequence of loosely coordinated phases. This matches the idea of the BSP and CGM computation models and there have been many parallel algorithms that utilize barrier synchronization for different domains of problems.

Basically, a parallel algorithm can be represented by a few parallel steps (e.g., loop iterations or loosely coordinated phases) with barrier synchronization as a regular sequence of alternating parallel steps and barrier points, as shown in Figure 1.

## 2. Point-to-Point Synchronization

Point-to-point synchronization happens only between two tasks, corresponding to only one communication channel in one direction. It typically means that only one single task needs data from another task in order to proceed. The whole communication pattern can be represented as a graph, with nodes as tasks and directed edges

Example communication structure using the barrier synchronization technique of alternating parallel steps and barrier points.

Figure 1: Example communication structure using barrier synchronization

as the required point-to-point synchronizations between the tasks. Figure 2 shows an example of such a structure.

Point-to-point synchronization gives a fine-grained description that matches the minimal synchronization requirements. However, it is difficult to program this way because it requires a very careful design to guarantee all the minimal synchronization requirements are satisfied. The advantage is intuitively obvious: all the processors do not need to be synchronized just because a few tasks may need data from a single task on one processor. In such cases, barrier synchronization is too conservative, while

Example communication structures using point-to-point synchronization techniques;

Directed graph of communication are composed by tasks (nodes) and their point-to-point synchronizations (directed edges).

Figure 2: Example communication structure using point-to-point synchronization

the point-to-point technique can reduce the cost for communication operations.

In order to take advantage of the point-to-point synchronization technique, and to simplify parallel programming, a regular communication structure (the graph representing tasks and synchronizations) is decomposed from the parallel algorithms themselves. This regular structure defines a communication pattern, which can be pre-built separately and used by any parallel algorithm that follows the same communication pattern. For the two parallel prefix sums algorithms in this thesis, three different communication patterns using barrier synchronization and point-to-point synchronization are built. These communication patterns are not limited to the parallel prefix sums algorithms; instead, any parallel algorithms that follow similar communication patterns can directly use them to simplify design and implementa-

tion.

Before the details of these communication patterns are presented in Chapter III, a brief introduction of the implementation platform, a parallel library STAPL, is given.

### E. Parallel Library - STAPL

The generic implementation of parallel prefix sums is built in STAPL (Standard Template Adaptive Parallel Library), which is a framework for parallel C++ code. Its core is a library of ISO Standard C++ components with interfaces similar to the sequential ISO C++ standard library (STL).

STAPL includes a run-time system, design rules for extending the provided library code, and optimization tools. Its goal is to allow a user to work at a high level of abstraction and hide many details specific to parallel programming. This is to allow a high degree of portability and performance adaptability across different computer systems. The components and their relationships are described in Figure 3.

Distributed data are stored in "pContainers". STAPL hides the details of physical distribution of data across processors from the user and provides flexible logical "Views" to access the distributed data in pContainers. When implementing parallel algorithms, programmers can always access the data in the way the algorithms require by creating logical Views accordingly. One View can hide the physical distribution of data in a pContainer.

STAPL has a collection of "pAlgorithms," which includes the parallel counterparts for most generic sequential algorithms in STL and some numeric and graph parallel algorithms. Parallel prefix sums is one of them, and is used by many other

#### **STAPL** components:

$(1)\ pContainers:\ parallel\ /\ distributed\ containers\ of\ data;$

View: the view of pContainer (how to visit data in pContainer, independent from physical distribution);

- (2) pRange: access to data through View; work function to apply to data; and Task Dependence Graph (DDG);

- (3) pAlgorithms: parallel algorithms;

- (4) Run-time system: it hides details of communications, scheduling, and so on.

Figure 3: STAPL components

## pAlgorithms.

A "pRange" connects pAlgorithms and pContainers together and enables pAlgorithms to be generic. Its core function call  $p\_for\_all(pRange\&pr)$  is the main entry point to execute parallel programs. A pRange provides access to chunks of data (or "subviews") in one or more Views, so each task will operate on one chunk (subview) of the View(s). A pRange also has a work-function object that describes the operation for each task, and a Data Dependence Graph ("DDG") object which represents the tasks and their synchronizations (and could be an instance of a pre-built communication pattern). A pRange corresponds to a whole View of pContainer(s), and is a collection of subranges where each subrange has access to one chunk of the View. The function call  $p\_for\_all(pRange \&pr)$  applies the work function of the

input pRange on each "subrange" of the pRange. Each such application is called as a "task". The orderings of all tasks on the p processors follow the synchronizations in the DDG.

In the parallel prefix sums algorithms implementation this collection (pRange) corresponds to the View of a linear sequence of subranges. That is, subranges are organized as a sequence, with each subrange having an offset from the global beginning of the whole pRange and each subrange has a preceding neighbor subrange and a succeeding neighbor subrange (except the first and last subranges).

The run-time system, including the Adaptive Remote Method Invocation (ARMI) communication library, hides all the details of communication, scheduling, and so on.

To support barrier synchronization, ARMI provides an  $rmi\_fence()$  function call that guarantees every processor stops there until all processors have reached the same place. More details and usage of  $rmi\_fence()$  will be introduced in Chapter III.

To support point-to-point synchronization, the pRange follows the directed edges in its DDG to pick up tasks that have no predecessors or those whose all predecessors have been finished. A task X is a predecessor of task Y if task X must be finished before task Y can start, due to the synchronization requirement of X to Y, and task Y is a successor of task X. This ordering is represented by a directed edge from task X to task Y in the DDG.

The DDG can be represented by a parallel graph (pGraph), which is one type of the pContainers implemented in STAPL and physically contains vertices and edges. It can also be any class that can compute the predecessor / successor relationships between tasks given unique IDs. Since the tasks and synchronizations in the two parallel prefix sums algorithms (RD and BT) can both be determined statically (by mathematically expressing the preceding / succeeding relationships) based on the input size n, this determination function is provided as a class using formulas to represent the DDG (or "FormulaDDG" in STAPL). The FormulaDDG can be prebuilt out of concrete parallel algorithms and reused to represent inherent common communication patterns. The construction of the DDG is explained briefly in the following two sections when presenting the pre-built communication patterns.

#### CHAPTER III

#### COMMUNICATION PATTERNS

As one of the main issues unique to parallel algorithms, communication needs to be carefully designed in order to be correct and efficient. When tasks should communicate with other tasks, which tasks should be the destination, what the communication data size would be, and all such characteristics compose a specific pattern for the algorithm.

There have been observations [23] showing that some parallel algorithms share the same or similar communication patterns. Optimizing the design and implementation of such communication patterns gives insight into improving the performance of parallel algorithms. Pre-built tuned-up communication patterns can dramatically simplify the work for parallel programmers and guarantee good performance in the final parallel programs as well. With that motivation, this thesis attempts to decouple the usually embedded communication patterns from the whole parallel algorithms and build a library of reusable communication patterns; this library can then be used directly when programmers try to build parallel algorithms that follow similar communication patterns.

In this section, it is assumed that the input size n is equal to the number of processors p. This assumption only holds for this section and more general cases will be discussed later.

#### A. Communication Pattern I: Barrier Sequence

The simplest and most intuitive communication pattern supported is a sequence of alternating parallel steps and barrier synchronization operations, as introduced in Section 1. In STAPL, this is supported by the function calls  $p\_for\_all(pRange)$  and

rmi\_fence(), exposed by ARMI.

*Rmi\_fence* is a collective operation as the superset of a barrier. It does not release until all processors arrive (as the barrier requires) and complete all outstanding communication requests [24].

If a parallel algorithm follows this pattern, i.e., the algorithm can be divided into a few parallel steps with barrier synchronizations between each two adjacent steps, then the only thing specific to the algorithm is what operations are applied to each local set of data (or subrange in STAPL) in each parallel step. If these operations are put to work in function objects, the typical framework for this algorithm would be:

```

// parallel step 2

pr.set_task(wf2);

p_for_all(pr);

rmi_fence();

...

}

```

As introduced in Section E,  $p\_for\_all()$  applies the work function object (set by PRange's  $set\_task$  function) to each local set of input data (subrange), which composes one parallel step. Then  $rmi\_fence$  applies barrier synchronization.

#### B. Communication Pattern II

#### 1. Recursive Doubling Pattern

The second communication pattern represents a commonly used parallel algorithmic technique, recursive doubling. This technique is used in parallel problems that first appear unavoidably sequential. "Recursive doubling" is also known as "pointer jumping" or "shortcutting". It means replacing a pointer with the pointer it points to, in a linked structure. This technique is used for various algorithms on lists and trees.

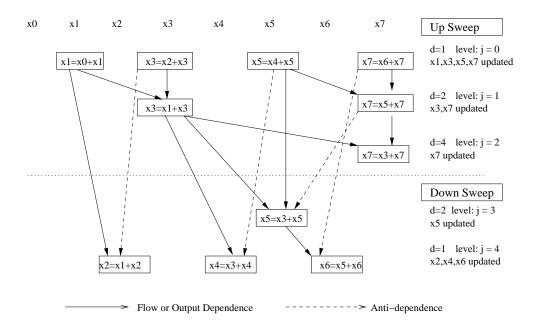

An example of this communication pattern for a prefix sums problem with 8 input elements  $x_0$ - $x_7$  is shown in Figure 4. Each processor keeps one input element x[i] and its copy y[i]; (y[i] is used to avoid unnecessary waiting for computation on x[i] during communicating, as explained by a later example). In this figure, the lines with arrows represent the synchronizations. For example, task  $x_4=y_2+x_4$  needs to

read the value of y2, so it has to wait for task y2=x2; it also needs to write to x4, so it has to wait until task y4=x4 correctly reads the old value of x4. Solid lines represent the synchronizations required by flow dependencies and output dependencies, while dotted lines represent the synchronizations required by anti-dependencies.

Each processor (P) owns one input element (x[i] and copy y[i]) in local memory. These data are communicated in order for processors to execute computations.

Figure 4: Communication pattern II example

Note that this pattern is not specific for the prefix sums problem. Any parallel problem using the recursive doubling technique has a similar synchronization structure.

Basically, this pattern is composed of a few levels of task pairs and synchronizations between tasks, as shown in Figure 4. The distances between source (or producer) tasks and destination (or consumer) tasks for synchronizations, called

"synchronization distances", are different at different levels.

For example, in Figure 4, there are six levels of computations. Tasks in the j-th level, where j is even, apply addition operations x[i] = y[i-d]+x[i], where d, the synchronization distance from the source task at the previous level, equals to  $2^{j/2}$ . Tasks in the j-th level, where j is odd, apply saving operations y[i] = x[i], and these tasks have synchronization distances from the source task at the previous level as  $2^{(j-1)/2}$ . From a different perspective, the same d for input synchronization distance and output synchronization distance could be used for the tasks at even levels.

The value of synchronization distance d is decided by the underlying idea of the recursive doubling strategy: "replacing a pointer with the pointer it points to," which leads to  $log_2(n)$  times of replacing. At each instance of replacing, the distance doubles; thus, the synchronization distance is doubled.

The reason to keep a copy y[i] for x[i] after each update step is to parallelize the reading and writing to the *i*-th element. For example, in the fourth step, x[11] needs to read y[7] (because  $d_2=2^{4/2}=4$ ), but x[7] needs to be updated to x[3]+x[7]. Without a copy y[7] for x[7], the update to x[7] has to wait until x[11] has read the correct value of x[7].

#### 2. STAPL FormulaDDG for Pattern II

This pattern in STAPL is provided as a pre-built FormulaDDG  $rd\_dependence\_oracle$ . A FormulaDDG is constructed through three functions:  $construct\_tasks$  to determine how many tasks need to be created for which subranges; enables and  $depends\_on$  decide the successor tasks and predecessor tasks for each task, i.e., the synchronizations. The following are the three functions for Communication Pattern II:

Function "construct\_tasks" for

```

rd_dependence_oracle:

(This function creates the vertices of DDG.)

Input: A subrange of the owner pRange for a

DDG instance of rd_dependence_oracle.

Output: A vector of pointers to the tasks (with

unique Ids) created for this subrange.

template < typename PRange >

vector<task_type*>

construct_tasks (PRange& subrange)

{

int i = the subrange's offset;

// since input pRange is a sequence of

// subranges, each subrange has an offset

// from the beginning.

int tasknum;

// #tasks for this subrange

if (i == 0) {

// subrange 0 is never updated

tasknum = 0;

} else {

tasknum = 2 * log2(i+1);

// processor i has 2*log(i+1) tasks

vector<task_type*> new_tasks;

```

```

new_tasks.reserve(tasknum);

// the vector to store the tasks to

// be created

if (tasknum == 0)

return new_tasks;

for ( int j = 0; j < tasknum; <math>j = j+1) {

// for each level

int taskid = j * p + i;

// a unique id for this task, meaning

// that this task is for subrange i,

// at j-th level in the whole DDG

if (j is even) {

// the task should do:

// x[i] = bin_op(y[i-d], x[i])

d = 2 (j/2);

} else {

// the task should do:

// y[i] = x[i]; no need for d

d = 0;

}

new_tasks.push_back(

new task_type(taskid, subrange, d, bin_op));

// create a new task with this "taskid"

```

The class  $task\_type$  in the pseudo code for  $construct\_tasks$  is a class that has a unique Id (a reference to the subrange it works on), a data member to save data specific to the task (like the synchronization distance d for this task), and a work function to specify the operation to be applied.

The following two functions, depends\_on and enables, take a task Id as an input parameter and return a vector of task Ids as this task's predecessors and successors. The computation is based on the dependencies required by the RD algorithm. The "upper", "lower", "left", and "right" neighbors in the pseudo-code refer to the geometric locations in Figure 4. The locations for these neighbors are always computable based on the input task Id and the type of dependences to/from the task. Mathematic details are not covered in this thesis.

```

Function "depends_on" to find predecessors for input task in rd_dependence_oracle:

(This function creates input edges to a vertex in DDG.)

Input: The task Id for a task in a DDG

```

instance of rd\_dependence\_oracle.

```

Output: A vector of task Ids for the pre-

decessors of the task.

void

depends_on(int taskid,

vector<task_id_type>& v)

{

int i = taskid % n;

// the index for the subrange

// for this input task

int level = taskid / n;

// the level of the task in the DDG

v.push_back(the upper neighbor task

for same subrange);

// flow dependence to this task

if (level is even) {

v.push_back(the left upper neighbor

that has non-vertical flow

dependence to the task);

} else {

v.push_back(the right upper neighbor

that has anti-dependence

to the task);

}

}

```

```

Function "enables" to find successors

for input task in rd_dependence_oracle:

(This function creates output edges from

a vertex in DDG.)

Input: The task Id for a task in a DDG

instance of rd_dependence_oracle.

Output: A vector of task Ids for the

successors of the task.

void

enables(int taskid,

vector<task_id_type>& v)

{

int i = taskid % n;

//the index for the subrange

int level = taskid / n;

//the level of the task in DDG

v.push_back(the vertically lower neighbor

that has flow dependence from

this task);

if (level is even) {

v.push_back(the left neighbor that has

anti-dependence from this task);

} else {

v.push_back(right lower neighbors that have

```

#### flow dependences from this task);

}

Given the pre-built FormulaDDG rd\_dependence\_oracle, any parallel problem using the recursive doubling technique only needs to build its own work function (i.e., the computation operation) for the tasks. It directly uses this DDG as its pRange's DDG and thus the correct synchronizations between tasks are guaranteed.

#### C. Communication Pattern III

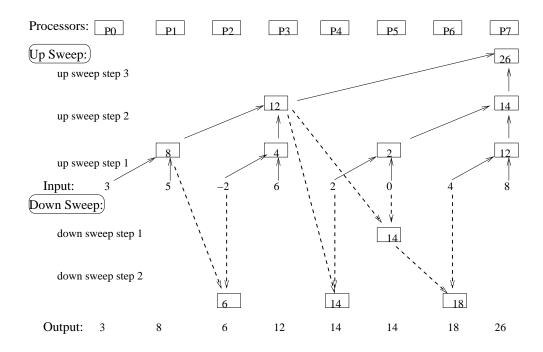

#### 1. Balanced Binary-Tree Based Pattern

This pattern first follows a balanced binary tree to compute partial results, and then follows another tree structure to pass these partial results back in order to get the final results. An example is shown in Figure 5. Similar to Figure 4, the solid lines represent the synchronizations required by the flow dependencies and output dependencies, while the dotted lines represent the synchronizations required by anti-dependencies.

This pattern includes two sweeps, the up sweep and the down sweep. As labeled in Figure 4, there are in total  $2*log_2(p)-1$  levels of tasks, and the value of synchronization distance d at level j is:  $2^j$  if the level is in the up sweep; or  $2^{2*log_2(p)-2-j}$  if the level is in the down sweep.

This is a general communication pattern which has both the up sweep and the down sweep. A specific parallel algorithm could specify whether and which processors have tasks in the down sweep. If all the processors do not have tasks in the down sweep, then the communication pattern is specialized as a simple binary tree structure.

Figure 5: Communication pattern III in BT algorithm

### 2. STAPL FormulaDDG for Pattern III

A helper function  $compute\_distance$  is used to compute the value for synchronization distance d for given level j:

Helper function "compute\_distance":

task\_id\_type

```

compute_distance(int j)

{

if ( j < log2(p) ) {

// this is an up sweep task

return 2^j;

} else {

// this is a down sweep task

return 2^(2*log2(p) - 2 - j);

}

}</pre>

```

Similar to Communication Pattern II, this pattern is represented by a pre-built FormulaDDG  $bt\_dependence\_oracle$ . The condition to decide whether this subrange (with offset i) has task(s) in the down sweep,  $i >= 3*(2^{nt})$  -1, comes from the BT algorithm since this communication pattern is currently used only for the implementation of parallel prefix sums. However, this can be modified to match the needs of other similar parallel algorithms.

```

Function "construct_tasks" for

bt_dependence_oracle:

(This function creates the vertices of DDG.)

Input: A subrange of the owner pRange for a DDG

instance of bt_dependence_oracle.

Output: A vector of pointers to the tasks (with

unique Ids) created for this subrange.

```

```

vector<task_type*>

construct_tasks (PRange& subrange)

{

bool has_downsweep_task = false;

int i = subrange's offset;

int nt = \#times that (i+1) can be

divided exactly by 2;

// #tasks for this subrange in the up sweep

// Refer to mathematic issue (a) below.

int tasknum = nt;

if (i >= 3 * (2^nt) - 1) {

// condition for the subrange to own

// down sweep task, coming from BT algorithm;

has_downsweep_task = true;

}

if (has_downsweep_task)

// if the subrange does have down sweep

// task, then it only has one such task.

// Refer to mathematic issue (b) below.

tasknum++;

vector<task_type*> new_tasks;

new_tasks.reserve(tasknum);

// the vector to store the tasks to be

// created

```

```

for (int j = 0; j < nt; ++j) {

// for each level in the up sweep

int taskid = j * p + i;

// a unique id for this task, meaning

// this task is for subrange i, at

// level j in the whole DDG

int d = 2^j;

// the distance for this level in up sweep

new_tasks.push_back(

new task_type(taskid, subrange, d, bin_op));

// create a new task with this "taskid"

// that will work on this "subrange",

// whose task-specific data is "d",

// and operation is "bin_op"

}

if (has_downsweep_task) {

//create the down sweep task

int j = 2 * log2(p) - 2 - nt;

// the down sweep task is at level

// 2*log2(p)-2-nt.

// Refer to mathematic issue (c) below.

int taskid = j * p + i;

int d = 2^(2*log2(p) - 2 - j);

new_tasks.push_back(

```

```

new task_type(taskid, subrange, d, bin_op));

// create a new task with this "taskid"

// that will work on this "subrange",

// whose task-specific data is "d",

// and operation is "bin_op"

}

return new_tasks;

}

```

There are three mathematical issues in *construct\_tasks* that require detailed explanations.

- (a) For a subrange with offset i, its number of tasks in the up sweep is the number of times that (i+1) can be divided exactly by 2. In other words, it is the number of occurrences of 2 as (i+1)'s factor.

- (b) A subrange has either 0 or 1 tasks in the down sweep of the BT algorithm.

- (c) If a subrange does have a down sweep task, then the task's level can be computed based on the offset *i*.

The following are the detailed explanations for these claims.

(1) The number of tasks in the up sweep can be observed based on the balanced binary tree structure of the up sweep. At any level in the up sweep, only when  $(i+1)/d_j$  is even can the subrange (with offset i) have a task at the level.

So, for a subrange to have tasks from level 0 to level j but not at level j+1, it must have:  $i+1=(2*\alpha 1)*d_j=\alpha 1*2^{j+1}$ , but  $i+1\neq (2*\alpha 2)*d_{j+1}=\alpha 2*2^{j+2}$ , where  $\alpha 1$  and  $\alpha 2$  are both natural numbers. In other words, (i+1) must be multiple

of  $\mathcal{Z}^{j+1}$ , but not a multiple of  $\mathcal{Z}^{j+2}$ . This means the subrange's number of tasks is equal to the number of times that i+1 can be divided exactly by 2.

(2) Parts of the subranges have their results computed in the up sweep, so they do not need down sweep tasks at all. If a subrange has a down sweep task, it cannot have more than one such task (proved below). In (2) and (3), the symbol m is used to represent the value of  $2 * log_2(p) - 2$ , for clearer expression.

Based on the BT algorithm (introduced in Chapter IV), the condition for the subrange with offset i to own a down sweep task at down sweep level j1 is:  $i+1 = 3*d_{j1}$ , or  $5*d_{j1}$ , or  $7*d_{j1}$ , i.e.,  $i+1 = (3+2*\beta 1)*d_{j1} = (3+2*\beta 1)*2^{m-j1}$ , where  $\beta 1$  is a constant non-negative integer.

Suppose there exists another task at any other down sweep level j2, then  $i+1 = (3+2*\beta 2)*d_{j2} = (3+2*\beta 2)*2^{m-j2}$ , where  $\beta 2$  is also a constant non-negative integer.

Since  $(3+2*\beta 1)$  and  $(3+2*\beta 2)$  are both odd, the times that (i+1) can be divided by 2 cannot be both m-j1 and m-j2 since  $j1\neq j2$ . Therefore, this subrange can have only one down sweep task.

(3) The level for the down sweep task of a subrange with offset i, if it exists, is equal to the number of its up sweep tasks (nt in the pseudo-code). Because in (1) it is known that the last level (level j) of an up sweep task for subrange with offset i satisfies:  $i+1 = \alpha * 2^{j+1}$ , where  $\alpha$  is an odd integer; and based on (2) it is known that this subrange's down sweep task must be at level j1 which satisfies:  $i+1 = (3+2*\beta)*2^{m-j1}$ . So  $\alpha * 2^{j+1} = (3+2*\beta)*2^{m-j1}$ . Since both  $\alpha$  and  $(3+2*\beta)$  are odd, we conclude that j+1 = m-j1, that is, j1 = m - (j+1) = m - the number of the subrange's up sweep tasks.

The depends\_on and enables functions for bt\_dependence\_oracle are briefly described by the following pseudo-code. The left, right, upper, and lower neighbors refer to the geometric locations in Figure 8.

In these two functions, to decide whether a task is an up sweep task or a down sweep task, simply compare the task's level with the number of up sweep tasks for the subrange i (as explained in  $construct\_tasks$  function).

```

Function "depends_on" to find predecessors

for input task in bt_dependence_oracle:

(This function creates input edges to

a vertex in DDG.)

Input: A taskid for a task in a DDG instance

of bt_dependence_oracle.

Output: A vector of taskids for the predecessors

of the task.

void

depends_on(int taskid,

vector<task_id_type>& v)

{

int i = taskid % n;

//the index for the subrange

int j = taskid / n;

//the level of the task in DDG

v.push_back(the vertically upper neighbor

that has flow dependence to

this task);

if (this task is an up sweep task) {

```

```

v.push_back(the left upper neighbor

that has flow dependence to

this task);

} else {

//this task is a down sweep task

v.push_back(the left upper neighbor

that has flow dependence to

this task);

v.push_back(the right first-pass

neighbor that has anti-

dependence to this task);

}

}

Function "enables" to find successors

for input task in bt_dependence_oracle:

(This function creates output edges

from a vertex in DDG.)

Input: A taskid for a task in a DDG instance

of bt_dependence_oracle;

Output: A vector of taskids for the successors

of the task.

void

enables (int taskid,

```

```

vector<task_id_type>& v)

{

int i = taskid % n;

//the index for the subrange

int j = taskid / n;

//the level of the task in DDG

if (this task is an up sweep task) {

v.push_back(the vertically lower neighbor

that has flow dependence from

this task);

v.push_back(the right lower neighbor that

has flow dependence from

this task);

if (this task is the lowest up sweep task

for the subrange)

{

v.push_back(some right neighbors' down

sweep tasks that have flow

dependences from this task);

}

v.push_back(the left neighbor's down sweep

task that has anti-dependence

from this task);

} else {

//this task is a down sweep task

v.push_back(some right neighbors' down sweep

```

```

tasks that have flow dependences

from this task);

}

```

Given the above pre-built FormulaDDG, the BT prefix sums algorithm only needs to specify its work function for the tasks and it uses this FormulaDDG as its own DDG, so all the synchronizations between tasks are guaranteed.

Other parallel algorithms using a similar communication pattern can use this FormulaDDG with only slight modifications.

#### CHAPTER IV

#### PREFIX SUMS ALGORITHMS IMPLEMENTATION

### A. 3-step Technique for p < n

When the pre-built communication patterns were introduced in the previous chapter, it was assumed that each processor owns and works on only one input element. This means the number of processors p is equal to the number of input elements n, which is an over-simplified assumption.

However, there is a standard 3-step technique for solving the more general situation where p < n:

- Step 1: Each processor applies the fastest sequential algorithm on its own local chunk of data, of size O(n/p), and gets some intermediate results.

- Step 2: Processors communicate with each other and do global computation on these p intermediate results using PRAM parallel algorithms.

- Step 3: Each processor does left-over local computations to get the final results based on the results of the previous global computations.

The underlying logic of this three-step technique is that after the first step, there are only p intermediate results, one for each processor; so a parallel problem using these intermediate results as input has input size equal to p. Then the algorithms introduced in the following sections of this chapter can be applied to the input set of size p and use the pre-built communication patterns to guarantee correct synchronizations.

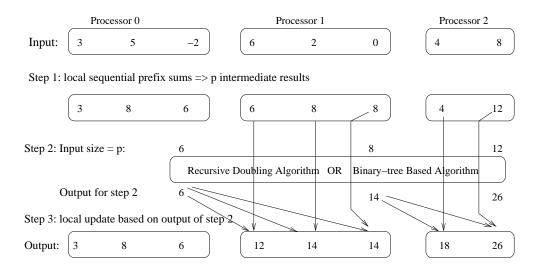

In the STAPL generic implementation of parallel prefix sums, the three-step technique is used as follows:

Step 1 applies sequential prefix sums on each processor;

Step 2 applies RD or BT algorithm on p intermediate results;

Step 3 finalizes local computation based on the output of step 2.

Figure 6: Example of applying three-step technique

- Step 1: Each processor applies a sequential prefix sums algorithm on its own O(n/p) input elements, and gets its own local total sum as the processor's intermediate result.

- Step 2: The RD or BT algorithms are applied to compute the prefix sums of the p intermediate results, along with corresponding communication pattern to guarantee correct synchronizations.

- Step 3: Each processor uses the globally computed prefix sums of intermediate results to update its own O(n/p) elements.

Figure 6 follows the three steps for computing prefix sums of an input set of 8 integers, [3, 5, -2, 6, 2, 0, 4, 8], on 3 processors, rather than the 8 processors needed in the PRAM model.

The input size is n for both Step 1 and Step 3. Each processor simply scans O(n/p) elements one by one. So the complexity in these two steps is Time =  $\Theta(n/p)$  and Work =  $\Theta(n)$ , assuming the input data are distributed evenly across the p processors.

The input size for Step 2 is p. Different algorithms (RD or BT), together with different communication patterns used for implementation, have different effects on the complexity of this step.

## B. RD Algorithm

# 1. RD Algorithm and Theoretical Complexity

The recursive doubling technique was first used by Kruskal, Rudolph, and Snir [25] to solve parallel prefix sums problem. The input sequence x can be regarded as a linked list of elements with links representing their preceding / succeeding relationships.

This algorithm can be described by the following pseudo-code. d is used to represent the distance for the update operation x[i] = y[i-d]+x[i].  $Bin\_op$  is the binary associative operator, which could also be as simple as addition, but could be very complicated.  $Parallel\_for$  means every processor executes this for-loop in parallel, with each working on one iteration.

Recursive doubling (RD) Algorithm:

Input: A set of elements "x" a copy "y";

A binary associative operator "bin\_op".

Output: Prefix sums of original input elements stored in "x".

```

for (d = 1; d < n; d = d * 2)

{

parallel_for (i=d; i<n; i=i+1) {</pre>

// parallel_for: each processor

// works on one "i" of the for-loop

// at the same time, i.e., i-th

// processor does:

// x[i] = bin_op(y[i - d], x[i])

// bin_op: the binary associative op

}

parallel_for (i=0; i<n; i=i+1) {</pre>

// parallel_for: each processor works

// on one "i" of the for-loop at the

// same time, i.e., i-th processor does:

// y[i] = x[i];

}

}

end

```

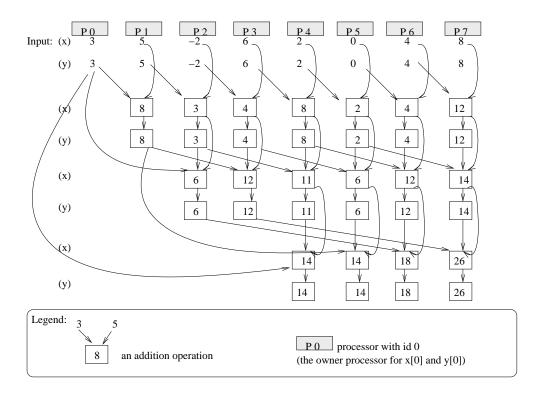

Figure 7 exemplifies how to use the RD algorithm to compute the prefix sums of the input set [3, 5, -2, 6, 2, 0, 4, 8] on 8 processors in parallel. The binary associative operator is simple addition in this example.

The distance d for each step changes from 1 to 2, then to 4, to 8, and so on until p/2. So it takes  $\Theta(log_2(p))$  iterations to finish the work. In each iteration, processor i updates x[i] or writes y[i] once; both are constant time operations. So, the total

Figure 7: Example of using the RD algorithm on 8 processors

complexity for the RD algorithm in Step 2 is Time =  $\Theta(log_2(p))$  and Work =  $\Theta(p^* log_2(p))$ .

### 2. Barrier Synchronization Implementation for RD Algorithm

As explained in Section A, in order to implement the RD algorithm with barrier synchronization, global barriers are put at the beginning and end of each parallel iteration using Communication Pattern I. The only thing that needs to be specified is the operation for each task, i.e., the work function object of the pRange. After that, the synchronizations between tasks are correctly guaranteed.

The RD algorithm's framework looks like the following pseudo-code.

### Framework of RD algorithm with

```

Barrier Synchronization option:

(Using Communication Pattern I)

Assumption: p = n (for step 2 only)

Input set "x" and its copy "y" are stored

in 2 pContainers.

Input: A pRange "pr" which has access to two views,

one for "x" and the other for "y";

A binary functor "bin_op" for prefix sums.

Output: Prefix sums of elements in "x" stored in

the viewO of "pr", which is the View for

input pContainer "x".

template <typename PRange, typename BinaryFunction>

p_prefixsums_RD_Barrier (PRange& pr,

BinaryFunction bin_op)

{

for (d = 1; d < n; d = d*2)

{

plus_workfunction<PRange,</pre>

BinaryFunction> plus_wf(d);

// work function: x[i]=bin_op(y[i-d],x[i]);

// the "distance" d for this level is

// passed as an argument to this work

// function because all the tasks at this

// level have same "d"s.

```

```

pr.set_task(plus_wf);

p_for_all (pr);

// applies plus_wf on each element of

// 'x' and 'y'

rmi_fence();

// barrier to guarantee every processor

// has updated x[i]

save_workfunction<PRange> save_wf;

// work function for y[i] = x[i];

pr.set_task(save_wf);

p_for_all(pr);

// applies save_wf on each element of

// 'x' and 'y'

rmi_fence();

// barrier to guarantee every process

// has saved updated x[i] to y[i]

}

}

```

Since the RD algorithm needs to operate on the elements of the copy y, the input pRange object pr for the algorithm has to support access to two Views, one for x's View and the other for y's View. This is supported by STAPL's combined-view pRange.

Similar to the original algorithm's pseudo-code, the STAPL generic implementation applies a work function on a pRange in each parallel step by calling  $p\_for\_all$ .

A DDG does not need to be specified explicitly for the pRange object here, because Communication Pattern I by default uses the DDG including one task per subrange and no orderings between tasks.

The first work function type  $plus\_workfunction$  has its operator() applying the input binary operator on y[i-d] and x[i] on one subrange in each task. This only deals with the second step; with p=n, each local chunk on one processor has only one single element. That is why only the first element in view0 and view1 in the subrange are worked on. The following is the pseudo-code for this work function.

```

void operator() (typename

PRange::subview_set_type& subrange_data)

{

int offset = at<0>(subrange_data)->offset();

// the offset for this subrange, i.e., "i"

if ( i < d) {

; // no-op

} else {

x_iterator xit =

at<0>(subrange_data)->begin();

// the element x[i]

y_iterator yit =

at<1>(subrange_data)->begin() - d;

// the element y[i-d]

*xit = bin_op(*yit, *xit);

// x[i] = bin_op(y[i-step], x[i])

}

}

};

```

In order for each task to know whether it should apply the binary operation (like addition) or just do no-op, the task has to make a decision based on the distance d for the current step and the subrange's index i. Basically, if i < d, this task should do no-op. Since each call for p-for-all is working for only one single step, this step's distance d is simply passed as an argument for this work function.

The save\_workfunction is very similar, but simpler.

```

Work function "save_workfunction" in RD

Algorithm's Barrier implementation:

(Operator() saves x[i] to y[i].)

template < typename PRange >

class save_workfunction :

public work_function_base<PRange>

{

private:

// no more need for bin_op and d

public:

void operator() (typename

PRange::subview_set_type& subrange_data)

{

x_iterator xit =

at<0>(subrange_data)->begin();

// the element x[i]

y_iterator yit =

at<1>(subrange_data)->begin();

// the element y[i]

*yit = *xit;

// y[i] = x[i]

}

};

```

Since there are  $\Theta(log_2(p))$  parallel steps in the RD algorithm, the number of

barriers is also  $\Theta(log_2(p))$ . Each processor is required to participate in each step, so the total number of synchronizations is  $\Theta(p*log_2(p))$ .

## 3. Point-to-point Synchronization Implementation for RD Algorithm

As explained in the previous section, barrier synchronization causes some processors to do unnecessary *no-ops* at some parallel steps based on the algorithm itself.

Alternately, point-to-point synchronization eliminates the requirement for all processors to participate in all parallel steps, i.e., it avoids the unnecessary *no-ops*.

Basically, when implementing a parallel algorithm using point-to-point synchronization, it is necessary to only respect the point-to-point synchronizations between tasks. For the RD algorithm, this is guaranteed by simply using Communication Pattern II in Section B.

The following is the pseudo-code for the implementation of the RD algorithm with point-to-point synchronization.

```

Framework of RD algorithm with

Point-to-point Synchronization option:

(Using Communication Pattern II)

```

```

Assumption: p = n (for step 2 only);

Input "x" and its copy "y" are stored in 2 pContainers.

```

```

Input: A pRange "pr" which has access to two views,

whose view0 is for "x", view1 is for "y";

A binary functor "bin_op" for prefix sums

operation.

```

```

Output: Prefix sums of elements in "x" are stored

into view0 of "pr".

template <typename PRange, typename BinaryFunction>

p_prefixsums_RD_Point2point (PRange& pr,

BinaryFunction bin_op)

{

Build a new pRange "ipr" with same views

as "pr", using an instance of "rd_dependence_

oracle" as its DDG;

workfunction wf(bin_op);

// if the task-specific data "d" of the task

// is 0, then the task does: y[i] = x[i];

// else it does: x[i] = bin_op(y[i-d], x[i]).

ipr.set_task(wf);

p_for_all(ipr);

}

```

Point-to-point synchronization does not care about single parallel steps; instead, it builds and applies the DDG for the whole algorithm. Tasks in different parallel steps could run at the same time and tasks in later parallel steps could also run earlier as long as all synchronizations (caused by data dependences) are respected. This is why the value of d as task-specific data needs to be stored; it is statically computed based on the level for a task in  $construct\_tasks$ .

Therefore, a unified work function object wf will work for any task. It does  $x[i] = bin_{-}op \ (y[i-d], \ x[i])$  if the task is at an even level, otherwise it does y[i] = x[i].

The following is the definition of the work function class. As mentioned before, since the p=n situation is assumed, each subrange has only one single element for x and one single element for y.

```

Work function "workfunction" in RD

Algorithm's Point-to-point implementation:

(Operator() either updates x[i] or saves it to y[i].)

template < typename PRange, typename BinaryFunction >

class workfunction :

public work_function_base<PRange>

{

private:

BinaryFunction bin_op;

public:

workfunction(BinaryFunction _bin_op) :

bin_op(_bin_op) {}

bool use_ddg_vertex_data() { return true; }

// this method tells the run-time system

// to pass task-specific data to the work

// function's operator()

void operator() (

typename PRange::subview_set_type& subrange_data,

typename PRange::DDGType::VERTEX& task_data)

```

```

{

int d = task_data.d;

// retrieve the "d" statically computed

// and saved in the task during

// "construct_tasks"

if (d > 0)

// this is an even-level task

{

x_iterator xit =

at<0>(subrange_data)->begin();

// the element for "x" in this subrange

y_iterator yit =

at<1>(subrange_data)->begin() - d;

// the element for "y" in subrange of

// "d" distance away