# AREA AND ENERGY EFFICIENT VLSI ARCHITECTURES FOR LOW-DENSITY PARITY-CHECK DECODERS USING AN ON-THE-FLY COMPUTATION

A Dissertation

by

KIRAN KUMAR GUNNAM

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

December 2006

Major Subject: Computer Engineering

# AREA AND ENERGY EFFICIENT VLSI ARCHITECTURES FOR LOW-DENSITY PARITY-CHECK DECODERS USING AN ON-THE-FLY COMPUTATION

# A Dissertation

by

# KIRAN KUMAR GUNNAM

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

Approved by:

Co-Chairs of Committee, Gwan Choi

Scott Miller

Committee Members, Jiang Hu

Duncan Walker

Head of Department, Costas Georghiades

December 2006

Major Subject: Computer Engineering

# **ABSTRACT**

Area and Energy Efficient VLSI Architectures for Low -Density Parity-Check Decoders

Using an On-the-Fly Computation. (December 2006)

Kiran Kumar Gunnam, M.S., Texas A&M University

Co-Chairs of Advisory Committee: Dr. Gwan Choi

Dr. Scott Miller

The VLSI implementation complexity of a low density parity check (LDPC) decoder is largely influenced by the interconnect and the storage requirements. This dissertation presents the decoder architectures for regular and irregular LDPC codes that provide substantial gains over existing academic and commercial implementations. Several structured properties of LDPC codes and decoding algorithms are observed and are used to construct hardware implementation with reduced processing complexity. The proposed architectures utilize an on-the-fly computation paradigm which permits scheduling of the computations in a way that the memory requirements and re-computations are reduced. Using this paradigm, the run-time configurable and multi-rate VLSI architectures for the rate compatible array LDPC codes and irregular block LDPC codes are designed. Rate compatible array codes are considered for DSL applications. Irregular block LDPC codes are proposed for IEEE 802.16e, IEEE 802.11n, and IEEE 802.20. When compared with a recent implementation of an 802.11n LDPC decoder, the proposed decoder reduces the logic complexity by 6.45x and memory complexity by 2x for a given data throughput. When compared to the latest reported multi-rate decoders, this decoder design has an area efficiency of around 5.5x and energy efficiency of 2.6x for a given data throughput. The numbers are normalized for a 180nm CMOS process.

Properly designed array codes have low error floors and meet the requirements of magnetic channel and other applications which need several Gbps of data throughput. A high throughput and fixed code architecture for array LDPC codes has been designed. No modification to the code is performed as this can result in high error floors. This parallel decoder architecture has no routing congestion and is scalable for longer block lengths. When compared to the latest fixed code parallel decoders in the literature, this design has an area efficiency of around 36x and an energy efficiency of 3x for a given data throughput. Again, the numbers are normalized for a 180nm CMOS process. In summary, the design and analysis details of the proposed architectures are described in this dissertation. The results from the extensive simulation and VHDL verification on FPGA and ASIC design platforms are also presented.

To my family.

#### **ACKNOWLEDGMENTS**

I would like to express my gratitude to my advisor, Dr. Gwan Choi, for his financial support and encouragement for my research. He supported me in all the difficult situations where I needed help. I would like to thank Dr. Scott Miller for his time in serving on my committee. His suggestions made me focus exclusively on LDPC decoder architectures though initially I set out to work on a conglomeration of different topics. Dr. Mark Yeary has been very helpful and he spent a lot of time improving my papers. I would also like to thank Dr. Duncan Walker who suggested that I look into scalabilty issues of the decoder architectures. I would like to thank Dr. Jiang Hu for his time and suggestions to improve the presentation aspects of my research.

I would like to take this opportunity to express my thanks to Intel, Schlumberger and Starvision Technologies for supporting my research. Dr. James Ochoa and Mr. Mike Jacox of Starvision Technologies in conjunction with Dr. Gwan Choi and Dr. John Junkins have supported my PhD program.

Several students and other people at Texas A&M helped me in my research work also. Thanks to Weihuang Wang, in particular, for working on the matlab simulation model for my architecture on the layered decoding for array codes and on the verification of some of the HDL modules. In addition, he spent several weeks with me working on writing the paper. Most of the figures presented in this dissertation were drawn by him. I appreciate the help of Mr. Abhiram Prabhakar and Mr. Euncheol Kim in providing the useful reviews for some of my work. Several members of the computer engineering group helped also. In

addition, Ms. Linda Crenwelge, associate editor of Choice magazine, provided me help with the editing of my papers. I am thankful for the additional staff at Texas A&M University for assisting in my degree program.

Several other researchers and professors outside Texas A&M University provided feedback on my work. Dr. Jinghu Chen of Qualcomm provided a review on one of my papers and supplied me with his software on density evolution. Dr. Zhongfeng Wang of Oregon State University provided several suggestions to improve the presentaion of the papers. In addition, I received several anonymous reviewers' comments as part of my paper submissions. Those suggestions are incorporated into the papers, as well as, into the dissertation.

Dr. Roger Robbins has been my career mentor for the last four years. His advice helped me see my career and life more clearly. Kanu Chadha gave his time to listen to me and to offer suggestions. My lovely wife, Anu, has supported me in many more ways than meet the eye. She did the difficult task of completing 36 credit hours in one year at Texas A&M for her masters degree course requirements while taking care of different things at home. I would like to thank my parents, and brother Ramakrishna, for their constant support and encouragement through every major decision in my life.

# TABLE OF CONTENTS

| Pag                                                                                                                                                        | зe          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| ABSTRACTi                                                                                                                                                  | ii          |

| DEDICATION                                                                                                                                                 | V           |

| ACKNOWLEDGMENTSv                                                                                                                                           | vi          |

| TABLE OF CONTENTSvi                                                                                                                                        | ii          |

| LIST OF FIGURES                                                                                                                                            | κi          |

| LIST OF TABLESxi                                                                                                                                           | ii          |

| CHAPTER                                                                                                                                                    |             |

| I INTRODUCTION                                                                                                                                             | 1           |

| 1.1. Motivation                                                                                                                                            | 5           |

| II QUASI-CYCLIC LOW-DENSITY PARITY-CHECK CODES AND DECODING                                                                                                | 1           |

| 2.1.Introduction12.2.Cyclotomic Cosets12.3.Array LDPC Codes12.4.Rate-compatible Array LDPC Codes12.5.Irregular Quasi-Cyclic LDPC Codes (Block LDPC codes)1 | 2<br>3<br>4 |

| 2.6.Irregular QC-LDPC Codes for Other Wireless Standards(802.11n and 802.20)                                                                               | 6           |

| III MULTI-RATE TPMP ARCHITECTURE FOR REGULAR QC-LDPC CODES                                                                                                 | 9           |

| 3.1 Introduction                                                                                                                                           |             |

| CHAP | TER                                                                                        | Page |

|------|--------------------------------------------------------------------------------------------|------|

|      | 3.4.Performance Comparison 3.5.FPGA Implementation Results 3.6.ASIC Implementation Results | 30   |

| IV   | VALUE-REUSE PROPERTIES OF OMS AND MICRO-ARCHITECTURES FOR CHECK NODE UNIT BASED ON OMS     |      |

|      | TOR CHECK WODE OWN DAGED ON OWNS                                                           | 55   |

|      | 4.1.Value-reuse Properties                                                                 | 35   |

|      | 4.2.Serial CNU for OMS                                                                     |      |

|      | 4.3.Parallel CNU                                                                           | 38   |

| V    | FIXED CODE TPMP ARCHITECTURE FOR REGULAR QC-LDPC CODES                                     | 541  |

|      | 5.1.Introduction                                                                           | 41   |

|      | 5.2.Reduced Message Passing Memory and Router Simplification                               | 42   |

|      | 5.3.Check Node Unit Micro-architecture                                                     |      |

|      | 5.4.Architecture                                                                           | 45   |

|      | 5.5.Results and Performance Comparsion                                                     | 48   |

| VI   | MULTI-RATE TDMP ARCHITECTURE FOR RATE-COMPATIBLE ARRA                                      | Y    |

|      | LDPC CODES                                                                                 | 53   |

|      | 6.1.Introduction                                                                           | 53   |

|      | 6.2.Background                                                                             | 54   |

|      | 6.3.TDMP for Array LDPC                                                                    |      |

|      | 6.4. Value-reuse Properties of OMS                                                         |      |

|      | 6.5.Multi-rate Architecture Using TDMP and OMS                                             |      |

|      | 6.6.Implementation Results and Discussion                                                  |      |

|      | 6.7.Conclusion                                                                             | 75   |

| VII  | MULTI-RATE TDMP ARCHITECTURE FOR IRREGULAR QC-LDPC                                         |      |

|      | CODES                                                                                      | 81   |

|      | 7.1.Introduction                                                                           | 81   |

|      | 7.2.LDPC Codes and Decoding                                                                | 82   |

|      | 7.3.Multi Rate Decoder Architecture Using TDMP and OMS                                     |      |

|      | 7.4.Discussion and Implementation Results                                                  |      |

|      | 7.5.Conclusion                                                                             | 100  |

| CHAPTER                                               | Page |

|-------------------------------------------------------|------|

| VIII FIXED CODE TDMP ARCHITECTURE FOR REGULAR QC-LDPC |      |

| CODES                                                 | 105  |

| 8.1.Introduction                                      | 105  |

| 8.2.Parallel Architecture Using TDMP and OMS          | 105  |

| 8.3.ASIC Implementation Results                       |      |

| 8.4.Conclusion                                        | 111  |

| IX SUMMARY                                            | 113  |

| 9.1 Key Contributions                                 | 113  |

| 9.2 Future Work                                       | 117  |

| 9.3 Conclusion                                        | 118  |

| REFERENCES                                            | 120  |

| VITA                                                  | 126  |

# LIST OF FIGURES

| FIGUI | RE                                                                                                      |

|-------|---------------------------------------------------------------------------------------------------------|

| 1.1   | Block diagram of a digital communication system                                                         |

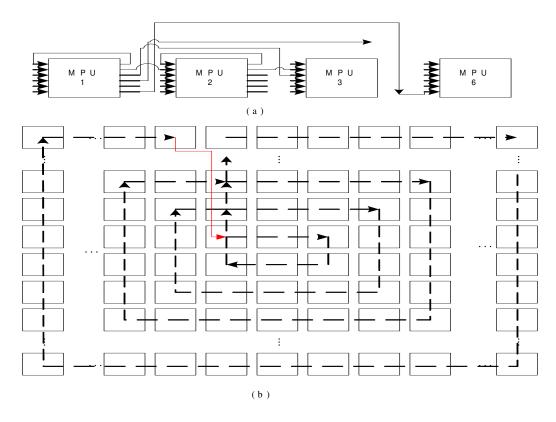

| 3.1   | Block diagram of the decoder architecture                                                               |

| 3.2   | Pipeline of the decoder                                                                                 |

| 3.3   | Comparison of architecture for (3,k=6,30) rate compatible array codes of up to length 1830              |

| 4.1   | Serial CNU for OMS using value-reuse property                                                           |

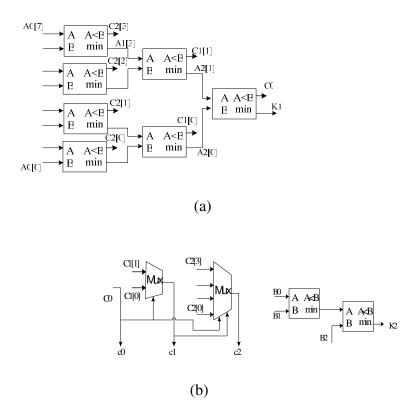

| 4.2   | Finder for the two least minimum in CNU (a) binary tree to find the least minimum                       |

| 4.3   | Parallel CNU based on value-reuse property of OMS                                                       |

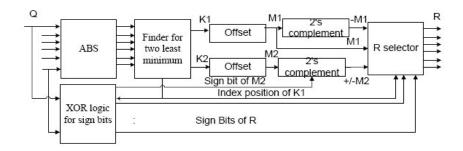

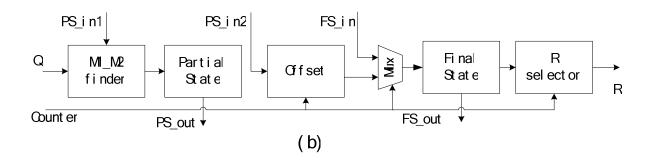

| 5.1   | Check node processing unit, Q: variable node message, R: check node message                             |

| 5.2   | Architecture45                                                                                          |

| 5.3   | Pipeline                                                                                                |

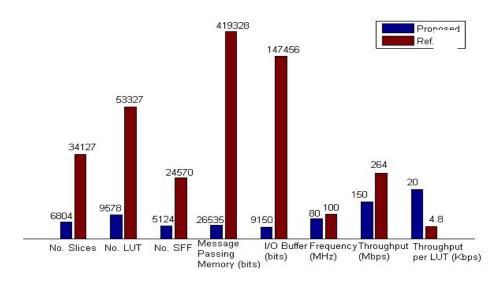

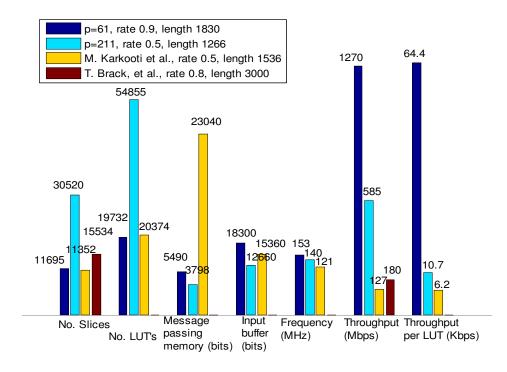

| 5.4   | Results comparison with M. Karkoot et al.,[37] and T. Brack, et al., [41]50                             |

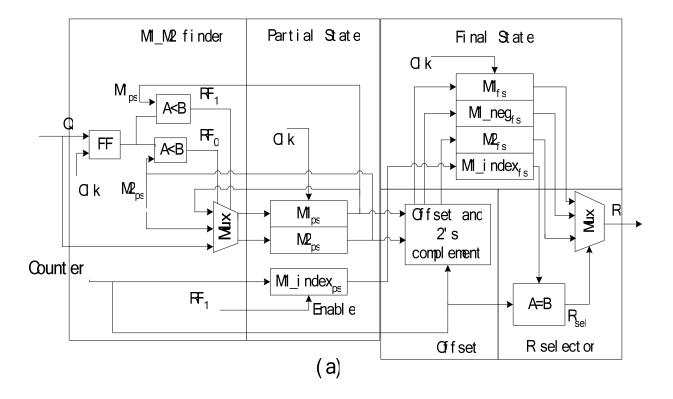

| 6.1   | Serial CNU for OMS using value-reuse property                                                           |

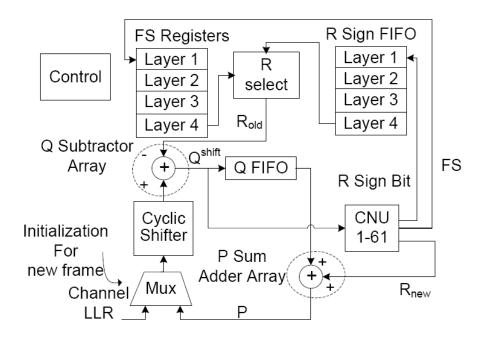

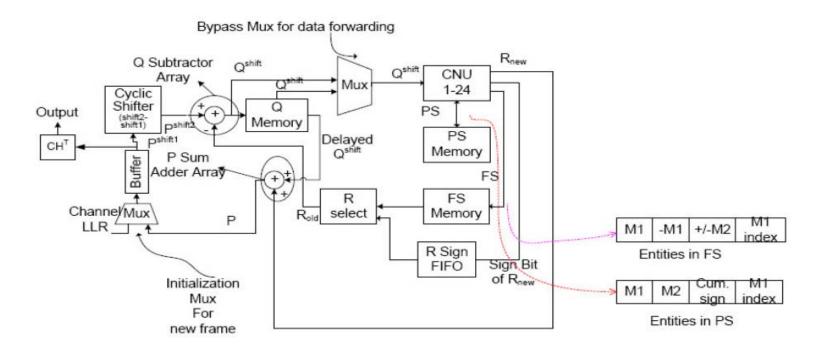

| 6.2   | LDPC Decoder using layered decoding and OMS62                                                           |

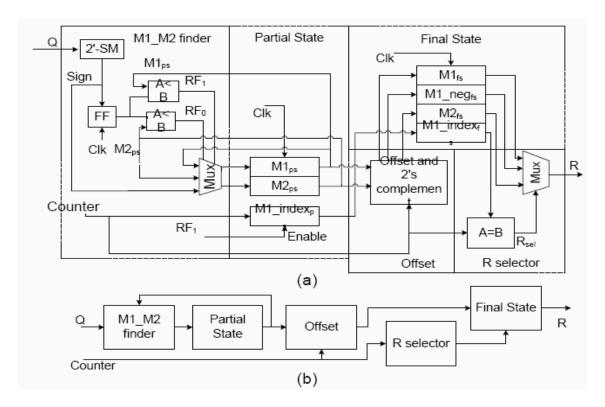

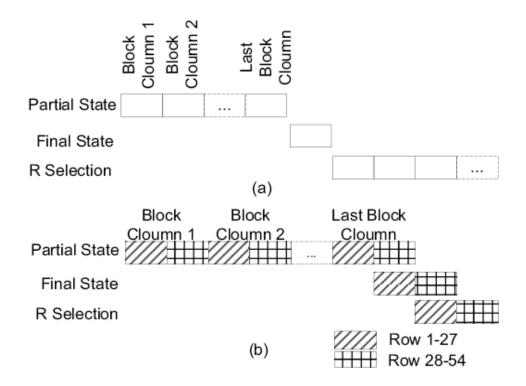

| 6.3   | Block serial processing and 3-stage pipelining for TDMP using OMS a) detailed diagram b) simple diagram |

| FIGURE                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

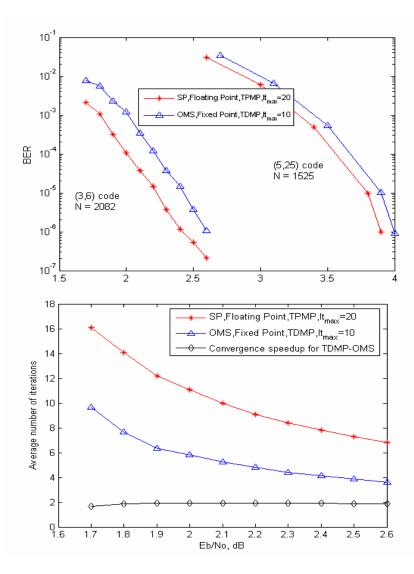

| 6.4 . (a) Bit error rate performance of the proposed TDMP decoder using OMS(j=3,k=6,p=347,q=0) Array LDPC code of length N=2082 and (j=5,k=25,p=61,q=0) array LDPC code of length N=1525            |

| 7.1 Operation of CNU (a) no time-division multiplexing (b) time-division multiplexing                                                                                                               |

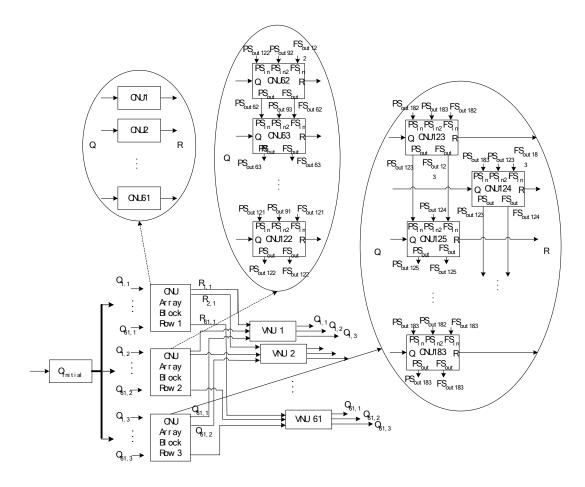

| 7.2 Multi-rate LDPC decoder architecture for block LDPC codes                                                                                                                                       |

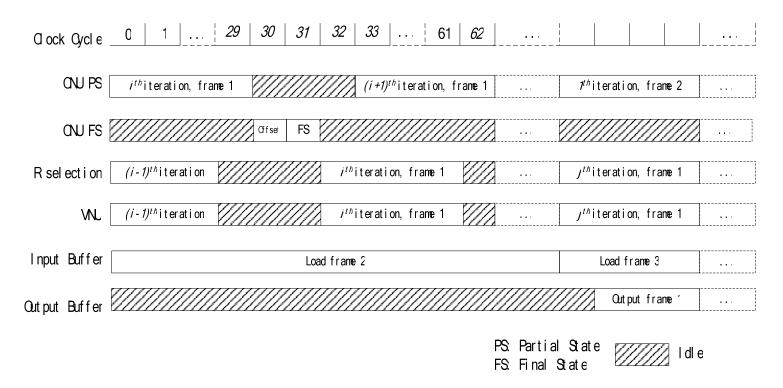

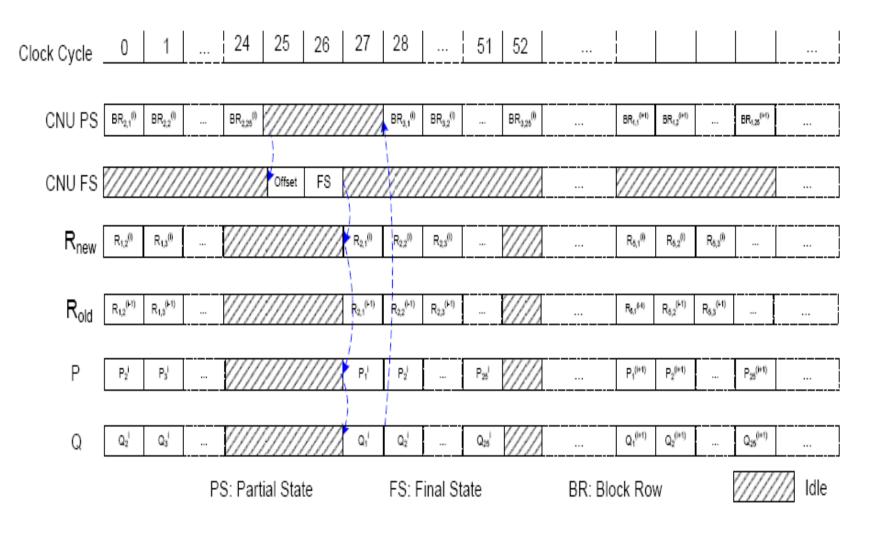

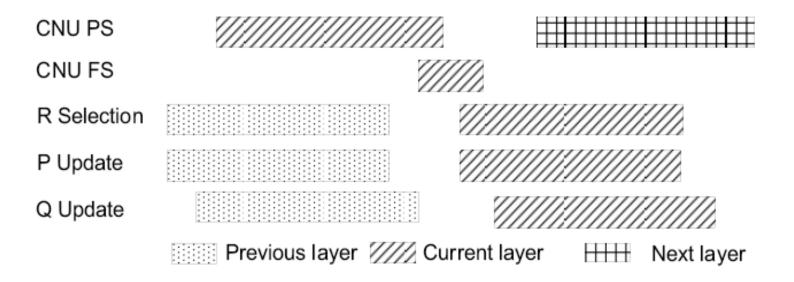

| 7.3 Three-stage pipeline of the multi-rate decoder architecture89                                                                                                                                   |

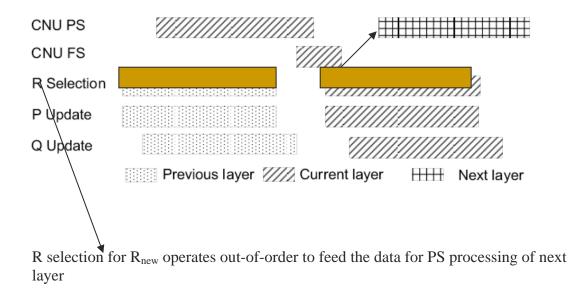

| 7.4 Out of order processing for R <sub>new</sub> selection89                                                                                                                                        |

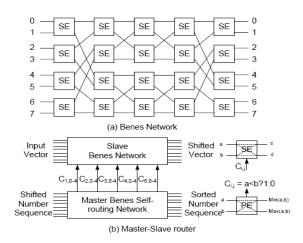

| 7.5 Proposed master-slave router to support different cyclic shifts that arise due to a wide range of expansion factors z(=24,28,,96) and shift coefficients (0,1,,z-1)                             |

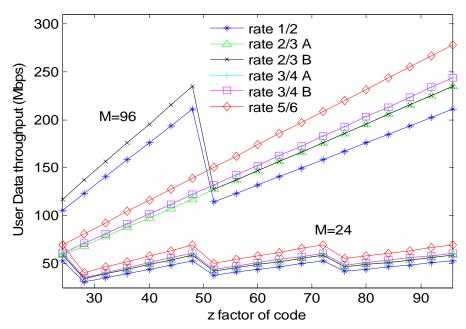

| 7.6 User data throughput of the proposed decoder vs. the expansion factor of the code, z, for different numbers of decoder parallelization, M                                                       |

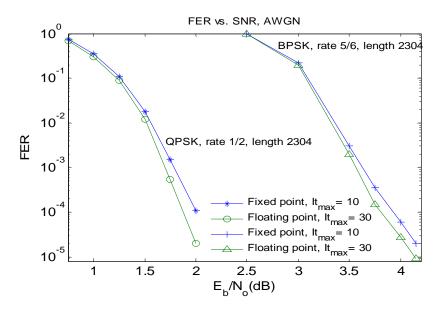

| 7.7 Frame-error rate results                                                                                                                                                                        |

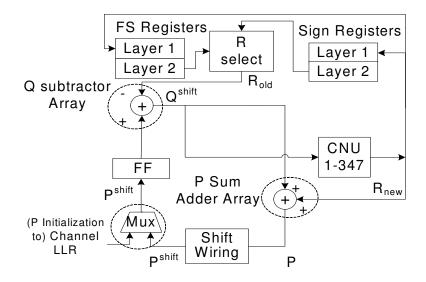

| 8.1 Parallel architecture for layered decoder                                                                                                                                                       |

| 8.2 (a) Illustration of connections between message processing units to achieve cyclic down shift of (n-1) on each block column n (b) Concentric layout to accommodate 347 message processing units |

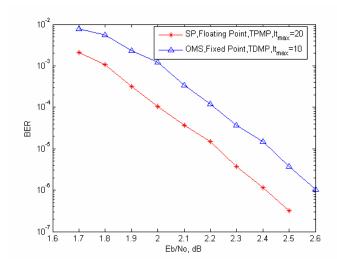

| 8.3 BER performance of the decoder for (3,6) array code of N=2082                                                                                                                                   |

# LIST OF TABLES

| TABLE                                                                                         | зe  |

|-----------------------------------------------------------------------------------------------|-----|

| 1.1 BER performance for different codes                                                       | .3  |

| 1.2 Quick summary of the proposed multi-rate decoder architectures                            | . 8 |

| 1.3 Quick summary of the proposed fixed-code decoder architectures                            | .9  |

| 3.1 Occupation of resources for a decoding iteration in terms of clock cycles2                | 26  |

| 3.2 Snapshot of partial sum registers in p CNUs operating in parallel to compute p R messages | 27  |

| 3.3 Snapshot of partial sum registers in p VNUs operating in parallel to compute p Q messages | 28  |

| 3.4 Memory requirement comparison                                                             | 30  |

| 3.5 FPGA results (Device: Xilinx 2v8000ff1152-5) for (3,30) code of length 18303              | 31  |

| 3.6 ASIC Implementation of the proposed TPMP multi-rate decoder architecture 3                | 33  |

| 3.7 Area distribution of the chip for (3, k) rate compatible array codes, 130nm CMOS          | 33  |

| 3.8 Power distribution of the chip for (3, k) rate compatible array codes, 130nm CMOS         | 34  |

| 4.1 Parallel CNU implementation                                                               | 40  |

| 5.1 FPGA results (Device: Xilinx 2v8000ff1152-5)                                              | 49  |

| 5.2 Summary of the proposed fixed-code decoder architecture, Code 1                           | 50  |

| 5.3 Summary of the proposed fixed-code decoder architecture, Code 2                           | 51  |

| 5.4 Summary of the proposed fixed-code decoder architecture, Code 3 and Code 4 5              | 51  |

| ΓABL | E Page                                                                                                                               |

|------|--------------------------------------------------------------------------------------------------------------------------------------|

| 5.5  | Area distribution of the fixed code TPMP architectures for array codes, 130nm CMOS                                                   |

| 5.6  | Power distribution of the fixed-code TPMP architectures for array codes, 130nm CMOS                                                  |

| 6.1  | FPGA implementations and performance comparison                                                                                      |

| 6.2  | Memory implementation for optimally scaled architecture ( $j=5,k=10,,k_{max}$ (=61), $p=61,M=p$ )77                                  |

| 6.3  | Memory implementation for scalable architecture ( $j=3,k=6,,k_{max}$ (=32), $p=347,M=61$ )                                           |

| 6.4  | ASIC Implementation of the proposed TDMP multi-rate decoder architecture 79                                                          |

| 6.5  | Area distribition of the chip for (5,k) rate compatible array codes, 130nm 80                                                        |

| 6.6  | Power distribution of the chip for (3,k) rate compatible array codes, 130nm 80                                                       |

| 7.1  | FPGA Implementation results of the multi-rate decoder (supports z=24, 48 and 96 and all the code rates)                              |

| 7.2  | FPGA Implementation results of the multi-rate decoder, fully compliant to WiMax (supports z=24,28,32,,and 96 and all the code rates) |

| 7.3  | Implementation comparison                                                                                                            |

| 7.4  | ASIC Implementation of the proposed TDMP Multi-rate decoder architecture 101                                                         |

| 7.5  | Area distribution of the chip for WiMax LDPC codes                                                                                   |

| 7.6  | Power distribution of the chip for WiMax LDPC codes                                                                                  |

| 7.7  | ASIC Implementation of the proposed TDMP Multi-rate decoder architecture for 802.11n LDPC codes                                      |

| 7.8  | Area distribution of the chip for IEEE 802.11n LDPC codes                                                                            |

| 7.9  | Power distribution of the chip for IEEE 802 11n LDPC codes 103                                                                       |

| TABLE                                                                                                                                         | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------------|------|

| 7.10 FPGA implementation results for the multi-rate decoder, fully compliant to IEEE 802.11n (Device, XILINX2V8000FF152-5, frequency =110MHz) | 104  |

| 7.11 ASIC implementation results for the multi-rate decoder for M=81 (Frequency = 500MHz)                                                     |      |

| 8.1 Proposed decoder work as compared with other authors                                                                                      | 112  |

# CHAPTER I

# **INTRODUCTION**

# 1.1. Motivation

The insatiable demand for data and connectivity at the user level, driven primarily by advances in integrated circuits, has dramatically impacted the evolution of the communications market. The period of the last 25 years witnessed the progress from 300 baud modems to multi-terabit fiber backbones, multi-gigabit wired communication links and multi-megabit wireless communication links.

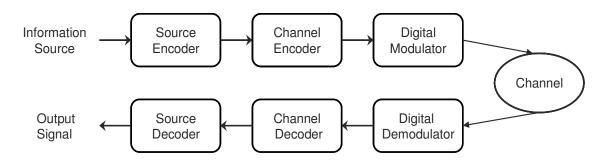

Fig 1.1. Block diagram of a digital communication system

Figure 1.1 shows a basic block diagram of a digital communication system [1]. First, an information signal, such as voice, video or data is sampled and quantized to form a digital sequence, then it passes through the source encoder or data compression to remove any unnecessary redundancy in the data.

This dissertation follows the style and format of *IEEE Transactions on Circuits and Systems*.

Then, the channel encoder codes the information sequence so that it can recover the correct information after passing through a channel. Error correcting codes such as convolutional [2], turbo [3] or LDPC codes [4] are used as channel encoders. The binary sequence then is passed to the digital modulator to map the information sequence into signal waveforms. The modulator acts as an interface between the digital signal and the channel. The communication channel is the physical medium that is used to send the signal from the transmitter to the receiver. At the receiving end of the digital communications system, the digital demodulator processes the channel-corrupted transmitted waveform and reduces the waveforms to a sequence of digital values that feeds into the channel decoder. The decoder reconstructs the original information by the knowledge of the code used by the channel encoder and the redundancy contained in the received data. Then, a source decoder decompresses the data and retrieves the original information. The probability of having an error in the output sequence is a function of the code characteristics, the type of modulation, and channel characteristics such as noise and interference level, etc [1].

Low-Density Parity Check (LDPC) codes and Turbo codes are among the best known near Shannon limit codes that can achieve good BER performance for low SNR applications [3]-[14] as shown in Table 1.1. When compared to the decoding algorithm of Turbo codes, LDPC decoding algorithm has more parallelization, low implementation complexity, low decoding latency, as well as no error-floors at high signal-to-noise ratios (SNRs). LDPC decoders require simpler computational processing. While initial LDPC decoder designs [15] suffered from complex interconnect issues, structured LDPC codes [10-11], [4], [16-25] simplify the interconnect complexity. Recently, Low-Density Parity-

Check (LDPC) codes have widely been considered as a promising error-correcting coding scheme for many real applications in telecommunications and magnetic storage, because of their superior performance and suitability for hardware implementation. LDPC codes are adopted/being adopted in the next generation digital video broadcasting (DVB-S2), MIMO-WLAN 802.11n, 802.12, 802.20, Gigabit Ethernet 802.3, magnetic channels (storage/recording systems), and long-haul optical communication systems.

Table 1.1

BER performance for different codes

| Rate ½ Code          | SNR required for |

|----------------------|------------------|

|                      | BER <1e-5        |

| Shannon, Random Code | 0 dB             |

| (255,123) BCH        | 5.4 dB           |

| Convolutional Code   | 4.5 dB           |

| Iterative Code Turbo | 0.7 dB           |

| Iterative Code LDPC  | 0.0045 dB        |

LDPC codes can be decoded by Gallager's iterative two-phase message passing algorithm (TPMP), which involves check-node update and variable-node update as a two phase schedule. Various algorithms are available for check-node updates and widely used algorithms are the sum of products (SP), min-sum (MS), and Jacobian-based BCJR (named after its discoverers Bahl, Cocke, Jelinik, and Raviv) [26-35]. The authors in [20] introduced the concept of turbo decoding message passing (TDMP, also called layered decoding) using BCJR for their architecture-aware LDPC (AA-LDPC) codes. TDMP

offers 2x throughput and significant memory advantages when compared to TPMP. TDMP is later studied and applied for different LDPC codes using the sum of products algorithm and its variations in [38]-[39]. TDMP is able to reduce the number of iterations required by up to 50% without performance degradation when compared to the standard message passing algorithm. A quantitative performance comparison for different check updates was given by Chen and Fossorier et al. [32]. Their research showed that the offset min-sum (OMS) decoding algorithm with 5-bit quantization could achieve the same bit-error rate (BER) performance as that of floating point SP and BCJR with less than 0.1 dB penalty in SNR.

Most of the current LDPC decoder architecture research is focusing on increasing throughput or reducing implementation complexity, neglecting power analysis. In fact, power consumption presents a critical issue in computing, particularly in portable and mobile platforms, because of battery life and power dissipation. Designing a practical architecture must consider the trade-off among throughput, power consumption and hardware complexity. An LDPC decoder architecture can be implemented in parallel message passing and/or serial message passing. In the parallel decoder architecture [15], the nodes in the bipartite graph are directly mapped into message computation units and the edges of the graph are mapped into network of interconnects. The parallel architecture achieves high throughput at the cost of interconnect complexity. In the architecture [16], a fully pipelined implementation with two memory buffers per stage, alternating between read/write, was introduced. In [18], a joint code decoder design approach was adapted to construct a class of (3,k)-regular LDPC codes and a partly parallel decoder architecture was proposed to reduce the hardware complexity and achieve reasonable throughput.

# 1.2. Problem Overview

A parallel decoder implementation [15] exploiting the inherent parallelism of the algorithm is constrained by the complexity of the physical interconnect required to establish the graph connectivity of the code and, hence, does not scale well for moderate (2K) to large code lengths. Long on-chip interconnect wires present implementation challenges in terms of placement, routing, and buffer-insertion to achieve timing closure. For example, the average interconnect wire length of the rate-0.5, length 1020, 4-bit LDPC decoder of [15] is 3 mm using 160nm CMOS technology, and has a chip area of 52.5 mm<sup>2</sup> of which only 50% is utilized due to routing congestion. On the other hand, serial architectures [16] in which computations are distributed among a number of function units that communicate through memory instead of a complex interconnect, are slow and do not meet the practical data throughputs considered in the present standards.

The authors in [19] reported that 95% of power consumption of the decoder chip developed in [18] results from memory accesses. The implementation [20] reports that 50% of it power is due to memory accesses in message passing. There are several other architectures presented in [22]-[24], [37-38], [42], [45]. However, all of these implementations focused on improving the throughput while ignoring the power consumption issue due to message passing memory.

The check-to-bit message update equation is prone to quantization noise since it involves the nonlinear function and its inverse. The function has a wide dynamic range which requires the messages to be represented using a large number of bits to achieve a fine resolution, leading to an increase in memory size and interconnect complexity (e.g., for a regular (3, 6)-LDPC code of length 1020 with 4-bit messages, an increase of 1 bit

increases the memory size and/or interconnect wires by 25%). The min-sum decoding algorithm [29], [32]-[33], [34] is an approximation for the Sum of Products algorithm to decode LDPC codes. The min-sum decoding algorithm does not have the complexity associated with non-linear functions used in the sum of products algorithm [26].

# 1.3. Main Contributions

The main contributions of this work are the following:

- 1 The On-the-fly computation paradigm by which the structured properties of LDPC codes are used to reduce computations, memory and interconnect.

- 2 New micro-architecture structures for switching network and check node processing.

- Efficient decoder architectures and implementations for regular and irregular LDPC codes that offers substantial gains over the existing academic and commercial implementations. Three unique run time configurable and multi-rate cores, each tailored in the design phase based on the class of code and the application, are designed. Two very high throughput and fixed code architectures are designed. Characteristics of these decoder ASIC implementations are briefly summarized in Table 1.2 and Table 1.3 along with the other recent state-of-theart implementations. Details of each decoder implementation are given in the next chapters.

Rate compatible array codes are considered for DSL applications. Irregular block LDPC codes are proposed for IEEE 802.16e, IEEE 802.11n, IEEE 802.20 and being considered for other wireless standards. The total savings in memory translate to around 55% for the IEEE 802.11n LDPC decoder, when compared to a very recent state of the

art decoder. In addition to the above savings, a master-slave router is proposed to accommodate 114 different parity check matrices in run time for IEEE 802.16e. This approach eliminates the control memory requirements by generating the control signals for the data router (slave) on-the-fly with the help of a self routing master network. If the memory approach is used for this as in the present state of the art, it would have resulted in a large chip area of around 140 mm<sup>2</sup> (in 180 nm technology) just for storing the control signals.

Properly designed regular array codes have low error floors and meet the requirements of magnetic recording channel and other applications which need several Gbps of data throughput. A high throughput and fixed code architecture for array LDPC codes has been designed. No modification to the code is done as this can result in early error floors. This parallel decoder architecture has no routing congestion and is scalable for longer block lengths. When compared to the latest state of the art decoders, this design has an area efficiency of around 10x for a given data throughput. In summary, all of these findings are explained in the text of this dissertation, with extensive theoretical simulations and VHDL verification on FPGA and ASIC design platforms.

Table 1.2

Quick summary of the proposed multi-rate decoder architectures

|                                                     | Semi-Parallel<br>multi-rate<br>LDPC decoder<br>[26]               | Multi-rate TPMP Architecture regular QC-LDPC (Chapter III) (3,k) rate | Multi-rate TDMP Architecture for regular QC- LDPC (Chapter VI) | Multi-rate TDMP Architecture for irregular QC- LDPC (Chapter VII) Irregular codes up |

|-----------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------|

| LDPC Code                                           | AA-LDPC, (3,6) code, rate 0.5, length 2048                        | compatible array codes $p=347$ . $k=6,7,12$                           | (5,k) rate compatible array codes $p=61$ . $k=10,11,61$        | to length 2304<br>IEEE 802.16e<br>WiMax LDPC<br>codes                                |

| Decoded Throughput, t <sub>d</sub> ,                | 640 Mbps                                                          | 2.37 Gbps                                                             | 590 Mbps                                                       | 1.37 Gbps                                                                            |

| Area                                                | 14.3 mm <sup>2</sup>                                              | 7.62 mm <sup>2</sup>                                                  | 1.6 mm <sup>2</sup>                                            | 2.1 mm <sup>2</sup>                                                                  |

| Frequency                                           | 125 MHz                                                           | 500 MHz                                                               | 500 MHz                                                        | 500 MHz                                                                              |

| Nominal Power Dissipation                           | 787 mW                                                            | 821 mW                                                                | 257 mW                                                         | 282 mW                                                                               |

| CMOS Technology                                     | 180 nm, 1.8V                                                      | 130 nm, 1.2V                                                          | 130 nm,.1.2V                                                   | 130 nm, 1.2V                                                                         |

| Decoding Schedule                                   | TDMP, BCJR,                                                       | TPMP, SP, it <sub>max</sub> =20                                       | TDMP, OMS,                                                     | TDMP, OMS,                                                                           |

|                                                     | it <sub>max</sub> =10                                             |                                                                       | $it_{max}=10$                                                  | $it_{max}=10$                                                                        |

| Area Efficiency for t <sub>d</sub> ,                | 44.75 Mbps/mm <sup>2</sup>                                        | 311 Mbps/ mm <sup>2</sup>                                             | 369 Mbps/ mm <sup>2</sup>                                      | 649.5 Mbps/ mm <sup>2</sup>                                                          |

| Energy Efficiency for t <sub>d</sub> ,              | 123<br>pJ/Bit/Iteration                                           | 17 pJ/Bit/Iteration                                                   | 44.2 pJ/Bit/Iteration                                          | 21 pJ/Bit/Iteration                                                                  |

| Est. Area for 180 nm                                | 14.3 mm <sup>2</sup>                                              | 14.6 mm <sup>2</sup>                                                  | $3.06 \text{ mm}^2$                                            | 4.02 mm <sup>2</sup>                                                                 |

| Est. Frequency for 180                              | 125 MHz                                                           | 360 MHz                                                               | 360 MHz                                                        | 360 MHz                                                                              |

| Est. Decoded<br>Throughput(t <sub>d</sub> ) ,180 nm | 640 Mbps                                                          | 1.71 Gbps                                                             | 426 Mbps                                                       | 989 Mbps                                                                             |

| Est. Area Efficiency for t <sub>d</sub> , 180 nm    | 44.75 Mbps/mm <sup>2</sup>                                        | 117 Mbps/ mm <sup>2</sup>                                             | 139.2 Mbps/mm <sup>2</sup>                                     | 246 Mbps/mm <sup>2</sup>                                                             |

| Est. Energy Efficiency for t <sub>d</sub> , 180 nm  | 123 pJ/Bit/Iteration                                              | 38.3 pJ/Bit/Iteration                                                 | 99.5 pJ/Bit/Iteration                                          | 47.3 pJ/Bit/Iteration                                                                |

| Application                                         | Multi-rate<br>application as well<br>as fixed code<br>application | DSL, Wireless                                                         | DSL, Wireless                                                  | Wireless,<br>IEEE 802.11n,<br>IEEE 802.16e,<br>IEEE 802.22                           |

| Bit error rate Performance                          | Good                                                              | Good                                                                  | Good                                                           | Very good and close to capacity                                                      |

| Scalability of Design for longer lengths            | Yes                                                               | Yes                                                                   | Yes                                                            | Yes                                                                                  |

$\label{eq:table 1.3}$  Quick summary of the proposed fixed-code decoder architectures

|                                                                    | Fully Parallel LDPC<br>decoder<br>[15]      | TPMP Architecture regular Array QC-LDPC (Chapter V)                                                                                  | TDMP Architecture for regular Array QC-LDPC (Chapter VIII)                                                             |

|--------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Decoded Throughput, t <sub>d</sub> ,                               | 1 Gbps                                      | 1.5 Gbps                                                                                                                             | 6.94 Gbps                                                                                                              |

| Area                                                               | 52.5 mm <sup>2</sup>                        | $3.39 \text{ mm}^2$                                                                                                                  | 5.39 mm <sup>2</sup>                                                                                                   |

| Frequency                                                          | 64 MHz                                      | 500 MHz                                                                                                                              | 100 MHz                                                                                                                |

| Nominal Power Dissipation                                          | 690 mW                                      | 156.5 mW                                                                                                                             | 75 mW                                                                                                                  |

| LDPC Code                                                          | Random LDPCr code,<br>rate 0.5, length 1024 | (4,30) array code of length 1830                                                                                                     | (3,6) array code of length 2082                                                                                        |

| CMOS Technology                                                    | 160 nm, 1.5V                                | 130 nm, 1.2V                                                                                                                         | 130 nm, 1.2V                                                                                                           |

| Decoding Schedule                                                  | TPMP, SP, it <sub>max</sub> =64             | TPMP, SP, it <sub>max</sub> =20                                                                                                      | TDMP, OMS, it <sub>max</sub> =10                                                                                       |

| Area Efficiency for t <sub>d</sub> ,                               | 19 Mbps/mm <sup>2</sup>                     | 442.4 Mbps/mm2                                                                                                                       | 1288 Mbps/mm <sup>2</sup>                                                                                              |

| Energy Efficiency for t <sub>d</sub> ,                             | 10.1 pJ/Bit/Iteration                       | 5.6 pJ/Bit/Iteration                                                                                                                 | 1.1 pJ/Bit/Iteration                                                                                                   |

| Est Area for 180 nm                                                | 66.4 mm <sup>2</sup>                        | 6.5 mm <sup>2</sup>                                                                                                                  | 10.1 mm <sup>2</sup>                                                                                                   |

| Est Frequency for 180 nm                                           | 56.8 MHz                                    | 360 MHZ                                                                                                                              | 72 MHz                                                                                                                 |

| Est Decoded Throughput t <sub>d</sub> , 180 nm                     | 887.5 Mbps                                  | 1.08 Gbps                                                                                                                            | 4.98 Gbps                                                                                                              |

| Est Area efficiency for t <sub>d</sub> , 180 nm                    | 13.36 Mbps/mm <sup>2</sup>                  | 166.1 Mbps/mm2                                                                                                                       | 493 Mbps/mm <sup>2</sup>                                                                                               |

| Est Energy efficiency for t <sub>d</sub> , 180 nm                  | 14.5 pJ/Bit/Iteration                       | 12.6 pJ/Bit/Iteration                                                                                                                | 4.8 pJ/Bit/Iteration                                                                                                   |

| Scalability of Design for other code parameters and longer lengths | No                                          | Yes                                                                                                                                  | Yes                                                                                                                    |

| Application                                                        | Fixed code application                      | Very High throughput<br>and low error-floor<br>applications such as<br>magnetic recording<br>channels, Ethernet and<br>optical links | Very High throughput and low error-floor applications such as magnetic recording channels, Ethernet and optical links. |

| Bit error rate Performance                                         | Good                                        | Good                                                                                                                                 | Good                                                                                                                   |

By examining the above implementation results for multi-rate architectures, we can conclude that irregular QC LDPC codes perform well and also their implementation complexity is less among the above 3 architectures. The implementation for irregular codes is more efficient as fewer number of non-zero blocks in the parity check matrix are needed to achieve excellent BER performance close to the capacity. Note that the underlying data flow graph for both regular QC-LDPC codes (Chapter VI) and irregular QC-LDPC codes (Chapter VII) is the same. This new data flow graph has several advantages which are discussed more fully in Chapters VI and VII. Scheduling of layered decoding, out-of-order processing, and bypassing techniques are employed to deal with irregularity. This is discussed fully in Chapter VII.

By examining the above implementation results, we can conclude that parallel TDMP architecture for array QC LDPC codes have the least complexity for very high throughput applications. A parallel layered architecture for irregular QC-LDPC codes can also be implemented based on this. However, the routing will be a problem and in addition irregular QC-LDPC will have a high error floor phenomenon. All of the above architectures are described in the following chapters.

In summary, the multi-rate and fixed code LDPC decoder architectures described in this dissertation achieve the best reported energy and area efficiencies while achieving the highest throughputs. The foundation of these architectures is based on minimizing the message passing and computation requirements by performing a thorough and systematic study.

#### **CHAPTER II**

# **OUASI-CYCLIC LOW-DENSITY PARITY-CHECK CODES AND DECODING**

# 2.1. Introduction

LDPC codes are linear block codes described by an  $m \times n$  sparse parity check matrix H. LDPC codes are well represented by bipartite graphs. One set of nodes, the variable or bit nodes correspond to elements of the code word and other set of nodes, viz. check nodes, correspond to the set of parity check constraints satisfied by the code words. Typically the edge connections are chosen at random. The error correction capability of the LDPC code is improved if cycles of short length are avoided in the graph. In a (r,c)regular code, each of the *n* bit nodes  $(b_1, b_2, ..., b_n)$  has connections to *r* check nodes and each of the m check nodes  $(c_1, c_2, ..., c_m)$  has connections to c bit nodes. In an irregular LDPC code, the check node degree is not uniform. Similarly the variable node degree is not uniform. We focus on the construction which structures the parity check matrix H into blocks of  $p \times p$  matrices such that: 1. a bit in a block participates in only one check equation in the block and 2. each check equation in the block involves only one bit from the block. These LDPC codes are termed as Quasi cyclic LDPC codes: Cyclic shift of code word by p results in another code word. Here p is the size of square matrix which is either a zero matrix or circulant matrix. This is a generalization of cyclic code in which cyclic shift of code word by 1 results in another code word.

# 2.2. Cyclotomic Cosets

One method to perform this construction is through cyclotomic cosets [49]. Another method is to achieve this property by employing random bit filling algorithm (for low

rate codes such as rate ½ codes) and deterministic constructions (for high rate codes such as rate 8/9 codes) [9]-[11]. The work [49] reports no performance degradation for a (3, 5) - LDPC code of length 1055, rate 0.4; constructed from cyclotomic cossets. The H matrix can be constructed with filling the matrices obtained by permuting identity matrix by the appropriate shift coefficients [49]. Say  $B_{j,k} \, \forall j = 1,2...r; k = 1,2,...c$  is a  $p \times p$  matrix, located at the  $j^{th}$  block row and  $k^{th}$  block column of H matrix. The scalar value s(j,k) denotes the shift applied to  $I_{p\times p}$  identity matrix to obtain the  $(j,k)^{th}$  block,  $B_{j,k}$ , and the rows in the  $I_{p\times p}$  identity matrix are cyclically shifted to the right s(j,k) positions for  $s(j,k) \in \{0,1,2,...,p-1\}$ . Let us define s as a s and s shift coefficient matrix in which

$$S_{j,k} = s(j,k) \ \forall j = 1,2..r; k = 1,2,..c \ .$$

(2.1)

The cyclotomic cosset containing the integer s is the set  $\{s, sq, sq^2, ..., sq^{m_s-1}\}$  where  $m_s$  is the smallest positive integer satisfying  $sq^{m_s} \equiv s \pmod{p}$  and q satisfies the relation  $q^c = 1 \pmod{p}$ . If c = 5, r = 3 and the desired length of code is in the vicinity of 1020. We find by trial and error that the values p = 211 and q = 71 result in cyclotomic cossets and the resulting code length n is 1055 (= cp). One possible construction for S is

$$\begin{bmatrix} Cosset_1 \\ Cosset_r \end{bmatrix} .SoS_{3\times 5} = \begin{bmatrix} 2 & 3 & 110 & 142 & 165 \\ 5 & 64 & 96 & 113 & 144 \\ 7 & 50 & 75 & 116 & 174 \end{bmatrix}$$

The H matrix can be now easily constructed with filling the matrices obtained by permuting  $I_{211\times211}$  matrix by the above shift coefficients. So an H matrix, in this construction, can be completely characterized by these two simple matrices viz.  $I_{p\times p}$  and

$S_{cxr}$ . To define H matrix, we start with fixing c, r and finding an appropriate p and shift coefficient matrix S such that the BER performance is maintained when compared to a random construction.

# 2.3. Array LDPC Codes

The reader is referred to [9]-[10], [36], [50-54] for a comprehensive treatment on array LDPC codes. The array LDPC parity-check matrix is specified by three parameters: a prime number p and two integers k, and j such that j, k < p.

It is given by,

$$H_{A} = \begin{bmatrix} I & I & I & \cdots & I \\ I & \alpha & \alpha^{2} & \dots & \alpha^{k-1} \\ I & \alpha^{2} & \alpha^{4} & \dots & \alpha^{2(k-1)} \\ \vdots & \vdots & \vdots & & \vdots \\ I & \alpha^{j-1} & \alpha^{(j-1)2} & \cdots & \alpha^{(j-1)(k-1)} \end{bmatrix}$$

(2.2)

where I is the  $p \times p$  identity matrix, and  $\alpha$  is a  $p \times p$  permutation matrix representing a single left or right cyclic shift of I. Power of  $\alpha$  in H denote multiple cyclic shifts, with the number of shifts given by the value of the exponent. In the following discussion, we use the  $\alpha$  as a  $p \times p$  permutation matrix representing a single left cyclic shift of I.

# 2.4. Rate-compatible Array LDPC Codes

Rate-compatible array LDPC codes are a modified version of the above for efficient encoding and multi-rate compatibility in [10] and their H matrix has the following structure

$$H = \begin{bmatrix} I & I & I & \cdots & I & I & \cdots & I \\ O & I & \alpha & \cdots & \alpha^{j-2} & \alpha^{j-1} & & \alpha^{k-2} \\ O & O & I & \cdots & \alpha^{2(j-3)} & \alpha^{2(j-2)} & & \alpha^{2(k-3)} \\ \vdots & \vdots & \vdots & \ddots & \vdots & \vdots & \vdots \\ O & O & \cdots & \cdots & I & \alpha^{(j-1)} & \cdots & \alpha^{(j-1)(k-j)} \end{bmatrix}$$

(2.3)

where O is the  $p \times p$  null matrix. The LDPC codes defined by H in (2.3) have a codeword length M = jp, number of parity-checks M = kp, and an information block length K = (k - j)p. The family of rate-compatible codes is obtained by successively puncturing the left most p columns, and the topmost p rows. According to this construction, a rate-compatible code within a family can be uniquely specified by a single parameter, say, q with  $0 < q \le j - 2$ . To have a wide range of rate-compatible codes, we can also fix j, p, and select different values for the parameter k. Since all the codes share the same base matrix size p; the same hardware implementation can be used. It is worth mentioning that this specific form is suitable for efficient linear-time LDPC encoding [10]. The systematic encoding procedure is carried out by associating the first N - K columns of H with parity bits, and the remaining K columns with information bits.

# 2.5. Irregular Quasi-Cyclic LDPC Codes (Block LDPC Codes)

The block irregular LDPC codes have competitive performance and provide flexibility and low encoding/decoding complexity [12]-[13]. The entire H matrix is composed of the same style of blocks with different cyclic shifts, which allows structured decoding and reduces decoder implementation complexity. For the LDPC codes proposed for IEEE 802.16e, each base H matrix in block LDPC codes has 24 columns, simplifying the implementation. Having the same number of columns between code rates minimizes the number of different expansion factors that have to be supported. There are four rates supported: 1/2, 2/3, 3/4, and 5/6, and the base H matrix for these code rates are defined by systematic fundamental LDPC code of  $M_b$ -by- $N_b$  where  $M_b$  is the number of rows in the base matrix and  $N_b$  is the number of columns in the base matrix. The following base matrices are specified: 12 x 24, 8 x 24, 6 x 24, and 4 x 24. The base model matrix is defined for the largest code length (N = 2304) of each code rate. The set of shifts in the base model matrix are used to determine the shift sizes for all other code lengths of the same code rate. Each base model matrix has 24 (=  $N_b$ ) block columns and  $M_b$  block rows. The expansion factor z is equal to N/24 for code length N. The expansion factor varies from 24 to 96 in the increments of 4, yielding codes of different length. For instance, the code with length N = 2304 has the expansion factor z=96 [10]. Thus, each LDPC code in the set of WiMax LDPC codes is defined by a matrix H as:

$$H = \begin{bmatrix} P_{1,1} & P_{1,2} & \cdots & P_{1,N_b} \\ P_{2,1} & P_{2,2} & \cdots & P_{2,N_b} \\ \cdots & \cdots & \cdots & \cdots \\ P_{M_b,1} & P_{M_b,2} & \cdots & P_{M_b,N_b} \end{bmatrix} = P^{H_b}$$

(2.4)

where  $P_{i,j}$  is one of a set of z-by-z cyclically right shifted identity matrices or a z-by-z zero matrix. Each 1 in the base matrix  $H_b$  is replaced by a permuted identity matrix while each 0 in  $H_b$  is replaced by a negative value to denote a z-by-z zero matrix.

# 2.6. Irregular QC LDPC Codes for Other Wireless Standards (802,11n and 802.20)

The LDPC codes proposed in other wireless standards area similar to the above structure. But the base matrices are different. So the same architectures can be re-used with minor changes.

# 2.7. Two Phase Message Passing (TPMP) and Decoding of LDPC

A quantitative performance comparison for different check updates [26]-[35] was given by Chen et al. [32]. Their research showed that the performance loss for OMS decoding with 5-bit quantization is less than 0.1dB in SNR compared with that of optimal floating point SP (Sum of Products) and BCJR. Assume binary phase shift keying (BPSK) modulation (a 1 is mapped to -1 and a 0 is mapped to 1) over an additive white Gaussian noise (AWGN) channel. The received values  $y_n$  are Gaussian with mean  $x_n = \pm 1$  and variance  $\sigma^2$ . The reliability messages used in belief propagation (BP)-based offset min-sum algorithm can be computed in two phases: 1. check-node processing and 2. variable-node processing. The two operations are repeated iteratively until the decoding criterion is satisfied. This is also referred to as standard message passing or two-phase message passing (TPMP). For the  $i^{th}$  iteration,  $Q_{nm}^{(i)}$  is the message from variable node n to check node m,  $R_{mn}^{(i)}$  is the message from check node m to variable

node n, M(n) is the set of the neighboring check nodes for variable node n, and N(m) is the set of the neighboring variable nodes for check node m.

The message passing for TPMP is described in the following three steps as given in [32] to facilitate the discussion on TDMP in the next section:

Step 1. Check-node processing: for each m and  $n \in N(m)$ ,

Sum of Products (SP) Check-node update

$$R_{mn}^{(i)} = \psi^{-1} \left[ \sum_{n' \in N(m) \setminus n} \psi(Q_{n'm}^{(i)}) \right] . \delta_{mn}^{(i)}$$

(2.5)

Here  $\psi(x) = -\log(\tanh(x/2))$  is the Gallager's function which is invariant under its inverse.

Offset min-sum(OMS) Check-node update (approximation to (2.5))

$$R_{mn}^{(i)} = \delta_{mn}^{(i)} \max(\kappa_{mn}^{(i)} - \beta, 0), \qquad (2.6)$$

$$\kappa_{mn}^{(i)} = \left| R_{mn}^{(i)} \right| = \min_{n' \in \mathbb{N}(m) \setminus n} \left| Q_{n'm}^{(i-1)} \right|. \tag{2.7}$$

where  $\beta$  is a positive constant and depends on the code parameters [32]. For (3, 6) rate 0.5 array LDPC code,  $\beta$  is computed as 0.15 using the density evolution technique presented in [12].

The sign of check-node message  $R_{mn}^{(i)}$  is defined as

$$\delta_{mn}^{(i)} = \left(\prod_{n' \in \mathcal{N}(m) \setminus n} \operatorname{sgn}\left(Q_{n'm}^{(i-1)}\right)\right), \tag{2.8}$$

Step 2. Variable-node processing: for each n and  $m \in N(n)$ ,

$$Q_{nm}^{(i)} = L_n^{(0)} + \sum_{m' \in M(m) \setminus m} R_{m'n}^{(i)}, \qquad (2.9)$$

where the log-likelihood ratio of bit n is  $L_n^{(0)} = y_n$ .

Step 3. Decision: for final decoding

$$P_n = L_n^{(0)} + \sum_{m \in M(n)} R_{mn}^{(i)} . \tag{2.10}$$

A hard decision is taken by setting  $\hat{x}_n = 0$  if  $P_n(x_n) \ge 0$ , and  $\hat{x}_n = 1$  if  $P_n(x_n) < 0$ . If,  $\hat{x}H^T = 0$ , the decoding process is finished with  $\hat{x}_n$  as the decoder output; otherwise, repeat steps (1-3). If the decoding process doesn't end within predefined maximum number of iterations,  $it_{\text{max}}$ , stop and output an error message flag and proceed to the decoding of the next data frame.

# 2.8. Turbo Decoding Message Passing (TDMP) or Layered Decoding

In TDMP, the LDPC code with j block rows can be viewed as concatenation of j layers or constituent sub-codes similar to observations made for AA-LDPC codes in [20]. After the check-node processing is finished for one block row, the messages are immediately used to update the variable nodes (in step 2, above), whose results are then provided for processing the next block row of check nodes (in step 1, above).

#### **CHAPTER III**

# MULTI-RATE TPMP ARCHITECTURE FOR REGULAR QC-LDPC CODES

# 3.1. Introduction

This chapter provides efficient multi-rate TPMP architectures for regular QC-LDPC codes. This architecture is targeted for Cyclotomic coset based LDPC and array LDPC. This architecture works for rate compatible array LDPC codes with a minor change in implementation to accommodate the slight irregularity in the parity check matrix.

The QC-LDPC codes are discussed in Chapter II. For the continuity of presentation, some of the material discussed in Chapter II is briefly summarized in this section. The H matrix can be constructed with filling in with matrices obtained by permuting identity matrix by the appropriate shift coefficients [49]. Say  $B_{j,k} \ \forall j=1,2...r; k=1,2,...c$  is a  $p\times p$  matrix, located at the  $j^{th}$  block row and  $k^{th}$  block column of H matrix. The scalar value s(j,k) denotes the shift applied to  $I_{p\times p}$  identity matrix to obtain the  $(j,k)^{th}$  block,  $B_{j,k}$ , and the rows in the  $I_{p\times p}$  identity matrix are cyclically shifted to the right s(j,k) positions for  $s(j,k) \in \{0,1,2,...,p-1\}$ . Let us define S as a  $c\times r$  shift coefficient matrix in which

$$S_{j,k} = s(j,k) \ \forall j = 1,2..r; k = 1,2,..c.$$

(3.1)

So an H matrix, in this construction, can be completely characterized by these two simple matrices viz.  $I_{p \times p}$  and  $S_{c \times r}$ . To define H matrix, we start with fixing c, r and

finding an appropriate p and shift coefficient matrix S such that the BER performance is maintained when compared to a random construction.

For example if c = 5, r = 3 and p = 211 the use of cyclotomic cosets [49] results in the following shift coefficient matrix for the code of length 1055(n = cp).

$$S_{3\times5} = \begin{bmatrix} 2 & 3 & 110 & 142 & 165 \\ 5 & 64 & 96 & 113 & 144 \\ 7 & 50 & 75 & 116 & 174 \end{bmatrix}$$

(3.2)

For regular array LDPC codes with similar parameters, this is given by

$$S_{3\times5} = \begin{bmatrix} 0 & 0 & 0 & 0 & 0 \\ 0 & 1 & 2 & 3 & 4 \\ 0 & 2 & 4 & 6 & 8 \end{bmatrix}$$

# 3.2. Block Message Independence Property for Regular QC-LDPC Codes

The reliability messages used in Gallager's Belief Propagation algorithm can be computed in two phases viz., check-node processing (3.3) and variable node processing (3.4) and this is repeated iteratively till the decoding criterion is satisfied (see Chapter II). The message passing equations are given by

$$R_{cj,bi} = \psi^{-1} \left[ \left( \sum_{i'=Row[cj][1]}^{Row[cj][c]} \psi(Q_{i',cj}) \right) - \psi(Q_{bi,cj}) \right] \mathcal{S}(cj,bi)$$

$$(3.3)$$

$$Q_{bi,cj} = \begin{pmatrix} \sum_{j=Col[bi][i]}^{Col[bi][r]} R_{j,bi} \\ \end{pmatrix} - R_{cj,bi} + \wedge (bi)$$

(3.4)

where  $R_{cj,bi}$  is the message from check  $c_j$  to bit  $b_i$ ,  $Q_{bi,cj}$  is the message from bit  $b_i$  to check  $c_j$ ,  $\psi(x) = -\log(\tanh(x/2))$  is the Gallager's function which is invariant under its inverse,  $\delta(cj,bi)$  is  $\pm 1$  and is given by

$$\delta(cj,bi) = \left(\operatorname{sgn}(Q_{bi,cj}) \prod_{i \in Row[cj]} \operatorname{sgn}(Q_{i,cj})\right) (-1)^{|Row[cj]|}$$

(3.5)

$(-1)^{|Row[cj]|} = 1$  for codes constructed with even parity.  $\land (bi)$  is the intrinsic reliability metric of bit  $i \cdot Row[c_j][1...c]$  ( $Col[b_i][1...r]$ ) gives the locations of bits (checks) connected to the check node  $c_j$  (bit node  $b_i$ ).

We can represent R and Q messages by the following matrices for deriving the new data independence property. This arrangement is similar to physical message storage employed in [16] except that these matrices are not really stored in the proposed architecture.

$$Rm = \begin{bmatrix} R_{1,Row[1][1]} & R_{1,Row[1][2]} & \dots & R_{1,Row[1][c]} \\ R_{2,Row[2][1]} & R_{2,Row[2][2]} & \dots & R_{2,Row[2][c]} \\ \vdots & \vdots & \vdots & \vdots \\ R_{p\bullet r,Row[p\bullet r][1]} & R_{p\bullet r,Row[p\bullet r][1]} & \dots & R_{p\bullet r,Row[p\bullet r][c]} \end{bmatrix}$$

$$Qm = \begin{bmatrix} Q_{1,Col[1][1]} & Q_{1,Col[1][2]} & \cdots & Q_{1,Col[1][r]} \\ Q_{2,Col[2][1]} & Q_{2,Col[2][2]} & \cdots & Q_{2,Col[2][r]} \\ \vdots & \vdots & \vdots & \vdots \\ Q_{p \bullet c,Col[p \bullet c][1]} & Q_{p \bullet c,Col[p \bullet c][2]} & \cdots & Q_{p \bullet c,Col[p \bullet c][r]} \end{bmatrix}$$

(3.6)

If we employ the partitioning of H matrix into r rows and c columns of p x p matrices, the R and Q messages in a p x p block can be processed simultaneously. The recent architectures [17]-[18], [37], [49] exploit this property to store messages in the memory partitioned into p independent memory banks and employ p copies of message computation units.

We now represent the R and Q messages in a p x p block as p x 1 vectors

$$\vec{R}_{j,k} = \left[ Rm_{1+(j-1)p,k}, ..., Rm_{l+(j-1)p,k}, ..., Rm_{p+(j-1)p,k} \right]^{T}$$

$$\vec{Q}_{k,j} = \left[ Qm_{1+(k-1)p,j}, ..., Qm_{l+(k-1)p,j}, ..., Qm_{p+(k-1)p,j} \right]^{T}$$

(3.7)

$$l = 1,2,..., p \ \forall j = 1,2,..., r, k = 1,2,..., c$$

Then R and Q messages in block matrix format are:

$$\vec{R} = \begin{bmatrix} \vec{R}_{1,1} & \vec{R}_{1,2} & \dots & \vec{R}_{1,c} \\ \vec{R}_{2,1} & \vec{R}_{2,1} & \dots & \vec{R}_{2,c} \\ \vdots & \vdots & \vdots & \vdots \\ \vec{R}_{r,1} & \vec{R}_{r,1} & \dots & \vec{R}_{r,c} \end{bmatrix}$$

$$\vec{Q} = \begin{bmatrix} \vec{Q}_{1,1} & \vec{Q}_{1,2} & \dots & \vec{Q}_{1,r} \\ \vec{Q}_{2,1} & \vec{Q}_{2,1} & \dots & \vec{Q}_{2,r} \\ \vdots & \vdots & \vdots & \vdots \\ \vec{Q}_{c,1} & \vec{Q}_{c,1} & \dots & \vec{Q}_{c,r} \end{bmatrix}$$

(3.8)

Now the Gallager's equations can be written as

$$\vec{R}_{j,k} = \psi \left[ \left( \sum_{k=1}^{c} \psi \left( \vec{Q}_{k,j}^{s(j,k)} \right) \right) - \psi \left( \vec{Q}_{k,j}^{s(j,k)} \right) \right] \cdot \vec{\mathcal{S}}_{k,j}$$

(3.9)

$$\vec{Q}_{k,j} = \left(\sum_{j=1}^{r} \vec{R}_{j,k}^{p-s(j,k)}\right) - \vec{R}_{j,k}^{p-s(j,k)} + \vec{\wedge}_{k}$$

(3.10)

$$\vec{\delta}_{k,j} = \left( \operatorname{sgn}(\vec{Q}_{k,j}) \prod_{k=1}^{r} \operatorname{sgn}(\vec{Q}^{s(k,j)}_{k,j}) \right)$$

(3.11)

$$\vec{\wedge}_k = \left[ \wedge \left( 1 + (k-1)p \right), \dots, \wedge \left( p + (k-1)p \right) \right] \tag{3.12}$$

where  $\vec{Q}_{k,j}^{s(j,k)}(\vec{R}_{j,k}^{p-s(j,k)})$  is the modified  $p \times 1$  vector  $\vec{Q}_{k,j}(\vec{R}_{j,k})$ , whose elements are circularly shifted in location by the amount s(j,k) (p-s(j,k)).

Say

$$\vec{A}_{j} = \sum_{k=1}^{c} \psi(\vec{Q}_{k,j}^{s(j,k)}), \ \vec{B}_{k,j} = \psi(\vec{Q}_{k,j}^{s(j,k)})$$

(3.13)

$$\vec{C}_k = \sum_{j=1}^r \vec{R}_{j,k}^{p-s(j,k)}, \vec{D}_{j,k} = \vec{R}_{j,k}^{p-s(j,k)}$$

(3.14)

Now

$$\vec{R}_{j,k} = \psi \left[ \vec{A}_j - \vec{B}_{k,j} \right] \vec{\delta}_{k,j} \tag{3.15}$$

$$\vec{Q}_{k,j} = \vec{C}_k - \vec{D}_{j,k} + \vec{\wedge}_k \tag{3.16}$$

We can observe that the  $j^{th}$  block row of R messages is only dependent on the  $j^{th}$  block column of Q messages and similarly the  $k^{th}$  block row of Q messages is only dependent on the  $k^{th}$  block column of R messages. Only one class of messages has to be stored if we schedule the pipeline of the R and Q message computation unit such that either one of R and Q message units output the block row at once and multiplexing the other units schedule such that it is able to produce the output in block column fashion.

If p Check to Bit serial message computation units, which have internal FIFOs of  $\operatorname{size}(c\times(r-1)+1)\approx c.r$  are employed, this is approximately equivalent to storage requirement of one class of  $\operatorname{messages}(p.c.r)$ . We do not need any additional memory for storing R and Q messages. By scheduling we can efficiently use the internal memory of the computational units.

## 3.3. Architecture

For the example (3, 5) - LDPC code of length 1055 described in Section 3.2, r = 3, c = 5 and p = 211. We can generalize the following discussion to any LDPC code with similar structure. A multi-rate architecture is obtained by designing the architecture such that it can support the maximum values of r and c.

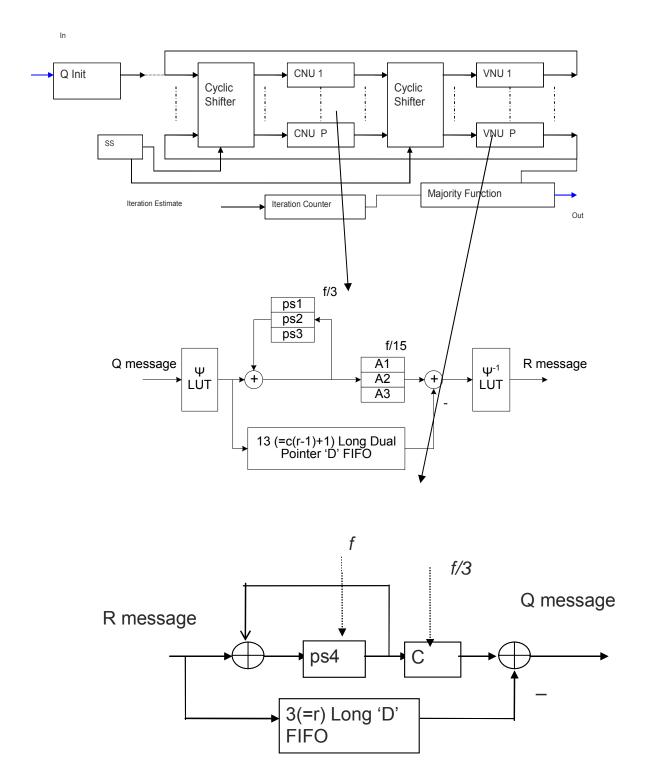

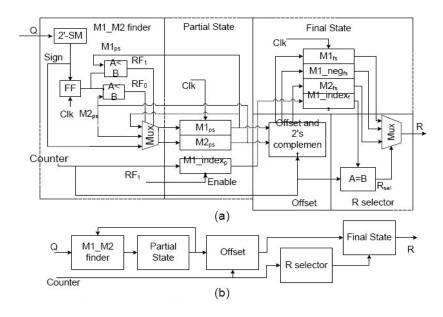

According to the observation made in Section 3.2, the pipeline is designed such that Q messages are produced block row wise and R messages are produced in block column fashion (Fig. 3.1). Initially the Q messages are available in row wise as they are set to soft log likelihood information of the bits coming in chunks of p (10). The Q Initializer (Q Init) is an SRAM of size n+p and holds the  $\wedge$  values of two different frames. It can supply p intrinsic values to the BCUs each clock cycle and also can simultaneously read p intrinsic values from the channel at the start of iterations of the next frame. The data path of the design is set to 5 bits.  $\psi$  and  $\psi^{-1}$  are implemented based on uniform quantization and according to the scheme of [12]. The maximum number of iterations is set to 20 and the iterations will stop when the decoded vector d (using Majority function of Bit to check messages)satisfies the relation  $dH^T = 0$ .

The p by p cyclic shifter is constructed with two input - two output switches and log2(p) stages of p/2 switches are used. The Switching Sequence (SS) unit supplies the binary sequences to toggle switches in order to produce the shifts in the matrix  $S_{3x5}(2)$ . The cyclic shifters of R and Q messages will receive sequences column wise corresponding to the shifts (2, 5, 7, 3... 174) for cyclic shift up and down respectively (refer to (3.9) and (3.10)). The check node processing array is composed of p serial Check Node Units (CNU) which computes the partial sum for each block row in a multiplexed fashion to produce the R messages in block column fashion. The registers ps1, ps2 and ps3 correspond to the partial sum for block row 1, 2 and 3 respectively.

Fig. 3.1. Block diagram of the decoder architecture

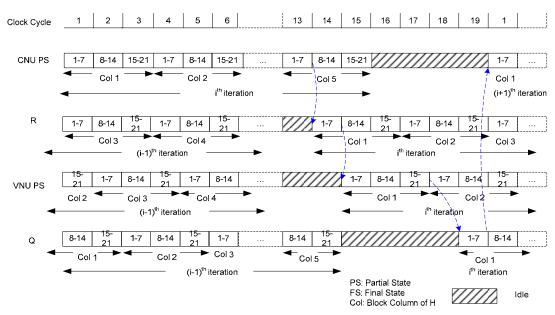

Fig. 3.2. Pipeline of the decoder

Table 3.1.

Occupation of resources for a decoding iteration in terms of clock cycles. (Shown for two iterations.)

| I | CBU Adders | CBU      | Sub | BCU Adders | BCU      | Sub |

|---|------------|----------|-----|------------|----------|-----|

|   |            | tractors |     |            | tractors |     |

| 1 | 1-15       | 14-28    |     | 15-29      | 19-33    |     |

| 2 | 20-34      | 35-49    |     | 34-48      | 38-52    |     |

I=Iteration Number.

Table 3.2.

Snapshot of partial sum registers in p CNU s operating in parallel to compute p R messages

| Clock, | 13,1                                                                  | 15,1                                                      | 22,1                                                             |

|--------|-----------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------|

| I      |                                                                       |                                                           |                                                                  |

| psĪ    | $\sum_{k=1}^5 \psi \left( \vec{Q}_{k,1}^{s(1,k)} \right)$             | $\sum_{k=1}^5 \psi \Big( \vec{Q}_{k,1}^{s(1,k)} \Big)$    | $\sum_{k=1}^1 \psi \Big( \vec{\mathcal{Q}}_{k,1}^{s(1,k)} \Big)$ |

|        | $\sum_{k=1}^{4} \psi \left( \vec{Q}_{k,2}^{s(2,k)} \right)$           |                                                           | 0                                                                |

| ps3    | $\sum_{k=1}^{3} \psi \left( \vec{\mathcal{Q}}_{k,3}^{s(3,k)} \right)$ | $\sum_{k=1}^5 \psi \left( \vec{Q}_{k,3}^{s(3,k)} \right)$ | 0                                                                |

The CNU B FIFO corresponds to (3.13) stores the intermediate computations. Its snapshot at 15<sup>th</sup> clock cycle is  $[\vec{B}_{5,3}, \vec{B}_{5,2}, \vec{B}_{5,1}, ..., \vec{B}_{1,1}]$ . The registers A1, A2 and A3 (which correspond to (3.13)) latch the ps1, ps2 and ps3 (Table 3.3) in 14,15 and 16 clock cycles respectively and one of these values (from 14- 28<sup>th</sup> clock cycle for 1<sup>st</sup> iteration) will be selected sequentially as one of the inputs to the subtractor and each subtraction operation during this period produces R messages in block column fashion. The variable node processing array is composed of p serial Variable Node Units (VNU) which compute the partial sum ps4 for each block row in a sequential fashion to produce the Q messages in block row fashion. The pipeline is shown in Fig. 3.2.

Table 3.3.

Snapshot of partial sum registers in p VNUs operating in parallel to compute p Q messages

| Clock,I | 15,1                                      | 17,1                                      | 29,1                                      |

|---------|-------------------------------------------|-------------------------------------------|-------------------------------------------|

| ps4     | $\sum_{j=1}^{1} \vec{R}_{j,1}^{p-s(j,1)}$ | $\sum_{j=1}^{3} \vec{R}_{j,1}^{p-s(j,1)}$ | $\sum_{j=1}^{3} \vec{R}_{j,5}^{p-s(j,5)}$ |

The VNU D FIFO corresponds to (3.14). Its snapshot at  $17^{th}$  clock cycle is  $\left[\vec{R}_{1,1}, \vec{R}_{2,1}, \vec{R}_{3,1}\right]$  and at  $29^{th}$  clock cycle is  $\left[\vec{R}_{1,5}, \vec{R}_{2,5}, \vec{R}_{3,5}\right]$ . The register C (which corresponds to (314)) latch the ps4 (Table 3.4), every three clock cycles and is one of the inputs to the subtractor and each subtraction operation during this period produces Q messages in block row fashion.

While this architecture is targeted for regular array LDPC codes and cyclotomic coset based regular QC-LDPC codes, this architecture works for rate compatible array LDPC codes with a minor change in implementation to accommodate the slight irregularity in the parity check matrix. Note that due to the slight irregularity in rate-compatible array LDPC matrix, each block row l has a node degree j-l+1. The variable-nodes in each block column n has a node degree equal to  $\min(n, j)$ . We have to devise a simple control mechanism to address this irregularity. One simpler way to facilitate implementation is to assume that all the block rows have equal check-node degrees and set the check-node messages corresponding to null blocks in H matrix to zero in order not to affect the variable-node processing.  $\bar{R}_{l,n}^{(i)} = 0$  if n < l in each iteration

i. Similarly the variable-node messages belonging to the null blocks are always set to positive infinity in order not to affect the check-node processing.  $\bar{Q}_{l,n}^{(i)} = \infty$  if n < l. For check-node update, the message with maximum reliability won't affect the CNU output.

# 3.4. Performance Comparison

## 3.4.1. Memory Advantage

Table 3.4 shows the comparison with the related work. The memory savings are 75% and savings in memory accesses are 66% when compared to [16]. When compared to [17], [20] the memory accesses are 50% less while the memory requirement is almost the same and this results in better low power characteristic for the proposed architecture. For example [20] reported that the NA-Mm accounts for 50% of their decoder power.