#

A Dissertation

by

SHIYAN HU

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2008

Major Subject: Computer Engineering

#

A Dissertation

by

SHIYAN HU

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

#### Approved by:

Chair of Committee, Jiang Hu

Committee Members, Charles J. Alpert

Mosong Cheng Donald K. Friesen

Weiping Shi

Head of Department, Costas N.Georghiades

May 2008

Major Subject: Computer Engineering

#### ABSTRACT

Algorithmic Techniques for Nanometer VLSI Design and Manufacturing Closure.

(May 2008)

Shiyan Hu, B.S., Beijing University of Aeronautics and Astronautics;

M.S., Polytechnic University, Brooklyn, NY

Chair of Advisory Committee: Dr. Jiang Hu

As Very Large Scale Integration (VLSI) technology moves to the nanoscale regime, design and manufacturing closure becomes very difficult to achieve due to increasing chip and power density. Imperfections due to process, voltage and temperature variations aggravate the problem. Uncertainty in electrical characteristic of individual device and wire may cause significant performance deviations or even functional failures. These impose tremendous challenges to the continuation of Moore's law as well as the growth of semiconductor industry.

Efforts are needed in both deterministic design stage and variation-aware design stage. This research proposes various innovative algorithms to address both stages for obtaining a design with high frequency, low power and high robustness. For deterministic optimizations, new buffer insertion and gate sizing techniques are proposed. For variation-aware optimizations, new lithography-driven and post-silicon tuning-driven design techniques are proposed.

For buffer insertion, a new slew buffering formulation is presented and is proved to be NP-hard. Despite this, a highly efficient algorithm which runs  $> 90 \times$  faster than the best alternatives is proposed. The algorithm is also extended to handle continuous buffer locations and blockages.

For gate sizing, a new algorithm is proposed to handle discrete gate library in contrast to unrealistic continuous gate library assumed by most existing algorithms.

Our approach is a continuous solution guided dynamic programming approach, which integrates the high solution quality of dynamic programming with the short runtime of rounding continuous solution.

For lithography-driven optimization, the problem of cell placement considering manufacturability is studied. Three algorithms are proposed to handle cell flipping and relocation. They are based on dynamic programming and graph theoretic approaches, and can provide different tradeoff between variation reduction and wirelength increase.

For post-silicon tuning-driven optimization, the problem of unified adaptivity optimization on logical and clock signal tuning is studied, which enables us to significantly save resources. The new algorithm is based on a novel linear programming formulation which is solved by an advanced robust linear programming technique. The continuous solution is then discretized using binary search accelerated dynamic programming, batch based optimization, and Latin Hypercube sampling based fast simulation.

To my parents Changxin Hu and Xiaoyu Hu.

#### ACKNOWLEDGMENTS

I would like to express my great thanks to my advisor Dr. Jiang Hu for his kind guidance for my Ph.D. study. Dr. Jiang Hu introduced me the field of VLSI Computer-Aided Design. He shared his deep knowledge and research experience with me and constantly provided invaluable advise to me. I truly appreciate all of his academic, moral and financial support to me.

Many thanks to my Ph.D. dissertation committee members, Dr. Charles Alpert, Dr. Mosong Cheng, Dr. Donald Friesen, Dr. Jiang Hu and Dr. Weiping Shi. I really appreciate their invaluable assistance to my dissertation.

In addition, I would like to thank Dr. Weiping Shi for instructing great courses on physical design where I learned a lot. He also spent much time in discussing various CAD problems with me. I really appreciate Dr. Charles Alpert in IBM Austin Research Lab for being my mentor and manager when I was an intern there. He shared his great academic and industrial experience with me. Special thanks to Dr. Mosong Cheng and Dr. Donald Friesen for giving many highly valuable comments on my preliminary examination, proposal and dissertation. I would also like to thank the graduate students Ganesh Venkataraman, Zhuo Feng, Pratik Shah, Zhanyuan Jiang and Nikhil Jayakumar in Computer Engineering group at Texas A&M University for their helps on my research.

Last, but not least, I would like to express my greatest gratefulness to my family for their long-lasting encouragement and support.

## TABLE OF CONTENTS

| CHAPTER |                                                                                                                                      | Page |

|---------|--------------------------------------------------------------------------------------------------------------------------------------|------|

| I       | INTRODUCTION                                                                                                                         | 1    |

|         | A. Preliminaries and Motivation                                                                                                      | 1    |

|         | B. Contribution                                                                                                                      | 4    |

|         | Cost Buffering                                                                                                                       | 4    |

|         | 2. Gate Sizing for Cell Library-Based Designs                                                                                        |      |

|         | <ul><li>3. Pattern Sensitive Placement for Manufacturability</li><li>4. Unified Adaptivity Optimization of Clock and Logic</li></ul> | 7    |

|         | Signals                                                                                                                              | 9    |

| II      | FAST ALGORITHMS FOR SLEW CONSTRAINED                                                                                                 |      |

|         | MINIMUM COST BUFFERING                                                                                                               | 11   |

|         | A. Introduction                                                                                                                      | 11   |

|         | B. Preliminaries                                                                                                                     | 15   |

|         | C. Complexity of Slew Buffering Problem                                                                                              | 18   |

|         | D. Slew Constrained Minimum Cost Buffering Algorithms $$                                                                             | 20   |

|         | 1. Overview of Classic Timing-Driven Buffering                                                                                       | 20   |

|         | 2. Discrete Slew Buffering Assuming Fixed Input Slew .                                                                               | 22   |

|         | a. Algorithm                                                                                                                         | 22   |

|         | b. Critical Differences from Timing Buffering                                                                                        | 24   |

|         | c. Implementation Experiences                                                                                                        | 25   |

|         | 3. Discrete Buffering without Input Slew Assumptions .                                                                               | 28   |

|         | a. Basic Modifications                                                                                                               | 28   |

|         | b. Reduction to Maximum Bipartite Matching                                                                                           | 30   |

|         | 4. Continuous Slew Buffering                                                                                                         | 32   |

|         | 5. Buffer Blockage Avoidance                                                                                                         | 37   |

|         | E. Discussion of Related Approaches                                                                                                  | 40   |

|         | 1. Minimum Cost Slew Constrained Timing Buffering                                                                                    | 40   |

|         | 2. Capacitance-Based Buffering                                                                                                       | 41   |

|         | F. Experimental Results                                                                                                              | 41   |

|         | 1. Experiment Setup                                                                                                                  | 41   |

|         | 2. Comparison with Timing Buffering                                                                                                  | 43   |

|         | 3. Slew Buffering with Non-Fixed Input Slew                                                                                          | 46   |

| CHAPTER |                                                                                                                                                                                                                                                                                                         | Page                                               |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|         | 4. Continuous Slew Buffering                                                                                                                                                                                                                                                                            | . 49<br>. 50                                       |

| III     | GATE SIZING FOR CELL LIBRARY-BASED DESIGNS                                                                                                                                                                                                                                                              | . 52                                               |

|         | A. Introduction B. Problem Formulation C. Optimization Methodology  1. Error Due to Nearest Rounding 2. Proposed Methodology D. Discretization Algorithm 1. Explore Gate Sizes Close to the Continuous Solution 2. Solution Pruning 3. Solution Clustering by LSH E. Experimental Results F. Conclusion | 54<br>55<br>55<br>58<br>58<br>61<br>62<br>65<br>68 |

| IV      | PATTERN SENSITIVE PLACEMENT FOR MANUFACTURABILITY                                                                                                                                                                                                                                                       | . 74                                               |

|         | A. Introduction                                                                                                                                                                                                                                                                                         | . 78<br>. 78                                       |

|         | 3. Lookup Table for Manufacturability Cost                                                                                                                                                                                                                                                              | . 82                                               |

|         | <ol> <li>Algorithmic Overview</li> <li>Solution Characterization</li> <li>Solution Propagation</li> <li>Solution Pruning</li> </ol>                                                                                                                                                                     | . 85<br>. 85                                       |

|         | <ul> <li>D. Single Row Optimization and Multiple Row Optimization</li> <li>1. Algorithmic Overview (Single Row Optimization)</li> <li>2. Unconstrained Optimal Manufacturability-Driven</li> </ul>                                                                                                      | . 88                                               |

|         | Placement                                                                                                                                                                                                                                                                                               | . 91                                               |

|         | E. Experimental Results                                                                                                                                                                                                                                                                                 | . 96                                               |

| CHAPTER |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page                                                                    |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

|         | <ol> <li>Experiment Setup</li> <li>Experiments with ISCAS'89 Benchmark Circuits</li> <li>Experiments with ISPD'04 Benchmark Circuits</li> <li>Conclusion</li> </ol>                                                                                                                                                                                                                                                                                                                                                                         | 96<br>97<br>100<br>102                                                  |

| V       | UNIFIED ADAPTIVITY OPTIMIZATION OF CLOCK AND LOGIC SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 105                                                                     |

|         | A. Introduction B. Preliminaries and Motivation C. Overall Flow D. Continuous Optimization 1. Linear Programming Formulation 2. Robust Linear Programming 3. Adaptive Application of Robust Linear Programming E. Discretization 1. Discretization PST Clock Buffers a. Solution Characterization b. Solution Propagation c. Acceleration by Pruning 2. Discretizing Logic Circuits 3. Fast Simulations for Timing Yield Estimation 4. Time Complexity F. Experiments 1. Continuous Adaptivity Optimization 2. Discretization C. Conclusion | 105 109 113 113 113 116 118 119 120 121 121 122 124 126 127 128 129 135 |

| VI      | CONCLUSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 136                                                                     |

|         | CES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                         |

| VITA    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 147                                                                     |

## LIST OF TABLES

| TABLE |                                                                                                                                                                                                        | Page |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| I     | Technology trend for VLSI chips [1]                                                                                                                                                                    | 1    |

| II    | C, Q values for sinks [19]                                                                                                                                                                             | 19   |

| III   | C, R, W values for each buffer type [19]                                                                                                                                                               | 20   |

| IV    | Comparison of discrete slew buffering (SB) and slew constrained timing buffering (VGL+S). #S refers to the average number of non-dominated solutions at driver. Slack is in ns. CPU time is in seconds | 43   |

| V     | Slew constrained buffering with pruning based on $(C, W)$ , CWB. #S: the number of non-dominated solutions at driver. Area Saving is obtained comparing to SB                                          | 45   |

| VI    | The comparison of SB and VGL+S+PSP (VGL+S incorporated with pre-buffer slack pruning [19]). Speed up refers to the runtime difference between SB and VGL+S+PSP                                         | 47   |

| VII   | Comparison of discrete slew buffering (SB) and slew constrained timing buffering (VGL+SB+PSP) on 100 large-degree nets. Slack is in $ns.$                                                              | 47   |

| VIII  | Results of slew buffering with non-fixed input slew. Area saving is obtained by comparing to SB. Degrad. refers to the slack degradation obtained by comparing to VGL+S                                | 48   |

| IX    | Results of continuous slew buffering. Area saving is obtained by comparing to SB. Degrad. refers to the slack degradation obtained by comparing to VGL+S                                               | 49   |

| X     | Handling blockage. Each net has 30% blockage area. Area saving is obtained by comparing to SB.                                                                                                         | 50   |

| TABLE | P                                                                                                                                                                                                                                                                                                  | Page |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| XI    | Capacitance-based buffering (CBB). Only a single typical buffer is used. Area saving is obtained by comparing to SB                                                                                                                                                                                | 50   |

| XII   | Comparisons using a library with 10 sizes per gate type. Timing constraints and slack are in $ps$ . CPU in seconds is runtime. Area refers to area cost. Area red. refers to the area reduction ratio between NEW and $[6]$                                                                        | 69   |

| XIII  | Comparisons using a sparser library with 6 sizes per gate type. Timing constraints and slack are in $ps$ . CPU in seconds is runtime. Area refers to area cost. Area red. refers to the area reduction ratio between NEW and $[6]$                                                                 | 69   |

| XIV   | Performance of each algorithm on ISCAS'89 benchmark circuits.  W.I. refers to the wirelength increase and V.D. refers to the variation reduction. CPU time is in seconds                                                                                                                           | 99   |

| XV    | Cell flipping using pruning technique in [51]                                                                                                                                                                                                                                                      | 101  |

| XVI   | Single Row Optimization results without considering wirelength constraint                                                                                                                                                                                                                          | 102  |

| XVII  | Statistics of ISPD'04 benchmark circuits [53]                                                                                                                                                                                                                                                      | 103  |

| XVIII | Performance of each algorithm on ISPD'04 benchmark circuits. CPU time is in seconds                                                                                                                                                                                                                | 104  |

| XIX   | Statistics of ISCAS'89 benchmark circuits. #Bk refers to the number of blocks and #Buf refers to the number of clock buffers                                                                                                                                                                       | 131  |

| XX    | Continuous optimizations on ISCAS'89 benchmark circuits. #Bk refers to the number of blocks and #Buf refers to the number of clock buffers. Area reduction is obtained by comparing the area of Our Discrete Solution with the minimum area of Logic Signal Adaptivity and Clock Signal Adaptivity | 132  |

| XXI   | Discrete Solutions for ISCAS'89 benchmark circuits with large tuning step. Runtime for computing nearest rounding and discrete solution includes the runtime for computing continuous solutions.  Area reduction and speedup are obtained by comparing to binary batch.                            | .132 |

TABLE Page

XXII Discrete Solutions for ISCAS'89 benchmark circuits with small tuning step. Runtime for computing nearest rounding and discrete solution includes the runtime for computing continuous solutions.

Area reduction and speedup are obtained by comparing to binary batch.134

## LIST OF FIGURES

| FIGURI | E                                                                                                                                                                   | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1      | The power consumption for a system-on-chip design [1]                                                                                                               | 2    |

| 2      | The slew-capacitance curve of an inverter                                                                                                                           | 16   |

| 3      | Underlying routing tree and buffer positions [19]                                                                                                                   | 19   |

| 4      | Slew constrained minimum cost buffering algorithm with fixed buffer input slew                                                                                      | 26   |

| 5      | Procedure of updating solution set for slew buffering with fixed buffer input slew                                                                                  | 27   |

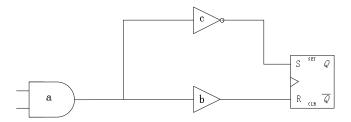

| 6      | An example of handling non-fixed input slew                                                                                                                         | 29   |

| 7      | Slew constrained minimum cost buffering algorithm with non-fixed buffer input slew                                                                                  | 33   |

| 8      | Procedure for updating solution set for slew buffering with non-fixed buffer input slew                                                                             | 34   |

| 9      | Continuous slew constrained minimum cost buffering algorithm with fixed buffer input slew                                                                           | 35   |

| 10     | Procedure of updating solution set for continuous slew buffering with fixed buffer input slew                                                                       | 36   |

| 11     | Continuous slew constrained minimum cost buffering algorithm with non-fixed buffer input slew                                                                       | 38   |

| 12     | Procedure of updating solution set for continuous slew buffering with non-fixed buffer input slew                                                                   | 39   |

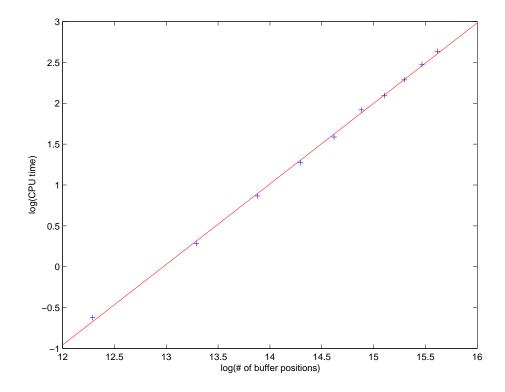

| 13     | Illustration of time complexity of SB. +: log (number of buffer positions) v.s. log (CPU time) for slew buffering with slew constraint 1.0ns. Line: best linear fit | 46   |

| FIGURI | $\Xi$                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 14     | An example for illustrating rounding error bound due to nearest rounding                                                                                                                                                                                                                                                                                                                                                                   | 57   |

| 15     | Pseudocode for discretization algorithm                                                                                                                                                                                                                                                                                                                                                                                                    | 60   |

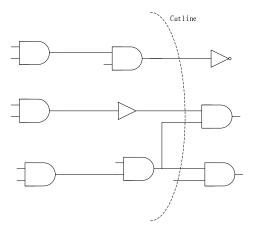

| 16     | A cutline                                                                                                                                                                                                                                                                                                                                                                                                                                  | 64   |

| 17     | Illustration of concepts in LSH                                                                                                                                                                                                                                                                                                                                                                                                            | 66   |

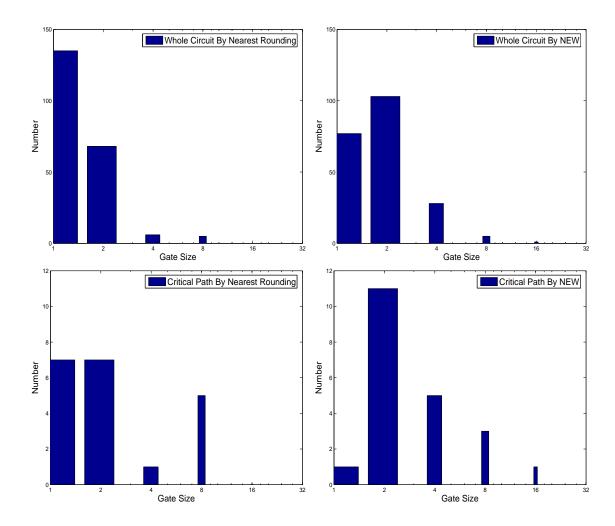

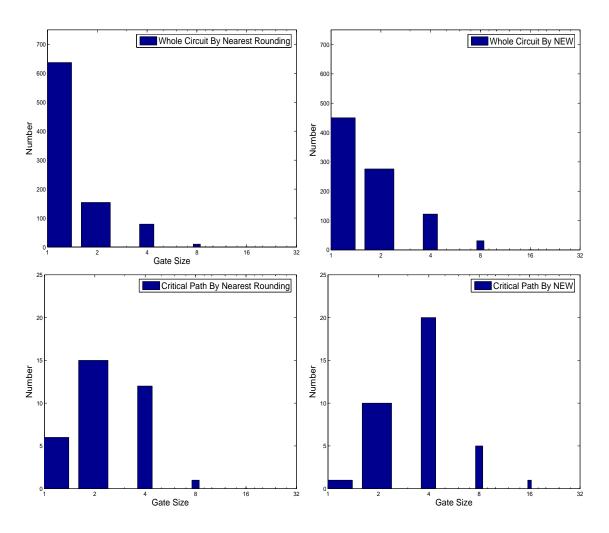

| 18     | Gate size histogram for the whole circuit and the critical path of C432 benchmark circuit.                                                                                                                                                                                                                                                                                                                                                 | 71   |

| 19     | Gate size histogram for the whole circuit and the critical path of C1908 benchmark circuit.                                                                                                                                                                                                                                                                                                                                                | . 72 |

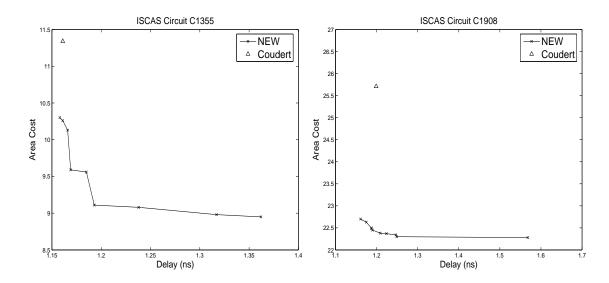

| 20     | Delay-cost tradeoff curves for optimizing two ISCAS benchmark circuits. The results of NEW and Coudert's approach [6] are shown.                                                                                                                                                                                                                                                                                                           | . 73 |

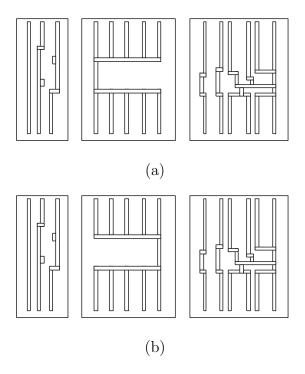

| 21     | Lithography optimization through cell flipping. This design is extracted from an ISCAS'89 benchmark circuit, where an NAND, an inverter and an XNOR gate are placed in series. Though flipping the middle inverter, average CD variation for boundary gate polys is reduced from 9.4% of the nominal value to 6.9% of the nominal value. Rectangles shown are polys. CD variation is obtained from Calibre LFD which considers OPC effects | . 79 |

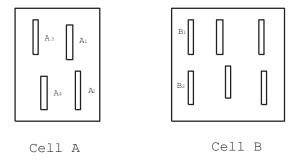

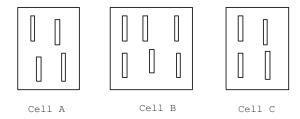

| 22     | Definition of manufacturability cost for cells. Rectangles shown are polys                                                                                                                                                                                                                                                                                                                                                                 | . 80 |

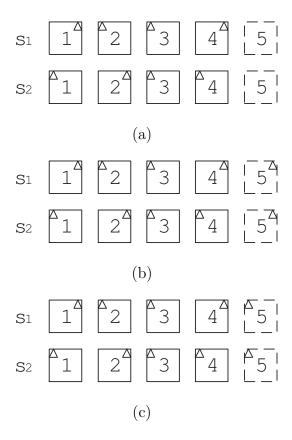

| 23     | Solution pruning: (a) before pruning (b) inferiority check when the fifth cell is unflipped (c) inferiority check when the fifth cell is flipped. The triangle denotes the cell orientation. A cell with triangle on the right denotes an unflipped cell and with triangle on the left denotes a flipped cell                                                                                                                              | . 86 |

| 24     | Cell flipping algorithm for a single row                                                                                                                                                                                                                                                                                                                                                                                                   | . 87 |

| 25     | A placement with three cells                                                                                                                                                                                                                                                                                                                                                                                                               | 90   |

| 26     | Graph $G$ corresponding to Figure 25                                                                                                                                                                                                                                                                                                                                                                                                       | 90   |

| FIGURI | ${f E}$                                                                                                                                                                                                                                                                                              | Pag€ |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

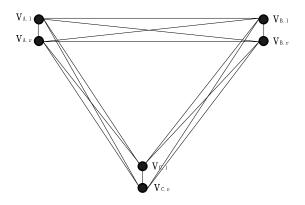

| 27     | Obtaining tradeoff between manufacturability cost and wirelength: (a) two initial solutions with best manufacturability cost (Optimal Litho) and best wirelength (Original) (b) an intermediate solution is obtained by exchanging cells with maximum link crossings (which are $C, E$ in this case) | 92   |

| 28     | Single row optimization algorithm                                                                                                                                                                                                                                                                    | 93   |

| 29     | Group optimization algorithm.                                                                                                                                                                                                                                                                        | 94   |

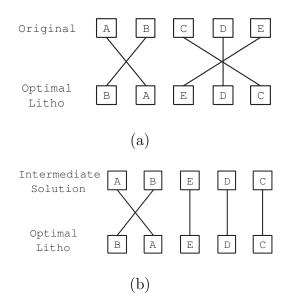

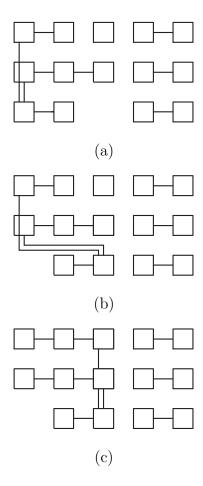

| 30     | An example of multiple row optimization: (a) original circuit (b) an intermediate solution in single row optimization (c) an intermediate solution in multiple row optimization                                                                                                                      | 95   |

| 31     | Multiple row optimization algorithm                                                                                                                                                                                                                                                                  | 97   |

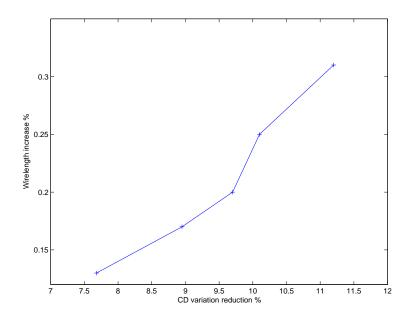

| 32     | Tradeoff between CD variation reduction and wirelength increase using single row optimization for s15850                                                                                                                                                                                             | 100  |

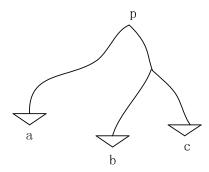

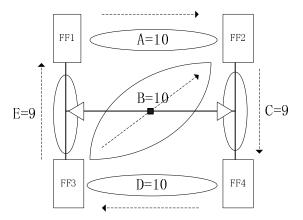

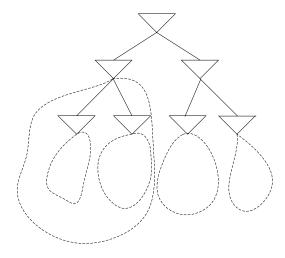

| 33     | A sequential circuit where the arrows show the signal flow directions. The central square is the clock source and the triangles are clock buffers                                                                                                                                                    | 111  |

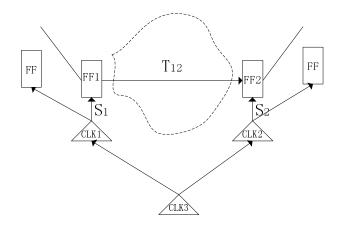

| 34     | Part of a sequential circuit. The dotted region is the circuit block                                                                                                                                                                                                                                 | 115  |

| 35     | Left: random sampling. Right: LH sampling. $\times$ denotes a sample                                                                                                                                                                                                                                 | 126  |

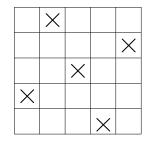

| 36     | A three-level clock tree. Dotted region refers to the covered circuit by the clock buffer                                                                                                                                                                                                            | 126  |

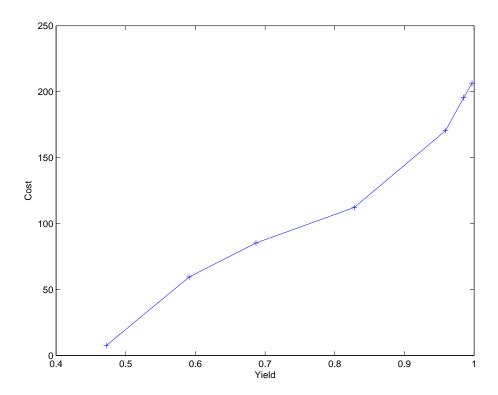

| 37     | Cost-Yield tradeoff curve for s1423 by the unified optimization                                                                                                                                                                                                                                      | 130  |

#### CHAPTER I

#### INTRODUCTION

#### A. Preliminaries and Motivation

As Very Large Scale Integration (VLSI) technology moves to the nanoscale regime, feature size keeps shrinking which results in large chip density (refer to Table I). Consequently, a chip often consists of millions of gates and circuit design becomes increasingly complex. Design automation techniques are essential to meet the challenge of tightening time-to-market pressure and shortening semiconductor product cycles.

Table I. Technology trend for VLSI chips [1].

| Technology node                                               | 130nm | 90nm | 65nm | 45nm |

|---------------------------------------------------------------|-------|------|------|------|

| Chip density $\left(\frac{Million\ transistors}{cm^2}\right)$ | 25    | 77   | 154  | 309  |

| Gate length $(nm)$                                            | 90    | 53   | 25   | 18   |

| Tolerable variation $(nm)$                                    | 5.3   | 3.75 | 2.5  | 2    |

| Wavelength (nm)                                               | 248   | 193  | 193  | 193  |

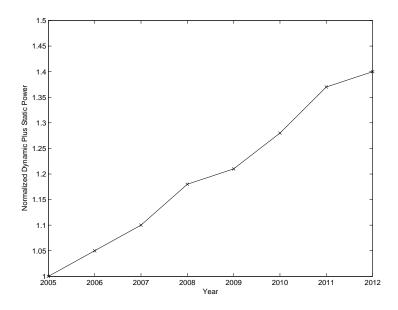

In spite of the advances in design automation techniques, design closure is increasingly difficult to achieve. A critical issue is to close the timing with low power consumption. Prevailing Integrated Circuit (IC) designs often have higher power dissipation than before due to greater device density, more metal layers and faster clock frequency, etc. This trend can be seen from Figure 1 which shows the power consumption of a class of system-on-ship designs. High power consumption has been a crucial concern for both portable electronics and non-mobile systems. For portable

The journal model is IEEE Transactions on Automatic Control.

electronics, low power dissipation may elongate battery lifetime. For non-mobile systems, large amount of heat due to high power dissipation imposes great difficulties to the packaging and cooling systems. Clearly, both circuit performance and reliability substantially depend on the solution to the power-heat problem.

Fig. 1. The power consumption for a system-on-chip design [1].

Power issues must be addressed in circuit design. For example, when performing buffer insertion to the circuit for timing and slew optimization, a significant part of the performance of the design depends on using as little buffering resources as possible since buffers themselves are a drain on power and can cause other gates to be sized to higher power levels. As power can be modeled by a generic cost function, cost minimization needs to be considered during circuit optimization. This dissertation explores two widely used optimization techniques, namely buffer insertion and gate sizing, and proposes several innovative algorithmic techniques for performance optimization with cost minimization.

On the other hand, with fast technology scaling, imperfections due to process,

voltage and temperature variations impose a tremendous challenge to the continuation of Moore's law as well as the growth of semiconductor industry. With increasingly shrinking features on the die, uncertainty in electrical characteristic of each individual device and wire significantly increases. Consequently, circuit performance is no longer determined solely by deterministic values and many previously negligible variations start to manifest, which may cause performance deviations or even functional failures. Even for 180nm technology, variations up to  $20\times$  in leakage and 30% in frequency have been reported in industrial chip designs [2].

Since variations may significantly divert circuit performance from the desired values, optimizations need to be performed to mitigate variation effects to achieve design and manufacturing closure. One way is to perturb the design to mitigate the variations it may receive. For example, an existing layout can be modified to be lithography friendly and then variations can be significantly reduced in fabrication process. Since there are always variations even after strongest variation mitigation techniques, it is also necessary to enable a circuit to be tunable after fabrication to further compensate for variations. These two classes of techniques are complementary to each other and this dissertation explores both of them to address the variation issues.

Clearly, to achieve design and manufacturing closure, efforts are needed in both deterministic design stage and variation-aware design stage. Deterministic design stage refers to the traditional circuit design without handling variations. With increasing design complexity, innovative effective and efficient algorithmic techniques are needed to compute a high quality design in terms of both timing and power. After that, variation-aware techniques are performed to the obtained deterministic design to improve the robustness of the design and the productivity.

#### B. Contribution

This dissertation heavily addresses both design stages and proposes various algorithms to address the challenge of obtaining a design with high frequency, low power and high robustness. For deterministic optimizations, new buffer insertion and gate sizing techniques are proposed. For variation-aware optimizations, new lithography-driven design techniques and post-silicon tuning-driven techniques are proposed.

#### 1. Fast Algorithms for Slew Constrained Minimum Cost Buffering

As interconnect scales slower than device, interconnect delay has become a significant bottleneck for circuit performance [3, 4]. As an effective technique to reduce interconnect delay, buffer insertion has been widely used in practice. For example, it has been well documented [3, 5] that the number of buffers on a chip is rising dramatically. Osler [5] cites two IBM ASIC designs where 25% of the gates are buffers. In addition, interconnect resistivity causes signal integrity to degrade more quickly with advancing technologies. Thus, buffers also need to be inserted on long interconnects to meet slew constraints, even if these nets are not timing critical.

In reality, slew constraint is much more prevalent than timing constraint: it is reported in [5] that only a fraction (roughly 5-10%) of nets need to be re-buffered for delay optimization; for the remaining fraction (roughly 90-95%), the slew based buffer insertion was sufficient to meet the net's timing constraint. In other words, it is sufficient to buffer all nets to fix slew violations without worrying about delay. Those small fraction of buffered nets that subsequently show up as critical can then be re-buffered with a delay based objective function. As the sheer number of buffers can degrade overall design performance by forcing the rest of the logic to be spread further apart to accommodate those buffers, one also wishes to use as little buffering

resources as possible.

We first formulate the problem as to find the minimum area buffering solution such that slew constraints are satisfied. Based on the new formulation, the general slew buffering problem is shown to be NP-Complete. Despite the difficulty of the problem, some highly efficient and practical algorithms are proposed. First, for a single buffer type, an optimal linear time solution is achievable. Second, for multiple buffer types, a very efficient dynamic programming based optimal slew buffering algorithm is designed under the assumption that the input slew to each buffer is fixed. Experiments show that compared to slew constrained timing buffering,  $> 90 \times$ speedup is achieved while still saving area. Third, if the input slew to each buffer is not fixed, the dynamic programming cannot be easily applied since the upstream knowledge is needed to compute the input slew. We propose a maximum matching based new algorithm to handle this difficult case. Experimental results demonstrate that up to 21.9% buffer area can be further saved. Fourth, when buffer positions can be freely chosen, slew buffering may allow more efficient buffer usage. A continuous slew buffering algorithm incorporating adaptive buffer selection idea is proposed for this purpose. It handles 1000 nets in only 30 seconds and often extra 5% buffer area saving can be obtained. The algorithm is further extended to handle blockages which makes it ready for practical use. Refer to Chapter II for the details of the project.

#### 2. Gate Sizing for Cell Library-Based Designs

In addition to interconnect optimizations, gate delay optimizations are studied in the dissertation. With increasing time-to-market pressure and shortening semiconductor product cycles, more and more chips are being designed with library-based methodologies. In cell library based designs, a handful set of gate sizing techniques exist. However, most of them handle the continuous gate sizing problem which is based on

the assumption that gate sizes can be any values within certain range. When gate implementations are restricted to discrete sizes, as in reality, the problem becomes much more difficult and very few approaches (see, e.g., [6]) are known. On the other hand, a large number of realistic cell libraries are "sparse". For example, when the cell sizes are geometrically spaced instead of uniformly spaced, significant sparseness is introduced. Refer to [7] for some realistic sparse libraries. Geometrically spaced gate sizes are desired because uniformly spaced gate sizes would result in a large number of gate sizes and managing this large volume of data is difficult [7]. Furthermore, it is proven in [7] that under certain conditions, the set of optimal gate sizes must satisfy the geometric progression.

In this project, we propose a novel gate sizing technique which directly handles discrete gate sizes. As many efficient solutions exist for the continuous gate sizing problem, one might think of obtaining a discrete solution through rounding a continuous solution. This is very fast but often results in large timing violations. In contrast, the method proposed by Coudert [6], which is based on the multi-dimensional descent optimization, directly handles the discrete sizes. However, it has some trial-and-error flavor and has room for further improvement. A dynamic programming approach can search solutions more systematically and thus has the potential to generate high quality solutions. However, it may suffer from large computation overhead, which imposes a great challenge to our problem.

The key idea of the new algorithm is to integrate the solution quality of dynamic programming with the short runtime of rounding continuous solution. That is, we narrow down the searching space of dynamic programming under the guidance from a best continuous solution. Thus instead of checking every implementation, our algorithm only investigates a number of discrete implementations around the best continuous solution. This enables us to find solutions with quality close to the best

continuous case and at the same time obtain huge speedup in computation. Our experimental results demonstrate that nearest rounding often leads to significant timing violations and compared to [6], our algorithm saves up to 21% area while satisfying the timing constraint. Refer to Chapter III for the details of the project.

#### 3. Pattern Sensitive Placement for Manufacturability

Lithography-induced variation is a main source of variations. It is due to the fact that with technology scaling, demands for minimum feature sizes have outpaced the advances in lithography hardware solutions and smaller amount of variations can be tolerated, which are evident from Table I. These impose great challenges on manufacturing reliability. In current lithography technology, 193nm wavelength is used to print 45nm features. This leads to a lot of refractive effects and images on wafer have remarkable mismatches from mask layouts. Lithography-induced variation also aggravates. As more variations are presented with e.g., gate length, timing and power of circuits are significantly affected.

Currently, semiconductor industry heavily relies on resolution enhancement techniques (RETs) for improving printability. Roughly speaking, printability refers to the difficulty in obtaining a good match between the intended image and the printed image in lithography process. Printability is often measured by critical dimension (CD) accuracy, which refers to the size of thin features which are difficult to print reliably. Thus, achieving high CD accuracy means that the printed patterns well match the desired ones. RETs are effective in improving CD accuracy. However, increasingly shrinking features on the die and increasing complexity of the design over-stretch the capability of RETs. This problem aggravates when RETs are applied to the layouts which are not lithography friendly. Furthermore, RETs often complicate photomark shapes and introduce large additional cost to photomask fabrication, which makes

RETs expensive to apply. To attack the above issues, efforts are needed in all process and design stages. With respect to physical design, manufacturability-aware methodologies would be performed in order to reduce the burden of manufactures and make RETs less expensive to apply. Furthermore, since variability has big impact on power, design for manufacturability also tends to mitigate the lithography-induced variations on power.

Placement of cells has remarkable effect on printability. This is due to the fact that gate lengths for transistors on the boundary regions of a cell significantly depend on its neighboring cells. Although sound library cell design can achieve high printability for internal transistors, it cannot handle the boundary transistors. On the other hand, as the gate length keeps shrinking with technologies, the placement will affect deeper and deeper regions of the cells.

In this project, the problem of cell placement considering manufacturability is studied. Instead of designing a new cell placer, our goal is to tune any existing cell placement solution to be lithography friendly. For this purpose, three algorithms are proposed, which are cell flipping algorithm, single row optimization approach and multiple row optimization approach. These algorithms are based on dynamic programming and graph theoretic approaches, and can provide different tradeoff between critical dimension (CD) variation reduction and wirelength increase. Using lithography simulations, our experimental results on realistic netlists and cell library demonstrate that over 15% CD variation reduction can be obtained by the new approaches while only less than 1% additional wire is introduced. Refer to Chapter IV for the details of the project.

#### 4. Unified Adaptivity Optimization of Clock and Logic Signals

In addition to lithography-driven optimizations, statistical optimization approaches are a class of effective approaches to handle variations and improve yield. In statistical optimizations, each gate or wire delay is modeled as a probabilistic density function (PDF) in contrast to a deterministic value. Based on that, the goal of the circuit optimizations is to optimize the PDF of the whole circuit delay. They are performed in the pre-silicon phase (e.g., [8, 9, 10]). That is, circuit parameters are determined in design time for yield optimization. With statistical variation models, they obtain the statistically optimized design and apply the design to all the dies. Although the optimized design is of good quality in statistical sense, the design is not necessarily ideal for each individual fabricated chip. Specific circuit parameter variations on the die cannot be mitigated. In addition, reliable statistical variation models are not easy to obtain [11].

In contrast to pre-silicon statistical optimizations, post-silicon tuning methodology can tune some circuit parameters after the chip is fabricated. This enables us to mitigate the specific circuit parameter variations on the individual chip to satisfy the design target. As a result, the timing yield can be significantly improved [12, 11].

Clearly, it is highly desirable to perform circuit adaptivity optimization for post-silicon tuning. Since making a circuit element post-silicon tunable necessarily introduces overhead, adaptivity optimization for post-silicon tuning aims to provide large tunability with small overhead. Previous works focus on either logic signal tuning (e.g., [12, 13, 11]) or clock signal tuning (e.g., [14, 15]). These approaches are effective, however, the resource utilization is not necessarily efficient since the interaction between logic circuit and clock network is not explored. Performing unified adaptivity optimization on clock and logic signals has the potential to significantly reduce

overhead while still having large tunability for achieving yield target.

Our unified optimization is based on a novel linear programming formulation which can be efficiently solved by an advanced robust linear programming technique. Due to the discrete nature of the problem, the continuous solution obtained from linear programming is then efficiently discretized. This procedure involves binary search accelerated dynamic programming, batch based optimization, and Latin Hypercube sampling based fast simulation. Our experimental results demonstrate that up to 50% area cost reduction can be obtained by the unified optimization compared to optimization on logic or clock alone. In addition, the proposed discretization approach significantly outperforms the alternatives in terms of solution quality and runtime. Refer to Chapter V for the details of the project.

#### CHAPTER II

# FAST ALGORITHMS FOR SLEW CONSTRAINED MINIMUM COST BUFFERING

As a prevalent constraint, sharp slew rate is often required in circuit design which causes a huge demand for buffering resources. This problem requires ultra-fast buffering techniques to handle large volume of nets, while also minimizing buffering cost. This problem is intensively studied in this paper. First, a highly efficient algorithm based on dynamic programming is proposed to optimally solve slew buffering with discrete buffer locations. Second, a new algorithm using the maximum matching technique is developed to handle the difficult cases in which no assumption is made on buffer input slew. Third, an adaptive buffer selection approach is proposed to efficiently handle slew buffering with continuous buffer locations. Fourth, buffer blockage avoidance is handled, which makes the algorithms ready for practical use.

Experiments on industrial netlists demonstrate that our algorithms are very effective and highly efficient: we achieve about 90× speed up and save up to 20% buffer area over the commonly-used van Ginneken style buffering. The new algorithms also significantly outperform previous works that indirectly address the slew buffering problem<sup>1</sup>.

#### A. Introduction

As VLSI technology moves to the 65 nm node and beyond, it has been well documented [3, 5] that the number of buffers on a chip is rising dramatically. Osler [5]

<sup>&</sup>lt;sup>1</sup>Copyright ©2007 IEEE. Reprinted, with permission, from S. Hu, C. J. Alpert, J. Hu, S. Karandikar, Z. Li, W. Shi and C. N. Sze, Fast algorithms for slew constrained minimum cost buffering, IEEE Transactions on Computer-Aided Design, Vol. 26, No. 11, pp. 2009-2022, November, 2007.

cites two IBM ASIC designs where one-fourth of the gates are buffers. For some multi-million gate ASICs, more than a million buffers are required today. This is a surprise to no one as devices continue to scale more quickly than interconnects. Higher relative interconnect resistance forces buffers to be placed closer together to achieve optimal performance. In addition, interconnect resistivity also causes signal integrity to degrade more quickly with each advancing technology. Thus, buffers need to be inserted on long interconnects to meet slew constraints, even if these nets are not timing critical.

In reality, slew constraint is much more prevalent than timing constraint: it is reported in [5] that only a fraction (roughly 5-10%) of nets need to be re-buffered for delay optimization; for the remaining fraction (roughly 90-95%), the slew based buffer insertion was sufficient to meet the net's timing constraint. In other words, it is sufficient to buffer all nets to fix slew violations without worrying about delay. Those small fraction of buffered nets that subsequently show up as critical can then be re-buffered with a delay based objective function. In the IBM physical synthesis methodology [5], buffers are inserted for satisfying slew constraints early, so that timing analysis uses legal slew constraints. Later, buffers on critical nets are ripped up and re-buffered for delay.

The sheer number of buffers can degrade overall design performance by forcing the rest of the logic to be spread further apart to accommodate those buffers. The buffers themselves are a drain on power and can cause other gates to be sized to higher power levels since they are now further apart on the chip. Therefore, a significant part of the performance of the design depends on using as little buffering resources as possible. van Ginneken's algorithm [16] and its derivative extensions [17, 18, 19, 20, 21, 22] are very effective for delay optimization. Further, Lillis' data structure [17] allows trading off delay for cost to more efficiently use buffer resources, yet this is

still suboptimal for area.

From a practical point of view, slew buffering should be as important as timing driven buffering. Unfortunately, there is very little previous work on it. For related works that consider slew and/or noise constraints [17, 23, 18, 24], they still optimize for delay instead of handling these constraints separately. Buffering of non-critical nets using these techniques may result in unnecessary runtime and resource overhead. Note that the work of [25] also addresses slew constraints without regards to delay. However, that work does not actually model slew; it simplifies the slew constraint to be equivalent to a capacitance constraint which means that interconnect resistivity is not modelled. While appropriate for very large fanout nets (e.g., over 1000 sinks), it essentially becomes equivalent to length-based buffering [26]. Length-based buffering [26] tries to achieve a similar result of slew buffering in spirit. However, we show that it can be area inefficient especially in handling multi-fanout nets.

This work proposes a new buffering formulation: find the minimum area (or cost) buffering solution such that slew constraints are satisfied. In this formulation, one does not need to know required arrival time at sinks, so it can be used earlier in the design flow than traditional buffering. It can be done totally independently of timing analysis, i.e., incremental timing is not required between buffering of individual nets. Based on the new formulation, the general slew buffering problem is shown to be NP-Complete. Despite the difficulty of the problem, some highly efficient and practical algorithms are proposed in this paper:

- 1. For a single buffer type, an optimal linear time solution is achievable by greedy algorithm under the assumption that the input slew to each buffer is fixed.

- 2. For multiple buffer types, a very efficient optimal slew buffering algorithm is designed under the assumption that the input slew to each buffer is fixed. Ex-

periments show that compared to slew constrained timing buffering, about  $90 \times$  speedup is achieved while still saving area.

- 3. If the input slew to each buffer is not fixed, the dynamic programming cannot be easily applied since the upstream knowledge is needed to compute the input slew. We propose a maximum matching based new algorithm to handle this difficult case. Experimental results demonstrate that up to 21.9% buffer area can be further saved.

- 4. When buffer positions can be freely chosen, slew buffering may allow more efficient buffer usage. A continuous slew buffering algorithm incorporating adaptive buffer selection idea is proposed for this purpose. It handles 1000 nets in only 30 seconds and often extra 5% buffer area saving can be obtained.

- 5. Buffering with blockage is handled in this paper, which makes the algorithms ready for practical use.

Although there is a close relationship between slew buffering and timing buffering, the two buffering algorithms are actually very different. For example, in slew buffering, inserting one buffer may only generate one new non-dominated solution. However, in timing buffering, numerous new non-dominated solutions can be introduced. Refer to Section b for details.

The rest of the chapter is organized as follows: Section B formulates the slew buffering problem. Section C presents the NP-Completeness proof for the general slew buffering problem. Section D describes the proposed slew buffering algorithms. Section E describes two related buffering algorithms for comparison. Section E presents the experimental results with analysis. A summary of work is given in Section G.

#### B. Preliminaries

The input to the slew buffering problem includes a routing tree T = (V, E), where  $V = \{s_0\} \cup V_s \cup V_n$ , and  $E \subseteq V \times V$ . For simplicity, the routing tree is assumed to be a binary tree in this paper. Trees in other topologies can be converted to a binary tree (see, e.g., [20]). Vertex  $s_0$  is the source vertex,  $V_s$  is the set of sink vertices and  $V_n$  is the set of internal vertices. Each sink vertex  $s \in V_s$  is associated with sink capacitance  $C_s$ . Each edge  $e \in E$  is associated with lumped resistance  $R_e$  and capacitance  $C_e$ . A buffer library B contains different types of buffers. Each type of buffer b has a cost  $W_b$ , which can be measured by area or any other metric, depending on the optimization objective. Without loss of generality, we assume that the driver at source  $s_0$  is also in B. A function  $f: V_n \to 2^B$  specifies the types of buffers allowed at each internal vertex. That is, for each vertex v, f(v), which is a subset of  $2^B$ , specifies the buffer types allowed at v.

The slew rate of a signal refers to the rising or falling time of a signal switching. A commonly used definition of slew is the 10/90 slew and it is adopted in this paper, where 10/90 slew refers to the time difference between when the waveform crosses the 90% point and the 10% point. Some other definitions, such as 20/80 or 30/70 slew, are also used in practice when the waveform has slowly rising or falling tail. The slew model employed in this work is chosen for its simplicity and is essentially equivalent to the Elmore model for delay. More accurate wire and gate delay models may be used if more accuracy is desired. Given that the motivation for the proposed buffering formulation lies in the requirement to efficiently buffer a large number of nets, this slew model is appropriate.

The slew model can be explained using a generic example which is a path p from node  $v_i$  (upstream) to  $v_j$  (downstream) in a buffered tree. There is a buffer (or the

driver)  $b_u$  at  $v_i$ , and there is no buffer between  $v_i$  and  $v_j$ . The slew rate  $S(v_j)$  at  $v_j$  depends on both the output slew  $S_{b_u,out}(v_i)$  at buffer  $b_u$  and the slew degradation  $S_w(p)$  along path p (or wire slew), and is given by [27]:

$$S(v_j) = \sqrt{S_{b_u,out}(v_i)^2 + S_w(p)^2}.$$

(2.1)

The slew degradation  $S_w(p)$  can be computed with Bakoglu's metric [28] as

$$S_w(p) = \ln 9 \cdot D(p), \tag{2.2}$$

where D(p) is the Elmore delay from  $v_i$  to  $v_j$ .

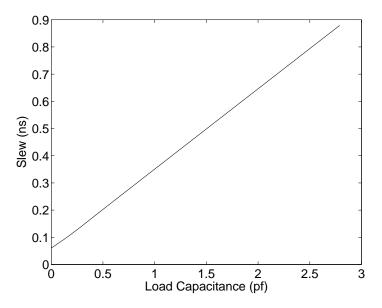

Fig. 2. The slew-capacitance curve of an inverter.

The output slew of a buffer, such as  $b_u$  at  $v_i$ , depends on the input slew at this buffer and the load capacitance seen from the output of the buffer. Usually, the dependence is described as a 2-D lookup table. In addition to handling the general case of arbitrary input slew, our work includes fast algorithms assuming a fixed input slew which is normally a conservative estimation (the slew constraint).

This assumption allows us to process large volume of nets quickly with small solution degradation. For fixed input slew, the output slew of buffer b at vertex v is then given by

$$S_{b,out}(v) = R_b \cdot C(v) + K_b, \tag{2.3}$$

where C(v) is the downstream capacitance at v,  $R_b$  and  $K_b$  are empirical fitting parameters. This is similar to empirically derived K-factor equations [29]. We call  $R_b$  the slew resistance and  $K_b$  the intrinsic slew of buffer b. Figure 2 shows a slew curve of one inverter generated by EinsTimer [30]. The linear order model is quite reasonable as seen from Figure 2.

A buffer assignment  $\gamma$  is a mapping  $\gamma: V_n \to B \cup \{\bar{b}\}$  where  $\bar{b}$  denotes that no buffer is inserted. The cost of a solution  $\gamma$  is  $W(\gamma) = \sum_{b \in \gamma} W_b$ . With the above notations, the basic slew buffering problem can be formulated as follows.

Discrete Slew Constrained Minimum Cost Buffer Insertion Problem: Given a binary routing tree T = (V, E), possible buffer positions, and a buffer library B, to compute a buffer assignment  $\gamma$  such that the total cost  $W(\gamma)$  is minimized such that the input slew at each buffer or sink is no greater than a constant  $\alpha$ .

Note that the continuous slew buffering problem is also considered in this paper where buffer positions can be freely chosen in a routing tree. A first glance at the above closed form model might suggest close relationship between timing buffering and slew buffering, however, they actually significantly differ. A detailed analysis is presented in Section b. Before closing this section, we note the following computational complexity result:

**Theorem 1:** The minimum cost slew buffering problem is NP-Complete, if the size of the buffer library is not constant and the cost of each buffer can be an arbitrary integer.

Refer to Section C for the proof. Since the size of the buffer library is bounded and the buffer area is not an arbitrary value in reality, our algorithms perform very well in practice.

#### C. Complexity of Slew Buffering Problem

#### Proof of Theorem 1:

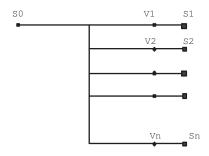

The problem is clearly in NP. We reduce from the minimum cost timing buffering problem with unbounded buffer library size<sup>1</sup> to show that the minimum cost slew buffering problem with unbounded buffer library size is NP-Complete. Let Q, R, C, W denote the required arrival time (RAT), resistance, capacitance and cost, respectively. It is shown in [19] that computing a timing buffering for the tree in Figure 3 with RAT at driver  $Q_{s_0} \geq 0$  and the total buffer cost at most  $M = N + \sum_{i=1}^{n} N^i$  is NP-Complete. Driver resistance is set to  $R_{s_0} = N^n$ , sink capacitance and sink RAT are listed in Table II, and the buffer library information is shown in Table III, where N is a sufficiently large positive integer,  $x_1, x_2, \ldots, x_{2n}$  are positive integers such that  $\sum_{1}^{2n} x_i = 2N$ , and there are n sinks and 2n buffer types in the buffer library.

We set intrinsic slew and intrinsic delay to zero, and slew resistance equal to driving resistance for each buffer type and driver. Furthermore, every edge in the tree has zero wire capacitance and zero wire resistance. It is then easy to check that the slew rate is equal to the delay in value. For example, delay and slew rate at  $v_1$  are both  $R_{s_0} \cdot C_{b_1}$  assuming that  $b_1$  is placed at  $v_1$ .

Given an instance of minimum cost timing buffering problem, we construct an instance of minimum cost slew buffering problem as follows. We reuse the routing tree in Figure 3 except that each sink  $s_i$  is changed to a sink  $s_i'$ , where  $C_{s_i'} = \frac{C_{s_i}}{N}$ . A

<sup>&</sup>lt;sup>1</sup>That is, the number of buffer types is not constant.

Fig. 3. Underlying routing tree and buffer positions [19].

| Sink $s_i$ | Sink capacitance $C_{s_i}$ | Sink RAT $Q_{s_i}$  |

|------------|----------------------------|---------------------|

| $s_1$      | $N^{n+2}$                  | $N^{n+1} + N^{n+2}$ |

| $s_2$      | $N^{n+1}$                  | $N^{n+1} + N^{n+2}$ |

|            |                            |                     |

| $s_n$      | $N^3$                      | $N^{n+1} + N^{n+2}$ |

Table II. C, Q values for sinks [19].

critical fact used in [19] is that every buffer position  $v_i$  must be inserted with a buffer, and this buffer must be either  $b_{2i-1}$  or  $b_{2i}$ .

We claim that there is a solution for the instance of slew buffering problem with slew constraint  $\alpha = N^{n+1}$  and the total buffer cost at most M if and only if there is a solution for the instance of minimum cost timing buffering problem with  $Q_{s_0} \geq 0$  and with the same cost bound.

We begin with the "only if" direction. Since slew constraint is set to  $N^{n+1}$ , it follows that the delay between  $s_0$  and  $v_i$  and delay between  $v_i$  and  $s_i'$  is no more than  $N^{n+1}$  each. Since  $C_{s_i'} = \frac{C_{s_i}}{N}$ , delay between  $v_i$  and  $s_i$  is bounded above by  $N^{n+2}$ . Noting that  $Q_{s_i} = N^{n+2} + N^{n+1}$ , we have  $Q_{s_0} \ge 0$ .

For the "if" direction, since we must insert one of  $b_{2i-1}$  and  $b_{2i}$  at every  $v_i$ , delay

| Buffer     | Driving resistance | Input capacitance | Cost (Area)     |

|------------|--------------------|-------------------|-----------------|

| $b_i$      | $R_{b_i}$          | $C_{b_i}$         | $W_{b_i}$       |

| $b_1$      | 1                  | $x_1$             | $x_2 + N^n$     |

| $b_2$      | 1                  | $x_2$             | $x_1 + N^n$     |

| $b_3$      | N                  | $x_3$             | $x_4 + N^{n-1}$ |

| $b_4$      | N                  | $x_4$             | $x_3 + N^{n-1}$ |

|            |                    |                   |                 |

| $b_{2n-1}$ | $N^{n-1}$          | $x_{2n-1}$        | $x_{2n} + N$    |

| $b_{2n}$   | $N^{n-1}$          | $x_{2n}$          | $x_{2n-1} + N$  |

Table III. C, R, W values for each buffer type [19].

between  $v_i$  and  $s_i$  is  $N^{n+2}$ , and thus the slew rate at  $s_i'$  is  $N^{n+1}$ . Since total delay from  $s_0$  to any sink  $s_i$  is no larger than  $N^{n+1} + N^{n+2}$ , one sees that delay between  $s_0$  and any  $v_i$  is bounded above by  $N^{n+1}$ . Therefore, in the buffered tree, slew rate at any buffer position/sink is bounded above by  $\alpha$ , which completes the proof.

#### D. Slew Constrained Minimum Cost Buffering Algorithms

#### 1. Overview of Classic Timing-Driven Buffering

To understand the context of the presented algorithms and to define notation, this section begins with a brief overview of van Ginneken/Lillis [16, 17] algorithm. The algorithm proceeds bottom-up from the leaf nodes toward the driver along a given routing tree. A set of candidate solutions is kept updated during the process. Each solution is associated with a three-tuple (C, W, Q), where C denotes the downstream capacitance at the current node, W denotes the cost (i.e., area) of the solution and

Q refers to the required arrival time (RAT).

Suppose that a solution  $\gamma_v$  at position v must "propagate" to an upstream position u and there is no branching point in between. If no buffer is placed at u, then only wire delay needs to be considered. Therefore, the new solution  $\gamma_u$  can be computed as

$$C(\gamma_u) = C(\gamma_v) + C_e,$$

$$W(\gamma_u) = W(\gamma_v),$$

$$Q(\gamma_u) = Q(\gamma_v) - D_e,$$

(2.4)

where e = (u, v) and  $D_e = R_e(\frac{C_e}{2} + C(\gamma_v))$ . Otherwise, suppose that we add a buffer  $b_i$  at u.  $\gamma_u$  can be then computed as

$$C(\gamma_u) = C_{b_i},$$

$$W(\gamma_u) = W(\gamma_v) + W_{b_i},$$

$$Q(\gamma_u) = Q(\gamma_v) - D_{b_i} - D_e$$

$$(2.5)$$

after buffer insertion. In Eqn. (2.5),  $D_{b_i}$  refers to the buffer delay and is computed as  $D_{b_i} = R'_{b_i} \cdot C(u) + K'_{b_i}$ , where  $R'_{b_i}$  is the driving resistance of  $b_i$  but not the slew resistance of  $b_i$ , and  $K'_{b_i}$  is the intrinsic buffer delay.

An important concept in van Ginneken/Lillis algorithm are non-dominated solutions. For any two solutions  $\gamma_1, \gamma_2$  at the same node,  $\gamma_1$  dominates  $\gamma_2$  if  $C(\gamma_1) \leq C(\gamma_2)$ ,  $W(\gamma_1) \leq W(\gamma_2)$  and  $Q(\gamma_1) \geq Q(\gamma_2)$ . Whenever a solution becomes dominated, it is removed from the solution set. Therefore, only solutions excel in at least one aspect of downstream capacitance, buffer cost and RAT can survive.

For handling branch merging, suppose that we have obtained all the non-dominated solutions of left branch  $T_l$  and right branch  $T_r$  at a branching point  $v_t^1$ . Denote the

<sup>&</sup>lt;sup>1</sup>For two branches, we arbitrarily assign them to be left branch and right branch.

left-branch solution set and the right-branch solution set by  $\Gamma_l$  and  $\Gamma_r$ , respectively. The merging process is performed as follows. For each solution  $\gamma_l \in \Gamma_l$  and each solution  $\gamma_r \in \Gamma_r$ , generate a new solution  $\gamma'$  according to:

$$C(\gamma') = C(\gamma_l) + C(\gamma_r),$$

$$W(\gamma') = W(\gamma_l) + W(\gamma_r),$$

$$Q(\gamma') = \min\{Q(\gamma_l), Q(\gamma_r)\}.$$

(2.6)

At a high level, van Ginneken/Lillis algorithm builds the solution set in a bottomup fashion. Assume that we have computed all feasible non-dominated solutions at a buffer position v. For the immediately upstream buffer position u (without passing any branching point), we first propagate all solutions up there through performing wire insertion of (u, v) to each solution. The propagated solutions resemble the choices when no buffer is inserted at u. Subsequently, for each propagated solution, we compute a new solution for inserting each buffer. The new solution is inserted into the solution set as long as it is not dominated by any existing one. The solution set is meanwhile updated to prune the solutions being dominated by the newcomer. At a merging point, we carry out the process just described to generate the new solution set. In this way, we keep climbing up the routing tree until the driver is met. After pruning solutions violating the timing constraint at driver, we select the best solution as the one with the smallest cost.

### 2. Discrete Slew Buffering Assuming Fixed Input Slew

## a. Algorithm