# DESIGN OF RF/IF ANALOG TO DIGITAL CONVERTERS FOR SOFTWARE RADIO COMMUNICATION RECEIVERS

A Dissertation

by

## BHARATH KUMAR THANDRI

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2006

Major Subject: Electrical Engineering

# DESIGN OF RF/IF ANALOG TO DIGITAL CONVERTERS FOR SOFTWARE RADIO COMMUNICATION RECEIVERS

#### A Dissertation

by

### BHARATH KUMAR THANDRI

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

## Approved by:

Chair of Committee, Jose Silva-Martinez Committee Members, Aydin Karsilayan

Shankar Bhattacharyya

Takis Zourntos Vinod Srinivasan

Head of Department, Costas Georghiades

May 2006

Major Subject: Electrical Engineering

#### **ABSTRACT**

Design of RF/IF Analog to Digital Converters for Software Radio Communication

Receivers. (May 2006)

Bharath Kumar Thandri,

B.E. (Hons.), Birla Institute of Technology and Science (BITS), Pilani, India;

M.S., Texas A&M University

Chair of Advisory Committee: Dr. Jose Silva-Martinez

Software radio architecture can support multiple standards by performing analog-to-digital (A/D) conversion of the radio frequency (RF) signals and running reconfigurable software programs on the backend digital signal processor (DSP). A slight variation of this architecture is the software defined radio architecture in which the A/D conversion is performed on intermediate frequency (IF) signals after a single down conversion.

The first part of this research deals with the design and implementation of a fourth order continuous time bandpass sigma-delta (CT BP  $\Sigma\Delta$ ) ADC based on LC filters for direct RF digitization at 950 MHz with a clock frequency of 3.8 GHz. A new ADC architecture is proposed which uses only non-return to zero feedback digital to analog converter pulses to mitigate problems associated with clock jitter. The architecture also has full control over tuning of the coefficients of the noise transfer function for obtaining

the best signal to noise ratio (SNR) performance. The operation of the architecture is examined in detail and extra design parameters are introduced to ensure robust operation of the ADC. Measurement results of the ADC, implemented in IBM 0.25  $\mu$ m SiGe BiCMOS technology, show SNR of 63 dB and 59 dB in signal bandwidths of 200 kHz and 1 MHz, respectively, around 950 MHz while consuming 75 mW of power from  $\pm$  1.25 V supply.

The second part of this research deals with the design of a fourth order CT BP  $\Sigma\Delta$  ADC based on  $g_m$ -C integrators with an automatic digital tuning scheme for IF digitization at 125 MHz and a clock frequency of 500 MHz. A linearized CMOS OTA architecture combines both cross coupling and source degeneration in order to obtain good IM3 performance. A system level digital tuning scheme is proposed to tune the ADC performance over process, voltage and temperature variations. The output bit stream of the ADC is captured using an external DSP, where a software tuning algorithm tunes the ADC parameters for best SNR performance. The IF ADC was designed in TSMC 0.35  $\mu$ m CMOS technology and it consumes 152 mW of power from  $\pm$  1.65 V supply.

# **DEDICATION**

To Shakuntala, my late grandmother.

To all my teachers - from high school to graduate school

#### **ACKNOWLEDGMENTS**

As I come close to finishing my graduate studies, it has been a great learning experience and I would like to thank a lot of people who have helped me through various stages of my career.

I would like to thank my advisor Dr Jose Silva-Martinez, who has been a great source of inspiration and support throughout my graduate studies. When I first approached him to start my M.S. research, he accepted me as his student in spite of my limited knowledge in analog and mixed signal design owing to my prior computer science background during my Bachelor's program. The endless doubts from my side never bothered him and he patiently answered all my questions, which was one of the main reasons I decided to continue my PhD under his supervision. The long discussions with him have helped me to understand different aspects of analog design and I am greatly indebted to him for all his guidance during my graduate studies.

I would like to thank all my PhD committee members – Dr Aydin Karsilayan, Dr Takis Zourntos, Dr Shankar Bhattacharya and Dr Vinod Srinivasan, for agreeing to serve in my committee and reading my dissertation. Dr Takis Zourntos explained various aspects of behavioral models in Matlab which helped me speed up my research work. The graduate control theory course that I took under Dr Bhattacharya was very interesting and I would like to thank him for discussions on possible application of non-linear control theory to my research work. The courses that I took under other professors

in our AMSC group helped me to learn various aspects of IC design. Special mention and thanks goes to Dr Ugur Cilingiroglu - his courses on basic analog IC design, semiconductor devices and MOS modeling helped me tremendously because of his clear explanation of all basic concepts. Our group secretary, Ella Gallagher, has always been a tremendous help in all aspects of administrative work.

I would like to thank all my colleagues in the AMSC group for the great discussions and help throughout my stay. Special mention goes to Chinmaya Mishra who helped with the design of digital blocks for the RF ADC project and to Xuemei Liu who helped in the design and layout of the IF ADC project.

Looking back in my career, I realize that I'm deeply indebted to all my teachers (from high school to graduate school) who have helped me grow in both technical and personal aspects. Special mention goes to Mrs Shyla George and Mr C Subramanian (both high school teachers) and to Dr Santosh Kumar (professor during my Bachelor's degree), who were great mentors.

I'm always grateful for the love and support from my family. One person who has made the greatest impact in my life is my late grandmother – Shakuntala. I would like to thank my parents and my sister for their constant love, encouragement and their belief in me, which has been a great source of inspiration throughout my graduate studies. I would like to thank my wife Preethi, who is always there for me with her unconditional love and a smiling face all the time. She will always be the shining light in my life and a great motivating factor for all my endeavors.

# TABLE OF CONTENTS

|             |                      |                                                                                                                                                | Page |

|-------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|

| ABSTRACT    |                      |                                                                                                                                                | iii  |

| DEDICATIO   | N                    |                                                                                                                                                | V    |

| ACKNOWLI    | EDGMI                | ENTS                                                                                                                                           | vi   |

| TABLE OF C  | CONTE                | NTS                                                                                                                                            | viii |

| LIST OF FIG | URES.                |                                                                                                                                                | xi   |

| LIST OF TA  | BLES                 |                                                                                                                                                | xvi  |

| CHAPTER     |                      |                                                                                                                                                |      |

| I           | INTR                 | ODUCTION                                                                                                                                       | 1    |

|             | 1.1.<br>1.2.<br>1.3. | Motivation                                                                                                                                     | 4    |

| II          | ANAI                 | Organization  LOG TO DIGITAL CONVERSION IN COMMUNICATION  EIVERS                                                                               |      |

|             | 2.1.                 | Receiver architectures                                                                                                                         | 8    |

|             |                      | <ul><li>2.1.1. Superheterodyne architecture</li><li>2.1.2. Direct conversion architecture</li><li>2.1.3. Software radio architecture</li></ul> | 14   |

|             | 2.2.                 | 2.1.4. Software defined radio architecture                                                                                                     | 19   |

|             | 2.2.                 | Overview of ADC architectures                                                                                                                  | 27   |

|             | 2.2                  | 2.2.2. Oversampled analog to digital converters 2.2.3. Bandpass sigma-delta analog to digital converters                                       | 32   |

|             | 2.3.                 | IF switched capacitor bandpass $\Sigma\Delta$ ADC design                                                                                       |      |

**CHAPTER** Page Ш OVERVIEW OF CONTINUOUS TIME BANDPASS SIGMA DELTA ANALOG TO DIGITAL CONVERTERS ......47 3.1. 3.2. Discrete time ADC equivalence......51 3.3. DAC pulse shapes ......53 3.4. Non-idealities of a continuous time bandpass  $\Sigma\Delta$  ADC ......55 3.4.1. Clock jitter ......56 3.4.2. Comparator metastability ......59 3.4.3. Excess loop delay......60 3.4.4. Finite quality factor of the bandpass loop filter .............62

|    |       | 3.4.5. Unequal DAC pulse rise and fall time               | 65  |

|----|-------|-----------------------------------------------------------|-----|

|    |       | 3.4.6. Frequency and Q tuning of the continuous time loop |     |

|    |       | filter                                                    |     |

|    | 3.5.  | Analysis of reported architectures                        |     |

| IV | Δ38   | GHz ADC FOR DIRECT DIGITIZATION OF BANDPASS               |     |

| 11 |       | ALS AROUND 950 MHz                                        | 72  |

|    | 4.1.  | Introduction                                              | 72  |

|    | 4.1.  | Proposed ADC architecture                                 |     |

|    | 4.2.  | •                                                         |     |

|    |       | Operation of the integrator DAC                           |     |

|    | 4.4.  | Behavioral simulations                                    |     |

|    | 4.5.  | Circuit implementation and simulation results             |     |

|    |       | 4.5.1. Q-enhanced LC bandpass filter                      |     |

|    |       | 4.5.2. Integrator DAC                                     |     |

|    |       | 4.5.3. Current DAC                                        |     |

|    |       | 4.5.4. Comparator                                         |     |

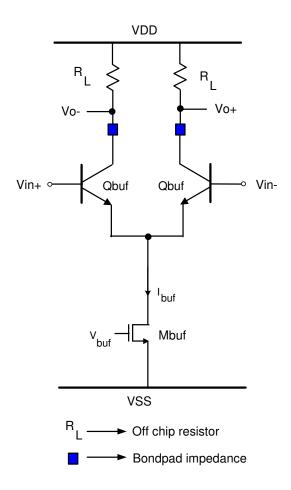

|    |       | 4.5.5. Output and clock buffer                            |     |

|    | 4.6.  | Top level simulations                                     | 118 |

|    | 4.7.  | Measurement results                                       | 121 |

| V  | A 500 | MHz ADC FOR BANDPASS IF DIGITIZATION AROUNI               | )   |

|    | 125 N | MHz USING A DIGITAL TUNING SCHEME                         | 132 |

|    | 5.1.  | Introduction                                              | 132 |

|    | 5.2.  | Architecture of the IF ADC                                |     |

|    | 5.3.  | Digital tuning loop for SNR optimization                  |     |

|    |       |                                                           |     |

|    |       |                                                           |     |

| CHAPTER  |      |                                                  | Page |

|----------|------|--------------------------------------------------|------|

|          | 5.4. | Circuit implementation and simulation results    | 155  |

|          |      | 5.4.1. gm-C bandpass filter using linearized OTA | 155  |

|          |      | 5.4.2. Current DAC                               |      |

|          |      | 5.4.3. Comparator                                | 162  |

|          | 5.5. |                                                  | 168  |

|          | 5.6. | Conclusions                                      |      |

| VI       | CON  | CLUSIONS                                         | 172  |

|          | 6.1. | Summary                                          | 172  |

|          | 6.2. | Future research work                             | 175  |

| REFERENC | ES   |                                                  | 178  |

| VITA     |      |                                                  | 186  |

# LIST OF FIGURES

|            |                                                                             | Page |

|------------|-----------------------------------------------------------------------------|------|

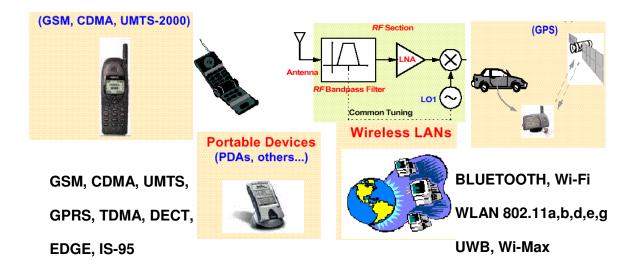

| Fig. 1.1.  | Wireless communication applications and standards                           | 2    |

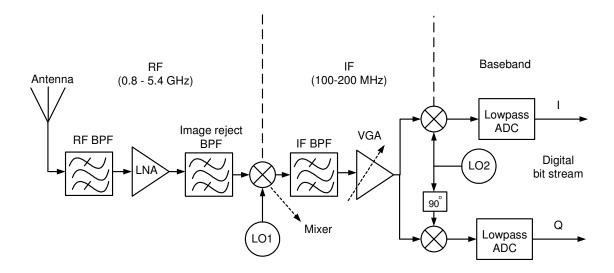

| Fig. 2.1.  | Superheterodyne receiver architecture                                       | 11   |

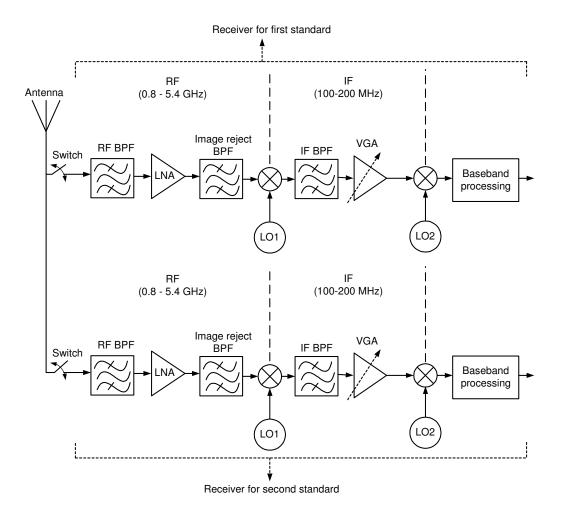

| Fig. 2.2.  | Implementation of multiple standards using the superheterodyne architecture | 13   |

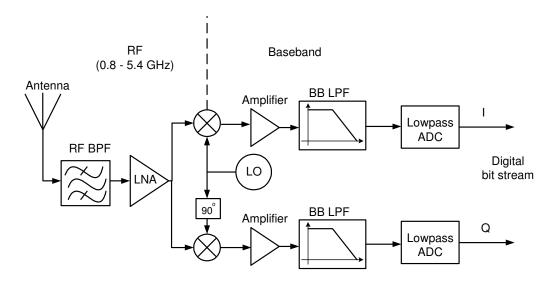

| Fig. 2.3.  | Direct conversion or homodyne architecture                                  | 14   |

| Fig. 2.4.  | Ideal software radio architecture                                           | 16   |

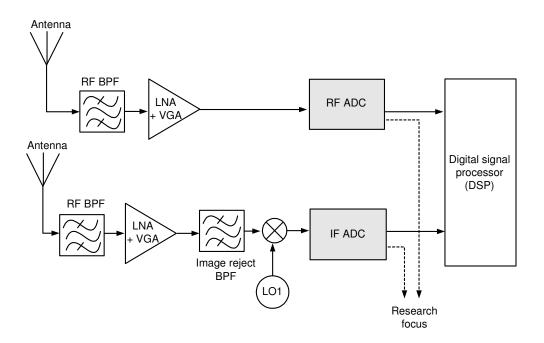

| Fig. 2.5.  | Modified software radio architecture                                        | 17   |

| Fig. 2.6.  | Software defined radio (or) digital IF architecture                         | 19   |

| Fig. 2.7.  | Possible software radio implementations in wireless applications            | 20   |

| Fig. 2.8.  | ADC for software radio communication receivers                              | 23   |

| Fig. 2.9.  | Generalized analog to digital conversion process                            | 24   |

| Fig. 2.10. | Classification of ADC architectures based on speed and resolution           | 26   |

| Fig. 2.11. | Sampling in time and frequency domain                                       | 28   |

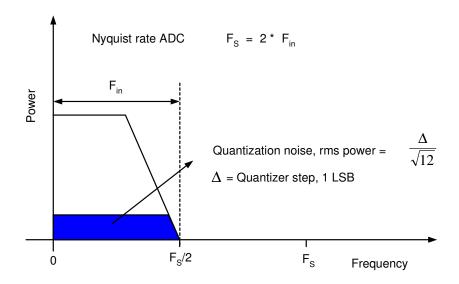

| Fig. 2.12. | Quantization noise in Nyquist rate converters                               | 29   |

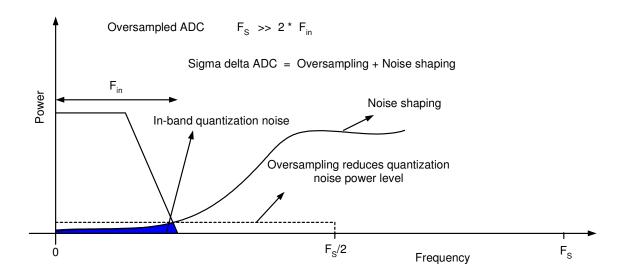

| Fig. 2.13. | Quantization noise in oversampled converters                                | 30   |

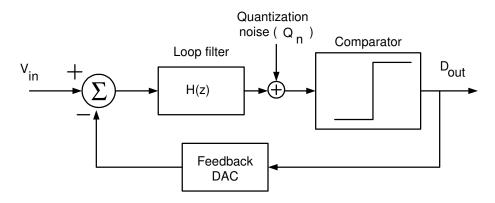

| Fig. 2.14. | Block diagram of a sigma-delta ADC                                          | 31   |

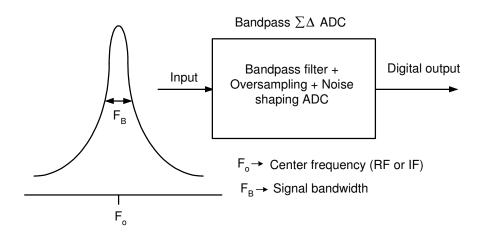

| Fig. 2.15. | Best ADC architecture for software radio                                    | 33   |

|            |                                                                           | Page |

|------------|---------------------------------------------------------------------------|------|

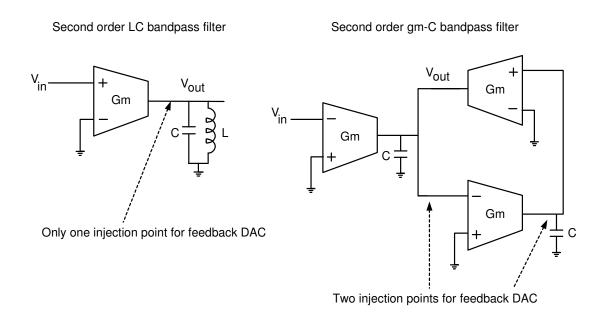

| Fig. 2.16. | Different implementations of integrated bandpass filters                  | 34   |

| Fig. 2.17. | Closed loop operation of a switched capacitor integrator                  | 36   |

| Fig. 2.18. | Schematic of the differential amplifier using NCFF compensation scheme    | 39   |

| Fig. 2.19. | Block diagram of the CRFB architecture for the SC modulator               | 40   |

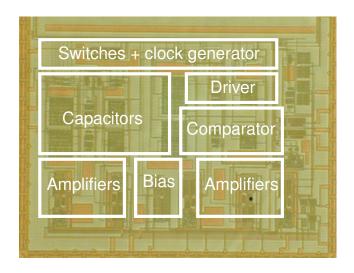

| Fig. 2.20. | Microphotograph of the switched capacitor bandpass $\Sigma\Delta$ ADC     | 41   |

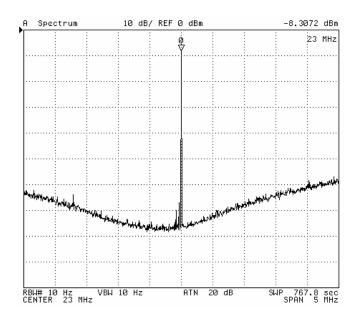

| Fig. 2.21. | Measured noise transfer function of the SC ADC                            | 41   |

| Fig. 2.22. | Output spectrum of the SC ADC for 5 MHz span                              | 42   |

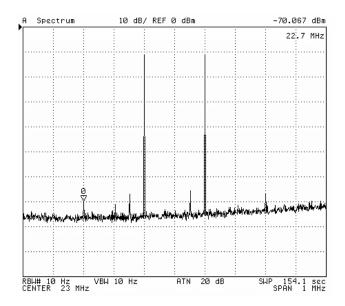

| Fig. 2.23. | Two tone IMD test for -11 dBr input signal                                | 43   |

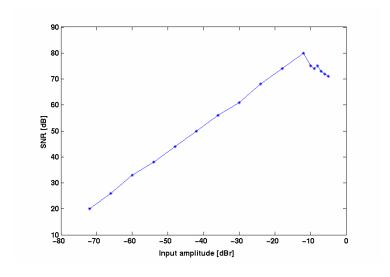

| Fig. 2.24. | Plot of SNR vs input amplitude for 270 kHz bandwidth                      | 43   |

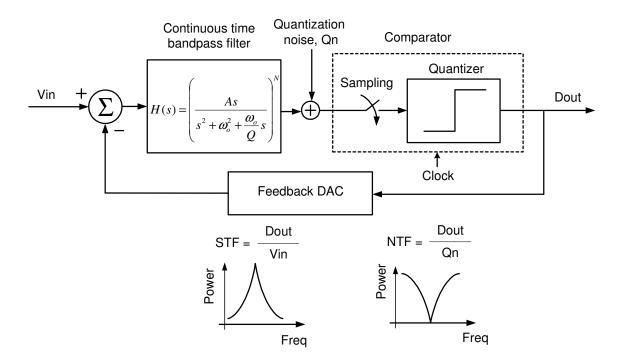

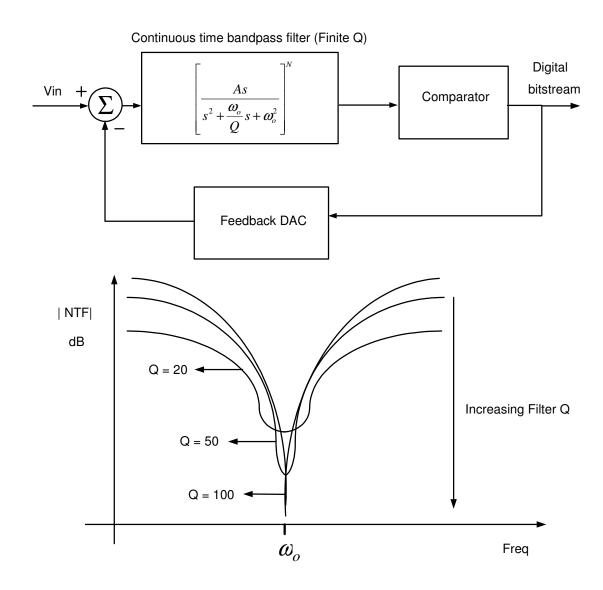

| Fig. 3.1.  | Block diagram of a continuous time bandpass $\Sigma\Delta$ ADC            | 47   |

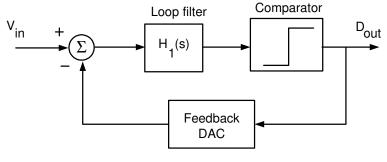

| Fig. 3.2.  | Block diagram of single loop and cascaded $\Sigma\Delta$ ADC architecture | 49   |

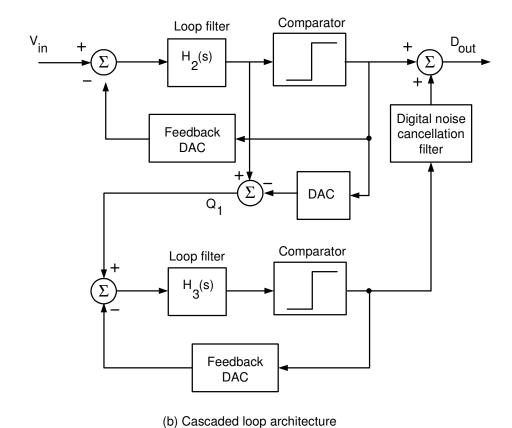

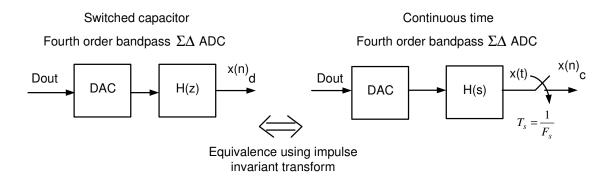

| Fig. 3.3.  | Open loop equivalence of continuous and discrete time $\Sigma\Delta$ ADC  | 52   |

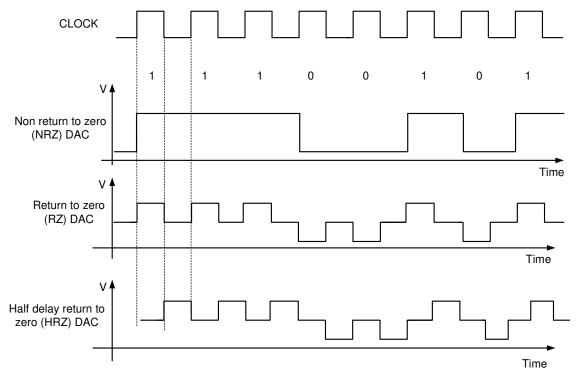

| Fig. 3.4.  | Different types of DAC pulse shapes                                       | 54   |

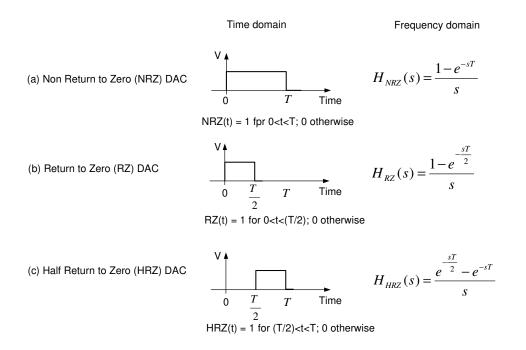

| Fig. 3.5.  | Representation of DAC pulses in time and frequency domain                 | 55   |

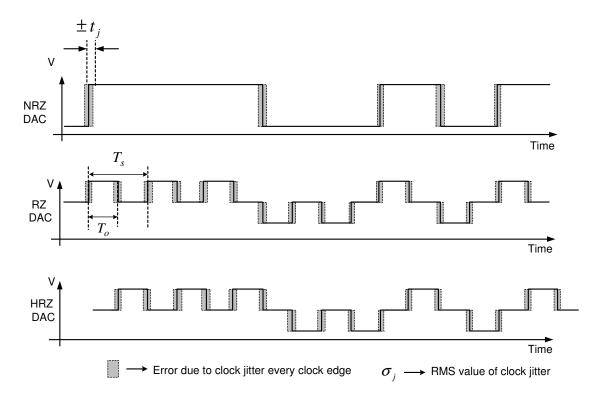

| Fig. 3.6.  | Effect of clock jitter on the DAC pulse shapes                            | 57   |

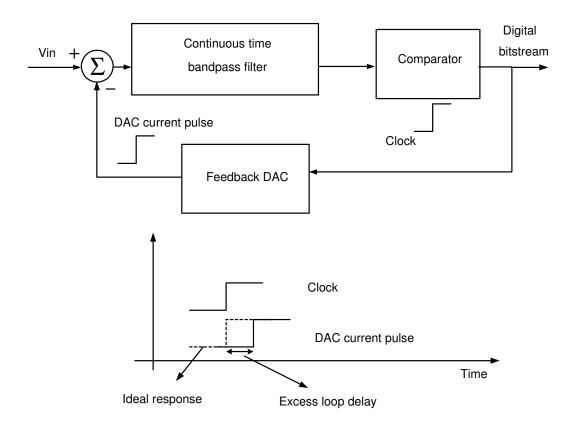

| Fig. 3.7.  | Excess loop delay in continuous time bandpass $\Sigma\Delta$ ADC          | 61   |

| Fig. 3.8.  | Effect of the bandpass filter's finite quality factor on the NTF          | 64   |

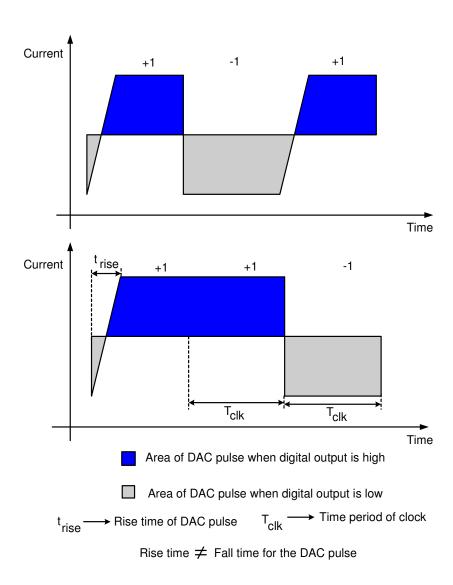

| Fig. 3.9.  | Effect of unequal DAC pulse rise and fall times                           | 65   |

| Pa                                                                             | ıge |

|--------------------------------------------------------------------------------|-----|

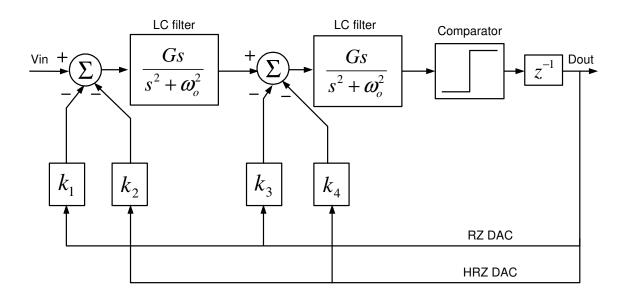

| .10. Architecture used in implementation of Ref [28]                           | 68  |

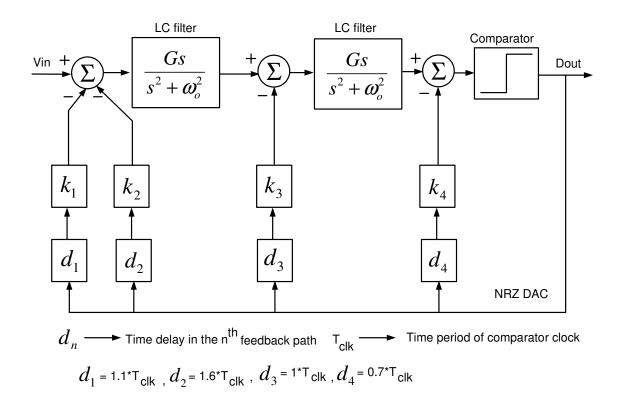

| .11. Architecture used in implementation of Ref [26]                           | 70  |

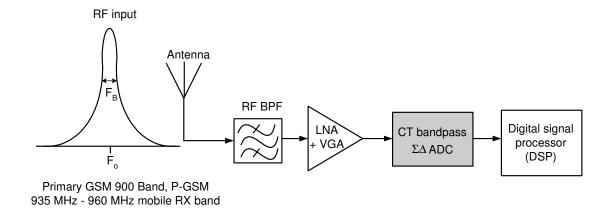

| .1. Target application for the RF ADC design                                   | 72  |

| .2. Calculation of the open loop transfer function                             | 77  |

| .3. Second order continuous time bandpass filter structures                    | 79  |

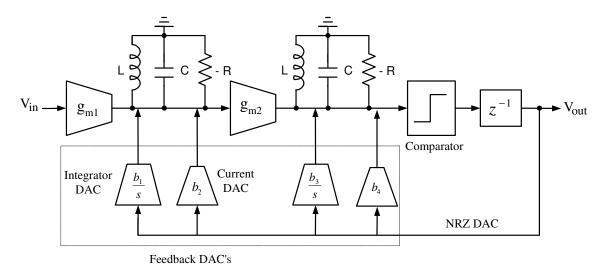

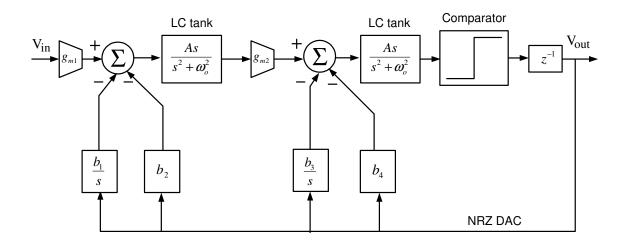

| .4. Block diagram of the proposed RF ADC architecture                          | 80  |

| .5. Transfer function of the proposed RF ADC architecture                      | 81  |

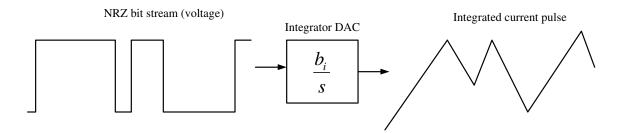

| .6. Typical output waveform of the integrator DAC block                        | 83  |

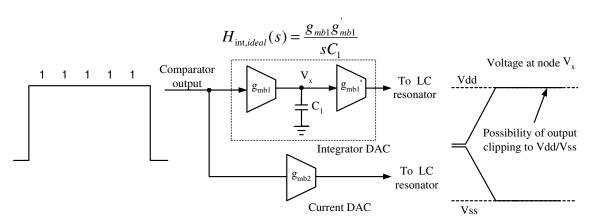

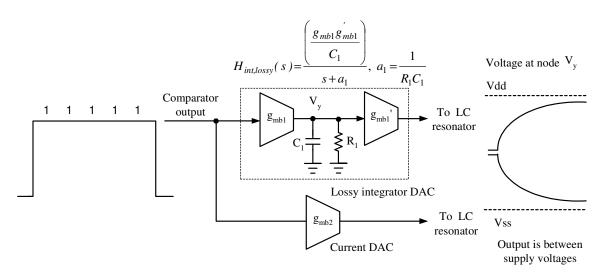

| .7. Schematic of the feedback DAC blocks with ideal integrator DAC             | 84  |

| .8. Schematic of the feedback DAC blocks with lossy integrator DAC             | 85  |

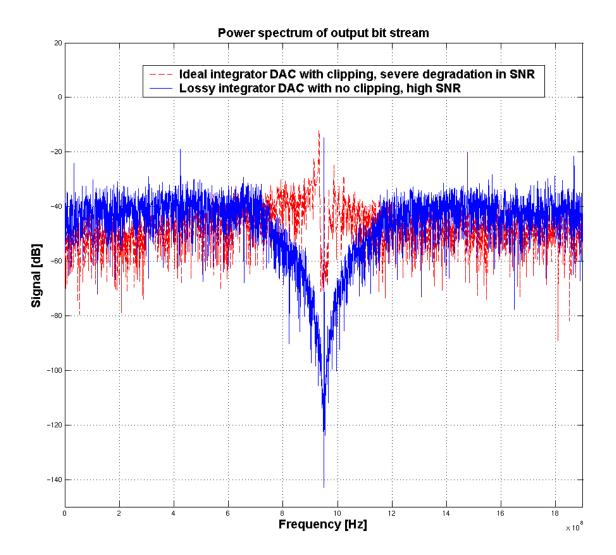

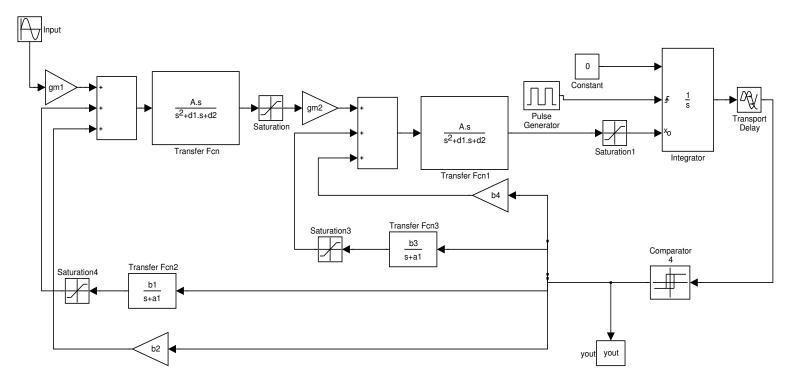

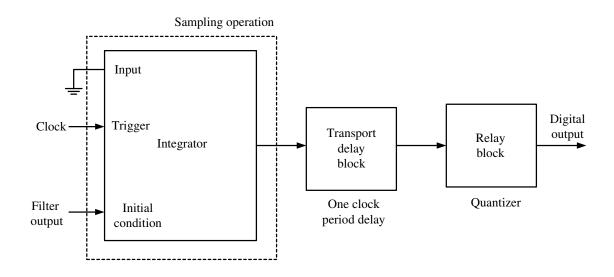

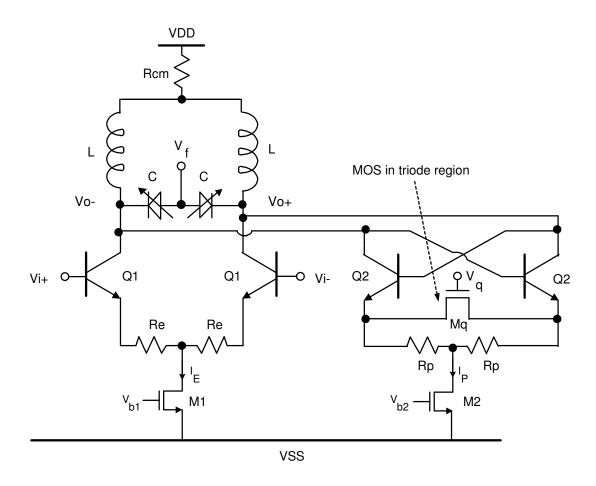

| .9. Output spectrum of the ADC architecture with and without integrator losses | 88  |

| .10. RF ADC architecture in Simulink for behavioral simulations                | 92  |

| .11. Behavioral model of the comparator in Simulink                            | 93  |

| .12. Schematic of the second order Q-enhanced LC bandpass filter               | 98  |

| .13. Post-layout simulation of the bandpass filter – center frequency tuning10 | 04  |

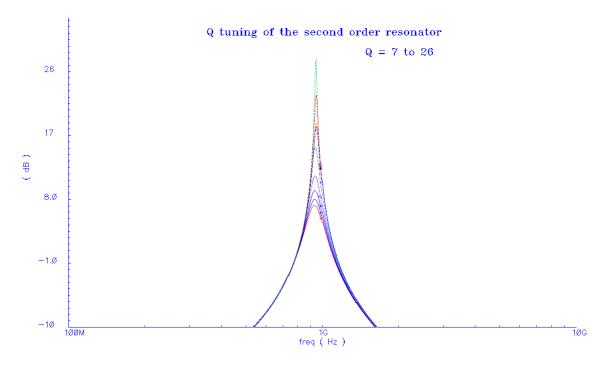

| .14. Post-layout simulation of the bandpass filter – Q tuning                  | 05  |

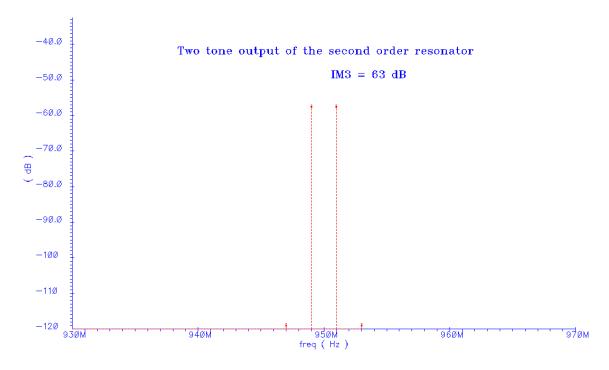

| .15. Post-layout simulation of the bandpass filter – two tone test             | 06  |

| .16. Schematic of the integrator DAC10                                         | 07  |

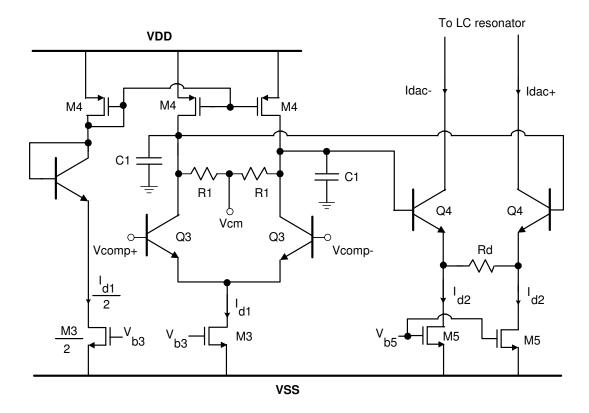

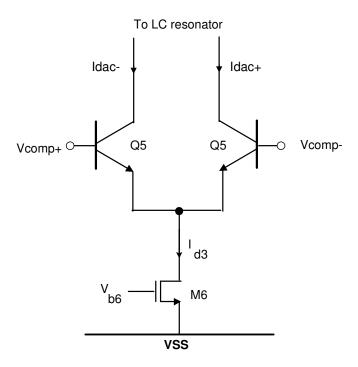

| .17. Schematic of the current DAC1                                             | 10  |

|            |                                                                     | Page |

|------------|---------------------------------------------------------------------|------|

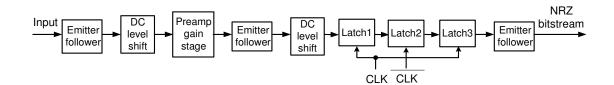

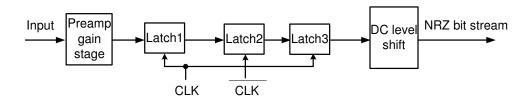

| Fig. 4.18. | Block diagram of the comparator implementation                      | 111  |

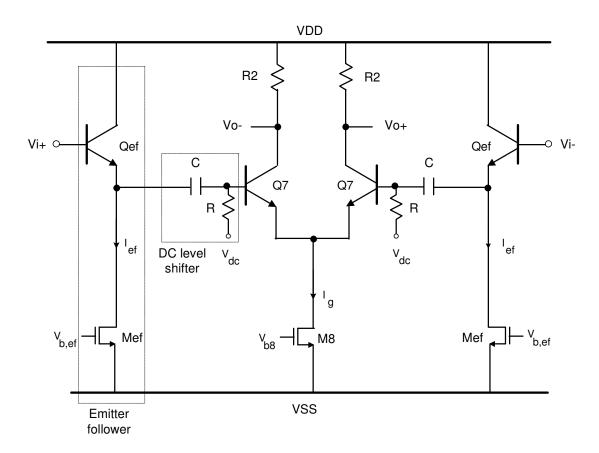

| Fig. 4.19. | Schematic of the preamplifier gain stage                            | 112  |

| Fig. 4.20. | Schematic of the latch                                              | 113  |

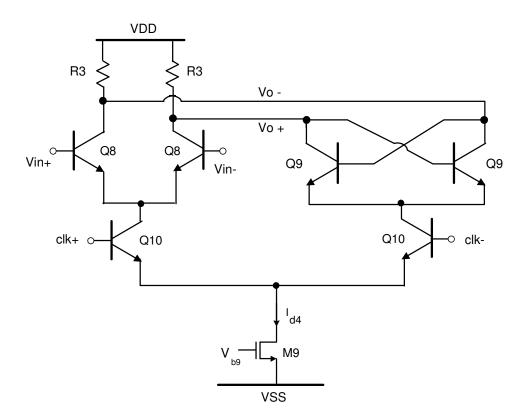

| Fig. 4.21. | Transient post-layout simulation result of the comparator           | 115  |

| Fig. 4.22. | Schematic of the output buffer                                      | 117  |

| Fig. 4.23. | Post-layout simulation of the ADC – output spectrum                 | 119  |

| Fig. 4.24. | Chip microphotograph of the RF ADC                                  | 121  |

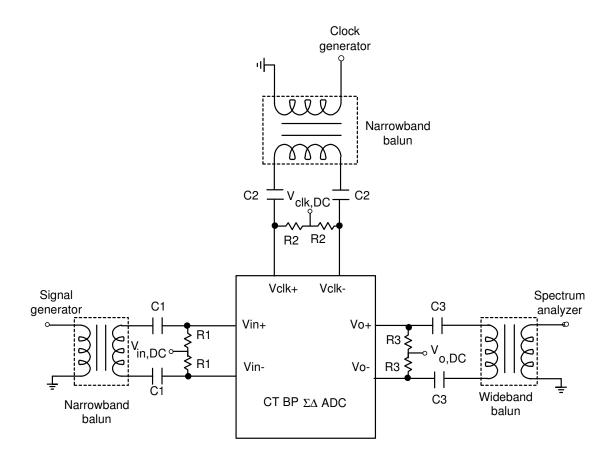

| Fig. 4.25. | Block diagram of the measurement setup                              | 123  |

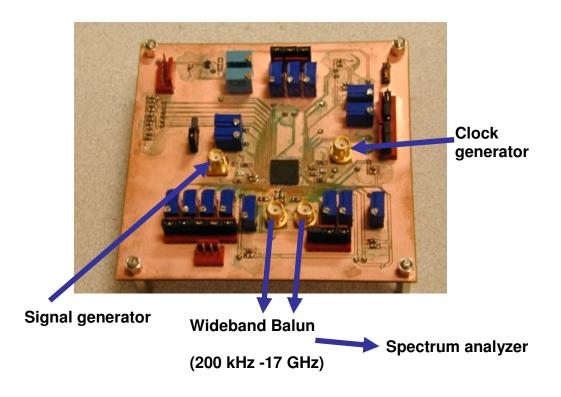

| Fig. 4.26. | Photo of the measurement setup                                      | 124  |

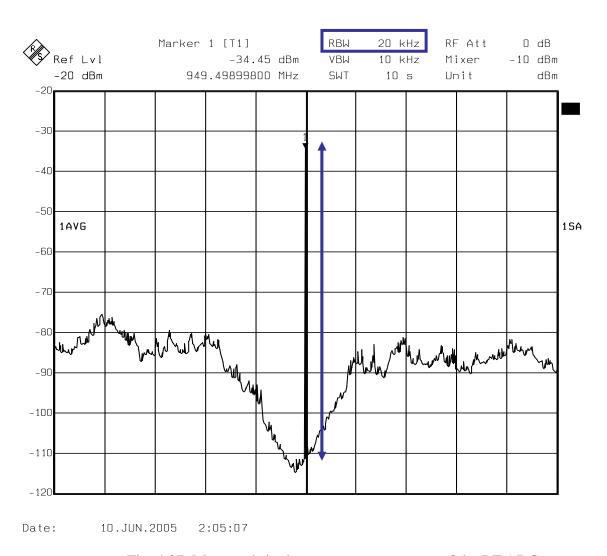

| Fig. 4.27. | Measured single tone output spectrum of the RF ADC                  | 125  |

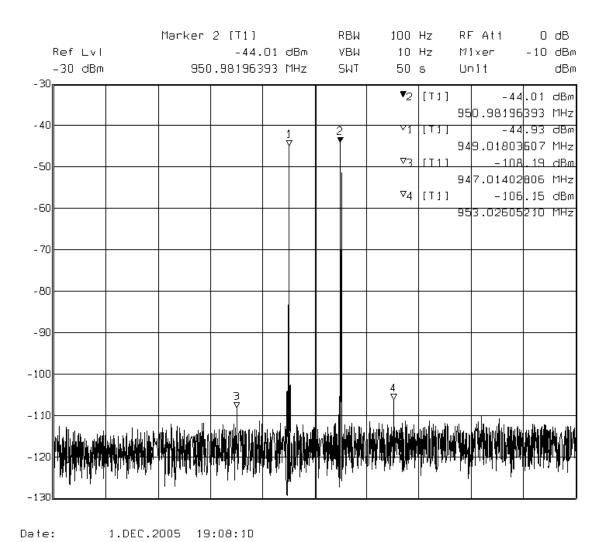

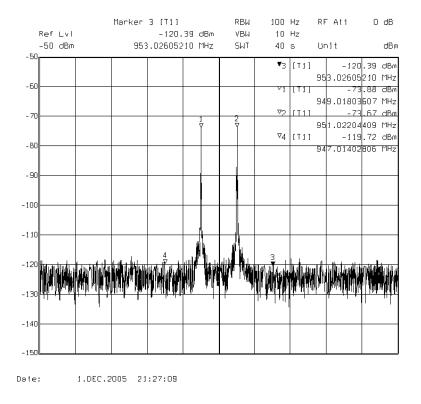

| Fig. 4.28. | Measured two tone output spectrum of the RF ADC                     | 126  |

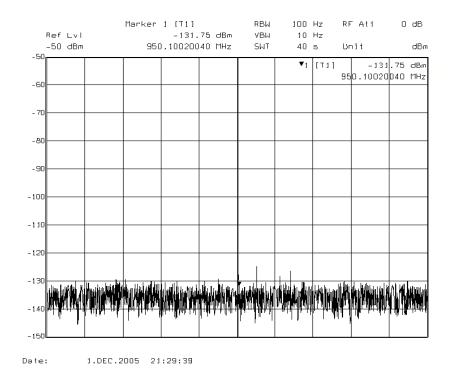

| Fig. 4.29. | Noise floor of the measurement setup with grounded inputs           | 127  |

| Fig. 4.30. | Noise floor of the measurement setup for the two tone input test    | 127  |

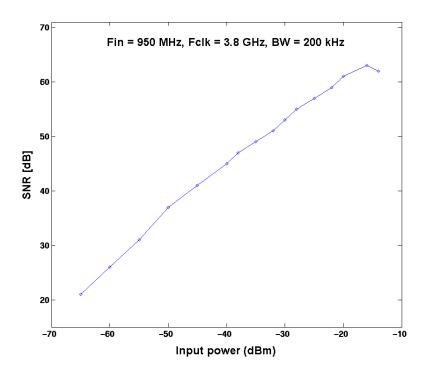

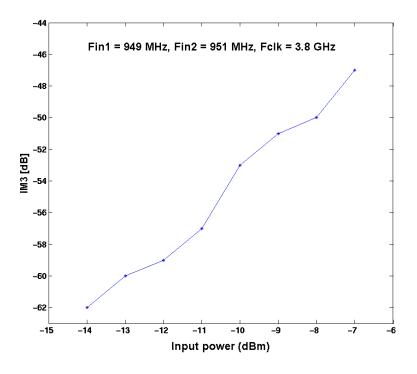

| Fig. 4.31. | Plot of measured SNR of ADC vs input power for the RF ADC           | 129  |

| Fig. 4.32. | Plot of the measured IM3 vs input power for the RF ADC              | 129  |

| Fig. 5.1.  | Target application for the IF ADC design                            | 132  |

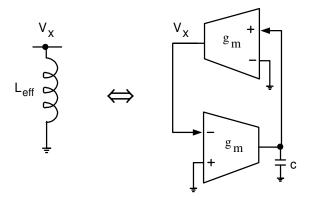

| Fig. 5.2.  | Implementation of a gyrator                                         | 137  |

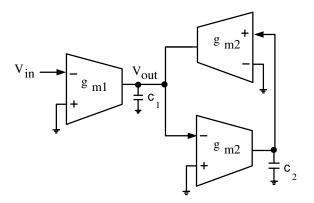

| Fig. 5.3.  | Implementation of an ideal second order g <sub>m</sub> -C resonator | 138  |

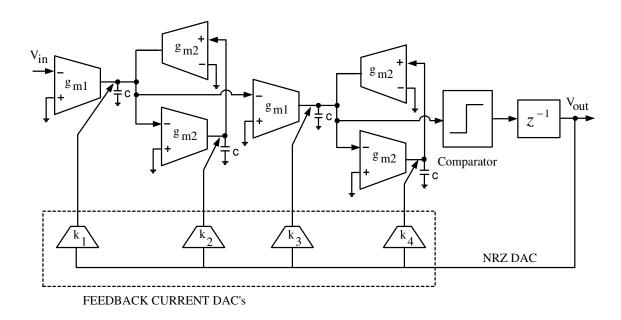

| Fig. 5.4.  | Block diagram of the IF ADC architecture                            | 141  |

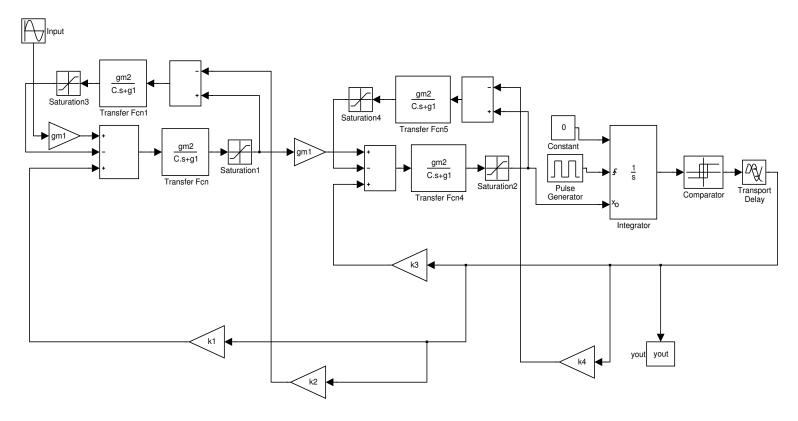

| Fig. 5.5.  | Simulink behavioral model of the IF ADC architecture                | 143  |

|            |                                                                     | Page |

|------------|---------------------------------------------------------------------|------|

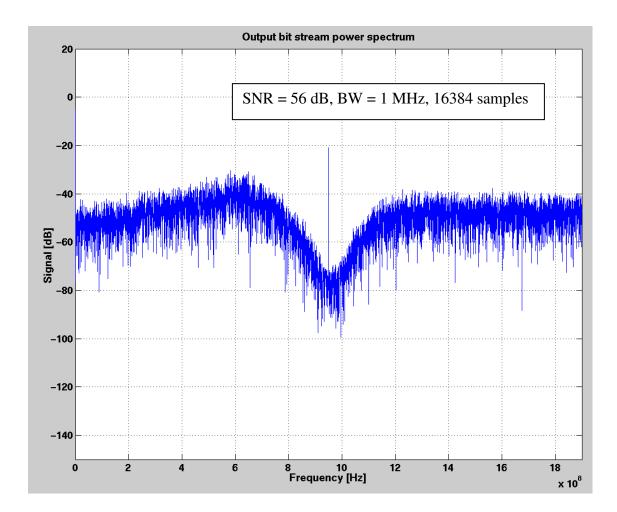

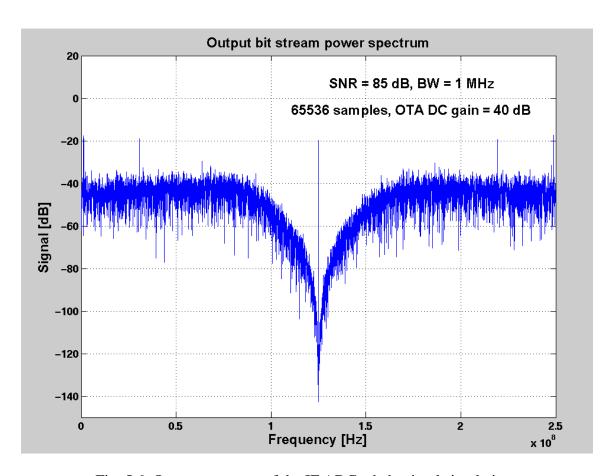

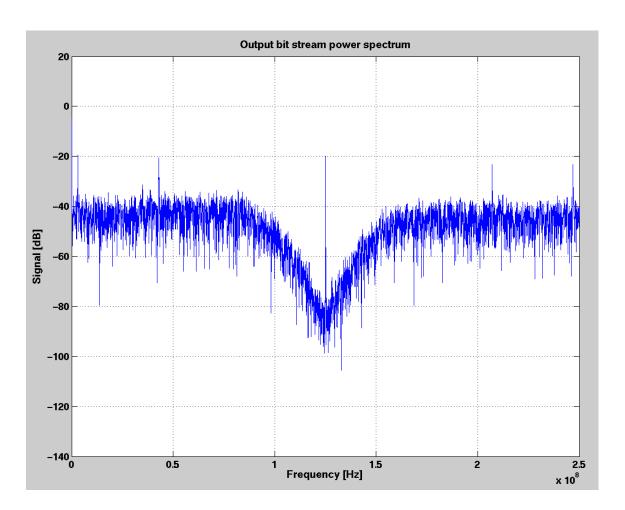

| Fig. 5.6.  | Output spectrum of the IF ADC – behavioral simulations              | 145  |

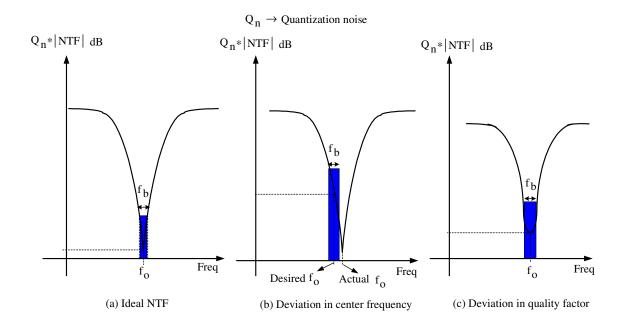

| Fig. 5.7.  | Effect of deviations in center frequency and Q of filter on the NTF | 147  |

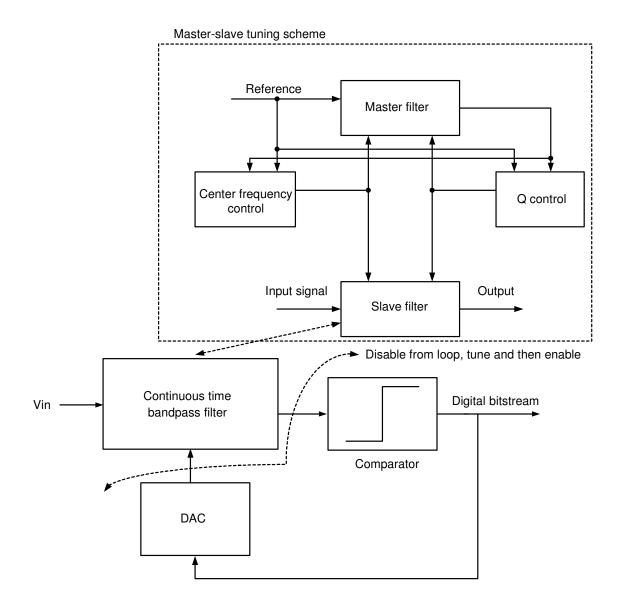

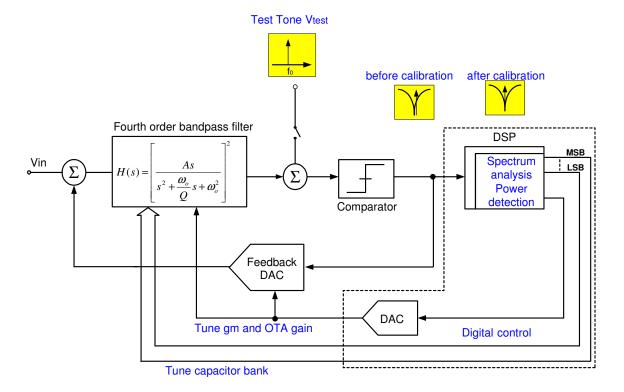

| Fig. 5.8.  | Conventional tuning scheme of a CT BP $\Sigma\Delta$ ADC            | 148  |

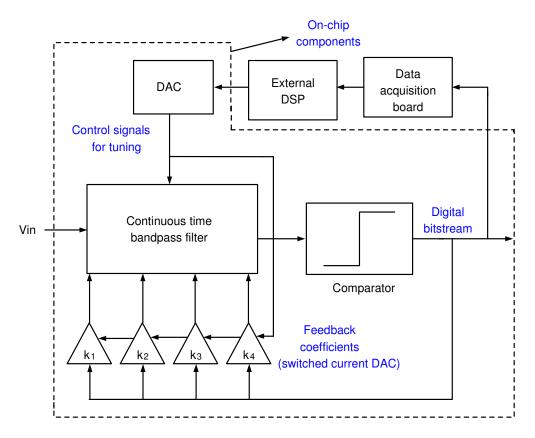

| Fig. 5.9.  | Block diagram of the proposed digital tuning scheme                 | 150  |

| Fig. 5.10. | System level implementation of the proposed digital tuning scheme.  | 152  |

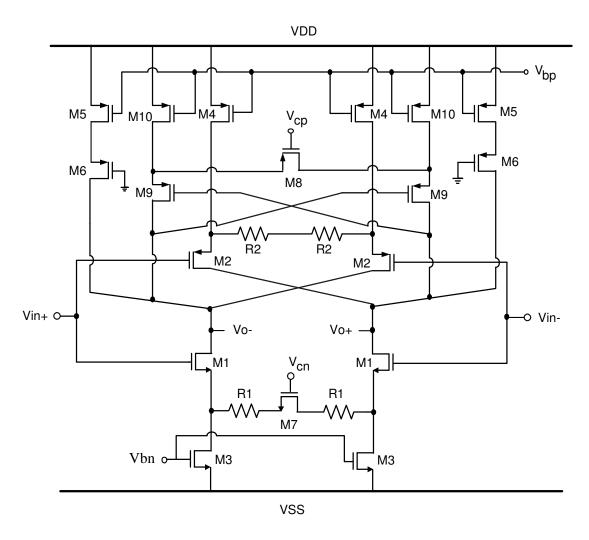

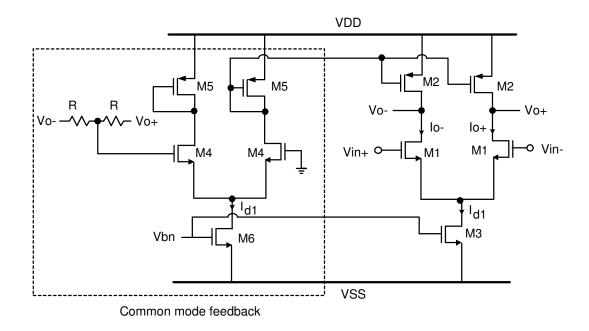

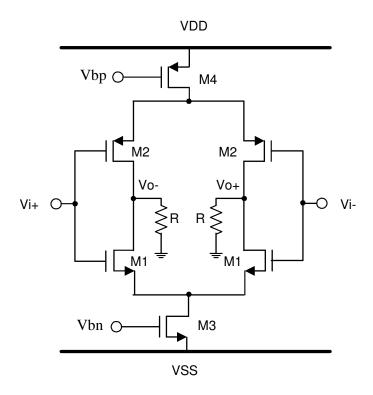

| Fig. 5.11. | Schematic of the linearized fully differential OTA                  | 157  |

| Fig. 5.12. | Schematic of the current DAC                                        | 161  |

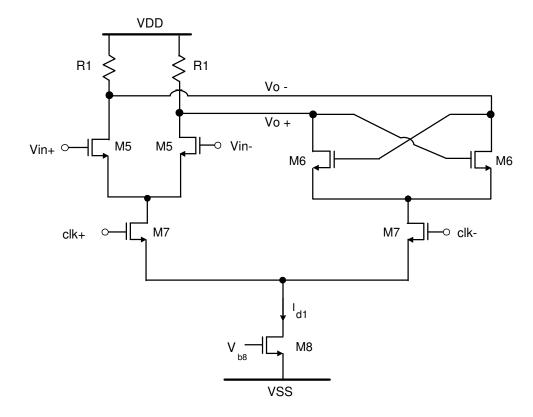

| Fig. 5.13. | Block diagram of the CMOS comparator                                | 162  |

| Fig. 5.14. | Schematic of the preamplifier gain stage                            | 163  |

| Fig. 5.15. | Schematic of the latch                                              | 165  |

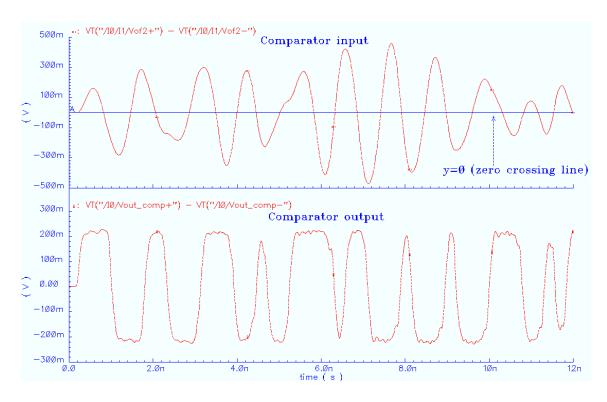

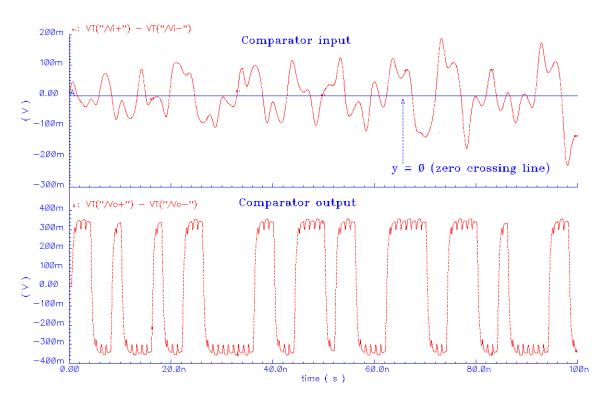

| Fig. 5.16. | Post-layout transient simulation of the comparator                  | 167  |

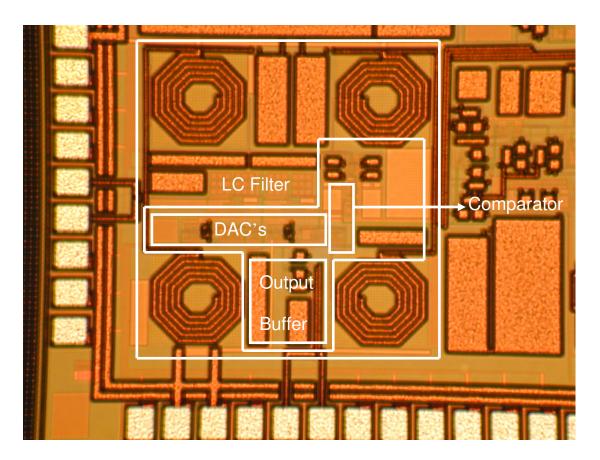

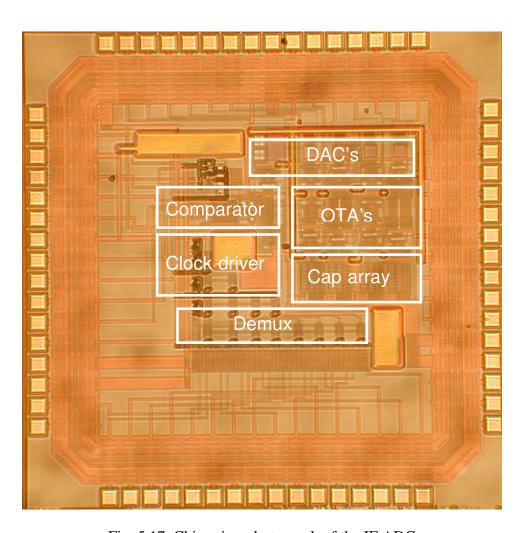

| Fig. 5.17. | Chip microphotograph of the IF ADC                                  | 168  |

| Fig. 5.18. | Output spectrum of the IF ADC from post-layout simulations          | 169  |

# LIST OF TABLES

|             |                                                                  | Page |

|-------------|------------------------------------------------------------------|------|

| Table 2.1.  | Coefficient values for the CRFB architecture                     | 40   |

| Table 2.2.  | Literature survey of RF/IF bandpass ADC's                        | 45   |

| Table 4.1.  | Specifications for the RF ADC                                    | 75   |

| Table 4.2.  | Values of optimized loop coefficients for the RF ADC             | 95   |

| Table 4.3.  | Parameter values for spiral inductor design                      | 101  |

| Table 4.4.  | Component and current values for the LC bandpass filter          | 103  |

| Table 4.5.  | Component and current values for the integrator DAC              | 108  |

| Table 4.6.  | Component and current values for the current DAC                 | 109  |

| Table 4.7.  | Component and current values for the preamplifier gain stage     | 116  |

| Table 4.8.  | Component and current values for the latch stages                | 116  |

| Table 4.9.  | Component and current values for the buffer stages               | 118  |

| Table 4.10. | Current consumption of different ADC blocks                      | 120  |

| Table 4.11. | Comparison of ADC performance                                    | 130  |

| Table 5.1.  | Performance summary of high IF bandpass ADC's in CMOS technology | 134  |

| Table 5.2.  | Specifications for the IF ADC                                    | 136  |

| Table 5.3.  | Values of optimized loop coefficients for the IF ADC             | 144  |

| Table 5.4.  | Target specifications for the OTA                                | 155  |

|            |                                                              | Page |

|------------|--------------------------------------------------------------|------|

| Table 5.5. | Component and current values for the OTA design              | 159  |

| Table 5.6. | Component and current values for the current DAC design      | 161  |

| Table 5.7. | Component and current values for the preamplifier gain stage | 164  |

| Table 5.8. | Component and current values for the latch stages            | 166  |

#### CHAPTER I

#### INTRODUCTION

#### 1.1. Motivation

The wireless communication industry has experienced tremendous growth since the early 1990's throughout the world, especially in Europe, Asia and the USA. The wireless market is poised for more growth in the future, with the demand increasing due to addition of new services which provide more functionality for the end users. One of the main reasons for this growth has been the major progress in the field of radio frequency (RF) integrated circuit design and the design trend is slowly advancing towards a single chip transceiver with very few external components. The major developments in system-on-chip (SoC) design, which enables integration of analog and digital designs on the same chip has led to integration of analog RF, analog baseband and digital signal processors on the same chip. This has resulted in sleek and low power handset devices with multi-purpose functionality like videos, voice, pictures and internet access.

The number of wireless standards has also increased drastically along with the market growth, with each standard catering to specific market segments. The most common wireless communication applications along with some of their standards are shown in Fig. 1.1. The personal communication (cell phones) segment includes standards like GSM (global system for mobile communications), GPRS (general packet radio service), EDGE (enhanced data rate for GSM evolution), CDMA (code division

This dissertation follows the style and format of IEEE Journal of Solid-State Circuits.

Fig. 1.1. Wireless communication applications and standards

multiple access), AMPS (advanced mobile phone systems), UMTS (universal mobile telecommunication system), PCS (personal communication service), TDMA (time division multiple access), DECT (digital European cordless telephone), IS-95 (digital version of AMPS) etc. The wireless local area network (WLAN) for laptops, desktops and PDA's include standards like IEEE 802.15, also known as Bluetooth, for the personal area network (PAN); IEEE 802.11 a/b/g and Wi-Fi for wireless home area networking, IEEE 802.16 a/e and Wi-Max for wide-area high speed wireless zones, in the wireless metropolitan Area Network (MAN) segment, and IEEE 802.20 for the wide area network (WAN). The satellite communication market segment comprising of navigation systems for locating position of objects (such as commercial systems used in cars) use the GPS (global positioning system) standard. Another wireless standard that is gaining popularity recently is IEEE 802.15.3a or UWB (Ultra wide band) for short range

high data rate applications in the local area network segment. The number of wireless standards is increasing everyday with committees being formed in all regions of worlds to define these standards.

The prominent differences between the wireless standards are the geographical area of usage, location in the frequency spectrum of the uplink and downlink channels for base stations and user handsets, channel spacing and the number of channels (total bandwidth of the standard), symbol and chip rates, type of multiple access techniques (time division, frequency division, code division multiple access or a combination of these techniques), type of modulation scheme [some examples include BPSK (binary phase shift keying), QPSK (quadrature phase shift keying), GMSK (gaussian minimum shift keying) etc..], specifications for minimum signal power delivered by the antenna (receiver sensitivity) and maximum transmit power at the transmit side, adjacent channel specifications (blocker specification), etc [1]. There are different governing bodies in each country which regulate the commercial usage of frequency spectrum, which has resulted in adoption of different standards in different regions of the world. The wireless communication service providers all over the world invest lot of infrastructure to support the wireless standards in base stations for their respective coverage areas. The end user devices (cell phones, wireless network cards etc) usually support transmission and reception of signals for only one standard. A major requirement of the next generation of wireless devices and base stations is a single chip set with minimum external components that can support multiple standards. This would enable a single wireless device which makes use of functionality that is supported by multiple service providers.

The support for multiple standards would increase the number of features supported by the mobile devices (internet access, voice, data, pictures etc) with a faster response time. There are many technical challenges, both at hardware and software level that needs to be overcome in order to realize such a multi-standard chip set.

Software radio architecture, which is described in detail in the next chapter, has been proposed as a solution for support of multiple wireless standards in the same chip. The main goal in a software radio transceiver is to perform the analog to digital (A/D) and digital to analog (D/A) conversion as close to the antenna as possible, with reconfigurable software programs running in the backend digital signal processor (DSP). This research deals with the design of analog to digital converters (ADC's) for use in software radio architectures.

#### 1.2. Research contributions

The main aim of this research is to explore new design techniques for radio frequency (RF) and intermediate frequency (IF) ADC's that can be used for digitization in a software radio communication receiver. Different ADC architectures were analyzed and a continuous time bandpass sigma-delta ( $\Sigma\Delta$ ) ADC architecture was found to be the best choice for this application. The main drawbacks of ADC's that have been previously reported in literature were identified and new design techniques are proposed both at architectural and circuit level to overcome these limitations. The integrated circuit implementations of the two ADC designs are then presented in detail.

The first part of this research presents the design of a direct radio frequency (RF) ADC at 950 MHz center frequency using 3.8 GHz clock in IBM 0.25 µm SiGe BiCMOS technology. A fourth order continuous time bandpass  $\Sigma\Delta$  ADC with LC filter was implemented using a new architecture with only Non-Return to Zero (NRZ) digital to analog converter (DAC) to reduce SNR degradation due to clock jitter. The operation of the proposed ADC architecture is examined in detail and extra parameters are introduced in the design to improve the operating range of the ADC. Power optimization techniques are used both at architectural and circuit level to obtain good signal to noise ratio (SNR) with minimum power consumption. The ADC consumes 75 mW of power and measurement results indicate SNR of 63 dB and 59 dB in signal bandwidths of 200 kHz and 1 MHz, respectively around 950 MHz center frequency. The proposed ADC design's power consumption is reduced by a factor of 83, when compared to an ADC reported in the literature for similar SNR performance. The measurement results of the ADC show that high resolution narrowband direct digitization is possible at RF frequencies with low power consumption and enhances the state of art for continuous time bandpass sigma delta (CT BP  $\Sigma\Delta$ ) ADC's operating at GHz sampling frequencies.

The second part of this research deals with the design of an intermediate frequency (IF) ADC at 125 MHz center frequency and 500 MHz clock in TSMC 0.35  $\mu$ m CMOS technology. The fourth order continuous time bandpass  $\Sigma\Delta$  ADC uses an architecture with only Non-Return to Zero (NRZ) DAC and gm-C (transconductance-C) filter, which is ideal for integrated implementation at intermediate frequencies. The gm-C filter uses a novel OTA (operational transconductance amplifier) design which combines cross

coupling and source degeneration to enhance its linearity performance at 125 MHz. A new automatic digital tuning algorithm is proposed to tune the ADC at the system level in order to guarantee the performance over process, voltage and temperature (PVT) variations. The digital bit stream is captured using an external digital signal processor (DSP) and the noise transfer function (NTF) is measured using Fast Fourier Transform (FFT) in the DSP. This information is used to tune the center frequency and quality factor (Q) of the gm-C bandpass filter, and the DAC currents, which maximizes the SNR performance for the ADC. The postlayout simulation of the fourth order modulator show SNR of 50 dB in 1 MHz bandwidth around 125 MHz, while consuming 152 mW of power from supply voltage of  $\pm$  1.65 V.

### 1.3. Organization

The main aspects of analog to digital converters in communication receivers are presented in Chapter II. The different types of architectures for communication receivers are discussed, followed by an analysis of possible ADC architectures for a software radio communication receiver. Chapter III presents an overview of continuous time bandpass (CT BP)  $\Sigma\Delta$  ADC's, which are well suited for use in a software radio communication receiver. The design approach, advantages and disadvantages of CT BP  $\Sigma\Delta$  ADC's are discussed and main drawbacks of implementations reported in literature are identified. A fourth order LC bandpass  $\Sigma\Delta$  ADC which performs direct digitization of RF signals around 950 MHz with 3.8 GHz clock is presented in Chapter IV. The proposed ADC architecture is analyzed in detail and the circuit implementation of the

ADC building blocks are then presented. A detailed description of the test setup and discussion of the measurement results are given at the end of the chapter. A fourth order gm-C bandpass  $\Sigma\Delta$  ADC for digitization of IF signals around 125 MHz with 500 MHz clock is presented in Chapter V. The architecture, circuit implementation and the digital tuning scheme of the IF ADC are described in detail, followed by simulation and measurement results. The final chapter draws some conclusion and provides a summary of this research work, together with possible future research directions for ADC's in software radio receivers.

## **CHAPTER II**

# ANALOG TO DIGITAL CONVERSION IN COMMUNICATION RECEIVERS

#### 2.1. Receiver architectures

The main objective of a receiver for wireless communication applications is to recover the base band signals that are modulated on a carrier wave at radio frequencies. The up converted base band signals are transmitted at over air (channel) using power amplifiers and the signal power at the transmitter output is very high, usually in the Watt range. The carrier signals are corrupted by noise and adjacent band interferers (that coexist in the electromagnetic spectrum) as they propagate through the channel and the signal power at the receiver input (after the antenna) is very low, usually in the nanowatt range. The two main considerations for signals as they pass through the receiver are noise and distortion. The lower bound of the signal is determined by the noise floor and the upper bound is dictated by the distortion components [2]. The lowest signal that can be detected at the input of the receiver is defined as the sensitivity of the receiver and is given by

Sensitivity (dBm) = -174 dBm/Hz + NF (dB) +  $10\log(BW)$  +  $SNR_{min}(dB)$  (2.1) where the NF is the noise figure of the receiver, BW is the bandwidth of the signal and  $SNR_{min}$  is the minimum signal to noise ratio required at the output of the receiver for a given bit error rate (BER). The sum of the first three terms gives the total integrated noise of the system and is usually referred to as the noise floor. Noise figure is a measure of how much noise the system adds to the signal as it passes through it and is defined as

$$NF = \frac{SNR_{input}}{SNR_{output}}$$

(2.2)

The signal bandwidth,  $SNR_{min}$  and sensitivity are usually specified for a wireless standard and the required noise figure of the receiver can be calculated from (2.1).

The nonlinear behavior of receiver gives rise to distortion components and metrics such as P<sub>1dB</sub> (1 dB input compression point), IIP3 (third order input intercept point), IM3 (third order intermodulation distortion), cross modulation etc are used to define the linearity requirements of a receiver. Due to device and component nonlinearities, the signals from adjacent channel mix together with the signal in the required bandwidth, which causes in-band distortion at the output. The wireless standards have desensitization or blocking specifications to determine how strong an adjacent band carrier can exist without corrupting the in-band signal. At the antenna, the power of the desired signal maybe in the order of -112 dBm (0.56  $\mu V_{rms}$  in a 50  $\Omega$ impedance) while the power of the interfering signals in adjacent bands maybe in the order of 30-60 dB higher. Following detection of signals at the antenna, the receiver must amplify the signals, suppress the interferers, translate the RF signals to base band and extract the desired information. The two main metrics that are used to evaluate the performance of a receiver are sensitivity and selectivity. A receiver with a high sensitivity can process weak desired signals in the presence of noise while a receiver with high selectivity can process a desired signal in presence of strong interferers at adjacent frequencies. The specifications of most wireless communication standards require receivers to have both high sensitivity and selectivity performance. In general,

the filters determine the selectivity and the other analog building blocks determine the sensitivity of the receiver. Along with these stringent specifications, all portable wireless devices have an additional requirement of low power dissipation in order to increase the battery life, which adds extra complexity to the receiver design.

The design of a high performance, low power integrated RF receiver in mainstream silicon technologies (CMOS, BiCMOS) is a very challenging task involving numerous tradeoffs during the design process, especially between noise, linearity and power consumption. The first step in the receiver design is to derive the system level performance requirements from the wireless standard specifications. The next step would be the choice of the best architecture for the receiver implementation. Then, the specifications for each building block of the receiver can be determined based on the receiver architecture and system level specifications.

This chapter presents an overview of different types of receiver architectures that are suitable for integrated circuit implementation. The chapter starts with a description of the superheterodyne architecture, which is the most widely used receiver architecture, followed by the direct conversion receiver architecture. The requirements of next generation of wireless communication devices is a single chip receiver that can support multiple standards, but superheterodyne or direct conversion architectures are not well suited for implementing more than one standard. The software radio architecture, which has been proposed as an alternative to the traditional architectures for implementing multiple standards in the same chip, is reviewed in detail. Intermediate frequency (IF) digitization or software defined radio architecture, which is practically feasible for

implementation in current silicon technologies, is also analyzed. The output of all the receiver architectures is in digital format, which can be readily given as input to the digital signal processor (DSP) following the receiver. Different ADC architectures for possible use in software radio implementation are analyzed to identify their advantages and disadvantages for this application. The chapter ends with a survey of ADC's that have been reported in literature for radio frequency and intermediate frequency digitization of signals in communication receivers.

## 2.1.1. Superheterodyne architecture

Fig. 2.1. Superheterodyne receiver architecture

The concept of superheterodyne architecture was introduced by Edwin Armstrong in 1918, where the incoming high frequency signal is down converted to a

lower frequency using a mixer and processed at lower frequencies. This architecture has many advantages for processing a high frequency input signal. The channel selection is implemented by varying the frequency of the local oscillator and range of signals that can be handled is determined by the tuning range of the oscillator. The down conversion of signals reduces the design requirements of receiver implementation as amplification and filtering of signals is easier to achieve at low frequencies rather than at high frequencies [3]. The basic architecture proposed by Armstrong has evolved over the years with minor variations and it is the most popular receiver architecture for wireless communication receivers.

The block diagram of a typical superheterodyne architecture used in modern communication receivers is shown in Fig. 2.1, where the RF signal is converted to base band in multiple frequency translation steps. The incoming signal at the antenna is preselected by off-chip RF bandpass filter (BPF), which is tuned to the RF carrier frequency. The quality factor of the BPF is very high and is usually implemented using off-chip SAW (surface acoustic wave) filters. The signal is then amplified by a low noise amplifier (LNA), followed by an image reject BPF before the down conversion to an intermediate frequency by the first local oscillator (LO1). The IF signal is further filtered by IF BPF and amplified by the variable gain amplifier (VGA) before being frequency translated to base band into parallel in-phase (I) and quadrature (Q) signals by the second local oscillator (LO2). The baseband analog signals are then converted into digital signals using low pass analog to digital converters (ADC) for both I and Q paths.

Fig. 2.2 Implementation of multiple standards using the superheterodyne architecture

The location of the intermediate frequency ( $f_{IF}$ ) is related to the image problem that arises during the down conversion process. The desired signal centered at carrier frequency ( $f_c$ ) is down converted to intermediate frequency  $f_{IF}$  using local oscillator frequency ( $f_c + f_{IF}$ ). However, the signal centered at image frequency ( $f_c + (2*f_{IF})$ ) is also down converted to  $f_{IF}$ , thereby corrupting the desired signal. A higher location of IF helps to provide the maximum attenuation of the image frequencies from the image reject BPF, while a lower IF relaxes the filtering and amplifier requirements for the IF

BPF and the VGA. A minor variation of the superheterodyne architecture such as Weaver image reject [4] architectures has been proposed to overcome the image problem. The current focus of research in RF receiver design is to support multiple standards in the same chip. The typical approach for implementing a multi standard receiver using superheterodyne architecture is to replicate paths for each standard and multiplex it in time using analog switches, as shown in Fig. 2.2. The main problem is that most of the blocks are analog in nature and have to be redesigned for each standard. There is minimal reuse of the components which results in large area and power consumption overhead. This approach becomes impractical as the requirement for number of standards increases and a more reasonable solution is required.

#### 2.1.2. Direct conversion architecture

Fig. 2.3. Direct conversion or homodyne architecture

The direct conversion receiver architecture directly down converts the signal to baseband rather than converting it into an IF first, and image rejection is no longer necessary in this approach. The block diagram of a direct conversion or homodyne architecture is illustrated in Fig. 2.3. The RF signal that comes out of the antenna is filtered by the RF BPF and amplified by the LNA before being down converted directly to baseband along parallel in-phase (I) and quadrature (Q) signals. The frequency translation is performed by using two mixers using 0° and 90° phase shifted local oscillator (LO) signals. The I and Q base band signals are amplified and low pass filtered before the A/D conversion. This architecture eliminates all intermediate frequency components and their associated design challenges, especially the image reject problem. However, two practical implementation problems that have limited the use of direct conversion architectures are DC offset and flicker noise [5]. DC offsets saturate the base band circuits and if uncorrected, degrade the bit error rate (BER) performance of the system. The power spectral density flicker noise of transistors is inversely proportional to frequency and it severely degrades the performance of base band circuits in direct conversion receivers. Direct conversion architectures are also not well suited for implementing multiple standards, as each block has to be replicated for every standard.

#### 2.1.3. Software radio architecture

The term "software radio" is used to define a broad class of radio transceivers where key operations such as modulation and demodulation of signals is done in software and the fundamental aspects of the radio operation can be reconfigured by

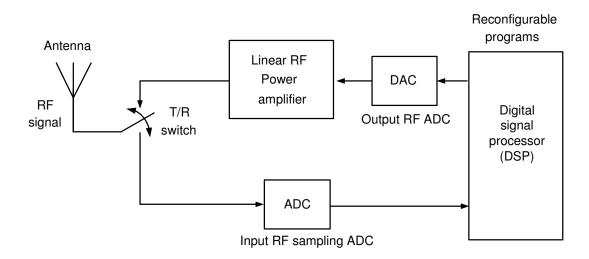

upgrading that software [6]. The concept of software radio was introduced by Joseph Mitola III in 1991 [7] and the block diagram of ideal software radio transceiver architecture is shown in Fig 2.4. The input RF signal is multiplexed in time between the transmit and receive paths through the T/R (transmit/receive) switch. The digital signal information from the DSP is converted to RF output frequencies by the DAC and driven to the channel by the linear power amplifier in the transmit path. In the receive path, the RF input signals are directly sampled and digitized by the ADC. The digital bit stream is given to the backend DSP, where demodulation and other signal processing algorithms results in recovery of the transmitted base band signal.

Fig. 2.4. Ideal software radio architecture

The ideal software radio receiver architecture shown in Fig. 2.4 has some very stringent requirements which cannot be implemented using currently available silicon IC technologies. The input RF signal power varies from a few  $\mu W$  to milli Watts, which

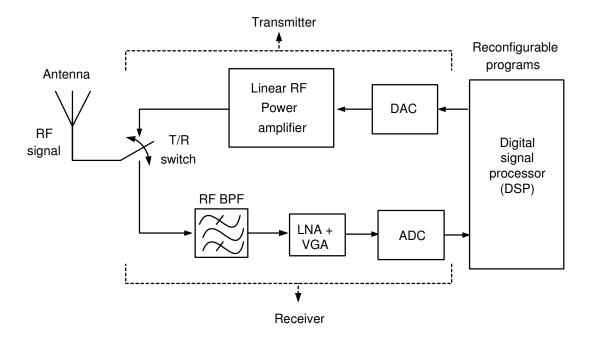

together with distortion and noise specifications translates to receiver dynamic range of around 120 dB. The ADC would require greater than 20 bits of resolution at GHz sampling frequencies, to satisfy the receiver's dynamic range requirement [6]. A modified form of the software radio architecture, shown in Fig. 2.5, greatly reduces the ADC resolution requirements and it is considered for this research. The input RF signal is processed by the RF BPF and amplified by the LNA. The variable gain amplifier (VGA) controls the signal amplitude variations to reasonable levels at the input of ADC. The ADC converts the RF signal to digital output and the analog processing blocks preceding it greatly reduces its dynamic range requirement.

Fig. 2.5. Modified software radio architecture

The two main components of software radio receiver are the RF front end blocks and the back end software platform and algorithms running on the DSP. The main emphasis in a software radio receiver is to perform the A/D and D/A conversion as close the antenna as possible; the modulation/demodulation schemes, protocols, equalization etc for both transmit/receive paths are all determined in software that runs in the digital signal processor (DSP) [7]. Software radio is the flexible and adaptive radio architecture that can provide multiple services, support multiple standards and multiple bands because it can be reconfigured and reprogrammed by the software programs that run in the DSP. This is a broad definition which includes all digital transceivers and software supported adaptability for multiple operations and environments [8]. The ultimate goal in radio receiver design is to directly digitize the RF signal at the output of the antenna and trends in receiver design have evolved towards this goal by incorporating digitization closer and closer to the receive antenna at increasingly higher frequencies and wider bandwidths [9]. The early digitization in the signal path also eliminates need for additional mixers (for down conversion), filters and analog processing blocks, which can result in significant savings in power and area. Additionally, the demodulation of in phase/quadrature (I/Q) in digital domain eliminates the problem of gain/phase mismatches between I/Q paths which occurs when the demodulation is done in analog domain. A new standard can be easily added by writing a software program for the radio interface and upper layer protocols, provided the first analog stage can provide a digitized version of the RF signal. This would require the use of a wideband and high resolution ADC and DAC to cover the frequency spectrum of all standards and their respective channels [10]. The DSP can also be replaced by field programmable gate arrays (FPGA's), any general purpose microprocessors or a combination of these in order to run the required software programs at the data rate output of the ADC. The clock frequency of currently available commercial DSP's is in the 1-2 GHz range and the DSP technology is on pace to support software radio requirements.

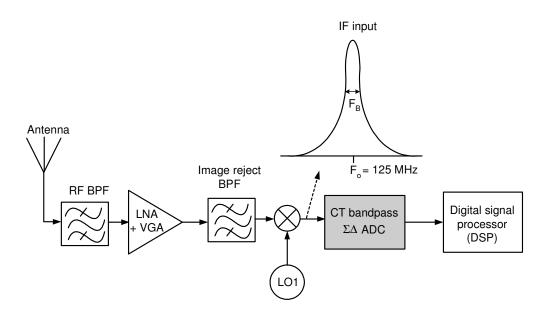

#### 2.1.4. Software defined radio architecture

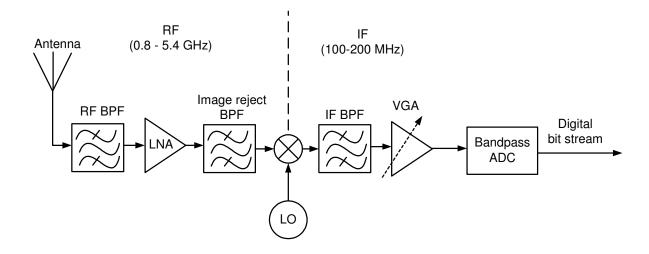

Fig. 2.6. Software defined radio (or) digital IF architecture

Software defined radio is the terminology used in literature to describe the idea of partial band digitization or intermediate frequency (IF) digitization. It is also sometimes referred to as digital radio receiver. The block diagram of a digital IF receiver architecture is shown in Fig. 2.6. The RF BPF selects the required channel(s) from the

signal appearing at the antenna. After amplification by the LNA, the signal is filtered by the image reject BPF to attenuate the components at image frequency. This operation is followed by down conversion to IF by the mixer and LO. The IF BPF further filters the signals and the VGA adjusts the signal strength to be processed by an IF bandpass ADC, which directly gives the digital output to DSP. There is no particular standard for the location of IF signals (though there are standards for location of input RF signals) and the choice of the intermediate frequency is based on the requirements of the IF circuits. The IF bandpass sampling solves flicker noise and DC offset problems which are usually present in base band ADC's. Though IF digitization has most of advantages of configuration of DSP programs, it needs additional analog components and usually supports only a single channel, with channel selection done by an analog filter.

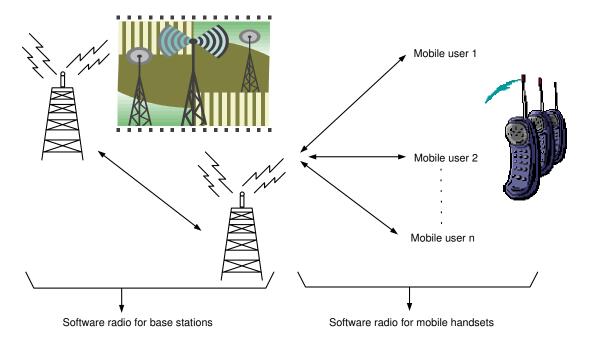

Fig. 2.7. Possible software radio implementations in wireless applications

The most common example of wireless communication application is the cell phone system. The wireless transmission coverage areas are usually divided into cells, with each cell covered by base stations. The hand sets transmit the information to the nearest base station and the signal goes through various base stations before reaching the target system. In this scenario, transmitters and receivers are required both in individual hand sets and in the base stations. A software radio receiver to support multiple standards can be implemented either in wireless base stations or in cellular handsets, as shown in Fig 2.7. Low power consumption is absolutely essential for mobile handsets, but is not a strict requirement for base stations. Large power consumption increases the temperature in base stations, and requires cooling systems to maintain a nominal temperature. The increase in temperature also raises the thermal noise floor (thermal noise is proportional to temperature), and degrades the overall signal to noise ratio (SNR). The thermal noise floor should be at the minimum level for high performance analog systems. To avoid these disadvantages, low power consumption is necessary even for chips operating in base stations.

There would be numerous benefits that would accompany the realization of a software radio architecture. The wide range of existing and new standards in the cellular and mobile marketplace has resulted in the adoption of wide range of hand set and base station architectures for different systems deployed around the world. The ability to develop and manufacture a single reconfigurable terminal, which can be configured at the final stage of manufacture to tailor it to a particular market, presents great benefits to equipment manufacturers. The mobile handset can be used worldwide if all wireless

standards, which are usually specific in one region, are supported in a single terminal. A powerful benefit of a software defined radio terminal, from the perspective of the network operator, is the ability to download new services to the terminal after it has been purchased and is operational on the network. The software radio can also guarantee compatibility between second generation and third generation networks [11]. Suppose a mobile device moves from 3G standard service area (like UMTS) to an area covered only by 2G standard (like GSM), then the device can still function if it supports both standards. This is very advantageous economically for service providers, since a large amount of money has been invested to install and maintain the base stations and the multi-standard support helps in reuse of existing infrastructure. The ability to adapt key transmission parameters to prevailing channel or traffic conditions is another important benefit of software radio. It is possible, for example, to reduce the complexity of the modulation format from 16-QAM (Quadrature amplitude modulation) to QPSK (quadrature phase shift keying) when channel conditions becomes poor, thereby improving noise immunity and decoding margin. It is also possible to adapt the channel coding scheme to prevent particular types of interference, rather than just Gaussian noise, as the device moves form one area to another. Many other parameters like data rate, channel and source coding, multiple access schemes and modulation type can be adapted dynamically to improve quality of wireless service [6]. Cognitive radio is a term used in literature to define an intelligent radio transceiver that makes use of RF spectrum dynamically based on its usage [12]. The functionality of cognitive radio encompasses

software radio together with some artificial intelligence embedded in it. A software radio solution will result in further research on intelligent radio architectures.

The main focus of this research work is to explore new design techniques at both architectural and circuit level for silicon implementation of analog to digital converters for use in software radio communication receivers. The software radio receiver, shown in Fig 2.8, is the target architecture and the ADC's are designed to operate in this framework. The RF ADC directly digitizes the RF signal after the VGA, while the IF ADC converts a frequency translated IF signal to digital output. The main goal of the design process is to obtain the maximum resolution (number of bits or SNR) for both the ADC's with minimum power consumption. The different possible ADC architectures are examined in detail next to identify the best architecture for this application.

Fig. 2.8. ADC for software radio communication receivers

## 2.2. Overview of ADC architectures

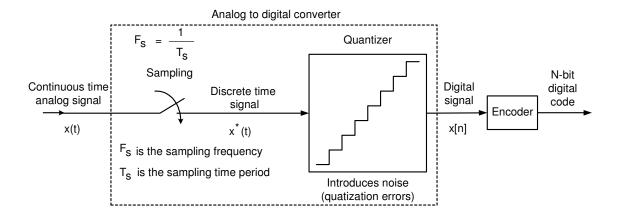

Analog to digital converters are used to transform analog signals (continuous in time and amplitude) to digital signals (discrete in time with amplitude quantization). A generalized analog to digital conversion process is shown in Fig. 2.9. The input analog signal is sampled at a frequency  $F_s$ , which converts it into a discrete time signal. The quantizer block converts the discrete time signal into the nearest digital bit code and the encoder converts it to N-bit output code. The sampler, encoder and the quantizer blocks together form the ADC. The process of quantizing a signal is non-reversible and

Fig. 2.9. Generalized analog to digital conversion process

it results in loss of information, usually accompanied by addition of quantization error. When the full scale voltage of value  $V_{FS}$  is applied to a N bit converter, the quantization step ( $\Delta$ ) is given by ( $V_{FS}$  / ( $2^N$ -1)) and the maximum quantization error is given by  $\pm(\Delta/2)$ . The quantization error has uniform probability density function, provided the quantization errors are sufficiently random in nature [13]. The quantization noise power

spectral density is uniformly distributed between  $(-F_s/2)$  and  $(F_s/2)$  with a magnitude of  $(\Delta^2/12)$ . The main performance measure of an ADC, signal to noise ratio (SNR), is defined as the ratio of the signal power to the integrated noise power over the signal bandwidth (usually measured for a sinusoidal input). It is related to its resolution (number of bits, N) by the following equation [13]

$$SNR (dB) = 6.02*N + 1.76 dB$$

(2.3)

Another performance metric of an ADC is the dynamic range (DR), which is defined as the ratio between maximum input signal power with acceptable distortion to the minimum detectable input signal power level. A signal is said to be detectable if the signal power is just above the noise power (when SNR = 0 dB). Signal to noise + distortion ratio (SNDR) is defined as the ratio of the signal power to the sum of noise and distortion components over the required signal bandwidth. The fundamental limit of noise floor in circuits is given by the thermal noise. The quantization noise floor of the ADC is assumed to be above the thermal noise floor and therefore determines the performance of the ADC. The quantization noise usually dominates the noise floor for ADC's with narrow or small bandwidth, but for ADC's that handle large signal bandwidth, the integrated thermal noise floor limits the performance of the ADC.

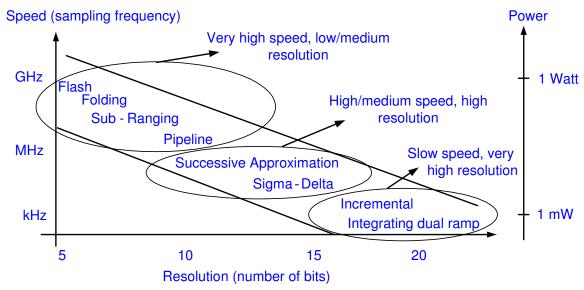

The different categories of the ADC architectures based on their speed, resolution and power is shown in Fig. 2.10. The sampling frequency, number of bits and power consumption are three parameters which tradeoff with each other for all ADC architectures [14]. The flash, folding, sub-ranging and pipeline ADC architectures are in the very high speed and medium to low resolution category, while the successive

Fig. 2.10. Classification of ADC architectures based on speed and resolution

approximation and sigma-delta ADC architectures are in the high/medium speed and high resolution category. The incremental and integrating dual ramp ADC architectures fall in the slow speed and very high resolution category. The power consumption for all ADC's increases at higher sampling frequencies, and is usually in the Watt range for GHz sampling frequencies. The RF ADC for software radio would require sampling frequency in the GHz range while the IF ADC would require sampling frequency in the range of MHz. There are two broad classifications of ADC's based on the relation of their sampling frequency to the bandwidth of the input analog signal, namely Nyquist rate and oversampled ADC's. The sigma-delta ADC is the only architecture in the oversampled category, while all other architectures in Fig. 2.10 belong to the Nyquist rate category.

## 2.2.1. Nyquist rate analog to digital converters

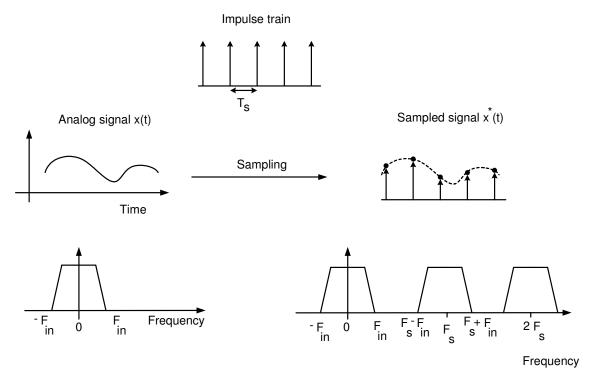

The process of sampling of a continuous time analog signal x(t) at a frequency  $F_s$  (time period =  $T_s = (1/F_s)$ ) in ADC is equivalent to multiplying the signal by impulse trains that repeat every  $T_s$  seconds. Mathematically, the sampled discrete time signal is given in time domain by

$$x^{*}(t) = \sum_{n=-\infty}^{+\infty} x(t)\delta(t - nT_{s})$$

(2.4)

where n is integer and  $\delta$  is the ideal impulse function. In frequency domain, the sampled discrete time signal is given by

$$X^{*}(f) = X(f) * \sum_{n=-\infty}^{+\infty} \frac{1}{T_{s}} \delta(f - n * F_{s})$$

(2.5)

where X(f) is the Fourier transform of the signal x(t). The sampling function modulates x(t) by carrier signals having frequencies at  $F_s$ ,  $2F_s$ ,  $3F_s$  ..etc and in frequency domain, this causes the spectrum of x(t) to be repeated at  $nF_s$  frequencies. The sampling process of an analog signal in time and frequency domain is shown in Fig. 2.11. When the analog signal has a band limited frequency  $F_{in}$ , then it must be sampled at a rate that is greater than  $2*F_{in}$  in order to avoid aliasing, where signal image components at higher frequencies fold back into the signal bandwidth. The Nyquist sampling theorem states that the sampling frequency should be at least  $2*F_{in}$  in order to be able to recover the original signal perfectly from the sampled version. All Nyquist rate ADC architectures have sampling frequency of  $2*F_{in}$ .

Fig. 2.11. Sampling in time and frequency domain

The general components of a Nyquist rate ADC consist of anti-alias filter (to limit the bandwidth of the input signals), sample and hold circuit and multi-bit quantizer. The quantization noise power of Nyquist rate ADC's extends in frequency from DC to F<sub>s</sub>/2, as shown in Fig 2.12. The signals at the input of RF and IF ADC's are located around a center frequency and the bandwidth depends upon number of channels or standards that are required to be converted to digital output. For example, suppose the RF ADC digitizes signals of 1 MHz around 1 GHz, then the Nyquist rate ADC would have a sampling frequency of atleast 2 GHz and will digitize the entire band from DC to 1 GHz. Since there is no inherent filtering in a Nyquist rate ADC, a lot of power is wasted while trying to reduce the quantization noise in the entire Nyquist bandwidth,

which contains frequency components outside the required signal bandwidth. This disadvantage makes Nyquist rate ADC unattractive for software radio applications.

Fig. 2.12. Quantization noise in Nyquist rate converters

## 2.2.2 Oversampled analog to digital converters

The ADC architectures that have a sampling frequency much greater than the Nyquist sampling criterion belong to the category of oversampled ADC's ( $F_s \gg 2*F_{in}$ , where  $F_{in}$  is the bandwidth of the input signal). The quantization noise power extends in frequency from DC to  $F_s/2$  and its root mean square value is the same as that of Fig. 2.12. The main difference is that the in-band quantization noise power is reduced as compared to Nyquist rate since the same power is spread over a much greater frequency range. The oversampling ratio (OSR) of the ADC is defined as  $F_s/(2*F_{in})$  and a 2x increase in sampling frequency results in 3 dB improvement of the ADC's SNR. A

sigma-delta ( $\Sigma\Delta$ ) ADC combines oversampling with noise shaping (using negative feedback loop), which greatly reduces the in-band quantization noise power and results in a high SNR within the signal bandwidth [15]. The negative feedback together with oversampling results in a SNR improvement of 9 dB (1.5 bits) for a 2x increase in the sampling frequency. The frequency spectrum of quantization noise in  $\Sigma\Delta$  (oversampled) ADC is shown in Fig. 2.13.

Fig. 2.13. Quantization noise in oversampled converters

The basic components of a  $\Sigma\Delta$  ADC is shown in Fig. 2.14, and it includes a loop filter in the forward loop followed by a comparator, with a feedback digital to analog converter (DAC) completing the negative feedback loop. While considering a small signal model (a linearized model is used for the non-linear comparator block) and

assuming a unity transfer function for the DAC and comparator, the output  $(D_{\text{out}})$  is given by

$$D_{out} = STF *V_{in} + NTF *Q_n$$

(2.6)

where Qn is quantization noise, STF and NTF are the signal and noise transfer functions.

The STF and NTF of the ADC are given by

$$STF = \frac{D_{out}}{V_{in}} = \frac{H(z)}{1 + H(z)}, NTF = \frac{D_{out}}{Q_n} = \frac{1}{1 + H(z)}$$

(2.7)

Fig. 2.14. Block diagram of a sigma-delta ADC

The digital output ( $D_{out}$ ) then passes through decimation and digital filter blocks, where down sampling is performed to get the final output. The loop filter H(z) is usually implemented a low pass filter and results in a low pass  $\Sigma\Delta$  ADC. When H(z) is a first order discrete time integrator (low pass filter), the loop filter, STF and NTF is given by

$$H_{LP}(z) = \frac{z^{-1}}{1 - z^{-1}}, STF = z^{-1}, NTF = (1 - z^{-1})$$

(2.8)

The NTF has a zero at DC and the quantization noise is high-pass filtered at the output, while the signal is delayed by one clock cycle at the output. The low pass  $\Sigma\Delta$  ADC's offer the advantage of high resolution in a narrow signal bandwidth, but they are still not suitable for RF/IF ADC's in Fig. 2.8 as the quantization noise is shaped over a wide range of frequencies (from DC to the signal bandwidth). The easy solution is to use a loop filter with a bandpass transfer function which results in the ideal ADC architecture for software radio application and is discussed in the next section.

## 2.2.3. Bandpass sigma-delta analog to digital converters

A bandpass  $\Sigma\Delta$  ADC is obtained by replacing H(z) in Fig. 2.14 with a bandpass filter. The following general discrete time low pass to bandpass transformation may be used to obtain a bandpass filter from a low pass prototype [15].

$$z^{-1} \to -z^{-1} \frac{z^{-1} - \alpha}{1 - \alpha z^{-1}} - 1 < \alpha < 1$$

(2.9)

This general transformation moves the zero of the NTF from zero to an arbitrary location below the sampling frequency  $F_s$ . For the case when  $\alpha = 0$ , (2.9) becomes  $z^{-1} \rightarrow -z^{-2}$ . This transformation is widely used because it preserves the properties of the low pass modulator and it is convenient for integrated implementation. If the order of the low pass filter is n, then the transformation results in a bandpass filter of order 2n. Using this transformation, the loop filter, STF and NTF of a  $2^{nd}$  order bandpass ADC is given by

$$H_{BP}(z) = \frac{-z^{-2}}{1+z^{-2}}, STF = z^{-2}, NTF = (1+z^{-2})$$

(2.10)

The zeros of the NTF are moved from DC to  $\pm(F_s/4)$ , and the STF delays the signal by two clock cycles. The quantization noise is shaped by a notch transfer function around  $\pm(F_s/4)$ , while the input signals have a bandpass transfer function. This noise shaping results in a high SNR in the signal bandwidth around the center frequency of the bandpass filter [16]. The oversampling ratio (OSR) for a bandpass ADC is defines as  $(F_s/(2*F_{in}))$ , where  $F_{in}$  is the bandwidth of the signals around the center frequency.

The analog signals that have to be digitized in software radio receivers are located at center frequency  $F_o$  (which can be at RF or IF) and the signal bandwidth is  $F_B$ . The quantization noise is attenuated only in the required signal bandwidth instead of the whole Nyquist bandwidth (DC to  $F_s/2$ ), which implies lesser power consumption to obtain similar dynamic range as compared to a Nyquist converter. Bandpass  $\Sigma\Delta$  ADC architecture is the best choice for digitization in software radio receivers, as shown in Fig. 2.15.

Fig. 2.15. Best ADC architecture for software radio

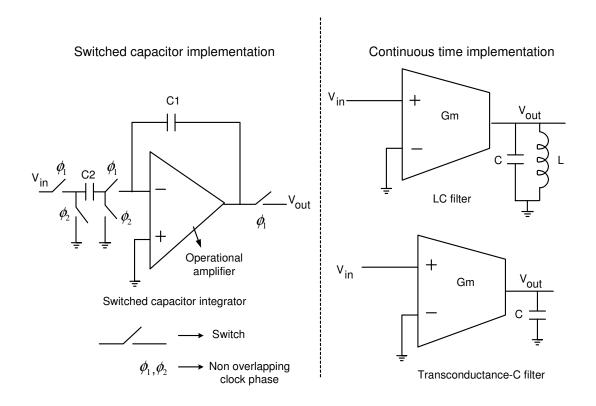

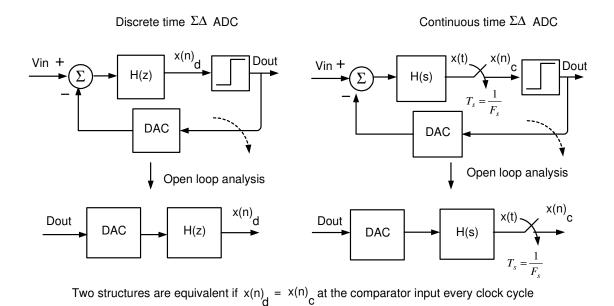

Fig. 2.16. Different implementations of integrated bandpass filters

The bandpass loop filter in  $\Sigma\Delta$  ADC's can be implemented either in switched capacitor (discrete time) or continuous time mode, as shown in Fig. 2.16. The switched capacitor integrator (basic building block of resonator) is realized using capacitors, switches and operational amplifier with local feedback. The center frequency of a switched capacitor bandpass filter is fixed by capacitor ratios (which are very accurate) and it does not require any automatic tuning scheme. The DC gain of the amplifier should be high to guarantee proper closed loop operation of the amplifier. The switching scheme uses two non-overlapped clock phases and the amplifier should settle to the final value within one-half of the clock period. The settling time specification requires the

amplifier which is working in closed loop to have gain bandwidth (GBW) product in the range of 10-20 times the clock frequency [17]. For a clock frequency of 2 GHz, the gain bandwidth requirements would be greater than 20 GHz. The power consumption of such an amplifier would be so huge (> 5 Watts) in mainstream silicon technologies that it is almost impossible to design a system with these building block specifications. It is also difficult to combine both high DC gain and GBW in an amplifier because of contrasting design approaches. Finally, the switches that can be implemented using CMOS or BJT transistors do not operate properly at GHz sampling frequencies. Due to all these limitations, switched capacitor bandpass  $\Sigma\Delta$  ADC's are usually not preferred above sampling frequencies of 200 MHz. To illustrate this point further, design overview and measurement results of a switched capacitor BP  $\Sigma\Delta$  ADC which was done in the initial phase of this research is presented in the next section.

## 2.3. IF switched capacitor bandpass $\Sigma\Delta$ ADC design

Switched capacitor bandpass (SC BP) modulators widely used for direct digitization of narrowband signals around an intermediate frequency in a radio receiver. The main emphasis of research in bandpass  $\Sigma\Delta$  ADC's is to increase the center frequency with a negligible increase in power consumption. The maximum achievable center frequency is directly related to the clock frequency, which is typically limited by the speed of the switched capacitor integrator. Various architectural level techniques such as two-path architecture [18], double sampling resonator [19], double sampling with pseudo two paths [20] and double delay resonator [21] have been proposed to

improve the effective clock frequency of SC BP  $\Sigma\Delta$  modulators. These architectural techniques relax the requirements of the amplifier performance. The limitations of switched capacitor circuits are examined and a compensation technique is proposed to improve the speed of the amplifier. The amplifier is used in the design of a high speed SC BP  $\Sigma\Delta$  ADC.

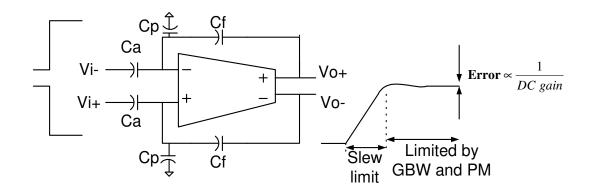

Fig. 2.17. Closed loop operation of a switched capacitor integrator

The SC integrator is the basic building block of a SC resonator (bandpass filter) and the overall speed of the filter is determined by the settling performance of the SC integrator. A switched capacitor (SC) integrator in feedback operation during the integrating clock phase is shown in Fig. 2.17. The closed loop transfer function during the integrating phase is given by

$$\frac{V_0}{V_i} \cong \frac{\partial A_{v_0} \omega_p}{s + (1 + \beta A_{v_0}) \omega_p}$$

(2.11)

where

$$\alpha = \frac{C_a}{C_a + C_f + C_p}, \beta = \frac{C_f}{C_a + C_f + C_p}$$

(2.12)

$\alpha$  is the feed forward factor,  $\beta$  is the feedback factor,  $A_{v0}$  is the open loop DC gain of the amplifier,  $\omega_p$  is the dominant pole of the open-loop amplifier,  $C_p$  is the sum of all parasitic capacitances at the input node of amplifier and  $C_a$ ,  $C_f$  are the input and feedback capacitors. Assuming an amplifier with an equivalent single pole response, as shown in (2.11), the output step response of the SC integrator after the slewing phase is given by

$$V_{out}(t) = -\left(\frac{\frac{C_a}{C_f}}{1 + \frac{1}{\beta A_{v0}}}\right) \left(1 - e^{-\beta \cdot \omega_{GBW} \cdot t}\right) V_{in} + V_o(t_0)$$

(2.13)

where  $\omega_{GBW}$  (= $A_{\nu0}\omega_p$ ) is the open-loop gain-bandwidth product of the amplifier and  $V_o(t_0)$  is the initial condition at the output node. The amplifier's settling consists of two phases: slew rate and linear settling dictated by the  $\omega_{GBW}$  and phase margin of the amplifier [22]. The error in the final settling is inversely proportional to amplifier's DC gain and speed in the linear region is determined by  $\omega_{GBW}$ . For a good settling performance, the amplifier must have a high gain along with high  $\omega_{GBW}$  and good phase margin. The exponential term in (2.10),  $\beta\omega_{GBW}$ , should be large such that the output settles properly within one-half of the clock period ( $T_{clock}$ ). For the worst case operating condition of the SC integrator and a clock frequency of 100 MHz, the amplifier  $f_{GBW}$  should be greater than 980 MHz and 1.3 GHz for a settling accuracy of 0.25 % and 0.033%, respectively. Assuming that the system settles properly within the integrating

phase, the settling error is ultimately determined by the factor  $\beta A_{v0}$ . For a settling error below 0.1 %,  $\beta A_{v0}$  must be greater than 60 dB; hence for  $\beta$  around 0.2 (-14 dB),  $A_{v0}$  must be greater than 74 dB for good settling performance.

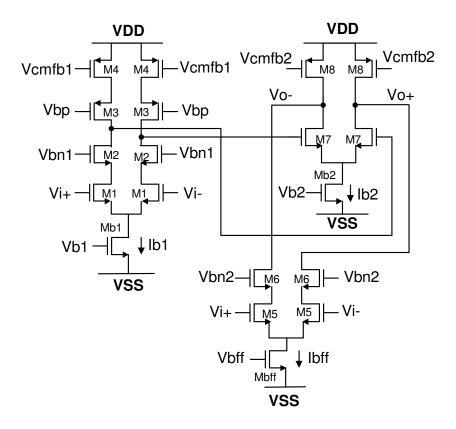

It is difficult to design an amplifier with both high gain and GBW because of contradicting design requirements. High gain amplifiers use cascode and multi-stage architectures, low bias currents and long channel devices, whereas high bandwidth amplifiers use single-stage architectures, high bias currents and short channel devices [23]. Two basic approaches for designing a high gain amplifier are cascode or vertical approach and cascade or horizontal approach. The signal swing in cascode amplifiers is constrained by the power supply voltage, which is a problem for low voltage designs. In cascaded amplifiers, each amplifier stage contributes a pole. Traditional Miller compensation schemes trade bandwidth for stability. The No Capacitor Feed Forward (NCFF) compensation scheme [24] has been proposed to overcome the limitations of Miller compensation schemes. A feedforward path, which has the same phase shift as the direct path, produces a left half plane (LHP) zero. The positive phase shift of LHP zero is used to cancel the negative phase shift of pole, resulting in a good phase margin. This scheme shows a great improvement in bandwidth, along with a high gain and good phase margin. The schematic of the differential amplifier designed in TSMC 0.35 technology using the NCFF compensation scheme is shown in Fig. 2.18. The post-layout simulations of the amplifier show DC gain of 80 dB, GBW of 1.4 GHz, phase margin of 62° and a 0.1% settling time of 2 ns while consuming 4.6 mA of current from a  $\pm$  1.25V power supply.

Fig. 2.18. Schematic of the differential amplifier using NCFF compensation scheme

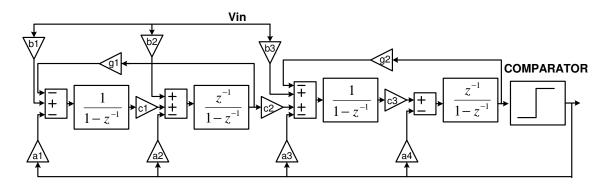

The architecture used for the modulator's implementation is a fourth order cascade of resonators in feedback (CRFB) [25]. The center frequency is located at ¼ of the sampling frequency, for ease of digital demodulation. The coefficients are optimized based on tradeoff between signal swing in the internal nodes, capacitance spread and the maximum SNR attainable with stable operation. The value of capacitor in the first stage is important as its kT/C noise contribution dominates the overall noise performance. The out of band gain of the noise transfer function (NTF) is an important parameter for stability; in this design, this parameter is chosen to be 1.5, giving some margin for PVT variations. Simulations were done in Simulink and Matlab to verify the stability of the

| Coefficients | Value                      |  |  |  |

|--------------|----------------------------|--|--|--|

| a1,a2,a3,a4  | -0.3122, 0, 0.5316, 0.5316 |  |  |  |

| b1,b2,b3     | -0.25, 0.25, 0.125         |  |  |  |

| c1,c2,c3     | 1, 1, 1                    |  |  |  |

| g1,g2        | 2, 2                       |  |  |  |

Table 2.1 Coefficient values for the CRFB architecture

Fig. 2.19. Block diagram of the CRFB architecture for the SC modulator

architecture over typical component variations. The block diagram of the architecture is shown in Fig. 2.19 and the optimized coefficients used in the modulator implementation are given in Table 2.1. Switches are implemented using only NMOS transistors with a boosted clock voltage to reduce the switch resistance. The comparator is a two–stage structure, with a low gain first stage followed by a latch. A single-bit DAC is used to feedback the digital output; the reference voltage used was 0.25 V.

Fig. 2.20. Microphotograph of the switched capacitor bandpass  $\Sigma\Delta$  ADC

Fig. 2.21. Measured noise transfer function of the SC ADC

The microphotograph of the SC BP  $\Sigma\Delta$  ADC designed in TSMC 0.35  $\mu m$  CMOS technology is shown in Fig. 2.20 and it occupies an area of 1.25  $mm^2$ . The bandpass modulator was characterized by directly injecting the output digital bit stream into a