# FAULT SIMULATION AND TEST GENERATION FOR SMALL DELAY FAULTS

A Dissertation

by

# WANGQI QIU

# Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

December 2006

Major Subject: Computer Science

# FAULT SIMULATION AND TEST GENERATION FOR SMALL DELAY FAULTS

A Dissertation

by

# WANGQI QIU

# Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

Approved by:

| Chair of Committee, | Duncan M. Walker      |

|---------------------|-----------------------|

| Committee Members,  | Jyh-Charn Liu         |

|                     | Rabinarayan Mahapatra |

|                     | Weiping Shi           |

| Head of Department, | Valerie E. Taylor     |

December 2006

Major Subject: Computer Science

## ABSTRACT

Fault Simulation and Test Generation for Small Delay Faults. (December 2006) Wangqi Qiu, B.S., Fudan University, China

Chair of Advisory Committee: Dr. Duncan M. Walker

Delay faults are an increasingly important test challenge. Traditional delay fault models are incomplete in that they model only a subset of delay defect behaviors. To solve this problem, a more realistic delay fault model has been developed which models delay faults caused by the combination of spot defects and parametric process variation.

According to the new model, a realistic delay fault coverage metric has been developed. Traditional path delay fault coverage metrics result in unrealistically low fault coverage, and the real test quality is not reflected. The new metric uses a statistical approach and the simulation based fault coverage is consistent with silicon data. Fast simulation algorithms are also included in this dissertation.

The new metric suggests that testing the K longest paths per gate (KLPG) has high detection probability for small delay faults under process variation. In this dissertation, a novel automatic test pattern generation (ATPG) methodology to find the K longest testable paths through each gate for both combinational and sequential circuits is presented. Many techniques are used to reduce search space and CPU time significantly. Experimental results show that this methodology is efficient and able to handle circuits with an exponential number of paths, such as ISCAS85 benchmark circuit c6288.

The ATPG methodology has been implemented on industrial designs. Speed binning has been done on many devices and silicon data has shown significant benefit of the KLPG test, compared to several traditional delay test approaches.

# **DEDICATION**

To my wife, parents and grandmother:

without their support, this would not have been possible.

#### ACKNOWLEDGMENTS

My doctoral study at Texas A&M University has been a great experience, since I started my Ph.D. program in the Fall semester of 2000. The study and dissertation has been supported by many colleagues for more than five years. Texas A&M University provides its students with superb academic freedom, excellent coursework, and a well-developed system, to help her students maximize their achievements.

I would like to thank Dr. Duncan M. (Hank) Walker, my advisor and committee chair, for his advising and kind support from the first day I landed in the United States. He guided me into the electronic design automation field, helped me enjoy the pleasure of research, kept me always going in the right direction, gave me novel ideas, and finally helped me achieve my goals. This dissertation would never have been completed without his advice and encouragement. The treasure I got from him will benefit my whole life.

I would also like to thank Dr. Weiping Shi and his students Xiang Lu and Zhuo Li. We have had very smooth and productive cooperation for years. Dr. Shi is an expert in VLSI physical design and extremely knowledgeable in delay fault modeling. I enjoyed working with him on a variety of projects, from very theoretical to very practical problems. Under his guidance, Xiang and Zhuo developed accurate as well as easy-to-use models for new technology, which greatly simplified my work, with more accurate results.

I am grateful to my committee. Besides Dr. Walker and Dr. Shi, Drs. Jyn-Charn Liu and Rabinarayan Mahapatra gave me a lot of intuitive ideas, effective guidance, helpful suggestions, and personal encouragement. I feel like I am working in a big family and everybody in the family is trying their best to help me succeed. I also greatly benefited from my industrial mentors and colleagues at Texas Instruments (TI) and Philips. Dr. Ananta Majhi at Philips Research did a huge amount of work to apply my research to a real industrial world. The results that he got for me gave me much useful feedback and were extremely important in helping determine our research direction. Hari Balachandran at TI did a lot of work to push my research into industrial production, and helped me get a great opportunity to work as a TIer. I had a wonderful experience at TI working with my supervisor Neil Simpson, colleagues Divya Reddy and Anthony Moore. They gave me more than two years of continuous support, and finally our work was recognized in both academia and industry.

Thanks to my team members: Jing Wang, Lei Wu, Ziding Yue, Hoki Kim, Zoran Stanojevic, Sagar S. Sabade, Ajaykumar A. Thadhlani and Bin Xue. I learned a lot from them during these years. Especially I would like to thank Ms. Jing Wang. She has contributed a huge amount of time and effort to the project, and solved several very critical problems.

My research was funded in part by SRC grant 000-TJ-844 and NSF grant CCR-0098329. I thank these sponsors for providing financial support.

Finally, I would like to thank my wife, Miao-Miao, my parents, and grandmother for their constant encouragement and support. Their love gave me endless confidence to go through hard times during my study. It is my honor to be loved in such a family.

# **TABLE OF CONTENTS**

| 1.   | INTI | RODUCTION                                           | 1   |

|------|------|-----------------------------------------------------|-----|

|      | 1.1  | Delay Testing                                       | 1   |

|      | 1.2  | Traditional Delay Fault Models                      |     |

|      | 1.3  | False Path Problem                                  |     |

|      | 1.4  | Scan-Based At-Speed Test Approaches                 | 7   |

|      | 1.5  | Combined Delay Fault Model – A More Realistic Model |     |

|      | 1.6  | Organization                                        |     |

| 2.   | STA  | TISTICAL FAULT COVERAGE METRIC                      | 13  |

|      | 2.1  | Background                                          | 13  |

|      | 2.2  | Path Delay Correlation                              | 13  |

|      | 2.3  | Delay Fault Coverage Metric                         | 15  |

| 3.   | FAU  | LT SIMULATION                                       | 21  |

|      | 3.1  | Fast Fault Simulation Algorithm                     |     |

|      | 3.2  | Comparison of Simulated Fault Coverage              |     |

| 4.   | TES  | Γ GENERATION                                        | 32  |

|      | 4.1  | Background                                          |     |

|      | 4.2  | Test Generation Flow                                |     |

|      | 4.3  | Path Generation                                     |     |

|      | 4.4  | Heuristics for False Path Elimination               | 47  |

|      | 4.5  | Experimental Results                                |     |

| 5.   | EXP  | ERIMENTS ON SILICON                                 |     |

|      | 5.1  | Philips Experiments                                 |     |

|      | 5.2  | Texas Instruments Experiments                       |     |

| 6.   | SUM  | IMARY AND FUTURE WORK                               | 99  |

|      | 6.1  | Summary                                             |     |

|      | 6.2  | Future Work                                         |     |

| REFE | EREN | CES                                                 | 102 |

| VITA | ۱    |                                                     | 118 |

# LIST OF FIGURES

Page

ix

| Figure 1. Delay variation vs. process variation.              | 2  |

|---------------------------------------------------------------|----|

| Figure 2. An example of a false path                          | 7  |

| Figure 3. Launch-on-capture clock waveforms.                  | 10 |

| Figure 4. Fmax varies with delay test patterns.               | 11 |

| Figure 5. Fault types addressed in this work.                 | 12 |

| Figure 6. An example of structurally-correlated paths         | 14 |

| Figure 7. Delay spaces for different path correlations.       | 15 |

| Figure 8. Delay space of a fault                              | 16 |

| Figure 9. Fault coverage computation.                         | 19 |

| Figure 10. Fault coverage vs. percentage of tested paths.     | 20 |

| Figure 11. Robust propagation path identification.            | 21 |

| Figure 12. Non-robust propagation path identification.        | 22 |

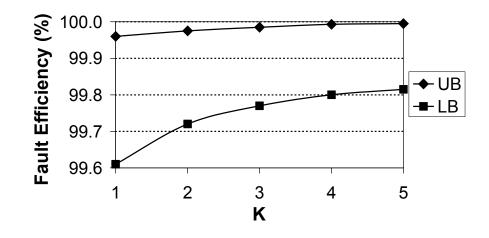

| Figure 13. Fault coverage vs. K (circuit c7552).              | 27 |

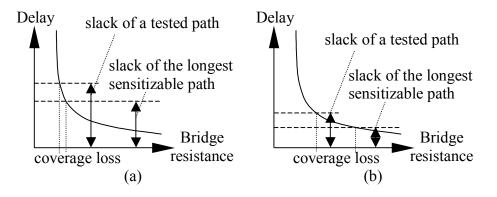

| Figure 14. Delay vs. bridge resistance                        | 29 |

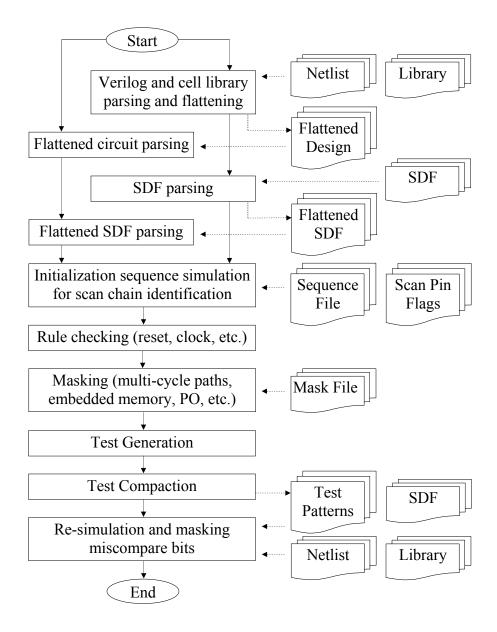

| Figure 15. KLPG test generation flow.                         | 34 |

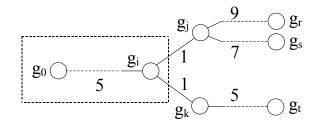

| Figure 16. A partial path and its <i>esperance</i> .          | 38 |

| Figure 17. Search space for a path through a particular gate. | 39 |

| Figure 18. Path generation algorithm.                         | 40 |

| Figure 19. Partial path extension.                            | 41 |

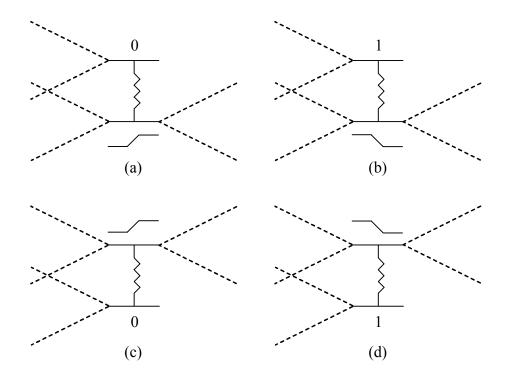

| Figure 20. Examples of direct implications                    | 43 |

| Figure 21. Conflict after applying direct implications.       | 44 |

| Figure 22. Direct implications on scan cells.                                          | 44 |

|----------------------------------------------------------------------------------------|----|

| Figure 23. A pipeline structure.                                                       | 45 |

| Figure 24. A path that passes direct implications but fails final justification.       | 46 |

| Figure 25. Time frame expansion for final justification using launch-on-capture        | 47 |

| Figure 26. Application of forward trimming                                             |    |

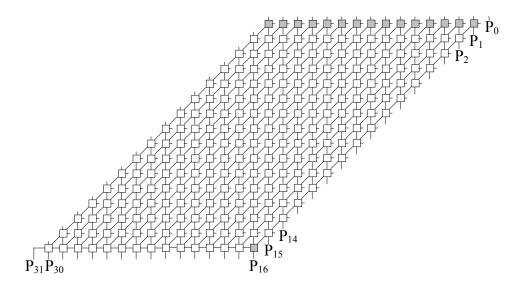

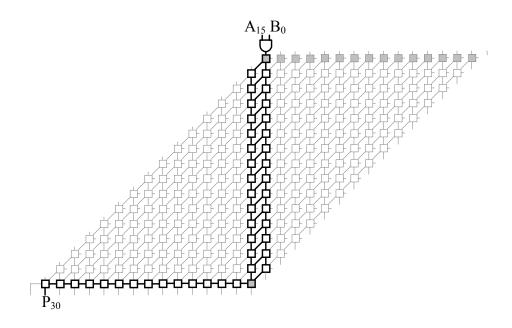

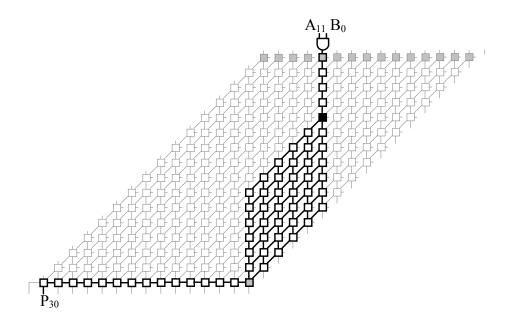

| Figure 27. Structure of ISCAS85 circuit c6288 16×16 multiplier.                        | 49 |

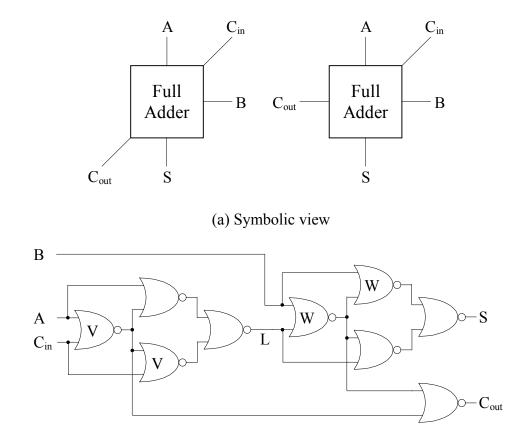

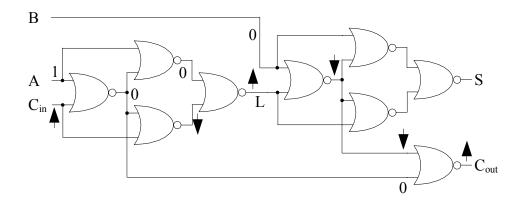

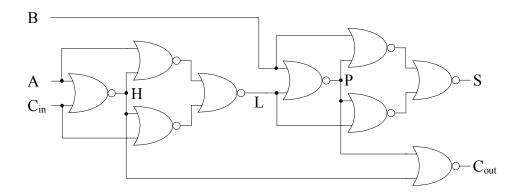

| Figure 28. Full adder module in c6288.                                                 | 50 |

| Figure 29. Longest structural paths in c6288.                                          | 51 |

| Figure 30. A longest robustly testable path through output <i>Cout</i> in a full adder |    |

| Figure 31. Longest structural paths through output <i>Cout</i> in a full adder         | 53 |

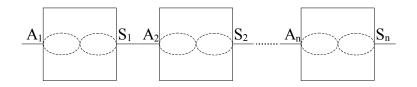

| Figure 32. An adder network example.                                                   | 54 |

| Figure 33. Dynamic dominators in a full adder                                          | 55 |

| Figure 34. Longest structural paths through a particular adder                         | 56 |

| Figure 35. Computation of PERT delay and S-PERT delay.                                 | 57 |

| Figure 36. A circuit with an exponential number of false paths.                        |    |

| Figure 37. Truth table of an AND gate using 7-value algebra.                           | 59 |

| Figure 38. Application of 7-value algebra                                              | 60 |

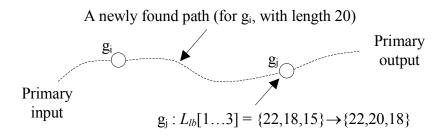

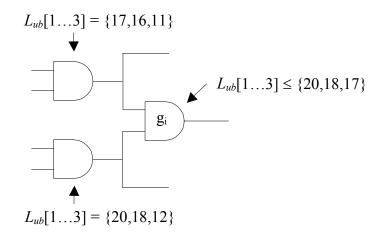

| Figure 39. Updating the lower bound of path lengths.                                   | 62 |

| Figure 40. Updating the upper bound of path lengths.                                   | 63 |

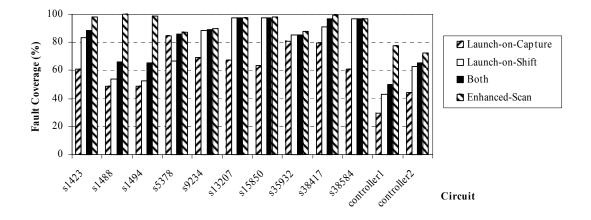

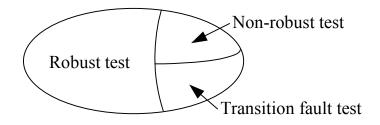

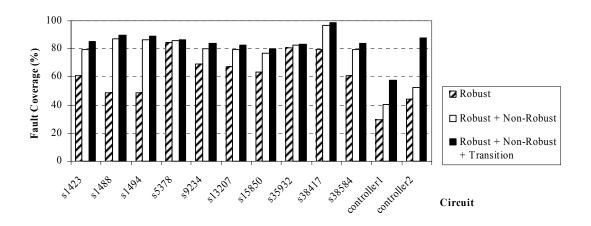

| Figure 41. Comparison of robust test fault coverage.                                   | 72 |

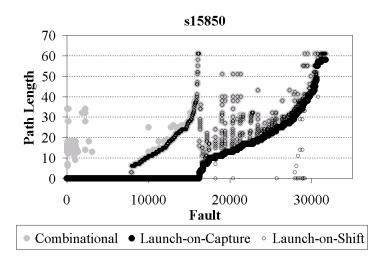

| Figure 42. Path length comparison using LOC and LOS.                                   | 73 |

| Figure 43. Restricted non-robust test in KLPG.                                         | 75 |

Page

# Page

xi

| Figure 44. Top-off transition fault test in KLPG                            | 75 |

|-----------------------------------------------------------------------------|----|

| Figure 45. Test composition of KLPG.                                        | 76 |

| Figure 46. Robust/non-robust/transition fault coverage of KLPG-1 test (LOC) | 78 |

| Figure 47. Test generation for resistive shorts.                            | 80 |

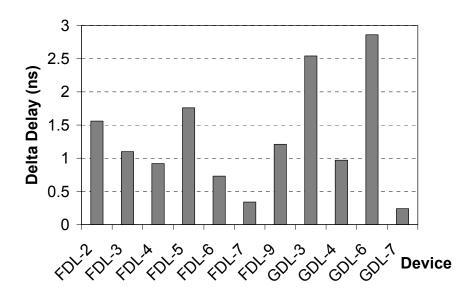

| Figure 48. KLPG tests sensitize longer paths than transition fault tests.   | 86 |

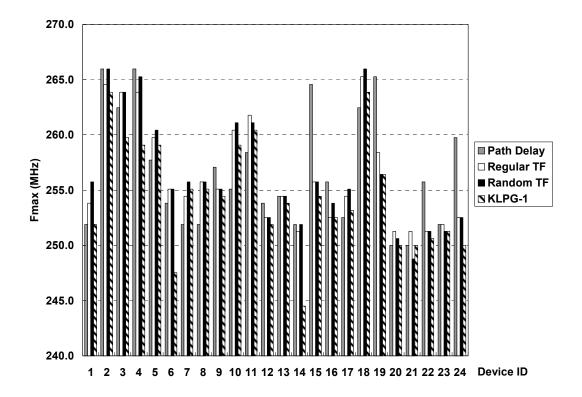

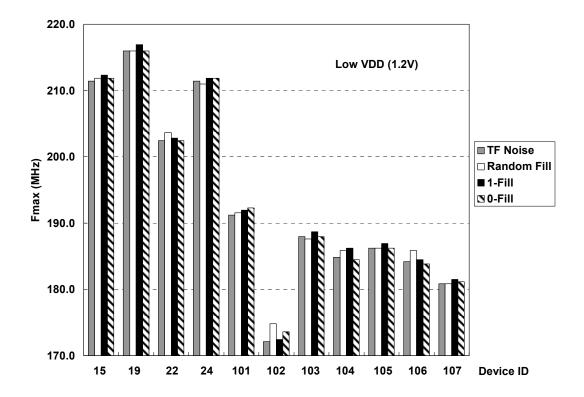

| Figure 49. Fmax comparison using four delay test methodologies              | 89 |

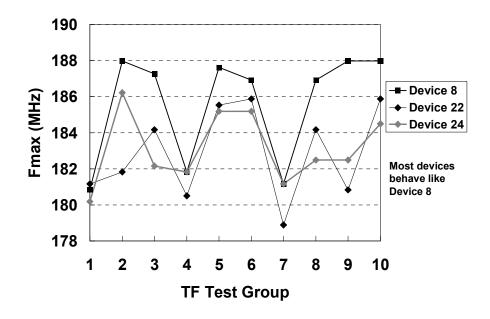

| Figure 50. "Signatures" of devices 22 and 24.                               | 91 |

| Figure 51. "Signatures" of devices 15 and 19.                               | 92 |

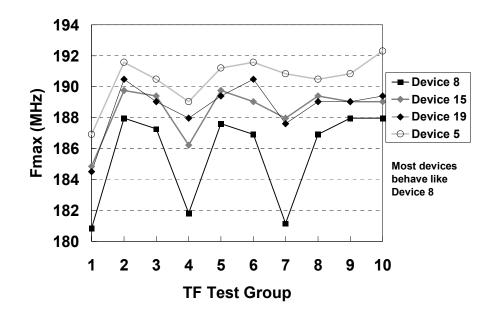

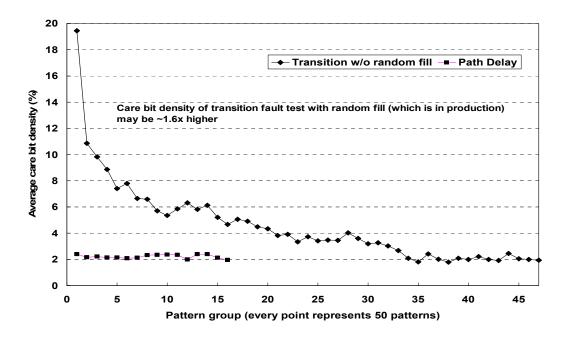

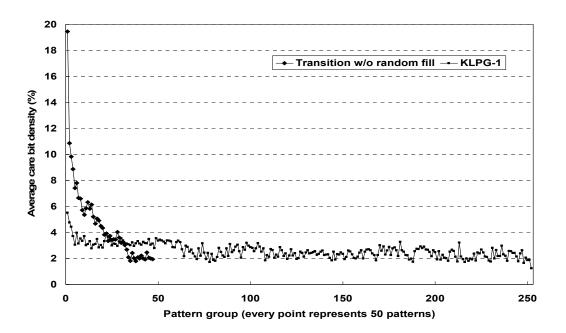

| Figure 52. Comparison of care bit density (TF vs. path delay)               | 94 |

| Figure 53. Comparison of care bit density (TF vs. KLPG-1)                   | 95 |

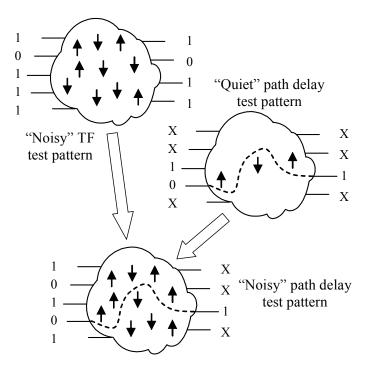

| Figure 54. Making path delay tests more "noisy"                             | 96 |

| Figure 55. Fmax comparison of "noisy" and "quiet" path delay tests.         | 97 |

# LIST OF TABLES

|                                                                                   | Page |

|-----------------------------------------------------------------------------------|------|

| Table 1. Fault coverage comparison for resistive opens and process variation      | 25   |

| Table 2. Fault coverage comparison for resistive shorts and process variation     | 28   |

| Table 3. Fault coverage comparison for process variation only                     | 30   |

| Table 4. Fault coverage comparison using traditional delay fault coverage metrics | 31   |

| Table 5. Maximum delays between input-output pairs in a full adder                | 50   |

| Table 6. Effectiveness of false path elimination techniques (K=3, robust)         | 66   |

| Table 7. CPU time vs. K (robust).                                                 | 69   |

| Table 8. Summary of sequential circuits used in ATPG experiments                  | 70   |

| Table 9. Summary of robust test generation for sequential circuits.               | 71   |

| Table 10. Comparison of test size KLPG-1 vs. TF (LOC)                             | 77   |

| Table 11. Test generation summary for resistive shorts                            | 82   |

| Table 12. Test volume comparison in Philips experiments                           | 84   |

| Table 13. Fmax comparison of KLPG-1 and transition fault tests                    | 85   |

| Table 14. Test volume comparison in Texas Instruments experiments.                | 88   |

#### **1. INTRODUCTION**

## 1.1 Delay Testing

Speed is crucial for high performance semiconductor products such as microprocessors. Due to many types of defects, integrated circuit (IC) fabrication processes produce defective ICs as well as good parts. Electronic testing screens out defective parts and guarantees the quality of shipped parts. Most defects are gross defects that cause errors at any speed (functional failure). However, some small manufacturing defects do not cause functional failure but affect speed. Delay testing detects such defects and ensures that the design meets the desired performance specifications. At smaller geometries, the number of timing-related defects is growing [1], and the effectiveness of functional and I<sub>DDO</sub> testing, which can detect some timingrelated defects [2][3], is reduced. Functional testing is less effective because the complexity of functional test generation grows exponentially with increasing gate counts [4][5]. I<sub>DDO</sub> testing is less effective because a defective device current is difficult to distinguish from the normal quiescent current for 130 nm and smaller technologies [6]. Previous research has shown that 500 defective parts per million (DPPM) would not be achievable without delay testing [7]. Another study has shown that if at-speed tests were removed from the test program for a 180 nm microprocessor design, the escape rate went up nearly 3% [8]. Murphy and ELF35 experiments has also shown that 3 out of 116

This dissertation follows the style and format of *IEEE Transactions on Very Large Scale Integration (VLSI) Systems.*

defective parts escaped when tested at a slower than functional speed at normal operating voltage [9]. The International Technology Roadmap for Semiconductors (ITRS) [10] projects at-speed delay testing as an increasingly important but difficult problem. Rising clock frequencies and the increasing influence of interconnect on circuit delays are making traditional functional and delay test approaches inadequate.

Process variation can also cause timing-related faults (delay faults). Process variations are small natural variations in physical parameters from unit to unit [7][11]. These variations are caused by processing and mask imperfections and various wear-out mechanisms [12]. Process variation can be further divided into inter-die variations and intra-die variations. Inter-die variations are independent of the design implementation, and are considered globally in die-to-die, wafer-to-wafer and lot-to-lot areas [13]. Intra-die variations are dependent of design implementation and are considered locally [12].

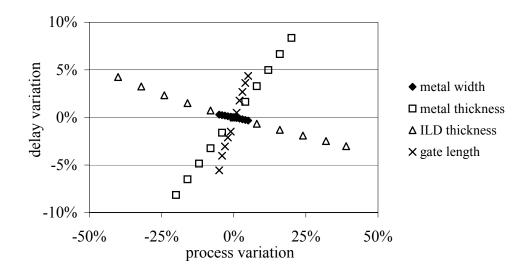

Figure 1. Delay variation vs. process variation.

Circuit delays are highly dependent on process variations because interconnect delays

are dependent on metal width, metal thickness, ILD thickness, via resistance, etc. and device delays are dependent on gate length, gate oxide thickness, etc. [14][15][16][17] Figure 1 shows the SPICE simulation results [12]. Due to process variation, some ICs without defects may also be slower than the specified speed. Delay testing must screen out these devices as well as the defective ones.

Typical delay testing is performed as follows. Each delay test pattern contains two test vectors. The first vector initializes the circuit under test (CUT) and the second vector tries to make transitions at the locations where delay faults are suspected, and propagate the slow transitions to observable primary outputs or memory cells. Logic values are measured in specified time and compared to correct values. A faulty circuit may pass a slow speed test but fail a high-speed test.

## 1.2 Traditional Delay Fault Models

A fault model is an abstraction of a type of defect behavior. A good fault model must be simple as well as accurate so that it can be efficiently used in simulation, test generation and diagnosis. Three classic delay fault models are commonly used in delay testing: transition fault model [18], gate delay fault model [19] and path delay fault model [20].

# 1.2.1 Transition Fault Model

The transition fault model assumes that the delay fault affects only one gate or line in the circuit under test, and the extra delay caused by the fault is large enough to prevent the transition from reaching any observable primary outputs or memory cells within the specified time. In other words, a transition fault can be detected on any sensitized path through the fault site. The transition fault coverage is measured as the percentage of faults that are detected by a test set [21]. This model is simple and it can be applied without any accurate timing models. A transition fault test can be composed by pairing stuck-at-0 and stuck-at-1 test patterns [22] and test generation for complicated sequential circuits has been extensively investigated [23][24][25] for many years. The traditional transition fault test generation algorithm normally selects the easiest path, in terms of high controllability and observability, to propagate a transition, so that the automatic test pattern generation (ATPG) cost is close to minimum. As a result, in most cases the selected paths are short. Furthermore, short paths indicate fewer number of side input constraints, so that the average care bit density of the pattern that tests one fault is low, thus high test compaction rate and low test volume can be achieved [26][27][28][29].

However, recent research shows that resistive opens are one of the major defect types that cause delay faults [30], and that small delay faults cannot be neglected in new technology [31]. As the transition fault model targets relatively large delay faults, its test quality for small delay faults is a concern [32][33].

## 1.2.2 Gate Delay Fault Model

The gate delay fault model is more general than the transition fault model because it considers the amount of extra delay due to a defect. Therefore, a gate delay fault may only be detected through a long path. This model requires an accurate timing model. The quality of a test set is defined as how close the minimum actually detected delay fault sizes are to the minimum possibly detectable fault sizes [34]. However, the actual

minimum detectable fault size is always larger because of process variation, and it varies from device to device. The gate delay fault model always gives pessimistic fault coverage, and it gets worse when process variation increases with newer technology [11].

## 1.2.3 Path Delay Fault Model

The path delay fault model is the most conservative of any of the classical models for delay faults because a circuit is considered faulty if the delay of any of its paths exceeds the specified time. The path delay fault model is more realistic in modeling physical delay defects because it can also detect small distributed delay defects caused by process variation, or the combination of local and distributed delay. However, a major limitation of this model is that the number of paths in the circuit (and therefore the number of path delay faults) can be exponential in the number of gates. For example, ISCAS85 benchmark circuit c6288, a 16-bit multiplier, has close to  $10^{20}$  paths.

Many techniques have been used to reduce the number of paths that must be tested in the path delay fault model. The simplest idea is to test the paths with maximum delays in a circuit. These paths are called the longest paths or critical paths. However, circuit optimization tends to compress the distribution of path delays in a circuit, so many paths are close to the maximum delay [35]. Because of manufacturing process variation, any of these paths can be the actual longest path. Therefore, a group of longest paths must be selected for testing. In practice, the path selection criteria can be based on if the nominal path delay is more than a certain threshold, e.g. 80% of the maximum specified delay of the circuit. It is assumed that the delays of the selected paths bound the maximum circuit delay with high confidence. The path selection is much more realistic if structural and spatial correlations of path delays are used [36], and then the number of paths that must be tested can be significantly reduced. However, delay faults can be caused by both local small defects, such as a resistive short or via, and process variations during IC manufacturing [37], or their combination. The delay faults caused by local small defects are termed local delay faults [38] and those caused by process variations are termed global delay faults [36] or distributed path delay faults [39]. This path selection strategy assumes that delay faults are only caused by global delay faults. Thus if no path through a local delay fault site is selected for testing, the delay fault cannot be detected. To solve this problem, some path selection methods ensure that for every line in the circuit, the longest path through it must be selected [40][41][42][43].

However, the test coverage is unrealistically low using traditional path delay fault coverage metrics due to the fact that only a small subset of paths is tested using any realistic test sets, though some test sets obviously have much higher test quality than others.

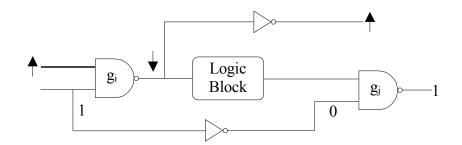

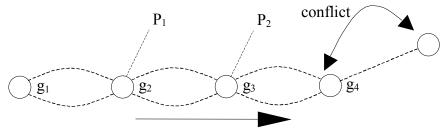

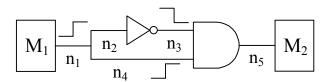

## 1.3 False Path Problem

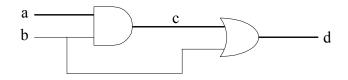

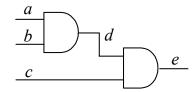

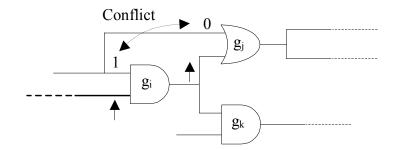

No matter which delay fault model is used, a delay fault is always tested by propagating a transition through a path or a set of paths and observing at the destination of the paths. However, due to logic dependence, not all paths can propagate transitions. These paths are called false paths or untestable paths. For example, in Figure 2, path *a*-*c*-d is a false path under the single-path sensitization criterion [44][45][46][47], because to propagate a transition through the AND gate requires line b to be logic 1 and to

propagate the transition through the OR gate requires line *b* to be logic 0. In this work, the terms "untestable" and "false" are used interchangeably. In fact, most paths are untestable. For example, more than 99% of the paths in ISCAS85 circuit c6288 have been proven untestable [48]. False path problem is the major problem in delay testing ATPG. Earlier approaches are inefficient in testable path generation because they get a list of candidate structural paths from timing analysis tools and check the testability for each path, and most of the paths are untestable. In this work, an efficient methodology is developed and the testability of each generated path is guaranteed.

Figure 2. An example of a false path.

## 1.4 Scan-Based At-Speed Test Approaches

Test speed is another challenge of delay testing. To detect small defects, and sometimes the combination of small defects and slow paths due to process variation, high-test speed is required. Applying a test at the CUT functional speed is called at-speed test. Build-in-self-test (BIST) can be applied at full functional speed, but it has low probability to sensitize enough critical paths, though evidence has been shown that BIST can achieve very high fault coverage for stuck-at and transition faults [49]. On the other hand, functional tests running at full speed are becoming unattractive due to the high cost of development and application [50]. AC scan test using automatic test

equipment (ATE) can solve these problems, though the pin interface speed of a low-cost ATE is normally much lower than the functional speed of the CUT. Fortunately, as high-speed on-chip clock generation using phase-locked loops (PLL), is becoming common in industry, performing an at-speed delay test using low speed ATE channels will no longer be a bottleneck in the near future.

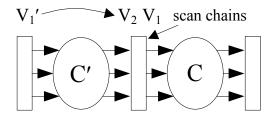

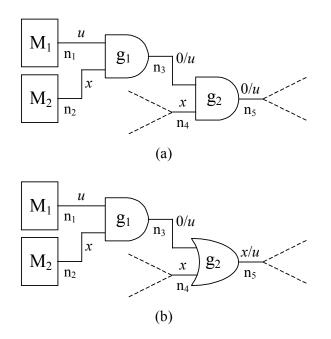

In this work, muxed scan design is assumed, with a scan enable signal selecting either serial scan data or functional logic data. The flip-flops are clocked with the system clock. Two scan-based at-speed test methodologies have found increasing usage in industry.

1.4.1 Launch-on-Shift (Skewed Load)

The procedure for the launch-on-shift (or skewed load [51][52]) test approach is:

1. The circuit is set to scan mode. The first test vector is scanned into scan chains using the slow scan clock, and the values are set on primary inputs (PIs).

2. The second test vector is obtained by shifting the scan chain by one bit. Usually the PIs do not change values due to the constraints from low-cost ATEs.

3. The circuit is set to the functional mode by flipping the scan-enable signals and pulsing the system clock to capture the circuit values in scan cells. The values on primary outputs (POs) are captured if necessary.

4. The circuit is set to scan mode and the values in the scan chains are scanned out using the slow scan clock. This step can be overlapped with step 1.

The advantage of this approach is that fast test generation methodologies for combinational circuits can be applied without many modifications. Scanned flip-flops are considered primary inputs in the ATPG for combinational circuits, and the adjacent scan bit dependencies must be added to the existing ATPG. These constraints may result in some paths being untestable.

The disadvantage of this approach is that the scan enable signals must operate at full speed. In addition, many of the sensitizable paths under the launch-on-shift constraints are sequential false paths, i.e. these paths are not sensitizable in functional mode, so some redundant faults would be detected.

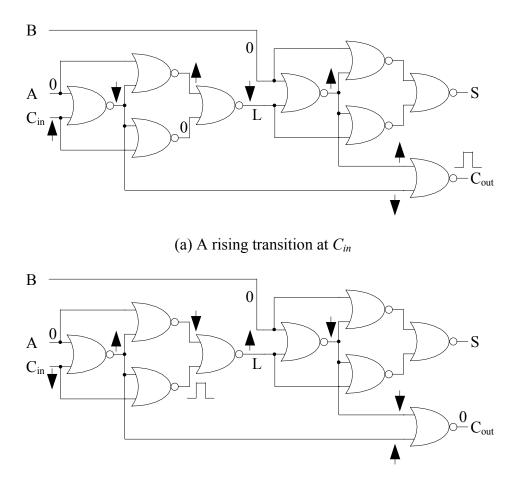

1.4.2 Launch-on-Capture (Functional Justification)

The procedure of the launch-on-capture (or functional justification, broadside [53]) test approach is:

1. Same as the launch-on-shift approach step 1.

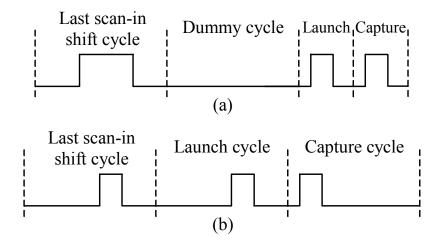

2. The circuit is set to functional mode. A dummy cycle is inserted if the scanenable signal cannot operate at full speed or the system clock frequency is very high, so that the launch clock pulse width is too large. Figure 3(a) shows the clock waveform. For comparison, Figure 3(b) shows the clock waveform if the time is sufficient for the scan enable signal to propagate. In this approach, the launch cycle is kept identical to the shift cycle with respect to period, rising edge, and pulse width.

3. The system clock is pulsed twice. At the first clock pulse, the second test vector is derived from the first vector. At the second clock pulse, the test is performed and the output values are captured in scan cells. The values on POs are captured if necessary.

4. Same as the launch-on-shift approach step 4.

Figure 3. Launch-on-capture clock waveforms.

The advantage of this approach is that it does not require the scan enable signal to operate at full speed. The sensitizable paths under the launch-on-capture constraints are also sensitizable in functional mode, unless the first vector represents an illegal state.

## 1.5 Combined Delay Fault Model – A More Realistic Model

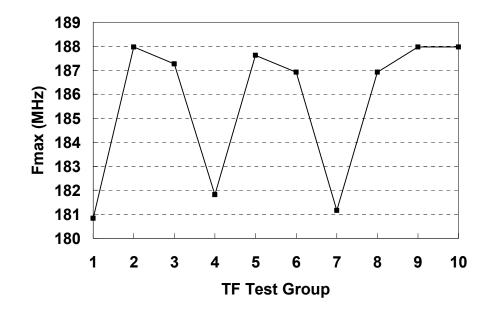

The traditional delay fault models do not completely describe all realistic fault behaviors, and the test quality of the test patterns based on these models is a concern. An experiment has shown that test quality varies from pattern to pattern even within a single transition fault test set, and it is reasonable to expect more variation among different test sets. In this experiment, the transition test patterns are divided evenly into 10 groups by their original order, and speed binning is run to get the maximum passing frequency (Fmax) for each group on the same device. Figure 4 shows the results. A 4% Fmax variation is observed. Higher variation is expected if the test set is divided into more groups, or more test sets are included into the experiment. In theory, a transition fault test set results in close-to-upper-bound Fmax, and it is interesting to find a test that results in the lower bound. To find such a test, a more realistic delay fault model, which more accurately describes fault behaviors, is developed in this work.

Figure 4. Fmax varies with delay test patterns.

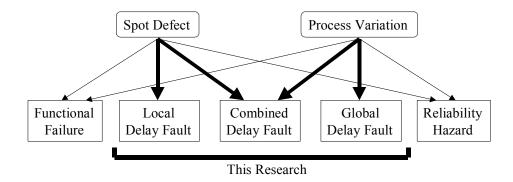

Figure 5 shows a comprehensive fault mechanism. Spot defects and parametric process variation can cause functional failures, delay faults, or reliability hazards. A local delay fault is a local delay increase caused by a spot defect, such as a resistive open or short. The gate or transition fault model targets these faults. Global delay faults are slow paths due to process parameter variation, such as transistor gate length variation. The path delay fault model targets these faults. Combined delay faults (CDF) are delay faults caused by a combination of spot defect and process variation. By considering the entire range of spot defect parameters and process variation, the CDF model encompasses both local and global delay faults. At this time, delays due to capacitive

and inductive coupling [54][55][56][57] are not considered.

Figure 5. Fault types addressed in this work.

# 1.6 Organization

In section 2, statistical delay fault coverage metric is proposed for the CDF model, to more accurately evaluate the test quality of traditional and proposed delay test methodologies. The metric is based on fault simulation that is presented in section 3. To get higher quality tests based on the CDF model, in section 4 an ATPG algorithm is presented and applied to benchmark circuits and industrial designs. In section 5, silicon data shows the accuracy of the new simulation results, and significant test quality increase using the new test generation methodologies. Section 6 concludes the dissertation with future directions.

#### 2. STATISTICAL FAULT COVERAGE METRIC

## 2.1 Background

The traditional metric of path delay fault coverage is the percentage of the paths which are tested under robust [20], non-robust [44], or functional [58] sensitization criteria, that is, coverage = number of tested paths / total number of structural paths. A structural path is a sequence of gates and nets without considering sensitization. Based on this metric, testing p long paths has the same fault coverage as testing p short paths, which does not reflect the real test quality. In addition, since the total number of structural paths is exponential in the number of gates, clearly this fault coverage metric results in very low fault coverage for any practical test set, which is far from the reality. Some research eliminated untestable paths [59][60], and then the coverage = number of tested paths / number of total testable paths. However, these methods are very expensive because the sensitization of all the paths must be checked and the coverage is still unrealistically low (around 20%). For example, as ISCAS85 benchmark circuit c6288 may have an exponential number of testable paths [48], the traditional path delay fault coverage of any practical test is close to zero.

## 2.2 Path Delay Correlation

Any two paths in a circuit have correlation in delays. Two paths have structural correlation when they share a common path segment. For example, in Figure 6 path a-d-e and b-d-e are structurally correlated because they share segment d-e. Two paths can

also have spatial correlation because the path delays are functions of the manufacturing process parameters, such as transistor gate length, which are spatially correlated. For two paths that are physically close to each other, the delay correlation is high because the paths have very similar process parameters.

Figure 6. An example of structurally-correlated paths.

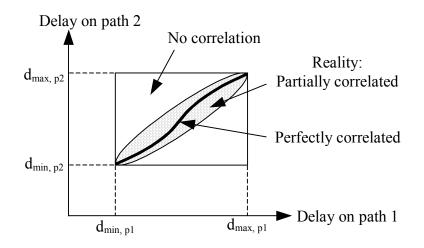

Figure 7 shows the delay space [39] for two paths, assuming the path delay is a onedimensional function of process parameters. The delay space is the bounded region in which the probable delay value combinations are represented. It is assumed that each path has min-max delays. If the two paths have no correlation, the delay value combination can be anywhere within the rectangle. If they are perfectly correlated, the delay space shrinks to a line, which means if path 1 has the max (min) delay under a combination of certain process parameters; path 2 also reaches its max (min) delay under the same combination of process parameters. In reality, the correlation is somewhere in between, and the realistic delay space is the shaded area. Using correlation information, the delays of untested paths can be predicted by the delays of tested paths [61].

An inter-die process variation model [62] is used in this work. In this model, the delay of a path is expressed as a linear function of process variables. If the delay of path  $p_1$  is less than that of path  $p_2$  under any process parameter combination, it is said that  $p_1$

is covered by  $p_2$ . Thus, if  $p_2$  is tested,  $p_1$  does not have to be tested. One limitation of this model is that it does not consider intra-die process variation. However, by assuming 100% intra-die process correlation, the upper bound of delay fault coverage can be computed, as shown in the next section.

Figure 7. Delay spaces for different path correlations.

## 2.3 Delay Fault Coverage Metric

Realistic delay fault coverage can be computed as the percentage of faulty chips that can be detected as faulty by a test set [39][63]. If presented in a probability formula, the coverage for test set t is:

# P(t detects delay fault | chip has a delay fault) (1)

Because this is a general metric and model-independent, to make it usable, it is necessary to map this abstract metric to CDF model, which considers both local and global delay faults.

In the CDF model it is assumed that there is at most one local delay fault (or no local delay fault) that can occur on any single line in the circuit. The position of the local delay fault is termed as fault site. The whole circuit is also subject to process variation, which may cause a timing failure by itself (global delay fault) or in combination with a local delay fault.

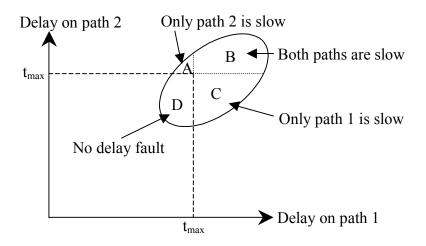

Figure 8. Delay space of a fault.

Under the CDF model, fault detection is probabilistic instead of deterministic. For example, suppose there are two paths,  $P_1$  and  $P_2$ , through a resistive open fault site, and the local extra delay is not large enough for either path to be definitely slow. Figure 8 shows the delay space for this fault.  $t_{max}$  is the maximum specified delay of the circuit. The circuit has some probability that path 1 or 2 is slow (Delay  $< t_{min}$  is not considered in this work). Suppose test set  $t_1$  tests path 1 only and test set  $t_2$  tests path 2 only. Neither  $t_1$ nor  $t_2$  can guarantee the detection of the fault, e.g.  $t_1$  cannot detect the delay fault in area A. Instead, each test set only has some probability of detection. Both test sets are required to guarantee detection. In this work the notion of detection probability (DP) [64] for a single fault site is used.

Using this probability model, the general metric expressed in formula (1) can be translated into formula (2) to compute the DP for fault site *i* with local extra delay  $\Delta$  (the size of the local delay fault):

# $DP_{i,\Delta}(t) = P(\ge 1 \text{ tested path through } i \text{ is slow } |\ge 1 \text{ path through } i \text{ is slow})$ (2)

In the example whose delay space is shown in Figure 8, according to formula (2), if test set *t* tests path 1 only, the DP is area( $B\cup C$ )/area( $A\cup B\cup C$ ); if *t* tests path 2 only, the DP is area( $B\cup A$ )/area( $A\cup B\cup C$ ); and if *t* tests both paths, the DP is 100%.

The above analysis is for a given local extra delay  $\Delta$ . For fault site *i* with an arbitrary  $\Delta$ , the DP for site *i* is computed as:

$$DP_{i}(t) = \int_{d > \Delta_{\theta,i}} DP_{i,\Delta}(t) \cdot p_{i}(\Delta) d\Delta$$

(3)

where  $\Delta_{0,i}$  is the value of local extra delay below which there is no delay fault.  $p_i(\Delta)$  is the PDF of  $\Delta$  at fault site *i*, and is computed using the PDF of delay caused by physical defects, such as resistive opens [31] or shorts [65][66][67].

The overall fault coverage for test set *t* is:

$$FC(t) = \sum_{i} DP_{i}(t) \cdot w_{i} \times 100\%$$

(4)

where  $w_i$  is the weight for fault site i ( $\sum_i w_i = 1$ ).  $w_i$  depends on the location of the fault. For example, the fault sites with many long paths through them are more likely to cause delay faults than the fault sites that have only short paths through them. Therefore, testing more paths through a high weighted fault site is an efficient way to increase the fault coverage.  $w_i$  is also sensitive to the ratio of local/global delay faults. If the ratio is high, the weights are almost equal for all fault sites. If it is low, the fault sites with only short paths can have weights close to zero. In this work, equal weights are used for simplicity.

If no local delay fault is considered, only formula (2) is used in the computation, with  $\Delta = 0$ , and *i* is removed because the whole circuit, instead of a particular site, is considered.

According to formula (2), if the path delays are not independent (and in reality, they are not), the DP computation is dependent on the delay space. For example, in Figure 8, the areas of A, B, C change if the delay space changes, and then the DP changes accordingly. Therefore, if accurate correlation information is not known, the DP computation is not easy. To solve this problem, two extremities are assumed. If no correlation is assumed, path delays are independent variables. This assumption results in the lower bound of fault coverage. If 100% intra-die process correlation is assumed (only inter-die process variation is considered) [62], the upper bound of fault coverage is computed.

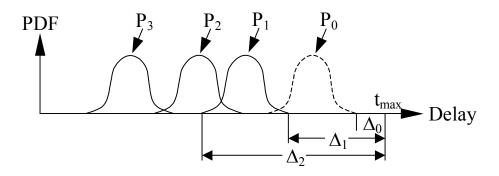

Applying this coverage metric (formulae 2-4) is inexpensive because only a small subset of paths must be considered. For example, Figure 9 shows the delays of four paths, each having a distribution due to process variation, through a certain fault site. Suppose path  $P_1$  is tested by t, and the longest testable path  $P_0$  is not tested. When  $\Delta_0 < \Delta < \Delta_1$ ,  $DP_{i,\Delta}(t)$  is 0; when  $\Delta > \Delta_2$ ,  $DP_{i,\Delta}(t)$  is 100%, because the tested path  $P_1$  is definitely slow; when  $\Delta_1 < \Delta < \Delta_2$ ,  $DP_{i,\Delta}(t)$  increases from 0 to 100% as  $\Delta$  increases. Thus, the fault coverage computation is required only in this interval. The main cost to compute the fault coverage (or test efficiency, which is a more accurate fault coverage because it excludes undetectable faults), which is the number of tested faults over the number of testable faults, is on the sensitization check for all the paths whose length is within this interval. However, if all the structural paths are assumed testable, a lower bound coverage can be computed and experiments show the error on ISCAS85 circuits is <4%. The cost of enumerating structural paths is low because the total number of structural paths through a gate can be computed from the number of paths of its immediate fan-in and fan-out gates.

Figure 9. Fault coverage computation.

The fault coverage metric suggests a test strategy:

1. Apply transition fault tests to detect large local delay faults, and from industrial experience, most local delay faults are large.

2. Apply at-speed test to one of the longest paths, e.g. the path with maximum nominal delay, through each gate or line, to eliminate or reduce the 0-DP area between  $\Delta_0$  and  $\Delta_1$  in Figure 9, because this is the second largest coverage loss factor.

3. Test more possible longest paths (such as  $P_2$  in Figure 9, if  $P_0$  does not exist) to

increase the DP between  $\Delta_1$  and  $\Delta_2$ .

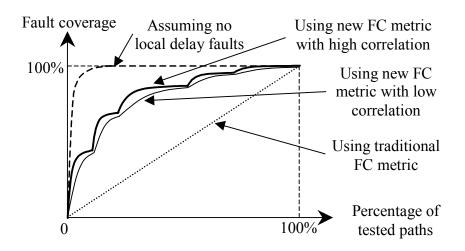

Figure 10 shows the conceptual relation between fault coverage and the percentage of tested paths, using different fault coverage metrics. The paths are sorted by their nominal delays in descending order. If there is no local delay fault, the fault coverage increases quickly after the first several potentially critical paths are tested, and reaches 100% after all potentially critical paths are tested. If the percentage of local delay faults is high (in reality it is), the curves have some "jumps" because at these points the first path through some fault sites is tested. It is clear that the new fault coverage metric is closer to industrial experience and more realistic. The traditional fault coverage is computed as the number of tested paths over the total number of testable paths.

Figure 10. Fault coverage vs. percentage of tested paths.

#### **3. FAULT SIMULATION**

The goal of the CDF simulation is to compute the detection probability for each fault site, for test set *t*. The DP's for all the fault sites are used to compute the overall fault coverage, so that the quality of the test set is evaluated [68][69].

## 3.1 Fast Fault Simulation Algorithm

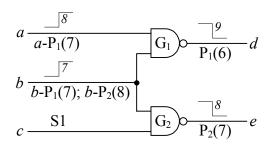

The fault simulation starts with spot-defect-free timing simulation for each test pattern. After this simulation, the initial and final logic values and the nominal transition time of the last event for each line are known. Figure 11 shows an example. The italic numbers next to the transition symbols indicate the transition time, assuming the unit gate delay model is used. S1 or S0 indicates a stable logic value 1 or 0 on the line.

Figure 11. Robust propagation path identification.

Then the robust/non-robust propagation paths from each line to primary outputs or scan cells are identified. A line's robust propagation paths can be computed using its immediate fan-out lines' robust propagation paths. In Figure 11, suppose line d has a robust propagation path  $P_1$  with length 6, and line e has path  $P_2$  with length 7. The robust propagation paths for line b are computed by checking the final logic values on the side

inputs of gate  $G_1$  and  $G_2$ . Then two paths are identified:  $b-P_1$  with length 7 and  $b-P_2$  with length 8. Because the propagation paths are robust, the slow signal is able to propagate through these paths independent of the delays on the side inputs to the paths. Therefore the extra delay  $\Delta$  on a line must be detected if  $t_{trans} + \Delta + l_{prop} > t_{max}$ , where  $t_{trans}$  and  $l_{prop}$ are the transition time and propagation path length associated with that line, respectively. In the simulation, since  $t_{trans}$  and  $l_{prop}$  are statistical values (with PDFs), the computed  $\Delta$ is a statistical value too. For resistive shorts, the sensitization condition, i.e. the opposite logic value on the other shorted line, must be checked.

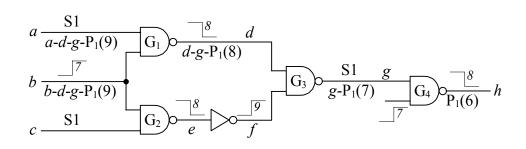

The non-robust propagation paths can be identified in a similar way. The difference is that if there is no transition on a line, the non-robust propagation paths from that line must also be computed. Line g in Figure 12 is an example. The reason is that a spot defect on line d may generate a glitch on g, and the computation of the non-robust propagation paths from d uses g's propagation paths. The complexity of the spot-defect-free simulation is  $O(V \cdot C)$ , where V is the number of vectors and C is the circuit size (number of gates/lines in the circuit).

Figure 12. Non-robust propagation path identification.

A problem with the non-robust propagation paths is that the fault detection through

these paths is dependent on the delays on the side inputs to the path. In Figure 12, an extra delay on line *b* does not affect the transition time on line *h*, even though line *b* has a non-robust propagation path. Therefore, the validation of these paths must be checked. After spot-defect-free timing simulation, each line has a few non-robust propagation paths. The validation check can be performed by introducing an extra delay  $\Delta$  on the line, where  $\Delta = t_{max} - t_{trans} - l_{prop}$ , and running fault simulation for the patterns which sensitize this path, to check if the slow signal can be detected at any primary output or scan cell. This procedure starts from the smallest  $\Delta$ . If a small  $\Delta$  can be detected through a non-robust propagation path, the validation check for the paths that can only detect large  $\Delta$  is not necessary, because testing those paths, such as  $P_3$  in Figure 9, does not increase the fault coverage. Experiments show that normally only a few paths must be checked for each line.

It is possible that some functional sensitizable paths are missed. However, because these paths always appear in pairs and the delay is determined by the shorter one, in most cases they do not contribute to the fault coverage. Thus, these paths are not checked unless there is no long robust or non-robust propagation path through the fault site.

#### 3.2 Comparison of Simulated Fault Coverage

ISCAS85 benchmark circuits are used in the experiments. The TSMC 180 nm technology with five metal layers is used to generate the layouts. Delays for each gate and interconnect are extracted and assumed to have a Normal distribution with  $3\sigma=10\%$

of the nominal value. The transistor gate length, the width and thickness of the five metal layers and the thickness of the five interlayer dielectrics are considered parameters in the process variation model [62]. The maximum specified delay  $t_{max}$  is set to be 8% longer than the nominal delay of the longest testable path.

In the first experiment, resistive opens are assumed on gate outputs. It is assumed that 80% of the opens have infinite resistance so that they can be detected by a transition fault test, and the remaining 20% are resistive, with log(R) uniformly distributed, where *R* is the open resistance [31]. This case is similar to the traditional gate delay fault model because the local delay fault size has a distribution. The delay fault coverage computed in this work is more accurate than the gate delay fault coverage, because process variation is also considered. The KLPG (K longest testable paths per gate) test generator [70] is used to generate K=500 testable paths through each gate (this process takes <10 minutes), for the fault coverage computation purpose. For >99% of the gates, K=500 covers all the possible longest testable paths through the gate, assuming a ±10% path delay variation. This increases fault coverage accuracy, because the fault sites with no transition fault test are not included in the computation, and the false paths are eliminated by the KLPG test generator.

Table 1 shows the fault coverage for the ISCAS85 circuits, using three test sets:

1. Transition fault test;

2. KLPG-1 test, which tests two longest paths through each gate, with one path having a rising transition and the other having a falling transition at the gate output;

3. (Critical) path delay test, which tests the  $C_{size}$  longest testable paths throughout

the circuit, where  $C_{size}$  is the circuit size (number of gates in the circuit), so that the number of patterns in this test set is about the same as the KLPG-1 test set.

The transition fault test is generated by a commercial ATPG tool. The other two test sets are generated by the KLPG test generator, and compressed by a simple greedy algorithm. All three test sets are applied at full functional speed.

| Circuit | TF    | KLF   | <b>PG-</b> 1 | Critical | TF+C  |

|---------|-------|-------|--------------|----------|-------|

|         | UB(%) | LB(%) | UB(%)        | UB(%)    | UB(%) |

| c432    | 98.85 | 99.64 | 99.98        | 57.78    | 99.51 |

| c499    | 98.68 | 99.59 | 99.96        | 25.95    | 99.27 |

| c880    | 98.82 | 99.61 | 99.95        | 24.38    | 99.25 |

| c1355   | 97.23 | 99.53 | 99.89        | 18.80    | 98.01 |

| c1908   | 98.51 | 99.44 | 99.92        | 31.99    | 99.11 |

| c2670   | 98.69 | 99.49 | 99.78        | 15.35    | 98.94 |

| c3540   | 97.97 | 99.51 | 99.90        | 25.66    | 98.60 |

| c5315   | 99.03 | 99.50 | 99.83        | 10.68    | 99.18 |

| c6288   | 97.51 | 99.12 | 99.65        | 12.83    | 98.14 |

| c7552   | 98.96 | 99.61 | 99.93        | 28.50    | 99.35 |

Table 1. Fault coverage comparison for resistive opens and process variation.

Column 2 shows the fault coverage for the transition fault test. For most fault sites, the transition fault test does not test through the longest paths, but the fault coverage is still reasonably high. The reason is that, based on test structure data, 80% of the resistive opens cause large extra delay if the test is applied at full functional speed. These numbers reflect the reality that a transition fault test detects most of delay faults. It should be noted that these numbers are the upper bound because it is too expensive for

the KLPG test generator to generate all the paths whose length is close to the paths that the transition fault test sensitizes (since most of these paths are short, and the KLPG test generator generates long paths first). This also happens to the path delay test because for the faults that are not on critical paths, random short paths are sensitized by this test set. Therefore, a 100% path delay correlation is used to compute the upper bound.

Columns 3 and 4 show the lower and upper bounds of the fault coverage for the KLPG-1 test. The lower bound is computed by assuming no path delay correlation (even no structural correlation). The upper bound is computed by using an inter-die process variation model [62] and assuming 100% intra-die process correlation. The bounds are close because the majority of delay faults caused by resistive opens can be modeled as transition faults. It can be seen that the upper bound fault coverage is almost 100% for most circuits. The reason is that for most fault sites, only 2-3 paths can be the longest paths with process correlation. Thus, most fault sites have 100% DP. The fault coverage upper bound for circuits c2670, c5315 and c6288 is lower than the other circuits because the number of longest paths per fault site for these circuits is relatively large even with process correlation. Column 5 shows the upper bound of the fault coverage for the path delay test. The coverage loss mainly comes from the fact that many local delay fault sites have no test, because they are not on a long path. Column 6 shows the upper bound of the fault coverage for applying both transition fault and path delay tests, which are used in industry. The higher fault coverage of this test reflects industrial experience [71].

Figure 13 shows the fault coverage for circuit c7552, assuming the K value in the KLPG test increases from 1 to 5. As can be seen, only a small number of paths are

needed through each fault site to achieve high fault coverage. The benefit of testing one of the longest paths (the fault coverage increase from the transition fault test to the KLPG-1 test) is more significant than that of testing more long paths (the increase from the KLPG-1 test to the KLPG-5 test).

Figure 13. Fault coverage vs. K (circuit c7552).

In the second experiment, random non-feedback resistive shorts are assumed. Table 2 shows the results. The number of shorts is approximately twice the number of lines in the circuits. Shorts between lines feeding the same gate are not included. Shorts between signal lines and power/ground grid are not considered because they are more likely to behave as stuck-at or transition faults [72][73][74][75]. The bridge resistance is assumed to be uniformly distributed between 0  $\Omega$  and 40 k $\Omega$  [76]. It can be seen that for transition fault and path delay tests, there is a large coverage loss but KLPG-1 test keeps high fault coverage. It is straightforward that the path delay test has low coverage because some bridging faults on non-critical paths are not sensitized randomly. However, this should not happen for the transition fault test. Although the transition fault test does not target

resistive shorts explicitly, a bridging fault can be detected by either shorted line in most cases. In addition, as the transition fault test generates at least one observable transition through each gate/line, and the probability that an opposite logic value is set on the other shorted line is high, most bridging faults can be sensitized. However, there is still a significant difference of coverage between the KLPG-1 and transition fault tests.

| Circuit | # Shorts | TF    | KLPG-1 |       | Critical | TF+C  |

|---------|----------|-------|--------|-------|----------|-------|

|         |          | UB(%) | LB(%)  | UB(%) | UB(%)    | UB(%) |

| c432    | 821      | 85.3  | 98.2   | 98.8  | 82.4     | 97.7  |

| c499    | 1 102    | 91.1  | 99.1   | 99.3  | 88.0     | 98.5  |

| c880    | 1 421    | 90.5  | 98.5   | 99.0  | 85.1     | 94.6  |

| c1355   | 2 488    | 88.9  | 98.6   | 99.0  | 84.1     | 96.0  |

| c1908   | 4 007    | 93.0  | 96.6   | 97.5  | 90.7     | 95.8  |

| c3540   | 8 919    | 84.1  | 94.6   | 95.9  | 85.3     | 92.1  |

| c5315   | 12 168   | 93.9  | 97.1   | 98.2  | 94.6     | 96.4  |

| c6288   | 14 170   | 80.6  | 95.0   | 99.1  | 90.1     | 94.2  |

| c7552   | 12 156   | 85.5  | 93.3   | 97.4  | 89.6     | 93.7  |

Table 2. Fault coverage comparison for resistive shorts and process variation.

Figure 14 shows the delay caused by most resistive shorts and explains why testing long paths is important. For most shorts, the slack of the longest sensitizable path through either shorted line is not very tight (Figure 14a), therefore the coverage loss, which is the range between the two dotted vertical lines, is small. However, for some shorts with one shorted line on a critical path, a large coverage loss occurs if the longest sensitizable path through that line is not tested even if the tested path is slightly shorter (Figure 14b). This also explains the results that applying both transition fault and path delay tests can get high fault coverage.

Figure 14. Delay vs. bridge resistance.

In the third experiment, no spot defects are assumed. The circuits are only subject to process variation. This case is equivalent to the traditional path delay fault model, and the new metric computes a more accurate and reasonable fault coverage. The KLPG test generator is used to generate all the potentially critical paths to compute more accurate fault coverage (the CPU time is <5 minutes per circuit).

Table 3 shows the fault coverage for this case, using the KLPG-1 and path delay tests. The fault coverage for the transition fault test is almost zero for all these circuits, since few critical paths are tested by luck because transition fault test normally sensitizes short paths to keep the test generation cost low. It can be seen that the KLPG-1 test results in high fault coverage. This is because many paths in this test set are also critical paths. After the process correlation is applied, most paths are trimmed and for most circuits there are <10 "must be tested" paths remaining (circuit c2670 has 14 paths remaining, which is the maximum number). The experiments show that the KLPG-1 test set covers all the "must be tested" paths for most circuits (KLPG-1 for c499 misses one path and

KLPG-1 for c2670 misses two). It is not surprising that the path delay test achieves higher fault coverage, and the number of critical paths in all the circuits is less than  $C_{size}$ , except for c6288.

| Circuit | KLF   | <b>P</b> G-1 | Critical |       |  |

|---------|-------|--------------|----------|-------|--|

|         | LB(%) | UB(%)        | LB(%)    | UB(%) |  |

| c432    | 100   | 100          | 100      | 100   |  |

| c499    | 99.81 | 99.94        | 100      | 100   |  |

| c880    | 99.83 | 100          | 100      | 100   |  |

| c1355   | 99.72 | 100          | 100      | 100   |  |

| c1908   | 99.77 | 100          | 100      | 100   |  |

| c2670   | 99.25 | 99.75        | 100      | 100   |  |

| c3540   | 100   | 100          | 100      | 100   |  |

| c5315   | 99.17 | 100          | 100      | 100   |  |

| c6288   | 96.44 | 100          | 98.89    | 100   |  |

| c7552   | 100   | 100          | 100      | 100   |  |

Table 3. Fault coverage comparison for process variation only.

For comparison, Table 4 shows the fault coverage for the three test sets using the traditional transition and path delay fault coverage metrics. It can be seen that the transition fault coverage does not reflect the real test quality since both transition fault and KLPG-1 tests have 100% fault coverage after removing undetectable faults. The traditional path delay fault coverage for the transition fault test is not included because the cost is too high to identify all the sensitized paths. The total number of testable paths, which is used in the traditional path delay fault coverage computation, is from the RESIST test generator [48]. As some aborted paths may also be testable, the numbers in

columns 5 and 6 are the upper bound. For example, in circuit c6288, 12 592 testable paths are found by RESIST and about  $10^{18}$  paths are aborted. The traditional path delay fault coverage is much lower than the real test quality.

| Circuit | Tra | nsition FC | Path Delay FC (%) |        |          |

|---------|-----|------------|-------------------|--------|----------|

| Circuit | TF  | KLPG-1     | Critical          | KLPG-1 | Critical |

| c432    | 100 | 100        | 57.81             | 3.01   | 4.30     |

| c499    | 100 | 100        | 25.99             | 0.28   | 0.15     |

| c880    | 100 | 100        | 24.41             | 2.19   | 2.38     |

| c1355   | 100 | 100        | 18.86             | 1.94   | 2.41     |

| c1908   | 100 | 100        | 32.04             | 0.37   | 0.90     |

| c2670   | 100 | 100        | 15.48             | 4.44   | 8.34     |

| c3540   | 100 | 100        | 25.73             | 1.01   | 1.89     |

| c5315   | 100 | 100        | 10.79             | 1.71   | 2.83     |

| c6288   | 100 | 100        | 13.08             | 11.69  | 19.19    |

| c7552   | 100 | 100        | 28.55             | 1.82   | 4.07     |

Table 4. Fault coverage comparison using traditional delay fault coverage metrics.

#### 4. TEST GENERATION

#### 4.1 Background

The problem of finding the longest path through each gate or line in a circuit has been extensively studied [41][42][ 77 ][ 78 ]. However, these methodologies are either inefficient or fail to guarantee the testability of the generated paths. The inefficiency comes from the fact that most prior work lists many long structural paths first, and then checks their testability. If there are subcircuits with a large number of paths, all the long paths listed are similar and it is possible that none of them is testable.

Many ATPGs for the global longest path generation were studied to see if they could be extended to solve the problem of finding the K longest testable paths through each gate (KLPG). A fast ATPG tool NEST [79] generates paths in a nonenumerative way, which can handle a large number paths simultaneously, but it is only effective in highly testable circuits, where large numbers of path delay faults are testable. DYNAMITE [80] is very efficient in poorly testable circuits, but in highly testable circuits many faults are treated separately, which results in huge memory consumption and so is not practical for large circuits. RESIST [48] exploits the fact that many paths in a circuit have common subpaths and sensitizes those subpaths only once, which reduces repeated work and identifies large sets of untestable paths. Moreover, for the first time this research identified 99.4% of all the path delay faults as either testable or untestable in ISCAS benchmark circuit c6288, which is known for having an exponential number of paths. However, the test generation for c6288 is still slow. RESIST took 1 122 CPU hours to find 12 592 paths on a SPARC IPX 28 MIPS machine. Following research [43] presented an efficient method to extend the RESIST algorithm to the problem of finding a set of longest testable paths that cover every gate. This method takes advantage of the relations of the longest paths through different gates, and guarantees their testability. However, partly because this work assumes a unit delay model, there is no obvious way to extend it to handle the problem of finding the K longest testable paths through each gate, and this method fails when applied to c6288, indicating that the advantages in the RESIST algorithm may not be easily applied to generating paths through a certain gate.

A timing analysis tool [81] presents another method to efficiently identify the global longest testable paths in a combinational circuit. Instead of generating many long structural paths and checking their testability, this tool grows paths from the primary inputs. In each iteration, a new gate is added, and the constraints are applied to that gate. Then instead of assigning logic values on one or more primary inputs to satisfy the constraints on the newly added gate, as done in VIPER [47], direct implications, which are more efficient, are applied to find local conflicts. If conflicts exist, the whole search space that contains the already-grown series of gates is trimmed off. This technique is called implicit false path elimination [45][82]. Some other false path elimination techniques, such as forward trimming and dynamic dominators, are also applied in this tool to identify false paths earlier. This tool is efficient and able to handle c6288.

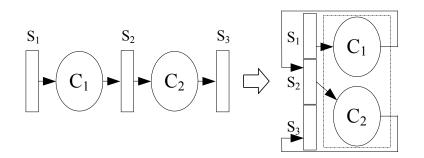

The algorithm in this work inherits the framework of the efficient timing analysis tool but aims at particular gates one by one, and it has been extended to handle scan-based sequential circuits in industry. Many heuristics are implemented in the algorithm to reduce the search space and avoid repeated work. Experiments have shown that this algorithm can achieve a linear CPU time and memory consumption in circuit size.

## 4.2 Test Generation Flow

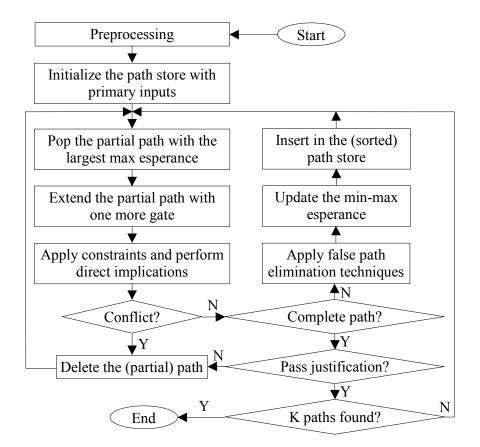

Figure 15. KLPG test generation flow.

Figure 15 shows the KLPG test generation flow. Files required in each step are listed on the right side. The first step is to parse the hierarchical netlist and library. In this work Verilog format is supported. When the hierarchical design is being flattened, each pin, cell, gate, and primitive is assigned an index. An index-to-hierarchical-name mapping table and hierarchical-name-to-index hash table are established and written to files. Since KLPG is not a design-for-testability (DFT) tool, it does not have to remember all the hierarchical names for future debugging (designs are assumed to be bug-free, e.g. a taped-out design). After this step, the long hierarchical names can be removed from memory to reduce memory consumption. Flattened design is also written to a file in Verilog format with simple names for pins, cells, gates, and primitives (using indices, such as N100, G200, etc.), so that the flattening does not have to be run for multiple times if test generation needs to be rerun, as long as the design is not modified.

The second step is to parse the standard delay format (SDF) file of the design. The SDF file specifies pin-to-pin path delays for cells and interconnects. In most cases, both maximum and minimum delays are included. The SDF file can be parsed cell by cell, so the memory consumption is insignificant. However, the whole hierarchical-name-to-index hash table must be read into memory to process hierarchical names in the SDF file. After the SDF file parsing is complete, the hash table can be removed from memory. Data structures that are used in the following steps can be set up at this point so that the peak memory usage can also be kept at a low level. In this work, the peak memory usage is about 1 KB per gate. An equivalent SDF file for the flattened design is saved. Because the new file does not contain any long hierarchical names, it can be processed faster in

future ATPG runs, without the hash table.

The following three steps (Test sequence simulation, rule checking, and masking) are similar to the standard flow used in commercial tools.

The sequence file (or procedure file) specifies test pin values under test mode, test setup clocking, pattern load/unload clocking, and other test configuration details. Scan pin flag file, which can also be included in the sequence file, specifies the functionality of each test pin, such as scan-in, scan-out, scan-enable, functional clock, test clock, etc. During test sequence simulation latches/flip-flops for clocking or testing are set to proper values, and every scan cell is identified (the scan chain it belongs to, position in the chain, inversion from scan-in and scan-out, etc.).

The purpose of rule checking (or test structure verification) is to verify that scan cells work properly during shift and test launch/capture, according to the given test sequence. Because commercial tools can do the same job, tool only provides basic rule checking, to roughly verify that the flattened design and test sequence do not have errors.

During the masking step, primary outputs and some scan cells are masked. For most designs, the destination scan cells of multi-cycle paths are masked. However, it has been observed that the transition fault coverage can be increased from 30.04% to 76.45% if the sources of multi-cycle paths are forced to X during ATPG, instead of masking the destinations. Masking is a tricky job for some designs. Circuits selected in this work do not have such problems.

In the test generation phase, K longest paths through each potentially faulty line are generated, with K paths having rising transitions at the fault site and the other K having

falling transitions. The corresponding test patterns are also generated, with one pattern per path before compaction. Then the patterns are statically compacted and saved.

The saved patterns need to go through re-simulation as a standard step in industry. During re-simulation, the hierarchical version of the design and SDF files are loaded into the simulator and any mismatches in scan-out data need to be masked. Then the patterns are rewritten in an industrial standard format such as the standard test interface language (STIL) format, and ready to be shipped to testers.

### 4.3 Path Generation

## 4.3.1 Preprocessing

Before path generation, some topology information is collected to help guide the path generation process and trim the search space. In this work, a launch point (of a path) is an unmasked primary input or scan cell, and a capture point is an unmasked primary output or a scan cell. First, the min-max delay from each gate to any capture point is computed without considering any logic constraint (PERT delay or STA delay). A gate's min-max PERT delay can be simply computed using its fan-out gates' min-max PERT delays and the rising/falling buffer-to-buffer delays between gates.

In addition to the PERT delays, the earliest and latest possible rising/falling transition times on the input and output lines for each gate are computed, assuming that a transition at any launch point can only occur at time zero. This procedure is similar to the PERT delay computation, with complexity linear in the circuit size. This information is useful under some sensitization criteria because transitions can occur only within the earliest/latest range.

#### 4.3.2 Path Store

To find the K longest testable paths through gate  $g_i$ , a path store is established for path generation. In the path store, many partial paths, which may become the K longest testable paths through gate  $g_i$ , are stored. A partial path is a path that originates from a launch point but has not reached a capture point. Figure 16 shows an example. The partial path starts from launch point  $g_0$ , and ends at gate  $g_i$ . At the beginning, the path store contains  $2n_{\text{LP}}$  partial paths, where  $n_{\text{LP}}$  is the number of launch points. There are two partial paths from each launch point, representing a rising or falling transition at that launch point. Each partial path has only one node (a launch point) initially. A partial path grows when one more gate is added to it. When a partial path reaches a capture point, it becomes a complete path.

Figure 16. A partial path and its esperance.

A value called *esperance* [45] is associated with a partial path. The min-max esperance is the sum of the length of the partial path and the min-max PERT delay from its last node to a capture point. In other words, the max esperance of a partial path is the upper bound of its delay when it grows to a complete path, and the min esperance is the

lower bound if the complete path is testable. In Figure 16, suppose the length of the partial path  $g_0...g_i$  is 5, and the PERT delays between gate  $g_i$  and capture points  $g_r$ ,  $g_s$ ,  $g_t$  are 10, 8, 6, respectively. The min-max esperance of partial path  $g_0...g_i$  is 11/15.

The partial paths are sorted by max esperance. Every time the path generator selects the partial path with the largest max esperance. Potentially this partial path will grow to a complete path with maximum delay.

#### 4.3.3 Algorithm

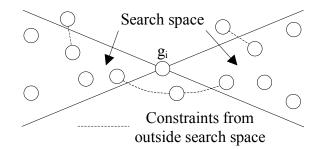

Before the path generation for gate  $g_i$ , all gates that are not in gate  $g_i$ 's fan-in or fanout cone are identified because when a partial path grows, it is impossible for any of these gates to be added (otherwise the partial path has no chance to pass through gate  $g_i$ ). These gates are still useful because they are related to constraints, such as side input constraints of a gate on the path that is being searched. Figure 17 shows the search space.

Figure 17. Search space for a path through a particular gate.

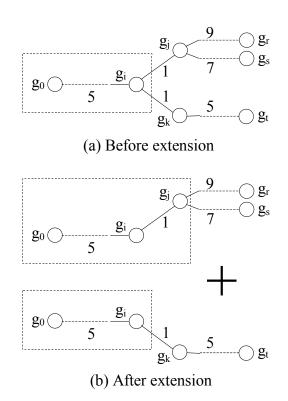

Figure 18 is the algorithm of finding the K longest testable paths through gate  $g_i$ . Each iteration of the path generation begins by popping the first partial path from the path store, which has the largest max esperance. The partial path is extended by adding a fan-out gate that contributes to the largest max esperance. For example, in Figure 19, the partial path  $g_0...g_i$  is extended by adding gate  $g_j$  because extending to  $g_j$  could potentially keep the max esperance. If the partial path has more than one extendable fanout, it must be saved in another copy, and in the copy, the already tried fan-out must be marked "blocked" or "tried." The esperance of the copy is then updated and the copy is pushed into the path store. For example (Figure 19), since gate  $g_i$  has 2 fan-outs, and extending the partial path to  $g_j$  may result in false paths later, the partial path  $g_0...g_i$  must be saved because extending it to gate  $g_k$  may get a longer testable path. Because fan-out  $g_j$  has been tried, in the copy the min-max esperance becomes 11/11.

Figure 18. Path generation algorithm.

After the partial path is extended (path  $g_0 \dots g_i g_j$  in Figure 19) the constraints to

propagate the transition on the added gate  $(g_j)$  are applied. Under the non-robust sensitization criterion [20], non-controlling final values on the side inputs are required. Under the robust sensitization criterion [44], in addition to non-controlling final values, the side inputs must remain non-controlling if the on-path input has a transition to the controlling value. Then direct implications are used to propagate the constraints throughout the circuit to prune non-solution search space. When a partial path reaches a capture point, it becomes complete path. Final justification is performed on it to find a vector pair. Direct implications and final justification will be discussed in detail in the following sections.

Figure 19. Partial path extension.

If the extended partial path is not a complete path, some false path elimination

techniques are applied to it, to more efficiently prevent the new partial path from becoming a false path. Then the min-max esperance of the partial path is updated and it is inserted into the path store. Since its max esperance may decrease and min esperance may increase after extension, it may not be inserted at the top of the path store. If this happens, in the next iteration another partial path will be selected for extension. For example (Figure 19), after extending partial path  $g_0...g_i$  to gate  $g_j$ , the min-max esperance changes from 11/15 to 13/15. If path  $g_j...g_r$  is blocked, which means path  $g_0...$  $g_r$  is a false path, after applying false path elimination techniques, the min-max esperance is 13/13.

Because each partial path consumes memory, and the path store cannot have an infinite size, when the number of partial paths exceeds the path store size limit, some partial paths with low max esperance are removed from the path store. The maximum esperance of the removed partial paths is recorded. In the future, any partial path with max esperance below that value must be removed from the path store because it may not truly be one of the K longest testable paths. Therefore, it may happen that K paths have not been found when the path store is empty. However, since a partial path is represented as a sequence of gates, usually it consumes less than 1 KB memory. Thus, the path store can have a large number of partial paths so that in most cases the algorithm does not abort unless none of the structural paths through the gate is testable.

The path generation iteration does not stop until the K longest testable paths through gate  $g_i$  are found or the path store is empty. Since the K longest testable paths through different gates may overlap, every time a new path is generated, it must be checked to

see if it has already been generated during the path generation for another gate.

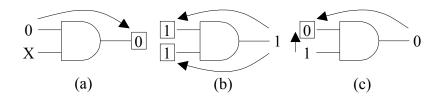

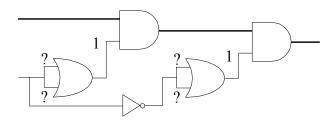

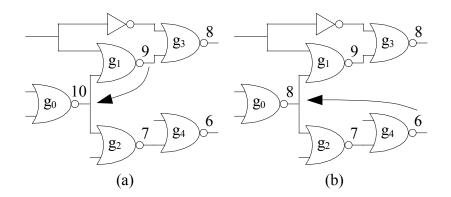

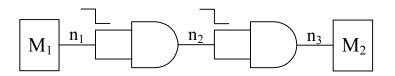

## 4.3.4 Direct Implication

A direct implication on a gate is one where an input or output of that gate can be directly determined from the other values assigned to that gate. Figure 20 shows some examples of direct implications on an AND gate. The values in boxes are implied from the existing values, which are not in boxes. Figure 20(a) is an example of forward implication, and (b)(c) are examples of backward implications. If a conflict happens during direct implications, the partial path is false. In other words, any path including this partial path is a false path. For example (Figure 19), if extending partial path  $g_0...g_r$  and  $g_0...g_s$  are determined to be false. Therefore, the partial path is deleted from the path store so that the whole search space that contains this partial path is trimmed off. Previous research has shown that most false paths can be eliminated by direct implications [45], and this is also observed in this work.

Figure 20. Examples of direct implications.

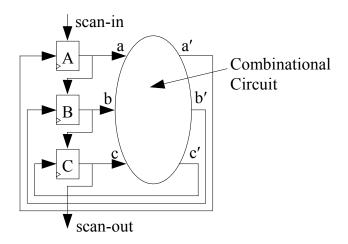

Direct implications can be performed on scan cells as well as regular gates to detect most local conflicts and eliminate sequential false paths.

Figure 21. Conflict after applying direct implications.