# DESIGN OF CMOS INTEGRATED PHASE-LOCKED LOOPS

## FOR MULTI-GIGABITS SERIAL DATA LINKS

A Dissertation

by

# SHANFENG CHENG

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

December 2006

Major Subject: Electrical Engineering

### DESIGN OF CMOS INTEGRATED PHASE-LOCKED LOOPS

## FOR MULTI-GIGABITS SERIAL DATA LINKS

## A Dissertation

by

## SHANFENG CHENG

## Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

| Chair of Committee, | Jose Silva-Martinez    |

|---------------------|------------------------|

| Committee Members,  | Aydin Ilker Karsilayan |

|                     | Peng Li                |

|                     | Manuel P. Soriaga      |

| Head of Department, | Costas Georghiades     |

December 2006

Major Subject: Electrical Engineering

### ABSTRACT

Design of CMOS Integrated Phase-locked Loops for Multi-Gigabits Serial Data Links. (December 2006) Shanfeng Cheng, B.Sc., Fudan University; M.Sc., Fudan University

Chair of Advisory Committee: Dr. Jose Silva-Martinez

High-speed serial data links are quickly gaining in popularity and replacing the conventional parallel data links in recent years when the data rate of communication exceeds one gigabits per second. Compared with parallel data links, serial data links are able to achieve higher data rate and longer transfer distance. This dissertation is focused on the design of CMOS integrated phase-locked loops (PLLs) and relevant building blocks used in multi-gigabits serial data link transceivers.

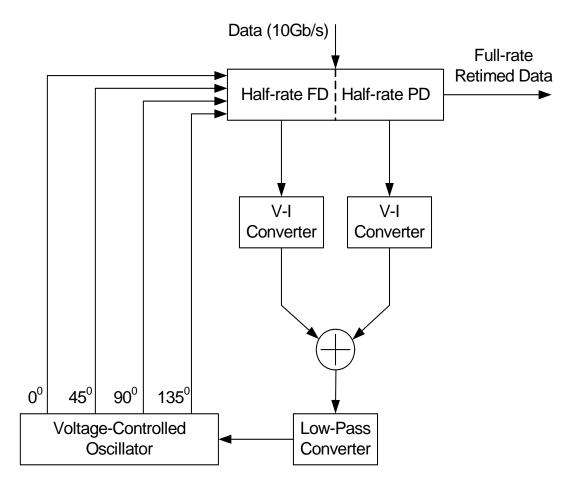

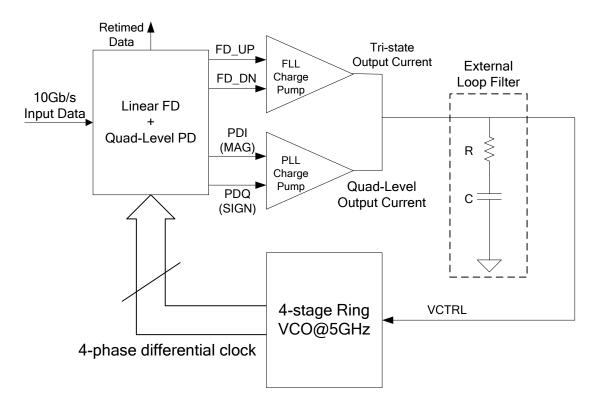

Firstly, binary phase-locked loops (BPLLs, i.e., PLLs based on binary phase detectors) are modeled and analyzed. The steady-state behavior of BPLLs is derived with combined discrete-time and continuous-time analysis. The jitter performance characteristics of BPLLs are analyzed. Secondly, a 10 Gbps clock and data recovery (CDR) chip for SONET OC-192, the mainstream standard for optical serial data links, is presented. The CDR is based on a novel referenceless dual-loop half-rate architecture. It includes a binary phase-locked loop based on a quad-level phase detector and a linear frequency-locked loop based on a linear frequency detector. The proposed architecture enables the CDR to achieve large locking range and small jitter generation at the same time. The prototype is implemented in 0.18  $\mu$ m CMOS technology and consumes 250 mW under 1.8 V supply. The jitter generation is 0.5 ps-rms and 4.8 ps-pp. The jitter peaking and jitter tolerance performance exceeds the specifications defined by SONET OC-192 standard. Thirdly, a fully-differential divide-by-eight injection-locked frequency divider with low power dissipation is presented. The frequency divider consists of a four-stage ring of CML (current mode logic) latches. It has a maximum operating frequency of 18 GHz. The ratio of locking range over center frequency is up to 50%. The prototype chip is implemented in 0.18  $\mu$ m CMOS technology and consumes 3.6 mW under 1.8 V supply. Lastly, the design and optimization techniques of fully differential charge pumps are discussed. Techniques are proposed to minimize the nonidealities associated with a fully differential charge pump, including differential mismatch, output current variation, low-speed glitches and high-speed glitches. The performance improvement brought by the techniques is verified with simulations of schematics designed in 0.35  $\mu$ m CMOS technology.

# DEDICATION

To the memory of my grandfather

#### ACKNOWLEDGMENTS

Firstly, I'd like to thank my advisor, Dr. Jose Silva-Martinez, for his enlightening guidance and advice to my research during my Ph.D. study at the Analog & Mixed-signal Center. He showed me the art of analog integrated circuit design through his in-depth knowledge and pioneering expertise. He was always accessible and willing to answer my questions. I was deeply affected by his serious attitude and full devotion to scientific research. I also would like to thank Dr. Edgar Sanchez-Sinencio, the director of the Analog & Mixed-signal Center, for what I learned in his courses. His courses were the most difficult while the most interesting ones I've ever had. What he taught will be useful throughout my career as an analog IC design engineer. I'd like to thank Dr. Aydin Ilker Karsilayan for his valuable input to the design of the SONET OC-192 CDR and his valuable comments to my publications.

I'd like to thank my friend, Haitao Tong, for the countless discussions which inspired my enthusiasm, my interest and my ideas. He is the most helpful and unselfish person I've ever met. His earnestness and meticulousness with academic research often stimulated me to work hard towards the goal instead of slacking off. I would not have gone this far in my Ph.D. research without the contributions and help from Haitao. I also would like to thank my mentor, Mr. Hui Pan, at Broadcom for guidance and discussions during my internship at Broadcom. I'd like to thank my friend, Jianhong Xiao, for interesting discussions and valuable input to my research. I'd like to thank all the labmates at the Analog & Mixed-signal Center for useful discussions and sharing ideas.

I would like to thank my wife, Yingying Chen, for her constant love, care and support. She gave me the encouragement and motivation to make it through all the hard work in all the years during my Ph.D. study. I'd like to thank my father and mother for being such wonderful parents. What they taught me in my early childhood has been, and will continue to be, invaluable lessons throughout my life. My gratitude for them is beyond words and will last forever.

I would like to thank Dr. Peng Li, Dr. Henry F. Taylor, and Dr. Soriaga for serving as my committee members and for their valuable input and suggestions.

I would like to thank MOSIS for manufacturing the prototype chips. I would like to thank Broadcom Corp. for providing testing equipment and facilities.

## TABLE OF CONTENTS

| Pag               | ge |

|-------------------|----|

| ABSTRACTi         | ii |

| DEDICATION        | v  |

| ACKNOWLEDGMENTS   | vi |

| TABLE OF CONTENTS | ii |

| LIST OF FIGURES | X |

|-----------------|---|

| LIST OF TABLES  |   |

# CHAPTER

| Ι   | INTR                                      | ODUCTION                                                                                              | 1                 |

|-----|-------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------|

|     | I.1.<br>I.2.<br>I.3.                      | Application Background<br>Architectures of Serial Data Link Transceivers<br>Research Focus            | 2                 |

| II  |                                           | ELING AND ANALYSIS OF PHASE-LOCKED LOOPS BASED ON<br>RY PHASE DETECTORS                               | 7                 |

|     | II.1.<br>II.2.<br>II.3.                   | Introduction<br>Steady-State Analysis of BPLL<br>Jitter Analysis                                      | 9                 |

|     | II.4.                                     | Summary                                                                                               |                   |

| III | A 100                                     | BPS CDR FOR SONET OC-192 STANDARD                                                                     | 58                |

|     | III.1.<br>III.2.<br>III.3.<br>III.4       | Introduction to Optical Transceivers<br>Existing CDR Architectures<br>Proposed Solution<br>Conclusion | 60<br>64          |

| IV  | A FUI                                     | LLY-DIFFERENTIAL LOW-POWER DIVIDE-BY-8 INJECTION-<br>ED FREQUENCY DIVIDER UP TO 18GHZ                 |                   |

|     | VI.1.<br>VI.2.<br>VI.3.<br>VI.4.<br>VI.5. | Introduction<br>Conventional Frequency Dividers<br>Proposed Divide-by-8 ILFD<br>Measurement Results   | 121<br>125<br>136 |

|     | VI.J.                                     | Conclusion                                                                                            | 144               |

# CHAPTER

| V DESIGN AND ANALYSIS OF HIGH-SPEED GLITCH-FREE FULLY                 |     |

|-----------------------------------------------------------------------|-----|

| DIFFERENTIAL CHARGE PUMP WITH MINIMUM CURRENT                         |     |

| MISMATCH AND VARIATION                                                | 145 |

| V.1. Introduction                                                     | 145 |

| V.2. Fully Differential Charge Pump with Accurate Matching and Minimu | um  |

| Current Variation                                                     | 146 |

| V.3. Glitch Suppression                                               | 153 |

| V.4. Complete Implementation of the Charge Pump                       |     |

| V.5. Conclusion                                                       | 161 |

| VI SUMMARY AND CONCLUSIONS                                            | 162 |

| REFERENCES                                                            | 165 |

| VITA                                                                  | 172 |

# Page

# LIST OF FIGURES

Page

Х

| Fig. 1.1. Comparison of a parallel ATA cable and a serial ATA cable2                 |

|--------------------------------------------------------------------------------------|

| Fig. 1.2. Typical architecture of a single-channel transceiver                       |

| Fig. 1.3. Typical architecture of a multiple-channel transceiver                     |

| Fig. 2.1. Transfer characteristic of an ideal BPD9                                   |

| Fig. 2.2. Phase-domain model of PLL based on binary PD9                              |

| Fig. 2.3. Schematic of a first-order loop filter                                     |

| Fig. 2.4. Steady-state waveforms of BPLL with 1st-order filter                       |

| Fig. 2.5. POUT0 and POUT1 across all the modes for BPLL with 1st order filter        |

| Fig. 2.6. Schematic of the second order loop filter                                  |

| Fig. 2.7. Steady-state waveforms of BCDR with C1=10C2 and TP=2TS21                   |

| Fig. 2.8. POUT0 and POUT1 vs. oscillation periods for BPLL with 2nd order filter24   |

| Fig. 2.9. Mapping relationship between bit patterns and jitter values                |

| Fig. 2.10. JISI with 10 Gb/s PRBS applied to a LPF of 4 GHz BW                       |

| Fig. 2.11. JISI amplitude with different number of buffer stages and bandwidth28     |

| Fig. 2.12. Transfer characteristic of a gradual-switching BPD                        |

| Fig. 2.13. Phase-sweeping characteristic of Alexander's BPD                          |

| Fig. 2.14. Input / output jitter waveforms in the slewing region                     |

| Fig. 2.15. Illustrative plot for BPLL jitter peaking                                 |

| Fig. 2.16. Simulated waveforms of BPLL with jitter peaking                           |

| Fig. 2.17. BPLL input-to-output jitter transfer characteristic                       |

| Fig. 2.18. Simulated BPLL waveforms with 20 KHz and 144 UI sinusoidal input jitter45 |

| Fig. 2.19. Jitter tolerance mask of a BPLL                                        | 47 |

|-----------------------------------------------------------------------------------|----|

| Fig. 2.20. Simulated waveforms of BCDR using an ABPD with 0.02 UI IRJISI          | 47 |

| Fig. 2.21. Simulated waveforms of BCDR using GBPD (KT=80) with 0.02 UI IRJISI.    | 50 |

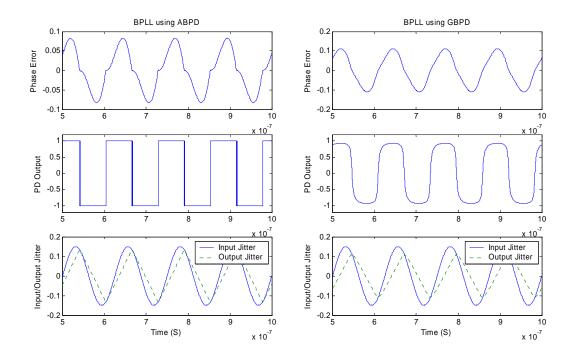

| Fig. 2.22. Simulated waveforms of BPLL using ABPD and GBPD                        | 52 |

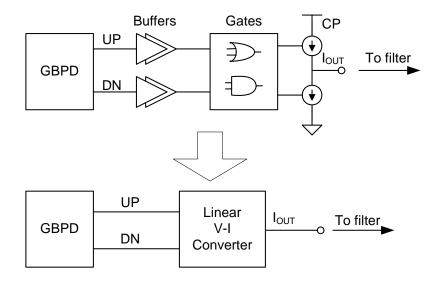

| Fig. 2.23. Structure modification to minimize jitter generation with GBPD         | 52 |

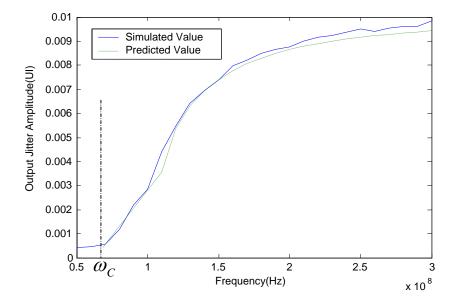

| Fig. 2.24. Simulated and predicted jitter generation caused by 0.01 UI JVCO       | 56 |

| Fig. 3.1. Block diagram of a typical optical transceiver                          | 59 |

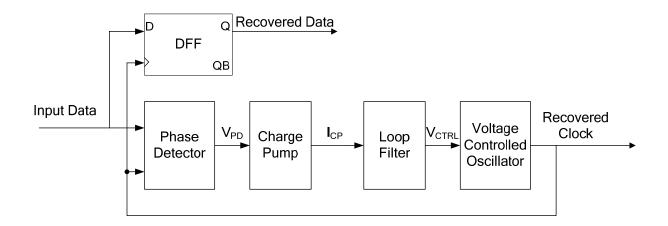

| Fig. 3.2. Block diagram of a single-loop CDR                                      | 61 |

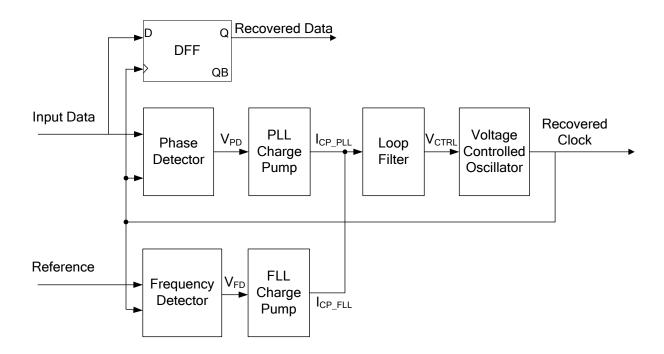

| Fig. 3.3. Block diagram of a dual-loop CDR with external reference                | 63 |

| Fig. 3.4. Structure of the referenceless CDR proposed in [25]                     | 64 |

| Fig. 3.5. Block diagram of the proposed CDR                                       | 67 |

| Fig. 3.6. Block diagram of the QPD                                                | 68 |

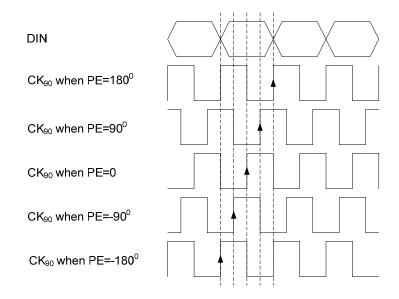

| Fig. 3.7. Timing diagram of CK90 and DIN under different phase errors             | 71 |

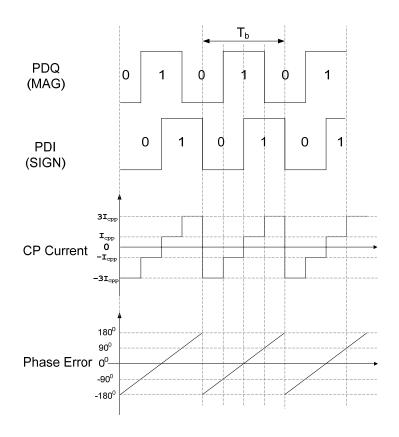

| Fig. 3.8. Output waveforms of the QPD with fixed input frequency difference       | 71 |

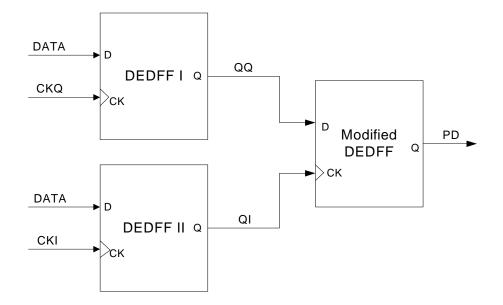

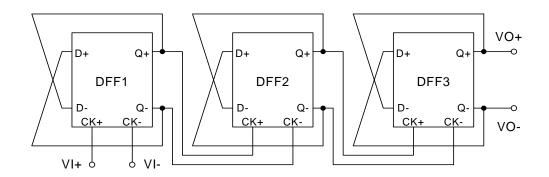

| Fig. 3.9. Schematic of half-rate binary PD                                        | 73 |

| Fig. 3.10. Schematic of double-edge D-flipflop                                    | 73 |

| Fig. 3.11. Modified double-edge D-flipflop with inversion on rising edge sampling | 74 |

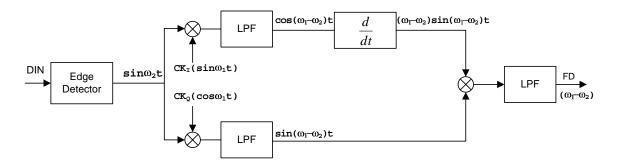

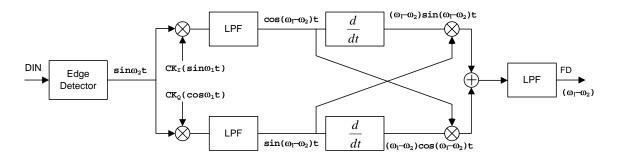

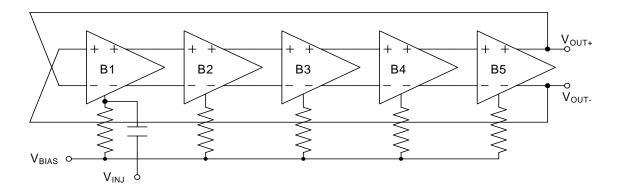

| Fig. 3.12. Frequency detector based on unbalanced quadri-correlator               | 75 |

| Fig. 3.13. Frequency detector based on balanced quadri-correlator                 | 75 |

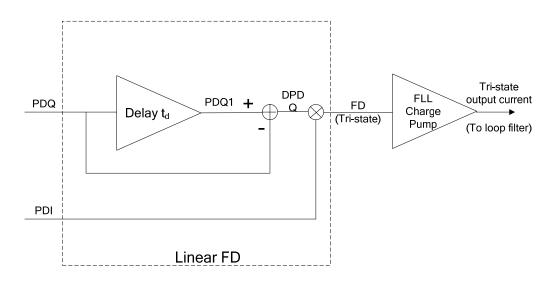

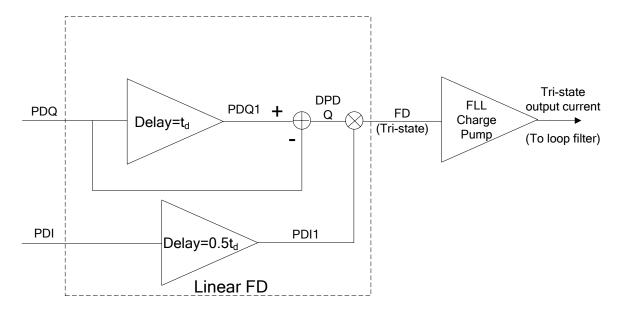

| Fig. 3.14. Block diagram of the linear FD                                         | 76 |

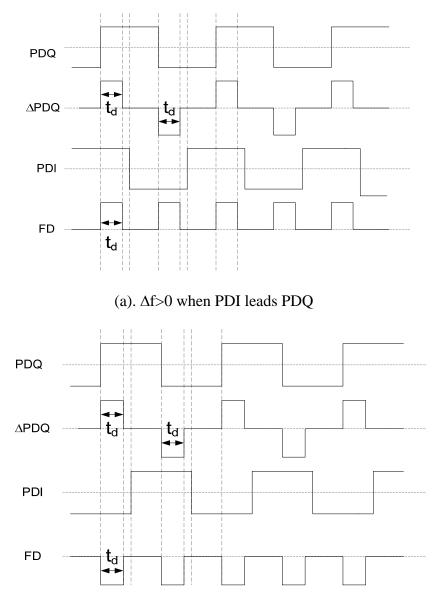

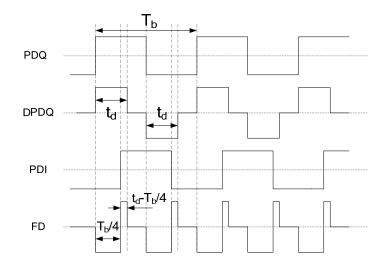

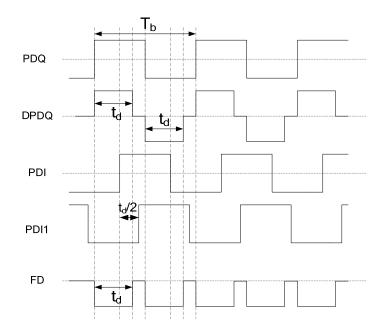

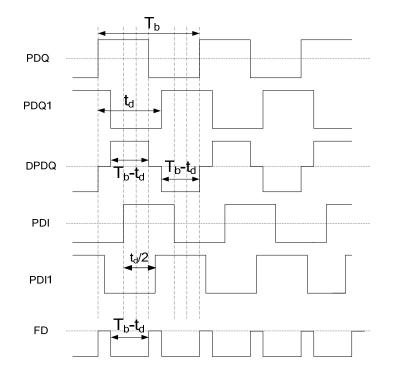

| Fig. 3.15. Timing diagram of the LFD                                              | 78 |

| Fig. 3.16. Timing diagram of LFD when $t_d > T_b/4$ and $\Delta f < 0$            | 80 |

Page

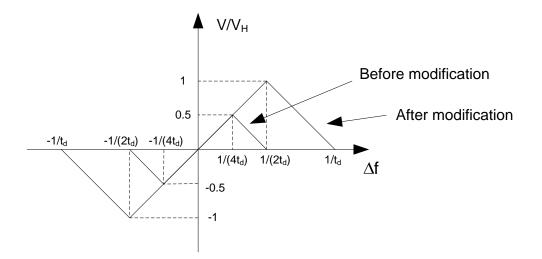

| Fig. 3.17. Block diagram of the revised LFD                                           | 82  |

|---------------------------------------------------------------------------------------|-----|

| Fig. 3.18. Timing diagram of the modified LFD when $\Delta f < 1/(2t_d$               | 82  |

| Fig. 3.19. Timing diagram of the modified LFD when $1/td > \Delta f > 1/(2t_d)$       | 83  |

| Fig. 3.20. Transfer curve of the LFD before and after modification                    | 83  |

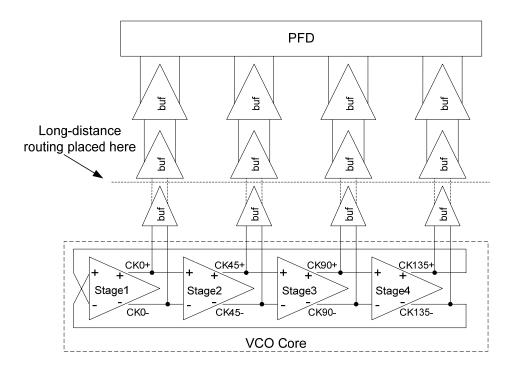

| Fig. 3.21. The block diagram of VCO and its drivers                                   | 85  |

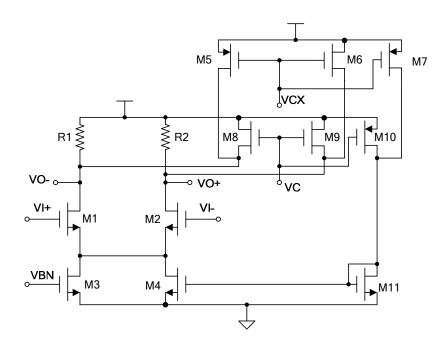

| Fig. 3.22. Internal schematic of each VCO stage                                       | 88  |

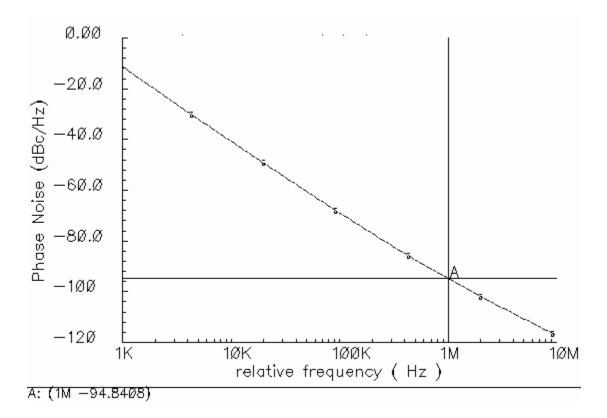

| Fig. 3.23. The phase noise of the VCO with post-layout parasitics                     | 89  |

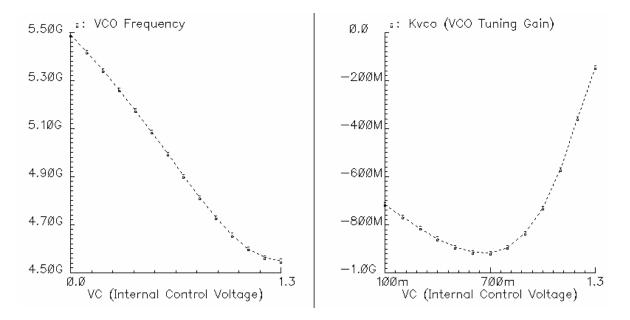

| Fig. 3.24. Tuning curve of the VCO when temp= $50^{\circ}$ C, VCX=0.6 V               | 90  |

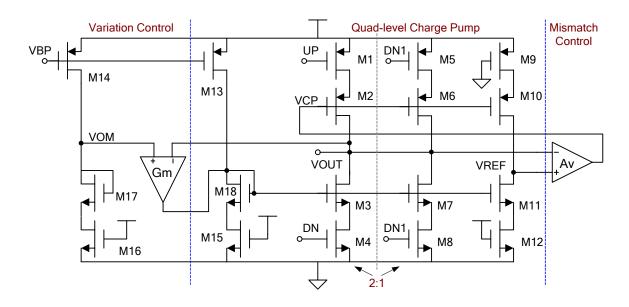

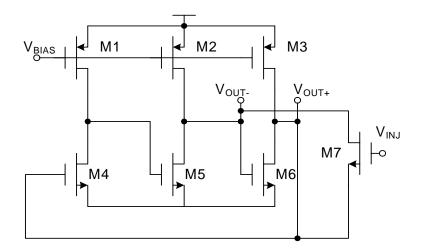

| Fig. 3.25. Schematic of the quad-level PCP                                            | 92  |

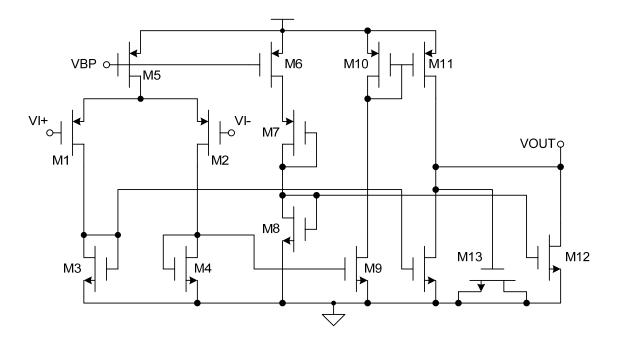

| Fig. 3.26. Schematic of the opamp used for mismatch control in the QCP                | 94  |

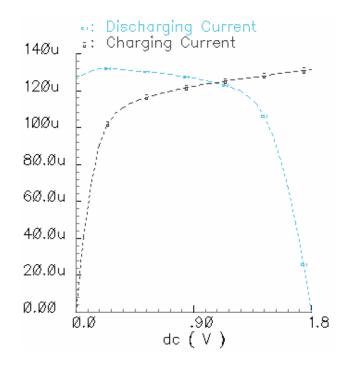

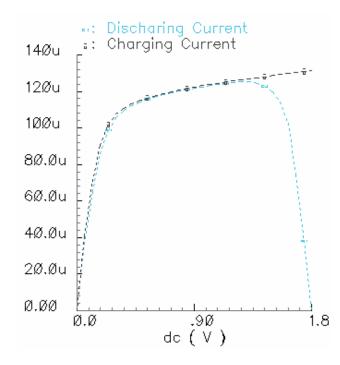

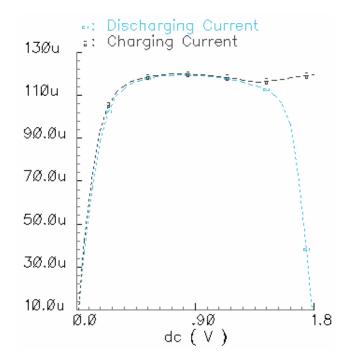

| Fig. 3.27. Output current of the QCP without mismatch and variation control           | 96  |

| Fig. 3.28. Output current of the QCP with mismatch control only                       | 97  |

| Fig. 3.29. Output current of the QCP with both mismatch control and variation control | 97  |

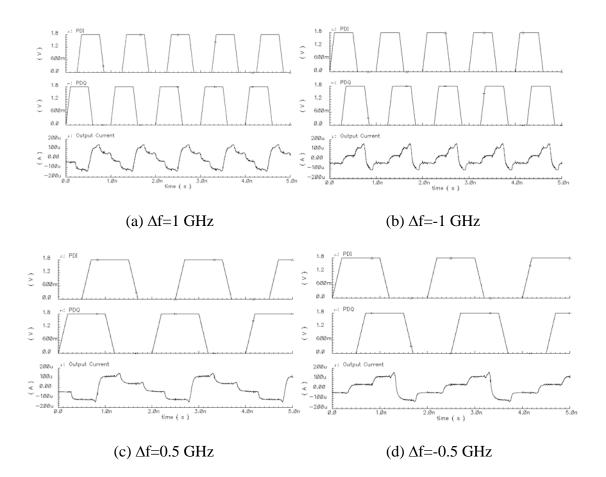

| Fig. 3.30. Transient waveforms of the QCP with LPE at different frequency offset      | 99  |

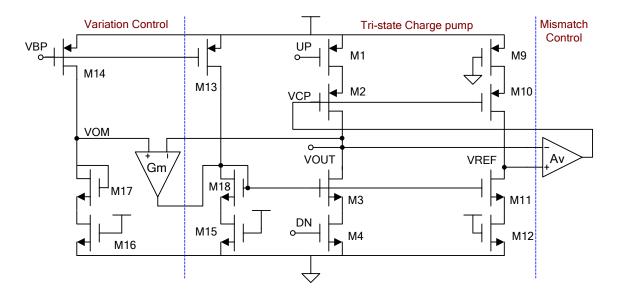

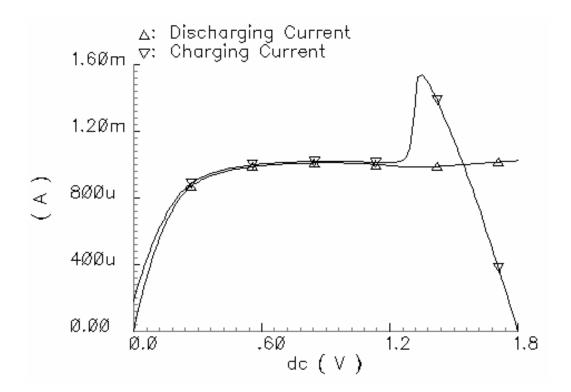

| Fig. 3.31. Schematic of the tri-state FCP                                             | 100 |

| Fig. 3.32. DC output current of the FCP                                               | 100 |

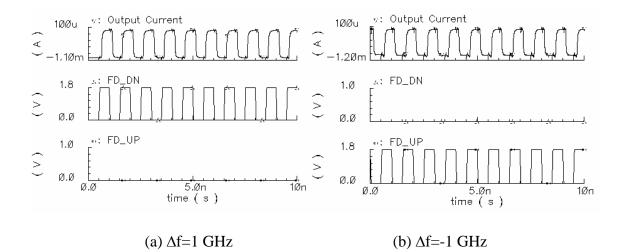

| Fig. 3.33. Transient output current of the FCP when $\Delta f=\pm 1$ GHz              | 101 |

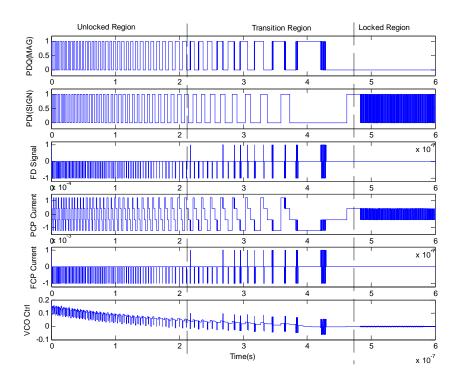

| Fig. 3.34. Transient waveforms of the CDR macro model during the locking process      | 103 |

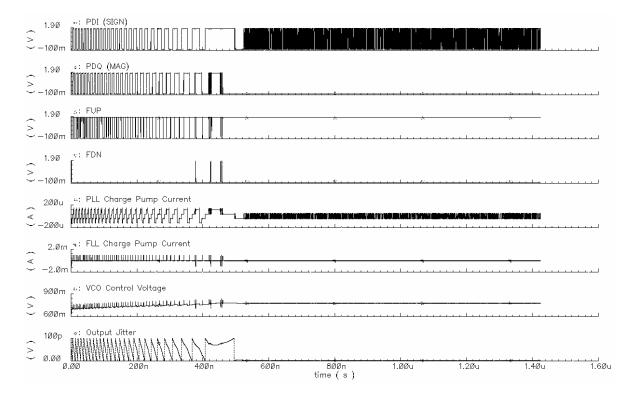

| Fig. 3.35. Transient waveforms of the transistor-level CDR during the locking process | 105 |

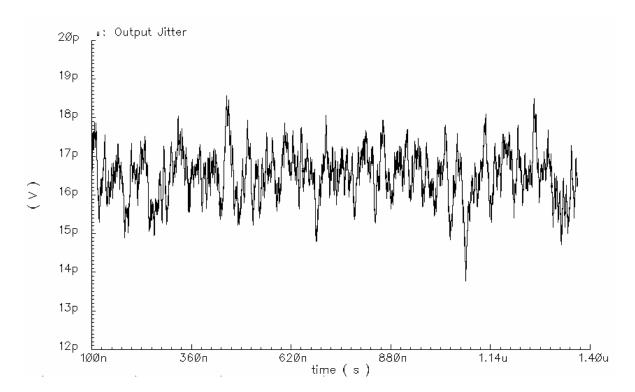

| Fig. 3.36. Jitter generation of the CDR in locked state                               | 107 |

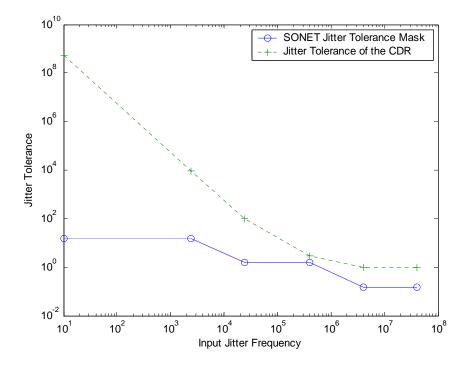

| Fig. 3.37. Jitter tolerance of the CDR versus SONET jitter tolerance mask             | 110 |

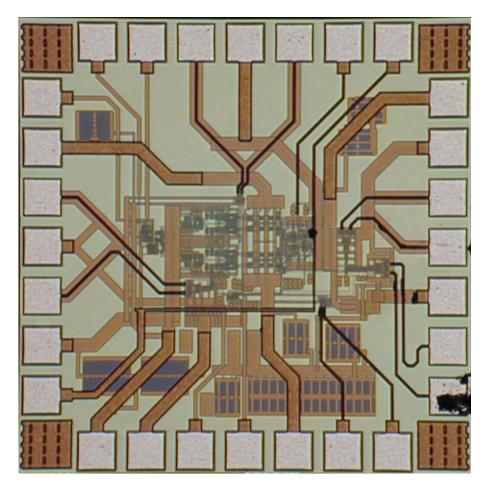

| Fig. 3.38. Micro-photo of the CDR prototype chip                                      | 117 |

Page

xiii

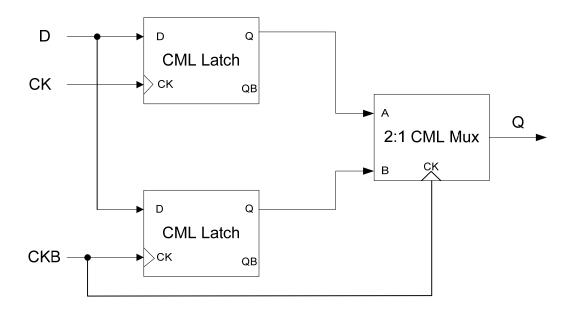

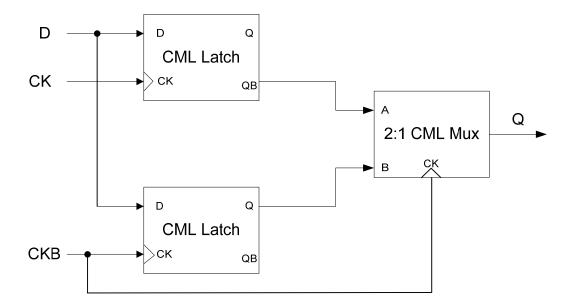

| Fig. 4.1. Conventional divide-by-8 CML static frequency divider                     | 122 |

|-------------------------------------------------------------------------------------|-----|

| Fig. 4.2. Ring-oscillator based ILFD proposed in [33]                               | 123 |

| Fig. 4.3. Single-ended divide-by-2 ILFD proposed in [34]                            | 124 |

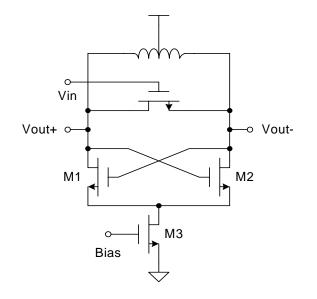

| Fig. 4.4. Divide-by-2 ILFD based on LC oscillator proposed in [35]                  | 125 |

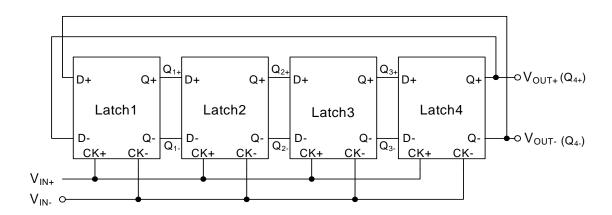

| Fig. 4.5. Schematic of the proposed divide-by-8 LILFD                               | 126 |

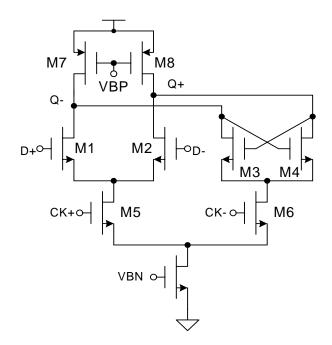

| Fig. 4.6. D-Latch cell used in each stage of the LILFD                              | 126 |

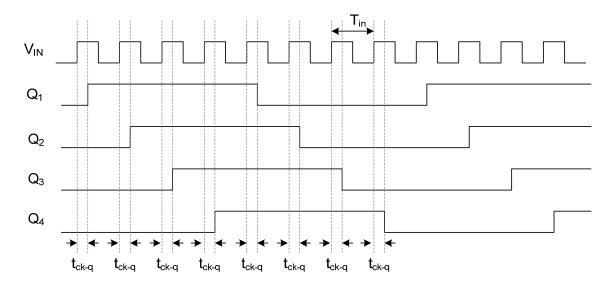

| Fig. 4.7. Timing diagram of the input and output signals of the LILFD               | 127 |

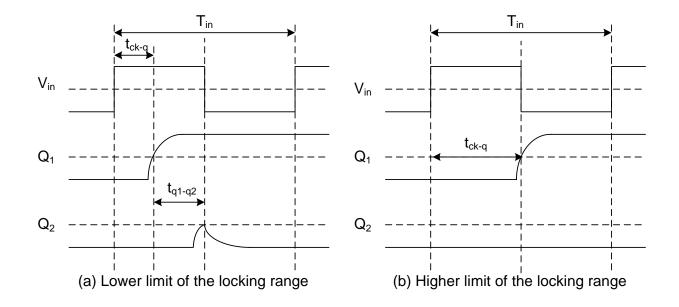

| Fig. 4.8. Timing diagrams at the boundaries of the locking range                    | 128 |

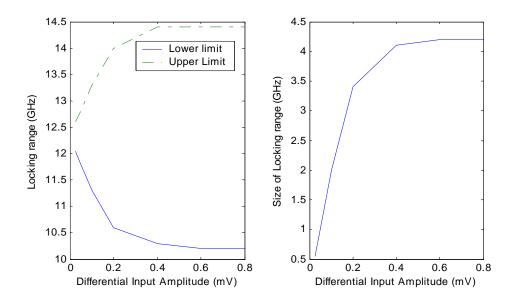

| Fig. 4.9. Simulated locking range vs. differential input amplitude when VBP=0.3 V   | 132 |

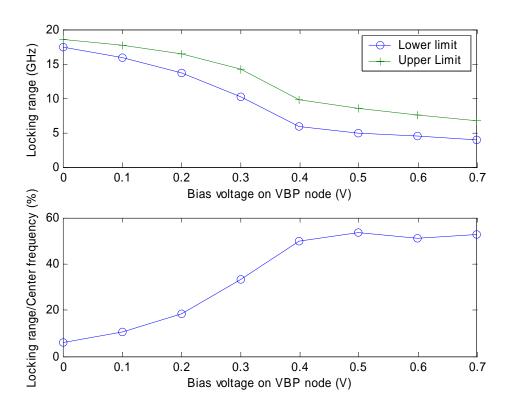

| Fig. 4.10. Locking range of the LILFD under different bias conditions               | 133 |

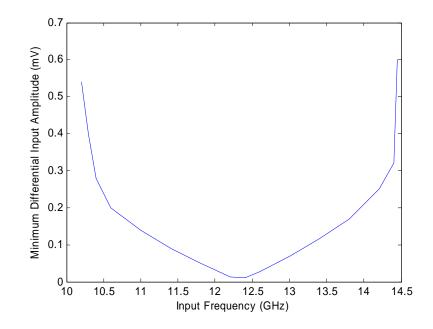

| Fig. 4.11. The input sensitivity of the LILFD versus input frequency when VBP=0.3 V | 134 |

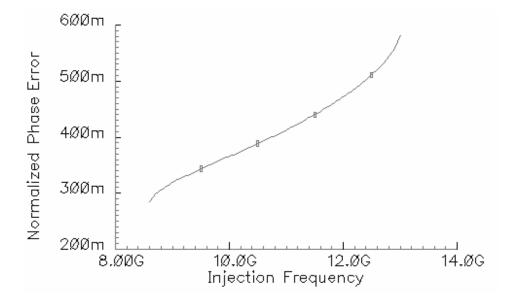

| Fig. 4.12. Normalized phase error vs. input frequency for the LILFD                 | 135 |

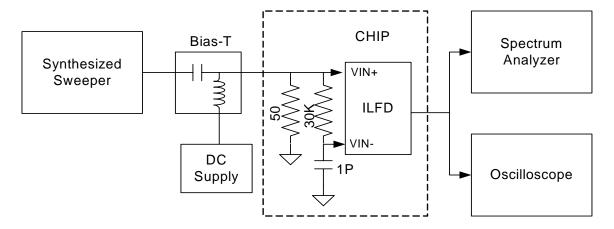

| Fig. 4.13. Test setup of ILFD chip                                                  | 136 |

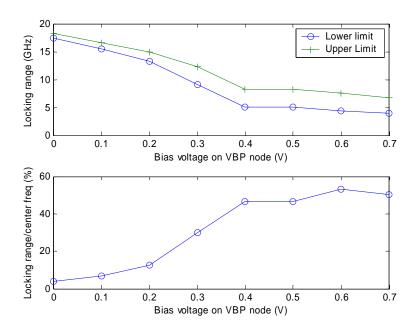

| Fig. 4.14. Locking range of the LILFD with 3 dBm input power vs. VBP                | 138 |

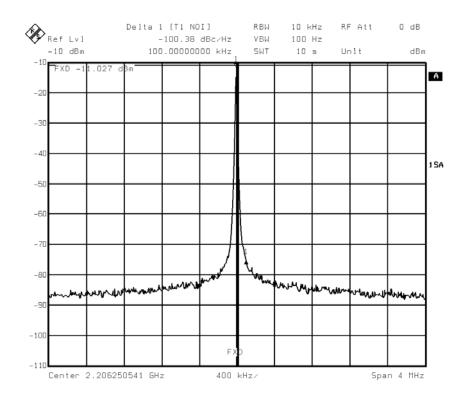

| Fig. 4.15. Output signal spectrum of the LILFD when locked at 17.6 GHz              | 138 |

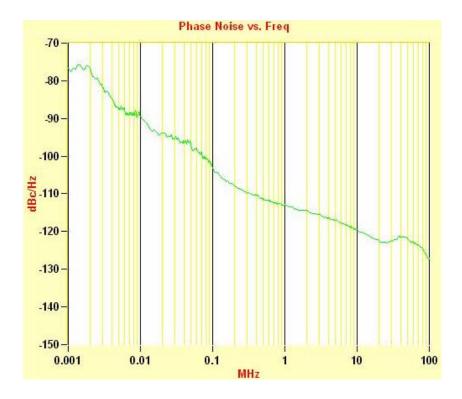

| Fig. 4.16. Measured output phase noise of the LILFD when locked at 17.6 GHz         | 139 |

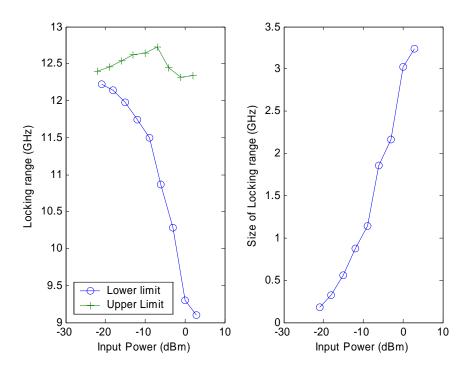

| Fig. 4.17. Measured locking range of the LILFD vs. input power when VBP=0.3 V       | 140 |

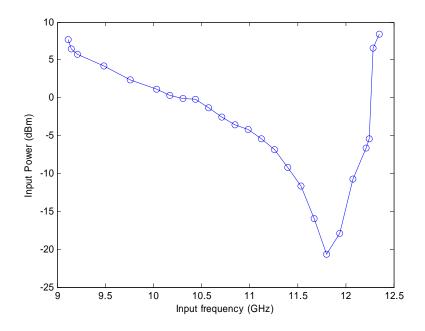

| Fig. 4.18. Measured input sensitivity versus input frequency when VBP=0.3 V         | 140 |

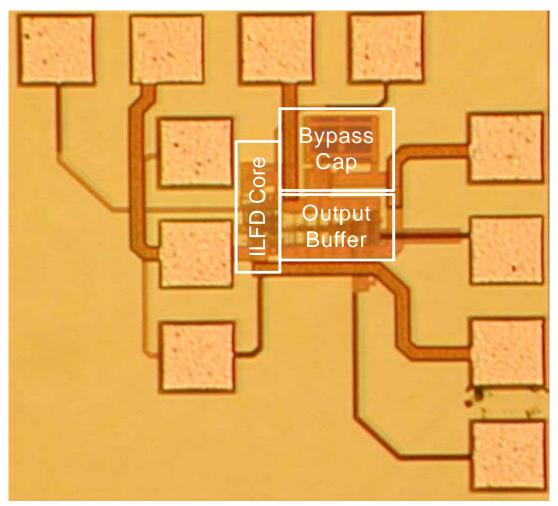

| Fig. 4.19. Die photo of the LILFD prototype chip                                    | 143 |

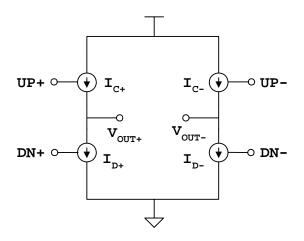

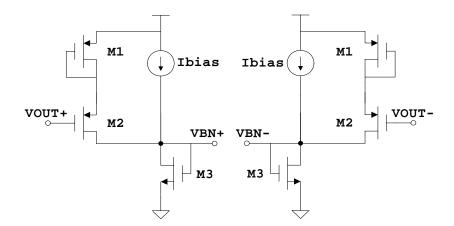

| Fig. 5.1. Conceptual diagram of a differential charge pump                          | 149 |

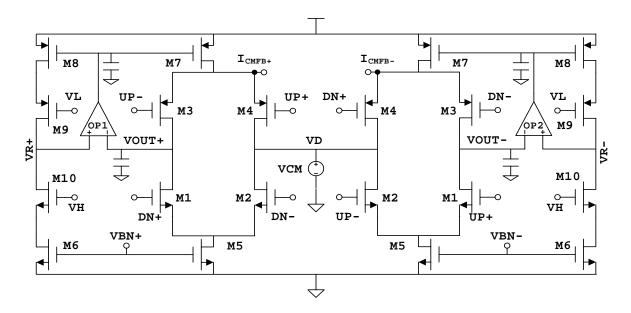

| Fig. 5.2. Proposed fully differential charge pump with mismatch suppression         | 149 |

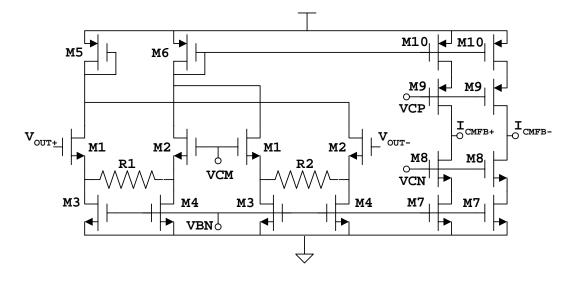

| Fig. 5.3. CMFB circuit for the differential charge pump                             | 151 |

# Page

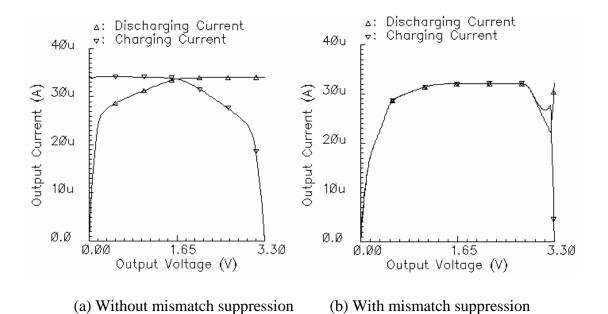

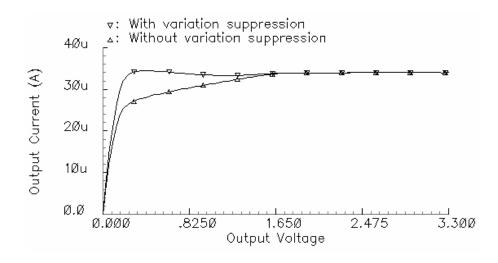

| Fig. 5.4. Output currents with and without mismatch suppression                                                                  | 151 |

|----------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 5.5. Variation suppression circuit                                                                                          | 152 |

| Fig. 5.6. Charge pump output current with and without variation suppression                                                      | 153 |

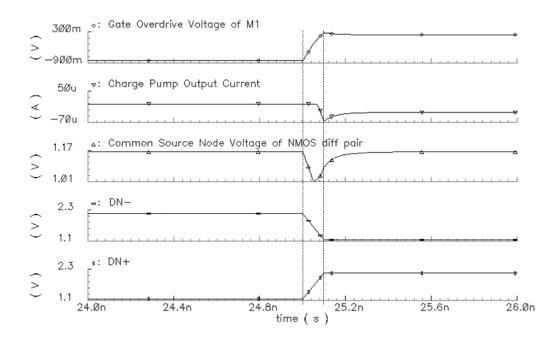

| Fig. 5.7. Transient waveforms of the NMOS diff. pair with fast input signal                                                      | 155 |

| Fig. 5.8. Proposed low-speed glitch suppression circuit                                                                          | 156 |

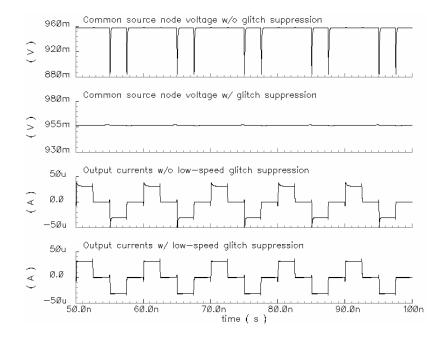

| Fig. 5.9. Common source node voltage and output current of the charge pump with and without low-speed glitch suppression circuit |     |

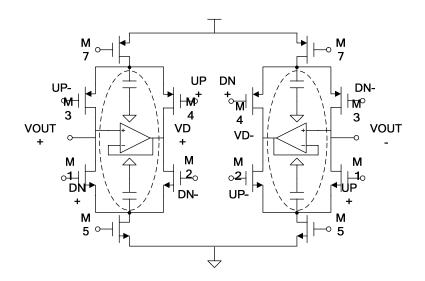

| Fig. 5.10. Proposed high-speed glitch suppression circuit                                                                        | 159 |

| Fig. 5.11. Output current with and without suppression of high-speed glitch                                                      | 159 |

| Fig. 5.12. Complete schematic of the proposed fully differential charge pump                                                     | 161 |

# LIST OF TABLES

| Table 3.1. Data rates and frame formats supported by SONET                            |

|---------------------------------------------------------------------------------------|

| Table 3.2. Mapping relationship between phase error, QPD output and QCP output        |

| Table 3.3. The range of frequency and amplitude of the VCO under different corners88  |

| Table 3.4. The range of frequency and amplitude of the VCO at different temperature89 |

| Table 3.5. PSRR of the VCO at different operating frequencies       91                |

| Table 3.6. Simulated full-chip performance summary of the CDR                         |

| Table 3.7. Performance comparison between this work and existing solutions            |

| Table 4.1. Performance comparison between the LILFD and existing solutions            |

### CHAPTER I

### INTRODUCTION

#### I.1. Application Background

High-speed serial data links are quickly gaining in popularity in recent years. They are taking the place of traditional parallel data links because serial data links enable data to be transmitted at higher data rates and over longer distance. Examples of traditional parallel data links include LPT (Line Printer Terminal, usually used to connect printers), Parallel ATA (Advanced Technology Attachment, commonly known as IDE interface, usually used to connect hard drives), SCSI (Small Computer System Interface, usually used to connect hard disks and scanners), etc. Parallel data links were widely used a few years ago. Compared with serial data links, parallel data links can directly transmit data in terms of bytes or words without the over head of assembling and disassembling. However, it's hard for parallel data links to achieve data rates higher than one gigabits/second. When the data rate goes above one gigabits/second, it is difficult to match the channel delay and synchronize the signals on the different channels of the parallel link. In comparison, serial data links can easily achieve data rates of several gigabits per second since the entire data stream is sent over a single channel and does not suffer from synchronization problem. Although serial data links can also have multiple channels, the different channels carry independent data streams and do not have to be synchronized. As an additional merit, the

This dissertation follows the style of IEEE Journal of Solid State Circuits.

cables for serial data links are more compact in form factor than cables for parallel data links and take less space in systems with limited space budget. Popular multi-gigabits serial data link applications or standards based on serial cables include Serial ATA [1], Serial SCSI [2], SONET/STM [3], 10 Gigabits Ethernet, 10 Gb/s Fiber Channel, etc. A comparison of Parallel ATA cable and Serial ATA cable is shown Fig. 1.1 to illustrate the difference in form factor. The Parallel ATA cable has 80 pins while the serial ATA cable has only 7 pins. Another type of serial data links are backplane transceivers in which the data is transmitted via metal trace on printed-circuit board (PCB) between different components on the same board. In this case, no additional cable is needed. Serial data links based on on-board traces include PCI Express [4], HyperTransport [5], RapidIO [6], etc.

Fig. 1.1. Comparison of a parallel ATA cable and a serial ATA cable

## I.2. Architectures of Serial Data Link Transceivers

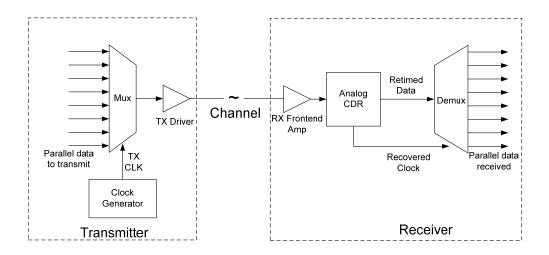

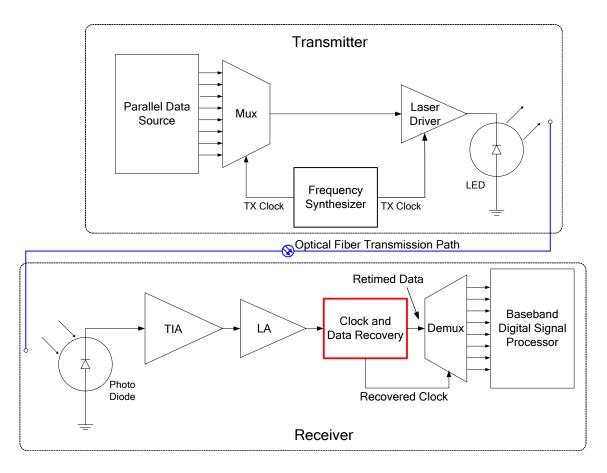

Based on the number of channels, serial data link transceivers can be categorized into single-channel and multiple-channel transceivers. Single-channel transceivers are usually implemented with the architecture shown in Fig. 1.2. In the transmitter, a clock generator

PLL is used to generate the transmitter clock. A multiplexer (MUX) unit driven by the transmitter clock is employed to assemble low-speed parallel data streams into a high-speed serial data stream. The serial data stream is sent into the link channel via the transmitter driver (TX Driver). In the receiver, the signal picked up from the channel is first amplified to full scale by the front-end amplifier. After that, the Analog CDR (clock and data recovery) module is employed to recover the clock from the incoming data stream and retime the data with the recovered clock. The implementation of the CDR here is based on PLLs with analog loop filters. The retimed data stream is then split into parallel low-speed data streams via the demultiplexer block (Demux). This architecture is not suitable to be used in multiple-channel transceivers mainly because the transmitter and the receiver have separate PLLs and VCOs. When multiple transmitters and receivers are integrated on the same chip, the VCOs will pull each other because they are not synchronized in phase or frequency. As a result, the PLLs may not achieve lock or stay locked properly.

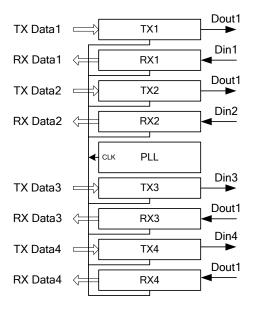

The typical architecture for multiple-channel serial data link transceivers is shown in Fig. 1.3. Four channels of transmitters and receivers are shown as an example, and they are usually integrated on the same chip in practical implementations. A single PLL is employed to generate the clock signal to drive the transmitters and receivers in all the channels. The transmitter structure here is similar to the transmitter structure shown in the left part of Fig. 1.2. Meanwhile, the receiver generates the recovered clock and the retimed data from the incoming data, making use of the same clock provided by the PLL. The recovered clock is generated from the clock provided by the PLL via dynamic phase-interpolation

automatically performed by a delay-locked loop (DLL) inside the receiver. The PLL used in multiple-channel transceivers must be able to generate at least four clock phases as the fundamental requirement by the phase-interpolation operation. Since there is only one VCO within the entire multiple-channel transceiver, no frequency pulling issues occur.

Fig. 1.2. Typical architecture of a single-channel transceiver

Fig. 1.3. Typical architecture of a multiple-channel transceiver

### I.3. Research Focus

In serial data link transceivers, the PLL is the most critical building block due to stringent performance requirements. In the transmitter, PLL is implemented as a frequency synthesizer which generates the transmitter clock from a crystal reference signal. In the receiver, the PLL takes the form of a CDR which is used to extract the recovered clock and the retimed data from the received signal. In serial data link transceivers, the most important performance index for the PLL is jitter in time domain instead of phase noise in frequency domain. The time-domain jitter must be controlled within a certain limit to maximize the eye-opening of the transmitted data and minimize the bit error rate (BER) of the received data. The jitter performance indexes include jitter generation, jitter tolerance to random jitter or deterministic jitter, jitter transfer bandwidth, jitter peaking, etc. In addition, the power dissipation of the PLLs used in serial data links must be minimized under the prerequisite of meeting the data rate requirements.

This dissertation is focused on the design of CMOS integrated phase-locked loops for applications in serial data link transceivers. The research will target at both optimization of system architectures and innovative design of various building blocks inside the PLL, e.g., phase detector, frequency detector, charge pump, voltage-controlled oscillators and frequency divider. The chip prototypes are implemented in standard CMOS processing technology since it is compatible with digital circuits and reduces the manufacturing cost. Chapter II covers the modeling and analysis of PLLs using binary phase detectors. It serves as the theoretical foundation for chapter III, which presents the design of a 10Gbps CDR for the application of SONET OC-192. Chapter VI presents the design of a fully differential injection-locked frequency divider with high operating frequency (up to 18 GHz) and low power dissipation. Chapter V discusses design and optimization techquiues of high-speed fully differential charge pumps. Chapter VI summarizes and makes conclusions about the entire dissertation.

#### CHAPTER II

# MODELING AND ANALYSIS OF PHASE-LOCKED LOOPS BASED ON BINARY PHASE DETECTORS

### II.1. Introduction

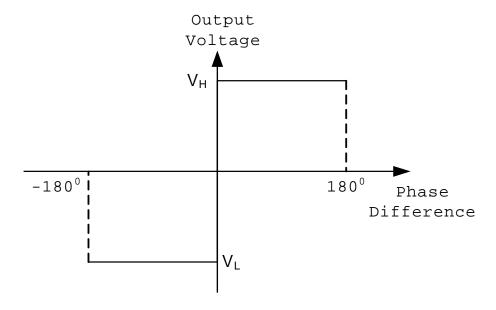

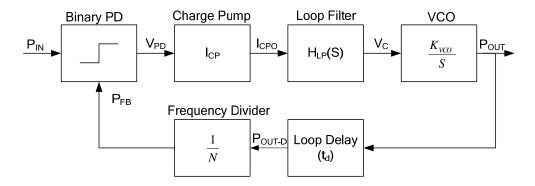

Phase-locked loops (PLL) using binary phase detectors (BPD) are receiving more attention with ever-increasing demand for higher operational frequency and data rate. BPD is also called bang-bang phase detector (PD). It outputs high level or low level depending on the sign of the input phase difference, as shown in Fig. 2.1. The advantage of BPD over linear phase detector (LPD) is that BPD can operate at a much higher speed without suffering from dead-zone problems or component mismatches [7]. PLLs based on BPDs, i.e., binary PLLs (BPLL), have found many applications in systems that require an ultra-high-speed reference input signal with a frequency comparable to the VCO frequency. Some examples include multi-gigahertz clock multipliers [8], optical receivers (STM, SONET) [7] [9], high-speed serial data links (SATA, PCI Express) [10].

BPLL is a nonlinear system because the BPD module has nonlinear phase-to-voltage transfer characteristic. It is a hybrid structure between a continuous system and a discrete-time system because the loop filter and VCO behave as continuous-time modules while the BPD works by using discrete-time sampling. Many efforts have been made investigating the nonlinear loop dynamics of BPLLs [11]-[13]. However, the existing models and analyses are incomplete, not very accurate and do not provide enough insights and

guidelines for IC designers. [11] and [12] mainly focus on the characterization of transfer and tolerance properties of BPLL in response to large sinusoidal input jitter without detailed analysis of the steady-state behavior of the loop itself. [13] focuses on a fully digital BPLL implementation with a pure discrete-time iterative method; this paper, however, does not discuss BPLL using analog filters which is more prevalent in practical applications. The condition for zero jitter peaking is not discussed in [11]-[13]. Also, no detailed discussions have been made in the existing literatures on jitter caused by intersymbol interference (ISI), which is the most dominant source of jitter generation in multigigabits binary CDRs. What is more, the condition to limit jitter peaking within a certain level has not been investigated, which makes it hard for designers to choose the minimum filter capacitance to achieve minimum silicon area and maximum level of integration.

The nonlinear loop dynamics of BPLL is modeled and analyzed in full detail in this work by combining discrete-time and continuous-time analysis. The steady-state waveforms of BPLL using 1<sup>st</sup> and 2<sup>nd</sup> order loop filters under a jitter-free environment are derived in section II. The existence of multiple oscillation modes is revealed and the stablest oscillation mode is determined by evaluating the tolerance against random jitter disturbance. Section III focuses on the jitter performance properties of BPLL. First, BPD and jitter due to ISI (JISI) are modeled. After that, jitter transfer bandwidth, jitter-peaking and jitter tolerance mask of BPLLs are characterized. Lastly, jitter generation due to JISI and VCO phase noise is analyzed. Section IV draws the conclusions of this analysis.

Fig. 2.1. Transfer characteristic of an ideal BPD

Fig. 2.2. Phase-domain model of PLL based on binary PD

BPLL is a phase-locked loop which detects the phase difference between the reference signal and feedback signal using a BPD. The reference signal can be a periodical signal or a random bit sequence. Particularly, when the incoming signal is random data, the BPLL becomes a Binary CDR (BCDR). The transfer characteristic of an ideal BPD is shown in

Fig. 2.1. The output of a BPD switches between low and high level depending on the sign of the input phase difference. The phase-domain block diagram of a BPLL is shown in Fig. 2.2.  $H_{LP}(S)$  models the transfer function of the loop filter.  $I_{CP}$  is the charge pump (CP) output current.  $K_{VCO}$  is the VCO gain.  $I_{CP}$  and  $K_{VCO}$  will be abbreviated as I and K in this work to reduce the length of long equations. The loop delay cell models the lumped delay (t<sub>d</sub>) caused by all the building blocks within the loop. The frequency divider module is optional depending on the actual implementation. For simplicity, it will be ignored in the following analysis since it is just a gain factor in the phase domain. The phase-domain model in Fig. 2.2 is implemented as a behavioral prototype with Simulink modules in Matlab to verify the correctness of the derived expressions. Steady-state analysis of a BPLL with 1<sup>st</sup> order and 2<sup>nd</sup> order filter are presented respectively.

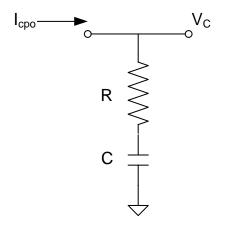

### II.2.1 BPLL with First-order Loop Filter

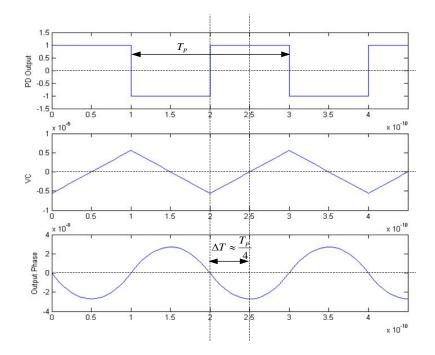

In this section, the steady-state behavior of BPLLs with first order loop filters will be analyzed. A first-order loop filter is the series combination of a resistor R and a capacitor C to convert the charge pump current into voltage. The schematic of the first order filter is shown in Fig. 2.3. It is widely used in practical implementations of BPLL and BCDR [7]-[9]. In some fully-digital implementations [8], the 1st-order loop filter is split into a proportional branch and an accumulative branch. The steady-state waveforms of the BPLL prototype with a 1<sup>st</sup>-order filter are drawn illustratively for better understanding in Fig. 2.4 based on simulation results. P<sub>OUT-D</sub> is the delayed version of the output phase as indicated

Fig. 2.3. Schematic of a first-order loop filter

in Fig. 2.2. It can be reasonably assumed that all the steady state waveforms are symmetric around zero and have the same period of TP in steady state. Since the BPD output is just the sign of phase error, it must be a square wave of 50% duty cycle with period of TP in the absence of input jitter. Thus, the waveform of VCO control voltage (VC) is obtained as,

$$V_{C}(t) = \begin{cases} \frac{It}{C} + IR + \frac{IT_{P}}{4C}, & -\frac{T_{P}}{2} < t < 0\\ -\frac{It}{C} - IR + \frac{IT_{P}}{4C}, & 0 < t < \frac{T_{P}}{2} \end{cases}$$

(1)

The output phase  $P_{OUT}$  is derived as the integration of  $KV_C(t)$ ,

$$P_{OUT} = \begin{cases} K \left( \frac{It^2}{2C} + IRt + \frac{T_P It}{4C} + \frac{IRT_P}{4} \right) & -\frac{T_P}{2} < t < 0 \\ K \left( -\frac{It^2}{2C} - IRt + \frac{T_P It}{4C} + \frac{IRT_P}{4} \right) & 0 < t < \frac{T_P}{2} \end{cases}$$

(2)

Please note that the initial conditions for the output phase and control voltage in (1) and (2) are derived based on the assumption of symmetry around zero. The peak of the output phase occurs at t=0, which is obtained from (68) as,

$$A_{OUT} = P_{OUT}(0) = \frac{IKRT_P}{4}$$

(3)

Fig. 2.4. Steady-state waveforms of BPLL with 1st-order filter

It can be seen from (3) that the output phase amplitude is proportional to R and  $T_P$  and it does not depend on the filter capacitor value. As shown in Fig. 2.4, the peaks of  $P_{OUT}$  are

aligned to the transition edges of  $V_{PD}$ . The zero-crossing time of  $P_{OUT-D}$  (point C) must sit between time A (where the BPD switches) and time B (the sampling instant immediately preceding time A). Otherwise, the BPD would have switched at time B instead of time A because the sign of the phase difference has already changed at time B. Denoting the values of  $P_{OUT-D}$  at point A and B as  $P_{OUT0}$  and  $-P_{OUT1}$ , this condition can be expressed as follows,

$$\begin{cases} P_{OUT0} = P_{OUT-D}(0) = P_{OUT}(-t_d) > 0 \\ -P_{OUT1} = P_{OUT-D}(-T_s) = P_{OUT}(-t_d - T_s) < 0 \end{cases}$$

(4)

The range for the oscillation period  $T_P$  can be solved by substituting (68) into (4) and the result is obtained as,

$$T_{MIN} = \frac{2t_d (2RC - t_d)}{RC - t_d} < T_P < \frac{2(T_s + t_d)(2RC - T_s - t_d)}{RC - T_s - t_d} = T_{MAX}$$

(5)

The above range is derived based on the condition  $RC>T_S+t_d$  which is satisfied in most practical designs and ensures the stability of the BPLL. Also, since the BPD output is a square wave with 50% duty cycle and each half cycle must be a multiple of  $T_S$  due to the sampling nature of the BPD, the complete cycle  $T_P$  must be a multiple of  $2T_S$ , as expressed below,

$$T_P = 2nT_S, \quad n = 1, 2, 3...$$

(6)

Combining (5) and (6), it can be concluded that  $T_P$  must be an even multiple of  $T_S$  staying within the upper limit  $T_{MAX}$  and the lower limit  $T_{MIN}$ . An interesting conclusion indicated by (5) is that the BPLL is able to oscillate at a range of oscillation periods (modes) in steady state. The actual oscillation mode depends on the initial voltage over the loop filter capacitor and the initial output phase of the VCO. The initial voltage on the capacitor to reach a particular oscillation period can be derived from (1) as follows,

$$V_{C0} = V_C(0) = IR + \frac{IT_P}{4C}$$

(7)

The initial output phase of the VCO is simply the value of  $P_{OUT}(0)$  which is given by (3). By applying the right initial voltage and output phase, all the oscillation modes can be produced by Matlab simulations. That verifies that all the oscillation modes are sustainable stable states of the BPLL in the absence of input jitter.

When the loop delay  $t_d$  is zero,  $T_{MIN}$  is zero and the actual lower limit for the possible oscillation periods becomes  $2T_s$ . When the loop delay is much larger than one sampling period, i.e.,  $t_d$ >> $T_s$ ,  $T_{MIN}$  is very close to  $T_{MAX}$  and the BPLL oscillates within a small frequency band in steady state. In this case, it can be approximated that the BPLL has only one mode equal to  $(T_{MAX}+T_{MIN})/2$  to achieve greater simplicity. It can be seen from (5) that the BPLL tends to oscillate at longer periods with the increase of the loop delay, which is intuitively consistent since longer latency decreases the response time of the loop.

When RC >>T<sub>S</sub>, the voltage variations on the capacitor can be ignored in steady state. Under this condition, the behavior of the BPLL closely resembles the behavior of BPLL with zero-order loop filter, i.e., a simple resistor; the values for  $T_{MIN}$  and  $T_{MAX}$  can be approximated as,

$$4t_d \approx T_{MIN} < T_p < T_{MAX} \approx 4(T_s + t_d)$$

(8)

It is easy to see that the BPLL has only two oscillation periods within the given range for  $T_P$ . When  $t_d \gg T_S$ , these two oscillation periods are proportional to the loop delay. In the special case when  $t_d=0$  and  $C=\infty$ , it is easy to see that  $T_{MIN}=0$  and  $T_{MAX}=4T_S$ ; thus, the BPLL has only one oscillation mode with  $T_P=2T_S$ .

Although the BPLL is able to have a range of sustainable oscillation modes in the jitter-free case, the steady states associated with each oscillation mode may be broken when the input jitter is large enough to change the decision of the BPD. When the input jitter stays smaller than both  $P_{OUT0}$  and  $P_{OUT1}$  as defined in (4) (refer to Fig. 2.4), the BPD output is exactly the same as the jitter-free case; the BPLL sustains its original oscillation mode without being disturbed. On the other hand, if the input jitter is larger than either  $P_{OUT0}$  or  $P_{OUT1}$ , the BPD will make different decisions from the jitter-free case. The original steady state will be broken and the loop may settle to a different oscillation mode. Therefore, we can define the following index to measure the relative stability of each oscillation mode,

$$D_{stable} = \min(P_{OUT0}, P_{OUT1})$$

(9)

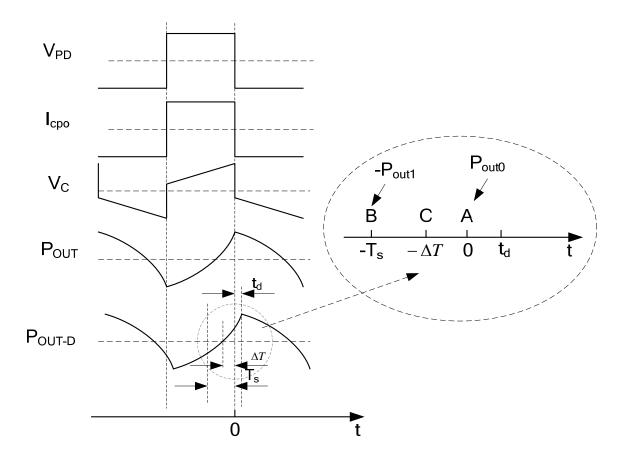

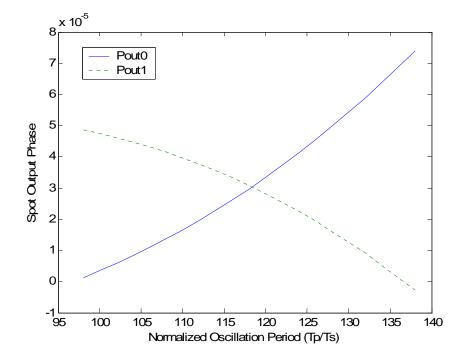

The stablest oscillation mode (SOM) can be determined by finding the maximum value of  $D_{stable}$ . When Gaussian input jitter (virtually unbounded) is applied, the BPLL is expected to settle to the SOM at the greatest probability out of all the possible modes. The values of  $P_{OUT0}$  and  $P_{OUT1}$  across all the oscillation modes under a test case (RC/T<sub>S</sub>=4 and t<sub>d</sub>=T<sub>S</sub>) is shown in Fig. 2.5.  $P_{OUT0}$  increases monotonically and  $P_{OUT1}$  decreases monotonically with the increase of T<sub>P</sub>. It is easy to see that the maximum value of  $D_{stable}$  occurs when  $P_{OUT0}=P_{OUT1}$ . Thus, based on the definition of  $P_{OUT0}$  and  $P_{OUT1}$  in (4), the following equation must be satisfied at the SOM,

$$P_{OUT}(-t_{d} - T_{s}) + P_{OUT}(-t_{d}) = 0$$

(10)

The period at the SOM is derived by solving (10) as,

$$T_{P-SOM} = \frac{(T_s + 2t_d)(4RC - T_s - 2t_d) - T_s^2}{2RC - T_s - 2t_d}$$

(11)

This result is verified by simulations: when Gaussian input jitter is applied, the oscillation period of the BPLL does settle to values close to  $T_{P-SOM}$  as predicted. Hence, in the presence of jitter disturbance, the expected value of the output jitter amplitude is equal to the output jitter amplitude at the SOM and it is obtained from (3) as,

$$\overline{A_{OUT}} = P_{OUT}(0)|_{T_p = T_{P-SOM}} = \frac{IKRT_{P-SOM}}{4}$$

(12)

In actual operation, the BPLL moves back and forth around the SOM due to the jitter disturbance. The variance from the SOM depends on the strength of the input jitter disturbance. It can be seen from (11) that  $T_{P-SOM}$  increases with the decrease of RC and the increase of  $t_d$ ; so does the expected output jitter amplitude. Therefore, the capacitor value should be maximized to minimize the output jitter within acceptable limit of the loop locking time. On the other hand, the loop delay  $t_d$  should also be minimized to reduce the output jitter.

Fig. 2.5. POUT0 and POUT1 across all the modes for BPLL with 1st order filter

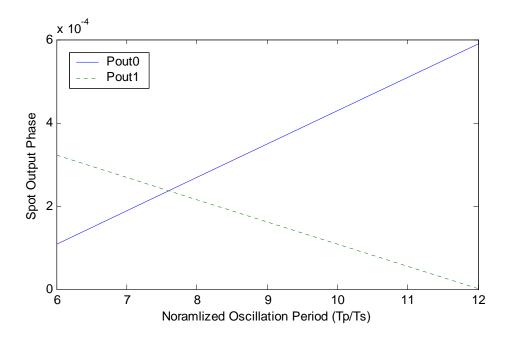

### II.2.2 BPLL with Second-Order Filter

In this section, the steady-state behavior of BPLLs with second order loop filters will be analyzed. The schematic of a second order filter is shown in Fig. 2.6. It adds  $C_2$ , a capacitor usually much smaller than  $C_1$ , in addition to the first order filter. Two reasonable

Fig. 2.6. Schematic of the second order loop filter

assumptions are made on the steady state of BPLL with  $2^{nd}$ -order filter: all the loop nodes have the same oscillation period of  $T_P$ ; the control voltage  $V_C$  and the output phase are symmetric around a stable DC value (assumed as zero in the following analysis). Based on these two assumptions and following the approach used in the first-order filter, the expression for VCO control voltage is derived and shown below,

$$V_{C}(t) = \begin{cases} V_{0} \left( 1 - \frac{2e^{-t/\tau}}{1 + e^{-T_{p}/2\tau}} \right) + \frac{I(t - T_{p}/4)}{C_{1} + C_{2}}, \ 0 < t < T_{p}/2 \\ V_{0} \left( -1 + \frac{2e^{-(t - T_{p}/2)/\tau}}{1 + e^{-T_{p}/2\tau}} \right) - \frac{I(t - 3T_{p}/4)}{C_{1} + C_{2}}, \ T_{p}/2 < t < T_{p} \end{cases}$$

(13)

where  $V_{0} = \frac{IRC_{1}^{2}}{(C_{1} + C_{2})^{2}}; \quad \tau = R(C_{1} \parallel C_{2})$

The initial voltages on  $C_1$  and  $C_2$  when t=0 are also obtained as shown below,

$$V_{10} = \frac{-I\left[e^{-\frac{T_p}{2\tau}}(T_p + 4R(C_1 || C_2)) + T_p - 4R(C_1 || C_2)\right]}{4(C_1 + C_2)(1 + e^{-\frac{T_p}{2\tau}})}$$

$$V_{C0} = \frac{-I\left[e^{-\frac{T_p}{2\tau}}(T_p - 4R(C_1 || C_2)\frac{C_1}{C_2}) + T_p + 4R(C_1 || C_2)\frac{C_1}{C_2}\right]}{4(C_1 + C_2)(1 + e^{-\frac{T_p}{2\tau}})}$$

(14)

The output phase can be derived as the integration of  $KV_C$  from (13), resulting in,

$$P_{OUT}(t) = K \Biggl[ V_0 \Biggl( t - \frac{T_P}{4} - \tau \Biggr) + \frac{2V_0 \pi e^{-t/\tau}}{1 + e^{-T_P/2\tau}} + \frac{It(2t - T_P)}{4(C_1 + C_2)} \Biggr]$$

when  $0 < t < \frac{T_P}{2}$

$$P_{OUT}(t) = -K \Biggl[ V_0 \Biggl( t - \frac{3T_P}{4} - \tau \Biggr) + \frac{2V_0 \pi e^{(T_P - t)/\tau}}{1 + e^{T_P/2\tau}} + \frac{It(t - T_P)}{2(C_1 + C_2)} \Biggr]$$

(15)

when  $\frac{T_P}{2} < t < T_P$

The initial output phase of the VCO is then derived as,

$$P_{OUT}(0) = KV_0 \left(\tau \tanh\left(\frac{T_P}{4\tau}\right) - \frac{T_P}{4}\right)$$

(16)

The time when  $P_{OUT}$  reaches the minimum value can be derived by finding the zeroderivative point of (15). The result is obtained as,

$$t_{\min} = LambertW \left( \frac{C_1 e^{\frac{C_1}{C_2}}}{C_2 \cosh\left(\frac{T_p}{4\tau}\right)} \right) \tau - \frac{V_0(C_1 + C_2)}{I} + \frac{T_p}{4}$$

(17)

LambertW(z) is a special function whose value is the solution of the following equation [16],

$$z = xe^x \tag{18}$$

To get more insight on the characteristic of  $t_{min}$ , we assume  $C_1 >> C_2$  and  $\tau > T_P$ ; these are typical conditions for 2nd-order filters used in practical implementations of BPLL. Under these assumptions, (17) can be further simplified as,

$$t_{\min} \approx LambertW\left(\frac{C_1}{C_2}e^{\frac{C_1}{C_2}}\right)\tau - \frac{V_0(C_1 + C_2)}{I} + \frac{T_P}{4} = \frac{T_P}{4}$$

(19)

Substituting (19) into (15), the output phase amplitude is obtained as,

$$A_{OUT} = |P_{OUT}(t_{\min})| \approx \frac{KIT_{p}^{2}}{32(C_{1} + C_{2})} + KV_{0}\tau \left(1 - \frac{1}{\cosh\left(\frac{T_{p}}{4\tau}\right)}\right)$$

(20)

Since we assumed that  $\tau > T_P$  and  $C_1 >> C_2$ ,  $A_{OUT}$  can be further simplified as,

$$A_{OUT} \approx \frac{KIT_P^2}{32C_2} \tag{21}$$

(21) indicates that the output phase amplitude is approximately proportional to the square of  $T_p$  and inversely proportional to the smaller capacitor in the filter. It is proportional to VCO gain and CP current as in the case of 1<sup>st</sup>-order filters. However, it does not depend on the filter resistor. The prototype BPLL was simulated with 2<sup>nd</sup> order filter and the steady-state waveforms are shown in Fig. 2.7. It verifies that the peaks and valleys of the output phase are actually located around  $T_P/4$  from the zero-crossing points as indicated by (19).

Fig. 2.7. Steady-state waveforms of BCDR with C1=10C2 and TP=2TS

Multiple oscillation modes also exist in the steady state of BPLL with 2<sup>nd</sup> order filter. Similar to the analysis of BPLL with 1<sup>st</sup> order filter, the zero-crossing point of the output phase must sit between the switching instant of the BPD and the immediately preceding sampling instant. This constraint can be expressed mathematically as,

$$\begin{cases} P_{OUT}(-t_d) > 0\\ P_{OUT}(-t_d - T_s) < 0 \end{cases}$$

(22)

Substituting (15) into (22) and using third-order Taylor series approximation under the typical condition  $\tau >> T_S + t_d$  and  $T_p >> T_S$ , the range of  $T_P$  is obtained as,

$$\sqrt{48RC_2 t_d} \approx T_{MIN} < T_P < T_{MAX} \approx \sqrt{48RC_2 (T_S + t_d)}$$

(23)

Also,  $T_P$  must be an even multiple of the sampling period  $T_S$ . Thus, the BPLL can oscillate at any even multiples of  $T_S$  limited between  $T_{MAX}$  and  $T_{MIN}$ . All the oscillation modes can be produced in simulation by applying the initial voltages and phase given by (14) and (16). When the loop delay is zero,  $T_{MIN}$  is zero and the lower limit of  $T_P$  becomes  $2T_S$ . When  $t_d >> T_S$ ,  $T_{MIN}$  is close to  $T_{MAX}$  and the BPLL can only oscillate within a narrow frequency band; it can be approximated that the BPLL has a fixed oscillation period equal to  $(T_{MIN}+T_{MAX})/2$ .

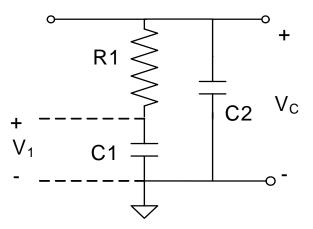

When the BPLL has Gaussian input jitter, the SOM can be determined using the same index  $D_{stable}$  defined in (10) for the analysis of BPLL with 1<sup>st</sup> order loop filter. The values for  $P_{OUT0}$  and  $P_{OUT1}$  (defined in (9) ) across all the possible modes under a test case

$(C_1/C_2=100, T_S=t_d, \tau/T_S\approx 200)$  are plotted in Fig. 2.8.  $P_{OUT0}$  increases monotonically while  $P_{OUT1}$  decreases monotonically with the increase of  $T_P$ . Notice that the maximum value of  $D_{stable}$  occurs when  $P_{OUT0}=P_{OUT1}$ . Thus, the oscillation period at the SOM ( $T_{P-SOM}$ ) can be determined by solving the following equation,

$$P_{OUT}\left(-t_{d}-T_{s}\right) = -P_{OUT}\left(-t_{d}\right)$$

$$\tag{24}$$

If we assume that the output jitter changes linearly with time in one sampling period, equation (24) can be approximated by the following equation,

$$P_{OUT}\left(-t_d - \frac{T_s}{2}\right) = 0 \tag{25}$$

Solving (25) yields the solution for  $T_{P-SOM}$ ,

$$T_{P-SOM} \approx \sqrt{48RC_2 \left(\frac{T_s}{2} + t_d\right)}$$

(26)

The expected value of the output jitter amplitude is equal to the output jitter amplitude at the SOM. It's derived by substituting (26) into (21),

$$\overline{A_{OUT}} = \frac{KIT_{P-SOM}^{2}}{32C_{2}} \approx \frac{3}{4} KIR(T_{s} + 2t_{d})$$

(27)

Equation (27) shows that under the conditions  $\tau \gg T_S + t_d$  and  $T_p \gg T_S$ , the expected output jitter amplitude is proportional  $T_S + 2t_d$  but independent of either C1 or C2.

Fig. 2.8. POUT0 and POUT1 vs. oscillation periods for BPLL with 2nd order filter

# II.3. Jitter Analysis

In this section, the behavior and response of the BPLL under the influence of various jitter sources is investigated. Jitter due to ISI (JISI) and bandwidth-limited BPD is modeled. After that, jitter transfer, jitter tolerance and jitter generation specifications of BPLL are characterized. The analysis of JISI and jitter tolerance only applies to BCDR which takes random data as the reference. The analysis in this section assumes that the BPLL uses the typical first-order filter. It is also assumed that voltage variations on the loop filter capacitor are negligible within a single sampling period since very large capacitors are usually used to avoid jitter peaking.

# II.3.1 Jitter Due to ISI

When an ideal pseudo-random data sequence (PRBS) is passed through a bandwidthlimited module, the output data will have inter-symbol interference between the adjacent data bits. That will make the transition edges of the data bits move back and forth from the original point along the time axis. The variation of transition edges along the time axis can be modeled as equivalent additive jitter in the phase domain.

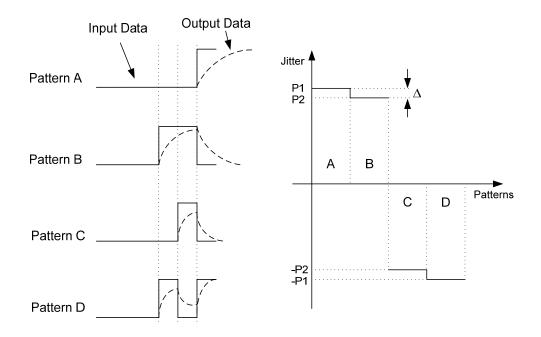

Fig. 2.9. Mapping relationship between bit patterns and jitter values

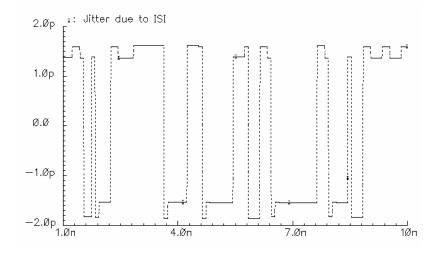

Fig. 2.10. JISI with 10 Gb/s PRBS applied to a LPF of 4 GHz BW

When an ideal PRBS is passed through a 1<sup>st</sup>-order low pass filter, it can be found from simple analysis that the JISI in the output data is mainly distributed around 4 levels. These four levels can be mapped to four bit patterns as shown in Fig. 2.9. It is assumed that the input data has stayed at low level for an infinite length of time before the start of these bit patterns. Also, the jitter shown here refers to the jitter of the last transition of the four bit patterns. The values of the four jitter levels can be represented with four numbers (-P1, -P2, P1 and P2) by choosing an intermediate reference phase. The last output transition of pattern A and B has longer delay from the input transition compared with pattern C and D because the output data is settled more completely before the last transition and the last transition takes longer time to cross zero. There are other bit patterns than those shown in Fig. 2.9. However, they can be assigned to the same group with one of the four listed patterns for similar jitter values because the bits leading the current transition. The plot

of JISI when a 10 Gb/s PRBS is applied to a LPF of 4 GHz bandwidth is shown in Fig. 2.10. The simulated jitter is actually distributed around four levels.

When the bandwidth of the LPF is smaller but comparable to half the data rate, it can be proved that P2 is close to P1. Therefore,

$$\begin{cases} P_2 = P_1 - \Delta \\ \Delta << P_1, P_2 \end{cases}$$

(28)

For simplicity, the JISI can be modeled as a random binary noise switching between -P1 and P1. The value of P1 is determined by the 3-dB bandwidth of the filter and the incoming data rate. Let us assume that the LPF has a single pole at  $\omega_c$  and the incoming data has a bit period of T. The value of P1, a good approximate for the amplitude of JISI, is obtained below by calculating the timing distance between the zero-crossing points of the transient waveforms,

$$P_{1} = \frac{-\ln(1 - e^{-\omega_{c}T})}{2\omega_{c}}$$

(29)

Cascading of 1<sup>st</sup> order LPFs with equal bandwidth can be approximated as a single LPF with an equivalent 3-dB frequency given by the following expression,

$$\omega_{eq,n} = \omega_c \sqrt{\sqrt[n]{2} - 1} \tag{30}$$

Thus, the amplitude of JISI induced by n-stage cascaded buffers is obtained based on (29),

$$P_1 = \frac{-\ln\left(1 - e^{-\omega_{eq,n}}\right)}{2\omega_{eq,n}} \tag{31}$$

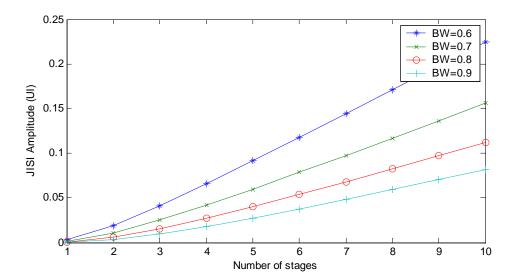

The change of JISI amplitude with the number of cascaded buffer stages is shown in Fig. 2.11. UI is the abbreviation for unit interval, which means the time length of one bit period of the input data. The bandwidth BW is normalized to the PRBS data rate  $(BW=\omega_c/DataRate)$ . Fig. 2.11 shows that JISI increases almost linearly with the number of stages when there are three or more stages. Therefore, proper caution should be exercised in physical implementations of BCDR to ensure not too much JISI is introduced if extra buffers are placed before the BPD for amplification purposes.

Fig. 2.11. JISI amplitude with different number of buffer stages and bandwidth

## II.3.2 Modeling of Bandwidth-Limited BPD

In physical implementations, the BPD has limited bandwidth and speed. The BPD is not able to switch abruptly when the input phase difference changes sign. When one of the two inputs to the BPD is PRBS, the bandwidth limitation of the internal building blocks of the BPD introduces JISI which may make the BPD produce a wrong output level.

Fig. 2.12. Transfer characteristic of a gradual-switching BPD

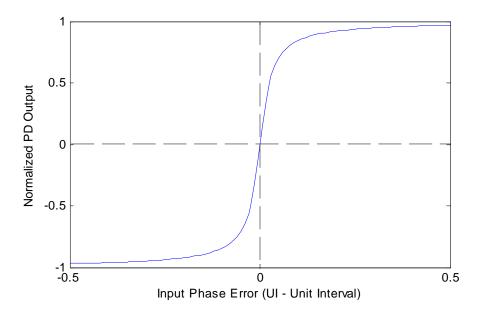

An illustrative plot for the transfer curve of a gradual-switching BPD (GBPD) is shown in Fig. 2.12. The transfer characteristic of a GBPD can be modeled by an inverse tangent function as,

$$V_{PD} = \frac{2}{\pi} \arctan\left(\phi_{in} K_T\right)$$

(32)

where  $\Phi_{in}$  is the input phase difference and  $K_T$  is a coefficient modeling the slope of the curve. Please note that the inverse tangent function is chosen somewhat arbitrarily to roughly emulate the transfer curve of a real GBPD. The actual value of  $K_T$  can be derived by fitting to the simulated transfer curve.

Fig. 2.13. Phase-sweeping characteristic of Alexander's BPD

The JISI introduced by the BPD has a more complex distribution than the one caused by a simple LPF due to nonlinear operation of sampling latches (positive feedback in holding mode) within the BPD. A simple and approximate approach is to refer the JISI caused by the internal building blocks of the BPD to the input terminals of the BPD. For an ideal BPD, it always outputs high level if the incoming data leads the sampling clock. However, the BPD may output low level under the effect of JISI even if the data leads the clock. If the JISI is larger than the input phase difference but has an opposite sign, the BPD will make a wrong decision. If we simulate the BPD by fixing the data phase and sweeping the clock

phase, the output of the BPD will go through three regions, i.e., all-low region, transitional region and all-high region. In the transitional region, the BPD may output high or low depending on the sum of JISI and the input phase difference. The length of the transitional region in terms of phase is equal to the peak-to-peak swing of JISI. Thus, the BPD with internal JISI can be modeled as a jitter-free BPD with additive input-referred JISI (IRJISI) of given amplitude at the input terminal.

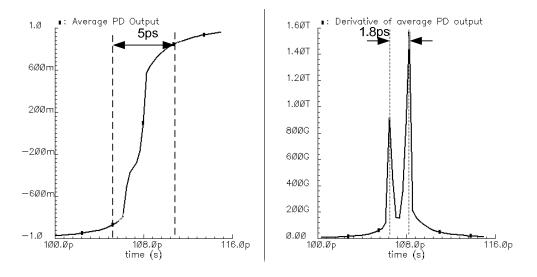

As an example, the classic Alexander's BPD [14] was implemented with 0.18um CMOS transistors and modeled using the proposed approach. The simulated phase-sweeping characteristic is shown in Fig. 2.13. It can be observed that the transition region covers a range of about 5ps. The derivative of average PD output relative to phase is proportional to the probability distribution of IRJISI. Thus, according to the derivative plot, the IRJISI of Alexander PD is mainly distributed around two levels, i.e.,  $\pm 0.9$ ps offset from the center phase.

When the BPD is used in BCDR, the gradual-switching curve and the effects of IRJISI should be modeled independently. The gradual switching coefficient  $K_T$  should be derived by applying two periodical signals to the BPD, which will not produce any JISI. Meanwhile, the IRJISI should be derived by applying a PRBS to one terminal and a periodical signal to the other. The JISI produced by any amplifiers (modeled as LPF) preceding the BPD can also be referred to the BPD input. Thus, the overall BPD plus its preceding amplifiers can be modeled as a gradual-switching BPD with input-referred IRJISI. In [12], The JISI and gradual switching of BPD are mixed together to yield a gradual-switching BPD with even

lower slope. That approach fails to identify the JISI as an active jitter source which contributes to the overall jitter generation of the system. In comparison, the model extraction method proposed here produces output jitter distribution very close to transistor-level simulation results.

#### II.3.3 Jitter Transfer and Jitter Peaking

Jitter transfer defines the transfer characteristic from the input jitter to the output jitter. In BPLL, the jitter transfer characteristic depends on both the frequency and amplitude of the input jitter due to the nonlinearity of the BPD. The capability for the output jitter to track the input jitter is limited by the phase slew rate of the loop (PSRL) [7], [12]. The PSRL is reached when the PD output is continuously low or high. When the voltage variations on the filter capacitor are ignored, the PSRL is given by,

$$\rho = \frac{\partial P_{OUT}}{\partial t} = IRK \tag{33}$$

When the maximum slope of the input jitter is smaller than the PSRL, the output jitter tracks the input jitter closely. The output jitter amplitude is nearly equal to the input jitter amplitude in the tracking region. At the upper bound of the tracking region, the maximum slope of the input jitter is equal to PSRL. Thus, if the input jitter is represented as  $A_{in}sin\omega t$ , the maximum tracking frequency is given below [12],

$$\omega_{TU} = \frac{\rho}{A_{IN}} = \frac{IRK}{A_{IN}}$$

(34)

where  $A_{IN}$  is the amplitude of the input jitter. In the tracking region, the only error between the input and output jitter is due to the binary switching of the BPD. The maximum error is the sum of the maximum phase shift which can be produced by the loop and the input jitter within a single sampling period. It is given by the following expression,

$$P_{E,\max} = \Delta P_{loop,\max} + \Delta P_{IN,\max} = IRKT_S + A_{IN}\omega_{IN}T_S$$

(35)

where  $\omega_{IN}$  is the radian frequency of the input jitter.

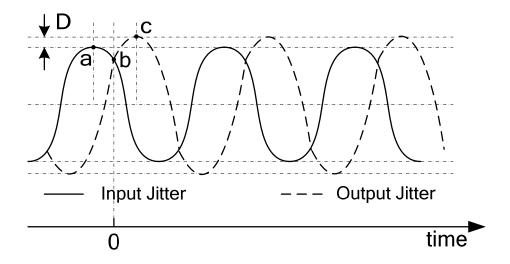

Fig. 2.14. Input / output jitter waveforms in the slewing region

When the maximum slope of the input signal goes beyond the PSRL, the BPLL leaves the full-tracking region and enters a transition region where the BPLL either tracks or slews depending on the instantaneous slope of the input jitter. When the input jitter goes near the

extreme points with relatively smaller slope, the output jitter tracks the input jitter closely. When the input jitter goes near the zero-crossing points with maximum slope, the PD output stays high or low for a continuous length of time and the loop slews. If the output jitter intersects the input jitter before the extreme points, the output jitter has the same amplitude as the input jitter. Otherwise, the output jitter amplitude is smaller than the input jitter amplitude.

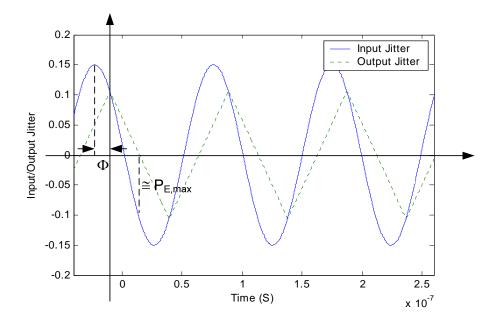

When the input jitter frequency goes even higher, the BPLL enters the slewing region where the loop slews for the entire period. An illustrative plot for the input and output jitter waveforms in the slewing region is shown in Fig. 2.14. Similar to the jitter-free steady state, all the loop nodes have the same oscillation period  $T_{IN}$  in steady state when an input jitter with fixed period  $T_{IN}$  is applied to the loop. Following the same procedure as the one used in the jitter-free steady-state analysis, the expressions for the input/output phase in the slewing region are obtained as,

$$P_{IN}(t) = A_{IN} \cos(\omega_{IN} t + \phi); \quad \phi = \cos^{-1} \frac{T_{IN} K I R}{4 A_{IN}}$$

(36)

$$P_{OUT}(t) = \begin{cases} K \left( \frac{It^2}{2C} + IRt + \frac{IT_{IN}t}{4C} + \frac{IRT_{IN}}{4} \right) & -\frac{T_P}{2} < t < 0\\ K \left( -\frac{It^2}{2C} - IRt + \frac{IT_{IN}t}{4C} + \frac{IRT_{IN}}{4} \right) & 0 < t < \frac{T_P}{2} \end{cases}$$

(37)

The output jitter amplitude  $A_{OUT}$  is derived from (37) as  $P_{OUT}(0)$ , yielding,

$$A_{OUT} = \frac{IRKT_{IN}}{4} \tag{38}$$

It is interesting to notice that output jitter amplitude in the slewing region does not depend on the input jitter amplitude or the capacitor value. The output jitter amplitude decreases at 20dB/dec with the increase of the input jitter frequency. The condition for the loop to stay in the full-slewing region is that the output jitter has smaller slope than the input jitter immediately after the input / output jitter intersect and the BPD switches. Otherwise, the output jitter would track the input jitter for at least a certain length of time after the intersection point, which means the loop is actually in the transition region. Thus, the lower frequency limit of the slewing region is defined by the following critical condition (the time of the intersection point is defined as zero in Fig. 2.14),

$$\frac{\partial P_{IN}(t)}{\partial t}\Big|_{t=0+} = \frac{\partial P_{OUT}(t)}{\partial t}\Big|_{t=0+}$$

(39)

By substituting (36)-(37) into (39) and assuming the voltage variations on the capacitor are negligible within one input jitter period, an approximate expression for the lower frequency limit of the slewing region is derived and shown below,

$$\omega_{LS} = \frac{IRK\sqrt{\pi^2 + 4}}{2A_{IN}} \tag{40}$$

The input-to-output jitter attenuation at this critical frequency is derived from (38) and (40) and given below,

$$\frac{A_{OUT}}{A_{IN}}\Big|_{\omega=\omega_{LS}} = \frac{\pi}{\sqrt{\pi^2 + 4}} = -1.48dB$$

(41)

The result above indicates that the 3dB frequency of the jitter transfer curve falls in the slewing region. Thus, the 3dB jitter transfer bandwidth can be derived from (38) and the result is shown below,

$$\omega_{3dB} = \frac{\pi IRK_{VCO}}{\sqrt{2}J_A} \tag{42}$$

The 3dB frequency of the prototype BPLL predicted by (42) is 10.13MHz for an example set of parameters (I=40 $\mu$ A, K=1GHz/V, J<sub>A</sub>=0.15UI, R=56 $\Omega$ , C=35nF). That agrees well with the simulation result (10.1MHz). In comparison, the estimated value based on the equation given in [12] deviates from the simulated value by 40% because it derives the 3dB frequency by approximate extrapolation instead of exact calculation.

Fig. 2.15. Illustrative plot for BPLL jitter peaking

Many CDR applications require the peaking in the jitter transfer characteristic to be limited within a certain small level so that the input jitter will not be amplified too much after passing through multiple data links [15]. Similar to a linear CDR, the capacitor in the first order loop filter must be reasonably large not to introduce jitter peaking. However, the definition of damping factor is no longer valid in analyzing the peaking effects in a BPLL. In the tracking or transition region, the output jitter amplitude is equal to or smaller than the input jitter amplitude because the output jitter tracks the input jitter near the peaks or valleys of the input sine wave. Therefore, the loop must stay in the slewing region to have peaking. An illustrative plot of BPLL waveforms with peaking is shown in Fig. 2.15. The output jitter consists of two pieces of symmetric parabolic curves within a single period; the maximum value of the output jitter occurs at the extreme point of the parabolic curve (point 'c' in Fig. 2.15) instead of the intersection point (point 'b' in Fig. 2.15) of the input / output jitter. The output jitter continues to rise after the intersection point 'b' until the extreme

point 'c' is reached, which results in peaking. The time when the output jitter reaches the peak can be derived from (37) based on the condition of zero-derivative, i.e.,  $P_{OUT}(t)=0$ . The result is obtained as,

$$t_{\max} = \frac{T_{IN}}{4} - RC \ge 0 \tag{43}$$

$t_{max}$  must be greater than the time of the intersection point 'b', which is defined as zero in Fig. 2.15. Otherwise, the extreme point does not actually exist in the output jitter and the output jitter peaks at the intersection point instead. Since the output jitter at the intersection point has no way to be larger than the input jitter amplitude, no peaking will happen. Substituting (43) into (37) yields the output jitter amplitude,

$$A_{OUT} = P_{OUT}(t_{\max}) = \frac{IK(T_{IN}^{2} + 16R^{2}C^{2})}{32C}$$

(44)

It can be seen from (44) that the output jitter amplitude increases with the increase of the input jitter period  $T_{IN}$ . Since the loop is in slewing region, the output jitter value at the intersection point is given by (38). Therefore, if  $T_{IN}$  decreases, the output jitter at the intersection point increases and the intersection point 'b' moves closer to the peak point 'a' of the input sine wave. When point 'b' and 'a' coincide, the loop reaches the lower limit of the slewing region and the output jitter reaches the maximum amplitude. In this case, the output jitter value at the intersection point (given by (38)) is equal to the input jitter amplitude, i.e.,

$$A_{OUT,Intersect} = \frac{KIRT_{IN}}{4} = A_{IN}$$

(45)

The corresponding input jitter period is obtained from (45) as,

$$T_{IN} = \frac{4A_{IN}}{KIR} \tag{46}$$

By substituting (46) into (44), the maximum output jitter amplitude that can be achieved for a given capacitor is obtained as,

$$A_{OUT} = \frac{1}{2CKIR^2} \left[ A_{IN}^2 + (CKIR^2)^2 \right]$$

(47)

To limit the peaking to G dBs, we have,

$$A_{OUT} = \frac{1}{2CKIR^2} \left[ A_{IN}^2 + (CKIR^2)^2 \right] \le 10^{G/20} A_{IN}$$

(48)

The minimum capacitor value to limit the peaking to be less than G dbs can be derived by solving (48) considering of the limit given by (43). The result is obtained as,

$$C \ge C_{MIN} = \frac{A_{IN}}{R^2 IK} \left( 10^{G/20} - \sqrt{10^{G/20} - 1} \right)$$

(49)

(49) indicates that the  $C_{MIN}$  is inversely proportional to the square of the filter resistance, and more important,  $C_{MIN}$  is proportional to the input jitter amplitude. That means, even if any large capacitor is used, a given level of peaking can always be produced by applying input jitter with large enough amplitude. Fortunately, in actual CDR applications, the maximum input jitter amplitude is limited by the jitter tolerance mask [15]. As long as there is no peaking within the jitter tolerance mask, the prescribed specifications can still be met with a BCDR. The BPLL model was simulated with the existence of peaking to verify the expressions derived above. The simulated waveforms are shown in Fig. 2.16. In the simulated case, the output jitter amplitude is 0.193UI (Unit Internal), which generates peaking of 2.2dB compared with the input jitter amplitude of 0.15UI. The simulated level of jitter peaking exactly matches the result predicated by the above expressions.

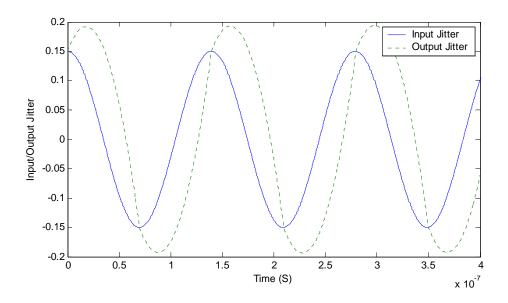

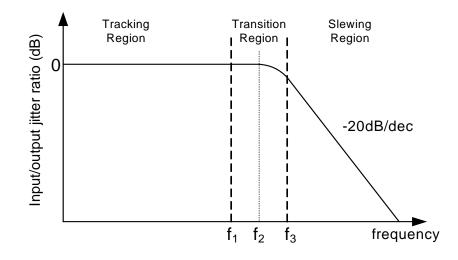

When a large enough capacitor is used to avoid any peaking, the jitter transfer curve of a BPLL over the entire frequency band is shown in Fig. 2.17. It resembles the transfer curve of a 1<sup>st</sup>-order LPF in that there is no attenuation in the tracking region while the output falls at 20dB/dec in the slewing region. There is no amplitude attenuation in the beginning part  $(f_1 \sim f_2)$  of the transition region while there is some amplitude attenuation in the ending part  $(f_2 \sim f_3)$ , according to the previous analysis.

Fig. 2.16. Simulated waveforms of BPLL with jitter peaking (0.15 UI input

jitter@7.168MHz, C=300pF)

Fig. 2.17. BPLL input-to-output jitter transfer characteristic

### II.3.4 Jitter Tolerance

Jitter tolerance is the maximum amplitude of the input jitter that can be applied to a CDR without causing bit errors. Jitter tolerance mask is the plot of the maximum input jitter amplitude versus the corresponding frequency. Usually the bit error rate increases drastically when the phase error between the clock and data exceeds a certain limit denoted as  $P_{EL}$ . The limit is 0.5UI in the ideal case but should be smaller in practical designs due to various jitter sources.

When the input jitter frequency is very high, the output jitter amplitude is heavily attenuated compared with the input jitter amplitude. In this case, the phase error is almost equal to the input jitter amplitude [12], hence,

$$P_{E} = \left| P_{IN} - P_{OUT} \right| \approx \left| P_{IN} \right| \le A_{IN} \le P_{EL}$$

$$\tag{50}$$

Thus, jitter tolerance is limited by  $P_{EL}$  at very high frequencies.

At intermediate frequencies, the loop slews for most of the entire period when the input jitter amplitude reaches the jitter tolerance mask (refer to Fig. 2.14). In this case, the slewing-region equations (36) and (37) can be used to represent the input and output jitter waveforms. Assuming the voltage variations on the capacitor are negligible in one period of the input jitter in the slewing region, the phase error is given by,

$$P_{E} = \left| P_{IN}(t) - P_{OUT}(t) \right| = \left| A_{IN} \cos\left(2\pi f_{IN}t + \phi\right) - K\left(-IRt + \frac{IR}{4f_{IN}}\right) \right|$$

(51)

The maximum phase error for a given input jitter frequency and amplitude is derived from (51) and given below,

$$P_{E,MAX} = A_{IN} \sqrt{1 - S_I^2} + A_{IN} S_I \left( \sin^{-1} S_I + \cos^{-1} \frac{\pi S_I}{2} - \frac{\pi}{2} \right)$$

(52)

where,

$$S_I = \frac{KIR}{A_{IN}\omega_{IN}}$$

(53)

$S_I$  is the ratio of the PSRL over the maximum slope of the input jitter.  $S_I$  must be less than  $2/\pi$  for equation (52) to hold. Unfortunately, it is not possible to derive simple analytical expressions for the maximum input jitter amplitude in terms of  $\omega_{IN}$  and  $P_{E,MAX}$  from (52). An approximation method is proposed in [12], which assumes that the maximum phase error occurs close to the zero-crossing point of the output jitter (refer to the illustration in Fig. 2.14). Under this assumption, we have,

$$P_{E,MAX} \approx A_{IN} \cos\left(\phi + \frac{\pi}{2}\right) = \sqrt{A_{IN}^{2} - \left(\frac{KIR}{4f_{IN}}\right)^{2}} \le P_{EL}$$

(54)

Thus, the input tolerance at intermediate frequencies becomes,

$$A_{IN} \le \sqrt{P_{EL}^{2} + \left(\frac{KIR}{4f_{IN}}\right)^{2}}$$

(55)

When the input jitter changes very slowly, slope on the input jitter can be considered as quasi-static frequency deviation since there is enough time for the capacitor to be charged (or discharged) to the right voltage to drive the VCO to produce the proper amount of frequency deviation. The changing rate of the input frequency is equal to the 2<sup>nd</sup>-order derivative of the input jitter. Thus, the frequency slew rate of the input signal (FSRI) is given by,

$$FSRI = \frac{\partial P_{IN}^{2}}{\partial t^{2}}\Big|_{MAX} = A_{IN} \omega_{IN}^{2}$$

(56)

On the other hand, the slew rate of the output frequency is proportional to the slew rate of the voltage on the capacitor. Thus the frequency slew rate of the loop (FSRL) is given by,

$$FSRL = \frac{KI}{C}$$

(57)

It is reasonably assumed that the jitter tolerance at very low frequencies is much larger than 1 UI. Therefore, the ratio of the input and output jitter amplitude is very close to 1 even when the phase error goes up to  $P_{EL}$  (up to 0.5UI). That means the frequency slew rate of the loop should be very close to the maximum changing rate of the input frequency (but a little smaller), hence,

$$FSRI \le FSRL \tag{58}$$

Combining (56)-(58), the jitter tolerance in the low frequency region is obtained as,

$$A_{IN} \le \frac{KI}{C\omega_{IN}^{2}}$$

(59)

Fig. 2.18. Simulated BPLL waveforms with 20 KHz and 144 UI sinusoidal input jitter

The BPLL model was simulated in Matlab with 20 KHz and 144 UI sinusoidal input jitter to verify the level of jitter tolerance in the low frequency region. The simulated waveforms are shown in Fig. 2.18. Although the maximum phase error is as large as 0.5 UI, the input jitter and output jitter curves almost overlap each other in the plot, which indicates little attenuation in terms of percentage. The input jitter tolerance predicted by (59) is 137 UI,

only 5% away from the actual simulation result. In comparison, the result predicted by the equation proposed in [12] is 343 UI, which is far away from the simulation result. The reason for the large deviation is that the equation in [12] is based on the incorrect assumption that the loop slews for most of the entire period with very low input frequencies. Actually, Fig. 2.18 shows that the loop tracks the input jitter closely for a greater part of the entire period.

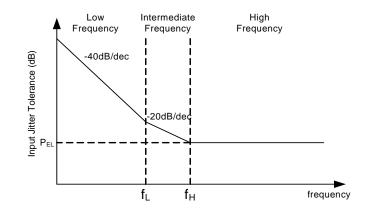

The jitter tolerance of the BPLL over the entire frequency band is shown in Fig. 2.19. It is divided into three regions based on different slopes. In the low frequency region, the jitter tolerance drops at 40 dB/dec with the increase of frequency as indicated by (59). In the intermediate frequency region, the jitter tolerance drops at 20 dB/dec as indicated by (55). In the high frequency region, the jitter tolerance has a flat value equal to  $P_{EL}$  as indicated by (50). To find the critical frequencies between the different regions, the jitter tolerance in the intermediate frequency region can be approximated as a straight line in the bode plot. The approximated expression is shown below,

$$A_{IN} \le \sqrt{P_{EL}^{2} + \left(\frac{KIR}{4f_{IN}}\right)^{2}} \approx \frac{KIR}{4f_{IN}}$$

(60)

The upper limit of the low frequency region  $(f_L)$  can be found as the extrapolated intersection point of (60) and (59). The lower limit of the high frequency region  $(f_H)$  can be found as the extrapolated intersection point of (60) and (50). The derived results for  $f_H$  and  $f_L$  are given below,

$$\begin{cases} f_L = \frac{1}{\pi^2 RC} \\ f_H = \frac{KIR}{4P_{FL}} \end{cases}$$

(61)

<

Fig. 2.19. Jitter tolerance mask of a BPLL

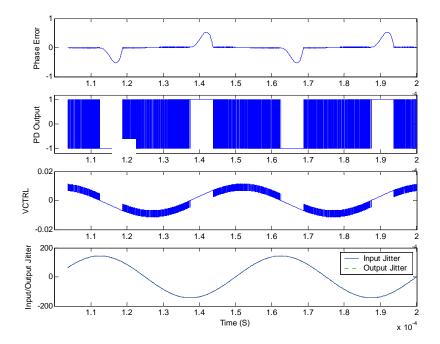

Fig. 2.20. Simulated waveforms of BCDR using an ABPD with 0.02 UI IRJISI

Jitter generation is the output jitter produced by the loop when no input jitter is applied. The jitter generation mainly consists of two parts. The first part is due to JISI caused by the bandwidth limitation of the BPD together with any preceding amplifiers if used. The second part is due to the phase noise of the VCO.

#### II.3.5.1 Jitter Generation Due to JISI

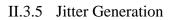

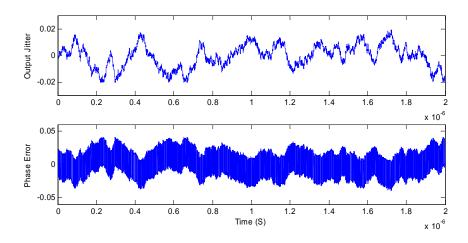

In ultra-high-speed BCDR, jitter generation due to JISI is the most dominant part in the overall jitter generation since most of the VCO phase noise is heavily suppressed by the loop dynamics [7]. JISI is mainly caused by the BPD and its preceding amplifiers. According to the modeling methods previously discussed, the BPD and its preceding amplifiers can be modeled as a jitter-free BPD with additive IRJISI at the input terminal. For simplicity, the IRJISI is modeled as a random binary pulse switching between two levels with equal amplitude and opposite direction. The width of each pulse is equal to 1 UI.

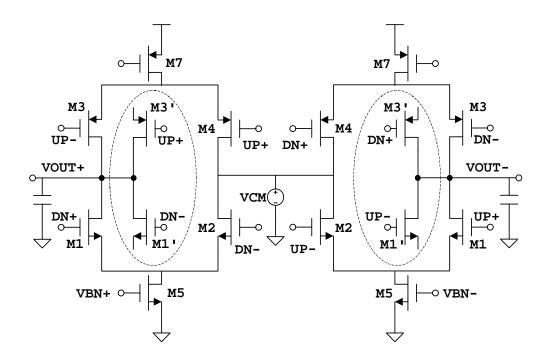

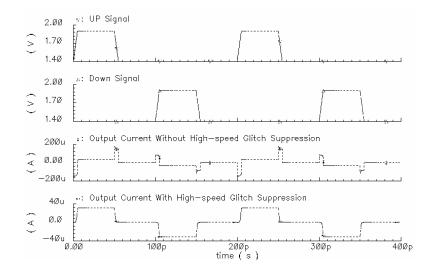

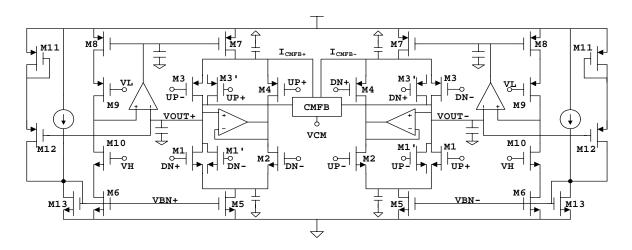

Let us assume that the amplitude of the IRJISI is  $A_I$ . The BCDR was simulated in Matlab using an abrupt-switching BPD (ABPD) with additive IRJISI ( $A_I$ =0.02 UI) applied at the input of the loop. The simulated waveforms are shown in Fig. 2.20. It shows that the output jitter has the same bound as the input jitter, which is [-0.02 UI, 0.02 UI]. That is because the ABPD is not able to discriminate any output phase between [- $A_I$ ,  $A_I$ ] when there is no input jitter other than the IRJISI. Hence, the loop has the same response for any output phase within [- $A_I$ ,  $A_I$ ]. To get more insight, let us assume the current output phase is  $P_0$ . If there is a positive pulse in IRJISI, the overall input phase difference of the BPD is positive as long as  $P_0 < A_I$ . That makes the BPD output a positive pulse. If there is a negative pulse in IRJISI, the phase difference is negative as long as P<sub>0</sub>>-A<sub>I</sub>. That makes the PD output a negative pulse. In other words, a positive pulse and a negative pulse in IRJISI add the same amount of shift (while in opposite direction) to the output phase (ignoring the voltage variations on the capacitor). Thus, the output jitter is simply proportional to the integration of IRJISI as long as the output jitter stays within the interval [-A<sub>I</sub>, A<sub>I</sub>]. Since the IRJISI is modeled as a random binary sequence, its integration can be easily large enough to go beyond the interval. In this case, the output jitter simply drifts with the random drifting of the integration of the IRJISI. When the output jitter goes below the lower boundary, the PD produces only positive pulses regardless of the value of IRJISI, bringing the output phase back within the boundary. The same thing happens when the output jitter goes above the upper boundary. In summary, the output jitter can drift to the boundaries but it is limited within the interval by the loop dynamics. The amplitude of phase error is simply the sum of the amplitude of the output jitter and the IRJISI because the current value of the IRJISI is independent of the current value of the output jitter. Since both the output jitter and the IRJISI are limited within  $[-A_I, A_I]$ , the phase error is limited within  $[-2A_I, 2A_I]$ . That is verified in Fig. 2.20 where the simulated phase error is limited within [-0.04 UI, 0.04 UI].