# MODELING DEFECTIVE PART LEVEL DUE TO STATIC AND DYNAMIC DEFECTS BASED UPON SITE OBSERVATION AND EXCITATION BALANCE

A Dissertation

by

# JENNIFER LYNN DWORAK

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2004

Major Subject: Electrical Engineering

# MODELING DEFECTIVE PART LEVEL DUE TO STATIC AND DYNAMIC DEFECTS BASED UPON SITE OBSERVATION AND EXCITATION BALANCE

A Dissertation

by

# JENNIFER LYNN DWORAK

Submitted to Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

| Approved as to style and content by:  |                                   |

|---------------------------------------|-----------------------------------|

| M. Ray Mercer<br>(Chair of Committee) |                                   |

| Narasimha Reddy<br>(Member)           | Karen Butler-Purry<br>(Member)    |

| Mark Holtzapple<br>(Member)           | Chanan Singh (Head of Department) |

May 2004

Major Subject: Electrical Engineering

# ABSTRACT

Modeling Defective Part Level Due to Static and Dynamic

Defects Based upon Site Observation and Excitation Balance. (May 2004)

Jennifer Lynn Dworak, B.S., Texas A&M University;

M.S., Texas A&M University

Chair of Advisory Committee: Dr. M. Ray Mercer

Manufacture testing of digital integrated circuits is essential for high quality. However, exhaustive testing is impractical, and only a small subset of all possible test patterns (or test pattern pairs) may be applied. Thus, it is crucial to choose a subset that detects a high percentage of the defective parts and produces a low defective part level.

Historically, test pattern generation has often been seen as a deterministic endeavor. Test sets are generated to deterministically ensure that a large percentage of the targeted faults are detected. However, many real defects do not behave like these faults, and a test set that detects them all may still miss many defects. Unfortunately, modeling all possible defects as faults is impractical. Thus, it is important to fortuitously detect unmodeled defects using high quality test sets.

To maximize fortuitous detection, we do not assume a high correlation between faults and actual defects. Instead, we look at the common requirements for all defect detection. We deterministically maximize the observations of the least-observed sites while randomly exciting the defects that may be present. The resulting decrease in defective part level is estimated using the MPG-D model.

This dissertation describes the MPG-D defective part level model and shows how it can be used to predict defective part levels resulting from static defect detection. Unlike many other predictors, its predictions are a function of site observations, not fault coverage, and thus it is generally more accurate at high fault coverages. Furthermore, its components model the physical realities of site observation and defect excitation, and thus it can be used to give insight into better test generation strategies.

Next, we investigate the effect of additional constraints on the fortuitous detection of defects—specifically, as we focus on detecting dynamic defects instead of static ones. We show that the quality of the randomness of excitation becomes increasingly important as defect complexity increases. We introduce a new metric, called excitation balance, to estimate the quality of the excitation, and we show how excitation balance relates to the constant  $\tau$  in the MPG-D model.

To my favorite teachers:

Roger and Dolores Dworak and Ray Mercer

#### ACKNOWLEDGMENTS

There are many people whom I would like to thank for their support and contributions to this work. First, I would like to thank my supervising professor, Dr. Ray Mercer. He is an outstanding teacher and researcher and friend, and I will always be grateful for the chance to learn from him. Because of him, I have learned not only more about testing and logic design, but also how to enjoy giving presentations and how to convey the most important ideas to others at conferences and in the classroom. I have learned that missing a plane will not bring about the end of the world, and most importantly, I have learned how much fun it can be to do research at a university with brilliant people.

I would also like to thank the members of my committee: Dr. A. L. Narasimha Reddy, Dr. Mark Holtzapple, and Dr. Karen Butler-Purry. They were always willing to help, and I appreciate all of their valuable insights and advice.

I am also grateful to Dr. Li Wang for his guidance and suggestions. He is a truly brilliant person, and I always enjoy discussing research with him.

I would also like to thank all of the other graduate students in our group for their help, questions, knowledge, and endless supply of random quotes. I would especially like to thank Professor Michael Grimaila for helping me to get started and for teaching me C. I would like to thank Sooryong Lee for his help with Gulf and with all sorts of data collection. Jimmy Wingfield's help with sByDDer was also invaluable, along with his patience and assistance with all of my bizarre computer problems. I would also like to thank Brad Cobb for always asking insightful questions, sharing his ideas, and listening to mine. These people, along with Justin Ray, Jason VanFickell, Nathan Mickler, Bryan Baer, Jason Wicker, Amy Wang, David Dorsey, Mike Trinka, and Theresa Huth have truly helped my research by giving me a chance to discuss

my ideas and to listen to their own ideas and suggestions. My experience at Texas A&M has been much richer for the chance to interact with them all.

I would also like to thank Carolyn Warzon for being such an efficient and knowledgeable secretary as well as a good friend. She always had the answers to all my questions and helped me in countless ways. I am very grateful for the chance to know her.

I would also like to thank Tammy Carda for all of her help, knowledge, and good advice. The students in the Electrical Engineering department are very lucky to have her.

I would also like to acknowledge the Electrical Engineering department at Texas A&M, including Dr. Singh and Dr. Huang, for their help and support. I am very grateful for the chance to have studied in a department with so many excellent professors and for the financial support that helped to make it possible.

I would also like to acknowledge the National Science Foundation, the Semiconductor Research Corporation (SRC), the Texas Advanced Technology Program, and IBM for their valuable support.

I would also especially like to thank Dr. Ken Butler and Dr. Bret Stewart at Texas Instruments for all of their suggestions and for giving us the opportunity to test our ideas on industrial manufactured circuits. I am also grateful to Dr. Tom Williams for all of his help.

I would also like to thank Dr. Don Ross for being such an excellent teacher for my first class on digital logic. It was because of Dr. Ross's class that I decided that I really wanted to be an electrical engineer, and it was through his recommendation that I came to work in this area under Dr. Mercer.

Finally, I would like to thank my family, especially my parents, my sisters Ruth Ann and Sarah, and my bother David, for all of their help and support. I am especially grateful to my parents for preparing me to meet the challenges of college and life. They have taught me so many things, and I will never be able to express how much their love and confidence in me has always meant and always will.

# TABLE OF CONTENTS

| CHAPTER |                                                                        | Page                       |

|---------|------------------------------------------------------------------------|----------------------------|

| I       | INTRODUCTION                                                           | 1                          |

| II      | TRADITIONAL ATPG AND PREVIOUS WORK                                     | 4                          |

| III     | TEST PATTERN GENERATION: EXCITATION, OBSERVATION, AND DEFECT DETECTION | 10                         |

|         | A. Fault Excitation                                                    | 11                         |

| IV      | EVALUATING TEST SET EFFECTIVENESS                                      | 14                         |

|         | A. Single Stuck-at Fault Coverage                                      | 15<br>17<br>19             |

| V       | THE PROBABILITY OF EXCITATION GIVEN SITE OBSERVATION                   | 24                         |

|         | A. Why Does This Probability Decrease?                                 | 27                         |

| VI      | THE MPG-D DEFECTIVE PART LEVEL MODEL                                   | 34                         |

|         | A. The Disjoint Assumption                                             | 36<br>38<br>43<br>46<br>58 |

| VII     | INCREASING DEFECT COMPLEXITY                                           | 71                         |

| CHAPTER  |                                                                                                                                                                                                                                  | Page         |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|          | <ul> <li>A. The Meaning of Complexity</li> <li>B. Comparison of Static and Dynamic Defects</li> <li>C. ATPG with the Transition Fault Model</li> <li>D. Fortuitous Detection for Static and Dynamic Defects</li> <li></li> </ul> | . 72<br>. 73 |

| VIII     | ANALYSIS OF COMPLEX DEFECT DETECTION                                                                                                                                                                                             | . 87         |

|          | A. Defect Levels for Static and Dynamic Defects B. The Observation Criteria                                                                                                                                                      |              |

| IX       | RANDOMNESS AND EXCITATION BALANCE                                                                                                                                                                                                | . 95         |

|          | A. Excitation Requirements                                                                                                                                                                                                       | . 99         |

| X        | CONCLUSIONS                                                                                                                                                                                                                      | . 115        |

| REFERENC | CES                                                                                                                                                                                                                              | . 120        |

| VITA     |                                                                                                                                                                                                                                  | . 127        |

# LIST OF TABLES

| TABLE |                                                  |  |  |  |      | ] | Page |

|-------|--------------------------------------------------|--|--|--|------|---|------|

|       |                                                  |  |  |  |      |   |      |

| I     | Probability of Excitation for Benchmark Circuits |  |  |  | <br> |   | 33   |

# LIST OF FIGURES

| FIGURI | ${f E}$                                                                   | Page |

|--------|---------------------------------------------------------------------------|------|

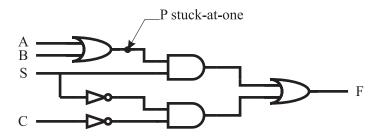

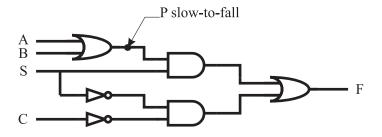

| 1      | Circuit containing site $P$ stuck-at one                                  | 10   |

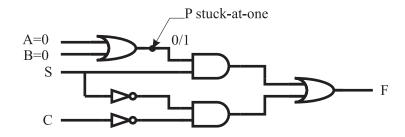

| 2      | Excitation for site $P$ stuck-at one                                      | 11   |

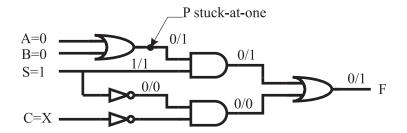

| 3      | Excitation and Observation for site $P$ stuck-at one $\dots$              | 12   |

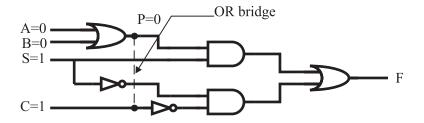

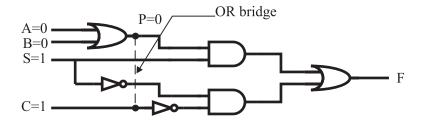

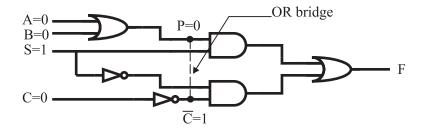

| 4      | Detection for OR bridge between $P$ and $C$                               | 13   |

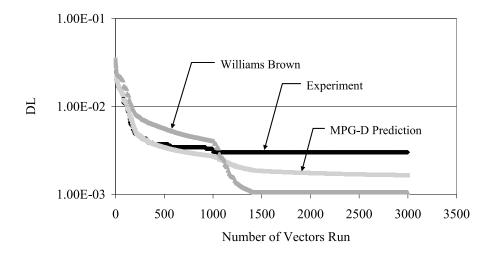

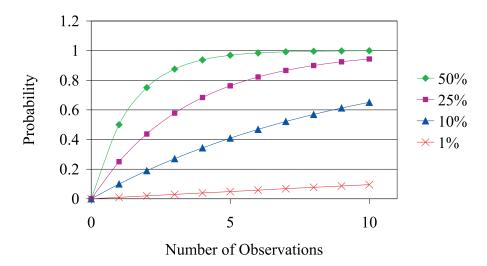

| 5      | Defect level changes as testing progresses                                | 16   |

| 6      | The probability of excitation decreases as testing progresses             | 25   |

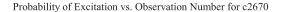

| 7      | Variation in probability of excitation between pattern sets for $c2670$ . | 29   |

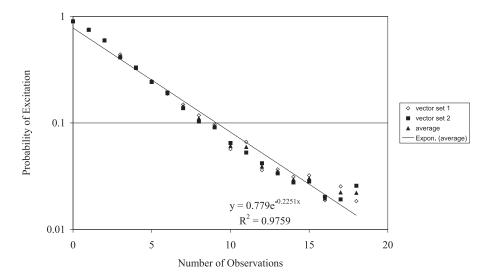

| 8      | Variation in probability of excitation between pattern sets for $c5315$ . | 30   |

| 9      | Probability of excitation curve for c2670                                 | 31   |

| 10     | Probability of excitation curve for c5315                                 | 32   |

| 11     | Statistically independent defect probabilities                            | 35   |

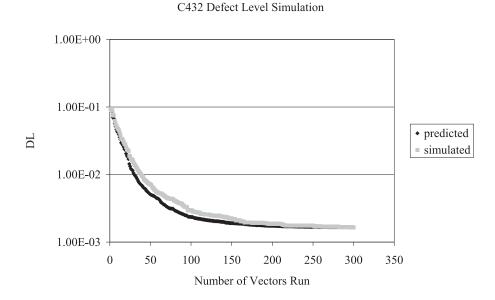

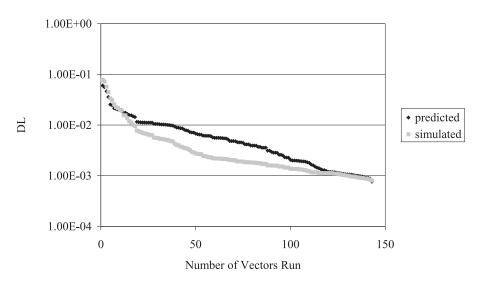

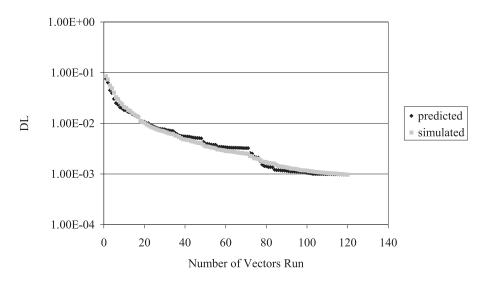

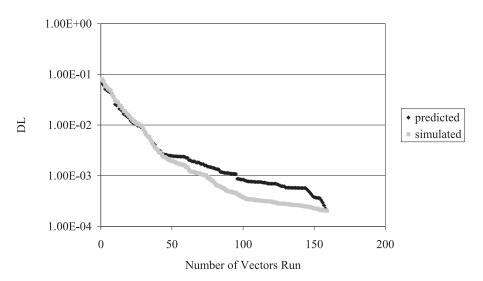

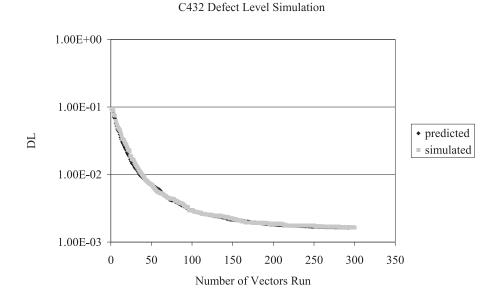

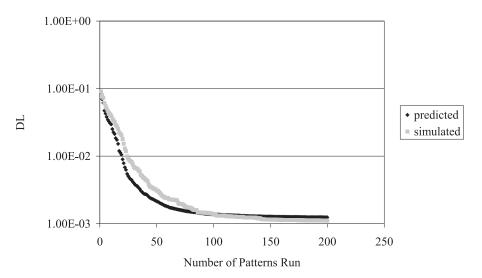

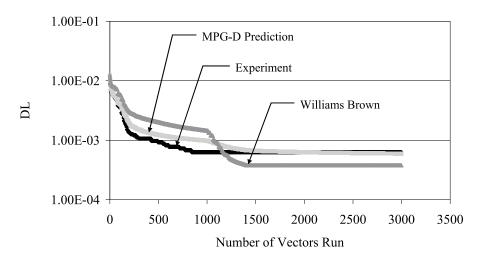

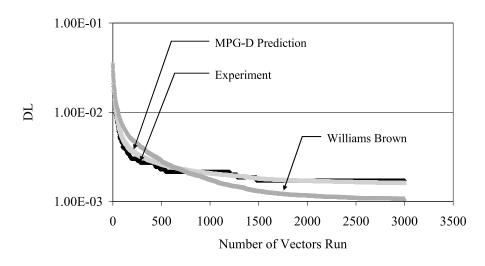

| 12     | C432 MPG-D prediction: $\tau = 4.275~A = 0.663$                           | 39   |

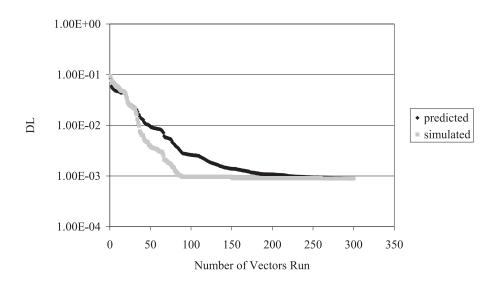

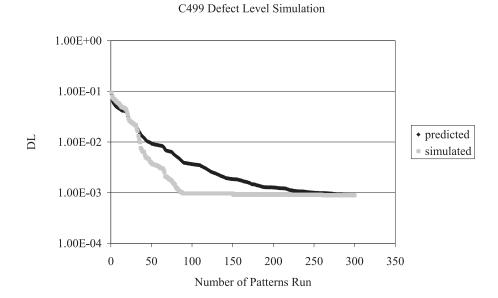

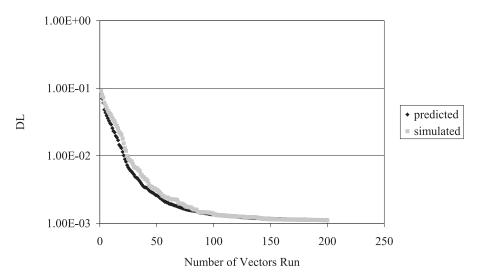

| 13     | C499 MPG-D prediction: $\tau = 7.64 \ A = 0.5011 \ \dots \ \dots \ \dots$ | 40   |

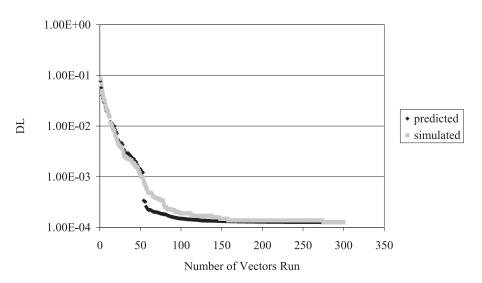

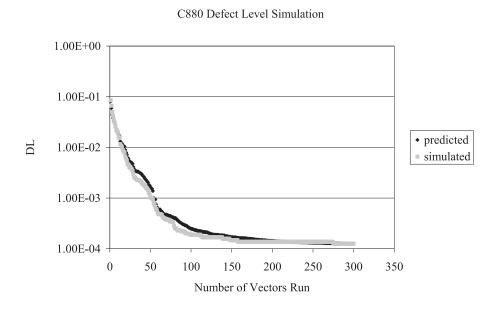

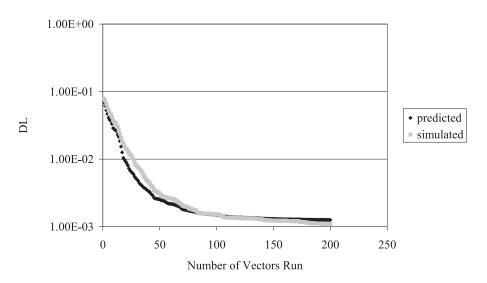

| 14     | C880 MPG-D prediction: $\tau = 3.8212~A = 0.9215~\dots$                   | 40   |

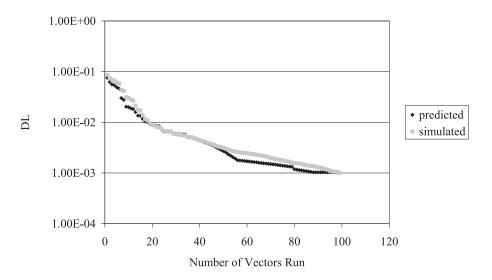

| 15     | C1355 MPG-D prediction: $\tau = 3.582 \ A = 0.821 \ \dots \dots \dots$    | 41   |

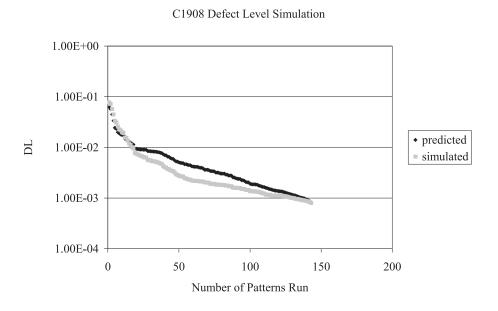

| 16     | C1908 MPG-D prediction: $\tau = 3.4554 \ A = 0.870 \ \dots \dots \dots$   | 41   |

| 17     | C2670 MPG-D prediction: $\tau = 4.4425 \ A = 0.790 \ \dots \dots \dots$   | 42   |

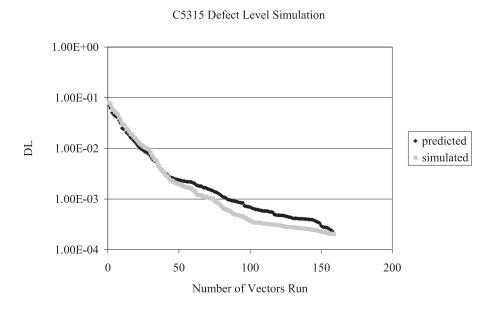

| 18     | C5315 MPG-D prediction: $\tau = 4.036 \ A = 0.905 \ \dots \dots$          | 42   |

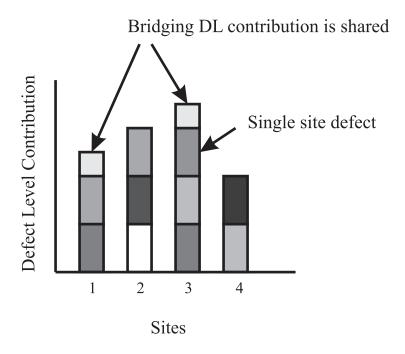

| 19     | Two-sided defects split DL contribution between two sites                 | 44   |

| FIGURI | E                                                                       | Page |

|--------|-------------------------------------------------------------------------|------|

| 20     | C432 MPG-D prediction (equal share): $\tau = 4.28~A = 0.302~C = 1.0~$ . | 49   |

| 21     | C499 MPG-D prediction (equal share): $\tau = 7.64~A = 0.198~C = 1.0~$ . | 50   |

| 22     | C880 MPG-D prediction (equal share): $\tau = 3.82~A = 0.393~C = 1.0~$ . | 50   |

| 23     | C1355 MPG-D prediction (equal share): $\tau = 3.58~A = 0.373~C = 1.0$   | 51   |

| 24     | C1908 MPG-D prediction (equal share): $\tau = 3.46~A = 0.408~C = 1.0$   | 51   |

| 25     | C2670 MPG-D prediction (equal share): $\tau = 4.44~A = 0.343~C = 1.0$   | 52   |

| 26     | C5315 MPG-D prediction (equal share): $\tau = 4.04~A = 0.411~C = 1.0$   | 52   |

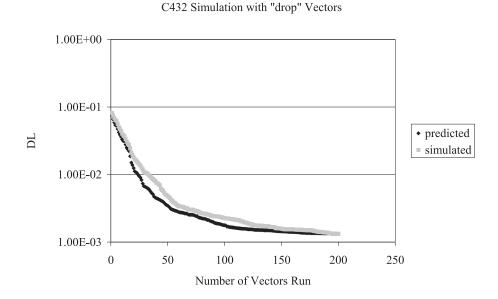

| 27     | "drop" MPG-D prediction (no share): $\tau = 4.28~A = 0.694~\dots$       | 53   |

| 28     | "drop" MPG-D prediction (equal share): $\tau = 4.28~A = 0.331~C = 1.0$  | 54   |

| 29     | "saf" MPG-D prediction (no share): $\tau = 4.28~A = 0.694~\dots$        | 54   |

| 30     | "saf" MPG-D prediction (equal share): $\tau = 4.28~A = 0.331~C = 1.0$ . | 55   |

| 31     | "opt" MPG-D prediction (no share): $\tau = 4.28~A = 0.694~\dots$        | 55   |

| 32     | "opt" MPG-D prediction (equal share): $\tau = 4.28~A = 0.331~C = 1.0$ . | 56   |

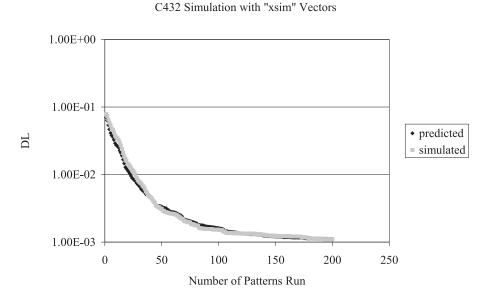

| 33     | "xsim" MPG-D prediction (no share): $\tau = 4.28~A = 0.694~\dots$       | 56   |

| 34     | "xsim" MPG-D prediction (equal share): $\tau = 4.28~A = 0.331~C = 1.0$  | 57   |

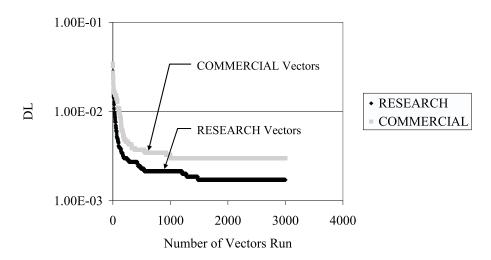

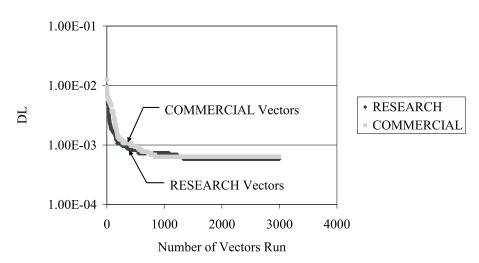

| 35     | Defect levels estimated for October production circuits                 | 63   |

| 36     | Defect levels estimated for February production circuits                | 63   |

| 37     | Defect level predictions for February 1999 research set                 | 65   |

| 38     | Defect level predictions for February 1999 commercial set               | 66   |

| 39     | Defect level predictions for October 1998 research set                  | 66   |

| 40     | Defect level predictions for October 1998 commercial set                | 67   |

| 41     | Circuit containing transition fault                                     | 74   |

| FIGURI | $\Xi$                                                                                 | Page |

|--------|---------------------------------------------------------------------------------------|------|

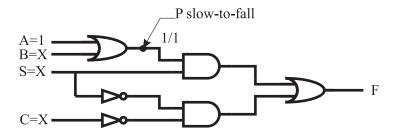

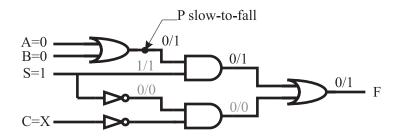

| 42     | ATPG preconditioning pattern for transition fault                                     | 75   |

| 43     | ATPG observation pattern for transition fault                                         | 75   |

| 44     | Test space for static defect detection—single patterns or pairs                       | 77   |

| 45     | Fortuitous detection of other static defects                                          | 78   |

| 46     | Test space for dynamic defect detection                                               | 79   |

| 47     | Fortuitous detection of other dynamic defects                                         | 80   |

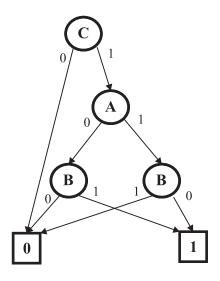

| 48     | OBDD for the function $F = C \bullet (A \oplus B) \dots \dots$                        | 82   |

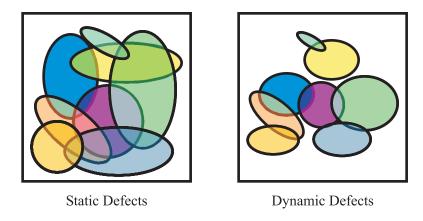

| 49     | Venn diagrams for static and dynamic defects                                          | 83   |

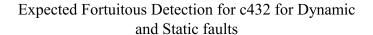

| 50     | Expected fortuitous detection for c432                                                | 85   |

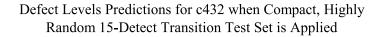

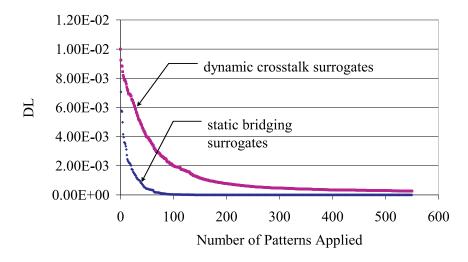

| 51     | Defect levels from static and dynamic surrogate simulation                            | 88   |

| 52     | Defect levels from static and dynamic surrogate simulation—log scale                  | 89   |

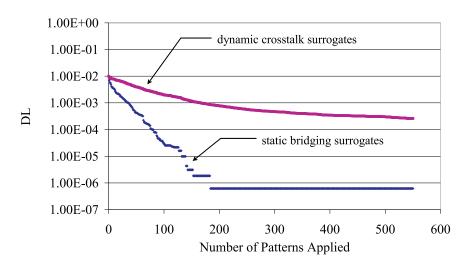

| 53     | Defect levels from OBDD and Greedy ATPG algorithms                                    | 93   |

| 54     | To excite OR bridge for observation at $P$ , set $P$ to zero and $C$ to one           | 96   |

| 55     | To excite OR bridge for observation at $P,$ set $P$ to zero and $\overline{C}$ to one | 96   |

| 56     | Example distribution of ones probabilities when a site is observed $$ . $$ .          | 100  |

| 57     | Ideal distribution of ones probabilities when a site is observed                      | 101  |

| 58     | Comparison of the difficulty in meeting constraints with less balance                 | 102  |

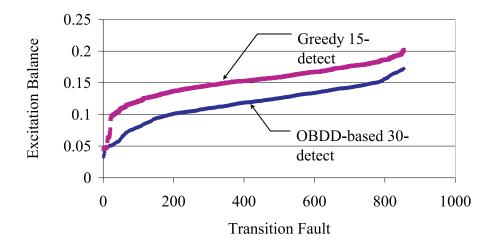

| 59     | Excitation balance for observation patterns of Greedy and sByD-Der test sets          | 104  |

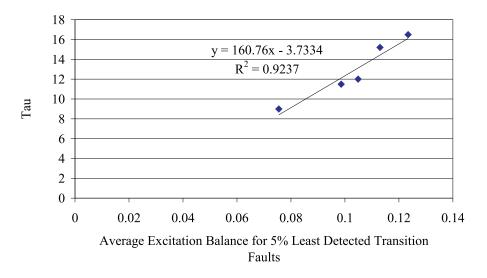

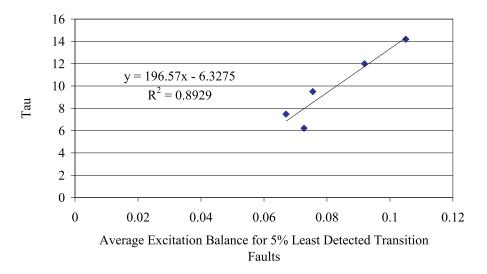

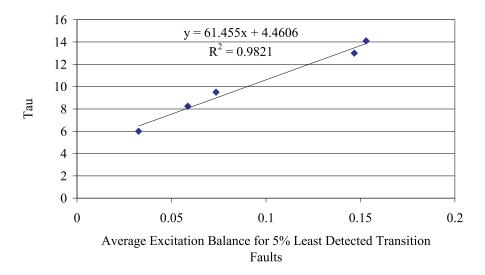

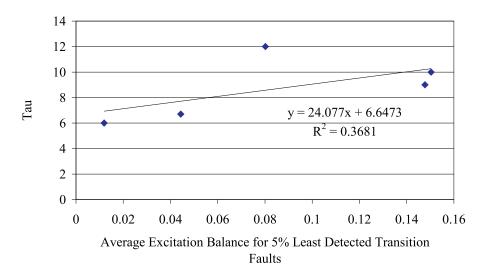

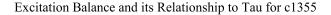

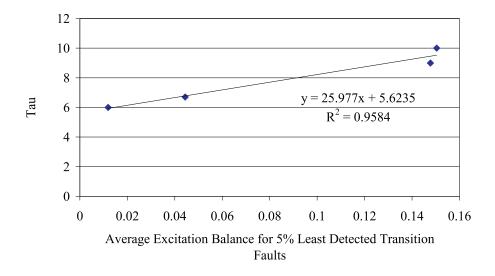

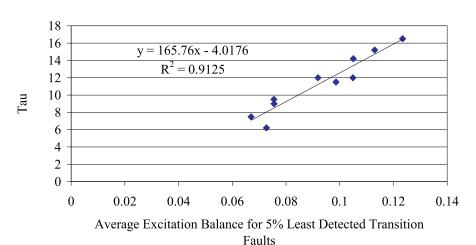

| 60     | $\tau$ depends on excitation balance                                                  | 106  |

| 61     | Excitation balance and $\tau$ for c432                                                | 109  |

| 62     | Excitation balance and $\tau$ for c499                                                | 109  |

| FIGURE |                                                       | Page |

|--------|-------------------------------------------------------|------|

| 63     | Excitation balance and $\tau$ for c1908               | 110  |

| 64     | Excitation balance and $\tau$ for c1355               | 110  |

| 65     | Excitation balance and $\tau$ for c1355, 4 test sets  | 111  |

| 66     | Excitation balance predicts $\tau$ for two circuits   | 112  |

| 67     | Excitation balance predicts $\tau$ for three circuits | 113  |

### CHAPTER I

#### INTRODUCTION

Unfortunately, when digital integrated circuits are manufactured, some (hopefully small) fraction is always defective. To avoid selling these defective circuits to customers, manufacture testing is employed to identify the parts that are defective. Unfortunately, exhaustively testing integrated circuits by applying all possible combinations of logic values to the primary inputs is extremely impractical for modern designs. As a result, testing itself is imperfect, and some defective circuits will almost always escape the testing process. The goal of test pattern generation is to minimize the number of escapes. This number of escapes is quantified by a metric known as defect level, or defective part level. It specifies what fraction of all integrated circuits that pass all applied tests are actually defective. Thus, the primary goal of testing is to obtain as low a defective part level as possible while expending a reasonable amount of testing resources.

Testing has historically been thought of as a very deterministic process because particular defects are modeled in simulation and tests are generated to purposely detect those modeled defects. However, testing is, in reality, very probabilistic. Modeling all defects is impossible, and thus many defects are never modeled at all and must instead be detected *fortuitously*. Effective digital circuit testing will maximize the probability of this fortuitous detection and minimize the defective part level.

Defective part level modeling tries to capture how a particular test pattern set will interact with the circuit design and the defects to predict how many test escapes will occur. When such modeling is based upon properties of the test set and their

The journal model is IEEE Transactions on Automatic Control.

effect on circuit nodes, it can be used to not only predict the defective part level, but also to guide the creation of better automatic test pattern generation (ATPG) algorithms. Thus, there is an inherent direct relationship in which better ATPG algorithms yield lower defective part levels, and better defective part level models yield better ATPG algorithms.

In this research, we have developed a defective part level model named MPG-D, which has been shown to be able to predict defective part levels for both benchmark and industrial circuits. We will describe the underlying basis for the model and show that its components have physical meaning. Thus, it can be used to guide test pattern generation to increase the fortuitous detection of unmodeled defects. We will start with the testing of circuits for static defects and then show how fortuitous detection and test pattern generation must change as we attempt to detect more complex and difficult dynamic defects.

Site observation is a primary indicator of the effectiveness of test pattern generation for simple static defects. However, we will show that the randomness of defect excitation will become more important as defects become more complex and more constraints must be satisfied for their detection. We will introduce a metric to estimate the quality of this excitation called *excitation balance* and will show how it relates to one of the constants in the MPG-D model.

Chapter II will present background for traditional ATPG and how it has evolved to create better test pattern sets. Chapter III will show how the two requirements of fault excitation and site observation are satisfied by a test pattern generated to detect a particular fault. Chapter IV will introduce defective part level modeling. Chapter V will focus on the probability of exciting an undetected defect given site observation and will show how this probability changes as the number of observations increases. Chapter VI will incorporate this analysis into the MPG-D defective part

level model. Successive variations of the model will be explained along with their advantages and disadvantages. Chapters VII and VIII will introduce the changes that must be made to adequately test more complex defects, such as timing defects. Chapter IX will present the concept of excitation balance and will discuss how it can be used to generate better test pattern sets and how it can be incorporated into the MPG-D defective part level model. Finally, Chapter X presents the major conclusions that can be drawn from this research.

## CHAPTER II

### TRADITIONAL ATPG AND PREVIOUS WORK

Digital integrated circuit testing consists of applying logic values to the circuit inputs and then capturing the values that appear at the circuit outputs. When the outputs match the expected values, the circuit has passed that particular test. If the output values do not match those specified by the circuit specification, then the circuit fails the test, and the part is deemed to be defective. (Note: Although many digital circuits are sequential instead of combinational, scan-based sequential designs can be viewed as combinational for testing purposes because elements of the scan chain essentially become circuit inputs and outputs in test mode. The work described in this dissertation is applicable to both combinational circuits and sequential scan designs.)

One of the most obvious ways to begin testing a combinational integrated circuit would be to apply every possible input combination as a test pattern. Unfortunately, the number of possible input combinations grows exponentially with the number of inputs. For example, a circuit with only 50 inputs has  $2^{50}$  (over  $1.1 \times 10^{15}$ ) possible input combinations. Thus, it is impractical to test one of today's integrated circuits by applying all possible input combinations to every chip. Only a very small subset of all possible patterns can be chosen and applied. Thus, it is important to choose a good subset that will detect a significant fraction of all defective parts. Historically, one of the ways of generating such a subset has been to target faults—specifically single stuck-at faults.

A defect is an actual imperfection in a manufactured circuit. In contrast, a fault is a model of a defect that is used to predict how that defect will affect circuit operation. Before testing begins, a set of faults is identified, and tests are generated to deterministically detect them. As the ATPG process progresses, patterns are

produced by targeting each undetected fault in the fault list until all of the faults have been detected at least once or until test generation has failed for all those faults that remain. The mostly widely used fault model is the single stuck-at fault model, which was developed by Eldred in 1959 [1].

In the single stuck-at fault model, each site in the circuit (gate input or gate output) is considered to be potentially "stuck-at-zero" or "stuck-at-one" regardless of the value that should appear at that location based upon the rest of the circuit's logic. For example, a circuit site would behave this way if it were shorted to ground or shorted to power. Thus, the size of the fault list targeted during test pattern generation is at most two times the number of sites in the circuit when single stuck-at faults are used as the targets. This means that in the very worst case the maximum number of test patterns required would be equal to the number of stuck-at faults (two times the number of circuit sites). This is generally much smaller than the number of possible input combinations, but could still be very large in one of today's integrated circuits (which often have hundreds of thousands or millions of sites).

Although test pattern generation using faults is often thought to be a very deterministic process, fortunately, many faults are fortuitously detected by tests generated for other faults. For example, when we generate a test by targeting fault A, we may find that the generated pattern also detects faults B and C, even though we were not specifically trying to detect them with that test pattern. In this example, faults B and C were fortuitously detected because they were detected by a pattern for which another fault (in this case fault A) was the target. Thus, because of fortuitous detection, the number of patterns required to detect all the stuck-at faults is much lower than the number of faults. For example, we worked with a commercial chip at Texas Instruments that contained over 120,000 stuck-at faults. However, all stuck-at faults that were deemed to be detectable were detected with a test set containing only 429

patterns—a reasonable test set size in a commercial environment.

Unfortunately, the single stuck-at fault model does not accurately describe the effects of all possible defects, and as a result, test sets created to detect all stuckat faults at least once may not detect an adequate number of the untargeted defects [2], [3], [4], [5], [6], [7]. In fact, as fault coverages approach 100%, the tests targeted at the remaining stuck-at faults are biased in favor of detecting those faults at the expense of the remaining defects [8], [9], [10]. For example, unintentional shorts between points in the circuit often can be better modeled as bridging faults. Both AND/OR and net-dominating bridging faults have been used to study these unintentional shorts [2],[11],[12],[13]. Unfortunately, the number of bridging faults grows quadratically, instead of linearly, with circuit size. Furthermore, because ATPG and fault simulation are done using gate-level netlists, stuck-at faults that occur within gates may not be detected by test set that detects all stuck-at faults on gate inputs and gate outputs at least once [14]. These defects may be best detected by two-pattern tests (such as those used to detect timing defects). Thus, even a test set with 100% stuck-at fault coverage may not really detect all possible stuck-at faults. In addition, still other defects do not manifest themselves as either stuck-at faults or bridging faults, but require another model.

As a result of the mismatch between stuck-at faults and many of the defects that actually appear in manufactured integrated circuits, different researchers have proposed various testing methods to increase the number of defective integrated circuits detected. For example, [15] used analysis of circuit layouts to find "likely" bridges in interconnects so that the "more likely" bridges could be explicitly targeted and so that the fault list would be of reasonable size. Others have suggested using multiple fault models and implementing several kinds of tests (including stuck-at patterns implemented with scan techniques, functional tests, and IDDQ tests) so that the

different types of tests would catch different types of defects [3]. Furthermore, the authors of [7] suggested using extensive testing and diagnosis of test chips to monitor chip fabrication processes, to create better fault models, and thus to generate better tests. However, it is not possible to model all types of defects or to target all possible fault models. Thus, regardless of the testing strategy applied, much of the research in our group is based upon the premise that, just as faults are fortuitously detected by tests targeted for other faults during test pattern generation, defects may be fortuitously detected by tests that target faults for which there is not an exact match. The question that remains is how to maximize that fortuitous detection.

In [16], a research team investigated and reported the effect of choosing a test to detect a given stuck-at fault during test pattern generation so that either controllability or observability of circuit lines would be maximized. Controllability was used to refer to the ability to place a particular value (such as a zero for AND bridges) on a circuit line while observability was used to refer to propagating the value of a given line to an observable primary output. It was found that while the controllability criteria did not result in improved tests, using observability as a guideline did improve the detection of non-targeted defects. Similarly, [17] also discussed the importance of site observation. Although the sites where either faults or defects occur must be observed at a primary output for the fault or defect to be detected (regardless of the type of error), the excitation criteria of a defect varies depending upon the type of defect. In other words, the common requirement for detecting different types of faults and/or defects is site observations. Thus, it was suggested that increasing the observation of the least detected faults and using random excitation could improve the detection of non-targeted defects in a circuit. These ideas were integrated by our research group at Texas A&M into the DO-RE-ME (Deterministic Observation, Random Excitation, MPG defective part level optimization) method of test pattern generation [18]. This method was used to generate test patterns that detected more defects in a commercial chip than those generated by a standard commercial ATPG tool. For this method, multiple observations, especially observations of the least detected sites, are accomplished deterministically. This is done because of the fact that all defects, regardless of type, must be observed at a primary output in order to be detected, and because the number of constraints that must be satisfied for a circuit site to be observed is often large, and thus observation is often difficult to accomplish by chance.

In contrast, excitation requirements vary from defect to defect and can often be satisfied randomly. For example, bridges generally require that both ends of the bridge be set to opposite values for excitation to occur. If circuit sites do not have highly skewed probabilities of being either zero or one, once a site has been observed several times, the odds of undetected defects never having been simultaneously excited and thus remaining at that site becomes relatively low. In fact, in the experiment described in [4], no escapes (undetected defects) occurred at rated speed when a minimum of 15 detections per fault was guaranteed during testing. Thus, the DO-RE-ME method attempts to randomly excite the undetected and unknown defects that may be present in the integrated circuits while deterministically observing the sites/faults where those defects may occur as many times as possible.

However, the number of test patterns required to obtain 15 observations of every site may be larger than testing time and tester memory requirements allow. Thus, some way of generating a test pattern set with an acceptable number of patterns is necessary. One way to do this is through generating N-detect sets where every site is detected at least N times and N is chosen so that the resulting test set length remains reasonable [19]. However, the true purpose of testing is to reduce the defective part level, and it is possible for tradeoffs to exist between, for example, observing one site

for the second time and observing 30 sites for the third time. Thus, a defective part level predictor which can allow test sets to be compared based upon defect levels instead of merely the number of detections of the least detected faults can be used to extract optimal (or near optimal) subsets of reasonable length from a superset of test patterns that contains too many patterns to be applied in its entirety.

# CHAPTER III

# TEST PATTERN GENERATION: EXCITATION, OBSERVATION, AND DEFECT DETECTION

Test patterns are generated by targeting faults. In most cases, at least when static defects are to be detected, stuck-at faults are used as the targets. Thus, test patterns are generated to specifically detect circuit sites that are either "stuck-at one" or "stuck-at zero." However, regardless of the fault or defect being detected, two conditions must be satisfied for that detection to occur: fault/defect excitation and site observation. This chapter will demonstrate in more detail what we mean by excitation and observation and will show how these requirements can be satisfied by a test pattern.

#### A. Fault Excitation

Consider the circuit in Fig. 1. This figure contains a modified multiplexer circuit with a single fault: point P is stuck-at a logic one. In order to excite this fault, a test pattern must create a difference in the logic value at point P between the fault-free and faulty circuits. Thus, the test pattern must set P to a logic zero in the good circuit by setting both A and B to a logic zero as shown in Fig. 2. The values in

Fig. 1. Circuit containing site P stuck-at one

Fig. 2. Excitation for site P stuck-at one

both the good and faulty circuits are shown at point P. The first value is the value in the good circuit while the value after the slash is the value in the faulty circuit. Thus, it is apparent that these two assignments to the primary inputs A and B have successfully excited the fault.

# B. Fault Observation

Unfortunately, while fault excitation is necessary for fault detection, it is not sufficient. Because a tester only has access to certain circuit points (primary outputs and elements of the scan chain), merely causing a difference in logic value at the location of the defect does not guarantee detection. We need to propagate the value at that site to a primary output (or scan chain element) so that the value at that site will determine the value at the output. This is called site observation.

To observe site P at primary output F, we need to first propagate the value at point P through the AND gate. This can be accomplished by setting S to a logic one as shown in Fig. 3. Because the S input to the AND gate is set to a non-controlling value, the other input value will determine the output value. Thus the difference in logic value is propagated through the AND gate. Furthermore, setting S equal to a logic one also automatically sets the second input to the final OR gate to a logic zero in both the good and faulty circuits. Thus, the difference in logic value propagates

Fig. 3. Excitation and Observation for site P stuck-at one

through this OR gate as well and is visible at primary output F. Therefore, by setting S to a logic one, we were able to fulfill all of the observation requirements for this fault.

At this point, because we have both excited the fault and observed the site where the error occurs at a primary output, we have managed to detect the fault. Notice that input C did not have to be assigned and is actually a "don't care." Thus, what we have actually generated is a partial pattern. There are actually two patterns that will detect this fault equally well—one in which C is equal to zero and one in which C is equal to one. Historically, C will be given a randomly assigned value, and only one of the two patterns will actually be applied to the circuit under test.

## C. Fortuitous Detection of Unmodeled Defects

Unfortunately, there is no guarantee that the defect that actually occurs in this integrated circuit will be a stuck-at fault. For example, the actual defect could very well be a bridge. However, if stuck-at faults were used as the targets during test pattern generation, the only way to detect a bridge is by fortuitously meeting its detection requirements. For example, consider the OR bridge in Fig. 4.

An OR bridge is an unintentional short between two circuit sites. If either of the sites is set equal to a logic one, the other side of the bridge will also be forced to a

Fig. 4. Detection for OR bridge between P and C

logic one. Thus, a difference in logic value occurs when the two sides of the bridge are set to opposite values in a non-defective circuit. This will satisfy the excitation requirement. Furthermore the side of the bridge set to an incorrect logic value will need to be observed for detection to occur.

Thus, if we are lucky, we may detect this fault with the test generated for P stuck-at one. Site P is already being observed by the test pattern. Furthermore, site P is equal to a logic zero in the nondefective circuit. Thus, it has the potential of being forced to a logic one in the defective circuit. Whether or not this actually occurs depends on the value chosen for C. If we were lucky, and C happened to be chosen to be a logic one, then the defect will be excited and detected.

Unfortunately, there is no guarantee that whatever requirements must be satisfied to detect an unknown defect will satisfied by a test pattern targeted toward a different fault. However, the site where the error occurs must be observed for detection to occur regardless of what fault or defect is being detected. The excitation requirements are the constraints that generally differ among the defects or faults that may occur at a circuit site. However, every time a site is observed with a different pattern, the probability of a defect remaining undetected decreases. Thus, the DO-RE-ME method deterministically maximizes the observation of the least observed sites while randomly exciting whatever defects may occur there. In this way, more unmodeled defects can be fortuitously detected.

## CHAPTER IV

### EVALUATING TEST SET EFFECTIVENESS

Establishing figures of merit to quantify the effectiveness of test pattern sets is essential to the testing process. Improvements to ATPG algorithms cannot be made if there is no standard by which to judge a test pattern set. However, even more importantly, such figures of merit are needed to evaluate whether a given test pattern set is adequate and has the capability of detecting a sufficient percentage of all defective integrated circuits. Historically, two important figures of merit for evaluating test set quality have been the single stuck-at fault coverage (evaluated using fault simulation) and the defective part level, or defect level, (the exact value of which is difficult or impossible to determine).

# A. Single Stuck-at Fault Coverage

Because test patterns have traditionally been generated by targeting single stuck-at faults, one of the easiest and most widely used figures of merit has historically been the single stuck-at fault coverage. The stuck-at fault coverage is equal to the percentage of the single stuck-at faults that are actually detected by a given test pattern set out of all of those faults that potentially could have been detected. Specifically, the single stuck-at fault coverage is generally calculated according to the following formula:

$$Fault\ coverage = \frac{\#\ of\ detected\ faults}{\#\ of\ detectable\ faults}$$

(4.1)

Although there may be a few difficulties in determining the exact value of single stuck-at fault coverage—specifically there is often a question of whether undetected faults are actually redundant (and therefore undetectable) or merely have not been detected by this particular test pattern set—in general this calculation is considered

to be relatively straightforward. If an undetected fault is truly redundant, then the fact that it is not detected by a given test pattern set should not lower the fault coverage. Unfortunately, in many cases, proving that a fault is actually undetectable is computationally very expensive, and thus it is unknown whether the nondetection is truly problematic or not. However, once an assumption has been made with respect to whether a given fault is actually detectable, it is easy to compute single stuck-at fault coverage under that assumption given the results of fault simulation.

## B. Defective Part Level

Unfortunately, single stuck-at fault coverage only measures the coverage of the stuck-at faults targeted during test pattern generation. A much more important figure of merit is the defect level, or defective part level. (The defect level is given as a fraction while the defective part level is given as the number of defective parts per million. Thus, the defective part level can be obtained from the defect level by multiplying by 10<sup>6</sup>.) Unlike fault coverage—which is essentially a measure of how well an ATPG algorithm is able to detect faults—defect level is ideally a measure of how well a test set detects actual manufacturing defects. Specifically, it is a measure of how many parts escape the testing process by passing all of the tests in a test pattern set even though those parts are defective (and could have been shown defective by some test pattern not included in the applied test set.) Thus, ideally, defect level calculations will effectively predict the detection rate of unmodeled defects that are not specifically targeted in the ATPG process.

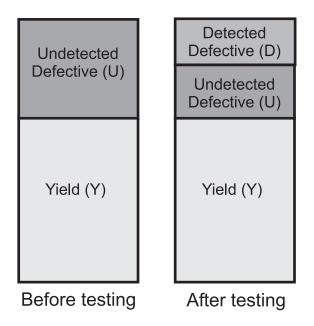

The boxes in Fig. 5 represent the ensemble of all integrated circuits under consideration. Before a test pattern set is applied, all of the integrated circuits belong to one of two categories: the yield or the undetected defective parts. The yield is

Fig. 5. Defect level changes as testing progresses

the fraction of all parts that are actually non-defective. The rest of the parts are defective. Because no test patterns have been applied yet, all of the defective parts are undetected. This situation is represented by the box on the left. However, once a set of test patterns have been applied, some of the defective parts fail at least one of the tests and show themselves to be defective. There are now three categories of parts: the yield, the undetected defective parts, and the detected defective parts. This situation is represented by the box on the right. If each of these categories is represented as the appropriate fraction of the whole (U + D + Y = 1.0), we can calculate the defect level according to Equation 4.2.

$$DL = \frac{U}{Y + U} \tag{4.2}$$

Thus, the defect level is merely equal to the probability that a part that passes all of the tests is still defective.

### 1. Previous Defect Level Models

Historically, several models have been developed to estimate the defect level. The most famous and widely used of these models is the Williams Brown model [20] shown in equation 4.3.

$$DL = 1 - Y^{1-DC} (4.3)$$

This model estimates defect levels as a function of the yield (Y) and the defect coverage (DC) and assumes statistical independence among the occurrences of different defects. However, the defect coverage is always unknown, and most people have traditionally used the single stuck-at fault coverage as the defect coverage. In that case, when 100% fault coverage is reached, the Williams Brown model predicts a defect level of zero.

The Williams Brown model and several other defect level models were analyzed and compared in [21]. However, most of these models predict defect level as a function of fault coverage. One of these predictors was proposed by Vishwani D. Agrawal, Sharad C. Seth, and Prathima Agrawal. They proposed a model that predicted DL as a function of the yield, fault coverage, and the average number of defects on a chip [22]. The value of the average number of defects must be experimentally determined for this model. A subsequent version [23] by Agrawal and Seth refined this model, but still depended upon fault coverage. Finally, a different model by R. L. Wadsack calculates defect level only as a function of the fault coverage and the yield [24].

Unfortunately, there is a significant disadvantage to using fault coverage in defective part level modeling—especially if fault coverage is assumed to be equal to the defect coverage. This is often a very optimistic assumption because defect coverage and fault coverage tend to become less correlated as fault coverages become very high. This lack of correlation is due to the mismatch between the modeled faults and the

actual defects on the chips. In fact, as fault coverages approach 100%, the standard deviation of the defect coverages of the test sets increases—making fault coverage an inaccurate metric for predicting defect coverage and defect level [25]. Furthermore, test pattern sets with identical fault coverages may have very different defect coverages and thus produce very different defective part levels [16],[25],[26]. Specifically, using targeted fault coverage as an estimate of the defect coverage does not take into account the fact that while the fortuitous detection of unmodeled defects is possible with tests generated for specific faults, such fortuitous detection is not guaranteed. Furthermore, even if a defect level model that uses fault coverage doesn't go to zero at 100% fault coverage, there is generally no way to analyze test sets that surpass 100% fault coverage—even though these longer test sets may detect additional defects. Thus, what is really necessary is a defect level model which does not depend exclusively upon fault coverages.

Another model was described by [21] and published in [27]. This model predicts defect level in terms of the number of patterns applied, the total number of vectors, and the number of chips failing at each vector. While this model does not depend upon fault coverage, it requires fallout data to determine the outcome of the calculations. However, most importantly, it gives no guidance with respect to how test pattern sets can be improved or optimized to detect more defects. A more complicated model that does not depend on fault coverage was published in [28]. It also predicts defect level as a function of the number of chips tested, the number that fail at each vector, the total number of vectors, the yield, and the estimated yield after n vectors have been applied. Also, like the other model, it relies on fallout data to produce its calculations, and it does not give any indication of how automatic test pattern generation techniques could be improved.

Another relatively recent model was presented by Jose T. Sousa and Vishwani D.

Agrawal in [29]. This model attempts to incorporate defect clustering into its analysis. However, one of the stated assumptions of the work is that the defect coverage equals 100% when the fault coverage equals 100%. Thus, the authors suggest that if this assumption proves inadequate, then better fault models should be used. A different recent defect level model was proposed by Li-C. Wang and his co-authors in [30].

Another recent metric was presented in [31]. In this case, test sets were evaluated based upon a predicted "Bridging Coverage Estimator." Here, defects are assumed to behave as bridges and the values at circuit sites are assumed to be uncorrelated with a 50% chance of being a one or a zero. Changes in BCE are used to estimate changes in defect level.

Ultimately, an ideal defect level model will not be based on simple fault coverage. An alternative to simple fault coverage is necessary to guide predictions of the amount of fortuitous detections of non-targeted defects and therefore the reduction in defect level, especially for test sets with very high fault coverages. Furthermore, an ideal model would be able to guide the ATPG process to generate better test pattern sets. For example, we would like to be able to choose good subsets of test patterns from supersets. Even more importantly, we would like to generate even better supersets by creating test patterns that maximize the fortuitous detection of unmodeled defects.

### 2. The MPG Defective Part Level Model

Because fault coverage cannot accurately predict defect coverage when fault coverages become very high, an alternative indicator for analyzing the effectiveness of a test pattern set and estimating the resulting defect level is necessary. Ideally, the components of such a model will represent some physical reality so that it can also provide direction for improving test pattern generation strategies. For this we will need an analysis of the detection requirements for not only stuck-at faults, but for the detec-

tion of the actual (often unmodeled) defects that are actually present in a given set of integrated circuits. Recall that two conditions must be satisfied for the detection of any fault or defect, regardless of the type of fault or defect that is actually occurring. First, a difference in logic value between the defective and non-defective circuits must be present at the defect location in the circuit. This is called fault/defect excitation. However, because this difference between the defective and non-defective circuits at an interior site cannot be detected by a tester, the difference in logic value at that site must be propagated to an observation point—either a primary output of the circuit or a flip-flop in the scan chain. This is called site observation. Thus, when the fault or defect is excited at the same time that the site where the difference in logic value occurs is observed, the fault or defect is detected by the test pattern. Because these two requirements must be met for fault detection, both should be included in any defect level model whose components have physical meaning in the process of defect detection. Our first model which accomplished this was named MPG in honor of its creators: M. Ray Mercer, Jaehong Park, and Michael Grimaila [18].

MPG is a significant improvement over fault coverage based defect level models because it doesn't require a close match between the modeled faults and the actual defects present in an integrated circuit. Instead, it uses the logic underlying the DO-RE-ME test pattern generation method and predicts the defect level based upon the number of times circuit sites have been observed. The equations for this model are shown below:

$$DL = 1 - \prod_{i=1}^{\# of sites} [1 - (1 - P_{excite})^{\# obs_i} P_{defect}]$$

(4.4)

$$P_{defect} = 1 - Yield^{1/\# of sites} (4.5)$$

Like the Williams Brown model, the MPG model assumes statistical independence for the occurrence of defects at different sites. Furthermore, it assumes that every site has an equal chance of containing a defect, and thus the probability of a defect occurring is uniform across all sites. Specifically,  $P_{defect}$  is the probability of the occurrence of a defect at a given site and is calculated from the yield according to Equation 4.5.  $P_{excite}$  is the probability of exciting a defect given that the site is observed, and  $\#obs_i$  is the number of times site i has been observed. Thus, as a site is observed more times, the probability that an undetected defect remains at that site  $((1 - P_{excite})^{\#obs_i}P_{defect})$  becomes dramatically smaller. This matches the reasoning underlying DO-RE-ME in which maximizing the number of observations of all sites—particularly those which would otherwise be observed the least—minimizes the number of defects that are missed during testing. However, most importantly, unlike the Williams Brown model, the defect level predicted using the MPG equation is not a direct function of fault coverage and does not go to zero when the fault coverage reaches 100%.

The MPG defect level estimator is an improvement over models based upon simple stuck-at fault coverage because it is based upon the requirements for the detection of all defects—both targeted and untargeted—and thus is capable of estimating non-target defect detection. Furthermore, each of its components (Yield,  $P_{defect}$ ,  $P_{excite}$ , #obs<sub>i</sub>, etc.) has physical meaning, and thus this model provides an intuitive understanding how different characteristics of the circuit, the defects, and the test pattern set interact to produce the final defective part level.

#### 3. MPG-1

One assumption made when calculating defect levels with the MPG model is that the probability of defect excitation given site observation is constant and uniform across circuit sites. However, this probability may vary dramatically from one defect to another. It is a function of the number of constraints that must be satisfied to excite

the defect and the difficulty in satisfying those constraints given site observation. For example, when the probability of exciting a bridging defect is compared with the probability of exciting a corresponding stuck-at fault, the probability of exciting the bridging defect is lower. While one constraint must be satisfied to excite a stuck-at fault (the site where the stuck at fault occurs must be set to a logic one in the case of a stuck-at-zero fault or a logic zero in the case of a stuck-at-one fault) an additional constraint must be satisfied for the excitation of a bridging fault. In that case, the additional constraint involves setting the other end of the bridge to a specific logic value. (What logic value is required depends upon the type of bridge and the logic value already present at the observed end of the bridge.) Depending upon which site is involved and its relative likelihood of being set to a logic one or a logic zero, this additional constraint could be very difficult or very simple to satisfy. Thus, there is a significant range of excitation probabilities for defects.

Furthermore, there is no guarantee that the defect present at a circuit site in one chip will be identical to the defects present at that site for all chips containing a defect there. In other words, a circuit site that is defective in a particular integrated circuit could be defective due to any of a large number of potential defects—each of which have their own excitation and detection probabilities. Thus, it is important to recognize the fact that the defective part level could decrease due to the detection of a defect at a given site in a single integrated circuit, but another (possibly more difficult-to-detect defect) could still be present at that site in a different integrated circuit. Taking this type of information into account led to the development of MPG-1 [32].

MPG-1 is very similar to the MPG model, but the calculation becomes iterative and the parameters change as each test pattern is applied. Specifically, after each test pattern is applied, the probability of an *undetected* defect still being present is now lower, and the probability of exciting an *undetected* defect at a site given that the site is observed is modeled as a decaying exponential function of the number of observations:

$$P_{excite} = \alpha e^{-\frac{\#obs_i}{\tau}} \tag{4.6}$$

In this case, the constant  $\alpha$  was chosen to be 1 for simplicity, and the constant  $\tau$  was chosen to best fit the empirical data. When the right value is chosen for  $\tau$ , this model provides a good match for the industrial and benchmark circuit defect level data.

### CHAPTER V

### THE PROBABILITY OF EXCITATION GIVEN SITE OBSERVATION

One of the characteristics of the MPG-1 model that distinguishes it from the original MPG model is its use of a varying probability of excitation as the number of site observations increases. Specifically, the MPG-1 model is concerned with the probability of exciting at least one *undetected* defect given a site observation.

### A. Why Does This Probability Decrease?

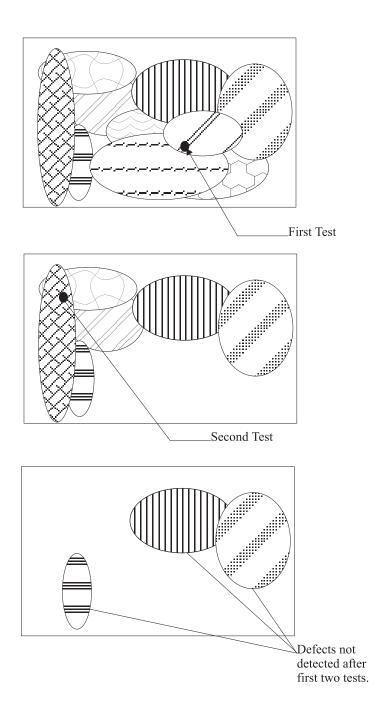

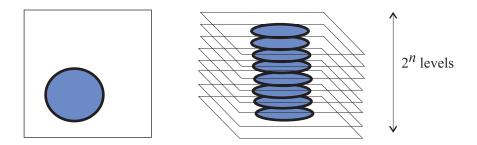

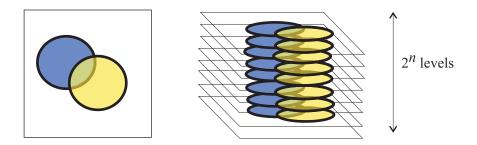

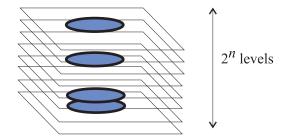

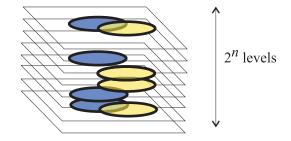

Intuitively, the probability of exciting an undetected defect at a site (given that the site is observed) should decrease as the site is observed more times. Consider Fig. 6. This figure shows the change in the test spaces for defect detection at a site as more test patterns that observe that site are applied. Let each of the boxes contain the set of all test patterns that will observe the site in question. Furthermore, within each of these boxes is a set of ovals corresponding to the set of all possible tests for defects at this site. Let each of the ovals contain those test patterns which will excite the corresponding defect given that the site is observed. Thus, if we happen to choose a test pattern that falls within one of the ovals, we will excite the defect and simultaneously observe the site where it occurs—detecting that defect. Large ovals correspond to defects that are easy to excite and detect while small ovals correspond to defects that are difficult to excite.

Before any test patterns are applied, there are many undetected defects, and a majority of the test patterns that can observe this site will successfully excite and detect at least one undetected defect. This is illustrated in the first box. There is also a significant amount of overlap among the test spaces that will excite different defects—especially among those defects that are easy to excite. Thus, with the ap-

Fig. 6. The probability of excitation decreases as testing progresses

plication of the first test pattern that observes this site, we are likely to fortuitously detect many previously undetected defects.

Once a test pattern is applied, many of the easy defects will likely be fortuitously detected. The detected defects disappear from the Venn diagram in the second box because detecting those defects again will not further reduce the defective part level. There are now many more test patterns that will observe this site but will not excite any new defects. Thus, the second time the site is observed, the probability of exciting an undetected defect with that observation is lower.

When the second test pattern that observes this site is applied, any additional defects fortuitously detected by that pattern will also disappear from the Venn diagram, and the probability of exciting at least one remaining defect becomes even lower. Thus, the probability of exciting an undetected defect at a site given that the site is observed must be a monotonically decreasing function. It can never increase for the manufacturing defects present at the end of production, and as additional test patterns that observe a site are applied, this probability tends to decrease until all but the most difficult to detect defects remain undetected.

In [32] we assumed that the probability of excitation given site observation would decrease as a decaying exponential with a time constant  $\tau$ . This monotonically decreasing function was chosen based upon the fact that, intuitively, it seems that the initial observations of a site should fortuitously detect many "easy" defects—causing significant reductions in this excitation probability—while subsequent observations should have a less dramatic impact because the probability of excitation would already be quite low. Using this decaying exponential equation for the probability of excitation gave good results in the MPG-1 model, but it was only later that we completed additional experiments to find the exact nature of this probability [33], [34].

### B. Surrogate Simulation

To investigate the fortuitous detection of unknown defects using gate-level circuit simulation, it is important to find a way of representing the untargeted and unmodeled defects. This is done through the simulation of surrogates—defect models that are not targeted during test pattern generation. For example, during ATPG, test patterns are usually generated by targeting single stuck-at faults. Thus, the detection of those stuck-at faults that were targeted and simulated during the ATPG process is guaranteed and cannot be used to give us adequate estimates of the fortuitous detection of unmodeled defects. On the other hand, the detection of other fault models (such as bridges) is not guaranteed by the ATPG process because the detection requirements of bridges and stuck-at faults differ. Thus, we can use the fortuitous detection of bridging surrogates as an indicator of the fortuitous detection of arbritrary unmodeled defects. Therefore, the primary requirement for a choice of surrogate is that its detection requirements differ from the requirements for detecting the targeted faults so that fortuity can be adequately represented. For the following experiments, AND and OR bridges were used as surrogates.

### C. Experimental Setup

Data were collected for several benchmark circuits: c432, c499, c880, c1355, c1908, and c5315 [35]. (In each case the number in the circuit name refers to the number of sites where a stuck-at fault could potentially occur. Thus, c432 contains 432 such sites and 864 possible stuck-at faults.) These benchmark circuits were analyzed using computer simulation. (None of the circuits were physically manufactured for this research.) For each circuit, the circuit schematic was read by an Automatic Test Pattern Generation (ATPG) computer program that both generates test patterns for

a target fault set and contains a fault simulator. The program we used is a version of Atalanta [36]. It was modified by Sooryong Lee for this project and other related research. The program creates a fault list containing all single stuck-at faults in the circuit and generates a test set to detect those faults. (The maximum number of test patterns generated for any circuit during these experiments was 300.) The program also allows information to be obtained about the detection of the surrogates (in this case bridges) which we specify and which are used to estimate the rate of non-target defect detection when the generated test patterns are applied.

To find the probability of excitation given that a site is observed, we applied test patterns targeted for stuck-at faults to each of the seven benchmark circuits and performed surrogate simulation to obtain data on non-target defect detection for each site as it was observed. Data were collected so that a count was kept of the total number of sites that were observed once, twice, three times, etc. and how many of those sites detected a surrogate when they were observed the first time, second time, third time, fourth time, etc. Then, the probability of surrogate excitation could be calculated by dividing these two numbers. For example, if 100 sites were observed at least once and 99 of those sites had at least one surrogate detected the first time they were observed, then the probability of exciting at least one undetected defect given that the site was observed once is 0.99. These data were then graphed to show how the probability of excitation given that a site is observed changes as the number of observations increases.

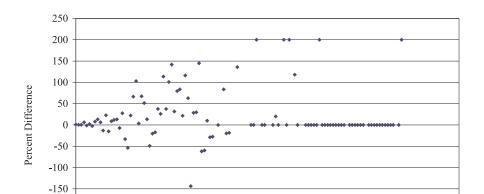

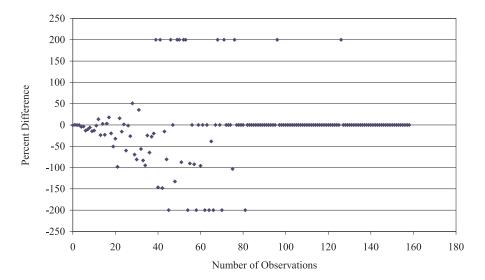

Although the circuit simulation and probability of excitation analysis were performed for seven different circuits, the data from only two circuits will be shown here because the results are so similar. These circuit simulations were run with two different pattern sets (both targeted for stuck-at faults) so that the effect of different patterns could be observed. The percent difference was calculated for the probability

-200 -250 0

20

40

Percent Difference vs. Observation Number for c2670

Fig. 7. Variation in probability of excitation between pattern sets for c2670

60

Number of Observations

80

100

120

140

of excitation results from the two test sets at each observation number. The graphed results are shown in Figs. 7 and 8. For the first few times a point in the circuit is observed, there is considerable agreement between the two pattern sets for the average probability of excitation. However, as the number of observations increases, the behavior of the probability of excitation becomes more chaotic, and there is a large difference between the data for the different pattern sets. This result is probably a quantization effect. This quantization has two probable sources—a decrease in the number of sites included in each sample, and the fragmentation of the actual test space being measured.

As the number of observations increases, the probability of excitation becomes very low and fewer circuit sites have been observed the appropriate number of times to contribute to the sample. It is reasonable to expect that as the sample size decreases, the variance of the sample set will increase. Furthermore, once a circuit site

Fig. 8. Variation in probability of excitation between pattern sets for c5315

has been observed multiple times, the number of defects remaining is significantly lower, and thus the space available to excite a defect is significantly reduced and fragmented. Many test pattern sets will excite no defects for a given observation number because they do not fortuitously hit the appropriate sections of the test space for any surrogate. This result actually occurred for both test sets, and the points that show a percent difference of zero after many observations are actually due to the fact that neither test set detected an undetected defect at any site for that number of observations. However, at other times, a test pattern will be lucky and manage to hit one of the few remaining areas that allow a defect to be excited while being observed. This occurrence obviously depends upon which test pattern is being applied, which patterns have already been applied, and what defects remain. Thus, the uncertainty and unpredictability increase drastically as the probability of excitation becomes smaller when the measurement is taken in this fashion.

Fig. 9. Probability of excitation curve for c2670

However, it is appropriate to focus on the beginning of the curve because after a site has been observed many times, its contribution to the defective part level becomes miniscule because so few defects are left. The value of the defective part level is dominated by the sites which have been observed less frequently. Thus, when we plotted the probability of excitation curves to find the appropriate values of  $\tau$ , we focused on the beginning of the curve where the percent difference was reasonable (under 100%) and used the average value of the probability of excitation to predict the best value of  $\tau$ .

The probability of excitation curves for two of the seven circuits studied can be seen in Figs. 9 and 10. Both of these curves are plotted on a logarithmic scale. Thus, the fact that the data fit a straight line indicates that the shape of the curve is exponential in nature. The  $R^2$  values are both very close to one, indicating a good fit between the data and the best-fit exponential curve. Thus, our hypothesis stated in

### Probability of Excitation vs. Observation Number for c5315

Fig. 10. Probability of excitation curve for c5315

number of observations

[32] was correct, and the probability of exciting an as yet undetected defect given that the site is observed does indeed decrease exponentially as the number of observations increases. The values of  $\tau$  for all seven simulated circuits can be found in Table I.

Table I. Probability of Excitation for Benchmark Circuits

| circuit | au     |

|---------|--------|

| c432    | 4.275  |

| c499    | 7.64   |

| c880    | 3.8212 |

| c1355   | 3.582  |

| c1908   | 3.4554 |

| c2670   | 4.4425 |

| c5315   | 4.036  |

### CHAPTER VI

### THE MPG-D DEFECTIVE PART LEVEL MODEL

Like the Williams Brown model, MPG, and MPG-1 assume statistical independence among the occurrences of defects at different circuit sites. However, we have discovered that in many cases defect level predictions can be made more quickly and accurately if a disjoint probability assumption is made instead. We have used that assumption to create a new defect level model, MPG-D [33], [37].

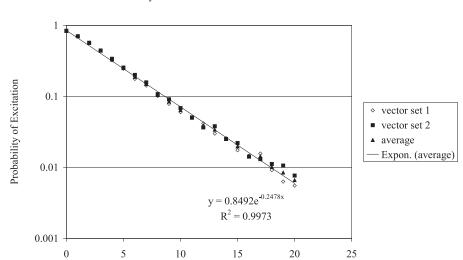

### A. The Disjoint Assumption

A disjoint assumption may be used for defect level calculations because the error introduced by using this assumption instead of an assumption of statistical independence is miniscule under most testing conditions. Ultimately, this is because the probability of a single defect occurring is low and therefore the probability of two or more defects occurring simultaneously is even lower.

Recall that the probability of a defect occurring at a circuit site can be calculated from the yield and the number of sites according to the following equation:

$$P_{defect} = 1 - Yield^{1/\# of sites}$$

(6.1)

For economic reasons, in most cases the yield cannot be very low. (If the yield is low, then a significant fraction of the manufactured circuits are defective and cannot be sold.) Thus, it is reasonable to expect that there is some minimum value for the yield. In this case, let the minimum yield be 0.3. Furthermore, one of today's commercial integrated circuits contains a significant number of circuit sites. In many cases, the number of circuit sites is on the order of 100,000 sites or more. Thus, if we assume that the yield is at least 0.3 and the number of circuit sites is at least 100,000,

Fig. 11. Statistically independent defect probabilities

then the maximum value for the probability of a defect occurring is approximately  $1.21*10^{-5}$ . Therefore, the probability of even a single defect occurring at a given site is very low.

If the probability of defects occurring is statistically independent, and we are considering the potential occurrence of two defects, then we can represent the four possibilities with a graph like that shown in Fig. 11.

In this figure, the different parts of the rectangles represent different probabilities as a Venn diagram. The vertical rectangle on the right represents the probability that the first defect occurs. Under the assumptions stated earlier, this probability is on the order of  $10^{-5}$ . The area to the left of this rectangle represents the probability that defect one does not occur and is therefore almost equal to one. The horizontal rectangle on the bottom represents the probability that defect two occurs and is also on the order of  $10^{-5}$ . Similarly, the area above this rectangle represents the probability that this defect does not occur. If the occurrence of the defects is statistically independent, then the probability that both defects occur simultaneously is represented by the intersection of their detection rectangles and corresponds to the square in the lower right corner. This square is very small and the corresponding probability is on the order of  $10^{-10}$ . If we assume disjoint probabilities, we neglect to take into account the possibility of this happening; however, because the possibility is so incredibly small, we don't introduce a significant amount of error by neglecting it.

### B. Calculating Defect Level with MPG-D

By assuming disjoint probabilities instead of statistical independence, we can replace the product over all circuit sites used to calculate defect level with MPG and MPG1 by a sum of each site's contribution to the overall defective part level. Thus, initially, before any vectors have been applied, we can distribute the total defective part level equally among all circuit sites. This will give each site i its own defect level contribution according to Equation 6.2.

$$DL\_contr_i(p) = \frac{1 - Yield}{\# of \ sites}$$

(6.2)

Of course, if layout or historical data indicate that certain sites are more likely to be defective than others, then a weighted distribution of the initial defect level may be used to assign more defect level contribution to sites that are more likely to be defective or contain more defects. However, because we usually do not have such data, we generally assign an equal initial defective part level contribution to all circuit sites.

Recall that the two requirements for defect detection are defect excitation and site observation. Every time that a site is observed, there is some probability of exciting an undetected defect at that site and further reducing the defect level. Thus, just as in MPG, and MPG-1, the final defective part level predicted through MPG-D will be a function of the number of times circuit sites are observed. Specifically, we will reduce the defective part level contribution of every site that is observed by a test pattern p according to equations 6.3, 6.4 and 6.5.

$$P_{excite_i} = e^{-\frac{\#obs_i}{\tau}} \tag{6.3}$$

$$\Delta site_i(p) = \begin{cases} DL_i(p-1) * (A * P_{excite_i}), & \text{if site } i \text{ was observed by pattern } p. \\ \\ 0, & \text{otherwise.} \end{cases}$$

(6.4)

$$DL\_contr_i(p) = DL_i(p-1) - \Delta site_i(p)$$

(6.5)

Here equation 6.3 specifies the probability of exciting an undetected defect at  $site_i$  given that  $site_i$  is observed and has been observed  $\#obs_i$  times previously. As was shown in the previous chapter, this probability should follow a decaying exponential of the number of observations of the site and some time constant  $\tau$ . However, while this equation gives us the probability of exciting an undetected defect, it does not tell us how much the defect level contribution of the site should be reduced. For this, we

will use the value of  $\Delta site$  as calculated in equation 6.4.

Recall that one of the underlying premises of the MPG-1 model was the fact that exciting at least one undetected defect at a site given that it was observed did not guarantee that all of the defects that could occur at that site (in different circuits) were also fortuitously excited. Instead, it is possible to fortuitously detect some of the defects at a circuit site while other defects still remain undetected. This idea is captured by the constant A in the MPG-D model. In equation 6.4, A represents the fraction of the remaining defective part level that will be removed given that at least one undetected defect is excited while the site is observed. Like  $\tau$ , the constant A must be chosen appropriately in order to obtain an accurate defect level prediction.

Thus, if a site is observed on a given pattern,  $\Delta site$  represents the average reduction in defective part level contribution that should occur at that site. If a site is not observed,  $\Delta site$  is equal to zero because site observation is required for defect detection. After each pattern is applied, we can use the information from fault simulation of that test pattern to determine which sites were observed and to obtain appropriate  $\Delta site$  and new defect level contribution values for every site in the circuit.

Then, the overall defect level predicted after the application of pattern p can be calculated as shown in equation 6.6.

$$DL(p) = \sum_{i=1}^{\#\_of\_sites} DL\_contr_i(p)$$

(6.6)

### C. Simulation Experiments

Initial experiments to evaluate the effectiveness of the MPG-D model were performed on several of benchmark circuits: c432, c499, c880, c1355, c1908, and c5315 [35]. Once again, we needed a way of simulating the fortuitous detection of unmodeled

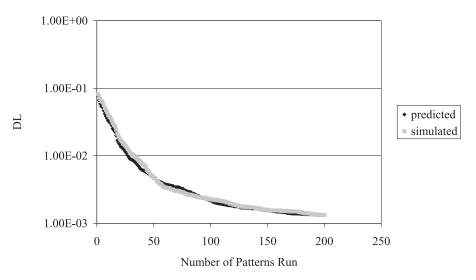

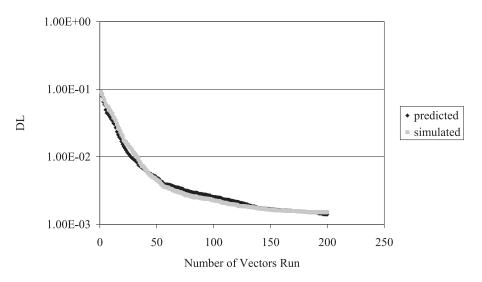

Fig. 12. C432 MPG-D prediction:  $\tau = 4.275~A = 0.663$

and untargeted defects. Thus, we generated test pattern sets for each circuit by targeting single stuck-at faults and used the fortuitous detection of random bridging surrogates to estimate the fortuitous detection of defects that would occur in an actual manufactured integrated circuit. Specifically, all of our surrogates were either nonfeedback AND bridges or nonfeedback OR bridges. It was not determined for these experiments how many of the bridging surrogates may have been redundant. We arbitrarily assumed a yield of 0.9 and calculated defect levels as the test set was applied based upon the surrogate simulation results and compared those to the values predicted by the MPG-D defective part level model. In each of the MPG-D predictions, the value of  $\tau$  was taken from Table I, and an appropriate value was found for A to best match the data. Graphs showing the simulation results along with the MPG-D predictions are shown in Figs. 12 through 18.