# PHOTONIC HARDWARE ACCELERATORS FOR RESERVOIR COMPUTING

# A Dissertation

by

# SYED ALI HASNAIN

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

Chair of Committee, Rabi Mahapatra Committee Members, Eun Jung Kim

Dezhen Song

Srinivas Shakkotti

Head of Department, Scott Schaefer

December 2020

Major Subject: Computer Engineering

Copyright 2020 Syed Ali Hasnain

#### ABSTRACT

Machine Learning (ML) approaches like Deep Neural Networks (DNNs) have emerged as a powerful tool for big data classification and prediction problems. While feedforward neural networks are good for non-temporal tasks, a lot of real-world problems like time series prediction (e.g. weather forecasting) and classification problems are temporal in nature. For such problems, Recurrent Neural Networks (RNNs) have been developed. However, the presence of recurrent connections coupled with iterative nature of training algorithms make RNN training extremely hard. Recently, it has been discovered that temporal problems can be solved by network of random recurrent connections coupled with a single trainable readout layer. This is called Reservoir Computing (RC). RC has emerged as a promising area but its implementation is challenging. In Software, RC provides limited performance, whereas hardware implementations have proved to be challenging due to many non-linear nodes present. To solve this problem, we propose to look towards the field of photonic computing to come up with high performance, power efficient photonic hardware accelerators for RC. We integrate ideas from ML, analog photonic computing, photonic device physics and hardware design to build architectures for photonic RC. We design a multi-layer photonic RC architecture to improve the performance of RC. We then integrate Time Division Multiplexing to exploit the inherent parallelism in reservoir layer and design a photonic architecture that is capable of running multiple tasks in parallel. To make photonic RC accelerators scalable, we design a first of its kind architecture that is completely on-chip.

Lastly, we study the limitations of the architectures design thus far and design a new kind of reconfigurable architecture that optimizes performance vs power consumption for any given task.

# **DEDICATION**

To my late grandfather and teacher, Prof S.M. Asif, who taught us the value of education and to my parents who made it all possible.

#### **ACKNOWLEDGEMENTS**

I would like to thank my committee chair, Dr. Rabi Mahapatra for his guidance and support throughout the course of my research. His valuable advice at every step not only made me a better researcher but also a better human being. Without his support, this dissertation would not have come to its fruition. I would also like to thank my committee members, Dr. Eun Jung Kim, Dr. Dezhen Song and Dr. Srinivas Shakkotti for their valuable feedback and constructive criticism. I would also like to thank Dr. Duncan Walker and Karrie Bourquin for their helpful support as graduate advisors throughout the course of my graduate studies.

I would also like to thank my former lab mate and collaborator Dr. Dharnidhar Dang, for his timely feedback and ideas on my work. His contribution has always been very valuable. We have also shared an interest for cricket, and played many matches together. I will also like to thank my lab mates Jyotikrishna Dass, Karl Ott and Jerry Yiu, who have always made themselves available for brainstorming ideas.

I would not have been able to complete my Ph.D. without the support of my family. Without the love, support, encouragement and guidance of my parents, I would never have been able to reach where I am today. They have always inspired me to do better. I would also like to thank my brother, Umair, for his continuous support. My sister, Aleena, for making me believe I can do this and my youngest sister, Shiza, for providing all the entertainment throughout these years. I would also like to thank my grandmothers for their prayers, love and support. My uncles, who have been very supportive throughout, have

each been a role model, in their own way for me and for that I am grateful to them. Last but not the least, I would like to thank my beautiful wife, Maham, for first agreeing to marry me and then supporting me through the last phase of this dissertation.

Finally, I would also like to thank my friends Qasim, Hameed ul Haq, Basim, Sajjad, Umair, Ovais, Hamza, Taimoor, Maliha and Maheen for making my journey in USA throughout my Ph.D. a beautiful one.

# CONTRIBUTORS AND FUNDING SOURCES

# **Contributors**

This work was supervised by a dissertation committee consisting of Dr. Rabi Mahapatra (advisor), Dr. Eun Jung Kim and Dr. Dezhen Song of Department of Computer Science and Engineering and Dr. Srinivas Shakkotti of Department of Electrical and Computer Engineering.

Dr. Dharnidhar Dang of University of California, San Diego helped review results presented in Chapter 2.

All other work conducted for the dissertation was completed by the student independently.

# **Funding Sources**

Graduate study was supported through graduate assistantships from the Department of Computer Science And Engineering.

# **NOMENCLATURE**

ML Machine Learning

RNN Recurrent Neural Network

RC Reservoir Computing

DNN Deep Neural Network

DFR Delayed Feedback Model

DL Delay Line

MZI Mach Zehnder Interferometer

MRR Micro Ring Resonator

GPU Graphic Processing Unit

NARMA Non-linear Auto Regressive Moving Average

NMSE Normalized Mean Square Error

BER Bit Error Rate

WER Word Error Rate

TDM Time Division Multiplexing

# TABLE OF CONTENTS

|                                                     | Page                   |

|-----------------------------------------------------|------------------------|

| ABSTRACT                                            | ii                     |

| DEDICATION                                          | iv                     |

| ACKNOWLEDGEMENTS                                    | v                      |

| CONTRIBUTORS AND FUNDING SOURCES                    | vii                    |

| NOMENCLATURE                                        | viii                   |

| TABLE OF CONTENTS                                   | ix                     |

| LIST OF FIGURES                                     | xii                    |

| LIST OF TABLES                                      | xiv                    |

| 1. INTRODUCTION                                     | 1                      |

| 1.1. The Reservoir Computing Model                  | 3<br>5<br>8<br>9<br>11 |

| 2. A MULTILAYER PHOTONIC RESERVOIR COMPUTING SYSTEM | 16                     |

| 2.1. Motivation                                     | 18<br>19<br>20         |

| 2.4.1. Principle Of Reservoir Computing             | 21                     |

| 2.5. MReC Architecture                              | 22<br>26               |

| 2.6.2. Santa Fe Time Series                            | 27 |

|--------------------------------------------------------|----|

| 2.6.3. Non-Linear Channel Equalization                 |    |

| 2.6.4. NARMA Task                                      |    |

| 2.7. Results And Analysis                              |    |

| 2.7.1. Prediction Error Rate Comparison                |    |

| 2.7.2. MReC Vs State Of The Art Architectures          |    |

| 2.7.3. Energy Consumption Comparison                   |    |

| 2.8. Summary                                           |    |

| 3. MULTILAYER PHOTONIC RESERVOIR COMPUTING USING TIME  |    |

| DIVISION MULTIPLEXING FOR PARALLEL COMPUTATION         | 20 |

| DIVISION MULTIPLEATING FOR PARALLEL COMPUTATION        | 39 |

| 3.1. Motivation                                        | 39 |

| 3.2. Related Work                                      |    |

| 3.3. Contribution                                      |    |

| 3.4. Time Shared Multilayer Photonic Architecture      |    |

| 3.4.1. TDM Integrated Input Layer                      |    |

| 3.4.2. Reservoir Layer                                 |    |

| 3.4.3. Output Layer                                    |    |

| 3.5. Experimental Methodology                          |    |

| 3.5.1. NARMA Task                                      |    |

| 3.5.2. Analog Speech Recognition                       |    |

| 3.6. Results                                           |    |

| 3.6.1. Comparison Using NARMA Task                     |    |

| 3.6.2. Comparison Using Speech Recognition             |    |

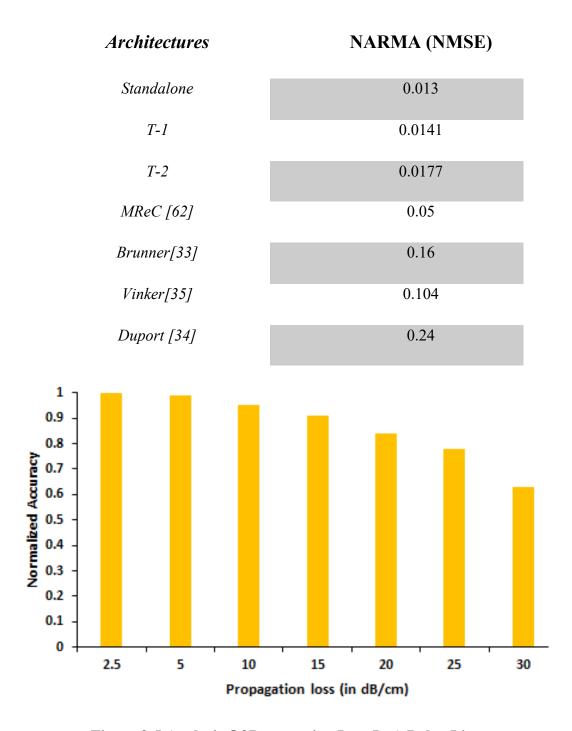

| 3.6.3. Comparison With Other Architectures             |    |

| 3.7. Summary                                           |    |

| 3.7. Sammary                                           |    |

| 4. ON-CHIP PARALLEL PHOTONIC RESERVOIR COMPUTING USING |    |

| MULTIPLE DELAY LINES                                   | 53 |

|                                                        |    |

| 4.1. Motivation                                        | 53 |

| 4.2. Related Work                                      | 54 |

| 4.2.1. Photonic RC Architectures                       | 54 |

| 4.2.2. Delay Lines                                     | 55 |

| 4.2.3. Photodiodes                                     |    |

| 4.3. Contribution                                      |    |

| 4.4. Multiple Delay Line Based Photonic Rc             |    |

| 4.4.1. Input Layer                                     |    |

| 4.4.2. Reservoir Layer                                 |    |

| 4.4.3. Output Layer                                    |    |

| 4.5. Evaluation Of Architecture                        |    |

| 4.5.1. Experimental Methodology                        |    |

| 452 Renchmarks                                         | 61 |

| 4.6. Results                                                       | 62 |

|--------------------------------------------------------------------|----|

| 4.6.1. Different Configurations Of The Proposed Architecture       | 62 |

| 4.6.2. Comparison With Other State-Of-The-Art System               | 64 |

| 4.6.3. Speed And Power Comparison                                  |    |

| 4.7. Summary                                                       |    |

| 5. RECONFIGURABLE OPTOELECTRONIC HARDWARE ACCELERATOR              | _  |

| FOR RESERVOIR COMPUTING                                            | 69 |

| 5.1. Motivation                                                    | 69 |

| 5.2. Contributions                                                 |    |

| 5.3. Review Of Multi-Layer Reservoir Computing Architecture        | 71 |

| 5.3.1. Input Layer                                                 |    |

| 5.3.2. Reservoir Layer                                             |    |

| 5.3.3. Readout Layer                                               |    |

| 5.4. Performance Of Multi-Layer Photonic RC Architectures          |    |

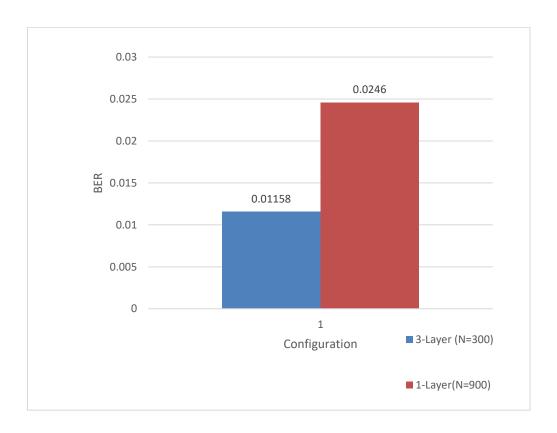

| 5.4.1. Performance Of Multi-Layer RC With Different Configurations |    |

| 5.4.2. Power Consumption Of Multi-Layer RC                         |    |

| 5.5. Reconfigurable Architecture For Photonic Reservoir Computing  |    |

| 5.6. Results                                                       |    |

| 5.7. Summary                                                       |    |

| 6. CONCLUSION AND FUTURE DIRECTIONS                                | 86 |

| 6.1. Conclusion                                                    | 86 |

| 6.2. Future Directions                                             | 88 |

| REFERENCES                                                         | 91 |

# LIST OF FIGURES

| Page                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-1 Traditional Programming Versus Machine Learning                                                                                                                                                                    |

| Figure 1-2 Deep Neural Network Architecture Comprising Of Multiple Neural Layers 2                                                                                                                                            |

| Figure 1-3 Deep Neural Network For Digit Classification                                                                                                                                                                       |

| Figure 1-4 An Unrolled Recurrent Neural Network                                                                                                                                                                               |

| Figure 1-5 Reservoir Computing Architecture                                                                                                                                                                                   |

| Figure 1-6 Three Stages Of The Reservoir Computing                                                                                                                                                                            |

| Figure 1-7 (A) Delay Line Reservoir Topology (B) Delay Line Feedback Topology (C) Single Cycle Reservoir Topology                                                                                                             |

| Figure 1-8 MZI Structure With Laser Light As Input And Electric Field On One Arm To Modulate Data                                                                                                                             |

| Figure 2-1 Single Node Photonic Computing Model                                                                                                                                                                               |

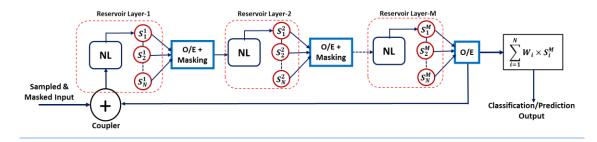

| Figure 2-2 Logical Schematic Of MReC Architecture                                                                                                                                                                             |

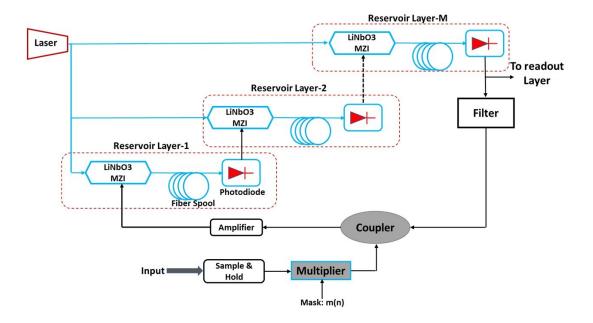

| Figure 2-3 MReC Microarchitecture                                                                                                                                                                                             |

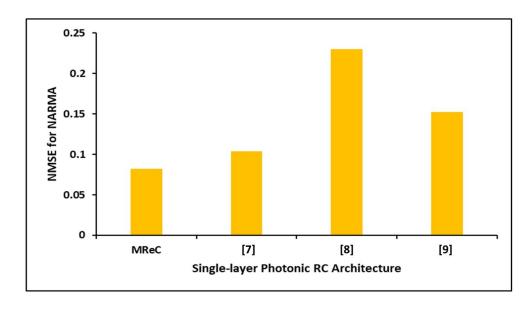

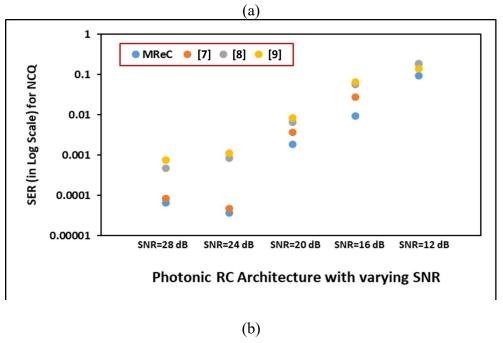

| Figure 2-4 (A) NMSE Comparison For NARMA Task When N=50 In All Rcs, (B) SER Comparison For NCQ For Photonic Rcs With N=50 When SNR Is Varied From 12 To 28 Db                                                                 |

| Figure 2-5 (A) WER Comparison Of 1-Layer MReC With [8] And [10] For Isolated Spoken-Digit Recognition Task (ISDR), (B) NMSE Comparison Of 1-Layer MReC With [10] For Santa Fe Task, W.R.T. Photodiode Attenuation As Feedback |

| Figure 2-6 Power Consumption For MReC Architecture Variations                                                                                                                                                                 |

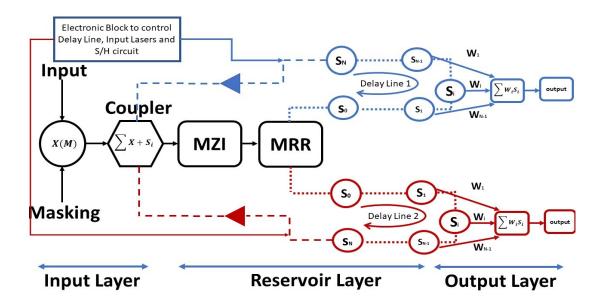

| Figure 3-1 Single Node Photonic Model With Internal States Corresponding To Virtual Neurons                                                                                                                                   |

| Figure 3-2 Time Shared Multi-Layer Photonic Reservoir Computing Architecture44                                                                                                                                                |

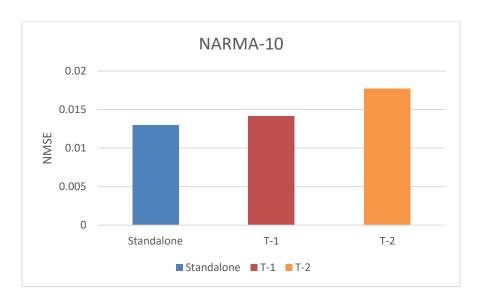

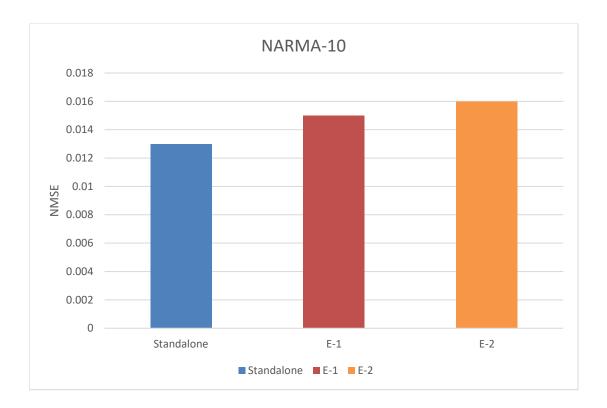

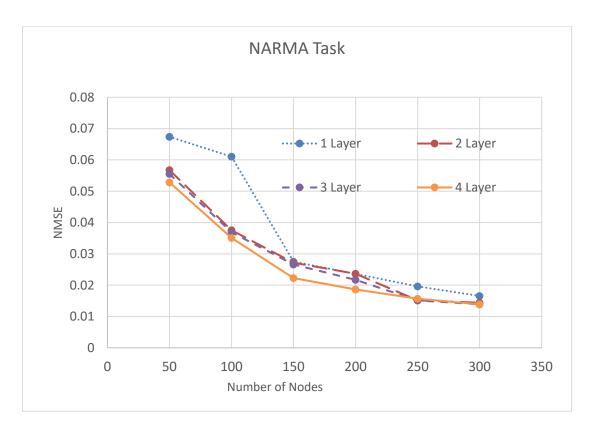

| Figure 3-3 Performance Results For NARMA-10 Task While Using Time Shared Multi-Layer Reservoir System                                                                                                                         |

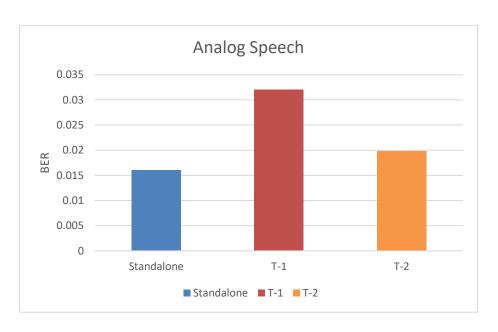

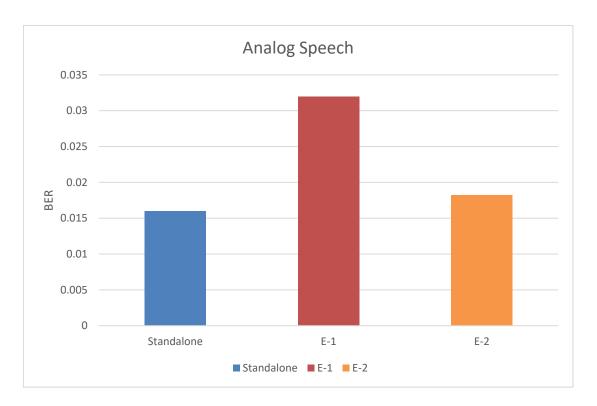

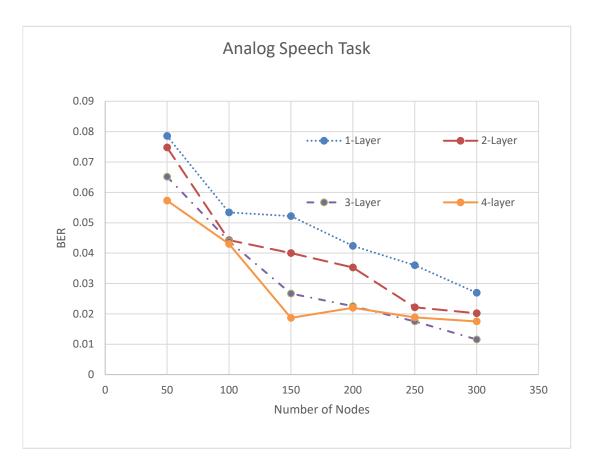

| Figure 3-4 Performance Results For Analog Speech Recognition For Different  Configurations                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3-5 Analysis Of Propagation Loss In A Delay Line                                                                                                                |

| Figure 4-1 Schematic Of Proposed Architecture                                                                                                                          |

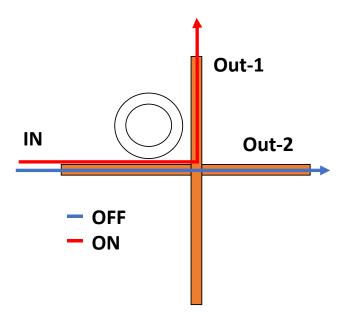

| Figure 4-2 An Electronically Tuned MRR Switch To Direct Light Based On ON/OFF State                                                                                    |

| Figure 4-3 NARMA Results For Different Configurations                                                                                                                  |

| Figure 4-4 Analog Speech Recognition For Different Configurations64                                                                                                    |

| Figure 4-5 Comparison Between Proposed Architecture And TDM Based Approach Presented In [83]66                                                                         |

| Figure 5-1 Review Of The Multi-Layer Photonic RC Architecture71                                                                                                        |

| Figure 5-2 Effect Of Number Of Nodes And Reservoir Layers On NARMA Task75                                                                                              |

| Figure 5-3 Effect Of Number Of Nodes And Reservoir Layers On Analog Speech Recognition Task                                                                            |

| Figure 5-4 Performance Comparison Between Two Systems Configurations With Increasing Nodes And Increasing Layers                                                       |

| Figure 5-5 Power Consumption In Watt For 1-Layer, 2-Layer, 3-Layer, And 4-Layer MReC Architecture                                                                      |

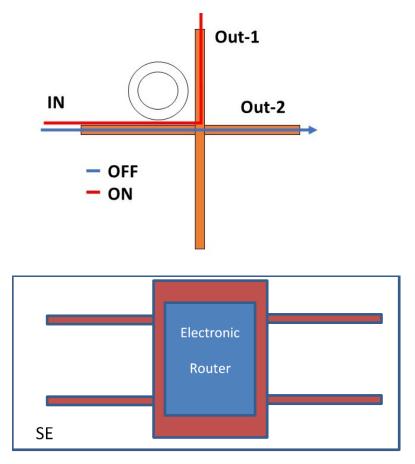

| Figure 5-6 (Top) 2x2 MRR Based Switch (Bottom) Block Diagram For An Electronically Controlled Switching Element With MRR Switch Being Controlled By Electronic Router. |

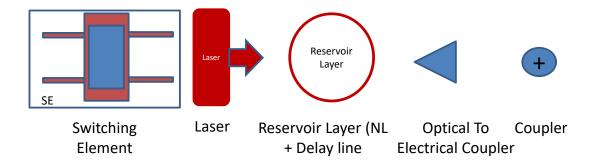

| Figure 5-7 Symbols Used In The Reconfigurable Photonic RC Architecture81                                                                                               |

| Figure 5-8 Propose Reconfigurable Architecture For Photonic Reservoir Computing82                                                                                      |

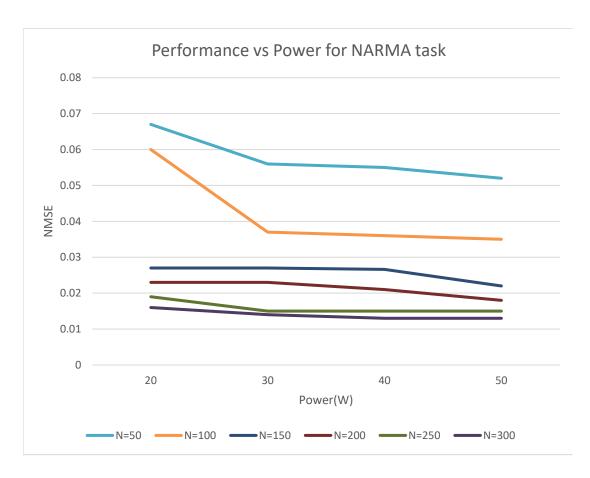

| Figure 5-9 Performance Of The Architecture For NARMA Task Vs Power  Consumed                                                                                           |

# LIST OF TABLES

| ŀ                                                                                                                 | Page |

|-------------------------------------------------------------------------------------------------------------------|------|

| Table 1-1 Summary Of Design Features Of Each Of The Proposed Photonic Architectures                               | 14   |

| Table 2-1 Parametric Details Of Components Used In The Proposed Architecture                                      | 26   |

| Table 2-2 Prediction Error Rate Comparison Of 1-Layer, 2-Layer, 3-Layer, And 4-Layer Proposed RC                  | 31   |

| Table 3-1 Parametric Detail Of Components For Time Division Multiplexing Integrated RC Architecture               | 47   |

| Table 3-2 Comparison Of Results For Different Photonic RC Architectures For The Common NARMA Benchmark            | 51   |

| Table 4-1 Results For Proposed Architecture vs Different Photonic RC Architectures For The Common NARMA Benchmark |      |

| Table 4-2 Comparison Of Size Of Delay Lines In State-Of-The-Art Photonic RC Architectures                         | 67   |

| Table 5-1 Parametric Details Of Opto-Electronic Components                                                        | 74   |

| Table 5-2 Performance Vs Power Of MReC Vs Reconfigurable RC                                                       | 83   |

## 1. INTRODUCTION

## 1.1. The Reservoir Computing Model

In the advent of big data, Machine Learning (ML) has emerged as a promising area to solve prediction and classification problems. Loosely speaking, ML "gives the computer's ability to learn without being explicitly programmed" (Arthur Samuel, 1959). More formally, ML can be defined as computational learning using algorithms to learn from and make predictions on data. ML is different from traditional programming as no explicit programming related to data is required. Figure 1.1 depicts this difference between traditional learning and Machine Learning.

# Data — Computer — Output Machine Learning Data — Computer — Program Output — Program

Figure 1-1 Traditional Programming Versus Machine Learning

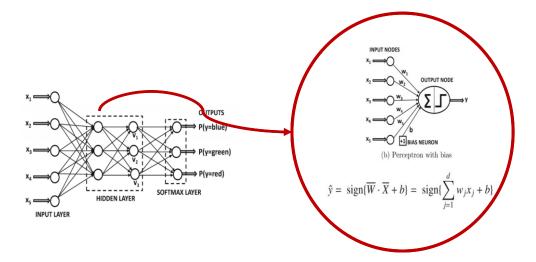

While many different ML methods exist, Artificial Neural networks (ANN) are extremely popular [1, 2, 3, 4, 5, 6, 7]. Given data, these networks compute transformations of features or representation to make a final decision on it as represented in Figure 1.2. Feed forward networks comprising of multiple layers (DNNs) have been used extensively

in literature to study non-temporal problems. These networks are also well understood due

Figure 1-2 Deep Neural Network Architecture Comprising Of Multiple Neural Layers

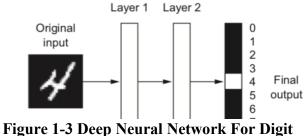

to their non-dynamic nature. DNNs comprise of several layers, with each layer containing many neurons as shown in Figure 1.3. Mathematically, these networks are trained by solving an optimization problem to compute the appropriate weights [8]. The training process is computationally very expensive and requires a lot of computational power.

However, many real-world problems are temporal in nature. For example, prediction problems like financial data forecasting or weather forecasting and classification problems like speech recognition [9]. The feedforward networks have been

Figure 1-3 Deep Neural Network For Digit Classification

Figure 1-4 An Unrolled Recurrent Neural Network

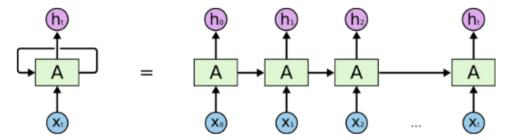

used to solve these temporal problems by means of converting temporal problems to spatial problems by delayed embeddings. However, this is not a natural way of representing time [10]. Furthermore, such methods give rise to problems like artificially introduced time horizons [11]. To solve temporal problems Recurrent Neural Networks (RNNs) have been proposed. The networks consist of many recurrent connections as shown in Figure 1.4. The recurrent connections give rise to even larger number of parameters to be trained and hence training an RNN is even more compute intensive.

## 1.2. Reservoir Computing

Recently, it has been discovered that temporal problems can also be solved by a random network of recurrent connections coupled with a single trainable readout layer. This idea was proposed by Rosenblatt in 1962[12]. Fairly recent works have explored this paradigm and have independently come up with two main models, the echo state networks (ESNs) and the liquid state machines (LSMs)[13, 14]. The ESNs are based on non-spiking artificial neural networks whereas the LSMs were proposed in the context of spiking neural networks. The two concepts combined together have been named as Reservoir Computing (RC)[15]. Reservoir Computing (RC) is a subset of RNN and is a promising

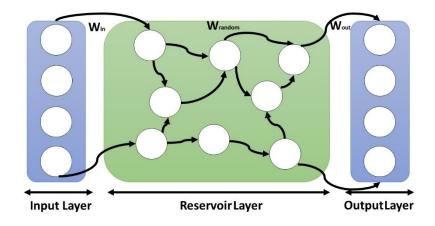

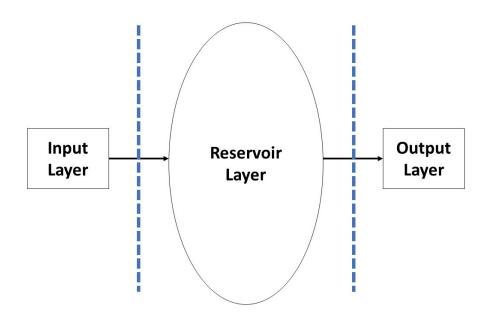

approach to solve large scale classification and prediction problems[16, 17, 18, 19, 20]. In an RC system, there are three main layers: input layer, reservoir layer and output layer. The basic idea behind RC can be summed up as follows:

- 1. The reservoir layer is used for feature extraction and comprises of several hidden layers. The readout layer is trained for prediction or classification problem.

- 2. Contrary to RNN, the weights of input layer,  $W_{in}$ , as well as the hidden layers inside the reservoir layer,  $W_{random}$ , are not trained but are randomly initialized.

- 3. Only the weights of the output layer,  $W_{out}$ , are trained. This allows for a far reduced training time compared to RNN. Figure 1.5 shows a representation of a RC network.

Figure 1-5 Reservoir Computing Architecture

RC has emerged as a promising field, with various benefits. The reduced training time makes the RC network very attractive. As with most neural networks this concept is inspired by the workings of biological brain. Several studies have argued that RC concept is similar to the workings of a brain, where an external stimulus excites the internal states

of network and processes information[21, 22, 14, 23, 24, 25]. Furthermore, the reservoir section of RC is independent of task being performed. This means that multiple tasks can use the same reservoir with a different readout layer for each task. A reservoir can be considered as a generic computation tool that is task independent. As a result, several tasks can be performed in parallel. As an example, recently, it has been shown that the same reservoir can be used for speech recognition as well as speaker recognition [26].

While RC is a promising approach, there are still many open research questions.

These questions can be categorized into three main research areas in the field:

- 1. Computational Aspect

- 2. Design of Reservoir

- 3. Implementation of RC

In our work, we focus on implementation of RC with the goals of improving accuracy as well as making the implementation high performing and energy efficient. While RC can be implemented on software using conventional processors, some applications require hardware accelerators. In an era where Internet of Things (IoT) and edge computing ideas are fast taking shape, compact, fast and energy efficient devices are required for computation and data processing. A hardware accelerator is designed with these needs in mind.

# 1.3. Hardware Implementations Of Reservoir Computing

While RC has performance comparable to RNNs [27], its implementation has been challenging. In the literature, software implementations of RC provide limited performance [10] while hardware implementations of RC prove to be difficult due to many

non-linear nodes that exist in reservoir layer [28]. To solve this challenge, we first study the different topologies of RC that have been proposed. RC networks have three stages: Input layer, Reservoir and Output layer, as shown in Figure 1.6.

Figure 1-6 Three Stages Of The Reservoir Computing

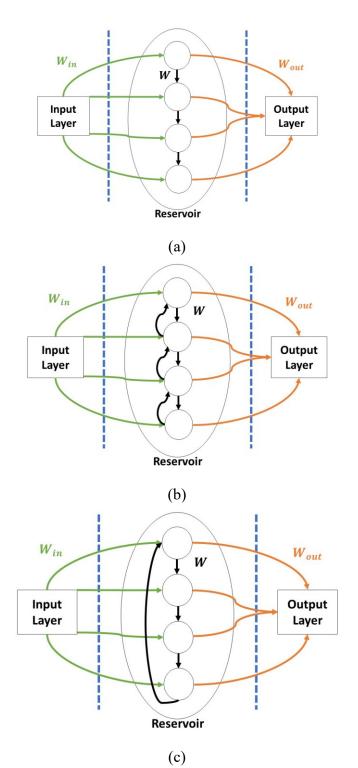

The input layer and output layer are consistent in all topologies. However, due to the random nature of reservoir layer, we can arrange the connections in several ways [29]. Researchers in [29] have investigated various reservoir topologies and have come up with three main topologies: Delay Line, Delay line with feedback and Single Cycle Reservoir (SCR). The topologies differ in the way feedback connections are arranged in the reservoir, as shown in figure 1.7.

The delayed feedback reservoir (DFR) model of RC[30, 31, 32], inspired by SCR has emerged as a very attractive model to implement Reservoir Computing. It uses only one single neuron along with a delay line in a ring topology to create the reservoir.

Figure 1-7 (A) Delay Line Reservoir Topology (B) Delay Line Feedback Topology (C) Single Cycle Reservoir Topology

especially in the photonics domain can be used for its implementation. Following this model, several silicon photonics based single layer RC implementations have been presented in the literature [33, 34, 35]. These single-layer photonic implementations demonstrate 100x improvements in speedup compared to previous RC implementations. However, the accuracy of these implementations is lower than software RNN implementations. Recently, authors in [36, 37] have demonstrated software implementation of multi-layer RC to be of identical accuracy as compared to RNN implementations at the expense of large execution time. These systems also employ fiber optics as delay line and contain off-chip elements. While the proposed architectures are very promising, they still lack performance, use only one layer of reservoir and employ off chip components. Therefore, there is a need for more accurate, high performing accelerators for RC that addresses these issues.

# 1.4. The Emergence Of Silicon Photonic

Silicon photonics has emerged not only as an exciting prospect for on chip interconnects but also for computation in the analog domain. The computation and communication in silicon photonics domain has proved to be high speed, high bandwidth and less power hungry compared to traditional electronic counterparts. Moreover, several commercial photonics CAD tool like IPKISS [38] are available now that enables working with photonic components easier. All of this serves as a motivation to design high speed and high bandwidth computing systems that can process large scale data, while consuming less power than their electronic counterparts.

## 1.4.1. Basics Of Silicon Photonics

Silicon photonics-based computing systems employ several optoelectronic components. Before discussing photonic architectures for RC, it is important to review these components.

# 1.4.1.1. Waveguides And Fiber Spools

Silicon photonic waveguide is one of the building blocks for not only photonic components but also many photonic computing and communication systems. Waveguides are used as building blocks for Micro Ring Resonators, Mach Zehnder Modulators, Couplers as well as feedback mechanisms in photonic components. A silicon core with cladding is used to make a waveguide. Using the principle of total internal reflection and difference in refractive index of core and cladding, light is contained inside the waveguide and travels through it.

A fiber spool is a fiber optic cable, that again uses the principle of total internal reflection to transmit light from one point to the other. These are often employed to provide a delay in photonic computing systems as well as communication over large distances.

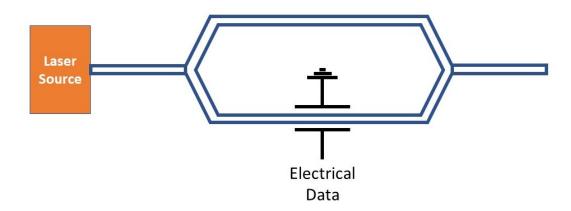

## 1.4.1.2. Mach Zehnder Modulator

A Mach Zehnder Modulator (MZM) or Mach Zehnder Interferometer (MZI) is another important photonic component. This component is used to modulate data over laser light. A MZM is basically two waveguides connected at either end by a Y junction. The length of the waveguides is normally unequal which causes light traveling through both arms to have different phase. The constructive and destructive interference helps

create an output. Researchers have also come up with clever methods to use electrical field to control light speed in one of the arms. This enables modulation of electrical data over the laser light. Figure 1.8 below shows the basic working of MZM.

Figure 1-8 MZI Structure With Laser Light As Input And Electric Field On One Arm To Modulate Data

Laser light enter the modulator from one end and is split into the two arms. In one arm light propagates without any change. However, on the other arm, an electric field is applied which changes the refractive index of that arm and slows down the propagation of light in this arm. Due to the applied electric field, light in lower arm goes out of phase with light in upper arm. At the output, constructive and destructive interference cause a modulated version of laser light. This phenomenon can be used as the activation function of a neuron.

# 1.4.1.3. Micro Ring Resonators

Optical Ring Resonators have been extensively discussed in literature [39, 40]. They are essential for the success of silicon photonics. Using resonance, they can enable

the control of photonic path. In literature several MRR designs have been proposed [41, 42]. The main focus of these design is speed, application and size. Recently a 2x2 MRR was proposed which can be employed as reconfigurable DEMUX/MUX[43]. Such a component is ideally suited for selection of a delay line in a multi delay line-based architecture.

#### 1.4.1.4. Photodiodes

Photodiodes are used for detection of light traveling through a component or system. It is also used for optical to electrical conversion of data. Photodiodes are often designed for a specific band and a rise/fall time.

## 1.5. Research Focus

This dissertation focuses on design of high speed and power efficient photonic Reservoir Computing hardware accelerators. We first review the working of a single node photonic computing model that is based on delayed feedback reservoir (DFR) computing model. We begin by extending the single node computing model, to incorporate multiple layers for Reservoir for Deep RC. Deep RC improves the performance of the system. We then study the ability of a reservoir to process multiple tasks in parallel and propose an improvement in our architecture to exploit parallel processing. To make the systems compact and on chip, we also make an effort to design a completely on chip system. Furthermore, we study the performance and power consumption of a system with different reservoir configurations and investigate reconfigurable photonic RC accelerators.

## 1.6. Contributions

The contributions of this dissertation are as follows:

MReC- A Multilayer Photonic Reservoir Computing Architecture: We propose MReC, a novel scalable and energy-efficient multilayer photonic reservoir computing architecture for large-scale classification and prediction. To the best of our knowledge, the proposed work is first of its kind using photonic components for multilayer reservoir computing. We introduce a multi-layer pipeline approach to enhance MReC's overall throughput by introducing multiple delay lines in series in the microarchitecture. We synthesized the proposed MReC architecture using commercial photonic CAD tools and ran system-level simulation on the architecture using four well-known classification and prediction benchmarks. The results demonstrate: (1) up to 26.8% reduction in prediction error rate in 1-layer MReC and up to 50% reduction in prediction error in 4-layer MReC compared to state-of-the-art design; (2) at least 132x improvement in speedup compared to best reported result; and (3) up to 34.21% improvement in power consumption compared to the best hardware implementation in literature. These improvements come at a cost of 12% area overhead.

Multiplexing for Parallel Computation: We review the RC computing principles and explain the single node photonic computing paradigm. We propose a new time-shared multi-layer photonic architecture for RC to perform tasks in parallel. Through experiments we show that our architecture can outperform some of the leading single layer architectures by up to 90% for NARMA task while performing analog speech recognition in parallel. We also show that our proposed architecture closely matches the performance of leading multi-layer photonic RC architecture with an increased error of 8% only due to

parallel processing. It is also shown that the proposed high-speed architecture has a power consumption of  $\sim$ 50W for a 4-layer network.

On-Chip Parallel Photonic Reservoir Computing using Multiple Delay lines: We propose a new architecture for on-chip parallel photonic reservoir computing employing multiple electronically tunable delay lines along with an MRR switch for delay line selection. Through simulations we show that the proposed architecture is up to 84% more accurate compared to a leading architecture while executing NARMA task alone and 80% more accurate when executing two tasks in parallel. It outperforms other architectures presented in literature. We also show that the proposed architecture performs 46% more accurate compared to an RC architecture employing Time Division Multiplexing (TDM) at input layer to execute tasks in parallel. It is shown that the architecture removes the off-chip fiber optics-based delay line at the cost of 0.0184 mm2 of on chip area. The power overhead is just 26mW.

Towards reconfigurable optoelectronic hardware accelerator for reservoir computing: we propose a new reconfigurable optoelectronic architecture for multi-layer RC. Our proposed architecture, is based on DFR model implemented by the use of Mach Zehnder Modulator (MZM) and on chip low loss delay lines for improved performance. It integrates photonic switches based on Micro Ring Resonators (MRR) to enable reconfigurability. The architecture enables layer selection and layer gating to select the number of layers required for a task. Selection of number of layers can optimize the architecture for a specific application, resulting in huge power savings, while maintaining the overall accuracy. Our experiments with NARMA task and analog speech recognition

task show that by optimally configuring an up-to 4-layer architecture, power savings up to 40% can be achieved compared to state-of-the-art architectures while gaining up to 80% more accuracy. Our scalable architecture has an on-chip area overhead of 0.0184mm<sup>2</sup> for a single delay line and MRR switch.

Each chapter of the dissertation focuses on key elements to improve for design.

The contribution of each of the works can be summed in Table 1-1

Table 1-1 Summary Of Design Features Of Each Of The Proposed Photonic Architectures

|           | Scalability | Performance | Parallelism | <b>Energy Efficiency</b> |

|-----------|-------------|-------------|-------------|--------------------------|

| Chapter 2 |             | ✓           |             | ✓                        |

| Chapter 3 |             | ✓           | ✓           |                          |

| Chapter 4 | ✓           | ✓           | ✓           |                          |

| Chapter 5 | <b>~</b>    | ✓           |             | <b>✓</b>                 |

# 1.7. Organization

The rest of the dissertation is organized as follows: Chapter 2 discusses the design of a proposed multilayer photonic reservoir computing architecture. This is followed by Chapter 3 which discusses a modified multilayer photonic computing architecture that integrates time division multiplexing in its reservoir layer to enable parallel processing. Chapter 4 investigates the use of multiple on chip delay lines and proposes an architecture for completely on chip parallel reservoir computing system. Chapter 5 investigates the effect of reservoir configuration on performance and power, and proposes an architecture for reconfigurable reservoir computing system. This is followed by Chapter 6 which discusses some of the potential applications in which RC and our proposed hardware accelerators can be employed. Chapter 7 concludes this dissertation.

# 2. A MULTILAYER PHOTONIC RESERVOIR COMPUTING SYSTEM<sup>1</sup>

Photonic reservoir computing is a promising paradigm for large-scale classification and prediction problems. However, its single-layer nature is a bottleneck for higher performance and accuracy. Therefore, in this chapter we investigate the design of a multilayer RC system that can outperform other state of the art architectures.

## 2.1. Motivation

Recurrent Neural Networks (RNN) are often used in sequential classification and prediction problems. Deep RNN is a promising approach to enhance the accuracy of large-scale machine learning applications [44, 45, 46]. However, training a deep RNN is very compute intensive as weights of all the layers are determined in a sequential fashion. A subset of RNN is Reservoir computing (RC). It has emerged as a promising candidate to provide reduced training time with similar accuracy[27]. RNN and RC both consist of two stages: feature extractor and feature classifier. Feature extractor in RNN comprises of several hidden layers with weights that are trained extensively using available datasets to fine tune desired features. However, in RC, randomly generated fixed weights are used in the hidden layers to generate such features. For the feature classification, weights are used both in RNN and RC to fine tune the output. It may be noted that the training of weights in RC takes place only in the classifier stage. This makes the training and

<sup>&</sup>lt;sup>1</sup>adapted with permission from Copyright © 2019, IEEE Dhang, D., Hasnain, S. A., & Mahapatra, R. (2019, March). MReC: A multilayer photonic reservoir computing architecture. In *20th International Symposium on Quality Electronic Design (ISQED)* (pp. 170-175). IEEE.

classification/prediction of an RC less time consuming compared to RNN. The feature extractor and the feature classifier of an RC are otherwise known as reservoir layer and output layer respectively as shown in Figure 2.1. While RC is a promising solution to reduced training time, its implementation has been a challenge.

**Figure 2-1 Single Node Photonic Computing Model**

In the literature, software implementations of RC provide limited performance [27, 10] while hardware implementations of RC prove to be cumbersome due to many non-linear nodes that exist in reservoir layer [28]. The delayed feedback reservoir (DFR) model of RC has emerged as a potential solution to this problem. It uses only one single neuron in a ring topology to create the reservoir. Following this model, several silicon photonics based single layer RC implementations have been presented in the literature [35, 34, 33]. These single-layer photonic implementations demonstrate 100x improvements in speedup

compared to previous RC implementations. However, the accuracy of these implementations is lower than software RNN implementations. Intuitively, a multi-layer RC approach would improve the accuracy of RC system similar to deep neural network. Recently, authors in [37, 36] have demonstrated software implementation of multi-layer RC to be of identical accuracy as compared to RNN implementations at the expense of large execution time.

Therefore, in this chapter we propose a hardware implementation of multi-layer Reservoir computing using photonic components. Our proposed architecture improves the overall performance of such system. A hardware based multi-layer RC not only increases the accuracy of such systems but is also going to be faster than software-based implementations.

## 2.2. Related Works

In literature, multiple single layer photonic RC architectures have been proposed[33, 34, 35]. These architectures are based on DFR model and employ fiber optics and Mach Zehnder Interferometer as the non-linear node. The delay line length varies from 20m to 1.7Km. However, the use of fiber optics of large lengths makes these architectures non-scalable. These implementations have power consumption ranging from 76W to 200W. Alternative to optoelectronic architectures for RC, memristor based models have also been proposed in literature [47]. These architectures employ memristor meshes to implement neurons[48, 49]. While they also show promising results for specific applications, the use of memristors raises reliability issues. The designs are also less fault tolerant.

SW based implementations of RC have also been presented which demonstrate performance at par with RNNs [36, 37]. However, the increased performance comes at the expense of a larger execution time. Another proposed model that employs multiple reservoirs was proposed in [50]. However, there are no implementation details.

## 2.3. Contribution

In this chapter the following contributions are made:

- We propose MReC, a novel scalable and energy-efficient multilayer photonic reservoir computing architecture for large-scale classification and prediction.

To the best of our knowledge, the proposed work is first of its kind using photonic components for multilayer reservoir computing.

- We introduce a multi-layer pipeline approach to enhance MReC's overall throughput by introducing multiple delay lines in series in the microarchitecture.

- 3. We synthesized the proposed MReC architecture using commercial photonic CAD tools and ran system-level simulation on the architecture using four well-known classification and prediction benchmarks. The results demonstrate: (1) up to 26.8% reduction in prediction error rate in 1-layer MReC and up to 50% reduction in prediction error in 4-layer MReC compared to state-of-the-art design [34]; (2) at least 132x improvement in speedup compared to best reported result [34]; and (3) up to 34.21% improvement in power consumption compared to the best hardware implementation in [33].

- 4. These improvements come at a cost of 12% area overhead.

## 2.4. Overview Of Photonic Reservoir Computing

RC's popularity is growing rapidly in the field of data science due to its highspeed prediction mechanism. The working principle of RC is as follows.

## 2.4.1. Principle Of Reservoir Computing

A RC comprises of an input layer, a reservoir layer, and an output layer as shown in Figure 2-1. The input layer of a RC distributes input data to its reservoir layer in discrete time through fixed connection weights. The reservoir layer is a dynamical system whose state at discrete time step n can be described as a set of N scalar variables  $S_i(n)$  (i = 1,2,...N) called neurons. All the neurons in a reservoir layer are randomly interconnected with fixed random weights, constituting a recurrent network (i.e. a network of neurons having feedback loops). Under the influence of input data, the reservoir layer exhibits transient responses. The transient behavior of a reservoir is governed by an evolution equation as depicted in Equation 1:

$$S_i(n) = f[\propto C_i x(n) + \beta \sum_{j=1}^{N} w_{ij} S_j(n-1)]$$

(2.1)

Here,  $S_i(n)$  is the state of  $i^{th}$  neuron at discrete time n, f is a non-linear function, x(n) is input to RC at discrete time  $n, C_i \& w_{ij}$  are the connection coefficients that define the topology of a reservoir layer, and  $\propto \& \beta$  are tuning parameters to regulate the dynamics of a reservoir. The transient states  $S_i(n)$  are fed to the output layer through readout weights  $W_i$  to determine the output O(n).

$$O(n) = \sum_{i=1}^{N} W_i s_i(n) + W_{bias}$$

(2.2)

Here,  $W_{bias}$  is the bias value required for the training of RC. During the training phase, the readout-layer weights  $W_i$  and bias weight  $W_{bias}$  are optimized to minimize error between the expected output O'(n) and the actual output O(n).

The performance of a RC is directly proportional to the number of neurons in its reservoir layer [44]. There are several attempts to design hardware implementation of RC which involves multiple photonic neurons [45]. However, such an approach is not feasible for designing RCs with thousands of neurons as it would cost significant power and area overhead [46]. A solution to this problem is a single node photonic RC with delay dynamics, which is explained in the following section.

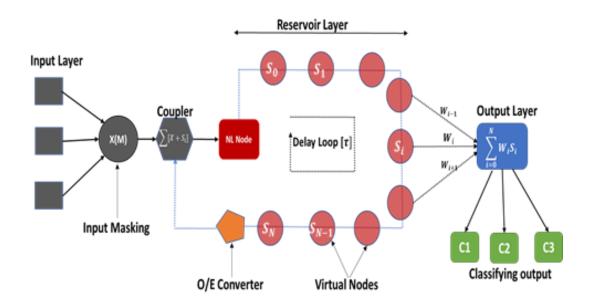

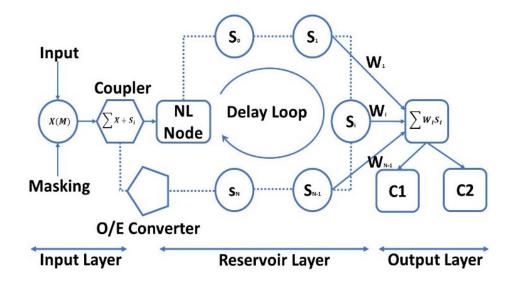

# 2.4.2. Single Node Photonic RC

A photonic implementation of RC fully exploits the advantages of optical properties of photonic hardware (low-power, high-bandwidth, and inherent parallelism). Figure 2-1 shows a conceptual diagram of a single node photonic RC. A single node photonic RC can be treated as a single-layer photonic RC architecture. It comprises of an input layer, a reservoir layer, and an output layer. In the input layer, input signal multiplied with a masking function is fed to an optical coupler. The random masking input serves the same purpose in this system, as weights of interconnects do in a standard electrical or software-based RC system. The reservoir layer comprises of a Mach Zehnder interferometer based non-linear node (NL node) and optical fiber spool-based delay loop. MZI along with the optical fiber spool is considered as neurons in RC system. In the output layer, data from the reservoir layer are trained offline. The details of each layer are presented in next section. The working principle of a single-layer RC is as follows.

The coupler receives discrete masked input  $x_i(n)$  from the input layer and feedback signal from the O/E converter. The O/E converter converts analog optical data of duration T to N discrete electrical samples  $s_i(n)$  which is fed to the coupler one by one. Each  $s_i(n)$  represents the state of a neuron in the reservoir layer at time step n. At time step n+1, The NL node receives sum of  $s_i(n)$  and masked input  $x_i(n+1)$  and then transforms it to  $s_i(n+1)$  as depicted in Equation.1. After that, the state value  $s_i(n+1)$  is stored in the delay loop to be used in the next time step, i.e. n+2. The ratio of delay  $\tau$  to the O/E conversion time t determines the number of neurons N in this kind of design.

## 2.5. MReC Architecture

A multilayer RC is realized by simply including multiple reservoir layers (NL + delay) in between architecture output of optical couplers and input of output layer as shown in Figure 2-2. Each reservoir layer stores multiple reservoir states. As shown, the output from 1st layer enters the NL Node of 2nd layer as input and so on. Each reservoir state from the last layer (Mth layer) is fed to the readout layer for training. The classification/prediction of output follows Equation.2. The weights and bias value are trained using a linear regression technique in an offline computer to determine the final output.

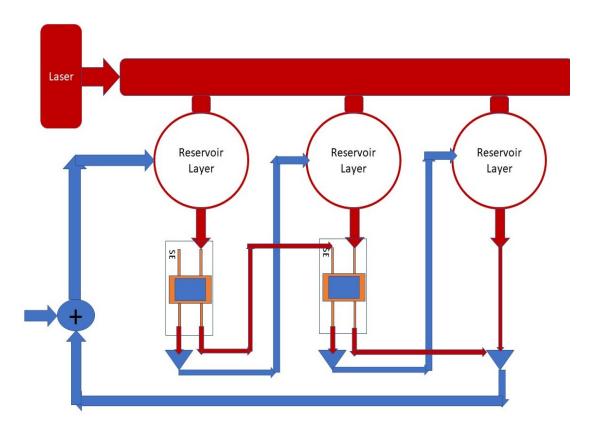

Figure 2-2 Logical Schematic Of MReC Architecture

Figure 2-3 MReC Microarchitecture

Figure 2-3 presents the microarchitecture of proposed MReC architecture. The entire microarchitecture can be divided into three parts: input layer, reservoir layer, and readout layer. These layers work in a pipeline fashion to process an input. The details are as follows:

#### **2.5.1.1.** Input Layer

As shown in Figure 2-3, the input electronic signal, x(t) is sampled with a period of  $T_S$  using a 'sample & hold' circuit. This in turn converts each continuous-time task x(t) to a discretized piecewise constant function p(n) where p(t) = p(n),  $nT_S \le t < (n+1) T_S$ , n is a time step. Each discrete input p(n) is multiplied with a periodic mask input m(n) of period  $T_S$ . Here  $m(n) = m_i(n)$  for  $(i-1)(\frac{T_S}{N}) < n \le (i+1)(\frac{T_S}{N})$ ; i=1,2...N;  $m_i(n)$  is randomly

chosen from [-1, +1]. The result of this multiplication is a masked input  $p_i(n)$  which drives the 1<sup>st</sup> reservoir layer in the 'reservoir computing segment'.

#### 2.5.1.2. Reservoir Layer

Reservoir computing segment is the heart of our proposed MReC architecture. It comprises of 'M' reservoir layer as shown in Figure 2-3. We consider up to four reservoir layers as an example for this work. Each reservoir layer consists of LiNbO3 Mach Zehnder Interferometer (MZI) as NL node and an optical fiber spool to provide delay. We consider sinusoidal nonlinearity in our design. The laser source provides optical carrier to the MZI of each reservoir layer. The output from the coupler is fed to the MZI of first reservoir layer through an electronic amplifier. For a timestep 'n', masked input  $p_i(n)$  from the coupler is fed to the MZI of first reservoir layer. The MZI converts  $p_i(n)$  into a reservoir state  $S_i^1$  where 1 stands for 1st reservoir layer and i = 1, 2...N (as we consider N reservoir states). The optical fiber spool provides a delay of  $T_S$  which is same as the sample time of 'sample & hold' circuit. For each time step n, the photodiode in the reservoir layer converts each reservoir state  $S_i^1$  from optical form to electronic form. The photodiode of each reservoir layer has an operating period of n second. Analytically, we can write n each reservoir layer has an operating period of n second. Analytically, we can write n each reservoir n in the first layer can be written as,

$$S_i^1(n) = Sin(\alpha S_i^1(n-1) + \beta m_i(n)x(n) + \emptyset)$$

(2.3)

The electronic output from the photodiode of one reservoir layer becomes an input to the next reservoir layer. This way, at any timestep n,  $i^{th}$  reservoir state of  $j^{th}$  reservoir layer can be written as,

$$S_i^j(n) = Sin(\alpha S_i^j(n-1) + \beta m_i(n)x(n) + \emptyset)$$

(2.4)

Here  $\propto$  and  $\beta$  are feedback gains;  $\emptyset$  is a bias value; and  $m_i(n)$  represents the mask input.  $\propto$ ,  $\beta$ , and  $\emptyset$  are adjustable parameters. The MZI used in our design has sinusoidal non-linearity; hence the above equation is based on a *sin* function. One cycle of MReC architecture is defined as the time taken by a masked input  $p_i(n)$  to travel from the 1<sup>st</sup> reservoir layer until the readout layer.

### 2.5.1.3. Output Layer

Using the photodiode from the last reservoir layer (here the  $M^{th}$  layer), all the N reservoir states  $S_i^M(n)$  are fed to an offline computer. The predicted output is determined using the following equation.

$$O(n) = \sum_{i=1}^{N} W_i S_i^M(n) + W_{bias}$$

(2.5)

Here Wi is calculated using linear regression training by comparing O(n) with target output O'(n).

#### 2.5.1.4. Pipeline Operation In MReC

Each reservoir layer in MReC amounts to a processing time of  $T_s$ . One masked input p(n) can be processed by one reservoir layer at a time, keeping the rest of the reservoir layers idle. This leads to underutilization of MReC architecture. We introduce a pipeline approach to fully utilize all the reservoir layers in MReC.  $T_d$  unit of time after feeding p(n) ( $T_d \ll T_s$ ), MReC's 1st layer is fed with a masked input q(n) from another task. This will keep two reservoir layers busy at a time. We can process M number of tasks in MReC at a time where M is the total number of reservoir layers. As the time interval  $T_d$

between two signals is negligible, one can assume that the overall throughput of MReC is Mx compared to single-layer photonic RC if M tasks are processed in a pipeline.

# 2.6. Experimental Methodology

We designed and synthesized optoelectronic components such as optical fiber spool, photodiode, coupler, MZI, and sampler using a commercial photonic design tool called IPKISS [38]. The synthesized components are used to design and simulate the proposed MReC microarchitecture using a CAD tool called Caphe. We integrate Caphe with Caffe [51], a C++ & Python based deep learning toolbox to rapidly build, train and evaluate machine learning models. Table 2-1 illustrates details of components used in our design. For power and area models, we use DSENT [52].

Table 2-1 Parametric Details Of Components Used In The Proposed Architecture COMPONENTS PARAMETERS VALUES

| LASER       | Wavelength | 1550nm     |

|-------------|------------|------------|

|             | Power      | 10W        |

| MZI         | Power      | 5W         |

| FIBER SPOOL | Length     | 20m        |

|             | Delay      | 0.1us      |

|             | Power      | Negligible |

| PHOTODIODE  | Power      | 5watt      |

|             | Rise Time  | 15ps       |

Four widely used machine learning benchmark tasks namely, spoken digit recognition, Santa Fe time series prediction, non-linear channel equalization, and NARMA task are run on MReC using Caffe. For the purpose of simulation, we modify the Caffe toolbox to integrate the errors introduced due to photonic components. The system is then tested with the benchmarks mentioned. The details of the benchmarks are as follows.

#### 2.6.1. Spoken Digit Recognition

Spoken digit recognition task is a widely-used classification task. The objective of the task is to classify ten spoken digits (0-9), each recorded ten times by five different persons. The dataset is obtained from [53]. The input  $p_i(n)$  to the reservoir comprises of an 86-dimensional (i = 1, 2, ... 86) state vector with up to 130 time-steps. The number of variables N <= 350. This requires an input mask  $m_{ij}$  of matrix size  $N \times 86$ , where each element is chosen randomly from  $\{-1, +1\}$  with equal probabilities.  $\sum_{i=1}^{86} m_{ji} p_i(n)$  (product of input and mask) is used to drive the reservoir. The metric to measure the performance of a system executing spoken digit recognition task is word-error-rate (WER). WER is the fraction of misclassified digits resulting from this task.

#### 2.6.2. Santa Fe Time Series

A time-series is a sequence of periodic data points over a continuous time interval. In our experiment, we use Santa Fe financial time-series recorded from a far-infrared laser operating in chaotic state [54]. The goal of this experiment is to predict a data point one time-step ahead in the future. The dataset contains 10000 points and we use 4000 points

out of it. Prediction performance is evaluated based on the normalized mean square error (NMSE) defined as:

$$NMSE = \frac{1}{n} \sum_{i=1}^{n} \frac{(O_i' - O_i)}{\sigma O_i^2}$$

(2.6)

where  $O'_i$  and  $O_i$  are predicted and expected values at time step i, n is total number of time step, and  $\sigma$  is the standard deviation. Here, NMSE = 0 implies perfect prediction and NMSE = 1 indicates no prediction.

#### 2.6.3. Non-Linear Channel Equalization

Equalization of communication channel is a way to facilitate reliable wireless communication. Whenever a signal is transmitted across a wireless communication channel, it encounters noise, channel effects (e.g. distortion, dispersion), and inter-symbol interference. Equalization of a wireless communication channel has been widely used as a benchmark task for RC simulation. The following two equations represent the relationship of the output s(n) a non-linear wireless channel to its input g(n).

$$z(n) = 0.08g(n+2) - 0.12g(n+1) + g(n) + 0.18g(n-1) - 0.1g(n-2) + 0.091g(n-1) + 0.091$$

$$3) - 0.05g(n-4) + 0.04gn(n-5) + 0.03g(n-6) + 0.01g(n-7)$$

(2.7)

$$s(n) = z(n) + 0.36z(n)^2 - 0.011z(n)^3 + d(n)$$

(2.8)

As depicted in Equation 2.7 and 2.8, s(n) encounters second-order  $z(n)^2$  and the third-order  $z(n)^3$  nonlinear distortions, and also additive Gaussian white noise d(n), which may result from the channel. s(n) is used as the final input to reservoir system.

#### **2.6.4. NARMA Task**

The NARMA task is one of the most widely used benchmarks in RC[55]. The input u(k) for this task consists of scalar random numbers, drawn from a uniform distribution in the interval [0, 0.5] and the target y(k + 1) is given by the following recursive formula:

$$y_{k+1} = 0.3y_k + 0.05y_k \left[ \sum_{i=0}^{9} y_{k-i} \right] + 1.5u_k u_{k-9} + 0.1$$

(2.9)

#### 2.7. Results And Analysis

Using Caphe, we simulate the proposed design to perform photonic feature extraction of above-mentioned benchmarks. These benchmarks are input for the proposed MReC architecture. The output from photonic simulation is fed to Caffe [51] which acts as the readout layer. In the readout layer, feature classification/prediction takes place. We determine classification/prediction error rate, power consumption, area overhead, and throughput for all the tasks. Since this is the first attempt to a multilayer RC system, we compare our proposed multilayer system with our single layer system first. We then compare our single layer results with three state-of-the-art single layer photonic RC systems [35, 34, 33] to show that our system performs better.

#### 2.7.1. Prediction Error Rate Comparison

# 2.7.1.1. Single Layer Vs Multilayer Proposed Architecture

We first evaluate prediction error rate for four benchmarks such as NARMA task, non-linear channel equalization task, isolated spoken-digit recognition task, and Santa Fe time series prediction task using a single-layer proposed RC as well as multilayer proposed

RC. The metric to determine prediction error rate differs from one task to other. For NARMA task, we consider normalized mean square error (NMSE) whereas for non-linear channel equalization task, we consider symbol error rate (SER) which is the fraction of misclassified symbols. For isolated spoken- digit recognition task, we determine word error rate (WER) which is the percentage of misclassified digits and for Santa Fe time series prediction, we evaluate NMSE which is the percentage of prediction error. For multilayer photonic RC, we consider 2-layer, 3-layer, and 4-layer of the proposed MReC architecture. Each layer of the multilayer RCs comprises of same number of reservoir nodes as that of a single-layer proposed RC. We consider number of reservoir nodes/layer, N=50 as most of the single-layer RC in literature use 50 nodes per layer for comparison. Table 2-2 presents prediction error rate of 2-layer, 3-layer, and 4-layer proposed RC normalized to a single-layer proposed RC for NARMA task, non-linear channel equalization task, isolated spoken-digit recognition task, and Santa Fe time series prediction task. For NARMA task, as we move from 1-layer to 4-layer, there is gradual reduction in the NMSE value from 0.082±0.0075 to 0.052±0.0045.

It is evident from the table that all the tasks show gradual reduction in prediction error rate with the rise in number layer of the proposed RC. NCQ task has a very small change in SER from 1-layer photonic RC to 4-layer photonic RC. This is due to the fact that NCQ task is prone to the noise introduced by a RC layer. This affects the overall reduction in SER value by the multilayer approach. In all the four cases, the prediction error rate saturates beyond the 3-layer architecture.

Table 2-2 Prediction Error Rate Comparison Of 1-Layer, 2-Layer, 3-Layer, And 4-Layer Proposed RC 1-Layer 2-Layer 3-Layer 4-Layer

| NARMA    | NMSE= 0.082±  | NMSE= 0.071± | NMSE= 0.058±  | NMSE= 0.052± |

|----------|---------------|--------------|---------------|--------------|

|          | 0.0075        | 0.0075       | 0.0065        | 0.0045       |

|          |               |              |               |              |

|          |               |              |               |              |

|          |               |              |               |              |

| NCQ      | SER=0.002     | SER=0.0019   | SER=0.0017    | SER=0.0015   |

|          |               |              |               |              |

| ICDD     | WED OO        | WED 0.75     | WED 0.62      | WED 0.55     |

| ISDR     | WER=0.9       | WER=0.75     | WER=0.62      | WER=0.55     |

|          |               |              |               |              |

| Santa Fe | NMSE= 0.092 ± | NMSE= 0.08 ± | NMSE= 0.067 ± | NMSE=0.06 ±  |

|          | 0.0075        | 0.0065       | 0.0045        | 0.0075       |

|          |               |              |               |              |

|          |               |              |               |              |

|          |               |              |               |              |

|          |               |              |               |              |

# 2.7.2. MReC Vs State Of The Art Architectures

As multilayer RC architecture is yet to be demonstrated in literature, we compare single-layer MReC with state-of-the-art architectures in [35, 34, 33]. The metric to compare prediction error rate differs from one benchmark task to another. For NARMA

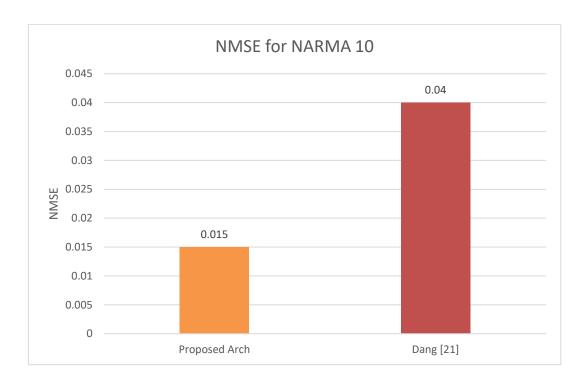

task, we compare normalized mean square error (NMSE) of the MReC architecture with [35, 34, 33]. Figure 2-4a illustrates comparison of NMSE of single-layer MReC architecture with [35, 34, 33]. For a fair comparison, the number of nodes in all the cases are chosen to be 50 (N=50). State-of-the-art photonic RC [4] performs with NMSE =  $0.104\pm0.012$ . The proposed MReC architecture with a single-layer shows improved performance with an NMSE =  $0.082\pm0.0075$ .

For "Non-linear channel equalization task", we determine symbol-error rate (SER) which is the percentage of misclassified symbols. As non-linear channel task is prone to channel noise, we also study the effect of a Gaussian noise (with zero mean) ranging from Signal-to-Noise (SNR) of 12 to 28dB. Figure 2-4b illustrates comparison of SER of single-layer MReC architectures with single-layer photonic RC in [35, 34, 33]. As evident from Figure 2-4b, MReC architecture with a single layer outperforms other photonic RC architectures irrespective of noise. With the rise in noise level in the reservoir layers, performances of photonic RCs in [35, 34, 33] degrade. When the noise is low (i.e. SNR is high) single-layer MReC demonstrates a low SER=7x10<sup>-5</sup> as opposed to a SER=8x10<sup>-5</sup> in [33], a SER=9x10<sup>-5</sup> in [35] and a SER=5x10<sup>-4</sup> in [34]. When the noise is high (SNR=12 dB), proposed RC shows a SER = SER=1x10<sup>-1</sup>, which is still better than SER=1.5x10<sup>-1</sup> in [33], and SER=2x10<sup>-1</sup> in [35] and [34]. We evaluate word-error-rate (WER) which is the

fraction of misclassified digits when executing the isolated spoken-digit recognition task.

Figure 2-4 (A) NMSE Comparison For NARMA Task When N=50 In All Rcs, (B) SER Comparison For NCQ For Photonic Rcs With N=50 When SNR Is Varied From 12 To 28 Db

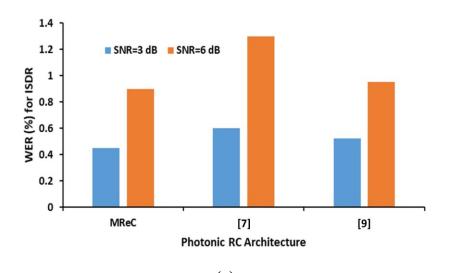

Figure 2-5a illustrates WER of single-layer MReC architecture as compared to [35] and [33] when number of reservoir nodes in each RC, N=50 while SNR = 3 dB and SNR = 6 dB. Photonic RC in [34] does not demonstrate results for isolated spoken digit recognition task. Therefore, we do not compare with [34] in this case. 1-layer MReC architecture shows lower WER compared to [35] and [33] . When SNR = 3 dB, proposed MReC with 1-layer has WER = 0.45% while [33] has WER = 0.52% and [35] has WER = 0.6%.

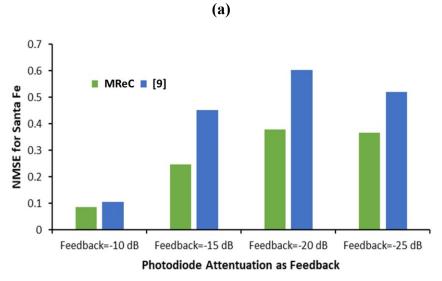

For Santa Fe task, we compared the NMSE result of MReC with that of in [33] as shown in Figure 2-5b. In Santa Fe task, a single data point needs to be predicted and hence, feedback from photodiode has a profound effect on photonic RC's accuracy. Therefore, we show NMSE results for a varying feedback parameter in terms of attenuation of photodiode. It is clearly evident that the MReC with one-layer outperforms the state-of-the-art design in [33]. Also, we obtain the best results for a feedback value of -10dB. The state-of-the-art silicon photonic diode does not produce an attenuation below -10dB. With the advancements in silicon photonic technology, if the attenuation is reduced, one may be able to predict task like Santa Fe with much better accuracy. From the above comparisons, we can conclude that MReC architecture with 1-layer outperforms other photonic RC architectures.

(B)

Figure 2-5 (A) WER Comparison Of 1-Layer MReC With [8] And [10]

For Isolated Spoken-Digit Recognition Task (ISDR), (B) NMSE

Comparison Of 1-Layer MReC With [10] For Santa Fe Task, W.R.T.

Photodiode Attenuation As Feedback.

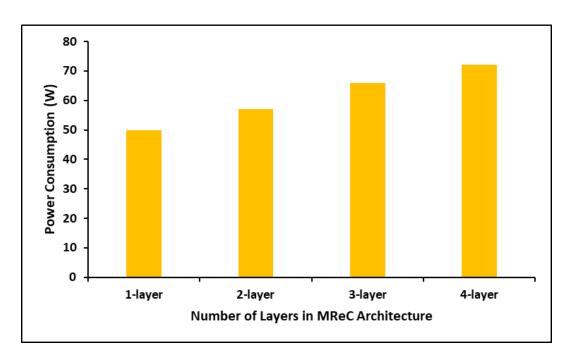

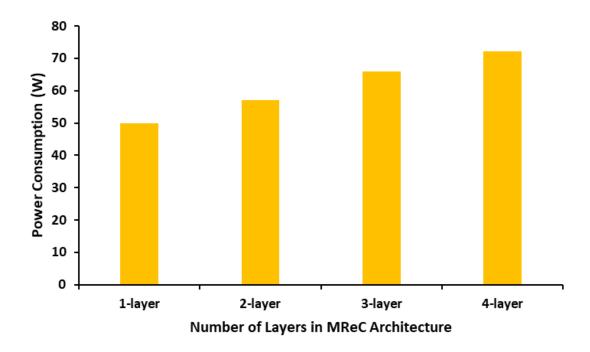

### 2.7.3. Energy Consumption Comparison

Table 2-1 illustrates all the optoelectronic components used in the proposed MReC architecture along with their parametric details. We use a standard optoelectronic power model called DSENT [52] to obtain the total power consumption in the MReC architecture. The total power consumption for a single-layer MReC architecture is approximately 50W (conservative estimate). This is lower than the state-of-the-art photonic RC architectures demonstrated in [35] which consumes 76W, in [34] which consumes 90W, and in [33] which consumes 200W. The higher power consumption in [35, 34, 33] is due to extra hardware usage e.g. more AWG in [35] and [33], and analog readout in [34]. The total power consumption of MReC architecture is a function of laser power and MZI power consumption. Note that there is only one MZI per reservoir layer. The number of states or nodes in each layer i.e. N depends on the sampling of input and the length of delay line. A multilayer photonic RC requires slightly higher optical signal strength compared to single-layer to sustain a longer optical transmission time. A multilayer approach also requires extra number of MZIs which results in additional MZI driver power. Figure 2-6 depicts variation in power consumption from 1-layer to 4-layer photonic RC. A 4-layer MReC consumes 72W which is lower than the best reported result (76W) by a single-layer state-of-the-art system in [35]. We can conclude that the multilayer photonic RC design is scalable in terms of power consumption.

Figure 2-6 Power Consumption For MReC Architecture Variations.

#### 2.8. Summary

In this chapter, we demonstrate MReC, novel multilayer photonic RC architecture for large-scale classification and prediction tasks. Each layer of the proposed architecture comprises of an MZI based nonlinearity and fiber optic delay line to emulate reservoir computing. We synthesize the proposed multilayer design using a standard photonic CAD tool called IPKISS [38] and execute three well-known classification benchmarks and one widely used prediction benchmark to demonstrate: (1) up to 26.8% reduction in prediction error rate when single-layer MReC is compared with state-of-the-art single-layer photonic RC architecture [34]; (2) up to 50% reduction in prediction error rate when 4-layer MReC is compared with state-of-the-art design and (4) up to 34.21% improvement in power

consumption compared to best reported result [33]. These improvements in MReC come at a cost of 12% area overhead.

The use of passive components in MReC allow it for a low power approach in photonic paradigm in addition to bandwidth advantages [56].

#

In the era of big data, large scale classification and prediction problems pose new challenges that the traditional Von-Neumann architecture struggles to address. This calls for implementation of new computational paradigms. Photonic reservoir computing is a promising paradigm for large-scale classification and prediction problems. Reservoir Computing (RC) has three layers: the input layer, reservoir layer and output layer. The reservoir layer is a random interconnected network of neurons that is independent of the task being performed using RC. This enables a particular reservoir to be used for multiple tasks, as only the output layer needs to be trained. The independent nature of reservoir layer provides an opportunity for parallel processing of multiple tasks at the same time. Unfortunately, the optoelectronic architectures for RC in literature do not exploit this capability. Therefore, in this chapter, we propose a multi-layer opto-electronic hardware architecture for parallel RC. Our architecture employs time division multiplexing to perform jobs in parallel.

#### 3.1. Motivation

Reservoir Computing (RC) has emerged as a promising candidate to provide reduced training time with similar accuracy as that of deep RNN [57]. RC is a subset of

<sup>&</sup>lt;sup>2</sup> adapted with permission from Hasnain, Syed Ali, Dharanidhar Dang, and Rabi Mahapatra. "Multilayer photonic reservoir computing architecture using time division multiplexing for parallel computation." Optoelectronic Devices and Integration IX. Vol. 11547. International Society for Optics and Photonics, 2020.

RNN. Like RNN, it also has two stages: feature extractor and feature classifier. However, unlike RNN, in RC the weights of feature extractor stage are randomly generated and remain fixed. Only the weights of feature classifier stage are trained to fine tune the output. As we know, RC has an input layer, a reservoir layer and an output layer. The reservoir layer comprises of hidden layers of artificial neurons whose weights were randomly generated. This makes the reservoir layer a generic computing tool, which is independent of the task being performed using RC. In theory, a single reservoir can therefore be used to perform multiple tasks [58].

#### 3.2. Related Work

Several studies have argued that RC concept is similar to the workings of a brain, where an external stimulus excites the internal states of network and processes information[59, 25, 60]. Furthermore, the reservoir section of RC is independent of task being performed. This means that multiple tasks can use the same reservoir with a different readout layer for each task. A reservoir can be considered as a generic computation tool that is task independent. As a result, several tasks can be performed in parallel. As an example, recently, it has been shown that the same reservoir can be used for speech recognition as well as speaker recognition[26].

However, RC uses many non-linear nodes in its reservoir layer, hence the hardware implementation of RC using traditional approach has proved to be challenging[28]. To solve this challenge, the delayed feedback reservoir (DFR) model has emerged has a potential solution. In this model, only one non-linear node is employed along with a delay line[60, 61]. The non-linear node coupled with a delay line forms the reservoir. In this

approach there are many virtual neurons, and the single non-linear element is referred to as a node. An implementation based on optoelectronic components is ideally suited for RC as photonic components like Mach Zehnder Interferometer (MZI) have a nonlinear response and a delay line can provide delayed feedback. Following the DFR model, several silicon photonics based single layer RC implementations have been presented in the literature [33, 34, 35]. These single layer silicon photonic implementations have shown promising results with improvements in speed of up to 100x. However, the accuracy of these implementations is lower compared to RNN approaches. Intuitively, a multi-layer RC approach would improve the accuracy of RC system similar to deep neural network. Software implementation of multi-layer RC has indeed demonstrated that it can achieve identical accuracy as compared to RNN implementations at the expense of large execution time[37, 36]. Encouraged by these results, researchers have also proposed a hardware implementation of multi-layer RC that has shown superior performance to single layer systems[62]. However, none of these architectures demonstrate parallel processing of independent tasks. The reservoir layer has the capability to process multiple tasks in parallel and therefore an architecture for parallel RC can be designed.

#### 3.3. Contribution

The major contributions of this chapter are as follows:

We propose a new time-shared multi-layer photonic architecture for RC to perform tasks in parallel.

- 2. Through experiments we show that our architecture can outperform some of the leading single layer architectures by up to 90% for NARMA task while performing analog speech recognition in parallel.

- 3. We also show that our proposed architecture closely matches the performance of leading multi-layer photonic RC architecture<sup>14</sup> with an increased error of 8% only due to parallel processing.

- 4. It is also shown that the proposed high-speed architecture has a power consumption of  $\sim$ 50W for a 4-layer network.

# 3.4. Time Shared Multilayer Photonic Architecture

The RC designs execute one input data stream per system. However, parallel computation with different data streams or tasks would be extremely beneficial when considering big data computing. One can argue that several independent tasks can be simultaneously executed using separate similar RC systems in parallel. However, such a system will have high power and area overhead. Any attempt to run multiple tasks in parallel on a single RC system has its own challenges as well. It is obvious that parallel computation of multiple photonic data streams on a single RC system will result in crosstalk and hence performance degradation. This is obviously not desirable.

On the other hand, if we carefully study the single node photonic computing model, such as the one shown in figure 3-1, we notice that the internal states that

Figure 3-1 Single Node Photonic Model With Internal States Corresponding To Virtual Neurons

correspond to virtual neurons can be related to different tasks. The reservoir will simply process them and provide excited states as input to read out layers.

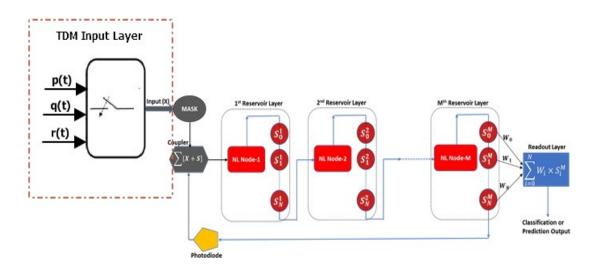

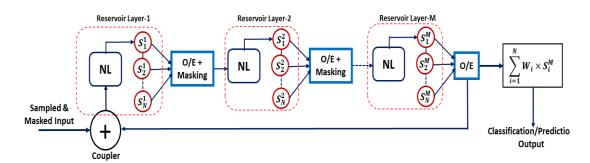

Therefore, we investigate the design for a new photonic RC system that overcomes the multitasking demands of big data applications and also satisfies the aforementioned technological needs (power, area, and crosstalk). This chapter introduces a time-multiplexed RC system based on a multilayer RC system in which time-division-multiplexing (TDM) is integrated with the input layer to execute multiple tasks in parallel[63, 64]. Fig 3-2., reprinted with permission from [65], shows the proposed architecture. The details of the architecture are as follows.

# 3.4.1. TDM Integrated Input Layer

In the input layer of proposed architecture, multiple inputs are first sampled using a a sample & hold (S/H) circuit. The S/H circuit is controlled using an electronic control block that runs a round robin algorithm giving each input a sampling time. The sampling converts a continuous signal x(t) to a discrete time signal p(n).

Figure 3-2 Time Shared Multi-Layer Photonic Reservoir Computing Architecture

Let  $p_l(n)$  represent the N input signal, where  $1 \le l \le P$ . The input layer obtains a masked version of input signals by multiplying the signals with a random masking signal m(n). The masking signal is randomly chosen from [-1,+1]. The result of this multiplication is a masked input  $p_l(n)$  which drives the reservoir layer in the 'reservoir computing segment'.

The random masking function is analogous of the random weights that are applied in the hidden layers. They help in generating the randomness and a dynamical response of the reservoir. The coupler unit, combines any past state with our current state and serves

as a feedback mechanism. This is analogous to the internal memory of an RNN. The S/H circuit runs a round robin algorithm, sampling each task for a certain period of time, before moving on to sample the next task.

# 3.4.2. Reservoir Layer