# LOW NOISE, JITTER TOLERANT CONTINUOUS-TIME SIGMA-DELTA MODULATOR

A Dissertation

by

#### NEGAR RASHIDI

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

Chair of Committee, Jose Silva-Martinez Committee Members, Aydin Karsilayan

> Peng Li Ben Zoghi

Head of Department, Miroslav Begovic

December 2016

Major Subject: Electrical Engineering

Copyright 2016 Negar Rashidi

#### ABSTRACT

The demand for higher data rates in receivers with carrier aggregation (CA) such as LTE, increases the efforts to integrate large number of wireless services into single receiving path, so it needs to digitize the signal in intermediate or high frequencies. It relaxes most of the front-end blocks but makes the design of ADC very challenging. Solving the bottleneck associated with ADC in receiver architecture is a major focus of many ongoing researches. Recently, continuous time Sigma-Delta analog-to-digital converters (ADCs) are getting more attention due to their inherent filtering properties, lower power consumption and wider input bandwidth. But, it suffers from several non-idealities such as clock jitter and ELD which decrease the ADC performance.

This dissertation presents two projects that address  $CT-\Sigma\Delta$  modulator nonidealities. One of the projects is a  $CT-\Sigma\Delta$  modulator with 10.9 Effective Number of Bits (ENOB) with Gradient Descent (GD) based calibration technique. The GD algorithm is used to extract loop gain transfer function coefficients. A quantization noise reduction technique is then employed to improve the Signal to Quantization Noise Ratio (SQNR) of the modulator using a 7-bit embedded quantizer. An analog fast path feedback topology is proposed which uses an analog differentiator in order to compensate excess loop delay. This approach relaxes the requirements of the amplifier placed in front of the quantizer. The modulator is implemented using a third order loop filter with a feed-forward compensation paths and a 3-bit quantizer in the feedback loop. In order to save power and improve loop linearity a two-stage class-AB amplifier is developed. The prototype modulator is implemented in 0.13 $\mu$ m CMOS technology, which achieves peak Signal to Noise and Distortion Ratio (SNDR) of 67.5dB while consuming total power of 8.5-mW under a 1.2V supply with an over sampling ratio of 10 at 300MHz sampling frequency. The prototype achieves Walden's Figure of Merit (FoM) of 146 f J/step.

The second project addresses clock jitter non-ideality in Continuous Time Sigma Delta modulators (CT- $\Sigma\Delta$ M), the modulator suffer from performance degradation due to uncertainty in timing of clock at digital-to-analog converter (DAC). This thesis proposes to split the loop filter into two parts, analog and digital part to reduce the sensitivity of feedback DAC to clock jitter. By using the digital firstorder filter after the quantizer, the effect of clock jitter is reduced without changing signal transfer function (STF). On the other hand, as one pole of the loop filter is implemented digitally, the power and area are reduced by minimizing active analog elements. Moreover, having more digital blocks in the loop of CT- $\Sigma\Delta M$  makes it less sensitive to process, voltage, and temperature variations. We also propose the use of a single DAC with a current divider to implement feedback coefficients instead of two DACs to decrease area and clock routing. The prototype is implemented in TSMC 40 nm technology and occupies  $0.06 \text{ } mm^2$  area; the proposed solution consumes 6.9mW, and operates at 500 MS/s. In a 10 MHz bandwidth, the measured dynamic range (DR), peak signal-to-noise-ratio (SNR), and peak signal-to-noise and distortion (SNDR) ratios in presence of 4.5 ps RMS clock jitter (0.22% clock period) are 75 dB, 68 dB, and 67 dB, respectively. The proposed structure is 10 dB more tolerant to clock jitter when compared to the conventional  $\Sigma\Delta M$  design for similar loop filter.

# DEDICATION

To my lifelong love and best friend, Ali

To my precious and devoted parents, Farideh and Gholamreza

#### ACKNOWLEDGEMENTS

All my work reflects the relationships with many inspiring and gracious people that I met during these years in school. I would like to extend my thanks to all their invaluable support.

First, I would like to take this opportunity to express my deepest gratitude to Dr. Jose Silva-Martinez, my dissertation chair of committee, my adviser, and a truly great teacher. His patience, leadership skills, wisdom, and warm heart carried me through this challenging process.

I also would like to express my heartfelt gratitude to Dr. Ben Zoghi for his kindness, great advice and his mentorship. Without his support and encouragement I could not even start this journey. Thank you very much!

I also would like to express my gratitude to the members of my dissertation committee, Dr. Aydin Karsilayan, Dr. Peng Li and Dr. Sebastian Hoyos for their great advice and feedback throughout this journey.

A special note of appreciation goes to Dr. Jay Porter for his advice, continual encouragement, and confidence in me. It has been a great honor to teach his course for one year on his behalf.

I am grateful to Dr. Shahin Mehdizad who gave me a lot of precious advice during my internship at Qualcomm and for his valuable discussions. I would like to thank Bharadvaj Bhamidipati, Dr. Jenny Kuo and Dr. Andrew Weil from Qulacomm for sharing their expertise and our fruitful discussions.

I would like to extend my gratitude to my friends Suraj and Judy. You have been my emotional support and compassionate friends. I was lucky to have so many great friends through these years. Among them, I would like to thank Alexander Edward and Carlos Briseno for the great moments we had together during chip design, implementation and test. I would like to thank Ehsan Zhian for all his help and all the discussions that we had when I got stuck. I would like to thank my mentors at TAMU, Ramy Saad and Yung-Chung Lo for their great mentorship.

I would like to thank my friends Hajir Hedayati, Masoud Moslehi, Samira Nourbakhsh, MohammadHossein Naderi, Amirhossein Tamjidi, Somaieh Bahrami, Parisa Gandomkar, Amin Hassanzadeh, Faryaneh Poursardar, Elif Kaya who have contributed to make these years very enjoyable; these friendships are a precious legacy of my experience at Texas A&M University.

I would like to thank all other friends and colleagues at Texas A&M University who made these years memorable, including Mohan Gedada, CJ Park, Parya Sepidband, Amir Tofighi, Fernando Lavalle, Fan Gui and all my friends in the Analog and Mixed Signal group.

I would also like to thank members of the Department of Electrical and Computer Engineering, in particular Ms. Tammy Carda and Ms. Ella Gallagher, and member of the Department of Engineering Technology, Ms. Emma Carrigan, for their constant help and support.

I am grateful to my mother Farideh and to my father Gholamreza for their dedication and unconditional love. I am thankful to my lovely sister Tala and brother Ata, your words of encouragement kept me always going.

Finally, I would like to thank my best friend and my love, Ali, for always being on my side with his love and for giving me the encouragement and motivation to make it through all the hard times during these years. I could not make this journey without his patience and sacrifices he has made in these years.

## NOMENCLATURE

ADC Analog to Digital Converter

DAC Digital to Analog Converter

$CT-\Sigma\Delta M$  Continuous Time Sigma Delta modulators

STF Signal Transfer Function

NTF Noise Transfer Function

DR Dynamic Range

SNR Signal to Noise Ratio

SNDR Signal to Noise and Distortion Ratio

GD Gradient Descent

FoM Figure of Merit

OOB Out Of Band

MASH Multi-stAge noise SHaping

PLL Phase Locked Loop

PN Phase-Noise

OSR Over Sampling Ratio

OBG Out of Band Gain

OpAmp Operational Amplifier

ELD Excess Loop Delay

# TABLE OF CONTENTS

|     |                   | Pa                                                              | age                        |

|-----|-------------------|-----------------------------------------------------------------|----------------------------|

| AB  | STR               | ACT                                                             | ii                         |

| DE  | DIC               | ATION                                                           | iv                         |

| AC  | CKNC              | OWLEDGEMENTS                                                    | v                          |

| NC  | )MEI              | NCLATURE                                                        | vii                        |

| ТА  | BLE               | OF CONTENTS                                                     | viii                       |

| LIS | ST O              | F FIGURES                                                       | X                          |

| LIS | ST O              | F TABLES                                                        | xiii                       |

| 1.  | INT               | RODUCTION: THE IMPORTANCE OF RESEARCH                           | 1                          |

|     | 1.1<br>1.2<br>1.3 | Motivation for high resolution, low power ADC                   | 1<br>1<br>2                |

| 2.  | OVI               | ERSAMPLING ADC                                                  | 3                          |

|     | 2.1<br>2.2<br>2.3 | Nyquist rate ADC vs oversampling ADC                            | 3<br>6<br>8<br>8<br>10     |

|     | 2.4               | , 1                                                             | 14<br>15<br>15<br>18<br>21 |

| 3.  |                   | ADIENT DESCENT BASED CALIBRATION FOR MASH 3-0 SIGMATA MODULATOR | 25                         |

|     |                   | Introduction                                                    | 25                         |

| 3.2                             | System Architecture                                                  |

|---------------------------------|----------------------------------------------------------------------|

|                                 | 3.2.1 Transfer function and stability                                |

|                                 | 3.2.2 Quantization noise reduction technique using a high resolution |

|                                 | quantizer                                                            |

| 3.3                             | Circuit implementation                                               |

|                                 | 3.3.1 Linear class AB amplifier                                      |

|                                 | 3.3.2 Mixed signal fast path employing analog differentiator         |

|                                 | 3.3.3 7-Bit quantizer                                                |

|                                 | 3.3.4 Current steering DAC                                           |

| 3.4                             | Digital calibration                                                  |

|                                 | 3.4.1 The generic gradient descent method                            |

|                                 | 3.4.2 Matching analog loop filter and digital filter                 |

| 3.5                             | ADC realization                                                      |

| 3.6                             | Conclusion                                                           |

| 4.1                             | W POWER, JITTER TOLERANT SIGMA-DELTA MODULATOR Introduction          |

|                                 |                                                                      |

|                                 | Introduction                                                         |

| 4.1                             | Introduction                                                         |

| 4.1                             | Introduction                                                         |

| 4.1                             | Introduction                                                         |

| 4.1<br>4.2                      | Introduction                                                         |

| 4.1<br>4.2<br>4.3               | Introduction                                                         |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5 | Introduction                                                         |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5 | Introduction                                                         |

# LIST OF FIGURES

| TIGURE                                                                                                                   | Page |

|--------------------------------------------------------------------------------------------------------------------------|------|

| 2.1 Bandwidth requirment [2] (a) Nyquist ADC , (b) Oversampling AD                                                       | C 4  |

| 2.2 Block diagram of a oversampled ADC                                                                                   | 5    |

| 2.3 DT and CT modulator and general STF and NTF                                                                          | 6    |

| 2.4 DT and CT equivalence                                                                                                | 7    |

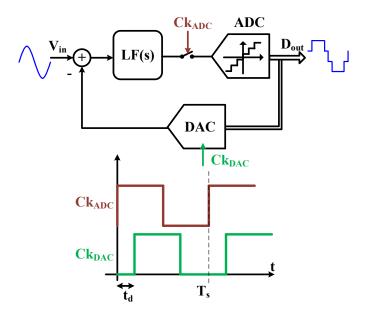

| 2.5 ELD in CT- $\Sigma\Delta$ modulator                                                                                  | 9    |

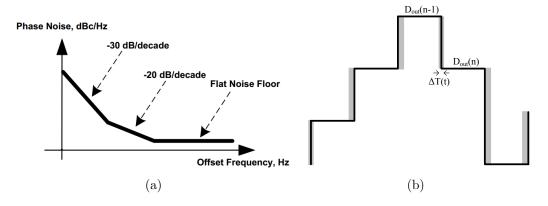

| 2.6 (a) Clock phase noise [28], (b) effect of jitter in DAC signal, and the error due to jitter                          |      |

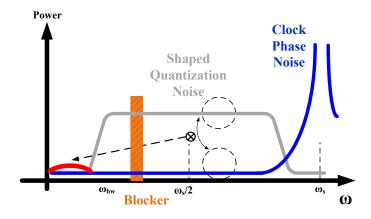

| 2.7 PN and quantization noise modulation in DAC                                                                          | 12   |

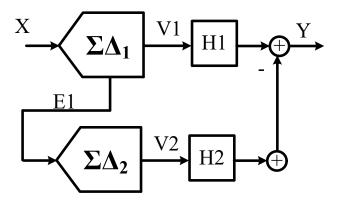

| 2.8 2-stage MASH                                                                                                         | 17   |

| 2.9 Insertion of an additional feedback path around quantizer to compensate ELD [39]                                     |      |

| 2.10 Insertion of auxiliary digital path after quantizer [39]                                                            | 20   |

| 2.11 Using digital differentiation to compensate ELD [47]                                                                | 21   |

| 2.12 Using FIR-DAC to reduce sensitivity to jitter [63]                                                                  | 22   |

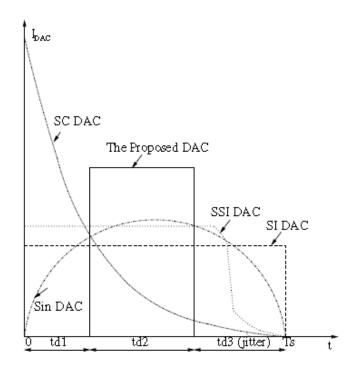

| 2.13 Different DAC shapes to reduce clock jitter effect [9]                                                              | 23   |

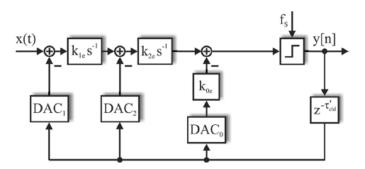

| 3.1 Proposed continuous-time Sigma-Delta modulator                                                                       | 29   |

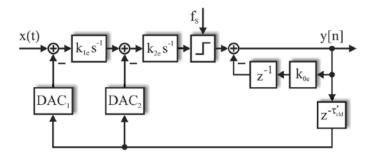

| 3.2 Block diagram of the proposed noise reduction technique                                                              | 30   |

| 3.3 Class-AB amplifier schematic                                                                                         | 32   |

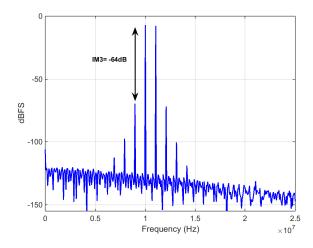

| 3.4 2 tone test for linearity simulation of first lossy integrator with rm output amplitude of -4dBFS at 10MHz and 11MHz |      |

| 3.5  | (a) Fast path and differentiator circuit (b) transient response of different nodes (c) schematic simulation                                           | 36 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.6  | Excess loop delay variation 0-100% $T_s$ (a) root-locus of NTF(z) poles including mixed signal fast path (b) SNDR vs ELD variation                    | 38 |

| 3.7  | Simplified two step, 7 bit quantizer [6]                                                                                                              | 39 |

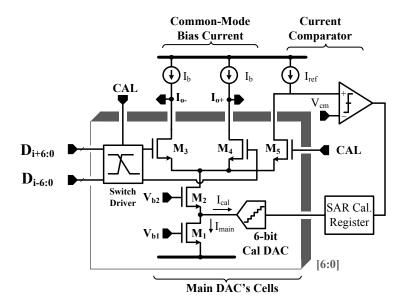

| 3.8  | Simplified main DAC schematic highlighting unit current source cell with fully digital on-chip calibration circuitry                                  | 40 |

| 3.9  | Different phases of proposed method                                                                                                                   | 41 |

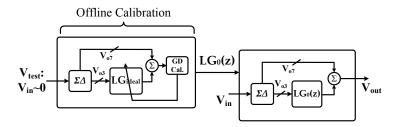

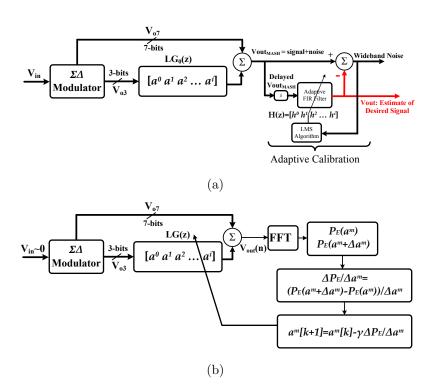

| 3.10 | Digital Calibration (a) LMS based adaptive noise cancellation technique [32, 77], (b) proposed FFT based Gradient Descent technique for offline phase | 43 |

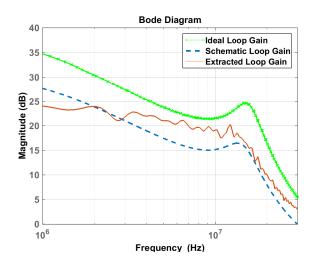

| 3.11 | Ideal loop gain and loop gain from schematic versus extracted one .                                                                                   | 46 |

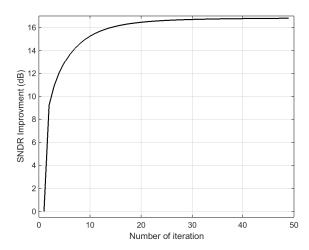

| 3.12 | Settlement of algorithm after 50 iterations                                                                                                           | 47 |

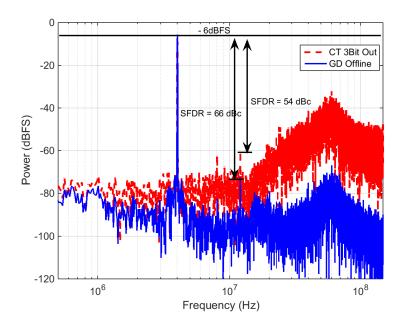

| 3.13 | Experimental results: spectrum of the 3-bit output, and cancellation after convergence, input 4 MHz with amplitude of -6 dBFS                         | 48 |

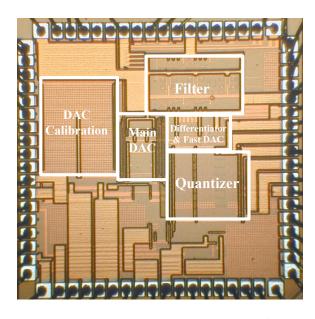

| 3.14 | Die micrograph of chip, active area is $1.1mm^2$ including clock generator and CML buffers                                                            | 49 |

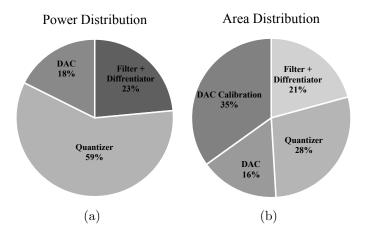

| 3.15 | (a) Power distribution of modulator, overall power 8.5 mW, (b) area distribution of modulator, overall area $1.1~mm^2~\dots~\dots$ .                  | 49 |

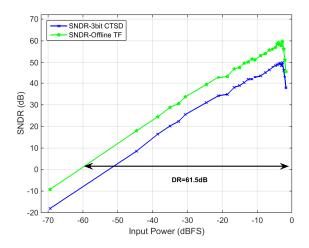

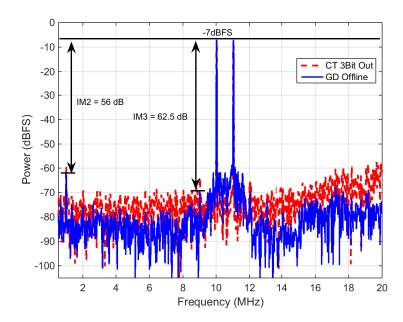

| 3.16 | Experimental results: SNDR vs input power for 3-bit $\Sigma\Delta$ loop and output of the gradient descent algorithm (input frequency 4MHz)           | 50 |

| 3.17 | Spectrum of outputs, two tone test, input at 10MHz and 11MHz with amplitude of -7dBFS, compensated using Gradient Descent                             | 51 |

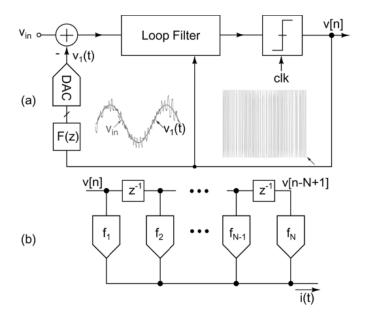

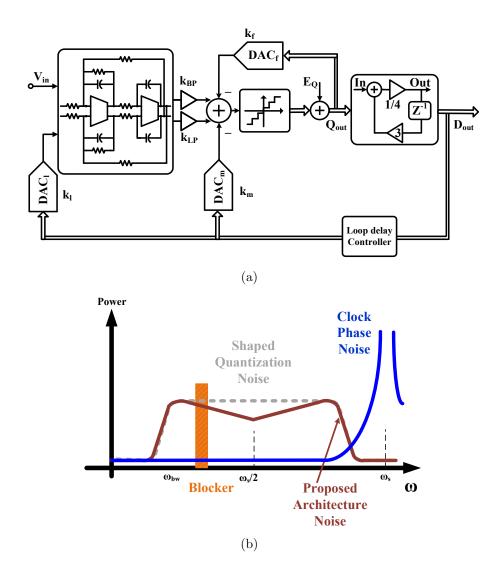

| 4.1  | (a) Block diagram of proposed CT- $\Sigma\Delta M$ and (b) clock jitter and out-of-band noise modulation for conventional and proposed architecture   | 55 |

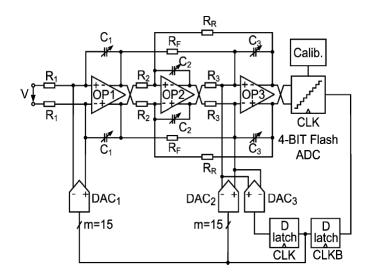

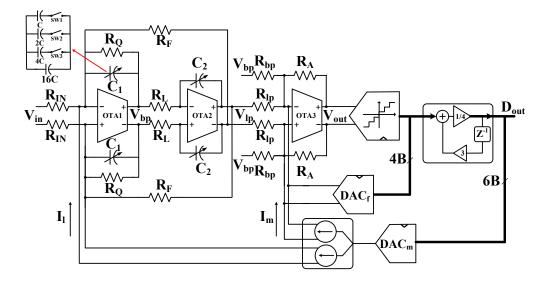

| 4.2  | Schematic of proposed CT- $\Sigma\Delta$                                                                                                              | 57 |

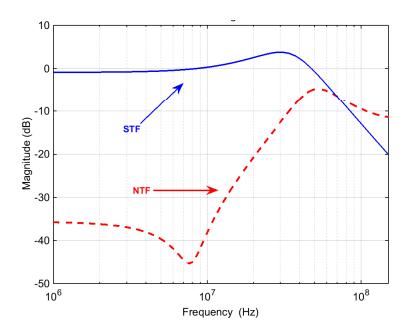

| 4.3  | STF and NTF of proposed system                                                                                                                        | 58 |

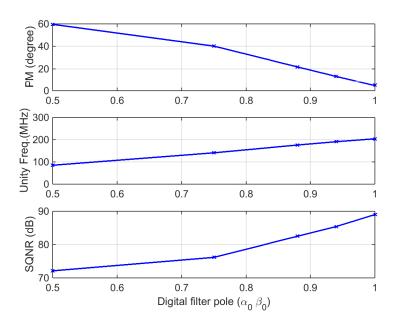

| 4.4  | Loop performance (phase margin, loop unity gain frequency and SQNR) vs $\alpha_0\beta_0$ of digital low pass filter                                   | 59 |

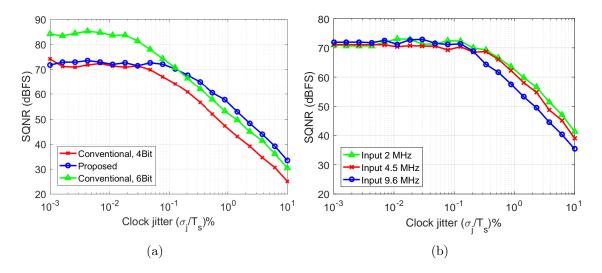

| 4.5  | Simulation results (a) SQNR for both conventional and proposed CT- $\Sigma\Delta M$ as function of clock jitter; input signal power is -6 dBFS at 9.6 MHz and (b) SQNR variation for different frequencies; input power is -6 dBFS                                                                                       | 61 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

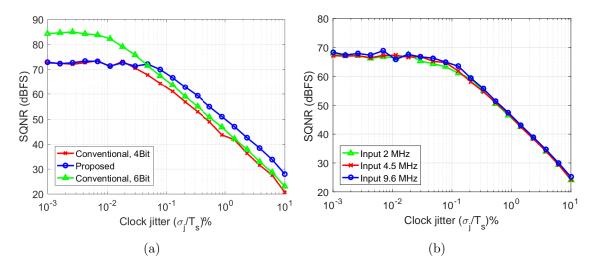

| 4.6  | Simulation results (a) SQNR for conventional and proposed CT- $\Sigma\Delta M$ as function of clock jitter in presence of -20 dBFS blocker at 55 MHz; input signal power is -6 dBFS at 9.6 MHz and (b) SQNR variation for different input frequencies in presence of -10 dBFS blocker at 20 MHz; input power is -10 dBFS | 62 |

| 4.7  | Fully differential feed-forward compensation OTA                                                                                                                                                                                                                                                                         | 64 |

| 4.8  | Digital filter schematic                                                                                                                                                                                                                                                                                                 | 66 |

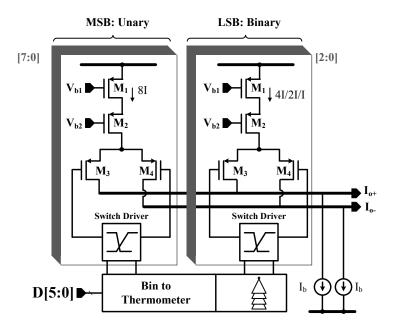

| 4.9  | Segmented DAC schematic                                                                                                                                                                                                                                                                                                  | 67 |

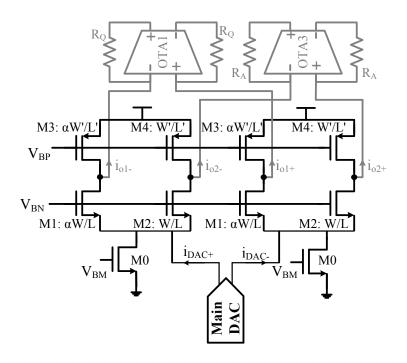

| 4.10 | Current divider schematic                                                                                                                                                                                                                                                                                                | 69 |

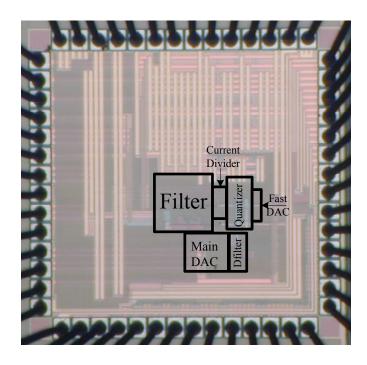

| 4.11 | Die micrograph of chip                                                                                                                                                                                                                                                                                                   | 71 |

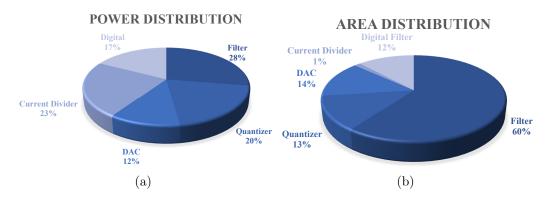

| 4.12 | (a) Power distribution of modulator with overall power of 6.9 mW and (b) area distribution of modulator with overall area of 0.06 $mm^2$                                                                                                                                                                                 | 72 |

| 4.13 | (a) Input clock jitter of PSG Vector Signal Generator (b) input clock jitter of Clock Generator Development Kit                                                                                                                                                                                                          | 72 |

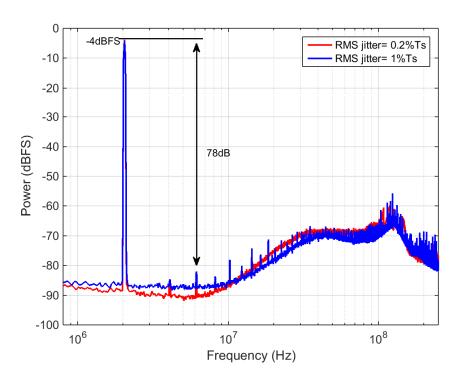

| 4.14 | Measured spectrum of CT- $\Sigma\Delta$ for input signal of -4 dBFS at 2 MHz, for the cases peak-to-peak clock jitter is 215 ps (RMS jitter = 1% Ts) and 120 ps (RMS jitter = 0.22% Ts)                                                                                                                                  | 74 |

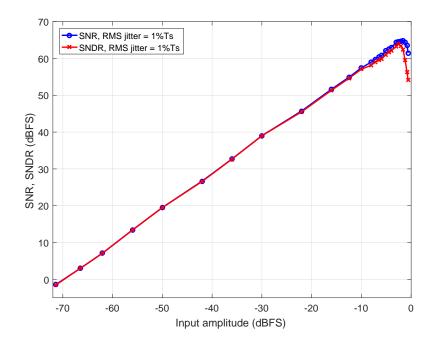

| 4.15 | Measured SNR and SNDR vs input power; input frequency is 2 MHz                                                                                                                                                                                                                                                           | 74 |

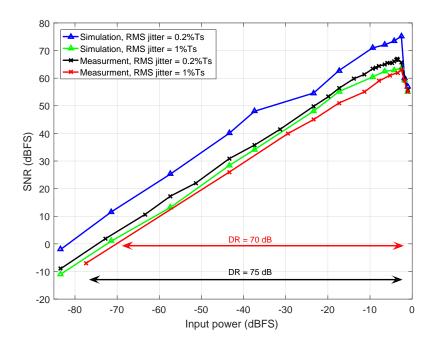

| 4.16 | SNR vs input power with input of 4 MHz                                                                                                                                                                                                                                                                                   | 75 |

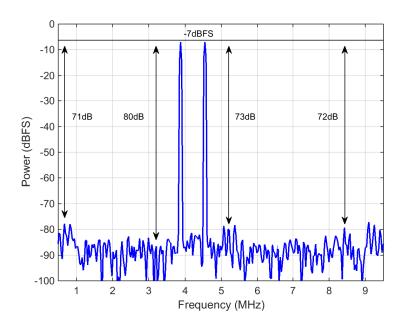

| 4.17 | Measured two-tone test with RMS power of -4 dBFS and frequencies of 3.8 MHz and 4.5 MHz with RMS clock jitter of 20 ps                                                                                                                                                                                                   | 76 |

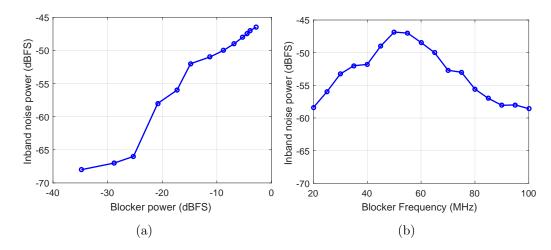

| 4.18 | Measured integrated in-band noise with RMS jitter of 20 ps, input tone -15 dBFS at 2 MHz (a) sweeping amplitude of 40 MHz blocker (b) sweeping blocker frequency, inband signal -15 dBFS at 2 MHz $$ .                                                                                                                   | 77 |

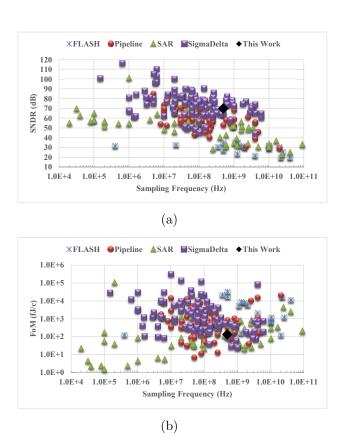

| 4.19 | Comparison of the proposed system with ISSCC and VLSI papers [49] (a) SNDR vs sampling frequency (b) FoM vs sampling frequency                                                                                                                                                                                           | 78 |

# LIST OF TABLES

| ΓABLE |                                                                                        | Page |

|-------|----------------------------------------------------------------------------------------|------|

| 2.1   | Continuous time Sigma-Delta modulator advantages vs disadvantages                      | 8    |

| 3.1   | System level specification                                                             | 27   |

| 3.2   | Passive element values                                                                 | 29   |

| 3.3   | Comparison of Class-AB vs Class-A output stage                                         | 34   |

| 3.4   | Differentiator circuit parameters                                                      | 35   |

| 3.5   | Performance comparison, $10\text{MHz} \leqslant \text{BW} \leqslant 25\text{MHz}$      | 52   |

| 4.1   | Loop filter parameters                                                                 | 62   |

| 4.2   | Passive components                                                                     | 63   |

|       | Qualitative comparison of proposed modulator vs conventional 4-Bit and 6-Bit           | 63   |

|       | OTA specification including first integrator's resistors and capacitor as a load       | 64   |

| 4.5   | Performance comparison, $2010 \leqslant Year$ , $10MHz \leqslant BW \leqslant 25MHz$ . | 78   |

#### 1. INTRODUCTION: THE IMPORTANCE OF RESEARCH

In this chapter we discuss the motivation for high resolution, low power ADCs, research contribution and dissertation organization.

#### 1.1 Motivation for high resolution, low power ADC

With the tremendous developments on wireless communications, different wireless services and standards are proposed each year, such as GSM, CDMA, UMTS and most recently 4G and 5G. Wireless communication is rapidly advancing and new wireless applications emerges. More recent application is Internet of Things(IoT), which combines all the wireless standards. Each standards has special signal power, signal bandwidth, signal frequency and coding methods, so the required hardware for each one should be unique and challenging. As a result, integrating different wireless in a single chip and to make them work efficiently for different standards is challenging trend in semiconductor industry. The software-defined radio receiver architecture is a potential candidate to realize the multi-standard receiver. With no DC offset and the relaxed image problem, this architecture eases the front-end circuit specifications. However, the requirements of large bandwidth (10MHz for video communication), high operational performance and trend to move ADC as close to antenna as possible make the ADC design a challenging problem in today's technology. And among many ADCs CT- $\Sigma\Delta$  is more suitable due to their oversampling, dynamic range, power consumption and trading speed for resolution.

## 1.2 Research contribution, technical challenges associated with ADC

In this work the problem of designing low power, high resolution CT- $\Sigma\Delta$  ADCs has been addressed. The solution to some of the non-idealities including ELD and jit-

ter is investigated. Two CT- $\Sigma\Delta$  modulators are proposed, implemented and tested in this thesis. Quantization noise reduction technique is proposed and several common issues of the modulator are presented and they resolved by use of the new proposed modulators.

## 1.3 Dissertation organization

The dissertation is organized as follows: Chapter 2 briefly describes the difference between Nyquist and oversampling ADC, and fundamental of CT- $\Sigma\Delta$ M, and non-idealities associated with that. Chapter 3 propose a CT- $\Sigma\Delta$ M to solve problem of ELD, and noise calibration. Chapter 4 presents the proposed modulator to reduce the effect of clock jitter in CT- $\Sigma\Delta$  ADC. Chapter 5 concludes the thesis and discusses the future work.

#### 2. OVERSAMPLING ADC

Among different kinds of ADC, CT- $\Sigma\Delta M$  is getting popularity due to its inherent properties. In this section we review oversampling ADCs and specially CT- $\Sigma\Delta M$ . Also, we discuss the common non-idealities associated with it, and we review the literature about solving the non-idealities issues in CT $\Sigma\Delta M$ .

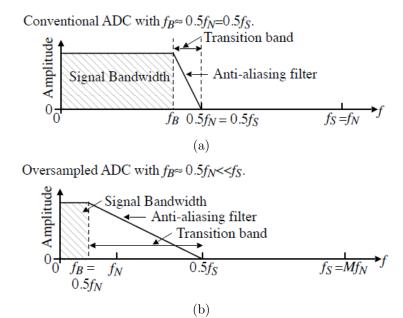

# 2.1 Nyquist rate ADC vs oversampling ADC

According to sampling theory in order to avoid aliasing, sampling frequency  $(f_s)$  should be at least twice signal bandwidth  $(f_{BW})$ :  $f_s > 2f_{BW}$ . In Nyquist ADCs which the spectrum is shown in Fig 2.1(a)  $f_{BW}$  is as close to  $0.5f_s$  as possible. Assuming quantization noise as white noise, the total quantization noise power and spectral density of quantization noise are [52]:

$$\sigma_e^2 = \int_{-\infty}^{\infty} e^2 p df_e de = \frac{\Delta^2}{12}, \quad S_e(\omega) = \frac{\Delta^2}{12} \cdot \frac{1}{f_s}$$

(2.1)

where  $\Delta$  is quantization step  $(\frac{FS}{2^N})$ ,

If the sampling frequency of ADC is much larger than band-width  $(f_s \gg 2f_{BW})$ , the ADC becomes oversampling ADC. One of the benefit of oversampling ADC is that the anti-alias filter implementation becomes easier as its transient band increase (Fig. 2.1(b)). Moreover, as total quantization noise power is constant and independent from sampling frequency, by increasing sampling frequency the spectral density of quantization noise decrease, and as a result in-band quantization noise reduces. So, by using a low-pass filter after ADC which is called decimation filter, the out of band quantization noise will be filtered out. In other words it trades precision for speed.

Figure 2.1: Bandwidth requirment [2] (a) Nyquist ADC, (b) Oversampling ADC

The integrated inband quantization noise for oversampling ADC is [52]:

$$IBN_{OSR} = \frac{1}{f_s} \int_{-f_{BW}}^{f_{BW}} \sigma_e^2 df = \frac{\Delta^2}{12} \frac{2f_{BW}}{f_s} = \frac{\Delta^2}{12} \frac{1}{OSR}$$

(2.2)

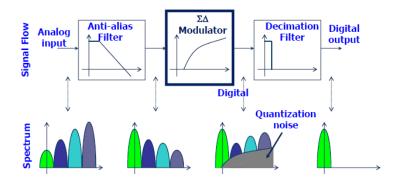

The block diagram of a oversampled ADC is shown in Fig 2.2. It consist of a low-pass anti-alias filter to prevent sampled signal from aliasing to in-band, a modulator which convert analog signal to digital, and a decimator to downsample the high frequency output to lower frequency outputs and finally a digital low pass filter is needed to remove high frequency noise and preserve input signal.

An oversampling converter uses a noise-shaping modulator to reduce the in-band quantization noise to achieve higher degree of resolution. Noise-shaping modulator ( $\Sigma\Delta$  modulator) introduce a feedback path to further increase the accuracy. The general form of discrete time (DT) and continuous time (CT) modulator are shown

Figure 2.2: Block diagram of a oversampled ADC

in Fig. 2.3. The Signal Transfer Function (STF) and Noise Transfer Function (NTF) euqation for the general system is shown in Eq. 2.3:

$$STF = \frac{D_{out}}{V_{in}} = \frac{LF}{1 + LF}$$

$$NTF = \frac{D_{out}}{E_Q} = \frac{1}{1 + LF}$$

(2.3)

If LF is chosen to be large in band, the STF will be very close to 1 and NTF will be very small in band, so the modulator will pass signal and rejects the quantization noise. The integrated inband quantization noise in presence of  $L^{th}$  order noise shaping  $(NTF(z) = |1 - z^{-1}|^L)$  can be computed as follows:

$$IBN_{OSR,L} = \frac{1}{f_s} \int_{-f_{BW}}^{f_{BW}} NTF^2 \sigma_e^2 df = \frac{\Delta^2}{12} \frac{\pi^{2L}}{(2L+1)OSR^{2L+1}}$$

(2.4)

here we assumed that  $f_s \gg f_{BW}$ , so  $|1 - z^{-1}|^2 = (2\sin\Omega/2)^2 \approx \Omega^2 = (\frac{2\pi f}{f_s})^2$ . So, the maximum SNR assuming input as a sine wave with amplitude of FS/2 will be:

$$SQNR_{Max}(dB) = 6.02N + 1.76 + 10(2L+1)\log OSR - 10\log \frac{\pi^{2L}}{2L+1}$$

(2.5)

Figure 2.3: DT and CT modulator and general STF and NTF

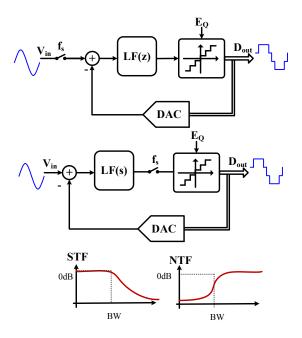

# 2.2 Discrete time vs continuous time $\Sigma\Delta$ modulator

Based on place of sampling the modulator can be discrete-time or continuous time. If sampling takes place at input, it results DT modulator and if it takes place after filter and before quantizer it makes CT modulator.

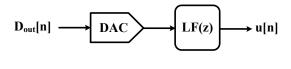

In order to determine the equivalence, in Fig. 2.3 the loop around quantizer is opened and inputs are zeroed, which is shown in Fig. 2.4. A continuous-time modulator would produce the same output bits as the discrete-time modulator if the outputs were equal at the sampling instants, meaning that  $u[n] = u(t)|_{t-nt_s}$ . This would be satisfied if the following condition were satisfied:

$$LF(z) = Z\{L^{-1}[DAC(s).LF(s)]_{t=nT}\}$$

(2.6)

where DAC(s) is the transfer function of the DAC, it can be rectangular, triangular,

$$D_{out}[n] \longrightarrow DAC \longrightarrow LF(s) \xrightarrow{t=nt_s} u[n]$$

Figure 2.4: DT and CT equivalence

quadratic, sine function [52]. In this thesis we used rectangular DAC shape, so we ignore the analysis of the other functions. We assume rectangular pulse of DAC to have magnitude of 1 that lasts from a to b:

$$DAC(t) = \begin{cases} 1 & a < t < b, 0 < a < b \\ 0 & otherwise \end{cases}$$

(2.7)

and the s-domain equivalent of DAC response is:

$$DAC(s) = \frac{e^{-as} - e^{-bs}}{s}$$

(2.8)

For a=0,  $b=t_s$ , this becomes a None-Return-Zero (NRZ) DAC pulse. A Return Zero (RZ) DAC pulse would exist if a=0,  $b=0.5t_s$ . Eq. 2.6 allows the transformation between continuous-time and discrete-time filters, and thus allows an analysis of the effects of non-ideal DAC output pulses to be performed on discrete-time equivalents of continuous-time filters. To find an equivalent DT- $\Sigma\Delta$  modulator for a CT- $\Sigma\Delta$  modulator (and vice versa), a time-domain DT-CT transformation method has to be used. The impulse invariant transformation (IIT) is one such method. To actually perform the transformation, the DAC feedback pulse shape has to be

Table 2.1: Continuous time Sigma-Delta modulator advantages vs disadvantages

| CT Advantages                                      | CT disadvantages                             |

|----------------------------------------------------|----------------------------------------------|

| CT- $\Sigma\Delta$ modulators remove (or relax the | CT filters are much more difficult           |

| requirement) the need for an anti-aliasing         | to design and simulate since DT              |

| filter                                             | filters are simply made up of delays         |

|                                                    | and gain stages in various loops.            |

| The CT operation of the loop filter relaxes        | $CT-\Sigma\Delta$ modulators exhibit several |

| the requirements on the GBW of amplifiers          | non-idealities such as clock jitter          |

| and hence allows the operation at higher           | and excess loop delay                        |

| speeds or lower power consumption                  |                                              |

| The requirements on the sample-and-hold            |                                              |

| (S/H) circuitry are relaxed because the            |                                              |

| sampling is performed after the loop filter        |                                              |

used in Eq. 2.6. There are several references that computed the transformation for different DAC pulse shapes. The use of continuous-time filters provides some improvements over discrete-time filters, while they suffer from some issues. Continuous time advantages and disadvantages are listed in Table 2.1.

#### 2.3 CT- $\Sigma\Delta$ non-ideality

Beside the advantages of CT- $\Sigma\Delta$ , it suffers from some of the non-idealities, in this section we focus on Excess Loop Delay (ELD), clock jitter and effect of OOB blocker.

## 2.3.1 Excess loop delay

Excess loop delay is a constant delay  $t_d = \tau_d T_s$ , between the sampling clock edge and the change in output of DAC which is shown in Fig. 2.5. The sources of ELD include switching time of DAC's output respect to clock edge and input, also the delay between quantizer clocking edge and subsequent latch (which used intentionally to have all the data at output of quantizer at the same time) [52].  $\tau_d$  is dependent on the switching speed of the transistors  $f_t$ , the quantizer clock  $f_s$ , the

number of transistors in the feedback path as well as the loading on each transistor.

Figure 2.5: ELD in CT- $\Sigma\Delta$  modulator

If the maximum switching frequency of transistor is comparable with sampling frequency, ELD's effect on performance is severe. This is becoming more possible nowadays, as desired speed of  $\Sigma\Delta$  increases and it becomes comparable with transistors' maximum switching frequency [13]. In Non-Return-Zero (NRZ) and high speed Return-Zero (RZ) DACs, excess loop delay shifts the DAC's pulse and it is extended to next sampling instant, so it increases the modulator's order and moves the poles of NTF toward unit cycle and exceed the stability boundary for certain excess delay. This issue is becoming more relevant nowadays, as the switching frequency increases to accommodate wider standards such as LTE with aggregated channels.

#### 2.3.2 Clock jitter effect in CT- $\Sigma\Delta$

The CT- $\Sigma\Delta$  modulator is getting more attention in high speed power efficient receivers due to compatibility with CMOS technology and its inherent properties [22], [3]. However, the CT- $\Sigma\Delta$ M is sensitive to clock jitter, and the problem becomes critical by increasing the sampling rate of ADC as high frequency low phase noise Phase Locked Loop (PLL) becomes more challenging to design [10]. Clock jitter is a common problem associated with the uncertainty in the timing of the clock edges caused by the finite phase noise (PN) in the generated clock waveform [61]. The clock signal driving sampling switches suffers from unavoidable clock jitter due to the noise components that accompany the frequency synthesizer. Fig. 2.6 shows the phase noise density in a typical oscillator. In the time-domain, the integrated effect of these noise components convolve with out-of-band noise and high frequency blockers, so folding back part of that information to baseband.

Figure 2.6: (a) Clock phase noise [28], (b) effect of jitter in DAC signal, and the error due to jitter

In data converters, the problem of clock-jitter is a very critical issue and can

significantly deteriorate the achievable SNR. The effect of clock jitter in CT- $\Sigma\Delta$  is divided in two parts, the jitter in forward path and feedback path. The jitter effect in forward path (aperture jitter embedded in the sample and hold) is strongly suppressed by loop filter, similarly to the noise shaping, so it has very little effect in system performance. But, clock jitter in feedback path introduce some error that deteriorates the ADC performance. As main focus of this dissertation is CT- $\Sigma\Delta$  modulators with NRZ rectangular shape DACs, so the jitter analysis of other types DACs are excluded.

Non-return-to-zero DACs are known to be highly sensitive to excess loop delay and also they cause even-order nonlinearities due to mismatch between rise and fall times, in contrast to RZ DAC waveforms. However, they are commonly used in CT modulators due to their simple implementation, relaxed SR requirement on the integrating amplifiers, and lower sensitivity to clock-jitter compared to RZ DACs [61]. Fig. 2.6(b) illustrates the effect of clock jitter in DAC, which can be approximated as [58]:

$$J_{error}(n) = (D_{out}(n) - D_{out}(n-1)) \frac{\Delta T(t)}{T}$$

(2.9)

where  $\Delta T$  is the time uncertainty because of jitter in DAC's clock. So, the frequency domain equivalent of Eq. 2.9 will be as:

$$J_{error}(\omega) = [(1 - z^{-1})D_{out}(\omega)] \otimes J_n(\omega)$$

(2.10)

where the symbol  $\otimes$  means the convolution of the functions. The clock jitter free  $\Sigma\Delta$  feedback signal carries digital data  $(D_{out}(\omega))$ , which includes the in-band desired signal  $(V_{in}(\omega))$ , the high-pass shaped quantization noise coming from the quantizer

$(E_Q(\omega))$ , and the remaining out-of-band thermal noise and blocker signal represented by  $(V_B(\omega))$  leading to:

$$D_{out}(\omega) = (V_{in}(\omega) + V_B(\omega)).STF_c(\omega) + E_Q(\omega).NTF_c(\omega)$$

(2.11)

where,  $STF_c(\omega)$  is the signal transfer function, and  $NTF_c(\omega)$  is the noise transfer function. So, the jitter-induced error signal can be computed as:

$$J_{error}(\omega) = (1 - z^{-1}) \left[ (V_{in}(\omega) + V_B(\omega)) . STF_c(\omega) + E_Q(\omega) . NTF_c(\omega) \right] \otimes J_n(\omega)$$

(2.12)

The in-band signal is shaped by  $1-z^{-1}$  and only the low-frequency in-band clock phase noise convolves with it and fall in-band, so its effect usually is not critical. The error due to out-of-band quantization noise and blockers increases at higher frequencies where the errors convolves with wide-band clock phase noise, and the result of the convolution falls over the desired band and increases the in-band noise level, as illustrated in Fig. 2.7. The SNR degradation due to jitter is well studied

Figure 2.7: PN and quantization noise modulation in DAC

in [11, 12], and the in-band jitter induced noise power is equal to [11]:

$$\sigma_{e_{j,NRZ}}^2 = 4OSR.BW^2.\sigma_{jitter}^2.\left\{\frac{\pi^2}{2}\left(\frac{A}{\frac{f_s}{2f_{in}}}\right)^2 + \frac{V_{FS}^2\sigma_H^2}{3(N-1)^2}\right\}$$

(2.13)

where  $\sigma_H^2 = \frac{1}{2\pi} \int_{-\pi}^{\pi} |NTF(e^{j\omega})(1 - e^{-j\omega})|^2 d\omega$  is RMS value of high pass filtered NTF. So, the SNR will have two parts, one associated with first part of inband jitter induced due to input signal and second part due to noise shaping behavior of CT- $\Sigma\Delta M$ :

$$SNR_{signal} = \frac{OSR}{4\pi^2 f_{in}^2 \sigma_{sitton}^2}$$

(2.14a)

$$SNR_{signal} = \frac{OSR}{4\pi^2 f_{in}^2 \sigma_{jitter}^2}$$

$$SNR_{NTF} = \frac{3(A/V_{FS})^2 (M-1)^2}{8OSR.BW^2 \sigma_{jitter}^2 \sigma_H^2}$$

(2.14a)

According to the Eq. 2.14, if the first term is dominant, SNR can be improved by increasing the OSR, for a given modulator and clock source. But, if the out of band gain of NTF is high, the jitter due to noise shaping behavior of  $\Sigma\Delta M$  will be dominant, and for improving SNR one can increase the quantizer levels; also  $\sigma_H$  (the RMS value of the transfer function  $NTF(z)(1-z^{-1})$ ) can be decreased by reducing the aggressiveness of the noise shaping or optimizing the shape of NTF. So, although increasing the out-of-band gain (OBG) of NTF results in a lower in-band quantization noise, but it results in large jitter. Also, it is interesting that the second term of SNR is inversely proportional to the oversampling ratio. So, if we want to optimize the total jitter-induced noise power by changing the OSR, it is necessary to know first which part of the noise power is dominant.

So, the most critical clock-jitter errors in a CT- $\Sigma\Delta$  modulator are those generated at the feedback path through the outermost DAC [61], and the challenge is to decrease the jitter error due to out-of-band quantization noise and high frequency blockers without demanding very low phase noise clock generator.

#### 2.3.3 Out-Of-Band blocker effect in CT- $\Sigma\Delta$

Moving analog to digital converter toward antenna makes the ADC more complex, and the ADC should be more robust to unwanted signals. Without filtering in receiver front-end, unwanted signals (particularly adjacent channel and alternate channel) propagate through the receiver chain without adequate suppression and hence show up at the ADC input. Moreover, strong out-of-band (OOB) blockers can saturate/overload the ADC building-blocks, degrade the quality of the analog to digital conversion (e.g., due to distortion, insufficient anti-aliasing, and folding OOB noise back over the desired band), and degrade the ADC dynamic-range (DR) [60].

The strength of OOB blocker suppression at a given blocker frequency varies according to the magnitude of STF. Owing to the higher OOB attenuation offered by feedback structure of CT- $\Sigma\Delta$  modulators, large OOB blocking power appearing at the quantizer input can be adequately suppressed and become comparable to the maximum input of the desired channel or even much weaker when they appear at the output of the modulator.

The OOB blocker's most significant effect is on first integrator's output. If slewing happens at the integrator output, the combined waveform including the desired in-band signal and the OOB blockers will experience hard nonlinearity due to nonlinear settling. This will give rise to substantial distortion at the modulator output as well as dramatic increase in the noise floor due to noise. The problem of increased SR requirements caused by OOB blockers is relaxed in later integrators as later stages are shaped by previous ones, also the OOB signals are attenuated as they propagate in the loop filter chain [60].

As shown in Eq. 2.12, the effect of blocker in jitter induced noise is notable. Assuming the modulator output and the clock-jitter are statistically independent of

each other and the clock-jitter is a stationary white process, the integrated in-band jitter-induced noise power (IBJN) due to the blocker  $x_{Blocker}(t) = A_B.cos(\omega_B t)$  in CT- $\Sigma\Delta$  with NRZ DAC is given by [60]:

$$\sigma_{e_{j,Blocker}}^{2} = 8.OSR.BW^{2}.\sigma_{j,rms}^{2}.A_{B}^{2}.|STF(j\omega_{B})|^{2}.sin^{2}(\omega_{B}.\frac{T_{s}}{2})$$

(2.15)

The blocker induced IBJN depends on the power of the blocker component in the feedback signal, determined by the product  $A_{BLK}^2.|STF(j\omega_B)|^2$ . The dependence of the blocker induced IBJN on the blocker frequency is twofold. First, for a given blocker level at the modulator input, the amplitude of the blocker component in the feedback depends on the value of the STF magnitude response at the blocker frequency,  $|STF(j\omega_B)|$ . Second, the term  $sin^2(\omega_{BLK}, \frac{T_s}{2})$  depends on the frequency of the blocker tone,  $\omega_{BLK}$ .

#### 2.4 Literature review for CT- $\Sigma\Delta$ issues

# 2.4.1 State of the art solutions for low noise, low power CT- $\Sigma\Delta$ ADC

The theoretical Signal-to-Quantization Noise Ratio (SQNR) of the L-th order modulator, with an N-bit quantizer and oversampling ratio of OSR is shown in Eq. 2.5. In order to increase the SQNR, we can increase the order of the modulator (L), but higher order modulators are more difficult to stabilize, so usually the order of the system is limited to five. The Out of Band Gain (OBG) of higher order filter is significant and it causes instability because of overloading quantizer.

By increasing the OSR, the SQNR improves, and it relaxes the front-end filter. Designing a filter with relaxed transient band is more power and area efficient. However, if the Band-Width (BW) is kept constant, the maximum frequency is usually limited by technology, and operation in higher speeds leads to high power dissipation.

Moreover, designing the decimation filter with high frequency causes some challenges in digital circuit design.

The other parameter to increase the SQNR is quantizer resolution (N). By increasing N, the quantization noise decreases and therefore, the SQNR will increase. However, the power and area of the quantizer are proportional to the number of bits and higher number of bits in the quantizer requires more stringent requirements on the DAC elements in the feedback path. A flash ADC is a popular candidate for  $CT-\Sigma\Delta$  due to its small delay but it is not suitable for high resolution quantizer because power and area increase 4 times by increasing each bit of the quantizer.

A higher value for OBG tends to push more of the quantization noise from signal band to higher frequencies, but on the other hand it causes the system to be sensitive to clock jitter and become unstable due to the reduction in the maximum stable amplitude. Lee's rule states that OBG < 2 should yield a stable modulator with a binary quantizer [62].

Another way to improve CT- $\Sigma\Delta$  modulator's performance in terms of quantization noise is using cascaded or MASH structure [42], [64]. The original idea of noise canceling technique using cascaded structures was proposed in [43] by using one bit quantizer in loop. A 2-stage MASH is shown in Fig. 2.8. In a cascaded converter, the quantization errors in each stage are processed in the following stage and output of the stages are digitally processed to cancel the quantization errors of all stages except the last one as shown in Eq. 2.16:

$$V1 = STF1.X + NTF1.E1 \tag{2.16a}$$

$$V2 = STF2.E1 + NTF2.E2$$

(2.16b)

$$Y = V1.H1 - V2.H2 (2.16c)$$

$$Y = X.STF1.H1 + E1(NTF1.H1 - STF2.H2) + E2.NTF2.H2$$

(2.16d)

As shown in Eq. 2.17, if NTF1.H1 = STF2.H2, the quantization noise of first stage is canceled and the output will have just the quantization noise of second stage (E2). So, without degrading the modulator stability the quantization noise is decreased.

$$NTF1.H1 = STF2.H2 \Longrightarrow Y = X.STF1.H1 + E2.NTF2.H2$$

(2.17)

However, the matching of digital filter with analog loop filter is essential for geting the best performance of ADC without leakage of quantization errors of previous stages. Moreover, MASH structure usually needs extra loops which needs extra filter, quantizer and DACs.

Figure 2.8: 2-stage MASH

For example [7] proposes a cascaded CT- $\Sigma\Delta$  modulator, in which 5-bit flash ADC is cascaded with a four stage 12-bit pipeleine ADC to reduce the in-band quantization noise. The flash ADC is in feedback loop with low resolution and the pipeline ADC is out of the loop so its latency does not affect the whole stability.

## 2.4.2 State of the art solutions for ELD compensation in CT- $\Sigma\Delta$ ADC

In literature, there are several ways to compensate excess loop delay [39]. In presence of ELD, for the case of RZ DAC, the DT-CT scaling factors are modified to match the original z-domain transfer function. For NRZ DAC which the pulse exceeds the sampling instant, some different way is proposed to compensate the ELD. [13] introduces one extra auxiliary Half-delay Return-Zero DAC (HRZ) which is delayed to next clock cycle the same as feedback pulse of main DAC, so the output is half delayed RZ DAC (also it can be fed-back to any integrator), and new scaling coefficient can be calculated by matching the converted DT transfer function with original ideal one. The simplest and classical ELD compensation technique is the insertion of an additional feedback path around quantizer [4], [39], which is shown in Fig. 2.9. This method is becoming the most popular way to make

Figure 2.9: Insertion of an additional feedback path around quantizer to compensate ELD [39]

the modulator to be tolerant to one period of ELD. However, the method needs one more DAC and also power hungry summing amplifier. By adding extra path around quantizer (specially in presence of high integrator gain variation), the [13]

shows that even the robustness of the modulator improves, and the feasibly measure of robustness is proposed as a filter gain margin in [81]. According to [52], the tolerable loop delay decreases with higher amplitude and NRZ feedback, so higher order modulators are more sensitive to excess loop delay and they are more prone to instability (because of increasing the order of modulator by one). [54] proposed ELD compensating by adding  $e^{s\tau}$  after filter, they assume that input is piecewise constant and just considering output as a sampled data, equations  $\frac{e^{s\tau}}{s}$ ,  $\frac{e^{s\tau}}{s^2}$  and ... are approximated with their expanded and truncated values, so the coefficients are scaled based on new parameters. [23] proposes ELD compensation using a predictive comparator. In this method they change the input reference voltage of comparator based on derivative of loop filter output, so they force the comparator output to have an early decision (with adaptive control, based on the sign-LMS algorithm). Almost similar method is used by [85], they proposed switching matrix with simple control logic for ELD compensation. This technique avoids the use of a powerhungry signal adder and the extra feedback, based on output sign the reference voltage of quantizer will be changed. Moreover, a digital ELD compensation method is proposed by [25], which is similar to classical compensation but the auxiliary path is shifted after quantizer. In this method, the analog summing amplifier and the additional DAC are replaced by a register and digital adders (Fig. 2.10). However this method requires to increase the DAC resolution in order to fully restore the performance. Also, the STF will have large peaking due to non-touching path in the loop. ELD compensation using a PI-Element is proposed by [71] and used in [35]. It combines two inner loops of the classical compensation to one single proportionalintegrating element (PI-element). A resistor in series with a capacitor can be used as a feedback element in last Operational Amplifier (OpAmp). In this technique, the STF will be affected because the feedback path is removed and added as a

Figure 2.10: Insertion of auxiliary digital path after quantizer [39]

feedforward path. Another compensation is analog compensation which is proposed by [66,67,80]. In this method the compensation loop is placed around sample and hold by bypassing the Flash ADC. Using this technique, ELD of more than one clock cycle can be compensated with a small loss in resolution. Basically this technique add feedback loop around sample and hold instead of whole quantizer. This technique requires one extra DAC and summing amplifier and also changes the STF.

Another method which is proposed by [47] and [74] is using digital differentiation, which is shown in Fig. 2.11.

In this method the ELD compensation path moved from the output of the last integrator to its input. In return, the DAC output signal must be differentiated before being integrated. In this method if ELD is larger than sampling period it can not be compensated with simple proportional gain. This technique avoid the summing amplifier at the expense of one register (since DAC2 and DAC3 may be combined to one single DAC whose current is scaled) and maybe one extra DAC.

Figure 2.11: Using digital differentiation to compensate ELD [47]

# 2.4.3 State of the art solutions for clock jitter problem in CT- $\Sigma\Delta$ ADC

In literature, some techniques are proposed to degrade the jitter effect in CT- $\Delta\Sigma$ . Non-Return-to-Zero(NRZ) DAC waveforms are known to be robust to jitter effect in comparison with RZ DAC, due to one transition in each cycle. In RZ-DAC, uncertainty in clock timing affects the rising and falling transition of clock signal [14], so it is more sensitive to jitter error. [51] claimed to have improvement of 14dB for NRZ DAC. Some papers are using Finite Impulse Response DAC (FIR-DAC) feedback to reduce the sensitivity of CT- $\Delta\Sigma$  to jitter [19,44,51,56,63] which is shown in Fig. 2.12. They propose to generate multilevel DAC signal while using 1Bit quantizer. DAC response extends over multiple clock cycles, so the clock jitter effect is averaged [9]. [56] claimed to reduce the noise floor due to clock jitter by 18dB using FIR filter. However, the FIR filter introduces excess loop delay, and the loop will need an extra path to compensate the FIR filter delay and make the system stable which will increase both power and area. [63] has proposed a method

Figure 2.12: Using FIR-DAC to reduce sensitivity to jitter [63]

to compensate the delay introduced by FIR DAC and [16] suggests CT- $\Delta\Sigma$  with PWM and a FIR-DAC in the feedback path. The idea is to convert the output of multi-bit quantizer to a single bit PWM signal, then the PWM signal is fed back to input through FIR filter.

Some other techniques are proposed to elaborate on the shape of the DAC signal to decrease the effect of jitter which are shown in Fig. 2.13. Ortmanns, et al [53] propose using SCR (Switched-Capacitor-Resistor) feedback which is used in DT modulators. Instead of having the traditional rectangular signal as a feedback, an exponentially decreasing feedback is generated. Hence, at time of the clock transition, almost all charge has been transferred to the integrator outputs and clock jitter causes little error. The more recent works on SC feedback are done by [18] and [50]. [18] propose Dual-Switched-Capacitor-Resistor(DSCR) to improve jitter performance of  $CT-\Delta\Sigma$ . The idea of DSCR is to divide the exponential feedback pulse into several

Figure 2.13: Different DAC shapes to reduce clock jitter effect [9]

identical unit pulses in order to alleviate the slew-rate requirement of OpAmp. In SCR and DSCR methods the first integrator needs high slew-rate and high GBW which will increase the power drastically. Some other pulse shaping techniques are SSI (Switched-Shaped-Current) [83], and sin-shaped DAC feedback [45], [41]. In SSI technique instead of generating an exponentially decreasing feedback waveform over the whole clock period as in SC or SCR feedback, a rectangular pulse is used in most of the clock period, and then feedback is exponentially decreased in the rest of the clock period. In order to generate such signal the method is benefited from the behavior of transistor in saturation and triode region. However, synthesis of a modulator with pulse shaped techniques are complicated. In sin-shaped DAC feedback, clock transition takes place when the sin-shaped feedback is at its minimum slope, so it will reduce charge error. The circuit complexity and thermal noise over-

head of some of these techniques prevent their adoption in high-resolution low-cost applications. [9] and [33] propose clock control methods to decrease jitter effect in Switched Current DACs. The idea is to generate delayed version of RZ rectangular DAC feedback. In this technique, RZ time period and active DAC feedback time is fixed by delay elements, but the problem is that the delay elements are PVT variant.

# 3. GRADIENT DESCENT BASED CALIBRATION FOR MASH 3-0 SIGMA-DELTA MODULATOR

#### 3.1 Introduction

The Analog-to-Digital Converter (ADC) is an essential building block in most consumer electronics products. Oversampling ADCs trade digital signal processing and clock frequency for relaxed analog circuits, and among many data converters,  $CT-\Sigma\Delta$  ADC is one of the most suitable candidates for high-speed, high-resolution and low power applications. Recently, the applications of  $CT-\Sigma\Delta$  are continuously growing and covering areas such as wireless front-end [36], [20], imaging [27] and advanced Long Term Evolution (LTE) standards [22], [3]. Although  $CT-\Sigma\Delta$  is well known for achieving higher resolution in comparison with other ADC architectures, still there are many challenges to improve its performance.

Increasing the Signal-to-Quantization Noise Ratio (SQNR) of the modulator always has been a challenging issue. Increasing order of the modulator, oversampling ratio, and the quantizer/DAC resolution are well known approaches to improve the SQNR. But increasing those parameters contradict with some system performances such as loop stability, bandwidth, power consumption and silicon area. Another way to improve SQNR in CT- $\Sigma\Delta$  modulator is cascaded or Multi-stage Noise SHaping (MASH) structure [42, 43, 64]. A major issue in a cascaded converter is maintaining good matching between digital compensating transfer function and process-temperature-voltage (PVT) sensitive analog loop filter.

As explained before, another challenge in  $CT-\Sigma\Delta$  is loop sensitivity to Excess Loop Delay (ELD) [1,52,54,66,67,80]. This issue is becoming more relevant nowadays, as the switching frequency increases to accommodate wider standards such as

LTE with aggregated channels. The classical ELD compensation technique is the insertion of an additional feedback path around quantizer that dominates loop performance at high frequency as well as system stability [4], [39]. However, the method needs an additional DAC and a power hungry summing amplifier that must be functional at clock rate. Another method uses digital differentiation after DAC [47], [74]. This technique avoids the use of an extra summing amplifier at the expense of one extra DAC that stresses the operational amplifier and can introduce extra delay that jeopardizes loop stability [74].

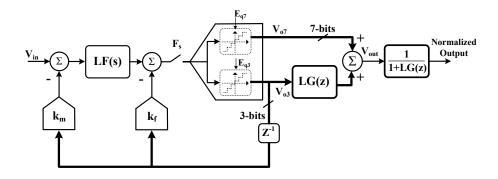

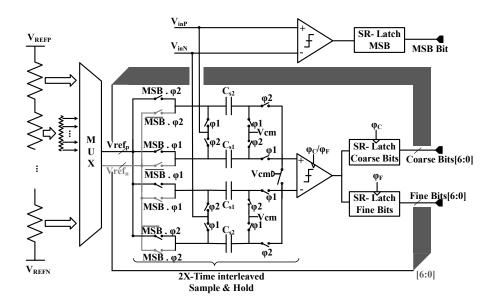

A key contribution of this chapter is the use of a modulator with an embedded 7-bit quantizer. The 3 most significant bits (MSB) of quantizer are used in feedback loop so it relaxes the main DAC linearity requirement and it saves power and area [6]. On the other hand, all 7-bits are used to mimic the operation of a MASH  $\Sigma\Delta$  modulator, so theoretically the over all quantization noise level will be competitive with a CT- $\Sigma\Delta$  with 7 bit quantizer. The adaptive Gradient Decent (GD) method is used to extract the analog loop gain transfer function of cascaded CT- $\Sigma\Delta$  and improve the modulator performance. The proposed method adaptively adjusts the digital FIR filter coefficients to decrease the rms of the quantization noise at output of the cascaded modulator. The feasibility of these techniques are experimentally verified in a prototype achieving SNDR of 51dB before calibration and SNDR of 60dB after the proposed calibration scheme is employed.

The ELD compensation is implemented through a current based differentiator which is applied after fast DAC and does not need any extra DAC nor a dedicated summing amplifier. The use of analog differentiator makes the circuit more tolerant to ELD, so it does not significantly affect loop stability. Further, in order to decrease power consumption, a linear class AB amplifier is used which can handle large current to improve fast path slew rate.

This chapter is organized as follows. Section 3.2 describes the system level architecture of the modulator. The circuit implementation of different blocks are presented in Section 4.3. Section 3.4 demonstrates the Gradient Descent based post-processing methods, and Section 3.5 shows modulator realization and measurement results. Finally, Section 4.5 concludes the chapter and compare the chip prototype with the state of the art designs.

# 3.2 System Architecture

# 3.2.1 Transfer function and stability

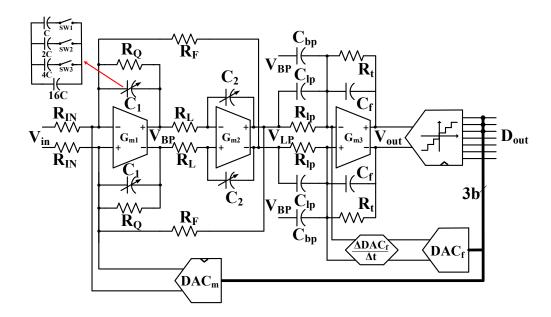

The proposed CT- $\Sigma\Delta$  modulator architecture is shown in Fig. 3.1, and its specification and expected performance from system level design are given in Table 3.1

The prototype was designed with limited performance (on purpose) to make the quantization the dominant source of noise. The modulator comprises a 7-bit internal quantizer, which only 3 bits are in  $\Sigma\Delta$  loop, operating at 300 MHz, and a third-order single-loop filter. Peak gain of noise transfer function is set to 5.3 dB. The third-order loop filter is realized as an active-RC topology due to its high linearity and large signal swing. Quantizer and DAC's excess loop delays are compensated using

Table 3.1: System level specification

| Design Parameters                                   | Specification |

|-----------------------------------------------------|---------------|

| Sampling Frequency                                  | 300 MHz       |

| OSR                                                 | 10            |

| Main feedback DAC                                   | 3-Bit         |

| $CT$ - $\Sigma\Delta$ loop order                    | 3             |

| Expected SQNR of 3-bit (-2 dBFS)                    | 51 dB         |

| Expected Signal to thermal noise of 3-bit (-2 dBFS) | 75 dB         |

| Expected SNDR after cancellation (-2 dBFS)          | 70 dB         |

| Expected total power consumption                    | 8.5 mW        |

fast path compressed by analog differentiator. The summing amplifier is combined with loop filter's last stage to decrease the number of amplifiers and save power, so the last integrator is used to add low-pass and band-pass outputs while completing the loop doing integration for the fast path.

The filter coefficients are chosen based on thermal noise, filter's node saturation (specially band pass output [26]) and feedback factor of summing amplifier. In order to increase SNR, the input resistor  $(R_{in})$  and input full scale voltage  $(V_{FS})$  are scaled up by 2; the passive component's values are given in Table 3.2. Input referred noise of filter is computed as shown in Eq.4.6:

$$V_{n,in,total}^{2} = \left[I_{n,DAC}^{2}R_{in}^{2} + V_{n,R_{in}}^{2} + \left(\frac{1}{A_{lp}Q}\right)^{2}V_{n,R_{Q}}^{2} + \left(\frac{1}{A_{lp}}\right)^{2}V_{n,R_{F}}^{2} + \left(\frac{1}{A_{lp}Q} + \tau_{1}s\right)^{2}V_{n,R_{L}}^{2} + \left(1 + \frac{1}{A_{lp}Q} + \tau_{1}s\right)^{2}V_{n,G_{m1}}^{2} + \left(\frac{1}{H_{LP}} + \frac{1}{A_{lp}}\left(\frac{1}{Q} - 1\right)\tau_{1}s\right)^{2}V_{n,G_{m2}}^{2}\right]BW$$

(3.1)

where,  $V_{n,X}$  and  $I_{n,X}$ , are rms noise voltage and current of component X, respectively.  $H_{LP}$  is transfer function from input to low-pass output of filter.  $A_{lp} = R_F/0.5R_{in}$ ,  $Q = R_Q/R_F$ , and  $\tau_1 = R_{in}C_1$  are low-pass gain and quality factor of biquad filter and time constant of first integrator, respectively. The noise current of DAC is approximately equal to  $I_{n,DAC}^2 \simeq 4KT\gamma(g_mcs + g_mb) \times 2$ , where  $g_mcs$  is transconductance of all DAC current sources, and  $g_mb$  is transconductance of bias currents of DAC. At low frequencies dominant noise sources are due to  $R_{in}$ ,  $G_{m1}$  and main path DAC,  $I_{n,DAC}$ , which the rms noise contribution of them are about 4 nV/rHz, 6.5 nV/rHz, and 6.3 nV/rHz respectively, so the noise is dominated by quantization noise. As the noise contribution of other components are reduced due to the voltage gain of previous stages, their contribution are minimum.

In order to compensate for process variations, capacitor bank is used which covers  $\pm 18\%$  with 3-bit programmability, so the RC time constant variations are minimized.

Table 3.2: Passive element values

| $R_{IN}$             | $R_Q$                  | $R_F$                  | $R_L$                  | $R_{lp}$               | $R_t$               | $C_1$  | $C_2$  | $C_f$             |

|----------------------|------------------------|------------------------|------------------------|------------------------|---------------------|--------|--------|-------------------|

| $1 \mathrm{K}\Omega$ | $5.4 \mathrm{K}\Omega$ | $1.8 \mathrm{K}\Omega$ | $1.8 \mathrm{K}\Omega$ | $41.5\mathrm{K}\Omega$ | $1\mathrm{M}\Omega$ | 5.6 pF | 5.6 pF | $0.2 \mathrm{pF}$ |

Figure 3.1: Proposed continuous-time Sigma-Delta modulator

# 3.2.2 Quantization noise reduction technique using a high resolution quantizer

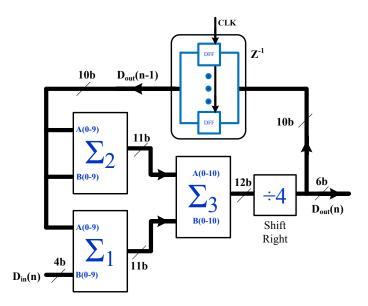

Fig. 3.2 shows the proposed technique for reducing the quantization noise. The

Figure 3.2: Block diagram of the proposed noise reduction technique

output of the 3-MSB of quantizer is fed-back into the loop and the whole 7-bit digital output is used for noise reduction. The 3 most significant bits  $(V_{o3})$  are filtered by the digital filter (LG(z)) which is ideally equal to the analog loop gain (LG(s)), and then the result is combined with the output of 7-bit quantizer  $(V_{o7})$ . Ignoring the effect of the sample and hold circuit at the input of the quantizers, conventional analysis shows that:

$$V_{o3} = \frac{LF(s)}{1 + LG(s)}(V_{in} + V_{th}) + \frac{1}{1 + LG(s)}E_{q3}$$

(3.2)

$$V_{o7} = \frac{LF(s)}{1 + LG(s)}(V_{in} + V_{th}) - \frac{LG(s)}{1 + LG(s)}E_{q3} + E_{q7}$$

(3.3)

$$V_{out} = \frac{1 + LG(z)}{1 + LG(s)} LF(s) \cdot (V_{in} + V_{th}) + \frac{LG(z) - LG(s)}{1 + LG(s)} E_{q3} + E_{q7}$$

(3.4)

In this equation, LF(s) is the loop filter's transfer function, and  $V_{th}$  is thermal noise. According to Eq. 3.4 if digital gain, LG(z), matches with analog loop gain,

LG(s) within the desired bandwidth, the quantization noise of 3-bit loop quantizer is canceled, and just the quantization noise of the 7-bit quantizer will affect the output signal, which is much smaller than the quantization noise of 3 bit quantizer; the final result is shown in Eq. 3.5.

$$V_{out} = LF(s)(V_{in} + V_{th}) + E_{q7}$$

(3.5)

And, normalizing the Eq. 3.5 to loop gain (1 + LG(s)), The output will be as:

$$V_{out}|_{normal} = STF(s).(V_{in} + V_{th}) + NTF(s).E_{q7}$$

$$(3.6)$$

Ideally, improvement due to quantization noise cancellation technique is equal to difference between feedback (3-bit) and whole resolution of quantizer (7-bit). A common issue in cascaded  $\Sigma\Delta$  converter architectures is that inband LG(s) must accurately match with LG(z) in order to reduce quantizer noise of the low resolution in-loop quantizer. Errors in the analog circuitry cause the actual LG(s) of the modulator to deviate from the desired transfer function and then limits the benefits of MASH approach, causing leakage of  $E_{q3}$  into the combined output of the cascaded modulator. In this thesis we used Gradient Decent method to match the digital loop gain with analog counterpart.

#### 3.3 Circuit implementation

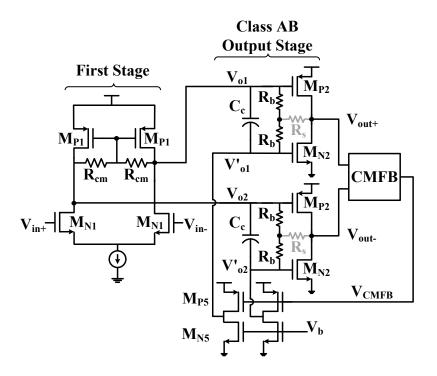

#### 3.3.1 Linear class AB amplifier

One of the challenges in  $\Sigma\Delta$ -ADC design is to make it power efficient. In literature, several methods are proposed to decrease the power consumption of the loop filter [84], [82]. Folded-cascode and multi-stage amplification techniques are the most popular ones for low voltage design. However, in a CT- $\Sigma\Delta$  loop filter composed of

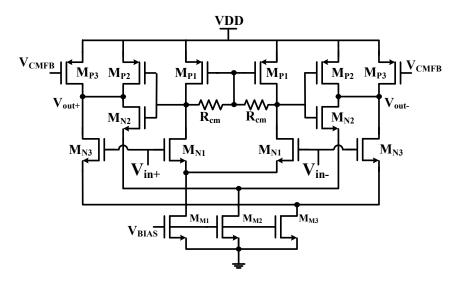

Figure 3.3: Class-AB amplifier schematic

the active RC integrators, the resistive load makes the folded-cascode OpAmp less efficient in terms of low frequency gain than the multi-stage amplifier. In this thesis, in order to save power, a two-stage amplifier with class-AB output stage is used to provide large output current with modest biasing current.

The two stage amplifier is shown in Fig. 3.3. First stage  $(M_{N1}, M_{P1})$  is conventional differential pair and second stage is class AB amplifier composed by  $(M_{N2}, M_{P2}, R_b \text{ and } R_s, C_c)$  with modified Monticelli [48] bias circuitry which increase second stage amplifier's linearity. Signals from  $V_{o1}$  to  $V'_{o1}$  are AC coupled by large capacitor  $C_c$ . Resistors  $R_b$  and control current generated by common-mode detector and transconductance amplifier  $(M_{N5}, M_{P5})$  set the bias voltage for class-AB transistor,  $M_{N2}$ . The common mode feedback mechanism adjusts the  $V_{gs}$  of  $M_{N2}$  through voltage drop in  $R_b$  resistor to force the drain current of  $M_{P2}$  equal to the

bias current of  $M_{N2}$ . Ignoring the effect of  $R_s$ , the transfer function from  $V_{o1}$  to  $V'_{o1}$  is shown in Eq. 3.7.

$$\frac{V'_{o1}}{V_{o1}} \approx \frac{1 + (2R_bC_c)s}{1 + s(C_c + C_{asN2})2R_b}$$

(3.7)

where in this design  $R_b = 10K\Omega$ , and  $C_c = 3pF$ . If  $C_c \gg C_{gsN2}$  the frequency of the pole and zero pair will be very close to each other and  $V_{o1}$  and  $V'_{o1}$  will be almost identical. Considering the effect of the large feedback resistor  $R_s$  the low frequency gain of OTA will be as follows:

$$\frac{V_{out}}{V_{in}} = g_{m_{n1}}.R_{L1}.(g_{m_{n2}} + g_{m_{p2}}).R_{L2}$$

(3.8)

where,  $R_{L1} = R_{cm}||R_{n1}||R_{p1}$  and  $R_{L2} = R_L||R_{n2}||R_{p2}$  are first stage and second stage's load, respectively;  $R_L$  is load of the amplifier. The large resistor  $R_s$  provides shunt feedback to decrease the output impedance of second stage but at the same time reduces the low-frequency gain. Fig. 3.4, shows a two tone test for the filter's first stage which is a lossy integrator. The tones are placed at 10 MHz and 11 MHz and the rms value of the composed signal is -4 dBFS, and the third order intermodulation is -64 dB. Although Rs reduces the loop gain, it prevents the class AB to suffer from significant cross over distortion.

Fully loaded, the total low frequency gain of the amplifier is 29dB, and using 1.2V power supply, the first stage and second stage's power consumptions are 0.27mW and 0.12mW, respectively. Table 3.3 shows the comparison of proposed class AB amplifier vs the conventional two-stage class A (miller amplifier) counterpart with the same gain-bandwidth product. According to this table, in order to have same GBW, class A amplifier needs almost twice current of class AB amplifier. Moreover, although

Figure 3.4: 2 tone test for linearity simulation of first lossy integrator with rms output amplitude of -4dBFS at  $10 \mathrm{MHz}$  and  $11 \mathrm{MHz}$

small signal linearity are almost the same (demonstrating that cross-over distortion is not an issue in the class AB topology), the large signal IM3 of class AB amplifier is almost 10 dB smaller than the class A amplifier.

Table 3.3: Comparison of Class-AB vs Class-A output stage

|                                                    | Class A                | Class AB               |

|----------------------------------------------------|------------------------|------------------------|

| GBW                                                | 2.36 GHz               | 2.4 GHz                |

| power                                              | 0.83 mW                | 0.39 mW                |

| noise                                              | $6.53~\mathrm{nV/rHz}$ | $6.59~\mathrm{nV/rHz}$ |

| IM3, cross over distortion (RMS Vout = $-20$ dBFS) | -88 dBc                | -92 dBc                |

| IM3, large signal distortion (RMS Vout = -6 dBFS)  | -67 dBc                | -58 dBc                |

# 3.3.2 Mixed signal fast path employing analog differentiator

In this section we describe the fast path operation, and the way we increase ELD tolerance. Analog differentiator is proposed in order to avoid the use of power hungry summing amplifier and at the same time compensate excess loop delay without

compromising fast path performance, while we increase ELD tolerance.

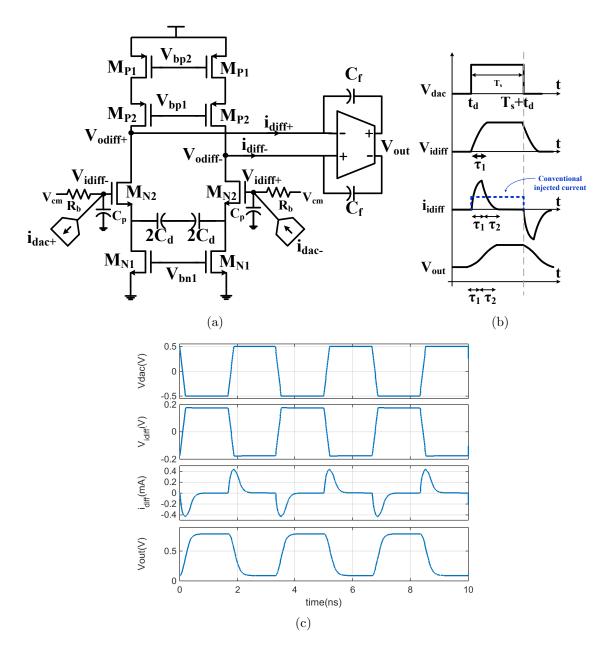

The main concept relies on minimizing the use of delayed clocks and the use of a wide-band analog differentiator. The proposed continuous time differentiator is shown in Fig. 3.5, and the fast path circuit parameters are displayed in Table 3.4. Feedback DAC output current  $I_{dac}$ , is converted to voltage by resistor  $R_b$  and

Table 3.4: Differentiator circuit parameters

|              |                    |       |             | I     |         |         |

|--------------|--------------------|-------|-------------|-------|---------|---------|

| $g_{m_{M2}}$ | $C_d$              | $C_f$ | $R_b$       | $C_p$ | $	au_1$ | $	au_2$ |

| 4.2m℧        | $0.27 \mathrm{pF}$ | 0.2pF | $350\Omega$ | 20fF  | 7ps     | 120ps   |

then fed to capacitive degenerated differential pair  $M_{N2}$ . DAC current signal is then indirectly differentiated on capacitors  $2C_d$ . Capacitor  $C_f$  along with an OTA  $G_{m3}$  integrates the output current of differentiator and generates a zero order path around quantizer. Overall, the fast path operates as a broadband amplifiers with half delay required by the quantizer. The input to differentiator is NRZ DAC's output with an equivalent trans-impedance gain of  $R_{dac}$ . Differentiator input is then characterized as:

$$V_{idiff}(s) = \frac{R_b}{R_b C_p s + 1} I_{dac}(s)$$

(3.9)

Transistor  $M_{N2}$  with capacitor of  $2C_d$  form a source degenerated circuit which provides the required differentiation operation. Ignoring the effect of the transistor output resistance, the output current of differentiator is described as:

$$i_{diff}(s) = \frac{2C_d s}{\frac{2C_d}{q_m} s + 1} V_{idiff}(s)$$

$$(3.10)$$

Figure 3.5: (a) Fast path and differentiator circuit (b) transient response of different nodes (c) schematic simulation

$$i_{diff}(t) = \begin{cases} \frac{-2R_bC_d}{\tau_2 - \tau_1} (e^{-t/\tau_1} - e^{-t/\tau_2}) . I_{DAC}, & \text{if } \tau_1 \neq \tau_2 = 2C_d/g_m\\ \frac{-2R_bC_d}{\tau^2} . t e^{-t/\tau} . I_{DAC}, & \text{if } \tau_1 = \tau_2 = \tau \end{cases}$$

(3.11)

Passing  $I_{diff}(t)$  through  $C_f$ , yields integration operation; the final output of integrator is obtained replacing  $t = T_s/2$ .

$$V_{out}(\frac{T_s}{2}) = \frac{1}{C_f} \int_0^{T_s/2} i_{diff}(t)dt = \frac{2R_b C_d I_{DAC}}{C_f(\tau_2 - \tau_1)} [\tau_1(e^{-T_s/2\tau_1} - 1) - \tau_2(e^{-T_s/2\tau_2} - 1)]$$

(3.12)

If  $T_s \gg \tau_1$ ,  $\tau_2$ , then  $V_{out}(T_s/2) \sim 2R_bI_{dac}C_d/C_f$ , so the fast path is strong function of  $R_bI_{dac}$ . The concept is shown in Fig. 3.5(b) and the schematic simulation (Cadence) is shown in Fig. 3.5(c). According to the figures the differentiator's current settles in less than half of sampling period, which makes it more tolerant to ELD. As shown in Fig. 3.5(b), the settling time of differentiator circuit should be less than half period  $4\tau_1 + 4\tau_2 < \frac{T_s}{2}$  to guarantee 98% or better voltage settling accuracy. Notice that the signal swing at  $M_{N2}$  gate should not be too large, otherwise the transistor might be pushed into triode region. To keep  $M_{N2}$  in saturation region,  $R_bI_{dac}$  is set to be 300 mV. Capacitor  $C_f$  (and accordingly  $2C_d$ ) is related to the capacitor loading of OpAmp by feed-forward path in loop filter and there is enough design flexibility to choose its value. To make the modulator more tolerant to ELD, we need to decrease  $\tau_1$  and  $\tau_2$ , which means decreasing  $R_b$ ,  $C_p$ ,  $C_d$  and increasing  $g_m$ ; the trade off is additional power consumption.

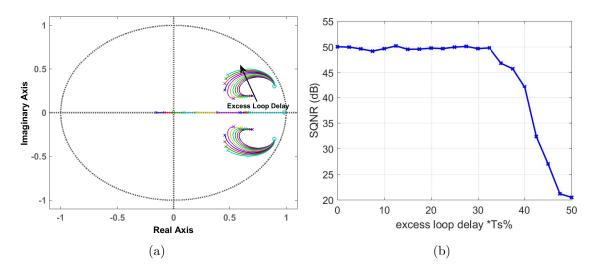

The effect of excess loop delay in system performance is shown in Fig. 3.6 which is system level simulation which is done using Matlab/Simulink. Fig. 3.6(a) shows the Root-Locus of Noise Transfer Function (NTF(z)) with 0-100% excess delay. The ELD is modeled as  $\tau$  in  $NTF(z) = \frac{1}{1+e^{-\tau s/T_s}LG(z)}$ . According to Fig. 3.6(a) all

Figure 3.6: Excess loop delay variation  $0-100\%T_s$  (a) root-locus of NTF(z) poles including mixed signal fast path (b) SNDR vs ELD variation