# POWER ELECTRONIC SOLUTIONS FOR INTERFACING OFFSHORE WIND TURBINE GENERATORS TO MEDIUM VOLTAGE DC COLLECTION GRIDS

A Dissertation

by

## MICHAEL T DANIEL

## Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

| Chair of Committee, | Prasad Enjeti         |

|---------------------|-----------------------|

| Committee Members,  | Le Xie                |

|                     | Shankar Bhattacharyya |

|                     | Won-jong Kim          |

| Head of Department, | Miroslav Begovic      |

May 2016

Major Subject: Electrical Engineering

Copyright 2016 Michael Daniel

#### ABSTRACT

Here in the early 21<sup>st</sup> century humanity is continuing to seek improved quality of life for citizens throughout the world. This global advancement is providing more people than ever with access to state-of-the-art services in areas such as transportation, entertainment, computing, communication, and so on. Providing these services to an ever-growing population while considering the constraints levied by continuing climate change will require new frontiers of clean energy to be developed. At the time of this writing, offshore wind has been proven as both a politically and economically agreeable source of clean, sustainable energy by northern European nations with many wind farms deployed in the North, Baltic, and Irish Seas.

Modern offshore wind farms are equipped with an electrical system within the farm itself to aggregate the energy from all turbines in the farm before it is transmitted to shore. This collection grid is traditionally a 3-phase medium voltage alternating current (MVAC) system. Due to reactive power and other practical constraints, it is preferable to use a medium voltage direct current (MVDC) collection grid when siting farms >150 km from shore. To date, no offshore wind farm features an MVDC collection grid. However, MVDC collection grids are expected to be deployed with future offshore wind farms as they are sited further out to sea.

In this work it is assumed that many future offshore wind farms may utilize an MVDC collection grid to aggregate electrical energy generated by individual wind turbines. As such, this work presents both per-phase and per-pole power electronic

converter systems suitable for interfacing individual wind turbines to such an MVDC collection grid. Both interfaces are shown to provide high input power factor at the wind turbine while providing DC output current to the MVDC grid. Common mode voltage stress and circulating currents are investigated, and mitigation strategies are provided for both interfaces. A power sharing scheme for connecting multiple wind turbines in series to allow for a higher MVDC grid voltage is also proposed and analyzed. The overall results show that the proposed per-pole approach yields key advantages in areas of common mode voltage stress, circulating current, and DC link capacitance, making it the more appropriate choice of the two proposed interfaces for this application.

For my family.

#### ACKNOWLEDGEMENTS

Above all I would like to thank Dr. Prasad N. Enjeti for the outstanding guidance he has given me in my research and professional life. His mentorship and understanding have made my time at Texas A&M the most fulfilling and enjoyable years of my life todate. I also thank Dr. Le Xie, Dr. Shankar P. Bhattacharyya, and Dr. Won-jong Kim; they are all outstanding professors who have given their valuable time to serve on my committee. I would also like to thank Dr. Robert S. Balog for his advice and professional guidance during my time at Texas A&M University.

Thanks are also extended to Tammy Carda, Jeanie Marshall, Melissa Sheldon, Sheryl Mallett, Eugenia Costia, Rebecca Rice, Annie Brunker, and all those in the Department of Electrical and Computer Engineering who have greatly simplified my life by guiding me through the "behind-the-scenes" of earning a PhD!

At the College of Engineering I would like to thank Yvonne Burrell for helping me take care of business, and Dr. Scott Miller for finding the support needed for me to start my career at Texas A&M University. I am truly grateful for the support provided by the College of Engineering during my PhD.

I would also like to thank Lieutenant Commander Michael Wagoner, USN, for working with me to navigate over a year of bureaucracy before finally being accepted into my current position with the U.S. Navy. I also acknowledge the outstanding support provided by the U.S. Navy during the final 18 months of my PhD. Thanks are also due to my past professors who have had a lasting impact on me, both professionally and personally. Dr. Ali Abur, Dr. Bradley Lehman, Dr. Ronald Musiak, Dr. Steven Northrup, Dr. John Burke, and Dr. Mary Vollaro have all provided outstanding mentorship and guidance during my years as a student.

I thank the colleagues I've had at my many internships during college and graduate school. Mark Bellandese, Dennis Bassaragh, and Daniel Anderson at Northeast Utilities helped me develop the professional character necessary for a successful engineering career. Michael Taranowski, Matthew Dayton, and Leroy Bennett at Lawrence Livermore National Laboratory challenged me to learn new skills quickly, and provided the inspiration that would lead to my master's thesis in 2012. Leroy Bennett gave me the best summary of what it means to be an engineer: if it's frustrating and time consuming, then it's the engineer's job! Thanks are also due to Andrea Gorgerino, Yannick Maurice, Cuong Le, Vazgen Avakian, and Jorge Cerezo at International Rectifier who provided a challenging and rewarding internship experience while giving me the flexibility to enjoy my time in southern California to the fullest.

I am truly grateful for the support and friendship of my colleagues in the Electric Power and Power Electronics program at Texas A&M. I would like to acknowledge and thank, in no particular order, Harish Krishnamoorthy, Bahaa Hafez, Ahmed Morsy, Somasundaram Essakiappan, Pawan Garg, Dibyendu Rana, Joshua Hawke, Sinan Al-Obaidi, Taeyong Kang, Fahad Alhuwaishel, Jorge Ramos-Ruiz, Jose Sandoval, Yong Zhou, Salwan Sabry, Weiran Dai, Yongheng Yang, Dogan Urgun, Payman Dehghanian, Po-Chen Chen, Hung-Ming Chou, Mohammad Shadmand, Haiyu Zhang, Nandita Venugopal, Sarah Dominey, Austin Clay Styer, Sewan Choi, Mehran Mirjafari, Vivek Sundaram, Yateendra Deshpande, Babak Farhangi, Matthew Johnson, Siavash Pakdelian, Souhib Harb, Angel Clark, Poornima Mazumdar, and Qin Yan.

I also extend thanks to my close friends from the Aggie Yacht Club and the extended sailing community surrounding Texas A&M, including Chris Bay, Rob Zedric, Nick Parkes, Matt Barrett, Patrick Chapates, Lance West, Alex Oyston, Kylee Reid, Anne Carter, and Stu Allison, who have been the keel to right me when I've been knocked down. I would also like to acknowledge and thank Ron Liston, Mike Lindstrom, Jim Simmons, Michael Kunz, Richard Kelton, Mike Martin, Sara Burns, Barry Christensen, John Schmitt, Jim Swartwout, and Josh Kablotski, for allowing me to experience more sailing than I would have ever thought possible when I started learning two years ago! Sailing has kept me focused and in good spirits during my PhD.

Finally, I give my thanks and love to my family for their patience and support throughout my graduate school career.

# TABLE OF CONTENTS

|                                                                                                                   | Page |

|-------------------------------------------------------------------------------------------------------------------|------|

| ABSTRACT                                                                                                          | ii   |

| DEDICATION                                                                                                        | iv   |

| ACKNOWLEDGEMENTS                                                                                                  | v    |

| TABLE OF CONTENTS                                                                                                 | viii |

| LIST OF FIGURES                                                                                                   | X    |

| LIST OF TABLES                                                                                                    | xvii |

| 1. INTRODUCTION AND LITERATURE REVIEW                                                                             | 1    |

| 2. A NEW WIND TURBINE INTERFACE TO MVDC COLLECTION GRI<br>WITH HIGH FREQUENCY ISOLATION AND INPUT CURRENT SHAPING |      |

| 2.1 Introduction                                                                                                  |      |

| 2.2 Proposed Approach                                                                                             |      |

| 2.2.1 Front-end Multilevel Rectifier                                                                              | 24   |

| 2.2.2 HF Inverter and Resonant AC Link                                                                            | 25   |

| 2.2.3 Output Rectifier to MVDC Grid                                                                               |      |

| 2.2.4 Control Strategies                                                                                          |      |

| 2.3 Case Study and Simulation Results                                                                             |      |

| 2.3.1 Steady State Operation                                                                                      |      |

| 2.3.2 Transient Response                                                                                          |      |

| 2.4 Experimental Results                                                                                          |      |

| 2.5 Conclusions                                                                                                   |      |

| 3. AN IMPROVED OFFSHORE WIND TURBINE TO MVDC GRID<br>INTERFACE USING HIGH FREQUENCY RESONANT ISOLATION AND        |      |

| INPUT POWER FACTOR CONTROL                                                                                        | 47   |

| 2.1 Introduction                                                                                                  |      |

| 3.1 Introduction                                                                                                  |      |

| <ul><li>3.2 Proposed Approach and Analysis</li></ul>                                                              |      |

|                                                                                                                   |      |

| 3.2.2 NPC Inverter                                                                                                |      |

| 3.2.3 Resonant AC Link                                                                                            |      |

| 3.2.4 Output Rectifier and Filter                                                                                 |      |

| 3.2.5 Control Strategy                                                                                            | 55   |

| 3.3 Design Example                                        | 56  |

|-----------------------------------------------------------|-----|

| 3.4 Simulation Results                                    | 59  |

| 3.5 Experimental Results                                  |     |

| 3.6 Conclusion                                            |     |

|                                                           |     |

| 4. EXPLORING COMMON MODE VOLTAGE STRESS AND CIRCULATING   |     |

| CURRENTS IN OFFSHORE WIND TURBINE TO MVDC COLLECTION GRID |     |

| INTERFACES                                                | 71  |

|                                                           |     |

| 4.1 Introduction                                          | 72  |

| 4.2 Per-Phase Interface                                   | 76  |

| 4.3 Per-Pole Interface                                    | 80  |

| 4.4 Simulation Results                                    |     |

| 4.5 CM Filter and Shielded Transformer                    |     |

| 4.6 Conclusions                                           |     |

|                                                           |     |

| 5. A POWER SHARING SCHEME FOR SERIES CONNECTED OFFSHORE   |     |

| WIND TURBINES IN A MEDIUM VOLTAGE DC COLLECTION GRID      | 97  |

|                                                           |     |

| 5.1 Introduction                                          | 97  |

| 5.2 Proposed Approach                                     |     |

| 5.3 Simulations Results                                   |     |

| 5.4 Conclusion                                            |     |

|                                                           |     |

| 6. SUMMARY                                                | 106 |

|                                                           |     |

| 6.1 Conclusions                                           | 106 |

| 6.2 Future Work                                           | 108 |

|                                                           |     |

| REFERENCES                                                | 110 |

# LIST OF FIGURES

Page

| Figure | 1-1: Offshore wind farm with MVDC collection grid1                                                                                                                                                                                                                                                                                                         |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure | <ul><li>1-2: Illustration of projected global energy shortfall. Source: Paul Chefurka,</li><li>2008 [1]. Reused with courtesy of Paul Chefurka</li></ul>                                                                                                                                                                                                   |

| Figure | 1-3: EIA projection of future renewable energy growth. Source: U.S. Energy<br>Information Administration, 2012 [7]. Reused with courtesy of the U.S.<br>Energy Information Administration                                                                                                                                                                  |

| Figure | 1-4: Estimate of global wind energy resources. Source: U.S. Department of Energy, 1980 [8]. Reused with courtesy of the U.S. Department of Energy4                                                                                                                                                                                                         |

| Figure | 1-5: Recent development of offshore wind energy resources. Source: Global Wind Energy Council, 2015 [9]. Reused with courtesy of the Global Wind Energy Council                                                                                                                                                                                            |

| Figure | 1-6: Power production at TEP Springerville PV station. Source: Curtright & Apt, 2007 [10]. Reused with courtesy of John Wiley & Sons                                                                                                                                                                                                                       |

| Figure | <ul><li>1-7: Altamont Pass wind speed on 18 April 2015. Source: WindFinder, 2015</li><li>[11]. Adapted with permission of WindFinder</li></ul>                                                                                                                                                                                                             |

| Figure | 1-8: Wind speed near Meerwind Ost/Sud on 21/22 April 2015. Source:<br>WindFinder, 2015 [12]. Adapted with permission of WindFinder                                                                                                                                                                                                                         |

| Figure | 1-9: Large offshore wind farms of the future will be sited further to sea and require more space between individual turbines. Background image source: 4COffshore, 2015 [14]. Adapted with permission of 4COffshore. Inset image source: European Wind Energy Administration 2011 [13]. Adapted with permission of the European Wind Energy Administration |

| Figure | <ul><li>1-10 Riffgat offshore wind farm and offshore substation. Photo: Siemens AG</li><li>2013 [18]. Reused with courtesy of Siemens AG</li></ul>                                                                                                                                                                                                         |

| Figure | 1-11: Offshore wind farm with 33 kV 3-phase MVAC collection grid                                                                                                                                                                                                                                                                                           |

| Figure | <ul><li>1-12: Example of an offshore HVDC converter station. Photo: Siemens AG</li><li>2014 [19]. Reused with courtesy of Siemens AG</li></ul>                                                                                                                                                                                                             |

| Figure | 1-13: Offshore wind farm with ±30 kV MVDC collection grid10                                                                                                                                                                                                                                                                                                |

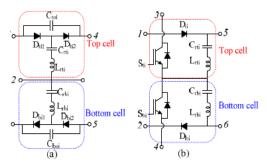

| Figure | 1-14: Resonant interface proposed by Chen et al. © 2013 IEEE [21].<br>Adapted with permission of the IEEE.                                                                                                                                                                                                                     | 2 |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Figure | <ul><li>1-15: Modular resonant DC/DC proposed by Parastar et al. © 2014 IEEE</li><li>[22]. Adapted with permission of the IEEE</li></ul>                                                                                                                                                                                       | 2 |

| Figure | 1-16: Capacitive coupled approach proposed by Jovcic. © 2009 IET [23].<br>Adapted with permission of the IET                                                                                                                                                                                                                   | 3 |

| Figure | 1-17: Isolated DC/DC approach proposed by Lam et al. © 2014 IEEE [24].<br>Adapted with permission of the IEEE                                                                                                                                                                                                                  | 4 |

| Figure | 1-18: Medium frequency generator approach proposed by Prasai et al. © 2008 IEEE [25]. Adapted with permission of the IEEE                                                                                                                                                                                                      | 5 |

| Figure | 2-1: Example of offshore wind farm with WTG to ±30 kV MVDC collection grid interface                                                                                                                                                                                                                                           | 0 |

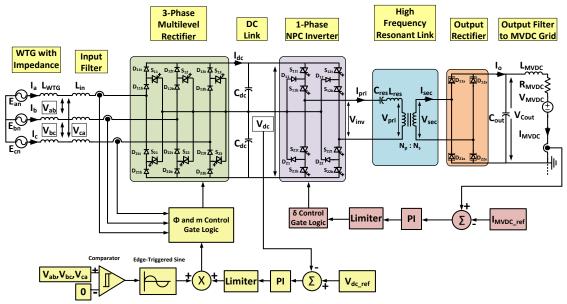

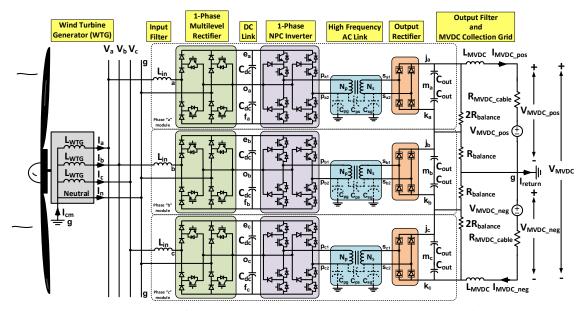

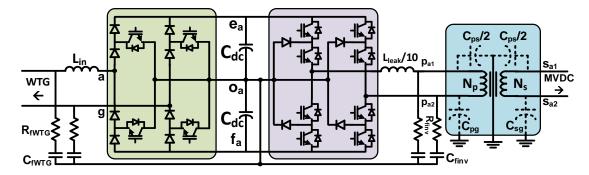

| Figure | 2-2: The proposed converter interface between WTG and MVDC collection grid using multilevel input rectifier, NPC inverter and high frequency resonant AC link                                                                                                                                                                  | 3 |

| Figure | 2-3: End-to-end detail of phase "a" converter module showing output<br>current control scheme and DC link voltage control scheme. The DC link<br>control also implements boost PFC functionality through input current<br>shaping                                                                                              | 4 |

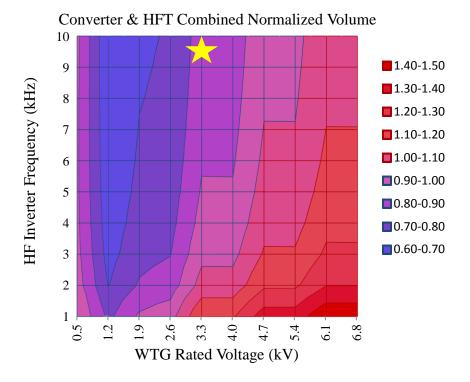

| Figure | 2-4: Surface describing normalized volume of proposed approach at various WTG voltages and inverter frequencies. The star indicates the chosen operating point studied in this work. The inverse square root effect of transformer volume scaling, as well as discontinuities when devices are added, can be clearly observed. | 8 |

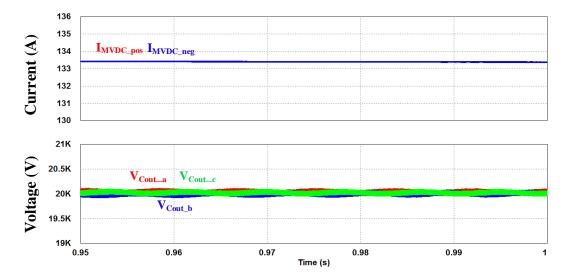

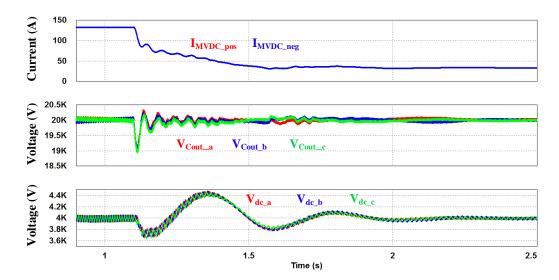

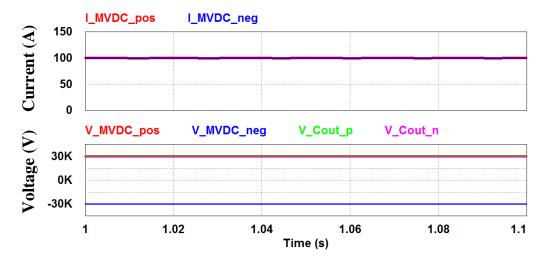

| Figure | 2-5: Output MVDC current is shown in the top plot while MVDC grid voltage and output capacitor voltages are shown at bottom. Full MVDC pole voltages are not shown as they are simply fixed DC sources at $\pm 30$ kV34                                                                                                        | 4 |

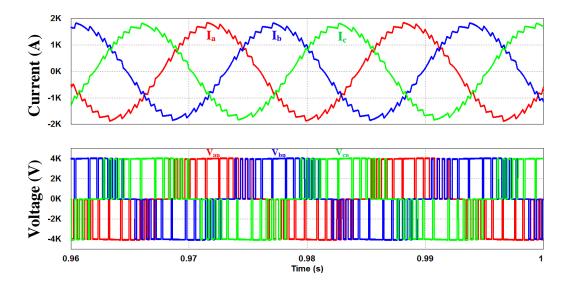

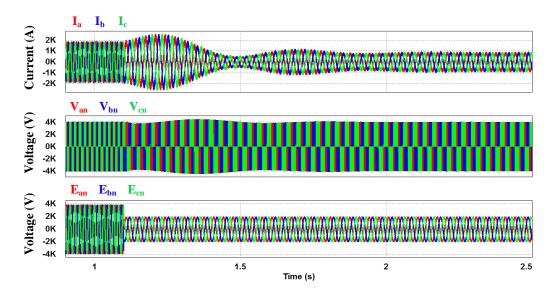

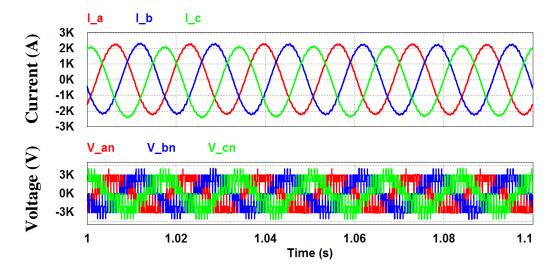

| Figure | 2-6: WTG currents are shown top while WTG terminal voltages are shown<br>at bottom. Hysteresis control yields and effective input switching frequency<br>of approximately 1.5 kHz                                                                                                                                              | 5 |

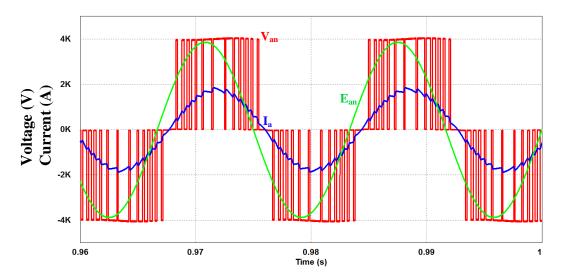

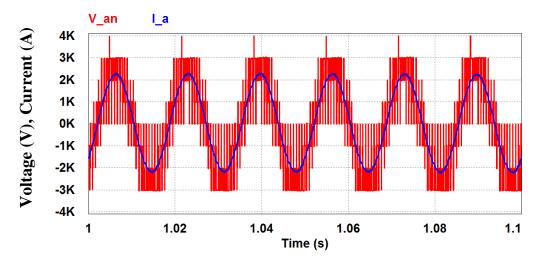

| Figure | 2-7: WTG phase "a" terminal voltage and current, as well as WTG internal voltage. Input current charging occurs while the corresponding WTG terminal is shorted by the rectifier input, while discharging occurs when the                                                                                                      |   |

|        | WTG terminal is clamped to the DC link through the outer rectifier diodes.<br>Note Van and Ia are in phase and both lag Ean                                                                                                                                                                                                                                                                                                                          |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure | 2-8: Steady-state DC link voltage is shown top while phase "a" DC link<br>current and DC link balancing current are show middle and bottom,<br>respectively. DC link current is composed of decaying portions of WTG<br>current only, which is characteristic of boost converter diode current. The<br>balance current is very small due to the perfectly matched capacitors used in<br>simulation                                                   |

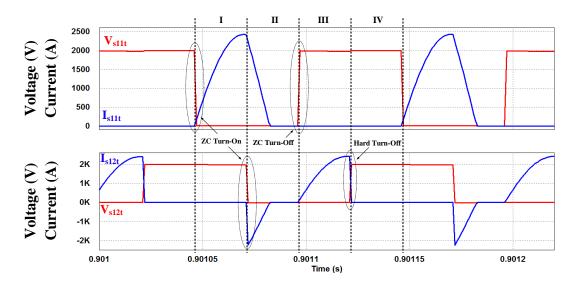

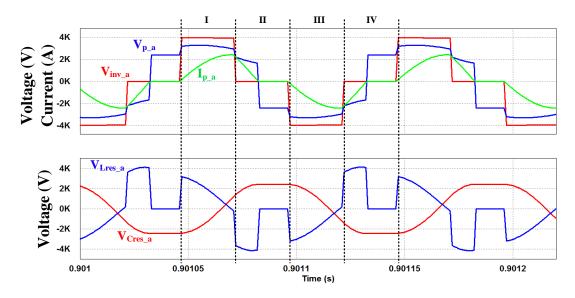

| Figure | 2-9: Top plot shows inverter output voltage (red), transformer primary voltage (blue), and primary current (green). Transformer current resonates to its peak before zero voltage is applied and current is allowed to freewheel back to zero before next half-cycle. Once Ip freewheels to zero Vp becomes – VCres as no voltage is present across the resonant inductor when $Ip = 0$ . Regions I-IV correspond to states described in Figure 2-11 |

| Figure | <ul> <li>2-10: Inverter switch voltage and current waveforms for S11t &amp; S12t from Figure 2-3. Both "t" and "b" switches in each pair operate simultaneously.</li> <li>S21 waveforms are S11 waveforms shifted 180°; same relationship holds between S12 &amp; S22. I-IV correspond to Figure. 2-11</li></ul>                                                                                                                                     |

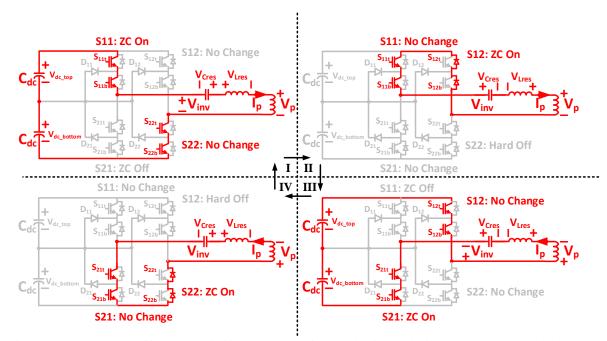

| Figure | 2-11. Summary of inverter switching states showing conducting paths in red.<br>Inverter continually steps through states I-IV and adjusts the amount of time<br>spent in zero voltage freewheeling states II & IV to control power transfer<br>through transformer. Polarity of VLres and Vp in states II & IV are shown<br>during current freewheeling before Ip = 0                                                                                |

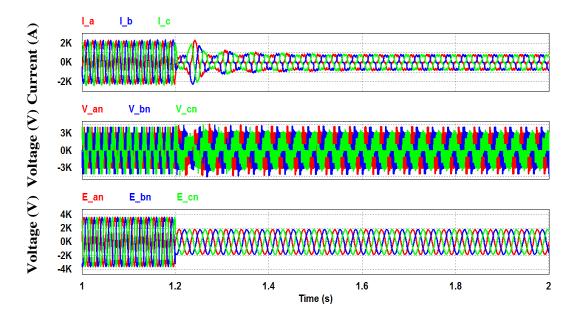

| Figure | 2-12: WTG current (top), terminal voltage (middle), and internal voltage (bottom) all reduce in frequency post transient, but terminal voltage continues to clamp to 4 kV DC bus                                                                                                                                                                                                                                                                     |

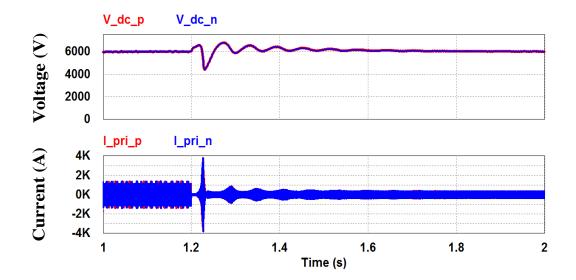

| Figure | 2-13: The inverter controller stabilizes the output MVDC current within 1 second post-transient. Note output capacitors rapidly rebalance and DC link controller stabilizes balanced DC link voltages within 1 second post-transient                                                                                                                                                                                                                 |

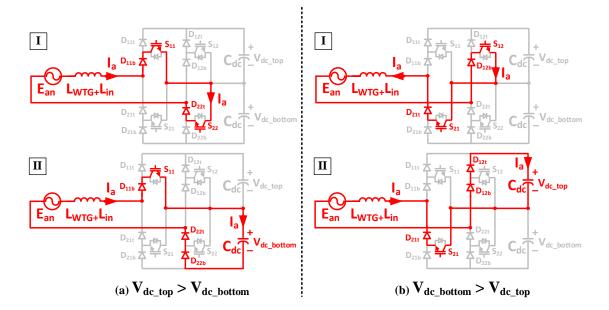

| Figure | 2-14: Switching methodology for capacitor voltage balancing. When top capacitor has greater voltage as in (a) I $\neg$ a can be shunted to the bottom capacitor by allowing the duty cycle of S21 & S22 to be slightly lower than S11 & S12. When top capacitor has lower voltage as in (b) Ia can be shunted to the top capacitor by allowing the duty cycle of S21 & S22 to be slightly higher than S11 & S12                                      |

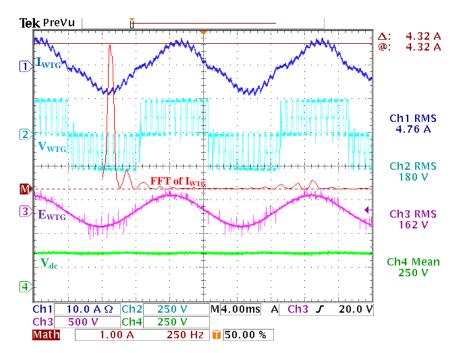

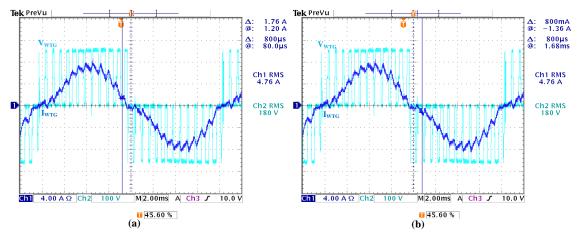

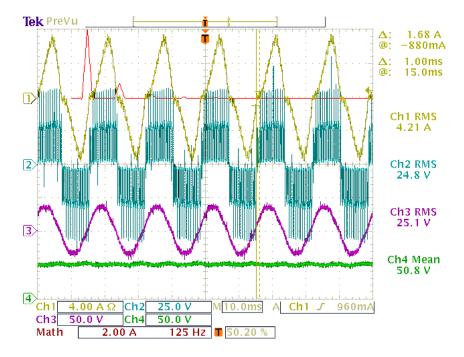

| Figure | <ul> <li>2-15: Active rectifier stage AC input waveforms and total DC output voltage.</li> <li>WTG internal voltage (Ch.3, purple) is measured as 162 Vrms at 60 Hz, while WTG terminal voltage (Ch2, light blue) has a higher RMS value due to switching harmonics as expected from simulation results in Figure 2-7.</li> <li>WTG current (Ch.1, dark blue) shows low phase displacement from WTG terminal voltage and the expected switching action from Figure 2-7. Output DC link voltage (Ch.4, green) is steady at 250 Vdc. Note the fundamental component of the input current (Ch. Math, red) is 4.32 Arms and accounts for most of the 4.76 Arms of input current.</li> </ul> |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure | 2-16. From the WTG voltage zero crossing at 0.88 ms, indicated by the blue dashed vertical cursor centered in (a) and (b), the current zero crossing is estimated to be within -0.8 ms, represented by the solid blue vertical cursor in (a), and +0.8 ms, represented by the solid blue vertical cursor in (b)                                                                                                                                                                                                                                                                                                                                                                         |

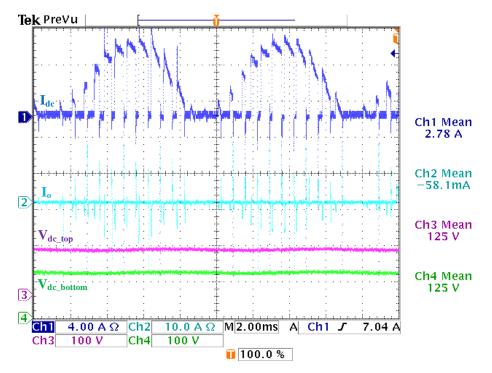

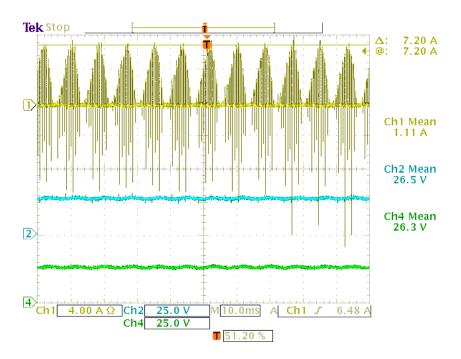

| Figure | 2-17: Active rectifier stage output DC waveforms. DC link top capacitor voltage (Ch.3, purple) and bottom capacitor voltage (Ch4, green) are balanced at 125 Vdc each, and balancing current Io (Ch.2, light blue) shows only a small DC value and clamping to Idc during capacitor balancing action as described in Figure 5-14. DC link current Idc (Ch.1, dark blue) shows typical boost diode current characteristic as expected from Figure 2-8                                                                                                                                                                                                                                    |

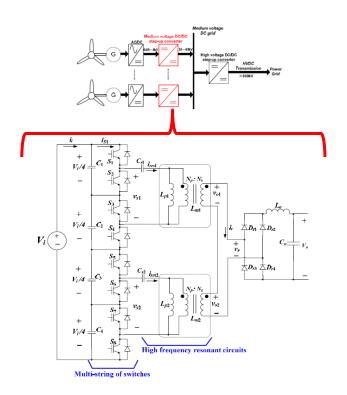

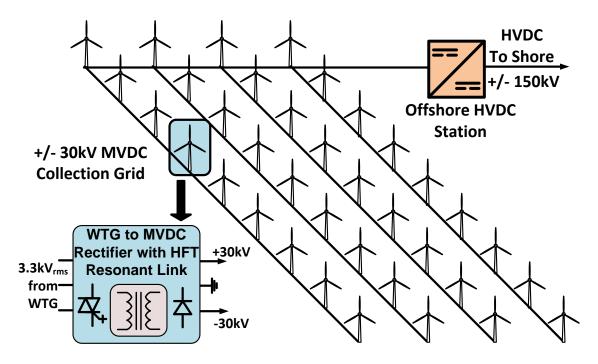

| Figure | 3-1: WTG interface to offshore wind farm with +/-30 kV MVDC collection grid architecture and HVDC link to shore, © IEEE 2014                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

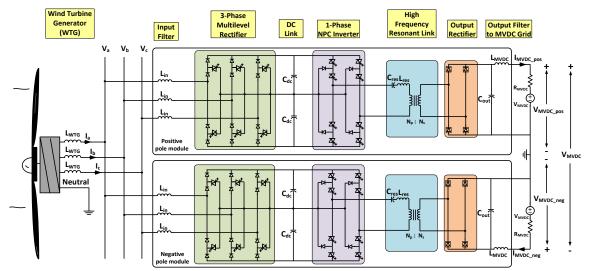

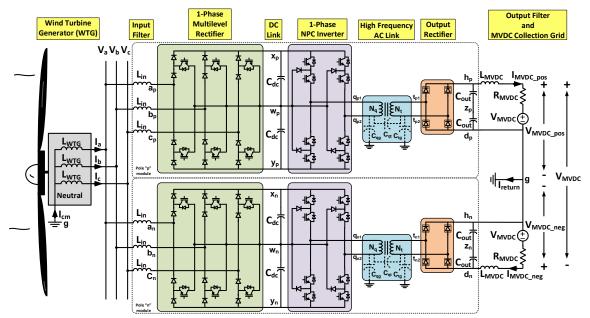

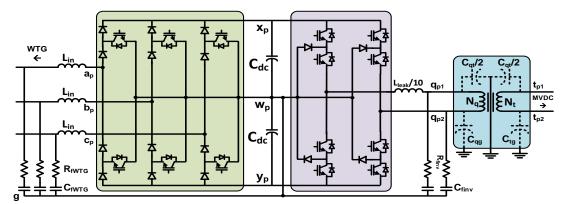

| Figure | 3-2. The proposed per-pole converter interface between WTG and MVDC collection grid using multilevel rectifier, NPC inverter and HF resonant AC link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure | 3-3. End-to-end detail of positive pole converter module showing output<br>current control scheme and DC link voltage control scheme. The DC link<br>control also implements boost PFC functionality through input reactive<br>power control                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure | 3-4: Simulated output current to MVDC grid and MVDC grid voltage in steady state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure | 3-5: WTG terminal voltages and currents. Note that the DC link voltages must be equal since both input rectifiers may simultaneously connect their DC links to the same phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure | 3-6: WTG terminal voltage and current for phase A of the positive pole module. Note terminal voltage with respect to ground is only $\pm$ half the DC link voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

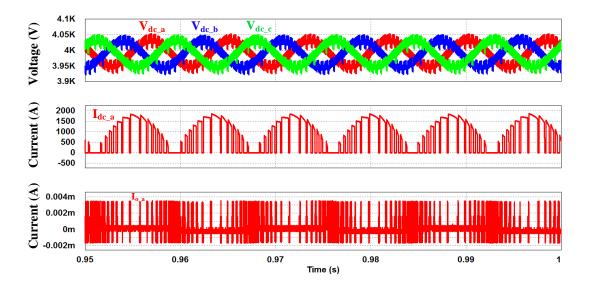

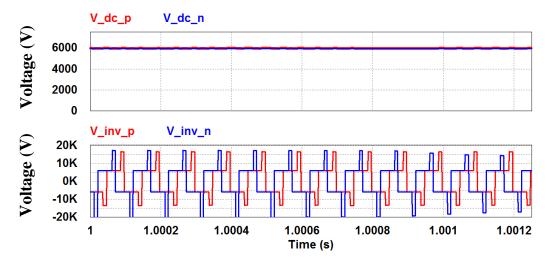

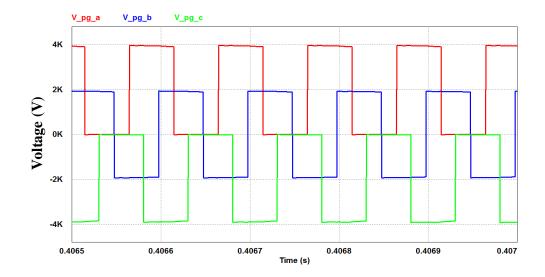

| Figure | 3-7: Positive and negative pole module DC link voltage as and inverter switching output voltages in steady state.                                                                                                                                                  | 53 |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

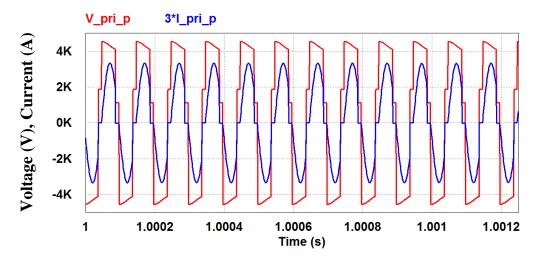

| Figure | 3-8: Steady state transformer voltage and current. Note ZCS and resonant frequency ripple riding on switching waveform.                                                                                                                                            | 53 |

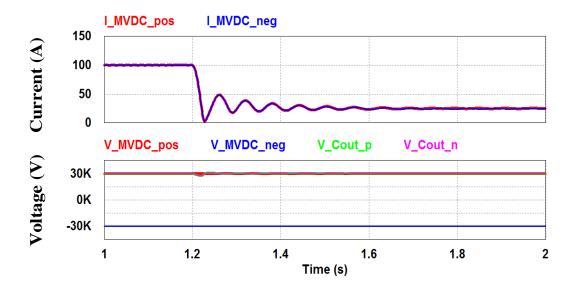

| Figure | 3-9: Output currents to MVDC grid and MVDC grid votlages during transient. While output current is drastically reduced, the output voltage remains fixed by the HVDC station and ripple is only a result of DC cable resistance.                                   | 55 |

| Figure | 3-10: Simulated DC link voltages and transformer primary currents for both positive and negative pole modules during transient. DC link voltage initially sags during spike in transformer current, but both settle to new steady state values within 0.5 seconds. | 55 |

| Figure | 3-11: WTG terminal current and voltage, as well as internal machine voltage during transient                                                                                                                                                                       | 66 |

| Figure | 3-12: AC input waveforms of prototype single phase multilevel rectifier                                                                                                                                                                                            | 58 |

| Figure | 3-13: DC link waveforms of prototype single phase multilevel rectifier                                                                                                                                                                                             | 59 |

| Figure | 4-1: WTG interface to offshore wind farm with +/-30 kV MVDC collection grid architecture and HVDC link to shore                                                                                                                                                    | 13 |

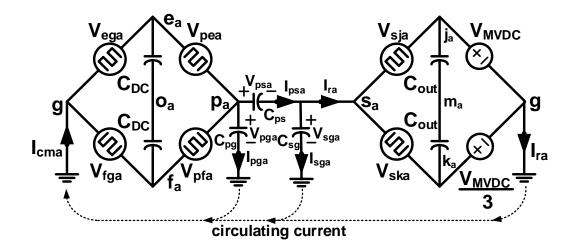

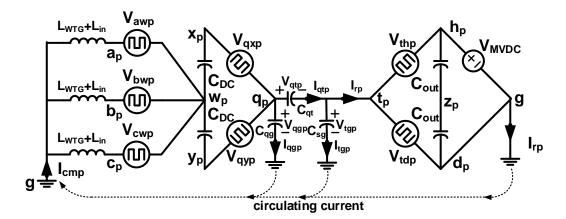

| Figure | 4-2: Per-phase interface using three end-to-end modules. Note the parasitic capacitances superimposed on each transformer. Outlined diodes indicate multiple devices in series                                                                                     | 78 |

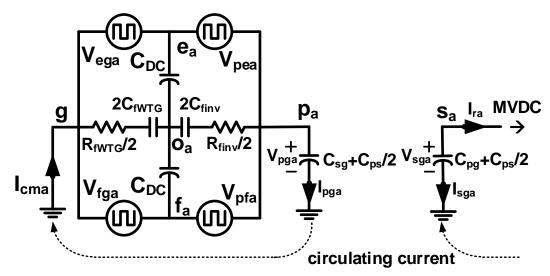

| Figure | 4-3: Detailed phase "a" CM equivalent circuit in per-phase approach                                                                                                                                                                                                | '8 |

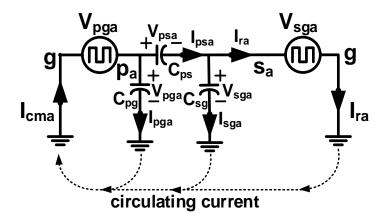

| Figure | 4-4: Simplified phase "a" CM equivalent circuit                                                                                                                                                                                                                    | '9 |

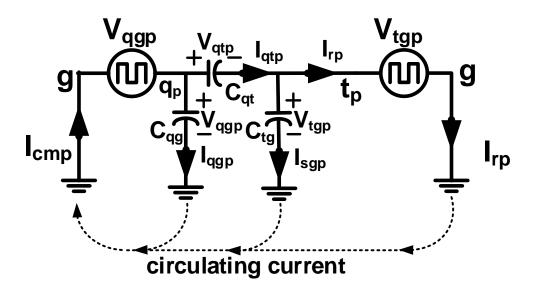

| Figure | 4-5: Per-pole interface using three end-to-end modules. Note the parasitic capacitances superimposed on each transformer                                                                                                                                           | 31 |

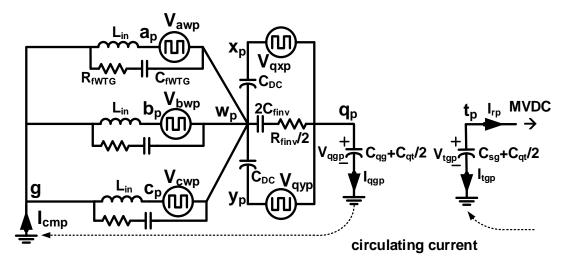

| Figure | 4-6: Detailed pole "p" CM equivalent circuit in per-pole approach                                                                                                                                                                                                  | 31 |

| Figure | 4-7: Simplified pole "p" CM equivalent circuit                                                                                                                                                                                                                     | 32 |

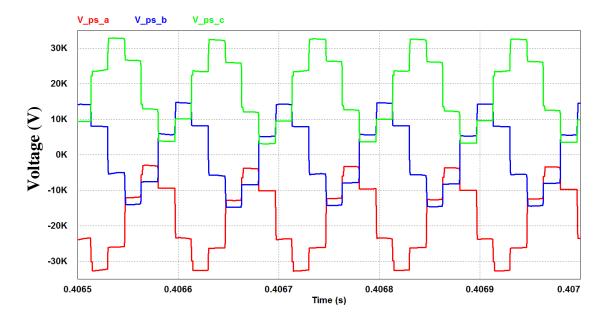

| Figure | 4-8: Voltage across Cpg in each phase of per-phase approach. Note that depending on WTG voltage phase, the DC value of each waveform in Figure 4-8 moves between -2 kV, 0 V, and +2 kV, hence each has approximately zero average as reflected in Table 4-2        | 34 |

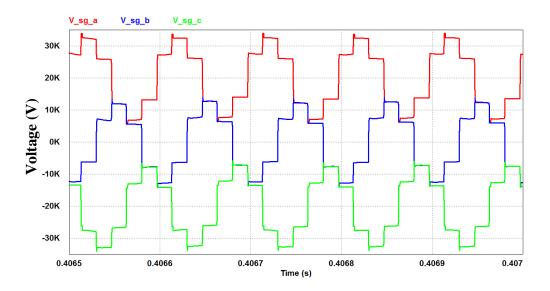

| Figure 4-9: Voltage across Csg in each phase of per-phase approach                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4-10: Voltage across Cps in each phase of per-phase approach85                                                                                                                                                                                                             |

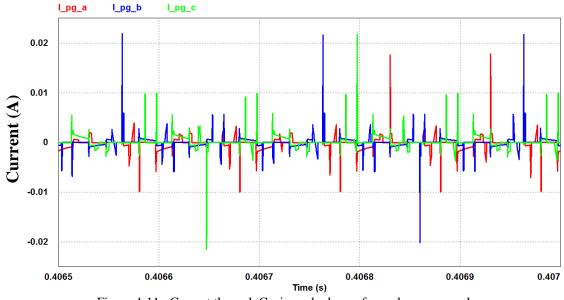

| Figure 4-11: Current through Cpg in each phase of per-phase approach85                                                                                                                                                                                                            |

| Figure 4-12: Current through Csg in each phase of per-phase approach                                                                                                                                                                                                              |

| Figure 4-13: Current through Cps in each phase of per-phase approach                                                                                                                                                                                                              |

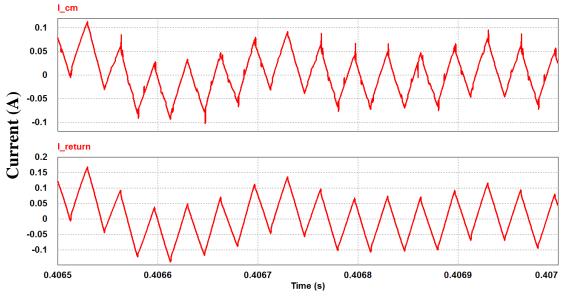

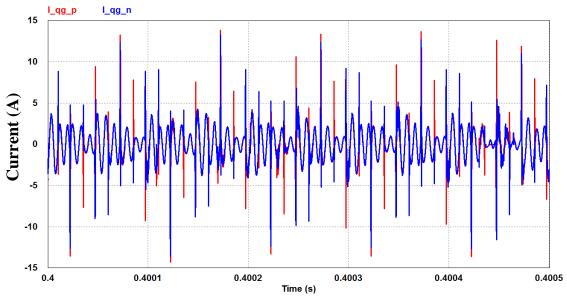

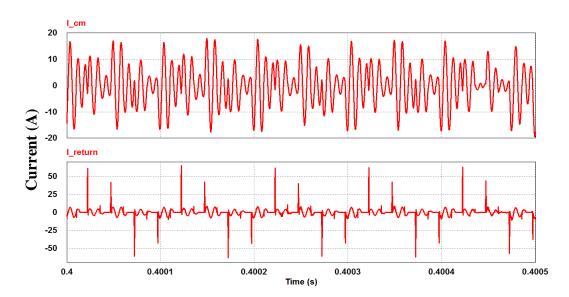

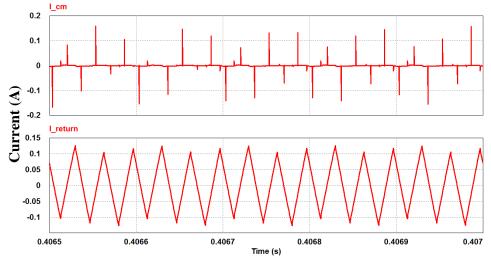

| Figure 4-14: Icm entering WTG neutral and Ireturn exiting MVDC ground                                                                                                                                                                                                             |

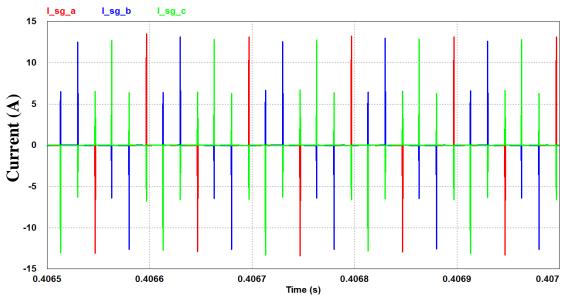

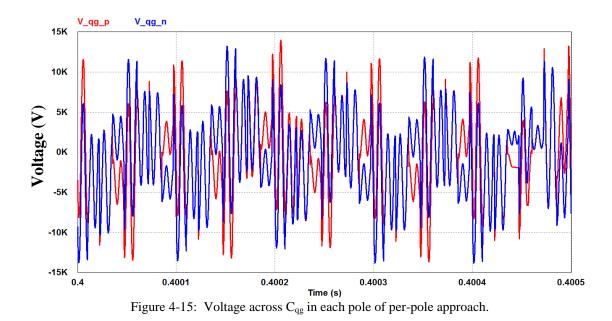

| Figure 4-15: Voltage across Cqg in each pole of per-pole approach                                                                                                                                                                                                                 |

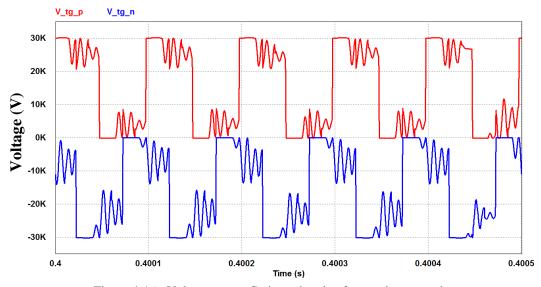

| Figure 4-16: Voltage across Ctg in each pole of per-pole approach                                                                                                                                                                                                                 |

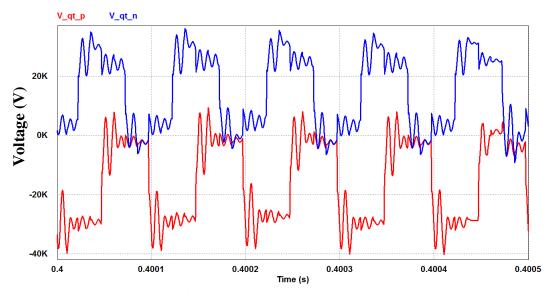

| Figure 4-17: Voltage across Cqt in each pole of per-pole approach                                                                                                                                                                                                                 |

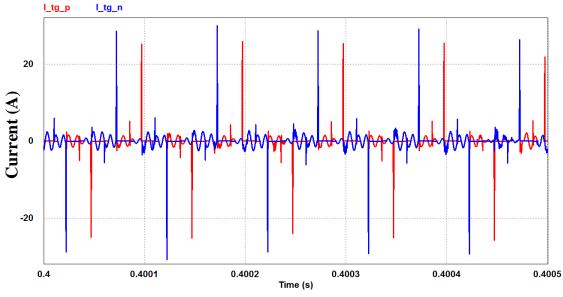

| Figure 4-18: Current through Cqg in each pole of per-pole approach                                                                                                                                                                                                                |

| Figure 4-19: Current through Ctg in each pole of per-pole approach                                                                                                                                                                                                                |

| Figure 4-20: Current through Cqt in each pole of per-pole approach90                                                                                                                                                                                                              |

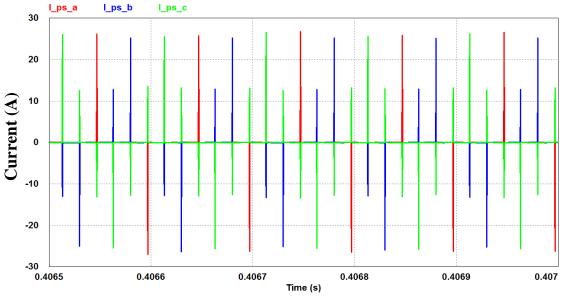

| Figure 4-21: Icm entering WTG neutral and Ireturn exiting MVDC ground90                                                                                                                                                                                                           |

| Figure 4-22: Phase "a" module with common mode filters and shielded transformer.<br>Note additional discrete inductance equal to transformer leakage is added at<br>inverter output to decouple Cdc and Cfinv when inverter switches are closed<br>and improve filter performance |

| Figure 4-23: Pole "p" module with common mode filters and shielded transformer.<br>Additional Lleak included as in per-phase case; see Figure4-2293                                                                                                                               |

| Figure 4-24: Phase "a" CM equivalent circuit with filter and shielding94                                                                                                                                                                                                          |

| Figure 4-25: Pole "p" CM equivalent circuit with filter and shielding                                                                                                                                                                                                             |

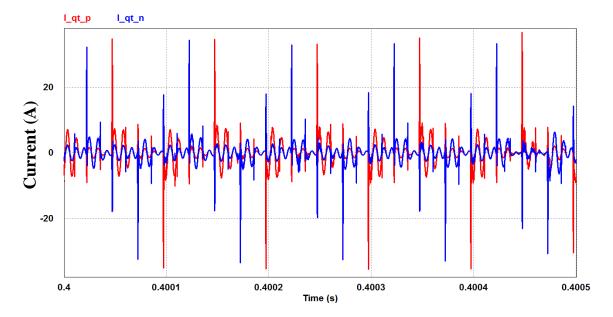

| Figure 4-26: Per-phase Icm and Ireturn with CM filter and HFT shield95                                                                                                                                                                                                            |

| Figure 4-27: Per-pole Icm and Ireturn with CM filter and HFT shield95                                                                                                                                                                                                             |

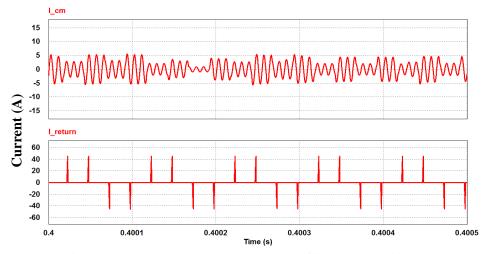

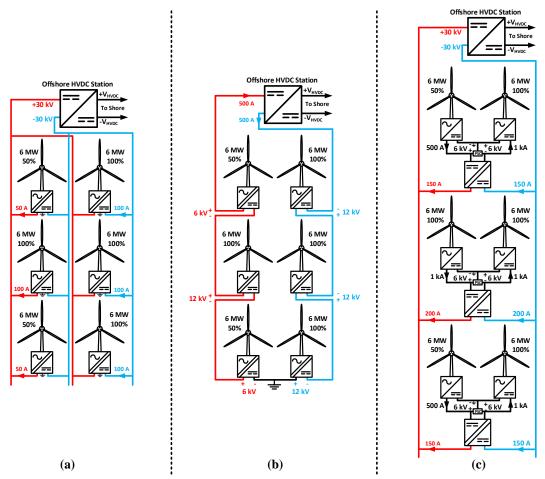

| Figure 5-1: Farm with six 6 MW WTGs using (a) parallel connection (b) series connection (c) proposed connection; case (b) is current sourced                                                                                                                                      |

| Figure 5-2: Details of power sharing converter                                                                                                                                                                                                                                    |

| Figure 5-3: Detail of series connected WTG pair. WTG neutral is ungrou<br>hence Ccm is included. Boxed devices are multiple series devices.                                                                                                                                     |                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

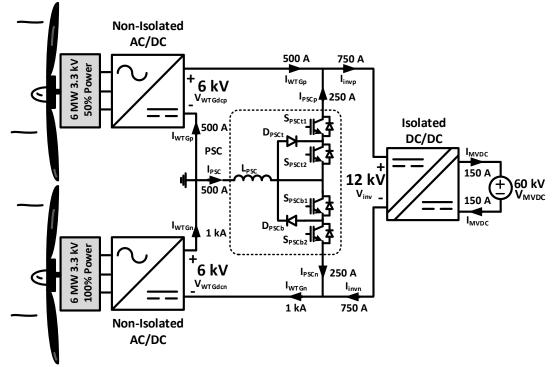

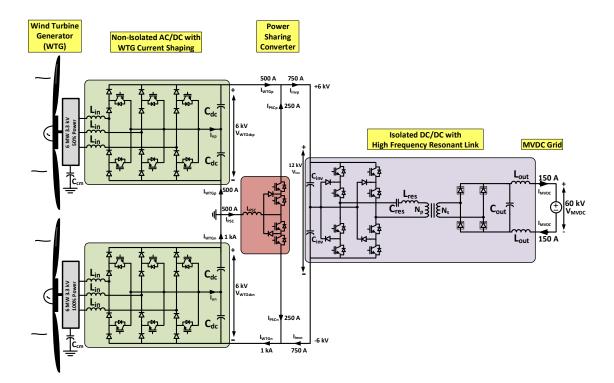

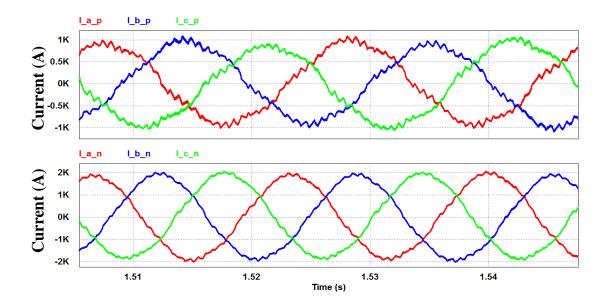

| Figure 5-4: Generator currents; note pole "p" generator currents (top) are less than pole "n" generator currents (bottom) since it is operating power. Also note pole "p" generator currents are approximately 48 79.4% of nominal frequency.                                   | at 50%<br>8 Hz, or |

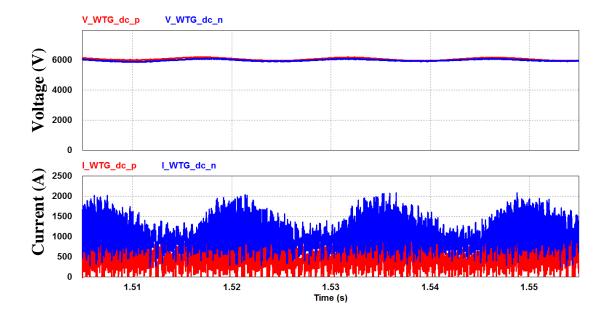

| Figure 5-5: Rectifier output DC link voltages (top) and currents (bottom).<br>value of pole "p" DC link current is approximately 500 A, while av<br>pole "n" current is approximately 1 kA. 3 MW are sourced by pole<br>WTG and 6 MW are source by pole "n" WTG                 | verage of<br>e "p" |

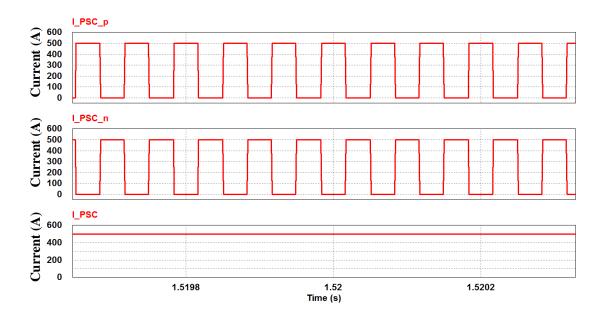

| Figure 5-6: Current in pole "p" PSC switch (top), pole "n" PSC switch (m<br>and PSC inductor (bottom). Steady state duty cycle is 50%, theref<br>average current is each switch is half IPSC. IPSC is difference bet<br>average of "p" and "n" DC link currents from Figure 5-5 | ore<br>ween        |

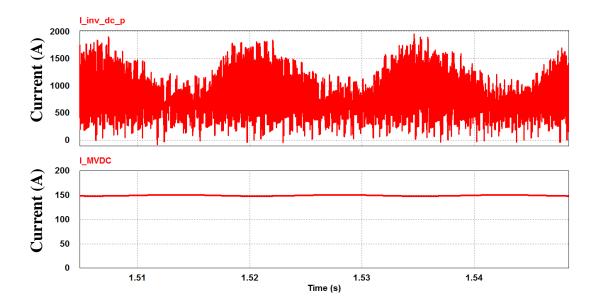

| Figure 5-7: Current into isolated DC/DC (top) and current injected into M grid (bottom). Average value of Iinv_dc_p is 750 A. MVDC grid is fixed by HVDC converter station at 60 kV pole-to-pole. Therefore 9 MW total are injected to MVDC grid.                               | voltage<br>ore,    |

## LIST OF TABLES

| Table 1-1: Outline of advantages and disadvantages of MVDC collection grids10    |

|----------------------------------------------------------------------------------|

| Table 2-1: Advantages and disadvantages of MVDC vs MVAC collection grid21        |

| Table 2-2: Volume distribution of normalizing point in volume trade study.    27 |

| Table 2-3: Case study input parameters                                           |

| Table 2-4: Case study output parameters                                          |

| Table 2-5: Lab-scale prototype hardware parameters    41                         |

| Table 3-1: Design Input Parameters   57                                          |

| Table 3-2: Design Output Parameters    57                                        |

| Table 3-3: Lab-Scale Prototype Design Parameters    68                           |

| Table 4-1: WTG-to-MVDC Interface Design Parameters    75                         |

| Table 4-2: Per-phase CM voltages and currents    91                              |

| Table 4-3: Per-pole CM voltages and currents                                     |

| Table 4-4: CM filter component values    93                                      |

| Table 4-5: Shielded & filtered per-phase voltages and currents                   |

| Table 4-6: Shielded & filtered per-pole voltages and currents       96           |

#### 1. INTRODUCTION AND LITERATURE REVIEW

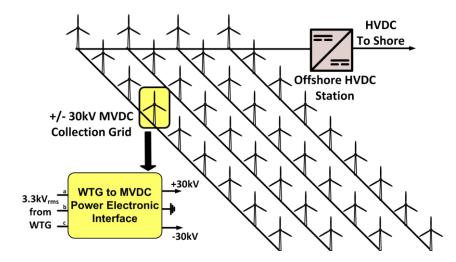

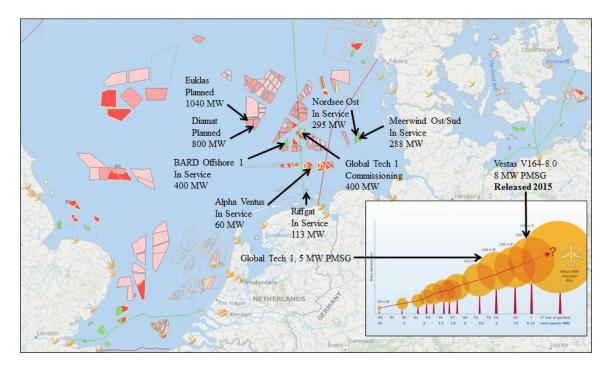

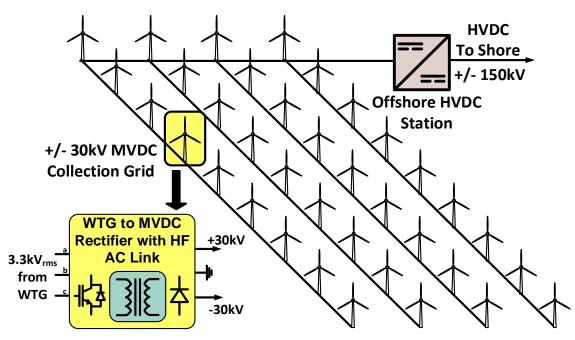

This work presents two novel power electronic methods for interfacing offshore wind turbine generators (WTGs) to medium voltage DC (MVDC) collection grids. The location of the proposed power electronic interfaces can be observed in Figure 1-1. The power electronic interfaces investigated in this work are proposed for WTGs rated for > 5 MW located in wind farms > 50 km from shore. While no offshore wind farms currently incorporate an MVDC collection grid, this work anticipates the necessity of such a topology based on the increasing trend in inter-turbine spacing and distance from shore.

The key elements that are addressed by this work include the important features that must be included in a power electronic interface for such an application, as well as its design, electrical behavior, and performance under various operating conditions.

Figure 1-1: Offshore wind farm with MVDC collection grid.

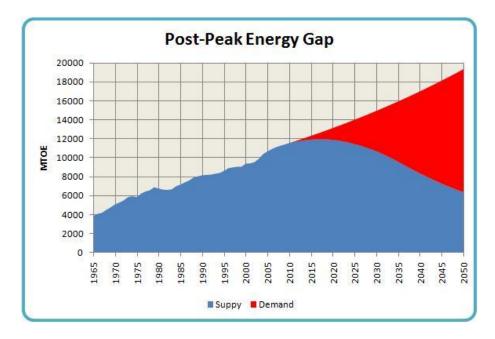

Considering the superposition of projected global energy supply and demand in Figure 1-2 it is clear that new energy resources must be developed to prevent a global energy shortfall [1]

Due to the constraints placed on energy development by policy designed to prevent global climate change, many nations are seeking to develop alternative energy resources that are both environmentally acceptable and economically viable [2].

As such, many nations for which it is a practical option have begun aggressively developing their offshore wind energy resources in an effort to secure reasonably priced and reliable energy while limiting climatological impact, improving energy security, and reducing dependence on less attractive alternatives like large nuclear or hydroelectric power facilities [3]-[5].

Figure 1-2: Illustration of projected global energy shortfall. Source: Paul Chefurka, 2008 [1]. Reused with courtesy of Paul Chefurka.

With a single 5 MW turbine capable of powering 3500 homes while eliminating 7200 tons of carbon dioxide and 160 tons of sulfur dioxide annually, offshore wind is an attractive alternative energy resource [6].

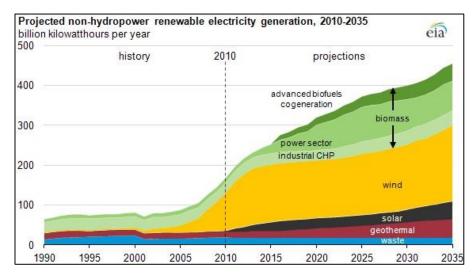

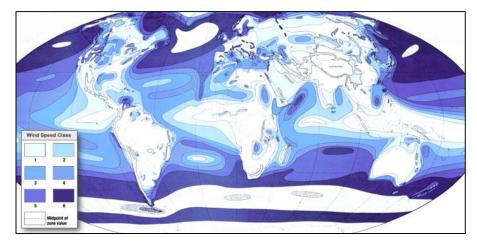

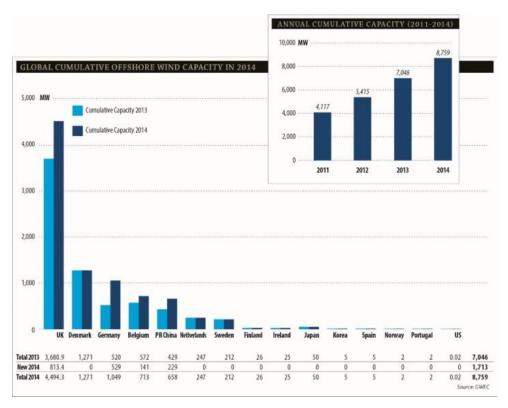

While much of the wind energy development projected by Figure 1-3 [7] is on land, there remains tremendous growth potential for offshore wind energy development as reinforced by Figure 1-4 [8] and recent growth shown in Figure 1-5 [9]

Figure 1-3: EIA projection of future renewable energy growth. Source: U.S. Energy Information Administration, 2012 [7]. *Reused with courtesy of the U.S. Energy Information Administration*.

Figure 1-4: Estimate of global wind energy resources. Source: U.S. Department of Energy, 1980 [8]. *Reused with courtesy of the U.S. Department of Energy.*

Figure 1-5: Recent development of offshore wind energy resources. Source: Global Wind Energy Council, 2015 [9]. *Reused with courtesy of the Global Wind Energy Council.*

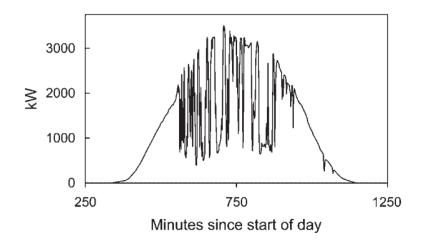

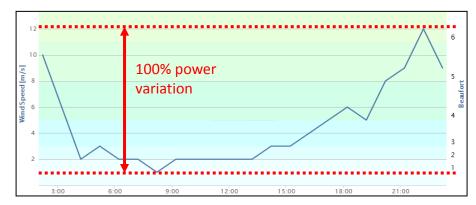

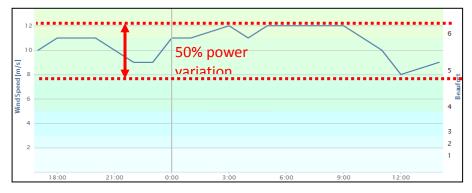

One of the key differentiators between offshore wind and other competing renewable energy resources is its dependability. For example, solar photovoltaic (PV) installations by their very nature must have practically zero output for nearly half of every day, and can suffer dramatic changes from near zero to full power as clouds interfere with the incident solar radiation. These characteristics are obvious in Figure 1-6 [10]. Offshore wind farms are even superior to their onshore counterparts in terms of intermittency. Figure 1-7 shows the wind speed over a 24-hour period at the 576 MW Altamont Pass wind farm in Livermore, CA dropping well below the typical WTG cut-in speed of 3.5 m/s for much of the day which[11]. The wind speed for a 24-hour period near Germany's 288 MW Meerwind Ost/Sud offshore wind farm, shown in Figure 1-8, only varies from 8 to 12 m/s, corresponding to an approximately 50% variation in WTG output power, far better than the 100% variation observed in Figures 1-6 and 1-7 [12].

Figure 1-6: Power production at TEP Springerville PV station. Source: Curtright & Apt, 2007 [10]. Reused with courtesy of John Wiley & Sons.

Figure 1-7: Altamont Pass wind speed on 18 April 2015. Source: WindFinder, 2015 [11]. Adapted with permission of WindFinder.

Figure 1-8: Wind speed near Meerwind Ost/Sud on 21/22 April 2015. Source: WindFinder, 2015 [12]. Adapted with permission of WindFinder.

Considering the tremendous recent growth and future potential outlined by Figures 1-4 and 1-5 it is important to consider the direction of that growth as outlined by Figure 1-9 [13],[14] to gain insight into the characteristics of future offshore wind farms [15]. While current wind farms like Global Tech I and BARD Offshore I are only designed to provide 200-400 MW and are sited about 100 km from shore, future projects several times that power are to be sited more than twice the distance from shore. Due to the large distance to shore of current wind farms, high voltage direct current (HVDC) is used to transport electrical energy to shore [16]. There is also a collection grid within the wind farm to aggregate the energy from each WTG before conversion to HVDC and transit to shore. Figure 1-10 shows the Riffgat wind farm.

Figure 1-9: Large offshore wind farms of the future will be sited further to sea and require more space between individual turbines. Background image source: 4COffshore, 2015 [14]. Adapted with permission of 4COffshore. Inset image source: European Wind Energy Administration 2011 [13]. Adapted with permission of the European Wind Energy Administration.

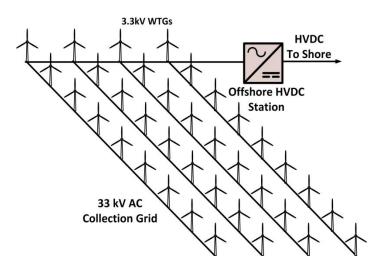

Current offshore wind farm collection grids are 3-phase medium voltage AC (MVAC) with a rated voltage of 33 kV, as shown in Figure 1-11. With HVDC already being used to transmit the energy to shore and inter-turbine spacing of nearly 1 km [17], an MVDC collection grid may be more suitable for use in future offshore wind farms.

Figure 1-10 Riffgat offshore wind farm and offshore substation. Photo: Siemens AG 2013 [18]. Reused with courtesy of Siemens AG.

Figure 1-11: Offshore wind farm with 33 kV 3-phase MVAC collection grid.

Figure 1-12: Example of an offshore HVDC converter station. Photo: Siemens AG 2014 [19]. *Reused* with courtesy of Siemens AG.

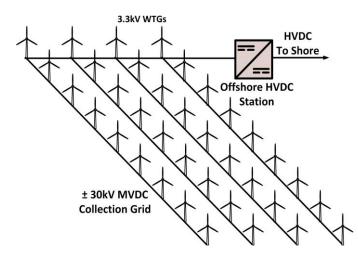

A practical example of the MVAC to HVDC converter described as "Offshore HVDC Station" in Figure 1-11 is shown in Figure 1-12. The structure of an offshore wind farm utilizing an MVDC collection grid is shown in Figure 1-13.

Figure 1-13: Offshore wind farm with  $\pm 30$  kV MVDC collection grid.

Compared to the traditional MVAC collection grid the proposed MVDC alternative exhibits the advantages and disadvantages outlined in Table 1-1 [20].

| MVDC Advantages                         | MVDC Disadvantages                         |

|-----------------------------------------|--------------------------------------------|

| No line frequency transformers present  | Addition of converter cost                 |

| Fewer undersea cables                   | Addition of converter losses               |

| More power flow control options         | Electromagnetic interference               |

| HVDC station interface is simplified    | Circulation currents & common mode voltage |

| Cable current & insulation ratings more | stress                                     |

| effectively used                        | Protection and control complexity          |

Table 1-1: Outline of advantages and disadvantages of MVDC collection grids.

The net result of the advantages and disadvantages outlined in Table 1 is that MVDC collection grids are better suited than MVAC collection grids for aggregated energy in large wind farms distant from shore, whereas MVAC grids may be better suited for use in small, dense wind farms only a few kilometers from shore.

Considering the future direction of offshore wind development described by Figure 1-9 it appears that MVDC collection grids may be a necessity for development of the next generation of offshore wind farms.

As such, this work proposes two candidate power electronic interfaces suitable for interfacing WTGs to an MVDC grid as described in Figure 1-1. The electrical behavior, control, and other salient characteristics of each approach are analyzed.

Several other power electronic approaches have been proposed for use as an interface between an offshore WTG and MVDC collection grid [21]-[29]. The previously proposed approaches can be divided into two broad groups: those that feature galvanic isolation and those that do not.

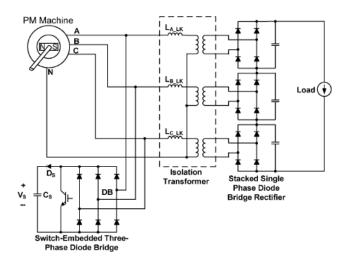

The first approach considered is proposed by Chen et al. [21]. This approach features a resonant topology that can provide high DC/DC gain, and thus is only proposed as the DC/DC stage in the WTG-to-MVDC interface as shown in Figure 1-14. Note that numerous active switches and tuned passive components are required.

Figure 1-14: Resonant interface proposed by Chen et al. © 2013 IEEE [21]. Adapted with permission of the IEEE.

Structure of module #i. (a) SL-based module. (b) DS-based module.

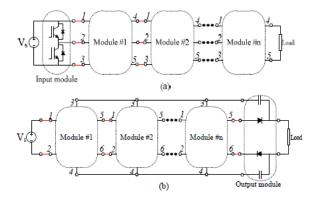

Figure 1-15: Modular resonant DC/DC proposed by Parastar et al. © 2014 IEEE [22]. Adapted with *permission of the IEEE*.

The second non-isolated approach to consider is that proposed by Parastar et al. [22] in which they describe a modular resonant converter suitable for the DC/DC stage of the WTG-t-MVDC interface as shown in Figure 1-15. Similar to the approach proposed by Chen et al. this topology requires numerous active switches and tightly tuned passive elements to achieve high DC/DC voltage gain.

A third non-isolated approach relevant to this work is Jovcic's capacitivecoupled topology shown in Figure 1-16 [23]. Note the high peak-to-average current at the output capacitor in this approach.

While non-isolated topologies may be suitable for the DC/DC gain stage alone, the need to provide galvanic isolation is present in this application. Therefore, others have proposed both DC/DC and end-to-end approaches that include galvanic isolation.

Figure 1-16: Capacitive coupled approach proposed by Jovcic. © 2009 IET [23]. Adapted with *permission of the IET.*

The approach proposed by Lam et al. [24] considers a soft-switching converter and diode rectifier output, shown in Figure 1-17. The input side of this approach requires numerous series-connected capacitors that must be balanced, and the output capacitor lacks the ability to be series connected with other WTGs in the offshore wind farm.

Figure 1-17: Isolated DC/DC approach proposed by Lam et al. © 2014 IEEE [24]. Adapted with *permission of the IEEE*.

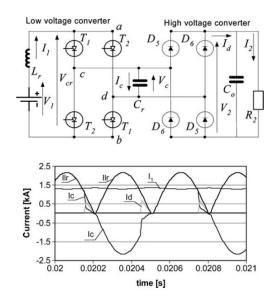

Figure 1-18: Medium frequency generator approach proposed by Prasai et al. © 2008 IEEE [25]. Adapted with permission of the IEEE.

The approach proposed by Prasai et al. [25], shown in Figure 1-18, assumes a medium frequency generator operating at approximately 1200 Hz to allow a medium frequency transformer to be used without then need for frequency conversion power electronics at the front-end. While this approach does feature a compact medium frequency transformer and only a single active switch, the medium frequency generator would require either a large number of poles or a large gearbox to yield the desired medium frequency from the low frequency turbine. Also note the proposed output voltage is only a few kV, necessitating another voltage boosting stage before the final interface with the MVDC grid.

Previous work has not only shown the necessity of using a DC grid to collect wind turbine energy, but has investigated several power conversion and control strategies for wind turbines in general [30]-[56]. This work provides a basis for the power electronic interface approaches proposed in this work.

In this work we address the problem of how to connect each turbine to an MVDC collection grid. Each WTG must be connected to the MVDC grid safely, reliably, and efficiently in order to build a wind farm more than 150 km from shore that can harvest the best wind energy resources with less visual and environmental impact.

The problem is that modern wind turbines output their energy at 3,300 volts AC, but the DC grid must be at least 30,000 volts DC. So the turbines can't be directly connected to the DC grid; they need some sort of interface to take the power from the turbine, process it, and then inject it into the DC grid.

This work presents two novel power electronic interfaces suitable for integrating state-of-the-art offshore wind turbine generators (WTGs) with medium voltage DC (MVDC) collection grids. The first interface is based on three end-to-end power electronic modules, one per WTG phase, hence it is considered a "per-phase" interface. The second interface is based on the same end-to-end module structure with a three-phase input rectifier at the module front-end and one module per MVDC pole, hence it is considered a "per-pole" interface. Both interfaces utilize a high frequency transformer (HFT) to provide galvanic isolation while reducing interface mass and volume. Module design, steady-state and dynamic electrical behavior, and practical control strategies are developed for both interfaces.

Sections 2 through 5 describe the results and impacts of this research in detail. Each section focuses on a unique component of the overall research. Section 2, *A New Wind Turbine Interface to MVDC Collection Grid with High Frequency Isolation and Input Current Shaping*, describes the design, analysis, and key features of a new per-phase approach for connecting individual offshore wind turbines to a medium voltage DC collection Grid. Simulation and experimental results demonstrate the desired high displacement power factor at the WTG terminals

Section 3, An Improved Offshore Wind Turbine to MVDC Grid Interface using High Frequency Resonant Isolation and Input Power Factor Control, outlines an advanced per-pole approach for the wind turbine to MVDC grid interface which requires less DC link capacitance and the potential for improved common mode voltage balancing among high frequency transformers.

Section 4, *Exploring Common Mode Voltage Stress and Circulating Currents in Offshore Wind Turbine to MVDC Collection Grid Interfaces*, investigates common mode voltage stress and circulating currents in both per-phase and per-pole interfaces proposed in the previous sections. This section also proposes and analyzes a circulating current mitigation strategy that reduces ground current returning to the WTG neutral in both proposed interfaces.

Section 5, *A Power Sharing Scheme for Series Connected Offshore Wind Turbines in a Medium Voltage DC Collection Grid*, analyzes how power electronic converter blocks from the proposed interfaces in previous sections can be combined with a power sharing converter to allow pairs of series connected WTGs to be interfaced to an MVDC collection grid. Simulation results demonstrate operation in power sharing mode with a power unbalance of 1:2 between series connected WTGs.

# 2. A NEW WIND TURBINE INTERFACE TO MVDC COLLECTION GRID WITH HIGH FREQUENCY ISOLATION AND INPUT CURRENT SHAPING<sup>\*</sup>

A new power electronic interface suitable for the integration of next-generation offshore wind turbines with medium voltage DC (MVDC) collection grids is introduced in this work. A practical design case study provides guidance for further development of the proposed interface. Detailed simulations show acceptable operation of the proposed approach from 25% to 100% rated power, including step changes in WTG input power. Simulation results demonstrate >0.95 displacement power factor magnitude, near sinusoidal WTG current, continuous output current, stiff DC link voltages, and inverter zero-current switching (ZCS). Preliminary hardware results from a 250 V<sub>dc</sub>, 700 W labscale prototype are introduced, demonstrating input rectifier boost characteristic with a dominant input current fundamental and >0.95 displacement power factor magnitude. The DC link current has a large peak-to-average ratio as expected, and DC link capacitor voltage balance is achieved via adjustment of relative duty cycles between high- and low-side active rectifier switches.

### 2.1 Introduction

As people around the globe continue to achieve higher standards of living and economic power, humanity must continually develop new energy resources to sustain

<sup>&</sup>lt;sup>\*</sup> Reprinted, with permission, from Daniel, M.T.; Krishnamoorthy, H.S.; Enjeti, P.N., "A New Wind Turbine Interface to MVDC Collection Grid with High Frequency Isolation and Input Current Shaping," IEEE Journal of Emerging and Selected Topics in Power Electronics (JESTPE), Volume 3, Issue 4, December 2015. © 2015 IEEE.

the ever-growing demand for services such as transportation, communication, computing, entertainment, etc[2]. To simultaneously satisfy the constraints placed on energy production by anticipated climate change, many nations are seeking to develop offshore wind energy as an environmentally and economically acceptable source of sustainable energy for the future[3]-[5].

Offshore wind farms are being sited further from shore than ever before[13], with Germany's Global Tech 1 farm, completed in 2014 and currently undergoing commissioning, constructed nearly 100 km out to sea[57]. In addition, state-of-the-art WTGs are available at 5 MW at 3.3 kV requiring nearly 1 km of inter-turbine spacing, as in the case of Germany's Alpha Ventus farm[17]. With 8 and 10 MW WTGs likely entering service in the near future [15], turbine spacing in excess of 1 km may be necessary for efficient operation.

The great distance to shore has made high voltage direct current (HVDC) a necessity in transporting offshore wind energy to customers on shore to eliminate reactive power requirements and reduce cabling cost and complexity[16].

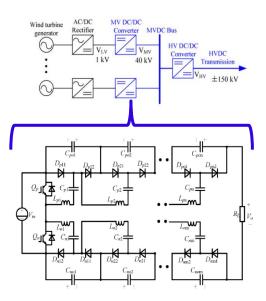

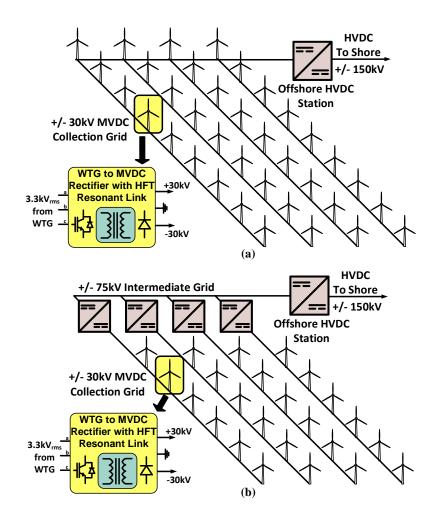

The growing inter-turbine spacing, combined with the necessity of using an HVDC link to shore makes the use of an MVDC collection grid architecture more suitable for aggregating WTG energy within the farm than the traditional MVAC alternative. Several architectures have been proposed for interfacing MVDC collection grids to the HVDC link to shore [21],[24],[26],[27]. Figure 2-1 illustrates an MVDC collection grid architecture with two possible approaches for interfacing the MVDC grid to the offshore HVDC converter station.

Compared to a traditional MVAC collection grid [26], the MVDC option has the advantages and disadvantages listed in Table 2-1, making the MVDC option a net disadvantage for small, dense wind farms close to shore, and a net advantage for large, distant wind farms.

Figure 2-1: Example of offshore wind farm with WTG to  $\pm 30$  kV MVDC collection grid interface. The MVDC grid can then be (a) interfaced directly to the offshore HVDC converter station [21], [24] or (b) boosted to an intermediate voltage level before conversion to HVDC for transmission to shore as proposed in [26], [27].

| MVDC Advantages                                    | MVDC Disadvantages                               |

|----------------------------------------------------|--------------------------------------------------|

| MVDC Advantages                                    | NIVDC Disauvantages                              |

| • Elimination of line frequency transformers.      | <ul> <li>Added cost of converter</li> </ul>      |

| • Simplification of collection grid undersea       | <ul> <li>Added losses of converter</li> </ul>    |

| cabling.                                           | • Electromagnetic interference                   |

| • Mitigation of inter-turbine power flow issues.   | • Common mode voltage stress and circulating     |

| • Simplification of HVDC converter station         | ground currents                                  |

| interface.                                         | • Complexity of protection, control, and circuit |

| • More effective use of cable current & insulation | breaking schemes.                                |

| ratings.                                           |                                                  |

|                                                    |                                                  |

Table 2-1: Advantages and disadvantages of MVDC vs MVAC collection grid

This work focuses on a new approach to interfacing individual WTGs to the MVDC collection grid. Several methods have been proposed for this interface. A nonisolated resonant switched capacitor (RSC) topology is proposed in [21] that utilizes cascaded RSC modules to achieve significant voltage gain, while the authors of [24] propose a modular multilevel inverter utilizing resonant ZVS to achieve voltage gain and isolation. In [26] and [27] multiple converter stages are proposed between the WTG and the HVDC link to shore, potentially requiring additional offshore platforms. Medium frequency generators have been proposed as the basis for WTGs interfacing to an MVDC grid via a simple diode rectifier in [25], although this alternative generator may be too large for a WTG due to requiring a large number of poles or gearbox to attain medium frequency operation. A modular multilevel converter architecture is proposed in [28] although it requires a four- armature machine to achieve substantial DC output voltage and does not provide galvanic isolation. A bridgeless PFC input scheme is proposed in [29], along with a complicated transformer connection to provide isolation. Parastar and Seok [22] propose a modular RSC approach lacking isolation, similar to the approach in [21]. Jovcic [23] proposed a non-isolated capacitive-coupled inverter topology with applications in MW-scale DC/DC conversion; however the lack of isolation and large peak-to-average ratio of the output capacitor current make this converter unsuitable to the application proposed in this paper. A multilevel active neutral point clamped (NPC) approach is proposed in [58], while a single-stage non-isolated resonant approach is considered in [59]. Deng and Chen [60] propose an NPC-based isolated approach utilizing a passive filter on the medium frequency transformer primary.

This work proposes a per-phase approach utilizing high frequency resonant isolation while providing output current control to the MVDC bus and input current shaping for PFC at the WTG [61]. A per-pole version of the proposed approach is presented in [62]. Compared to [21]-[29],[58]-[60] the proposed approach has the following advantages:

- 1) Provides "end-to-end" conversion interface from WTG to MVDC grid

- 2) Provides galvanic isolation

- 3) High output diode rectifier device rating utilization

- 4) Fewer inverter input capacitor voltage levels to balance

- 5) Uses conventional direct-drive synchronous generator.

- 6) Compact high frequency transformer.

- 7) Resonant link allows ZCS, which more suited to IGBTs than ZVS [63].

- 8) Input current shaping capability for PFC.

- Large generator inductance an advantage for multilevel rectifier boost PFC operation.

#### 2.2 Proposed Approach

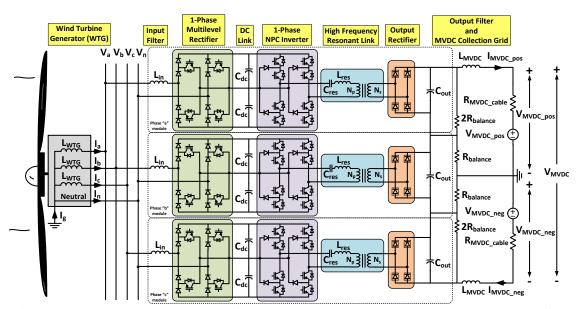

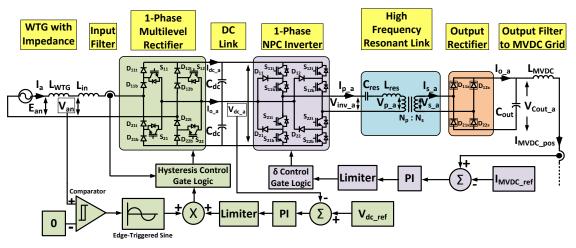

Figure 2-2 provides a high-level illustration of the proposed approach, while Figure 2-3 details a single end-to-end phase module including the two control schemes. For the proposed approach a direct-drive permanent magnet synchronous generator (DD-PMSG) is assumed. This type of machine has a synchronous reactance of approximately 0.6 per-unit, which is inversely proportional to machine volume [64], [65]. The MVDC voltage is considered to be fixed by the HVDC converter, necessitating current control at the converter output. Hence black-start from a de-energized state is achieved by first energizing the offshore HVDC station and MVDC grid from the shore-based HVDC converter station, which is similar to how a traditional VSC HVDC would be energized.

Figure 2-2: The proposed converter interface between WTG and MVDC collection grid using multilevel input rectifier, NPC inverter and high frequency resonant AC link.

Figure 2-3: End-to-end detail of phase "a" converter module showing output current control scheme and DC link voltage control scheme. The DC link control also implements boost PFC functionality through input current shaping.

Once the MVDC collection grid is energized to the appropriate MVDC voltage individual WTGs may begin injecting power to the MVDC collection grid.

## 2.2.1 Front-end Multilevel Rectifier

Due to the large generator impedance a boost-type input rectifier is desirable. The proposed single phase multilevel rectifier adapted from [66] satisfies this requirement while also providing input current shaping capability and a DC bus neutral point which allows each semiconductor device to only block half the DC bus voltage. Note that the DC bus voltage must be chosen to be greater than the peak of the internal WTG voltage for boost operation. The DC link capacitor  $C_{dc}$  must be designed to suppress the second harmonic of the input current according to (2.1) to achieve a stiff DC bus voltage. A suitable design margin must be added to the results of (2.1), (2.5), and (2.7) to sufficiently suppress the desired frequency.

$$C_{dc} = \frac{1}{2} \left[ \frac{1}{\omega_{WTG}} \right] \left[ \frac{I_{dc}}{RF_{Vdc}V_{dc}} \right]$$

(2.1)

The input inductance  $L_{in}$  is chosen to be small compared to  $L_{WTG}$  and allows for a voltage sensing point separated from the switching at the input terminals of the multilevel rectifier.

# 2.2.2 HF Inverter and Resonant AC Link

The NPC inverter, dual of the proposed multilevel rectifier, also allows the DC bus voltage to be shared between its component semiconductor devices. This approach uses quasi-square wave switching with free-wheeling zero states provided by closing either both positive or negative pole pairs of IGBTs.

The resonant filter is designed via (2.2), (2.3), and (2.4) to limit the distortion of the primary transformer current and voltage by designing for a maximum allowable third harmonic voltage at the transformer primary winding as described in [67]. The HF transformer turns ratio must be designed to allow the output current controller to boost the DC link voltage to 1/3 the bipolar MVDC voltage with an acceptable duty cycle.

$$Q_{\rm res} = \sqrt{\frac{\frac{V_{\rm inv,3}^2}{v_{\rm p,3}^2} - 1}{2.67^2}}$$

(2.2)

$$L_{\text{res}} = \left[\frac{Q_{\text{res}}}{\omega_{\text{res}}}\right] \left[\frac{N_p}{N_s}\right]^2 \left[\frac{V_{\text{MVDC}}^2}{9P_{\text{WTG}}}\right] - L_{\text{leak}}$$

(2.3)

$$C_{\text{res}} = \frac{1}{Q_{\text{res}}\omega_{\text{res}} \left[\frac{N_p}{N_s}\right]^2 \left[\frac{V_{\text{MVDC}}^2}{9P_{\text{WTG}}}\right]}$$

(2.4)

The inverter switching frequency was selected by performing a high level trade study of the effects of WTG voltage and switching frequency on the overall volume of the proposed power electronic interface at a given power level of 8 MW and MVDC grid 25

voltage of  $\pm 30$  kV. For this analysis the volume of the output diode rectifier was considered fixed as it is determined primarily by the output power and MVDC voltage. The input rectifier and inverter volumes were scaled linearly with the number of devices, taken to be the 5SNA 1500E330305 IGBT [68] and 5SDF 20L4521 diode [69], required for sufficient voltage blocking and current conduction since additional gate drives, snubbers, balancing networks, busbars, etc., are required for each additional device. Total heatsink volume in each converter was scaled linearly with total converter losses to reflect that heatsink surface area must increase linearly with losses to achieve the same thermal resistance [70], and hence the same junction temperature, at the higher level of losses. Since most heatsinks are composed of thin fins, an increase in surface area (i.e. adding fins) yields the same proportion increase in heatsink volume, meaning that it is appropriate to scale heatsink volume linearly with losses. The device losses themselves are considered to scale with the square of the device current (conduction losses) and linearly with switching frequency (switching losses). The transformer volume is taken to scale linearly with the number of turns necessary to achieve the required primary voltseconds at a given DC link voltage and switching frequency; hence the transformer volume scales linearly with voltage at a given frequency and by the inverse square root of frequency at a given voltage. This is expected since inductance, and hence turns<sup>2</sup>, must scale proportionally with volt-seconds, meaning a transformer operating at a 10x higher frequency only requires 1/10 the applied volt-seconds per cycle and hence only  $1/\sqrt{10}$  as many turns. Once the relative volume of each component was calculated across the range of WTG voltages and inverter frequencies each point was normalized against the 500 V<sub>rms</sub> WTG, 1 kHz inverter case, given the volume distribution summarized in Table 2-2 for the overall system at that point [71]. The resulting surface representing normalized converter interface volume over a range of WTG voltages and inverter frequencies is given in Figure 2-4. Note that at while the volume due to power electronics increases at both high voltage and high current the result of a reduction in transformer size at higher frequencies yields an overall lower volume solution across all voltage levels studied. Hence the design proposed in this work operates at 10 kHz as it provides a minimum volume for the given conditions. While implementing a 2-3 MVA, 10 kHz transformer may seem impractical, recent work [72], [73] has shown that 1-2 MVA can be processed by transformers operating from 15-20 kHz. From these promising results we can infer that the technical barriers to constructing the proposed HFT can be overcome.

| Volume Component  | Contribution to Total System Volume |

|-------------------|-------------------------------------|

| Input Rectifier   | 25%                                 |

| DC Link Capacitor | 25%                                 |

| HF Inverter       | 25%                                 |

| HF Transformer    | 25%                                 |

Table 2-2: Volume distribution of normalizing point in volume trade study.

Figure 2-4: Surface describing normalized volume of proposed approach at various WTG voltages and inverter frequencies. The star indicates the chosen operating point studied in this work. The inverse square root effect of transformer volume scaling, as well as discontinuities when devices are added, can be clearly observed.

#### 2.2.3 Output Rectifier to MVDC Grid