# DYNAMIC VOLTAGE AND FREQUENCY SCALING TECHNIQUES FOR CHIP MULTIPROCESSOR DESIGNS

A Dissertation

by

### JAE YEON WON

### Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

| Chair of Committee,    | Jiang Hu         |

|------------------------|------------------|

| Co-Chair of Committee, | Paul V. Gratz    |

| Committee Members,     | Le Xie           |

|                        | Radu Stoleru     |

| Head of Department,    | Miroslav Begovic |

August 2015

Major Subject: Computer Engineering

Copyright 2015 Jae Yeon Won

#### ABSTRACT

Due to chip power density limitations as well as the recent breakdown of Dennard's Scalingover the past decade, performance growth in microprocessor design has largely been driven by core scaling. These trends have led to Chip Multi-Processor(CMP) designs, currently with tens of cores, and expected to grow to the thousands in the pursuit of exascale computing. The more complicated CMP design is more leading power consumption relatively in computer architecture. The increased power consumption generates thermal issues, and so performance degradation. Therefore, it is certain that power efficient algorithm in CMP and main memory are essential. For the power efficiency, we focus on dynamic voltage/frequency scaling (DVFS) techniques for CMP and main memory.

In the first work, we focus on the "uncore", consisting of an on-chip communication fabric and shared LLC in CMP. The uncore now occupies as much as 30% of the overall die area, which is not negligible in CMP design, but has rarely researched. We find there are predictable patterns in uncore utility which point towards the potential of a proactive approach to uncore power management. In this work, we utilize artificial intelligence principles to proactively leverage uncore utility pattern prediction via an Artificial Neural Network (ANN).

Even though the uncore takes non-negligible portion of CMP power consumption, processor cores still exist as major power consumers. For core DVFS, We explore a novel approach with the potential to achieve synergistic energy-savings *and* performance gain in chip multiprocessors (CMPs). In current designs, performance must typically be traded-off to achieve energy savings or, conversely, performance gains come with significant energy overhead. Resources shared by processor cores, such as on-chip interconnect and shared memory, play an increasingly critical role in determining the overall CMP performance. Our key observation is that per-core DVFS can be used as a client regulation mechanism for the shared resources. Based on this observation, we propose a new DVFS technique inspired by TCP Vegas, a congestion control protocol from the IP-networking domain.

In addition to uncore in CMP, main memory is also critical shared resource in total system. As uncore is critical resource for CMP performance while occupying critical portion of total CMP energy consumed, main memory is also critical for total performance and accounts for large fraction of total energy consumption. Most conventional approaches focused on utilization of cores and memory only for memory power management. We found, however, the uncore plays an important role of total system performance and its utilization must be considered as well for memory power management. From the observation, we propose shared resource utilization aware power management technique for main memory. Our technique chooses low V/F level of memory for some congested case in uncore, and so derives negligible performance degradation while saving more energy by the low V/F level. We also proposed coordination policies to avoid oscillation issues among individual DVFS techniques (i.e. over energy saving or over performance increment).

Full system simulations on PARSEC benchmarks show that our coordinated technique reduces total energy dissipation by over 47% across all benchmarks with less than 2.3% performance degradation.

## DEDICATION

To my wife

#### ACKNOWLEDGEMENTS

First of all, I would like to give my appreciations to my advisers, Dr. Jiang Hu and Dr. Paul Gratz. I was very grateful to have had working with them during my doctoral studies. Their advises were very helpful for my researches and even beyond researches for my future life. Especially, I would like to take this chance to thank Dr. Jiang Hu for taking care of my family when I had my little kid. Also, I would like to thank my committee members, Dr. Le Xie and Dr. Radu Stoleru. Their comments and advises about my dissertation made my dissertation and researches more concrete and robust.

My appreciations go to all my friends in our research group. Also, I thank Chia-Yu Wu and Dr. Yong Zhang for your advises and discussions. I could have pleasant life during my studies at Texas A&M through the discussions with you.

I also thank my father and mother to encourage me pursuing my doctoral degree. Sincerely, I appreciate for your dedication of your whole life for me. Also, I would like to thank my sweeties, Ashley and Aiden to wake me up with big smiles every day. From deep down in my heart, I would like to give special thanks to my wife, Eunyoung Lee for your dedicated love to me.

Finally, the fund supporting from Korean government, National Institute for International Education is acknowledged.

### NOMENCLATURE

- DVFS Dynamic Voltage Frequency Scaling

- CMP Chip Multi-processor

- V Voltage

- F Frequency

- ANN Artificial Neural Network

- PI Proportional Integral

- LLC Last Level Cache

- PCU Power Control Unit

- ED Energy Delay product

- E Energy

- D Delay(Run-Time)

- RTT Round Trip Time

## TABLE OF CONTENTS

|     |                                                                | $\operatorname{Pa}_{i}$                                                    | ge                        |

|-----|----------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------|

| AB  | STR.                                                           | ACT                                                                        | ii                        |

| DE  | DICA                                                           | ATION                                                                      | iv                        |

| AC  | KNC                                                            | WLEDGEMENTS                                                                | v                         |

| NO  | MEN                                                            | NCLATURE                                                                   | vi                        |

| TA  | BLE                                                            | OF CONTENTS                                                                | vii                       |

| LIS | T OI                                                           | F FIGURES                                                                  | ix                        |

| LIS | T OI                                                           | F TABLES                                                                   | xi                        |

| 1.  | INTI                                                           | RODUCTION                                                                  | 1                         |

| 2.  | BAC                                                            | KGROUND AND RELATED WORK                                                   | 8                         |

|     | <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> </ol> | 2.2.1 PI Controller                                                        | 8<br>11<br>13<br>13<br>16 |

| 3.  |                                                                | INE LEARNING IN ARTIFICIAL NEURAL NETWORKS FOR IMP<br>ORE POWER MANAGEMENT | 18                        |

|     | 3.1                                                            | 3.1.1ANN Controller Architecture                                           | 18<br>18<br>21<br>28      |

|     | 3.2                                                            | 0                                                                          | 30                        |

|     | 3.3                                                            |                                                                            | 32                        |

|     |                                                                | 1 1                                                                        | 32                        |

|     | 3.4                                                            |                                                                            | 34<br>42                  |

| 4. |                                   | CRGY SAVINGS WITHOUT PERFORMANCE LOSS THROUGH RE-         CRCE SHARING DRIVEN POWER MANAGEMENT         44                                                                                                                                          | 4                |

|----|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|    | 4.1                               | Resource Sharing Driven Per-Core DVFS444.1.1TCP Vegas in Network Control444.1.2Fairness though TCP Vegas444.1.3TCP-Vegas Based DVFS Control44                                                                                                      | 5                |

|    | <ul><li>4.2</li><li>4.3</li></ul> | Experimental Results564.2.1Experiment Setup564.2.2PARSEC Application Cases and Analysis56Conclusion56                                                                                                                                              | 0                |

| 5. |                                   | ORDINATED DYNAMIC VOLTAGE FREQUENCY SCALING TECH-         UE FOR MAIN MEMORY       66                                                                                                                                                              | 0                |

|    | 5.1<br>5.2                        | Coordinated Memory DVFS with CMP Power Management665.1.1Shared Resource Utilization Aware Memory DVFS665.1.2Coordinated DVFS policy66Experimental Results765.2.1Experiment Setup765.2.2PARSEC Application Cases and Analysis of Coordinated DVFS76 | 0<br>6<br>0<br>0 |

| 6. | CON                               | CLUSION AND FUTURE WORK                                                                                                                                                                                                                            | 4                |

|    | 6.1                               | Conclusion                                                                                                                                                                                                                                         | 4                |

| RF | EFER                              | ENCES                                                                                                                                                                                                                                              | 5                |

## LIST OF FIGURES

## FIGURE

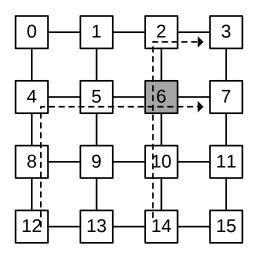

| 2.1  | 16-core CMP in a $4 \times 4$ 2D mesh array. The darkened tile indicates<br>location of the Power Control Unit (PCU). The dashed lines indicate<br>paths traversing the NoC [62].    | 12 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

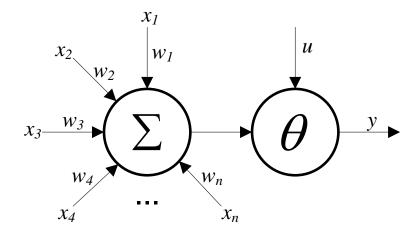

| 2.2  | Model of a single neuron $[62]$                                                                                                                                                      | 14 |

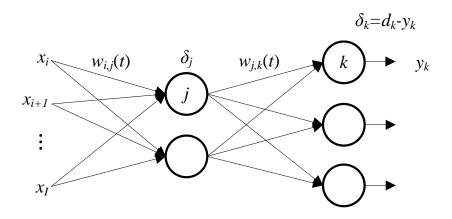

| 2.3  | Multi-layer feed-forward ANN [62]                                                                                                                                                    | 16 |

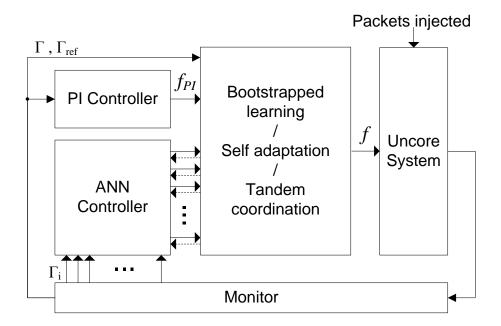

| 3.1  | Architecture of the uncore DVFS control system [62]                                                                                                                                  | 19 |

| 3.2  | Proposed 3-layer feed-forward ANN [62]                                                                                                                                               | 20 |

| 3.3  | Input and target sets for ANN learning [62]                                                                                                                                          | 22 |

| 3.4  | Bootstrapping learning applied to the <i>Bodytrack</i> application of the PARSEC benchmark suite [62].                                                                               | 25 |

| 3.5  | Pipelined monitoring and control intervals [62]                                                                                                                                      | 32 |

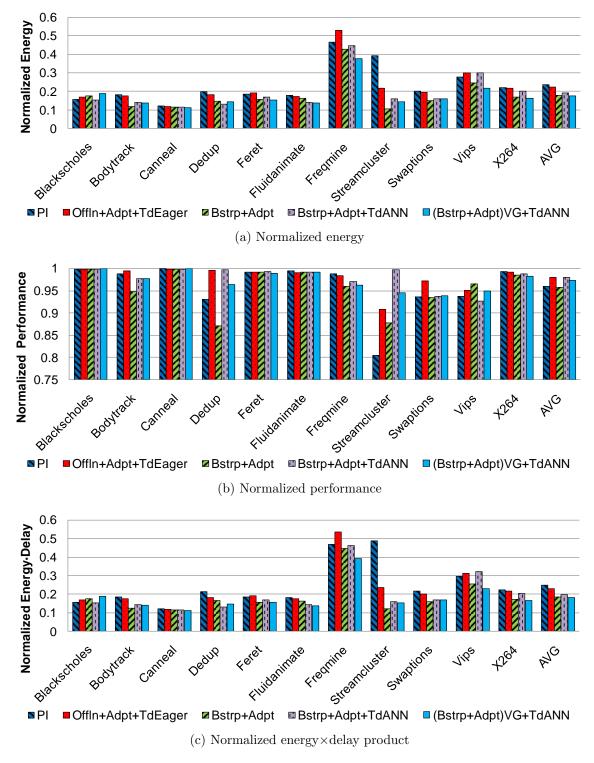

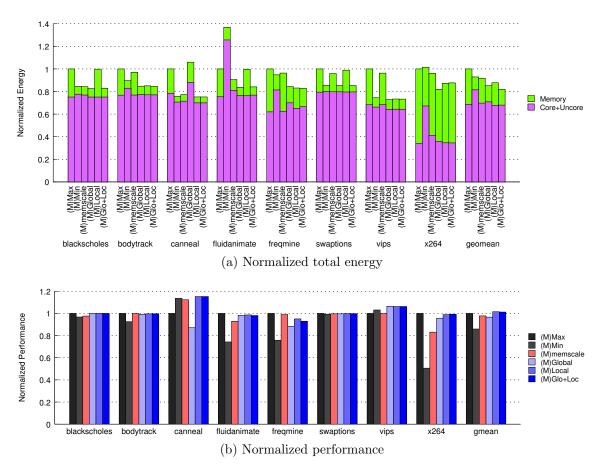

| 3.6  | Overall full-system experimental results [62]                                                                                                                                        | 37 |

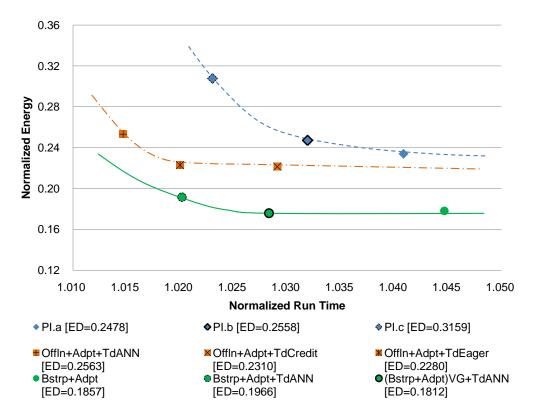

| 3.7  | Pareto optimal points and normalized energy-normalized run-time curves for PI control-, offline-, and bootstrapped learning-based methods [62].                                      | 38 |

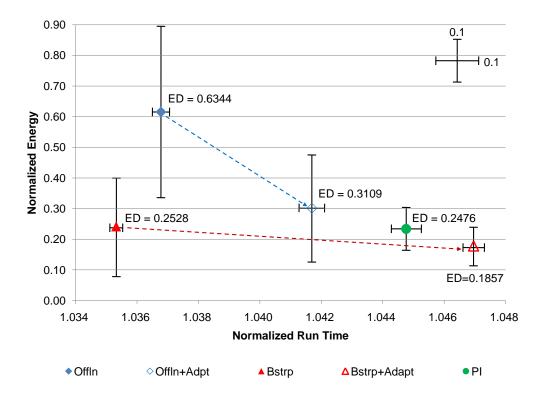

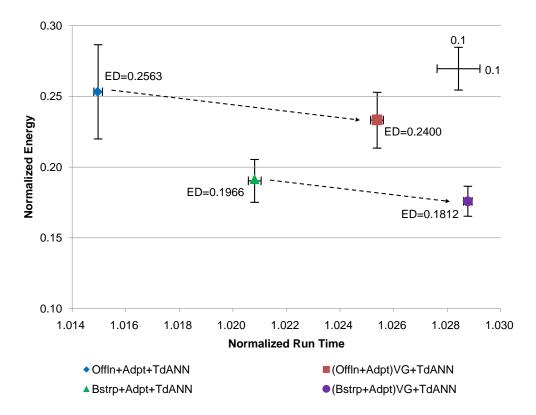

| 3.8  | Effect of online self-adaptation. ED: energy $\times$ delay product [62]                                                                                                             | 39 |

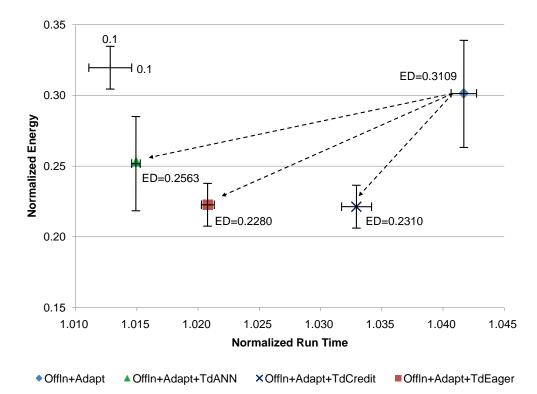

| 3.9  | ANN-PI tandem control based on offline supervised learning [62]                                                                                                                      | 40 |

| 3.10 | The effect of variable learning gain [62]                                                                                                                                            | 41 |

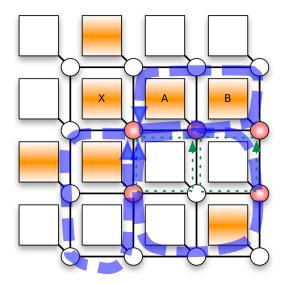

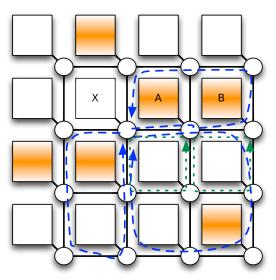

| 4.1  | A 16-core CMP with on-chip network and per-core DVFS. Orange (white) cores are in a high (low) voltage/frequency state. Red circles are network routers experiencing congestion [63] | 46 |

| 4.2  | Full-system simulation results of single application PARSEC benchmark suite [63]                                                                                                     | 51 |

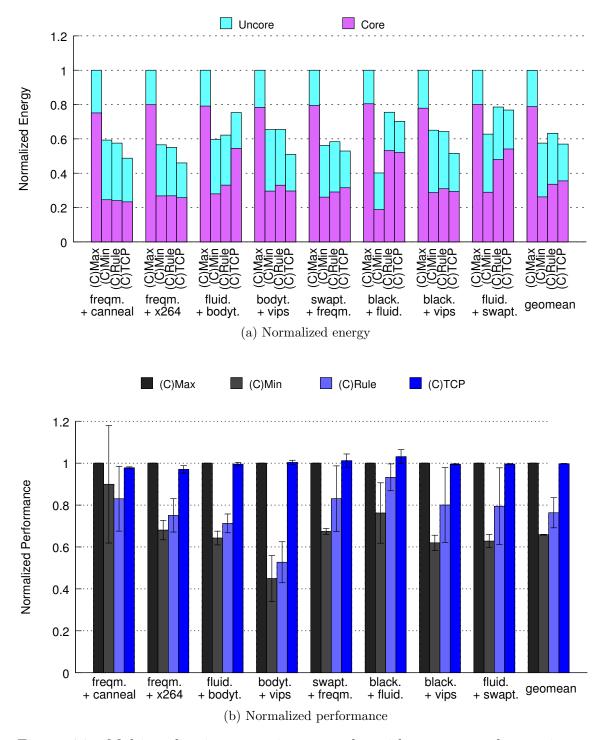

| 4.3 | Multi-applications experiment results with uncore at the maximum $V/F$ [63]                                               | 57 |

|-----|---------------------------------------------------------------------------------------------------------------------------|----|

| 4.4 | Comparison with static core V/F levels in single-application cases [63].                                                  | 58 |

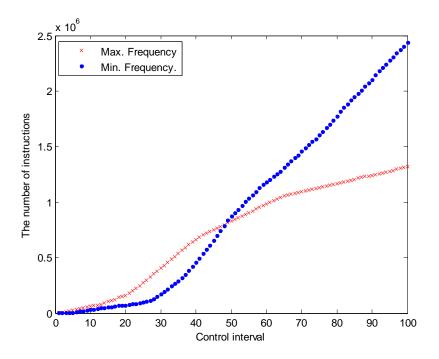

| 5.1 | The number of instructions executed in <i>canneal</i>                                                                     | 62 |

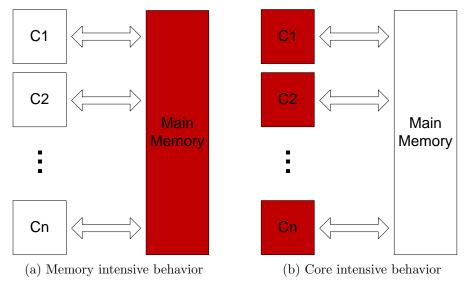

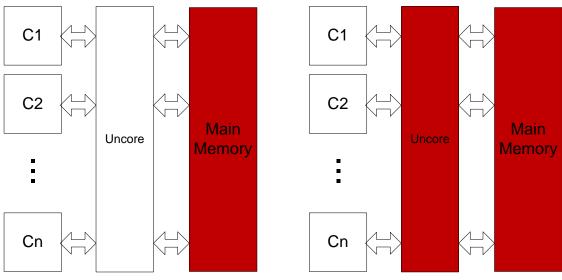

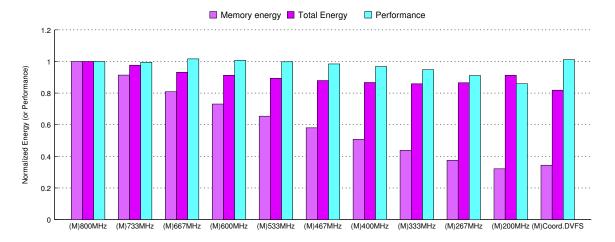

| 5.2 | Conventional main memory DVFS                                                                                             | 63 |

| 5.3 | Our shared resource congestion aware memory DVFS                                                                          | 65 |

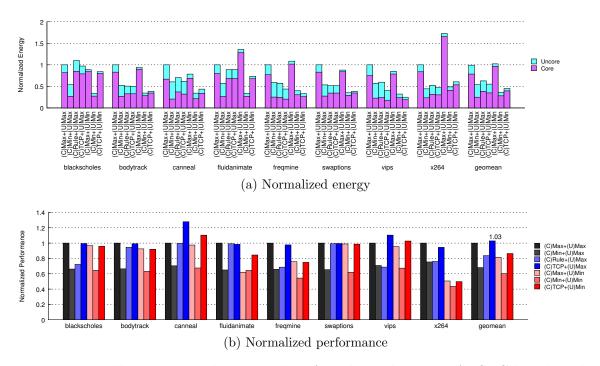

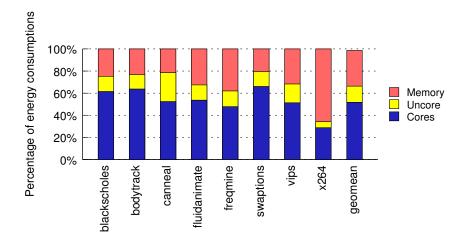

| 5.4 | Energy distribution of <i>PARSEC</i> [3] applications in CMP and main memory.                                             | 73 |

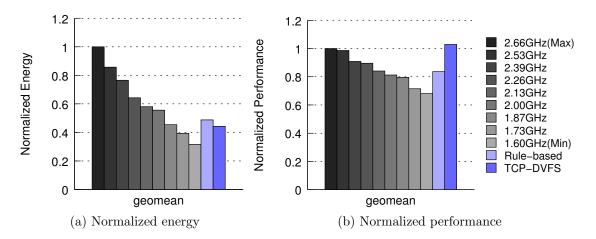

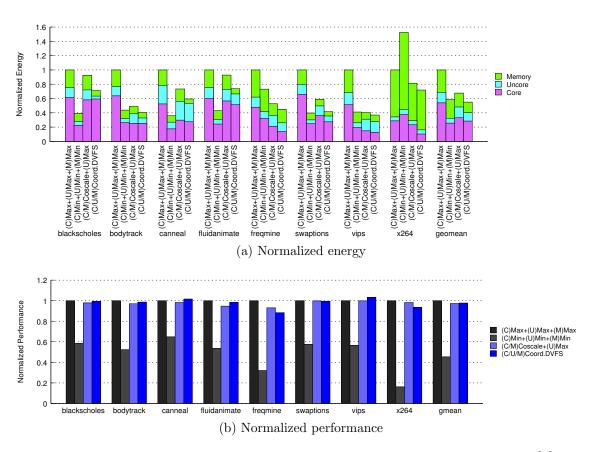

| 5.5 | Full-system simulation results of PARSEC benchmark suite [3]                                                              | 74 |

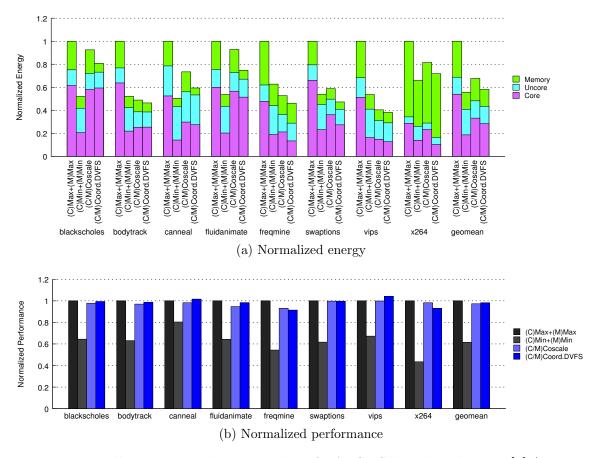

| 5.6 | Full-system simulation results of PARSEC benchmark suite [3] (Uncore frequency is fixed to maximum frequency.             | 77 |

| 5.7 | Full-system simulation results of PARSEC benchmark suite [3] (Fre-<br>quencies of cores and uncore are fixed to maximum). | 79 |

| 5.8 | Comparison with static memory V/F levels (Frequencies of cores and uncore are fixed to maximum)                           | 81 |

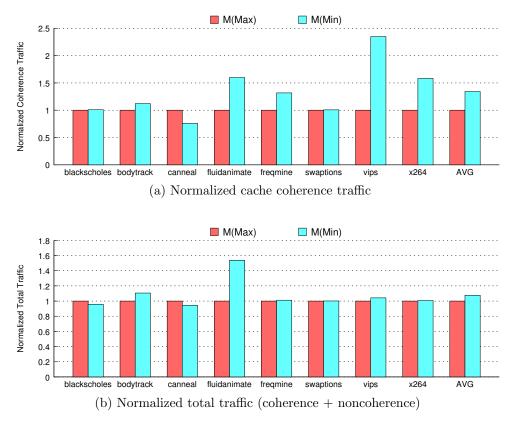

| 5.9 | Cache coherence traffic in the shared source                                                                              | 82 |

## LIST OF TABLES

## TABLE

| 3.1 | Rules governing the choice between the ANN controller and the PI controller decision under ANN-centric tandem control. Parameter $\bar{e}_i$ represents the error occurred in previous V/F selections, and $\xi_i$ represents the consistency between the ANN and PI controller decisions [62]. | 29 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | ANN control computing runtime in PCU clock cycles [62]                                                                                                                                                                                                                                          | 31 |

| 3.3 | System parameters used for full-system simulations [62]                                                                                                                                                                                                                                         | 33 |

| 3.4 | ANN configuration parameters [62]                                                                                                                                                                                                                                                               | 35 |

| 4.1 | Configuration and parameters of the experiment platform [63]                                                                                                                                                                                                                                    | 52 |

| 4.2 | Standard deviation ( $\sigma$ ) and mean of RTTs from our TCP-DVFS, nor-<br>malized with respect to results from cores at the max V/F level [63].                                                                                                                                               | 56 |

| 5.1 | Configuration and parameters of the experiment platform                                                                                                                                                                                                                                         | 71 |

#### 1. INTRODUCTION

Historically, advances in transistor process technology yielded scaling performance and energy efficiency together with scaling transistor density, a phenomenon known as Dennard scaling. Recently, however, Dennard's scaling [16] has broken down, leading to much tighter constraints on power consumption with each passing process technology generation. As a result, industry and academia have shifted to many-core, chip-multiprocessor (CMP) designs as a means to utilize increasing transistor density to efficiently gain performance. As scaling continues, however, energy and power management promise to be continuing concerns.

The "uncore" in modern CMPs, consisting of an on-chip communication fabric and shared LLC, now occupies as much as 30% of the overall die area [33]. Even though the die area of the uncore is smaller than CMP cores and their own private caches, the portion of the uncore, 30%, is not negligible in CMP power consumption. Also, uncore plays an important role of total system performance as a shared resource of cores and bottle-neck between CMP cores and external memory. Regarding that current work-load varies from core-intensive to uncore or memory-intensive, uncore becomes more critical resource for some far uncore, memory or both-intensive applications.

With the importance of uncore power management, the power management for the CMP cores still exist as a main concern regarding that 70% of the overall die area is responsible for CMP cores and private caches. Also with increasing corecounts in CMP designs, the shared resources, such as interconnect and cache, have become critical to the overall performance. Properly allocating these shared resources among threads or tasks is essential for efficient performance scalability. The goal in this context is to ensure that all clients (threads or tasks) achieve completion with low target delays and by doing so receive fair access to shared resources on chip. Interestingly, we find that there is a synergy between power management policies and techniques that achieve fair resource allocation for concurrently executing threads.

In addition to the CMP, main memory in computer architectures is usually adopted as a cost efficient memory device compared to cache memory [25]. Chip Multi-processor(CMP) includes multiple cores, private caches for each core and a shared cache for all cores. Even though cache memory is used as the fastest memory device, cache memory is not cost efficient to handle large size of data. To implement cache memory, it takes larger area than main memory. In other words, main memory plays an important role as a faster memory device to handle larger data. Certain types of main memory such as DRAM keep refreshing to hold data and takes comparable portion of energy consumption to CMP [2]. Therefore, power management for the main memory is necessary as much as CMP power management. In CMP power management, shared resource has been proven as critical resource for high performance and energy consumption [9, 62]. As such, main memory is also shared by all cores and shared cache of CMP, thus important for total performance and accounts for large fraction of total energy consumption.

To struggle with the power issue in CMP architecture, many researches has been conducted. Our first work focuses on dynamic voltage and frequency scaling (DVFS) for the CMP uncore. Although DVFS has been extensively studied in the literature [6, 22, 41, 47, 52, 53, 56], they have paid less attention on the uncore's power consumption. That is, they are restricted to either core DVFS or DVFS voltage/frequency (V/F) domains partitioning around cores, merely including a slice of the uncore. Classifying the uncore into separated V/F domains incurs large performance overhead in communication, as packets must pass between different V/F domains, experiencing synchronization delays at each hop.

In this work, we consider a different, but practical scenario where the entire uncore comprises a single V/F domain. In such setting, data need not experience synchronization delays in the network-on-chip (NoC) fabric interconnecting the cores. A few recent works seek to address uncore and/or NoC power management via DVFS [39, 10, 9]. These approaches are largely *reactive*, i.e., they set V/F state based purely upon past uncore state. Such approach works well only when the uncore load and its performance impact change slowly. In realistic applications, however, uncore load and its utility (i.e. the system's performance sensitivity to the uncore) often have abrupt changes. A reactive controller, such as a rule-based [39] or Proportional Integral (PI) controller [10, 9], may tune the uncore V/F to a higher level due to high load or poor performance observed in the previous interval. Utility, however, can suddenly change in the next interval, and a V/F increase consequently wastes energy that could otherwise be saved.

To improve upon this behavior requires a more proactive approach – a technique which can predict the load and make corresponding decisions. This requires the controller to maintain knowledge that associates past application behavior patterns with future uncore utility. In this work, we explore the use of an Artificial Neural Network-based (ANN) technique to achieve the desired proactive/predictive control [43]. ANNs are a general neural model derived from biological systems, that can be applied to approximately classify nonlinear and dynamic behaviors. As such, ANNs are particularly useful in identifying patterns in a current system state and predicting future behavior accordingly. ANNs have been used in branch prediction [61] and predicting traffic congestion hotspots in NoCs [31]. For the purposes of this work, we propose that the ANN is fed by the individual measured state of each core, together with some history of recent state in those cores. Based upon this input, the ANN will predict the future utility of the uncore, and the V/F state will be traced and set appropriately. This predictive control scheme allows faster, more proactive responses to abrupt state changes. The ANN's multi-input control is a clear advantage versus the single-input PI control [10] where information loss occurs during the data aggregation.

ANNs obtain their predictive ability via training of their internal parameters (weights). Thus, in typical ANN applications, a priori training set including inputs and desired output is required. For typical general-purpose processor implementations, difficulties exist in developing representative training sets, as this requires offline analysis of captive applications assumed to be similar to the expected workload of the processor. Architecting an efficient training mechanism without a priori knowledge of the workload's behavior is a significant challenge which we address in this work. We propose a novel technique in which a simple PI controller is used as a secondary classifier during a purely online training phase, dynamically pulling the the ANN up (by its bootstraps) to accurate prediction. Since the PI controller itself has been shown to produce reasonable power management, we propose that both the ANN and the PI controller work in tandem once the ANN training phase is complete. In this work we investigate novel policies determining which controller, the ANN or PI, should decide the next V/F state of the uncore, as well as when and how to modulate ANN online training during system runtime.

In addition to the uncore power management technique through DVFS, our work also considers DVFS techniques for cores and private caches as well. We observe that power-efficiency and shared resource management can be synergistic. There are two mechanisms by which this is true: First, and most obviously, shared resource management can balance resource utilization among threads and tasks, improving system's performance without impacting energy consumption and thus improving efficiency; Second, Power management techniques, such as dynamic voltage/frequency scaling (DVFS) can be used as a means to implement shared resource management. Thus the shared resource management policy actually *drives* power management policy in a direct sense. For example, when an on-chip network is congested, decreasing a particular core's voltage/frequency reduces its packet injection and therefore improves the network quality of service for the other cores. If well managed, core performance may not be impacted as it must wait for data from the congested network in any event. Further, the reduced congestion can allow other cores which may be more performance critical to make greater forward progress by reducing network and memory latency.

Based on this observation, we develop a simple, low-overhead, per-core DVFS policy inspired by TCP Vegas, a network congestion control technique that aims at ensuring small queuing delays. Simulations on PARSEC benchmarks indicate that our policy can reduce energy dissipation by 43% on average without performance degradation (or even performance increment). This work also compares our technique to state-of-art- methodology and shows that our technique is more efficient than other techniques.

Beyond CMP power management techniques, many researches have been conducted for memory power management to reduce entire power consumption. Deng and et al. proposed active low-power modes for main memory through dynamic voltage frequency scaling [15]. Also many researches on power management of main memory have been proposed [12, 14, 45]. However, the researches focus on main memory only and do not consider with CMP power management. This would occur too much energy saving with much performance degradation or less energy saving due to over V/F scale. To solve this issue, a coordinated DVFS technique of cores in CMP and main memory [13]. The work solves oscillation issue of operating V/F level without over energy saving. In this work, we explore coordinated memory DVFS techniques to maximize total energy saving. We do not consider only cores in CMP and main memory, but also shared resource in CMP. In general, lots of requests to main memory requires high voltage(V) and frequency(F) level to maximize system performance even though high V/F level derives less energy saving. Likewise, low V/F level is preferred when there are few requests to main memory for more energy saving. The low V/F level is sufficient to process few accesses of main memory with less performance degradation. However, we found that high V/F level to process lots of requests to main memory sometimes leads performance degradation while less energy saving. In this case, actually, the high V/F level generates congestion in uncore or memory controller, more requests to main memory or more cache coherence traffic. Our technique chooses low V/F level for the case, and so derives performance increment(or less performance degradation) by solving congestion while saving more energy by low V/F level.

The individual contributions of this work are as follows:

- We develop an ANN-based mechanism for uncore power management based upon offline training.

- We augment the offline-trained ANN controller with online self-adaptation and show that it improves the energy-delay product by 8% compared to a state-ofthe-art previous work [9].

- We propose a novel, purely-online, tandem ANN-PI power manager, which further improves energy-delay product by 27% versus prior techniques [9] while removing the need for offline training. Compared to constantly high uncore V/F, the performance degradation from our approach is less than 3%.

- We develop resource sharing driven DVFS technique for CMP cores power management and show that it improves performance by 2.9% with 43% energy savings compared to maximum frequency simulations.

- Our proposed cores power management policy is compared to a conventional work [24] and show that our work improves performance by 19.2% with similar energy savings.

- We propose coordinated uncore power management policy to cope with other DVFS policies.

- We propose shared resource aware power management technique for memory and shows 66% energy saving of main memory without no performance degradation (18% energy saving of total energy).

- Our proposed memory DVFS technique is compared to a conventional work [15] and shows that our work saves 24% more energy and improves performance by 3.5%.

- We propose coordinated policy among cores, uncore and memory and compared to a conventional work [13]. Our work shows that our work saves 12% more energy and improves performance by 0.4%.

Our full system simulations on PARSEC benchmarks shows 66% energy saving of main memory and 18% energy saving of total energy consumption. In addition to solely main memory DVFS, our coordinated DVFS technique for core, uncore and main memory shows 47% energy saving with less than 2.3% performance degradation.

#### 2. BACKGROUND AND RELATED WORK

#### 2.1 Dynamic Voltage Frequency Scaling on CMP and Related Work

Many works utilize Dynamic Voltage and Frequency Scaling (DVFS) techniques to save energy; often, these schemes are independently applied to either the NoC or onto the cores to save power, but not holistically. The earliest work, utilizing only dynamic voltage scaling (DVS) by Shang et al. [56] regulated the voltage of individual NoC links independently to save power during periods of link under-utilization. Soteriou et al. also explored DVFS regulation of links in NoCs. In this work DVFSspecific instructions were inserted into a given application, based upon profiling, to instruct the voltage-frequency regulation of links during run-time [58]. Son et al. proposed simultaneous CPU-NoC link DVFS for a specific application – parallel linear system solving [57]. Luo, et al., combined NoC link DVS with task scheduling of embedded systems [41]. Ogras, et al., applied state-space control for DVFS on tile-based designs where the NoC was partitioned and associated with processing cores [52]. Mishra et al. examined DVFS in NoC router designs [47]. The work of Guang et al. [22] partitioned a multi-core chip into voltage/frequency islands and its NoC was also regionally mapped onto those islands. They proposed a rule-based DVFS control for each island according to queue occupancy. Next, Rahimi, et al., proposed another rule-based DVFS based on both link utilization and router queue occupancy [53]. Bogdan, et al., described a DVFS approach based on a fractional state model, where the NoC was also partitioned to be associated with each voltage/frequency island [6]. There are very few previous works addressing DVFS for caches. Flautner et al. presented one such work, which applied DVS to individual cache lines [19].

These previous works all partition the NoC or caches into fine-grained voltage/frequency domains. Another realistic scenario is that the NoC, or uncore, constitutes a single V/F domain, such that the interfacing overhead can be avoided [39, 10, 9]. Liang and Jantsch [39] tuned the voltage/frequency state of the NoC according to network load as predicted by injection rate. Network congestion, however, is often a poor indicator of the entire chip's performance. Further, the DVFS policy in this work is a simple rule-based approach. To capture the impact of the uncore upon overall system performance, Chen, et al. [10], proposed an approach using AMAT (Average Memory Access Time). They employed a PI (Proportional and Integral) controller to implement their DVFS policy. In a recent work, Chen et al. [9] developed the concept of critical latency, the product of LLC throughput demand and the latency of the LLC and NoC, as an expression of uncore utility. This formulation brings significantly more energy savings than any prior work to-date. A dynamic reference technique was introduced for the PI controller which also facilitates additional energy-efficiency improvements. Collectively, these three approaches can be broadly classified as *reactive*, i.e. the V/F state for the next control interval is set based upon the current state and some limited amount of history. In this work, we propose a *proactive* mechanism, in which an ANN is used to detect program phase patterns exhibited in uncore utilization demands. Through finer ANN-based predictions, the controller can make the uncore V/F level better trace the uncore utility changes, and discover opportunities for additional energy savings without degrading the performance of the uncore.

Bitirgen and et al. examined the use of an ANN to manage shared resource allocation in a multicore environment [5]. They show an ANN can be an effective tool for complex management problems within a given hardware budget. Unlike this prior work, here we examine the use of an ANN for a different problem power management of the LLC and interconnect. Further, we explore the means of using a secondary classifier to provide online training and collaborative control.

Main memory is well known as a cost efficient and essential component in computer architecture. And, its power consumption compared to CMP (cores and uncore) takes large portion and the system requires power management for the memory parts. One work about memory power management technique utilizes estimated time for certain work-load [15]. The policy selects memory V/F level based on the estimated time for the certain work-load. They proposed an OS-level power management technique for memory through run-time estimation and used simplied model for accurate estimation.

Some work also focus on Quality-of-Service to enhance fairness and entire performance. Memory QoS techniques include fair queuing scheduling for its access [50], request grouping [49] and fairness-driven source throttling [17]. Cache QoS is obtained by enforcing priority-based capacity limit among threads [27] and access bandwidth allocation [51]. Coordinated QoS among NoC, cache and memory is studied in [37].

We proposed an on-chip memory power management technique and utilized measured performance counters for cores, shared memory and memory. We observed performance of the shared resource beyong memory itself affects the performance of memory. Thus, our technique which is based on measurement can be used in any architecture.

Many researches about independent power management technique have been proposed [26, 52] Even though the techniques are efficient for the specific component, it would affect other power management techniques for other connected components. Without awareness of other power management results, each techniques would overreact and oscillate between too far up and down.

To avoid the oscillation issues, a coordinated power management technique has

been proposed [13]. The work presented the coordinated power management for cores and main memory. In the work, they proposed new policy for cores' DVFS technique while using a pre-proposed technique for memory power management. In addition to new technique for core power management, they proposed coordinated DVFS through awareness of results of other power management techniques. They suggested OS-level power management policy which has longer control interval(i.e. 5ms of epoch) and used simplied model for more accurate estimation of processing time. Also, they assumed all running applications are single threaded application for more accurate estimation of run-time.

In our proposed work, we proposed a coordinated DVFS technique for cores and memory and additionaly we also considered shared resource, uncore, power management. Uncore takes large portion of energy consumption in CMPs and so is critical for power management of entire CMPs [9, 42, 62]. Also, uncore affects to other components' power management. In our work, we proposed an on-chip power management technique which is faster than OS-level power management. Our policy can also be used in any architectures because it is based on measurement of control interval.

#### 2.2 Uncore Power Management

We consider a common case in multicore processor design where the entire chip is composed of an array of identically-sized tiles. Each tile contains a processor core and private caches. The communication fabric is a 2D mesh NoC with one router residing in each tile. A shared LLC is partitioned into slices and distributed uniformly among these tiles. The NoC and the LLC together are referred to as the *uncore* system. We further assume that the CMP contains a Power Control Unit (PCU) [11]: a small micro-controller with direct control of the uncore's V/F state via memory-mapped micro-architectural registers, which emulates our proposed power management policy in software. This PCU is associated with one of the central tiles in the 2D mesh as indicated by the darkened tile #6 of Figure 2.1.

Figure 2.1: 16-core CMP in a  $4 \times 4$  2D mesh array. The darkened tile indicates location of the Power Control Unit (PCU). The dashed lines indicate paths traversing the NoC [62].

Similar to the design originally proposed by Chen et al. [10, 9], we assume that data (*i.e.* L1 Miss rate, the L2 Miss rate, etc.) used in measuring uncore utility, are encoded into the unused bits in the packet headers being routed onto the NoC. This data is opportunistically collected when these packets pass through the router containing the PCU (Figure 2.1). This approach minimizes the overhead of monitoring, since no extra status packets are created, and there is no need for a secondary overlay status network to convey statistical uncore utility information. Although this implies some staleness in the collection of status data, Chen et al. found that, with appropriate extrapolation, the data obtained produces results nearly indistinguishable from omniscient data collection for the 50K-cycle control intervals [10].

#### 2.2.1 PI Controller

As a basis of comparison and as a sub-component of our design we also utilize a proportional-integral (PI) controller [10, 9]. A PI controller has two components, the proportional "P" component calculates error,  $e_t$ , as the difference between the reference value and measured output in a closed loop. While the P component achieves steady-state rapidly, it is highly sensitive to noise and thus can be vulnerable to multi-core system input patterns which can change dynamically. To increase robustness, the integral "I" of past error is added in a weighted sum. The final output,  $u_t$  of the controller is calculated as shown in Equation 2.1.  $K_p$  and  $K_i$  are the proportional and integral error gain, respectively, and are typically determined empirically.

$$u_t = K_p e_t + K_i \sum_{k=1}^t e_k$$

(2.1)

#### 2.3 Concept of Artificial Neural Networks

An ANN is an information processing paradigm, inspired by biological neural networks, that attempts to capture the learning behavior, response behavior and general functionality of a biological central nervous system, so as to emulate a form of intelligence artificially. An ANN consists of computation nodes called neurons and interconnections between them, called synapses. ANNs are used to determine relationships between sets of input data to sets of output data, so as to identify and understand patterns.

ANN networks are usually organized in layers of neurons, where information processed from each subsequent layer is fed as an input to the next layer, until the last layer computes a useful result. This model, employed in this work, is known as the multi-layer perceptron ANN. A typical single neuron model is depicted in

Figure 2.2: Model of a single neuron [62].

Figure 2.2, and is defined by Equation 2.2 [43]:

$$y = \theta\left(\sum_{j=1}^{n} w_j x_j - u\right) \tag{2.2}$$

In this equation,  $x_1, x_2, \dots, x_n$  are its inputs,  $w_1, w_2, \dots, w_n$  are the weight parameters, u is the threshold parameter,  $\theta$  is the activation function and y is its output. The activation function can take various forms, *e.g.* if  $\theta$  is a step function, the output changes from 0 to 1 when the weighted sum of the inputs is exceeds a threshold u.

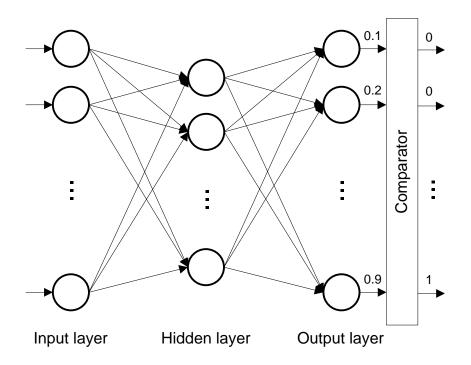

While single neurons can perform classification functions based upon their inputs, this function is limited to linearly separable patterns [46]. Multi-level networks of these perceptron models, i.e. ANNs, do not have this limitation [28]. Here, each neuron is treated as a node, forming directed graph with input and output edges. An example ANN is illustrated in Figure 2.3, where each circle represents a neuron. The ANN in Figure 2.3 does not contain any cycles, and is therefore called a feedforward ANN. Other ANN variants exist which have cycles, however, we do not consider them in this work, so as to reduce complexity.

An ANN is a very flexible framework, capable of modeling many different and complex systems, through configuration of its topology, its activation functions and by tuning its parameters. When the ANN is employed as a controller, its output is the control variable and its inputs are from the states/outputs of the system to be controlled. Through a learning procedure, the ANN weights are tuned to associate certain input patterns with a desired output(s).

There are two general forms of ANN learning algorithms: supervised and unsupervised. Under supervised learning, the ANN is typically trained iteratively with a data set that has known solutions starting from an arbitrary set of parameters. In each iteration, the ANN output is compared to the known solution, and the parameters are tuned such that the difference between them is reduced or converges, i.e. they form a "good match." For the simplest ANN, one that has a single neuron, each input weight  $w_i$  is updated by

$$w_j(t+1) = w_j(t) + g \cdot (d-y) \cdot x_j$$

(2.3)

where d is the known solution, g (0.0 < g < 1.0) is a learning gain factor and t indicates iteration index.

For a multi-layer network, the learning procedure includes two passes of backward traversals along the network, from the output(s) to the inputs. The errors are backpropagated in the first traversal and the edge weights are updated during the second traversal [23]. We use a 2-layer ANN topology in Figure 2.3, as an example, to illustrate this process. The error,  $\delta_k$ , is defined as  $\delta_k = d_k - y_k$  for each output node k. For each edge (j, k) between the middle layer and the output layer, its weight is  $w_{j,k}$ . The errors are back-propagated to the middle layer and the error  $\delta_j$  at each

Figure 2.3: Multi-layer feed-forward ANN [62].

middle layer node is obtained by

$$\delta_j = \sum_{k=1}^{K} (w_{j,k}(t) \cdot \delta_k) \tag{2.4}$$

where K is the fanout of node j. For the edge weight update, we illustrate with the edges from the inputs to the middle layer in Figure 2.3. Let the weighted sum of inputs to node j be  $\psi_j = \Sigma w_{i,j}(t) \cdot x_i$ . Edge weights  $w_{i,j}$  are updated by

$$w_{i,j}(t+1) = w_{i,j}(t) + g \cdot \delta_j \cdot \frac{d\theta(\psi_j)}{d\psi_j} \cdot x_i$$

(2.5)

This procedure is repeated for all edges in a layer-by-layer backward traversal of the network.

#### 2.4 Quality of Service in CMP

In a CMP with shared resources that have a specific bandwidth, such as on-chip networks, caches and memory controllers, contention resolution can shape overall performance. For example, if a few cores dominate memory access, fairness suffers and the other cores may form bottlenecks that harm the overall application performance [17]. Contention resolution is a central subject of Quality-of-Service (QoS). The exact concept of QoS is somewhat complicated and can be interpreted in different ways depending on one's emphasis. While Grot, *et al.*, summarize ten attributes of CMP Network-on-Chip (NoC) QoS [21], in practice, most prior work in CMP QoS is focused on service prioritization [7, 27], service guarantees [35, 21, 20, 60], service fairness [50, 51, 17] or some combination of these. Ultimately, however, for most CMP applications, the focus is overall CMP performance and application runtime.

QoS can be achieved through a combination of arbitration at the service side, service categorization and regulation at the client (processor cores) side. For onchip networks, typical QoS approaches include source throttling [?], router arbitration [21], or a combination of both [35]. Source throttling can be based on assigned injection rates [35], application types and network congestion [?]. Global QoS arbitrates according to packet age [36] or whether a flow conforms to its assigned rate [21]. Memory QoS techniques include fair queuing scheduling for its access [50], request grouping [49] and fairness-driven source throttling [17]. Cache QoS is obtained by enforcing priority-based capacity limit among threads [27] and access bandwidth allocation [51]. Coordinated QoS among NoC, cache and memory is studied in [37].

Existing CMP QoS works mostly treat energy consumption as an implementation overhead to achieve fairness and pay little attention to its interaction with power management.

# 3. ONLINE LEARNING IN ARTIFICIAL NEURAL NETWORKS FOR IMP UNCORE POWER MANAGEMENT

#### 3.1 Tandem ANN and PI Control

An overview<sup>1</sup> of the proposed uncore DVFS control system is depicted in Figure 3.1. Besides an ANN controller, it includes a PI controller, as the PI controller plays a role complementary to the ANN control and has very low overhead. The center of this system is the coordination between the two controllers. In this section, we will first introduce the ANN controller architecture. Then, we will describe the ANN learning including how to utilize the PI controller for a bootstrapped learning. The last part will be on the new techniques of tandem ANN-PI control operations.

### 3.1.1 ANN Controller Architecture

The output of our ANN controller is the uncore V/F level. Its inputs should reflect the uncore performance as well as how sensitive whole system performance is to uncore latency, effectively a measurement of the uncore's *utility* to the system. To this end, we adopt the *critical latency* metric introduced by Chen et al. [9], which is defined as

$$\Gamma = \eta \cdot \lambda_U \tag{3.1}$$

where  $\lambda_U$  is the uncore latency and  $\eta$  is the criticality factor. The uncore latency covers the overall request excluding the memory access latency, i.e., NoC travel latency plus LLC access latency. The criticality factor is the product of private cache miss rate and the ratio of *load* instructions versus total instructions. Chen et

<sup>&</sup>lt;sup>1</sup>Reprinted with permission from "Up by Their Bootstraps: Online Learning in Artificial Neural Networks for CMP Uncore Power Management", by Jae-Yeon Won, Xi Chen, Paul Gratz, Jiang Hu and Vassos Soteriou, 15-19 Feb. 2014, The 20th IEEE International Symposium on High Performance Computer Architecture(HPCA), © 2014 IEEE

al.[9] collect the critical latency data from all cores and average them into a single value as the input to a PI controller. In contrast, an ANN controller can directly process multiple inputs, and is therefore able to utilize detailed, per-core information.

The DVFS control action is performed periodically in every control interval  $\mathcal{I}$ . Since the ANN controller accepts multiple inputs, it may examine monitored  $\Gamma$  of an arbitrary number of history intervals. Thus, if the ANN controller examines the past m intervals, including the current interval, and there are n cores, then it has  $m \cdot n$  inputs.

From the inputs to the output, there can be different numbers of layers of neurons, which implies a tradeoff between capability and overhead. From our experience, a 3layer structure performs well and has limited overhead. Such a structure is depicted in Figure 3.2. If the uncore V/F has k levels, we use k outputs, each of which indicates the selection of a corresponding V/F level. The value of each output is a number

Figure 3.1: Architecture of the uncore DVFS control system [62].

Figure 3.2: Proposed 3-layer feed-forward ANN [62].

between 0 and 1. Since an output can take fractional value, we use a comparator to select the output with the maximum value, and round the other outputs to zero.

For the activation functions, we employ the commonly used Gaussian functions defined by

$$f(x) = ae^{-\frac{(x-b)^2}{2c^2}}$$

(3.2)

We set a to 1 to maintain the neuron's output dynamic range between 0 to 1. Parameters b and c can be adjusted according to input values which is introduced in Equation (3.1). The learning algorithm here is the common back propagation algorithm described in Section 2.3.

#### 3.1.2 ANN Learning

ANN learning is a procedure of identifying/improving the weight parameters based upon the expected output(s) for a given input set. ANN learning can be carried out offline or online. The basic supervised learning is introduced in Section 2.3. In Section 3.1.2.1, we describe how to apply traditional supervised learning offline for our ANN controller. New online self-adaptation techniques for tuning the ANN controller are discussed in Section 3.1.2.2. We propose an "up by the bootstraps" learning technique using PI control as a secondary classifier in Section 3.1.2.3.

### 3.1.2.1 Offline Supervised Learning

In offline supervised learning, first a set of cases with known solutions for ANN training is created. Since the DVFS control is carried out periodically for each control interval, this set should include the target uncore V/F level of every control interval. The target level should be the optimal level defined by the minimum uncore V/F level such that the runtime increase is no more than  $\alpha$ % compared with the highest V/F level, where  $\alpha$  is a parameter. Ideally, the optimal V/F level can be found by enumerating all combinations, e.g., simulate all V/F levels in interval  $\mathcal{I}_i$  and then simulate all V/F levels in interval  $\mathcal{I}_{i+1}$  for every case at  $\mathcal{I}_i$ . By approximation, we enumerate uncore V/F levels for the entire trace, i.e., if there are k V/F levels, the entire trace is simulated for k times, each with a different uncore V/F level. These simulation results are partitioned into control intervals and the target V/F level is chosen for each interval.

The interval partitioning starts with simulation result of the highest frequency, i.e., uncore frequency is  $f_{max}$ , and each interval consists of  $\kappa$  clock cycles. Finding the corresponding intervals of other simulations with different uncore V/F is challenging, as the executed instruction count in multithreaded benchmarks tends to vary with uncore V/F state<sup>2</sup>. In lieu of instruction count we use a count of the number of committed *store* instructions from each thread, as this number tends to be invariant with uncore latency, to determine overall runtime of equivalent intervals from one uncore V/F to the next. For example, if there are 9876 *store* instructions in the first interval for uncore frequency  $f_{max}$ , we define the first interval for other uncore frequency traces  $f < f_{max}$  by the cycle when the 9876th *store* instruction is committed. This procedure is repeated for subsequent intervals and all k uncore frequency levels. For each interval, the target frequency is the minimum one such that the runtime of this interval is no greater than  $(1 + \alpha\%) \cdot \kappa$  clock cycles, where the cycles are in terms of  $f_{max}$ .

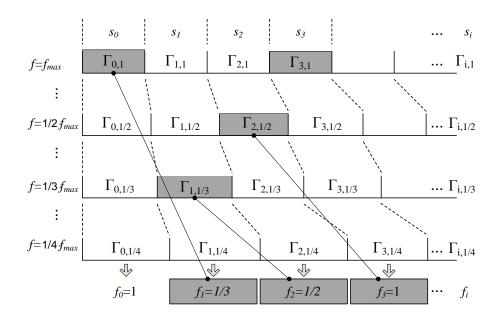

Figure 3.3: Input and target sets for ANN learning [62].

<sup>&</sup>lt;sup>2</sup>Spin-locks and other synchronization primitives tend to vary in instruction counts when uncore latency is changed.

The ANN controller decides the uncore V/F level of interval  $\mathcal{I}_{i+1}$  based on the critical latencies observed from n cores of the last m intervals. Likewise, we use the the critical latencies of all n cores across intervals  $\mathcal{I}_{i-(m-1)}, \mathcal{I}_{i-(m-2)}, \dots, \mathcal{I}_i$  and the target uncore frequency at interval  $\mathcal{I}_{i+1}$  as one training set. Figure 3.3 shows a simple example with m = 1 where the shaded intervals correspond to the target frequencies and  $s_i$  is the number of *store* instructions at interval  $\mathcal{I}_i$ . In interval 1, the  $\Gamma_{1,1/3}$  is the observed critical latency when the uncore operates at  $f_1 = \frac{1}{3}f_{max}$ . The critical latency  $\Gamma_{1,1/3}$  for all cores, and the target frequency  $f_2 = \frac{1}{2}f_{max}$  of interval 2, form a data set for the supervised learning. This procedure is repeated for  $\Gamma_{2,1/2}$  and  $f_3 = f_{max}$ , and so on. Once the training data sets are obtained, supervised learning is performed as described in Section 2.3.

### 3.1.2.2 Online Self-Adaptation

While offline supervised learning can produce good results, it has a weakness. The actual applications may have quite different characteristics from the training cases. In other words, an ANN well-trained for certain workloads may perform poorly on different workloads (i.e. the workloads it was not trained on). To overcome this weakness, we propose two online self-adaptation techniques: feedback adaptation and self-sharpening.

Feedback Adaptation: Feedback adaptation is similar to supervised learning described in Section 2.3 except that the target frequency is obtained online as in the case of feedback control. In typical feedback control techniques, such as PI control [10], the controller attempts to correct the error of the system's output with respect to a reference. The error at interval  $\mathcal{I}_i$  is defined by

$$e_i = \Gamma_i - \beta \cdot \Gamma_{ref,i} \tag{3.3}$$

where  $\Gamma_i$  is the critical latency observed during interval  $\mathcal{I}_i$ ,  $\beta$  is a coefficient, and  $\Gamma_{ref,i}$  is the reference. We adopt the idea of dynamic reference [9], which is the critical latency when no data packet experiences queuing delay. The coefficient  $\beta$  is typically selected to have a value of 1.1, implying that a small queuing delay during NoC congestion is allowed. The adaptation action is taken only if the error magnitude  $|e_i|$  is greater than a certain threshold  $\tau$ . If there is a large positive (negative) error, we set the target frequency to be one level above (below) the uncore frequency used in interval  $\mathcal{I}_i$ . This target frequency together with the critical latencies of all cores across intervals  $\mathcal{I}_{i-m}$ ,  $\mathcal{I}_{i-(m-1)}$ ,  $\cdots$ ,  $\mathcal{I}_{i-1}$ , form a data set to train the ANN once. Such trainings are interleaved with the ANN control operation and thus can be conducted at run-time.

**Self-sharpening:** The self-sharpening technique is based on the observation that the ANN should ideally have one output of value 1, while the other outputs have a value of 0. In typical operations, however, the ANN produces a set of fractional outputs in [0, 1]. Thus, if the ANN output is  $\{0.1, 0.2, \dots, 0.9\}$ , the uncore frequency selection is effectively the same as if the output is  $\{0, 0, \dots, 1\}$ . Under self-sharpening, we set the ANN output error as  $\{-0.1, -0.2, \dots, 0.1\}$  and back propagate this error through the ANN, as carried out with supervised learning, reinforcing the ANN's decision.

#### 3.1.2.3 Bootstrapped Learning Using a PI Controller

Although the self-adaptation techniques presented in Section 3.1.2.2 can improve upon the performance of offline supervised learning by refining the ANN's behavior according to the actual workload demands, it cannot completely replace offline learning<sup>3</sup>. General-purpose CMP workloads can vary so greatly that developing a

$<sup>^{3}</sup>$ We explored purely online training with the techniques discussed in Section 3.1.2.2, however the results were poor due to the long training time required, these results were dropped from this

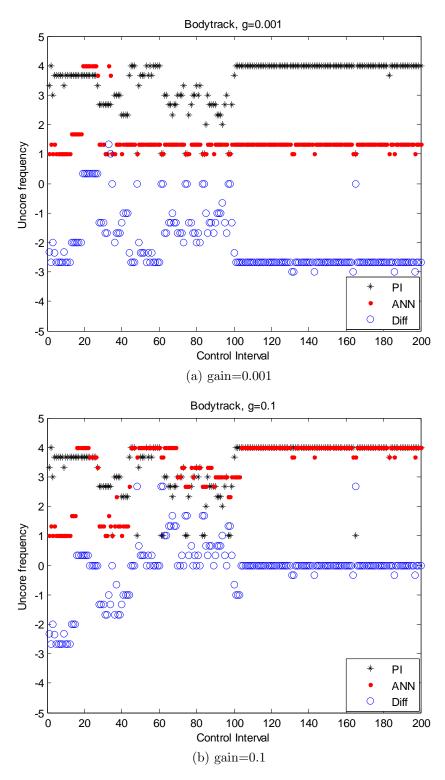

Figure 3.4: Bootstrapping learning applied to the *Bodytrack* application of the PAR-SEC benchmark suite [62].

representative set, at design time, for training may be impossible. Therefore, an ANN controller design which does not rely on offline learning is often desirable. Ideally, one would prefer the ANN training as purely online, i.e. during the application's runtime, without the need for an a priori training set. There are, however, several challenges to this form of pure, "up by its bootstraps", online training. For example, online training requires knowledge of the desired output for any given input, at runtime, before the ANN itself is trained well enough to produce that output. Although the PI controller [10, 9] has its weakness, it has very low overhead and it requires very little start-up delay in producing V/F control at its best ability. We thus propose instantiating a PI controller for online training of the ANN. In this "bootstrapped" learning, the ANN learns from the PI controller while the PI controller is controlling the V/F state of the uncore. Hence, the PI control is a surrogate for the training set in supervised learning. The PI controller provides a realistic, dynamically generated training set for online ANN training. When combined with continuous online self adaptation (feedback-adaption and self-sharpening described in Section 3.1.2.2) the ANN can exceed the performance of the PI controller. In Section 3.1.3, we will show that the PI controller may also be used for tandem control once the ANN is trained as well.

The offline supervised learning is often conducted based upon complete traces of many applications. By contrast, bootstrapped learning is performed during the beginning phases of each single application. Hence, it should be much faster and requires a greater learning gain (see Equation (2.3)). Furthermore, bootstrapped learning is focused on the behavior of a single, ongoing application, while the offline supervised learning is intended to be more general. As a result, bootstrapped learning is much more focused to the application at hand and can perform significantly better. paper for brevity. Figure 3.4 compares the bootstrapped learning with different gains applied to the *Bodytrack* application of PARSEC benchmark suite [3]. The x-axis holds the indication of the control interval, and the y-axis indicates the uncore frequency selection in terms of the ratio of  $f_{max}$  versus uncore frequency; for example, value 4 implies that the uncore frequency is  $\frac{1}{4}f_{max}$ . The green crosses are the V/F selections chosen by the PI controller, the red dots are those chosen by the ANN, and the blue circles represent the differences between them. Figure 3.4a shows the results with a learning gain of g = 0.001, which is common for the offline supervised learning. One can see that the ANN output remains quite different from the PI controller's output after 200 intervals. Experimental results with g = 0.1 are shown in Figure 3.4b, which exhibits that the ANN output starts to follow the PI control after approximately 100 intervals.

### 3.1.2.4 Variable Learning Gain

To further improve the learning efficiency, we propose a variable gain scheme, which can be applied with the bootstrapped learning and the online self-adaptation. In this scheme, the gain g can vary in a range  $[g_{min}, g_{max}]$  according to the error  $e_i$ defined by Equation (3.3). A small (large) error means the result is close to (far from) a desired one, based on which the learning should be more (less) emphasized and use a large (small) gain. Using this rationale, the variable gain is given by

$$g_{i} = \begin{cases} g_{max} & \text{if } e_{i} \leq \tau \\ g_{max} - \left(\frac{e_{i} - \tau}{e_{max} - \tau}\right) \cdot \left(g_{max} - g_{min}\right) & \text{if } \tau < e_{i} < e_{max} \\ g_{min} & \text{otherwise} \end{cases}$$

(3.4)

where  $\tau$  and  $e_{max}$  are two constant parameters.

### 3.1.3 ANN-PI Tandem Control

As discussed in Section 3.1.2, the ANN controller pro-actively adjusts the uncore V/F level according to its experience, learned either offline or bootstrapped online. This methodology, however, may not always be accurate. One can predict rain from heavy clouds, but heavy clouds do not always yield rain. Alternately, the PI controller always bases its V/F selection only upon current observations. Thus, ANN control and PI control can be viewed as complementary to each other. We propose three ANN-PI tandem control schemes, elaborated next.

# 3.1.3.1 ANN-Centric Tandem Control

In the first scheme, ANN-Centric Tandem Control, after the ANN is fully trained, both the ANN and PI controllers make their V/F selection for the next control interval. One of their results is chosen to be applied to the uncore. The choice depends on the average error defined by

$$\bar{e}_{i} = \frac{\sum_{j=i-m+1}^{i} \sum_{l=1}^{n} e_{j,l}}{m \cdot n}$$

(3.5)

where  $e_{j,l}$  is the error defined in Equation (3.3) for control interval  $\mathcal{I}_j$  and core l. This is the average control error among all n cores across the past m control intervals. The choices also rely on the consistency ( $\xi_i$ ) between ANN and PI control, which is defined as

$$\xi_i = 1 - \left(\sum_{j=i-m+1}^{i} \frac{|f_{j,ANN} - f_{j,PI}|}{k-1}\right) / m$$

(3.6)

where k is the number of uncore V/F levels,  $f_{j,ANN}$   $(f_{j,PI})$  is the uncore frequency level computed from the ANN (PI) in control interval  $\mathcal{I}_j$ . In dividing with k-1, the difference is normalized to be no greater than 1. The second term in Equation (3.6) is the average normalized difference between the ANN and the PI computed results in the past m intervals.

| $\mathcal{I}_i$ | $\bar{e}_i$  | $\xi_i$      | $\mathcal{I}_{i+1}$ |

|-----------------|--------------|--------------|---------------------|

| PI              | $\downarrow$ | $\downarrow$ | ANN                 |

| PI              | $\downarrow$ | $\uparrow$   | PI                  |

| PI              | $\uparrow$   | $\downarrow$ | ANN                 |

| PI              | $\uparrow$   | $\uparrow$   | ANN                 |

| ANN             | $\downarrow$ | $\downarrow$ | ANN                 |

| ANN             | $\downarrow$ | $\uparrow$   | ANN                 |

| ANN             | $\uparrow$   | $\downarrow$ | PI                  |

| ANN             | $\uparrow$   | $\uparrow$   | ANN                 |

Table 3.1: Rules governing the choice between the ANN controller and the PI controller decision under ANN-centric tandem control. Parameter  $\bar{e}_i$  represents the error occurred in previous V/F selections, and  $\xi_i$  represents the consistency between the ANN and PI controller decisions [62].

The rules for the choices between the PI or the ANN are listed in Table 3.1. The first row says that the ANN result will be chosen for interval  $\mathcal{I}_{i+1}$  if the control in interval  $\mathcal{I}_i$  is based on the PI, the average error  $(\bar{e}_i)$  is small and the consistency between the ANN and the PI results  $(\xi_i)$  is low. According to the second row, if the PI is chosen for interval  $\mathcal{I}_i$ , the average error is low, and the consistency is high, then the PI control result is chosen for interval  $\mathcal{I}_{i+1}$ . The other rows of Table 3.1 can be interpreted in the same way.

This scheme is intentionally biased in favor of the ANN, only in rows 2 and 7, where the advantage of PI is obvious, is the PI controller chosen for the next control interval. In all the other cases, the ANN result is selected for actual use. The intent under this technique is to select the ANN as soon as it begins producing reasonably accurate results, under the assumption that the ANN can perform better in the long run once training is complete.

### 3.1.3.2 Eager Tandem Control

We introduce an alternative scheme for the ANN-PI tandem control, which is solely based on the control error  $e_i$  (defined by Equation (3.3)) at the control interval  $\mathcal{I}_i$ . If  $e_i > \tau > 0$  ( $e_i < -\tau < 0$ ), where  $\tau$  is a threshold, and the critical latency is significantly greater (less) than the reference, then the higher (lower) frequency between the ANN and PI results is chosen for the next interval  $\mathcal{I}_{i+1}$ . The rationale for this technique is the same as that of the feedback adaptation technique described in Section 3.1.2.2, except that it is directly applied to control decisions, while the adaptation is to improve the ANN.

### 3.1.3.3 Credit-Based Tandem Control

As another variant of the eager tandem control scheme, we concentrate not only to  $e_i$ , but also to the method selected in interval  $\mathcal{I}_i$ . If  $e_i > \tau > 0$  ( $e_i < -\tau < 0$ ) and the method chosen in  $\mathcal{I}_i$  gives the higher (lower) frequency, this method is more credible and will be chosen again for  $\mathcal{I}_{i+1}$ . Otherwise, the other method is chosen for  $\mathcal{I}_{i+1}$ . Although this scheme also uses  $e_i$  as in the eager tandem control, the  $e_i$  here is employed to compare which method performs better in  $\mathcal{I}_i$ . The one which performs better in  $\mathcal{I}_i$  is assumed more trustworthy.

# 3.2 Design Implementation

In this section we describe the implementation details including monitored data collection and control computation. For data collection, we employ a similar scheme to that proposed by Chen et al. [10]. As with their work, there is a PCU (Power Control Unit) [11], which is a microcontroller which handles power management for the CMP system. The microcontroller is similar to that utilized in current CMP designs such as in the Intel i7 [33]. Every core collects its critical latency  $\Gamma$  informa-

tion, and encodes it (piggy-backed in the header flit) onto the unused bits of each outgoing packet. If a packet passes by the PCU, even when the corresponding tile is not its destination, the  $\Gamma$  information is downloaded to the PCU. The PCU retains all relevant data in its local memory. We have experimentally verified that the proposed monitor technique incurs negligible error relative ideal monitoring. More details about the data collection design can be found in the prior work of Chen et al. [10, 9].

In our design, all computation required by our schemes is performed *in emulation*, by running software onto the PCU (i.e. there is no actual ANN hardware, the ANN is emulated in software on the PCU). The computation mainly consists of (a) computing the PI control decision, (b) ANN training, (c) computing the ANN control decision, and (d) choosing between the ANN and PI results in the tandem control schemes. Items (a) and (d) exhibit very low complexity, and their overhead is negligible relative to our control interval size. The ANN training process, including self-adaptation and bootstrapped learning, does not block the ANN control computation, and is therefore not timing-critical. We therefore focus here on estimating the computational cost of the ANN control decisions. Table 3.2 shows the ANN control computation runtime with different numbers of history intervals. These data are obtained based on a baseline 16-core CMP design. As it would be expected, the computational overhead increases with the number of history intervals.

| # history | Runtime       | Runtime       | Total   |

|-----------|---------------|---------------|---------|

| intervals | @hidden layer | @output layer | runtime |

| 10        | 27,513        | 1,741         | 29,254  |

| 5         | 13,779        | 1,741         | 15,520  |

| 1         | 2,772         | 1,741         | 4,513   |

Table 3.2: ANN control computing runtime in PCU clock cycles [62].

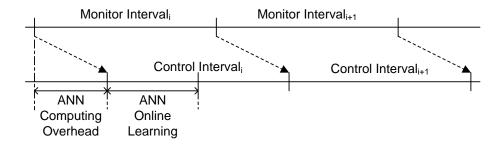

Figure 3.5: Pipelined monitoring and control intervals [62].

As in the work by Chen et al. [10, 9], we assume a control interval to be 50 thousand core clock cycles. The ANN control computation accounts for a significant portion of the overall control interval. In order to minimize the negative effect of this latency, we use two sets of different intervals for the critical latency monitoring and the control output change as illustrated in Figure 3.5. The two sets of intervals are offset by the ANN control computation time, effectively pipelining the overhead. By doing so, the ANN control computing does not block either the monitoring process or the control output change. However, the ANN computation does lead to increased staleness in the monitored data by the time the control decision is implemented. The impact of this computational latency is examined in Section 3.3.2.5.

### 3.3 Evaluation

In this section, we describe our experimental setup and subsequent evaluation of our proposed techniques.

### 3.3.1 Experiment Setup

The experimental baseline platform is a 16-core CMP with a 2-level cache hierarchy, split L1i and L1d private caches, and a combined, shared L2 last-level cache. Cache coherence is maintained via a MESI directory cache coherent protocol. The

| Parameter             | Configuration                     |  |

|-----------------------|-----------------------------------|--|

| # of cores            | 16                                |  |

| Core frequency        | Fixed at 1GHz                     |  |

| L1 data cache         | 2-way 256KB, 2 core cycle latency |  |

| $I_{2}$ cache $(IIC)$ | 16-way, 2MB/bank, 32MB/total      |  |

| L2 cache (LLC)        | 10 core cycle latency             |  |

| Directory cache       | MESI, 4 core cycle latency        |  |

| NoC                   | 4x4 2D mesh, X-Y DOR              |  |

| NOC                   | 4-flits depth/VC                  |  |

| Uncore V/F            | 10 levels, voltage: 1V - 2V       |  |

|                       | frequency: 250MHz - 1GHz          |  |

| Control interval      | 50000 core cycles                 |  |

| V/F transition        | 100 core cycles per step          |  |

Table 3.3: System parameters used for full-system simulations [62].

NoC topology is a  $4 \times 4$  2D mesh, with each node/router attached to a single processor core. Table 3.3 summarizes the baseline CMP setup.

Simulation experiments are performed using the gem5 [4] full system simulator, with the *Ruby* memory model and the *Garnet* network simulator [1]. The benchmark applications are taken from the PARSEC shared-memory, multi-processor, benchmark suite [3]. Specifically, we use the 11 PARSEC benchmarks currently supported by our simulation infrastructure, *Blackscholes, Bodytrack, Canneal, Dedup, Ferret, Fluidanimate, Freqmine, Streamcluster, Swaptions, Vips, and X264*. In each case, the entire benchmark is simulated, but only the Region Of Interest (ROI), is evaluated. The performance metric is evaluated as the runtime of the entire ROI. The energy consumption evaluation includes both dynamic and leakage energy. ORION 2.0 [30] and CACTI 6.0 [48] are used to estimate the energy consumption of the NoC and the LLC, respectively, both of which are based on 65*nm* CMOS process technology.

To focus on the evaluation of our uncore DVFS techniques, the core frequency

is fixed at 1GHz throughout the simulations. There are 10 uncore frequency levels between  $f_{max} = 1GHz$  and 250MHz. For each frequency, there is a corresponding voltage level between 1V and 2V, which is roughly the minimum voltage allowing correct uncore operation. The control interval is 50 thousand unscaled core clock cycles at 1GHz and each step uncore V/F level change takes 100 core cycles (100 cycles per step is sufficient assuming on-die regulation [18]). During V/F transitions, the uncore operation is halted.

The ANN configuration is summarized in Table 3.4. The ANN inputs are the critical latencies as viewed by each of the 16 cores in the past 5 intervals; thus the ANN has 80 first-layer nodes. The hidden layer and the output layer each has 10 nodes. The learning gain g is set to 0.001 for the offline learning. For the bootstrapped learning, the gain is either set at 0.1 or set as a variable value between 0.001 and 0.1, as described in Section 3.1.2.4. The error threshold  $\tau$ , error bound  $e_{max}$ , and consistency threshold  $\xi$  are used in the tandem control. The values of these parameters are identified empirically. Each ANN control computation takes 15 thousand core cycles, but does not block any uncore operations (see Section 3.2).

3.3.2 Experimental Evaluation

3.3.2.1 Overall Results

We compare the following 6 methods:

**Baseline:** the uncore constantly operates at highest V/F.

**PI:** best method from Chen et al. [9].

**Offln+Adpt+TdEager:** ANN trained with offline learning, operates with selfadaptation and eager tandem control.

Bstrp+Adpt: bootstrapped learning, self-adaptation and ANN control.

| Parameter                           | Configuration   |

|-------------------------------------|-----------------|

| # history intervals                 | 5               |

| # nodes at input layer              | $5 \times 16$   |

| # nodes at hidden layer             | 10              |

| # nodes at output layer             | 10              |

| Offline learning gain               | 0.001           |

| Constant bootstrapped learning gain | 0.1             |

| Variable bootstrapped learning gain | [0.001, 0.1]    |

| Error threshold $\tau$              | 0.001           |

| Max error bound $e_{max}$           | 0.1             |

| Consistency threshold $\xi$         | 0.6             |

| Computing overhead                  | 15K core cycles |

Table 3.4: ANN configuration parameters [62].

**Bstrp+Adpt+TdANN:** bootstrapped learning, self-adaptation and ANN-centric tandem control.

(Bstrp+Adpt)VG+TdANN: bootstrapped learning and self-adaptation with variable gain, ANN-centric tandem control.

Among the many techniques we investigated, the above includes only the best offline learning-based method and three best bootstrapped learning-based approaches. The results are normalized with the baseline and displayed in Figure 3.6. Compared to the PI control [9], our best method can reduce the uncore energy and the energydelay product by 25% and 27%, respectively. The performance degradation from our DVFS is less than 3% of the baseline. All applications show improved energy-delay versus PI control except *Blackscholes*. Blackscholes presents some difficulties for the ANN as it has two very short phases (beginning and end of simulation) with many misses, broken up by a long phase with few misses. Hence, the ANN's training on the initial phase is to short to be beneficial for that phase, nor it is useful for the middle phase. Similarly the final phase is ill-served by the training on the middle phase.