# THE DESIGN SPACE OF ULTRA-LOW ENERGY ASYMMETRIC CRYPTOGRAPHY

#### A Dissertation

by

#### ANDREW DAVID TARGHETTA

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Chair of Committee, Paul V. Gratz Committee Members, Sunil P. Khatri

> Harlan R. Harris Maury H. Rahe

Head of Department, Miroslav M. Begovic

May 2015

Major Subject: Computer Engineering

Copyright 2015 Andrew David Targhetta

#### ABSTRACT

The energy cost of asymmetric cryptography, a vital component of modern secure communications, inhibits its wide spread adoption within the ultra-low energy regimes such as Implantable Medical Devices (IMDs), Wireless Sensor Networks (WSNs), and Radio Frequency Identification tags (RFIDs). In literature, a plethora of hardware and software acceleration techniques exists for improving the performance of asymmetric cryptography. However, very little attention has been focused on the energy efficiency. Therefore, in this dissertation, I explore the design space thoroughly, evaluating proposed hardware acceleration techniques in terms of energy cost and showing how effective they are at reducing the energy per cryptographic operation. To do so, I estimate the energy consumption for six different hardware/software configurations across five levels of security, including both GF(p) and  $GF(2^m)$ computation. First, we design and evaluate an efficient baseline architecture for pure software-based cryptography, which is centered around a pipelined RISC processor with 256KB of program ROM and 16KB of RAM. Then, we augment our processor design with simple, yet beneficial instruction set extensions for GF(p) computation and evaluate the improvement in terms of energy per cryptographic operation compared to the baseline microarchitecture. While examining the energy breakdown of the system, it became clear that fetching instructions from program memory was contributing significantly to the overall energy consumption. Thus, we implement a parameterizable instruction cache and simulate various configurations. We determine that for our working set, the energy-optimal instruction cache is 4KB, providing a 25% energy improvement over the baseline architecture for a 192-bit key-size. Next, we introduce a reconfigurable GF(p) accelerator to our microarchitecture and measure the energy per operation against the baseline and the ISA extensions. For ISA extensions, we show between 1.32 and 1.45 factor improvement in energy efficiency over baseline, while for full acceleration we demonstrate a 5.17 to 6.34 factor improvement. Continuing towards greater efficiency, we investigate the energy efficiency of different arithmetic by first adding  $GF(2^m)$  instruction set extensions to our processor architecture and comparing them to their GF(p) counterpart. Finally, we design a non-configurable 163-bit  $GF(2^m)$  accelerator and perform some initial energy estimates, comparing them with our prior work. In the end, we discuss our ongoing research and make suggestions for future work. The work presented here, along with proposed future work, will aid in bringing asymmetric cryptography within reach of ultra-low energy devices.

# ACKNOWLEDGEMENTS

I would like to thank Don Owen, Allen Luettgen and Francis Israel for their contributions to this work. Without their invaluable guidance and efforts, none of this work would have been possible.

# TABLE OF CONTENTS

|    |                   | Page                                                                                                                                                 |

|----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| AF | BSTR              | ACTii                                                                                                                                                |

| A( | CKNO              | OWLEDGEMENTS iv                                                                                                                                      |

| TA | BLE               | OF CONTENTS                                                                                                                                          |

| LI | ST O              | F FIGURES vii                                                                                                                                        |

| LI | ST O              | F TABLES ix                                                                                                                                          |

| 1. | INT               | RODUCTION                                                                                                                                            |

|    | 1.1<br>1.2<br>1.3 | Asymmetric Cryptography                                                                                                                              |

| 2. | BAC               | CKGROUND 6                                                                                                                                           |

|    | 2.1               | Asymmetric Cryptography                                                                                                                              |

|    |                   | 2.1.2 The One-Way Function and Finite Fields92.1.3 Prime Fields and Modular Exponentiation112.1.4 Binary Fields132.1.5 Elliptic Curve Cryptography16 |

|    | 2.2<br>2.3        | HW/SW Codesign and Computer Architecture                                                                                                             |

| 3. | REI               | ATED WORK                                                                                                                                            |

| 4. | ALC               | GORITHMS AND SOFTWARE                                                                                                                                |

|    | 4.1<br>4.2        | ECDSA36Multi-precision Routines384.2.1 Prime Field Multiplication394.2.2 Binary Field Multiplication454.2.3 Binary Squaring47                        |

|    |                   | 4.2.4 Field Addition/Subtraction and Inversion 48                                                                                                    |

|    | 4.3    | Software Build/Run-time Environment | 49  |

|----|--------|-------------------------------------|-----|

| 5. | MIC    | ROARCHITECTURES                     | 50  |

|    | 5.1    | Baseline                            | 50  |

|    |        |                                     | 51  |

|    |        |                                     | 53  |

|    | 5.2    | 1 1                                 | 54  |

|    |        |                                     | 55  |

|    |        |                                     | 56  |

|    | 5.3    | · ·                                 | 61  |

|    |        | 5.3.1 Cache Implementation          | 61  |

|    |        |                                     | 63  |

|    |        | 5.3.3 Prefetching                   | 64  |

|    | 5.4    |                                     | 65  |

|    |        | 5.4.1 Coprocessor Interface         | 66  |

|    |        | 5.4.2 Prime-field Arithmetic Unit   | 69  |

|    | 5.5    |                                     | 78  |

|    |        | 5.5.1 Coprocessor Instructions      | 79  |

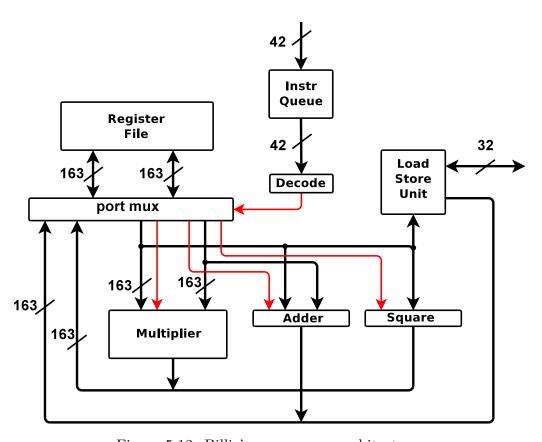

|    |        | 5.5.2 Microarchitecture             | 80  |

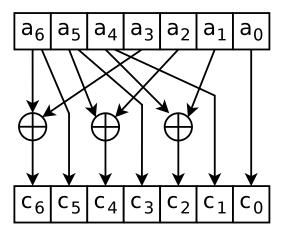

|    |        | $5.5.3  GF(2^m)$ Arithmetic Units   | 82  |

| 6. | MET    | ГНОDOLOGY                           | 85  |

| 0. | 101171 |                                     | 30  |

| 7. | EVA    | LUATION                             | 86  |

|    | 7.1    | Prime Fields                        | 86  |

|    | 7.2    | Binary Fields                       | 92  |

|    | 7.3    | Prime Fields vs. Binary Fields      | 93  |

|    | 7.4    | Power Consumption                   | 96  |

|    | 7.5    | Evaluation with Instruction Cache   | 98  |

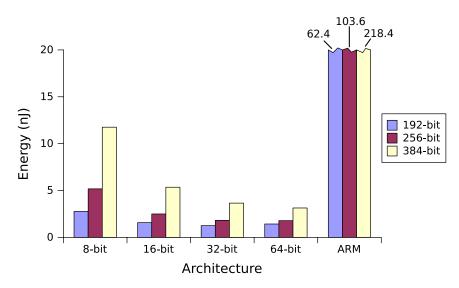

|    | 7.6    | Performance Evaluation              | 02  |

|    | 7.7    | Double Buffer Evaluation            | 05  |

|    | 7.8    | Baseline Validation                 | 06  |

|    | 7.9    | FFAU Evaluation                     | 07  |

| 8. | CON    | NCLUSIONS AND FUTURE WORK           | 11  |

| DE | סיםיםי | ENCES 1                             | 1 / |

# LIST OF FIGURES

| FIGURE |                                                                                                        |    |

|--------|--------------------------------------------------------------------------------------------------------|----|

| 1.1    | The hardware acceleration trade-off                                                                    | 4  |

| 2.1    | Basic cryptography                                                                                     | 7  |

| 2.2    | Asymmetric cryptography for confidentiality or authenticity                                            | 8  |

| 2.3    | Elliptic Curve point addition and doubling on $E(\mathbb{R})$                                          | 17 |

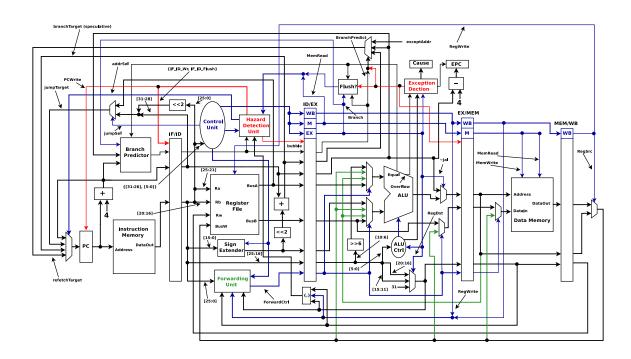

| 2.4    | The microarchitecture of a 5-stage pipeline processor                                                  | 26 |

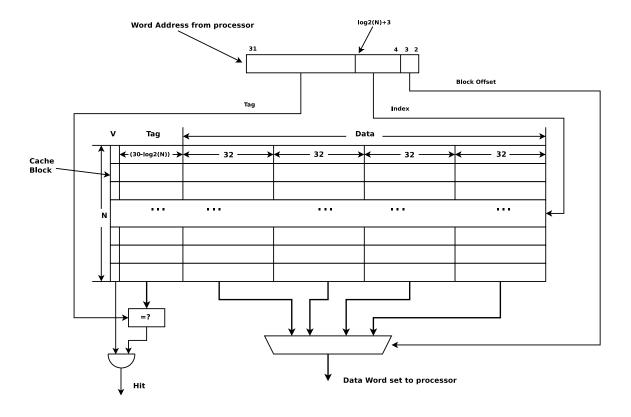

| 2.5    | A direct-mapped cache with a block size of 16 bytes and a 32-bit word width                            | 29 |

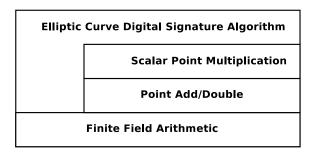

| 4.1    | Elliptic Curve Digital Signature Algorithm computation hierarchy                                       | 36 |

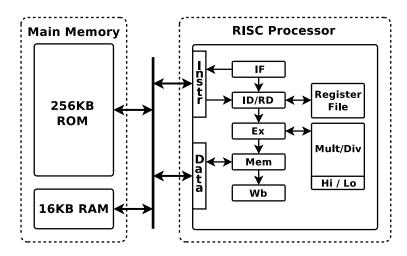

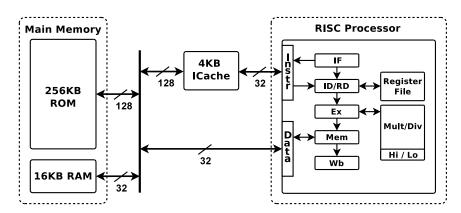

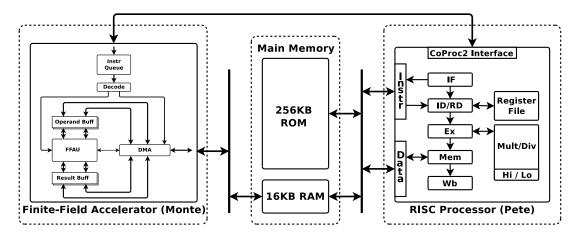

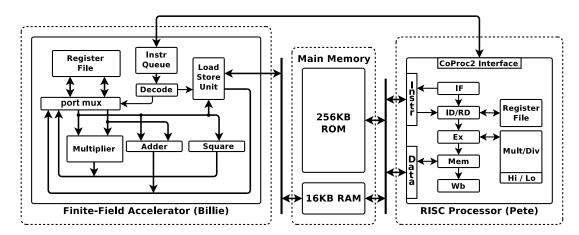

| 5.1    | Baseline: RISC Processor w/ ROM and RAM                                                                | 51 |

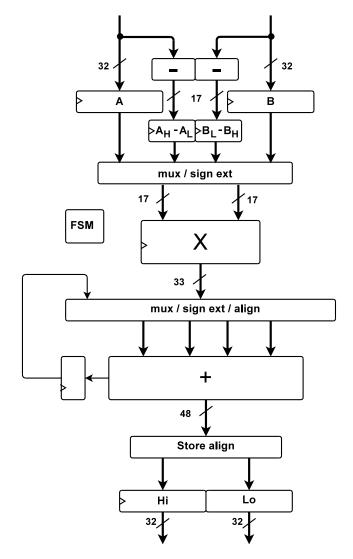

| 5.2    | The Karatsuba Multiply Unit within the baseline architecture                                           | 54 |

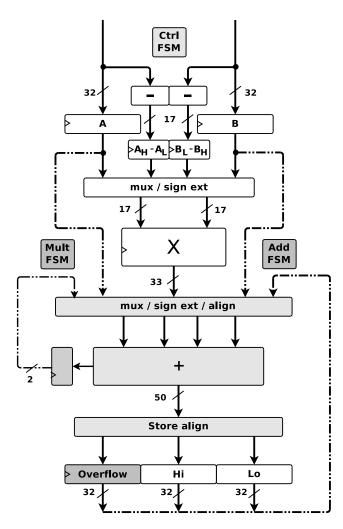

| 5.3    | The Karatsuba Multiply-Accumulate Unit including support for prime-field ISA extensions                | 58 |

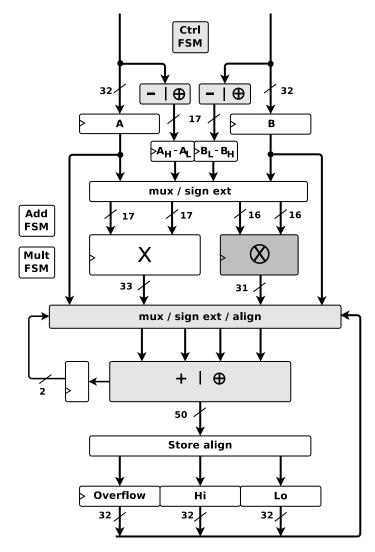

| 5.4    | The Karatsuba Multiply-Accumulate Unit including support for prime-<br>and binary-field ISA extensions | 59 |

| 5.5    | The implementation of a direct-mapped instruction cache                                                | 60 |

| 5.6    | Pete with an instruction cache                                                                         | 63 |

| 5.7    | The prime field accelerated architecture, "Pete with Monte."                                           | 66 |

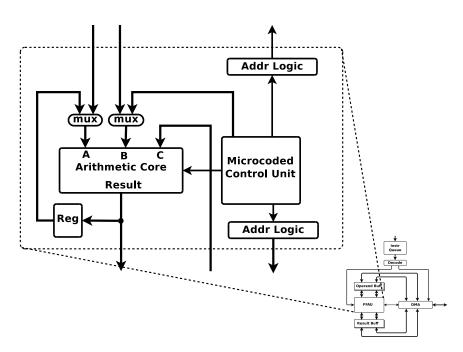

| 5.8    | The Finite-Field Arithmetic Unit at the center of "Monte"                                              | 70 |

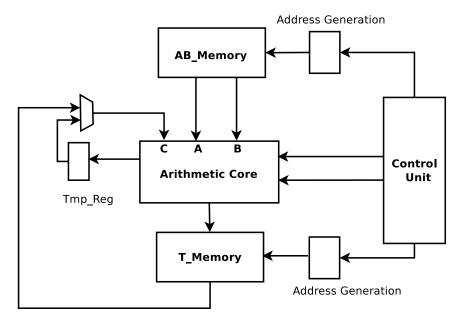

| 5.9    | Top Level Architecture of the FFAU                                                                     | 72 |

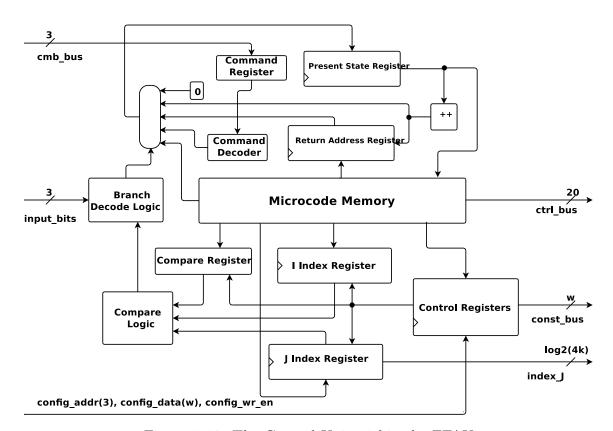

| 5.10   | The Control Unit within the FFAU                                                                       | 75 |

| 5.11   | The binary-field accelerated architecture "Pete with Billie"                                           | 78 |

| 5.12 | Billie's coprocessor architecture                                                                                          | 80  |

|------|----------------------------------------------------------------------------------------------------------------------------|-----|

| 5.13 | Binary-field squaring unit                                                                                                 | 84  |

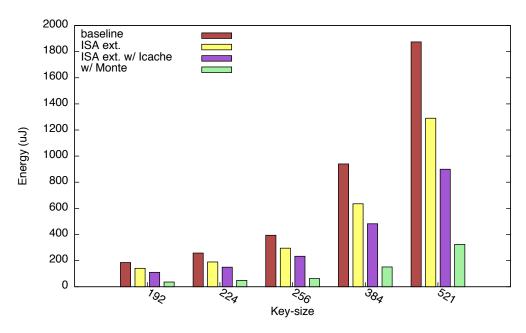

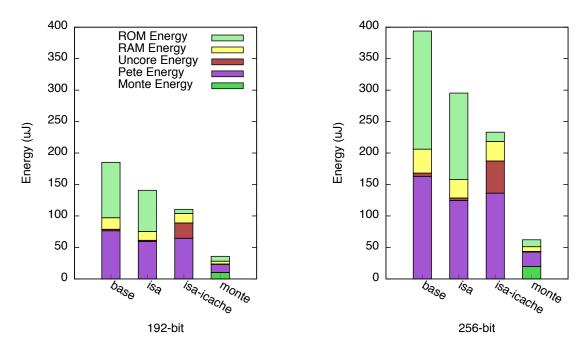

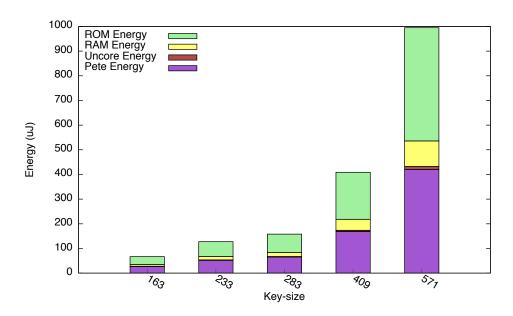

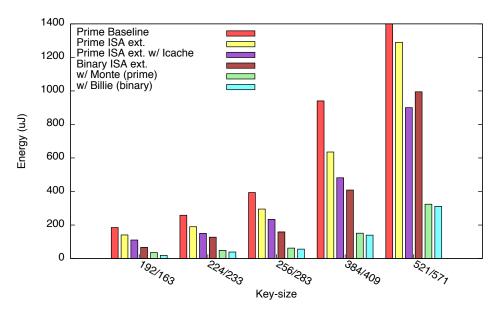

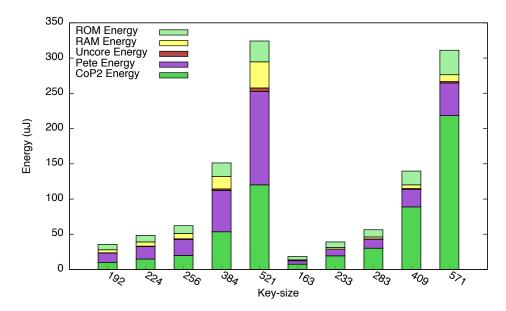

| 7.1  | Energy per Sign + Verify vs. key size and microarchitecture for prime fields                                               | 87  |

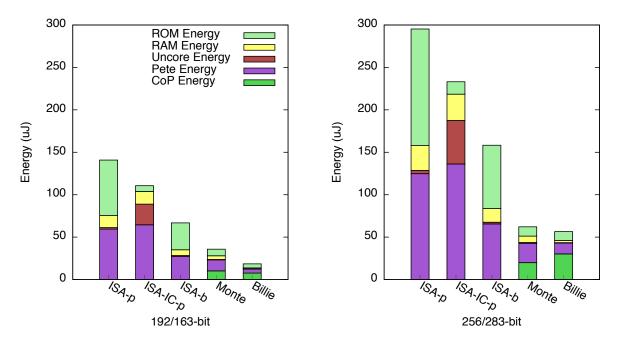

| 7.2  | Breakdown of energy per Sign + Verify for 192 and 256-bit key sizes into various sub-components                            | 88  |

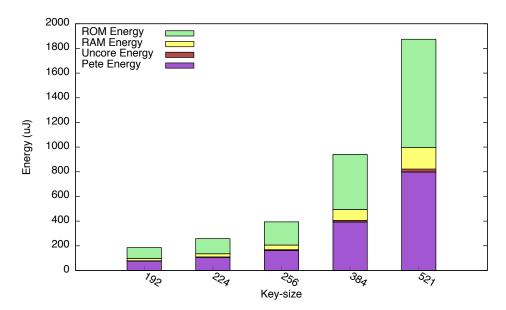

| 7.3  | Energy per Sign + Verify vs. key size for our baseline with no hardware acceleration                                       | 89  |

| 7.4  | Energy per Sign $+$ Verify vs. key size for the ISA extended microarchitecture and the architecture accelerated with Monte | 91  |

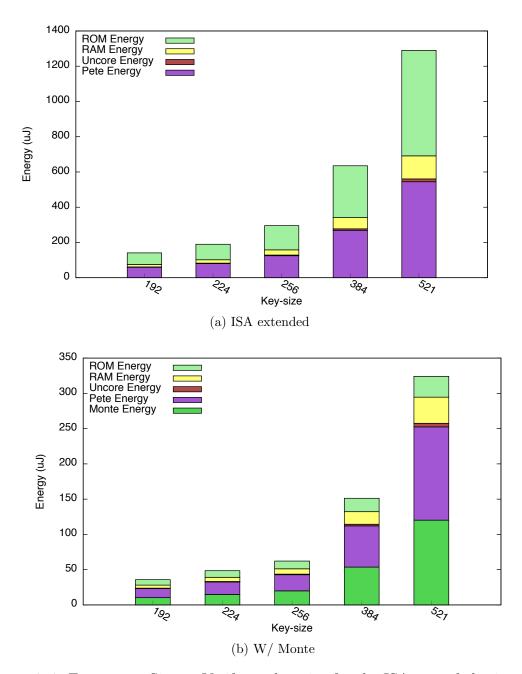

| 7.5  | Energy per Sign + Verify vs. key size for binary fields                                                                    | 92  |

| 7.6  | Energy per Sign + Verify vs. key size for binary ISA extensions                                                            | 93  |

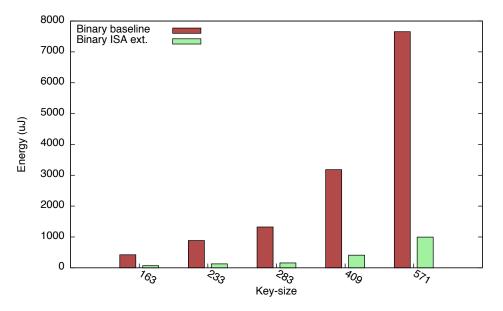

| 7.7  | Energy per Sign + Verify vs. key size, comparing prime and binary fields of equivalent security                            | 94  |

| 7.8  | Energy per Sign + Verify vs. key size for Monte and Billie                                                                 | 95  |

| 7.9  | Breakdown of energy per Sign + Verify for 192/163- and 256/283-bit key sizes into various sub-components                   | 97  |

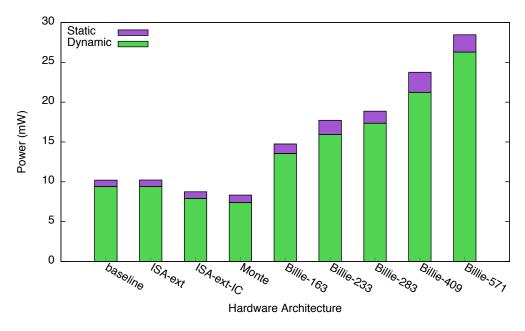

| 7.10 | Static and dynamic power of evaluated microarchitectures                                                                   | 98  |

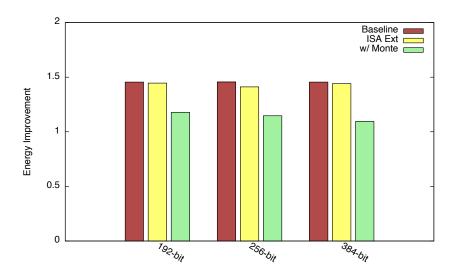

| 7.11 | Energy improvement with ideal instruction cache vs. key size                                                               | 99  |

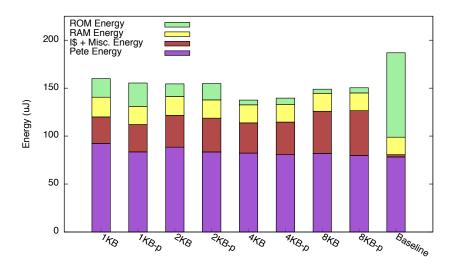

| 7.12 | Energy per 192-bit Sign + Verify with real instruction cache for various cache configurations                              | 100 |

| 7.13 | Energy per Sign + Verify vs. key size for prime ISA extended microarchitecture with 4KB instruction cache.                 | 102 |

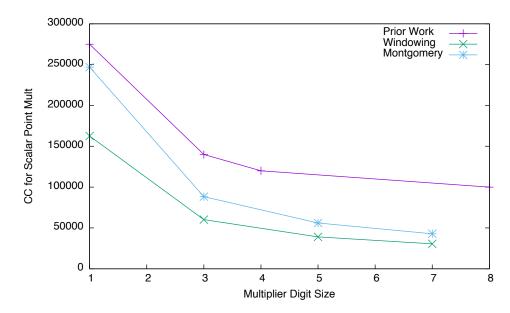

| 7.14 | Performance for 163-bit scalar point multiply comparing Billie to prior work                                               | 105 |

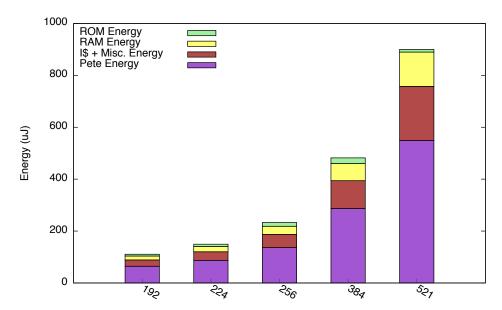

| 7.15 | Energy per Montgomery multiplication vs. datapath width                                                                    | 109 |

# LIST OF TABLES

| ΓABLE |                                                                                            |        |

|-------|--------------------------------------------------------------------------------------------|--------|

| 5.1   | Instruction set extensions for prime fields                                                | . 55   |

| 5.2   | Instruction set extensions for binary fields                                               | . 58   |

| 5.3   | Coprocessor 2 Instructions used to control Monte                                           | . 66   |

| 5.4   | Arithmetic Core Computational Capabilities                                                 | . 73   |

| 5.5   | Index Register Control Codes                                                               | . 75   |

| 5.6   | Coprocessor 2 Instructions used to control Billie                                          | . 79   |

| 7.1   | Latency per operation for prime-field microarchitectures                                   | . 103  |

| 7.2   | Latency per operation for binary-field microarchitectures                                  | . 104  |

| 7.3   | Area utilization, static power, and dynamic power vs. datapath width                       | n. 108 |

| 7.4   | Average power, execution time, and energy per Montgomery multiplication vs. datapath width | . 110  |

| 7.5   | Average power and energy per modular multiplication vs. key size for the ARM Cortex-M3     |        |

#### 1. INTRODUCTION

Since the advent of the microprocessor in the early 1970s, the number of components that fit on a single Integrated Circuit (IC) has continued to climb. This increase has primarily been due to advances in IC fabrication techniques, leading to trends in device scaling first described by Gordon Moore in 1964 [1]. "Moore's Law," the name given to the rapid growth in integrated circuit density, has given rise to the System on a Chip (SoC), which has allowed miniature computer systems to be embedded in everything from microwaves to the human body.

As SoCs become more ubiquitous, the desire to communicate with them escalates. For example, many programmable thermostats now have built-in wireless capabilities. Moreover, these devices are being trusted to communicate increasingly sensitive data, while concerns for privacy grow stronger. Therefore, embedded devices need to be equipped with algorithms such as asymmetric cryptography in order to securely communicate.

## 1.1 Asymmetric Cryptography

Asymmetric cryptography, also known as public key cryptography, has become an essential component in modern, secure communications. Unlike its symmetric counterpart, asymmetric cryptography requires separate keys for encryption and decryption, allowing it to solve a host of security challenges not possible with symmetric cryptography alone. Uses for asymmetric cryptography range from session key establishment for secure communications to digital signatures for message authenticity and non-repudiation. While symmetric cryptography is based on data shifts and permutations, asymmetric cryptography is built upon a foundation of mathematically hard problems. As a result, the computational requirements for asymmetric

cryptography are far greater than that of symmetric cryptography [2].

Employing asymmetric cryptography on ultra-low energy devices, such as Implantable Medical Devices (IMDs) [3, 4], Wireless Sensor Networks (WSNs) [5], and Radio Frequency Identification (RFID) tags [6, 7], can be especially challenging. In this class of applications, the energy cost of each operation is paramount to the device's utility. For example, in a typical IMD, each extra Joule expended in computation reduces the life of the device, and each surgical replacement of the device endangers the life of the patient. Security in this application is of critical importance; unauthorized access to an implanted cardiac defibrillator's programming interface poses an unambiguous threat to the patent's health and privacy.

Despite the obvious need for security in this domain, relatively few designs have incorporated encryption; among these, most employ symmetric (shared-key) encryption techniques [3]. More secure schemes for communication exist that involve asymmetric cryptography. However, the high computational cost of asymmetric cryptography has put these schemes out of reach for ultra-low energy applications. In the WSN domain, Wander et al. found that even weak asymmetric cryptography (160-bit ECC, equivalent to 1024-bit RSA) consumes approximately 72% of the energy allotted for communication handshaking. Moreover, they assume that only 5% to 10% of a WSN's energy budget is available for handshakes [8]. Pabbuleti et al. show that asymmetric cryptography reduces the energy cost of transmitting the signature compared to hash-based authentication protocols; however, the energy cost of computation rapidly exceeds the cost of signature transmission when considering 128-bit security levels [9]. For RFID tags, it is difficult to quantify the energy budget for encryption; however, because most tags are passive energy harvesters, the budget is significantly less than that of a WSN node.

To alleviate this computational burden, special purpose hardware can be designed

into an embedded system to accelerate portions of the cryptographic algorithms. Hardware designed to perform specific computations will typically do so more efficiently compared to hardware designed for general purpose computation. For the end user, hardware acceleration yields an overall design that is not only more responsive but is also much more energy efficient. Whereas past work has extensively evaluated the performance gains associated with hardware acceleration, this work focuses primarily on the energy benefit. In other words, this work attempts to comprehensively quantify energy improvements available through the hardware acceleration of asymmetric cryptography.

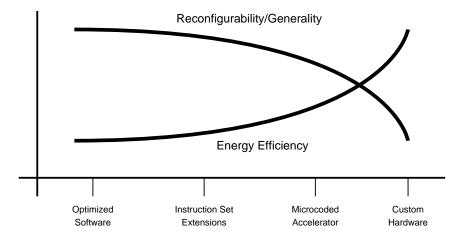

In the ultra-low energy domain, a spectrum of hardware/software acceleration techniques exists, in which an increase in hardware acceleration will lower reconfigurability in exchange for energy efficiency. Figure 1.1 depicts this trade-off with compiled software executing on a power-conscious processor on one side and a fully dedicated cryptographic processor on the other. The more interesting research lies in the middle, where some degree of reconfigurability is maintained while the energy consumed per operation is much less than that of a pure software implementation. This area is precisely the portion of the spectrum our work attempts to capture.

Understanding the energy design space specific to asymmetric cryptography is important in order to ensure the correct trade-offs are made prior to device fabrication. For example, a lack of reconfigurability could render the device obsolete sooner, as security requirements change, while too little hardware acceleration could render the device inoperable under assumed energy budgets. Furthermore, too much hardware acceleration could unnecessarily increase the cost of design validation and device fabrication. Thus, we compare different points on the spectrum and let the system designer choose which level of acceleration is appropriate.

Figure 1.1: The hardware acceleration trade-off.

#### 1.2 Thesis Statement

In this dissertation, I provide a thorough evaluation of the design space of energy-efficient asymmetric cryptography. In doing so, I describe the steps taken to design and accurately model our embedded system, which includes the development of an embedded processor with application specific extensions as well as two custom arithmetic accelerators. This dissertation showcases the energy efficiency of our custom arithmetic logic, making a strong argument for hardware acceleration of asymmetric cryptography.

#### 1.3 Contributions

For comparison, we start by evaluating a baseline architecture in terms of energy cost per signature and verification operation, as defined by the Elliptic Curve Digital Signature Algorithm (ECDSA) [10, 11]. Our baseline represents the left-most side of Figure 1.1 and consists of a low-power RISC processor without an instruction cache and a minimal memory layout, typical of an embedded microcontroller. Moving to the right within Figure 1.1, we add simple yet effective instruction set extensions

to our baseline architecture and evaluate the improvement in terms of energy cost per operation. Next, we evaluate our system with a reconfigurable, microcoded accelerator that we designed for prime finite-field arithmetic. As a comparison, we evaluate the energy benefit of a non-configurable, accelerator that we designed for binary finite-field arithmetic. Although the non-configurable aspect implies that the level of security is fixed after device fabrication, this configuration yields the highest degree of energy efficiency. Finally, we include an instruction cache in our design and measure the energy improvement that it provides for the ISA extended architectures. The contributions of this work are summarized as follows:

- Detailed power, energy and performance analysis of ultra-low energy asymmetric cryptography for several different hardware/software configurations within the same technology node, using the same experimental techniques

- Design space exploration across a range of Elliptic Curve Cryptography (ECC) key-sizes that includes up to 521-bit prime and 571-bit binary, providing insight into current and future secure data exchange for embedded systems

- Development of a microcoded, prime-finite field accelerator that maintains reconfigurability via microcode programming while decreasing the energy per digital signature

- Development of a binary-field accelerator that further reduces the energy of asymmetric cryptography while outperforming prior work

- Evaluation of the energy benefit of an instruction cache in the context of asymmetric cryptography

- Detailed hardware models and recommendations for future energy exploration within the ultra-low energy domain

#### 2. BACKGROUND

In this chapter, we refresh the reader's understanding of the relevant background topics for this study. We start by reviewing basic cryptographic concepts and introducing the mathematics that underpin all asymmetric cryptosystems. Then we provide a brief primer on computer architecture in order to explain some of the terminology referenced throughout this work. Finally, we review how energy is consumed in digital circuits and discuss the relationship between power and energy. A reader already familiar with these topics may skip this chapter.

#### 2.1 Asymmetric Cryptography

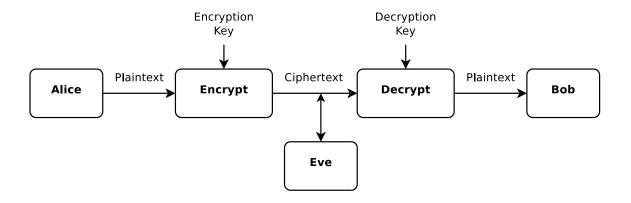

The field of cryptography encompasses the techniques and mechanisms used to communicate securely over an insecure channel. The primary objective is to encrypt data prior to communication in such a way that it can only be decrypted by the intended recipient. Consider the textbook scenario, depicted in Figure 2.1, where Alice encrypts a plaintext message using her encryption key and sends the encrypted data, also know as the ciphertext, to Bob over a public channel. Bob uses his decryption key to translate the ciphertext back into plaintext. Along the way, the data is intercepted by Eve, an eavesdropper; however, Eve is unable to recover the plaintext message without Bob's decryption key.

In cryptography, there are two distinct categories: symmetric and asymmetric. Symmetric cryptography uses the same key for encrypting and decrypting data, whereas asymmetric cryptography uses one key for encrypting and a separate key for decrypting. By keeping one key private and making the other key publicly available, asymmetric cryptography (a.k.a public-key cryptography) can solve a host of problems not possible with symmetric cryptography alone[12]. Classic schemes, such

Figure 2.1: Basic cryptography

as substitution ciphers, along with some modern encryption algorithms, such as DES and AES, fall into the symmetric cryptography category. RSA and Diffie-Hellman key exchange are examples of early asymmetric cryptography, while modern schemes employ Elliptic Curve Cryptography, such as Elliptic Curve Diffie-Hellman (ECDH) key exchange and the Elliptic Curve Digital Signature (ECDSA).

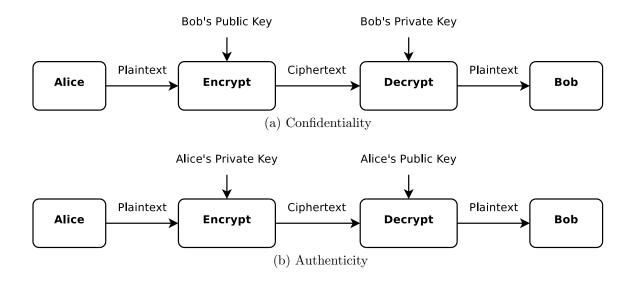

#### 2.1.1 Confidentiality, Authenticity, and Integrity

Confidentiality refers to the protection of a message from eavesdropping, while authenticity refers to trust in the origin of the message. Data integrity ensures the message has not been modified, whether accidental or malicious. In an asymmetric cryptosystem, each communicating entity has its own private/public key pair. Then, depending on how the keys are used, asymmetric cryptography can provide data confidentiality or authenticity/integrity. Figure 2.2a demonstrates the use of asymmetric cryptography for confidentiality, while Figure 2.2b demonstrates its use for authenticity/integrity. For confidentiality, Alice uses Bob's public key to encrypt a message and sends the resulting ciphertext to Bob who uses his private key to decrypt the ciphertext. In this scenario, only Bob's private key can be used to recover

a message encrypted with his public key. Furthermore, Bob's private key cannot be derived from his public key. Even though the message is sent via an unsecured channel, it is still protected from unauthorized access.

Figure 2.2: Asymmetric cryptography for confidentiality or authenticity

For authenticity, Alice uses her private key to encrypt a message before she sends it to Bob, who in turn uses her public key to decrypt the ciphertext. If the decryption process yields an intelligible message, then Bob has high degree of confidence that the message originated from Alice. Remember that only Alice's private key could have been used to encrypt a message that can be decrypted with her public-key. It should be noted that tampering with the ciphertext will yield an unreadable message after decryption, so data integrity is ensured as well.

Both confidentiality and authenticity can be achieved by encrypting first for confidentiality and then again for authenticity. In which case, two encryption operations

<sup>&</sup>lt;sup>1</sup>The underlying assumption here is that Bob is able to somehow authenticate Alice's public key. This is where certificates and the public-key infrastructure come into play.

will be required on the sender's side as well as two decryption operations on the receiver's side. Likewise, both key pairs from Alice and Bob are required. In this scenario, an adversary who stands between Alice and Bob can neither decipher their communication nor successfully impersonate one or the other.

With the properties of confidentiality, authenticity and data integrity, asymmetric cryptography can solve secret-key distribution problems. In order for two entities to communicate securely using a symmetric cipher, they must somehow securely exchange a shared secret key. Without asymmetric cryptography, this would require an additional medium that can guarantee privacy; otherwise, an adversary could discover the shared key and easily decrypt future communication. Moreover, large key rings are required if a number of devices need to communicate securely. For instance, n devices would require a total of  $\frac{n(n-1)}{2}$  different secret keys, where each device must store n-1 keys [2].

With asymmetric cryptography, any two entities can easily and securely exchange a temporary secret-key and then use symmetric cryptography to encrypt data traffic for the remainder of the communication session. It should be noted that asymmetric cryptography is ill-suited for bulk data encryption due to its high computational cost. Thus, it is more energy efficient to amortize a key-exchange across a lengthy communication session [13]. We will talk more about the protocols developed for secure key exchange after delving into the mathematics.

## 2.1.2 The One-Way Function and Finite Fields

Improving the energy efficiency of an asymmetric cryptosystem requires an understanding of the underlying mathematics. Therefore, the following section will briefly review the necessary mathematical concepts. At the core of asymmetric cryptography is the mathematical one-way function with a trapdoor. A one-way function has a forward operation that is easy to compute but an inverse operation that is considered computationally infeasible to compute. When a one-way function has a trapdoor, certain knowledge can make the inverse operation also easy to compute [14]. One-way functions for asymmetric cryptography are constructed using finite fields, which are part of a division of mathematics known as abstract algebra. In order to understand *finite fields*, we must first understand *groups* and *rings*.

A group,  $\{G, \bullet\}$ , is a set (G) with a binary operation  $(\bullet)$  and the following properties:

- Closure, if  $a, b \in G$ , then  $a \bullet b \in G$

- Associative,  $a \bullet (b \bullet c) = (a \bullet b) \bullet c$  if  $a, b, c \in G$

- Unit Element, there exists an element, e, such that  $a \bullet e = e \bullet a = a$  for all  $a \in G$

- Inverse Element, for all  $a \in G$  there exists an element a' such that  $a \bullet a' = a' \bullet a = e$

If the *commutative* property,  $a \bullet b = b \bullet a$  for all  $a, b \in G$ , holds true, then the group is an *Abelian group*.

A ring,  $\{R, +, \times\}$ , is a set (R) with two binary operations  $(+, \times)$  and the following properties:

- R is an Abelian group with respect to +

- Closure over ×

- Associative over  $\times$

- Unit Element with respect to ×

• Distributive,  $a \times (b+c) = a \times b + a \times c$  and  $(b+c) \times a = b \times a + c \times a$

If the *commutative* property holds true for  $\times$ , then the ring is commutative. Note that the + and  $\times$  operations are commonly referred to as addition and multiplication, respectively.

A Field,  $\{F, +, \times\}$ , is a commutative ring such that all elements except the additive identity element (i.e., zero) in F have a multiplicative inverse element. For multiplication, the inverse element of a is denoted by  $a^{-1}$ . The inverse of a with respect to addition is denoted by -a. In a field, the subtraction and division operations are derived from addition and multiplication by utilizing the inverse element of the second operand, so the following holds true:

•

$$a - b = a + (-b)$$

•

$$a/b = a \times (b^{-1})$$

In other words, a field is a set of elements over which we can perform addition, subtraction, multiplication and division; however, division by zero is not allowed. If F is finite, then the field is referred to as a finite field.

#### 2.1.3 Prime Fields and Modular Exponentiation

The modulo operation, a modulo p where a and p are integers, is equal to r such that a = q \* p + r for some value of q. The integers from 0 to p-1 are known as the set of residues modulo p. If p is prime and all arithmetic computations on the set of residues are performed modulo p, the result is a prime field, denoted by GF(p). The unit element with respect to addition for prime fields is 0, while the unit element for multiplication is 1. The following are examples of GF(7) computation:

• Addition:  $2 + 5 \mod 100 = 0$

<sup>&</sup>lt;sup>2</sup>GF stands for Galois Field and is named after the French mathematician, Evariste Galois.

• Subtraction:  $3 - 6 \mod 100 = 4$

• Multiplication:  $5 \times 4 \mod 100 = 6$

• Division:  $2 \div 4 \mod 100 = 4$

For division, if  $a, b, c \in GF(p)$ ,  $c = a \div b$  modulo p such that  $c \times b \equiv a$  modulo p and is found by first solving for  $b^{-1}$  modulo p then computing  $a \times b^{-1}$  modulo p. It should be noted that big integer division is extremely costly in terms of computation. Thus, more efficient methods exist to perform the reduction operation  $(modulo\ p)$  and compute the inverse  $(a^{-1}\ modulo\ p)$ . We will discuss these methods in more detail when we talk about the specific algorithms used in this study.

Traditional public-key cryptosystems such as RSA, Diffie-Hellman, and the Digital Signature Algorithm (DSA) utilize modular exponentiation  $(y = g^x \mod p)$  as the one-way function [11, 15, 12]. The brute-force method for computing modular exponentiation is to multiply g by itself x times, but far more efficient techniques exist, such as the suite of repeated square-and-multiply algorithms [2]. Each square or multiply in modular exponentiation is an operation performed over a finite field.<sup>3</sup> Assuming a 4096-bit RSA algorithm, on the order of 1.5\*4096 field multiplications, each of size 4096 bits, must be performed for each modular exponentiation. The reverse operation, compute x given y, g, p, is referred to as the Discrete Logarithm Problem (DLP) and is considered intractable as the size of the modulus increases. Methods considerably more efficient than brute force exist for computing the DLP. Thus, very large integers must be used to ensure security with traditional public-key cryptosystems based upon modular exponentiation. As we will see shortly, more efficient one-way functions exist, which allow computation over smaller fields.

$<sup>^3</sup>$ To be pedantic, the operations are over a  $multiplicative\ Abelian\ group$  because modular exponentiation only uses multiplication.

## 2.1.4 Binary Fields

Prime fields are commonly used for asymmetric cryptography, but when considering elliptic curves, other types of fields may be used as well. For finite-field computations, the order does not necessarily have to be prime but must be a power of a prime, e.g.,  $GF(p^m)$  where m is an integer such that m > 0, and p is the characteristic of the finite field. If m > 1, polynomial arithmetic, such that the coefficients are computed modulo p can be used.

Finite fields with a characteristic of 2, referred to as binary fields or  $GF(2^m)$ , are especially attractive for custom hardware implementations because addition is simply a bitwise XOR operation. Since multiplication is derived from addition, the partial-product accumulation within multiplication is similar to that of integer multiplication but without the carry logic. For this reason, binary-field arithmetic is often called "carry-less" arithmetic.

Because we use polynomial arithmetic for binary-field computation, we borrow the polynomial representation. As such, a  $GF(2^m)$  field is denoted in the following way:  $a(x) = a_{m-1}x^{m-1} + \cdots + a_2x^2 + a_1x + a_0$  where x is the indeterminate of the polynomial, and the coefficients,  $a_{m-1}, \dots, a_2, a_1, a_0 \in [0, 1]$ . In a computer system, a binary-field element is stored as an m-bit binary vector,  $(a_{m-1}, \dots, a_2, a_1, a_0)$ . As with prime fields, the result of a binary-field multiplication needs to be reduced. Binary-field reduction is performed modulo an irreducible polynomial, f(x). Note that unlike prime fields, binary-field addition and subtraction do not require reduction because there are no arithmetic carries.

The following are examples of  $GF(2^7)$  computation assuming  $f(x) = x^7 + x + 1$ :

• Addition:

$$(x^6 + x^4 + x^3 + 1) + (x^5 + x^4 + x^2 + 1) = x^6 + x^5 + x^3 + x^2$$

• Subtraction:

$$(x^6 + x^4 + x^3 + 1) - (x^5 + x^4 + x^2 + 1) = x^6 + x^5 + x^3 + x^2$$

- Multiplication:  $(x^6 + x^3 + x) \times (x^6 + x^2 + 1) \mod (x^6 + x^3 + x) \times (x^6 + x^2 + 1) \mod (x^6 + x^3 + x) \times (x^6 + x^2 + 1) \mod (x^6 + x^3 + x) \times (x^6 + x^2 + 1) \mod (x^6 + x^3 + x) \times (x^6 + x^2 + 1) \mod (x^6 + x^3 + x) \times (x^6 + x^3 + x) \times (x^6 + x^3 + x) + (x^6 + x^3$

- Squaring:  $(x^6 + x^3 + 1)^2$  modulo  $f(x) = x^5 + 1$

Let us take a closer look closer at multiplication. First, we must perform polynomial multiplication, such that the coefficients are computed *modulo* 2, as shown below:

$$(x^{6} + x^{3} + x)(x^{6} + x^{2} + 1) = x^{12} + x^{8} + x^{6} + x^{9} + x^{5} + x^{3} + x^{7} + x^{3} + x$$

$$= x^{12} + x^{9} + x^{8} + x^{7} + x^{6} + x^{5} + x$$

Then we reduce the result of the polynomial multiplication by dividing it by f(x) and taking the remainder, *i.e.*, compute  $modulo\ f(x)$ . The necessary polynomial division is shown below:

It should be noted that polynomial division is extremely costly in terms of computation. Thus, more efficient algorithms exist to perform the reduction operation, and we will elaborate on those algorithms in Section 4.2.

For the squaring example, we have the following:

$$(x^{6} + x^{3} + 1)(x^{6} + x^{3} + 1) = x^{12} + x^{9} + x^{6} + x^{9} + x^{6} + x^{3} + x^{6} + x^{3} + 1$$

$$= x^{12} + x^{6} + 1$$

$$= (x^{5})(x^{7}) + x^{6} + 1$$

$$= (x^{5})(x + 1) + x^{6} + 1$$

$$= x^{6} + x^{5} + x^{6} + 1$$

$$= x^{5} + 1$$

One thing to note is that most of the terms generated in the first step cancel out.

Mathematically, this can be explained by observing that

$$(a+b)(a+b) = a^2 + (ab+ab) + b^2$$

where (ab + ab) equals zero because addition is an exclusive OR operation. This concept can be extrapolated to more terms as shown below:

$$(a+b+c)(a+b+c) = a^2 + b^2 + c^2$$

For this reason, binary-field squaring is much less computationally expensive compared to binary-field multiplication.

Although the squaring algorithm for binary fields is fast, a reduction operation must still be performed. Thus, the example above includes a glimpse of the aforementioned fast-reduction techniques. In the fourth step, we are able to substitute x + 1 for  $x^7$  because of modular congruency shown below:

$$x^7 + x + 1 \equiv 0 \mod 0 f(x)$$

$x^7 \equiv x + 1 \mod 0 f(x)$

Finally, it should be noted that although binary-field arithmetic can be efficiently realized in hardware, some protocols, such as the Elliptic Curve Digital Signature Algorithm (ECDSA) still require prime-field mathematics [16]. In the next section, we will introduce a more efficient one-way function based on elliptic curves.

#### 2.1.5 Elliptic Curve Cryptography

The Elliptic Curve Cryptography (ECC) analog of modular exponentiation is scalar point multiplication, which involves repeated addition-and-doubling of points on an elliptic curve defined over a finite field. As with modular exponentiation, the reverse operation, known as the Elliptic Curve Discrete Logarithm Problem (ECDLP), is considered intractable.

Elliptic curves are defined by a form of the Weierstraß equation. When prime fields<sup>4</sup> are used as the *underlying field*, K, the elliptic curve equation can be simplified to the following:

$$E: y^2 = x^3 + ax + b (2.1)$$

where  $a, b \in K$  and the discriminant,  $\triangle = -16(4a^3 + 27b^2) \neq 0$ . For binary fields, the simplified Weierstraß equation is given by:

$$E: y^2 + xy = x^3 + ax^2 + b (2.2)$$

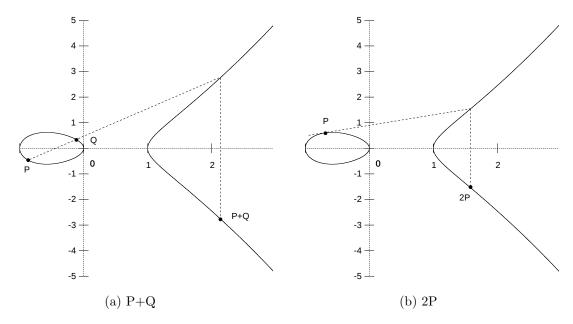

For cryptography, K is a finite field; however, for pedagogical purposes, it is useful to view elliptic curves defined over the set of real numbers,  $K = \mathbb{R}$ , as shown in Figure 2.3. A graphical representations of point addition on an elliptic curve,

<sup>&</sup>lt;sup>4</sup> A prime field has a characteristic  $\neq 2, 3$ .

Figure 2.3: Elliptic Curve point addition and doubling on  $E(\mathbb{R})$

$E(\mathbb{R})$ , is depicted in Figure 2.3a. As shown, P and Q are added by first drawing a straight line through the two points and then locating the third point of intersection between the line, PQ, and the elliptic curve. The point, P+Q, is then the x-axis reflection of the third point of intersection. For point doubling, shown in Figure 2.3b, the x-axis reflection of 2P is the second point of intersection between the tangent line of point P and the elliptic curve.

The set of points defined on the elliptic curve along with the point addition operation form an *Abelian group*. The unity element for this Abelian group is the point at infinity,  $\infty$ . When the line between two points is vertical, the third point of intersection is said to be at infinity. Thus,  $P - P = \infty$  where -P is the x-axis reflection of P.

Mathematically, point addition and doubling for prime fields can be described by the equations below such that  $A = (x_a, y_a)$ ,  $B = (x_b, y_b)$ , and  $C = (x_c, y_c)$ . • Addition:

$$x_c = \left(\frac{y_b - y_a}{x_b - x_a}\right)^2 - x_a - x_b \tag{2.3}$$

$$y_c = \left(\frac{y_b - y_a}{x_b - x_a}\right) (x_a - x_c) - y_a \tag{2.4}$$

#### • Doubling:

$$x_c = \left(\frac{3x_a^2 + a}{2y_a}\right)^2 - 2x_a \tag{2.5}$$

$$y_c = \left(\frac{3x_a^2 + a}{2y_a}\right)(x_a - x_c) - y_a \tag{2.6}$$

Note that from Eq. (2.2), we can develop slightly different point addition and doubling expressions for binary fields.

Just like modular multiplication and squaring are used by the modular exponentiation algorithm, point addition and doubling are used for the scalar point multiplication algorithm, which is the elliptic curve one-way function. Scalar point multiplication, Q = xP, can be computed via the repeated point add-and-double method such as right-to-left binary point multiplication described in Algorithm 1. The right-to-left binary point multiplication algorithm is nearly identical to the algorithms used for modular exponentiation, except square and multiply have been replaced with double and add, respectively. It should be noted that Algorithm 1 is shown here purely for example sake. Due to its simplicity, it is relatively inefficiently and susceptible to side-channel attacks. In practice, more efficient sliding-window algorithms are utilized, in which more than one bit of the multiplier is scanned at once [16].

As we can see from Eq. (2.3) to Eq. (2.6), each point operation requires a field inversion, which can be up to two orders of magnitude more costly than a field

# **Algorithm 1** Calculate Q = xP [16]

```

Input: P \in E(F_q) and integer x \ge 1

Q \Leftarrow \infty

while x \ne 0 do

if x is odd then

Q \Leftarrow Q + P

end if

x \Leftarrow \lfloor x/2 \rfloor

if x \ne 0 then

P \Leftarrow 2P

end if

end while

return Q

```

multiplication. Rather than using 2-dimensional, affine coordinates, we can use 3-dimensional, projective coordinates. When using projective coordinates, intermediate field inversions are not necessary. Instead, a conversion into projective coordinates is performed at the beginning of a scalar point multiplication. Then throughout the scalar point multiplication, projective coordinates are used, requiring no inversion operations. Finally at the end of the scalar point multiplication, one inversion is required to map the result back into affine coordinates.

Various projective coordinates have been proposed in literature; however, for prime fields, Jacobian coordinates stand out as being the most computationally efficient [16]. The mapping between Jacobian and affine points is  $(X,Y,Z) \rightarrow (X/Z^2,Y/Z^3)$  such that  $Z \neq 0$ , and the point at infinity is represented as (1,1,0). To project an affine point onto a Jacobian point, we simply set Z = 1. However, to convert a Jacobian point into an affine point, we must perform one field inversion to calculate  $Z^{-1}$ . For prime fields, the negative of a Jacobian point, (X,Y,Z), is simply (X, -Y, Z). We can further improve the computational efficiency by using a

mixture of Jacobian and affine points. In particular, we use Jacobian coordinates for the point double operation, but when we perform a point addition, we actually add an affine point to a Jacobian point.

For binary fields, Lopez and Dahab introduced a more efficient coordinate system with the projective mapping of  $(X, Y, Z) \to (X/Z, Y/Z^2)$  and the point at infinity being represented as (1,0,0) [17]. Because the additive inverse of an element in a binary field is the element itself, the negative of a point is represented differently compared to the prime counterpart. Specifically, in the Loped-Dahab (LD) coordinate system, the negative of the point (X,Y,Z) is (X,X+Y,Z).

Determining the number of finite-field operations for ECC is not as straightforward as it is for modular exponentiation because each ECC addition and doubling encompasses potentially dozens of finite-field operations. Given the same key size, there is an order of magnitude more field operations for a typical ECC scalar point multiplication compared to an RSA modular exponentiation, but the advantage of elliptic curves over modular exponentiation for asymmetric cryptography is that the ECDLP is considered to be computationally harder than the DLP. Consequently, the size of integers used for ECC is much smaller than that of modular exponentiation-based schemes of equivalent security. For this reason, ECC is substantially more energy efficient than modular exponentiation schemes for the same level of security and is the only asymmetric cryptosystem evaluated in this study [8, 13]. Given existing computational capabilities, integer computation in the range of 192-bits to 384-bits maintains adequate security for ECC. To provide similar levels of security, RSA would need 1024-bit to 15360-bit computations [18].

The discussion here on elliptic curve cryptography is in no way intended to be comprehensive. For a more in-depth treatment, we recommend two excellent books dedicated to the subject, the "Guide to Elliptic Curve Cryptography" and the "Hand-

book of Elliptic and Hyperelliptic Curve Cryptography" [16, 19].

## 2.2 HW/SW Codesign and Computer Architecture

The work presented here investigates the energy efficiency of asymmetric cryptography on an ultra-low power embedded system. The term *embedded system* refers to a special-purpose, System on a Chip (SoC), *i.e.*, a small self-contained computer system. An embedded system is comprised of two major design components, namely hardware and software. The *hardware* is the tangible part, typically containing digital logic gates fabricated on a silicon substrate, while the *software* is the program that orchestrates computation on the hardware. Often, these two components are designed separately; however, hardware/software co-design can yield far more efficient systems.

At the heart of any modern computer system is the *processor core*. Although higher performance systems contain processors with multiple cores, we focus here on a system with a single core. A typical processor core follows the stored-program model, in which it sequentially fetches *instructions* from memory and performs arithmetic and logic operations on data accordingly. The unit of data that is processed by a given instruction is referred to as a *word*. Common word widths for modern processors include 32-bits and 64-bits; however, some embedded systems use 8-bit and 16-bit words. Data words can be stored in either memory or registers, the latter having a much faster access time than the former. A *register* is nothing more than a grouping of logic storage elements knowns as flip-flops. From the programmer's point of view, data and instructions are stored in the same memory but usually in different locations, *i.e.*, a *Von Neumann architecture*.

The *Instruction Set Architecture* (ISA) is the programmers interface to the processor and essentially defines the hardware/software boundary. We can broadly cate-

gorize an ISA into one of two categories: RISC or CISC. In a Reduced Instruction Set Computer (RISC) architecture, instructions only perform operations on data within registers. Therefore, data is loaded from memory into registers prior to computation and then stored back out to memory after computation. For this reason, RISC architectures are synonymous with load-store architectures. A Complex Instruction Set Computer (CISC) architecture, on the other hand, is a register-memory architecture, where instructions can operate on data in memory as well as in registers. Common examples of a RISC architecture include MIPS, SPARC, PowerPC, and the ubiquitous ARM, while well-known CISC architectures include Intel's x86 and Motorola's 68000.

One of the primary advantages of a RISC architecture is that the instructions have a simpler, fixed-width format and are therefore easier to decode in hardware. Coupled with the load-store concept, a RISC machine is also easier to pipeline and hence a good choice for an embedded system. This is especially true if code compatibility is not a requirement, which means the designer is not forced to use a legacy CISC ISA. For our work, we chose a subset of the MIPS ISA due mostly to its popularity in the academic community but also partially because of being well supported in the GNU toolchain.

The implementation of an ISA is commonly called the *microarchitecture*. An ISA can have various microarchitectures depending on the generation of the machine and the level of expected performance. For example, the R2000 and R3000 both implement the MIPS-I ISA; however the R3000 is an improvement over the R2000 [20]. Both machines are binary compatible, which implies a program does not have to be modified to run on either machine.<sup>5</sup> The field of computer architecture encompasses

<sup>&</sup>lt;sup>5</sup>Binary compatibility does not necessary mean a program written for one machine will run well on the other as a certain amount of machine-level software optimization might be present.

microarchitecture design as well as ISA design. Although very little research today is being put towards full ISA design, a hardware/software codesign project such as this will often include both aspects of computer architecture by extending or enhancing an existing ISA.

The microarchitecture of our research processor is based on the classic five-stage pipelined processor taught in many computer architecture classes [21]. In such a design, instruction execution consists of five stages, each normally requiring a single clock cycle. The five stages are described below:

- 1. Fetch: An instruction is read from memory (or an instruction cache, which will be discussed later), and the Program Counter (PC), which keeps track of the processor's place in the instruction sequence, is updated.

- 2. Decode: The instruction is decoded, creating control signals that will flow down the pipeline, and the register file is read. Also, hazards (briefly discussed later) are detected and handled.

- 3. Execute: This stage contains the Arithmetic-Logic Unit (ALU), which performs an arithmetic or logic operation on the data read from the register file. If the instruction is a load or store instruction, the memory address is calculated. If the instruction is a branch instruction, which changes the control flow of the program, the branch address is determined.

- 4. Memory: If the instruction is a load or store instruction, the memory (or the data cache) is accessed. Instruction exceptions are also handled in this stage. An exception interrupts normal program execution and can be caused by a number things, including an unrecognized instruction, an arithmetic overflow, or even an external notification.

5. Write-Back: The register file is updated in this last and final stage. If the instruction was a load, the value read from memory is written into the appropriate register. If the instruction was an arithmetic-logic instruction, the destination register is written.

In an *in-order* microarchitecture, instructions flow through the pipeline in program order, ideally progressing to the next stage every clock cycle. This implies that the ideal throughput of such a machine is one instruction per clock cycle (IPC=1).<sup>6</sup> Real processors, however, do not achieve ideal IPC due to hazards in the pipeline. A hazard occurs when an instruction must stall because it depends on the results of an instruction ahead of it in the pipeline. Hazards are a negative effect of instruction execution overlap and must be handled properly to ensure correct execution. We will now briefly describe the hazards possible in our 5-stage pipelined processor and discuss how they are handled.

Three types of hazards exist in a traditional processor: data, control and structural. A data hazard exists when an instruction needs the result of another instruction ahead of it in the pipeline. In computer architecture terminology, this presents a Read-After-Write (RAW) data hazard. Forwarding logic allows the pipeline to continue without stalling in the case of back-to-back arithmetic-logic instructions so long as each instruction only requires one clock cycle in the execute stage. However, when an arithmetic-logic instruction immediately following a load instruction needs the data being loaded, the pipeline must stall until the load is complete.

A control hazard is caused by a branch instruction, which modifies the control flow of the program. The problem is that the processor must update the PC in

$<sup>^6</sup>$ More aggressive microarchitectures fetch multiple instructions per clock cycle and execute them out of order. These designs can achieve an IPC greater than one.

<sup>&</sup>lt;sup>7</sup>Other types of data hazards exist but are not relevant for an in-order processor.

<sup>&</sup>lt;sup>8</sup>Note that some literature uses the term *interlocking* to refer to pipeline stalling.

the fetch stage, but the branch address is not determined until the execute stage. Various techniques have been developed to reduce pipeline stalls caused by control hazards, such as delaying the branch decision and predicting the branch outcome early in the pipeline. The latter technique has proven useful in many microarchitectures, while the former actually complicates the design of modern, more aggressive microarchitectures.

In MIPS, the branch decision is delayed one clock cycle with a branch delay slot. In other words, the instruction immediately following the branch in program order is always executed, regardless of the outcome of the branch. To further reduce the effects of control hazards, we use a simple branch predictor to predict the branch outcome in the decode stage and then verify the prediction in the execute stage. If the prediction was incorrect, the instruction that was speculatively fetched is invalidated, and instruction fetch resumes at the correct branch target address. Of course, if the prediction was correct, the processor simply continues execution uninterrupted.

A structural hazard exists when two or more instructions require the same hardware resource in a given clock cycle. In an in-order, pipelined processor such as ours, structural hazards only exist when a hardware resource is needed in two or more pipeline stages. For instance, memory is accessed in the fetch and memory stage. Similarly, the register file is read in the decode stage and written in the write-back stage.

A simple solution to avoid memory structural hazards in a pipelined processor is to store instructions and data in separate memories. This type of architecture, commonly referred to as a Harvard architecture, is in contrast with the Von Neumann architecture. Another solution is to provide multiple ports to the same memory. A memory with two read/write ports is typically called a *dual-port* memory. One disadvantage to such an approach is that the density of the memory goes down as

the number of ports goes up (e.g., a single-port memory requires six transistors per bit, while a dual-port memory requires eight). A third solution is to use separate caches for data and instructions. While many embedded systems use a hybrid of the aforementioned solutions, most computer system today use caches to solve memory structural hazards. Structural hazards caused by the register file are usually avoided with multiple ports. In particular, the register file in our processor has two read ports and one write port.

Figure 2.4: The microarchitecture of a 5-stage pipeline processor

Putting all these concepts together, Figure 2.4 depicts the 5-stage pipelined processor design used in our research. The forwarding paths for avoiding data hazards are highlighted in green, while the signals for stalling and invalidating (i.e., flushing) instructions are highlighted in red. The control signals that flow through the

pipeline are colored blue and all other components of the datapath are colored black. Note that the term *datapath* describes the data buses, registers, and arithmetic-logic components within the microarchitecture.

For asymmetric cryptography, the width of the datapath (*i.e.*, the word width), specified by the ISA, can have a significant effect on the computational efficiency. As seen in Section 7.9, larger datapaths prove to be beneficial in our accelerator architecture. For MIPS-I and II, the datapath is 32-bits wide, while for MIPS-III and above, the datapath increases to 64-bits. We currently utilize a 32-bit datapath for our processor, but for future work, we would like to investigate the energy benefit of using a 64-bit processor.

As will be discussed in Section 5.3, we investigate the energy impact of an instruction cache in our system. Thus, a brief description of caches is in order. We already mentioned that caches can help eliminate structural hazards due to memory access, but it is interesting to note that caches were developed primarily because the access time of main memory was not keeping up with the speed of the processor. Starting in the 1980s and continuing until about 2005, processor and main memory speed have diverged exponentially [21]. Processor performance has increased drastically due to advances in VLSI and computer architecture. Meanwhile, main memory speed has been growing at a much slower rate as commodity DRAM capacity increases and cost decreases.

To bridge this performance gap, computer architects began placing caches between main memory and the processor. *Cache* is simply smaller, faster memory that leverages the principals of temporal and spacial locality. *Temporal locality* is the observation that when an instruction or data word is accessed in memory, it is very likely to be accessed again in the near future. Similarly, *spacial locality* observes that when a word is accessed in memory, words within close proximity will likely be

accessed as well.

By using faster SRAM technology, rather than slower, more dense DRAM, and keeping the memory small, the access time for a cache can be orders of magnitude less than that of main memory. Initially, processors only had a single level of cache; however as the processor-memory performance gap continued to increase, more levels of cache were added to the memory hierarchy. The access time of the lowest level of cache, L1, must be matched with the speed of the processor, requiring only one or two processor clock cycles. Moving up in the memory hierarchy, each level of cache is larger and slower than the level below it. The goal of a well designed memory hierarchy is to give the programmer the illusion of a single memory that is large but also fast. While a typical computer system today will have up to three levels of cache, many embedded systems only use one level of cache or no cache at all.

The simplest of all cache designs, illustrated in Figure 2.5, is the *direct-mapped* cache. In such a cache, a block of data in main memory maps to only one location in the cache. Because the cache is much smaller than main memory, many blocks in memory will map to the same block in the cache. Consequently, a *tag* must be stored with a given cache block in order to uniquely identify that block in memory. In addition to the tag, other bits must be stored to keep track of the state of each cache block. In our simple architecture, we only need to know if the cache block contains valid data; thus a single *valid bit* is sufficient.

One of the advantages of a direct-mapped cache is simplicity. As shown in Figure 2.5, the word address from the processor is broken up into three components, namely tag, index and block offset. The index is used to select a cache block from the cache. Due to spacial locality, a cache block will usually contain multiple words

<sup>&</sup>lt;sup>9</sup>Modern computer systems use more advanced caching techniques, which lie outside the scope of this work.

Figure 2.5: A direct-mapped cache with a block size of 16 bytes and a 32-bit word width.

(a power of two for hardware simplicity). Thus, the block offset selects a particular word within a cache block. To ensure the cache block referenced by the index is the exact block in memory the processor is addressing, the tag stored in the cache is compared with the tag portion of the address. Also, the valid bit is checked. If the tags match and the valid bit is set, a cache *hit* is detected, and the appropriate word is forwarded to the processor; otherwise, a cache *miss* is detected, causing the cache controller to access the next level in the memory hierarchy. As a miss is being handled, an in-order processor such as ours, must stall, waiting for the correct cache block to be returned from the memory system. This wait time is commonly referred to as the *miss penalty*. More details about the cache design used in this study can

be found in Section 5.3.

# 2.3 Energy Consumption in Digital Circuits

Understanding how energy is consumed in CMOS logic is key to creating energy efficient designs. The general equation for energy is given by

$$Energy = Power * \Delta Time \tag{2.7}$$

such that Power is the average computation power, and  $\Delta Time$  is the time per operation. While  $\Delta Time$  is dependent upon the computation time, Power is dependent upon the CMOS implementation and usage.

CMOS circuits dissipate power in three different ways. First, there is static power dissipation, which can be described by the formula below:

$$P_{static} = V * I_{leak} (2.8)$$

where V is the source voltage and  $I_{leak}$  is source to drain current when the transistor is turned off, referred to as leakage current. The second type of energy consumption is switching power, given by the following formula:

$$P_{switching} = (1/2) * \alpha * C * f * V^2$$

$$(2.9)$$

C is the capacitance the transistors must drive and is made up of wire and gate capacitance. The clock frequency, f, and the switching activity factor,  $\alpha$ , capture the rate at which the transistors switch. The third component of power is short

circuit power and is given by the following formula:

$$P_{short} = V * I_{sc} (2.10)$$

$I_{sc}$  is the short circuit current which exists between the type N and P transistors during a logic state transition [22].

In computing, we can reduce energy per operation by either reducing the power consumed in the computation logic or by reducing the amount of time required per operation. Often, a small increase in power can be traded for a significant reduction in execution time such that there is an overall benefit in energy conservation [23]. Conversely, an increase in execution time might be traded for a significant reduction in power as seen with Dynamic Voltage Frequency Scaling (DVFS) [24].

#### 3. RELATED WORK

Researchers have dedicated much effort to achieving significant acceleration using hardware in FPGA and ASIC designs; however, only a few publications seem to investigate the energy consumption aspect of public-key cryptography for embedded devices. In order for public-key cryptography to be viable in energy-constrained applications, a better understanding of the energy cost associated with asymmetric encryption in both hardware and software is necessary.

Wander et al. compared the energy cost of 1024-bit RSA with that of 160-bit ECC to show that 160-bit ECC significantly reduces energy consumption when executed on an 8-bit Atmel ATmega128L microprocessor [8]. The results provide a very compelling argument for ECC, showing that, based on an assumed battery life, the device using ECC could execute 4.2 times the number of key exchange operations. While their work looked at the energy cost for asymmetric cryptography on the far left side of the range shown in Figure 1.1, our work examines its cost for additional points on the spectrum.

Also on the far left of the spectrum, Potlapally et al. investigated the energy requirements of OpenSSL on an Intel SA-1110 StrongARM processor [13]. To do so, they devised a LabVIEW based testbed that measures, in real-time, the power consumption of a handheld device with the SA-1110 processor. Their experimental results motivate further research by showing that for 1KB data transfers, asymmetric cryptography consumes greater than 90% of the total energy spent on cryptographic processing. This equates to 56% of the total energy expended during the data transfer. Additionally, they show that 163-bit ECC requires less energy than 1024-bit RSA when client authentication is used. Their work is particularly relevant considering

the SA-1110 is comparable in size to the processor evaluated in our study.

Pabbuleti et al. evaluated the energy cost of several public-key authentication schemes based on ECC (ECDSA) and one-time hashes (LD-OTS and W-OTS) [9]. For their experiments, the authors used a CC2500 low-power RF transceiver paired with an MSP430 microcontroller, 256 KB of flash and 16 KB of RAM. To facilitate independent energy measurements, the authors used separate shunt resistors to measure the current independently through the microcontroller and the transceiver. Thus, their evaluation included not only the cost of computing the signature, but also the cost of transmitting the signature. While ECC based protocols require much more energy for computation compared to the hash-based schemes, the hash-based schemes require more energy for transmission because of longer signatures. Unfortunately, the energy cost of computation for ECDSA does not scale well to greater security levels. As a result, 160-bit ECDSA was shown to be more energy efficient at the 80-bit security level compared to LD-OTS and W-OTS, but 256-bit ECDSA was much less efficient at the 128-bit security level.

Keller et al. examined public-key energy consumption for FPGAs [25]. First, the design of an entire asymmetric cryptographic processor is explained. Then, the design is implemented on an Xilinx Spartan 3E FPGA and characterized in terms of energy consumption. The processor is capable of utilizing binary or prime finite-fields. For prime-field mathematics, the authors used 192-bit integers, while for binary-field mathematics, the authors used 163-bit polynomials. For energy consumption characterization, the authors kept the bit lengths the same but made various algorithmic changes. They found that the power consumption of the FPGA remained quite constant throughout their experimentation, and thus, the fastest system configuration was also the most energy efficient. In the design by Keller et al., the field size was fixed at synthesis time, placing it on the far right of the spectrum of Figure 1.1. By

contrast, the prime-field accelerator presented here is run-time configurable for up to 521-bit ECC. Furthermore, our work evaluates the energy cost for ASIC technology as opposed to FPGA logic, which presents a significantly different power-performance profile.

Goodman et al. compared public-key cryptography on a Domain-Specific Reconfigurable Cryptographic Processor (DSRCP) with previously reported FPGA implementations and a software only implementation on a strongARM [26]. The DSRCP was implemented in a 0.25  $\mu$ m process technology, and the energy consumption numbers were true measurements. The authors report orders of magnitude lower energy consumption for the DSRCP compared to software and FPGA implementations. For public-key cryptographic algorithms, reconfigurability of the DSRCP is possible, while the energy consumed by the DSRCP is half that of previously reported non-reconfigurable hardware solutions. Because the DSRCP can only perform public-key encryption, it lies on the right side of the diagram in Figure 1.1. Our work investigates more reconfigurable points to the left on the diagram.

Wenger et al. compared 192-bit prime- and 191-bit binary-field implementations of ECC in terms of energy consumption on a custom cryptographic processor[27]. Their results show that binary-field computation provides a 2.82 factor improvement in energy efficiency for an ECDSA signature. Specifically, their custom processor, "Neptun," requires only 19.53  $\mu J$  for a 191-bit binary-field signature compared to 55.10  $\mu J$  for a 192-bit prime-field signature. Results were reported assuming a 1 MHz clock rate and a low-power 130 nm technology node. Even though each architecture was tuned for a particular field, the difference in power consumption between the two is insignificant. Thus, the majority of the energy savings due to binary-field support comes from a reduction in execution time. The authors attribute fast field squaring and a 50% reduction in the number of field multiplications as the primary

benefits of binary-fields. For an ECDSA verification, however, binary-field computation only provides a 1.49 factor improvement in energy efficiency because the twin multiplication algorithm for verification is not as efficient for binary-fields. As with the DSRCP by Goodman *et al.*, the Neptun processor is designed specifically for ECC but maintains a certain degree of reconfigurability. Our work not only investigates more reconfigurable architectures but also covers a larger portion of the design space by evaluating greater security levels.

For symmetric encryption, Wu et al. show a 2.25x performance improvement over pure SW with CryptoManiac, which requires  $1/100^{th}$  of the area of an Alpha 21264. Although the authors did not investigate energy, we acknowledge that this design would yield a significant reduction in energy per symmetric cryptographic operation. It should be noted that this work is complementary to ours because symmetric and asymmetric cryptography are used cooperatively.

#### 4. ALGORITHMS AND SOFTWARE

#### 4.1 ECDSA

In this study, we examine the energy cost for the Elliptic Curve Digital Signature Algorithm (ECDSA), which is a variant of the Digital Signature Algorithm (DSA) that utilizes elliptic curve scalar point multiplication in place of modular exponentiation [10]. We chose ECDSA as our benchmark because it is a standardized elliptic curve-based algorithm found in many protocol implementations, including OpenSSL [18]. Figure 4.1 depicts the computational hierarchy of ECDSA with finite-field arithmetic at the foundation.

Figure 4.1: Elliptic Curve Digital Signature Algorithm computation hierarchy

Finite-field arithmetic is essentially addition, subtraction, multiplication, and inversion on a finite set of elements. In terms of clock cycles per operation, field inversion is the most costly, with multiplication coming in second. The number of field inversions required is kept to a minimum, however, making multiplication the most costly operation overall. Significantly, when we accelerate ECC, the finite-field

arithmetic is the portion of the algorithm that gets mapped into hardware, while the rest remains in software and is consequently reconfigurable.

Next in the computational hierarchy are the point addition and doubling algorithms that perform mathematical operations on an elliptic curve over a finite field. The underlying field can be either prime -GF(p) or binary  $-GF(2^m)$  both of which are endorsed by the National Institute of Standards and Technology (NIST). Mathematically speaking, the point double and add operations constitute an Abelian group with the points on the curve and a point at infinity (i.e., the identify element). Although an elliptic curve is described in two dimensions with the Weierstraß equation, practical implementations use a three-dimensional coordinate system to avoid costly field inversions. For our GF(p) implementations, we use mixed Jacobian-Affine coordinates, while for  $GF(2^m)$ , we use mixed Lopez-Dahab-Affine. These coordinate systems are optimal in that they require the least amount of field operations for their respective curves [16].

Continuing up the hierarchy, we have the scalar point multiplication algorithms. ECDSA defines an operation for signing a message and another operation for verifying the signature of a message. Our study examines the energy cost of both in order to understand the cost of an SSL handshake. An ECDSA signature requires a single scalar point multiplication (X = kP), while a verification requires a twin scalar point multiplication  $(X = u_1P + u_2Q)$ . For a single scalar point multiplication, we use a sliding-window algorithm that uses two pre-computed points (3P) and takes advantage of the fact that point subtraction is only marginally more costly than addition. For the twin scalar point multiplication, we use an algorithm that pre-computes P - Q and P + Q and then simultaneously scans both multipliers  $(u_1)$  and  $u_2$ . In such a case, the cost of a twin scalar point multiplication is less than two single scalar point multiplication [28]. We evaluated Montgomery scalar point

multiplication for use with our binary-field coprocessor but found the algorithm to be more costly in terms of performance and energy compared to the sliding-window algorithm [17].

Encompassed within ECDSA is also arithmetic performed modulo the order of the base point of the specified curve and is done in addition to the scalar point multiplications to complete either a signature or a verification operation. For most implementations, the scalar point multiplication constitutes the majority of the ECDSA computation, but as will be shown later, this is not always the case with hardware acceleration. For inversion modulo the group order, we implement the extended Euclidean algorithm on Pete for all hardware/software configurations.

# 4.2 Multi-precision Routines

Because asymmetric cryptography involves computation on integers typically much larger than the word width of the machine with which they are computed, multi-precision routines are necessary to perform the finite-field arithmetic essential for ECDSA. With multi-precision computation, large integers are stored in memory as arrays of w-bit words, where w is the width of the computational datapath. Multi-precision computation then proceeds one word at time. For the architectures evaluated in this study, w = 32. The size of the array necessary to store an n-bit integer is given by  $k = \lceil n/w \rceil$ . The computational complexity for the multi-precision addition routines are O(k). In other words, the addition algorithm run time is linearly related to the number of words required to represent the field. For multiplication, the computational complexity is  $O(k^2)$ .

Of the multi-precision routines, inversion and multiplication have the highest computational complexities; however, software acceleration techniques, such as the use of three-dimensional coordinate systems, reduce the number of required inversions [29]. In terms of energy, multiplication is the most costly multi-precision routine. Therefore, we will begin by briefly reviewing the specific multi-precision multiplication algorithms used in this study. Because we evaluated the use of prime and binary fields, our discussion will include both types of computation. For a more in-depth coverage of the material presented in this section, consult Hankerson et al. [16].

```

Algorithm 2 Operand scanning multiplication [30]

```

```

Input: A = (a_{k-1}, ..., a_1, a_0), B = (b_{k-1}, ..., b_1, b_0)

Output: P = A * B = (p_{2k-1}, ..., p_1, p_0)

1: P \leftarrow 0

2: for i from 0 to k-1 do

u \leftarrow 0

3:

for j from 0 to k-1 do

4:

(u,v) \leftarrow a_j * b_i + p_{i+j} + u

5:

p_{i+j} \leftarrow v

6:

end for

7:

p_{i+k} \leftarrow u

9: end for

```

# 4.2.1 Prime Field Multiplication

Prime-field multiplication requires a multi-precision integer multiplication followed by a reduction operation to map the multiplication result back into the finite field. Multi-precision integer multiplication can be broadly divided into two categories: product scanning and operand scanning. Operand scanning, described in Algorithm 2, is the traditional "school-book" technique, also known as "pencil-andpaper" multiplication. When implemented in software, operand scanning requires a nested for-loop with the inner-loop iterating over the multiplicand and the outerloop iterating over the multiplier. Within the inner-loop, the primary arithmetic computation is given by