# ENERGY EFFICIENCY AND PERFORMANCE IN MULTIPROCESSORS SYSTEMS ON CHIP

# A Dissertation

by

# DAVID KADJO

# Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

| Chair of Committee, | Paul V. Gratz       |

|---------------------|---------------------|

| Committee Members,  | Jiang Hu            |

|                     | Rusty H. Harris     |

|                     | Vivek Sarin         |

| Head of Department, | Miroslav M. Begovic |

May 2015

Major Subject: Computer Engineering

Copyright 2015 David Kadjo

#### ABSTRACT

As process technology shrinks, the transistor count on CPUs has increased. The breakdown of Dennard scaling has led to diminishing returns in terms of performance per power. A trend which promises to impact future CPU designs. This breakdown is due in part to the increase in transistor leakage driven static power. We, now, have constrained energy and power budgets. Thus, energy consumption has to be justified by an increased in performance. Simultaneously, architects have shifted to chip multiprocessors(CMPs) designs with large shared last level cache(LLC) to mitigate the cost of long latency off-chip memory access. A primary reason for that shift is the power efficiency of CMPs. Additionally, technology scaling has allowed the integration of platform components on the chip; a design referred to as multiprocessors system on chip(MpSoC). This integration improves the system performance as the communication latency between the components is reduced.

Memory subsystems are essential to CPUs performance. Larger caches provide the CPU faster access to a larger data set. Consequently, the size of last level caches have increased to become a significant leakage power dissipation source. We propose a technique to facilitate power gating a partition of the LLC by migrating the high temporal blocks to a live partition; Thus reducing the performance impact. Given the high latency of memory subsystems, prefetching improves CPU performance by speculating future memory accesses and requesting the data ahead of the demand. In the context of CMPs running multiple concurrent processes, prefetching accuracy is critical to prevent cache pollution effects. Furthermore, given the current constraint energy environment, there is a need for lightweight prefetchers with high accuracy. To this end, we present *BFetch* a lightweight and accurate prefetcher driven by control flow predictions and effective address speculation.

MpSoCs have mostly been used in mobile devices. The energy constraint is more pronounced in MpSoCs-based, battery powered mobile devices. The need to address the energy consumption in MpSoCs is further accentuated by the proliferation of mobile devices. This dissertation presents a framework to optimize the energy in MpSoCs. The proposed framework minimizes the energy consumption while meeting performance and power budgets constraints. We first apply this framework to the CPU then extend it to accommodate the GPU.

#### ACKNOWLEDGEMENTS

I would like to thank Dr. Paul V. Gratz for the opportunity to participate in research with the Computer Architecture, Memory Systems and Interconnection Networks(CAMSIN) research group. His advice and counsel have guided me through my academic journey at Texas A&M University.

I would also like to express my gratitude to my advisory committee members: Dr. Jiang Hu, Dr. Vivek Sarin and Dr. Rusty Harris for their invaluable feedback. Also, thanks to Dr. Daniel A. Jimenez for his constructive assessments during part of this work.

Special thanks to my colleagues of the CAMSIN and TACO(Texas Architecture and Compiler Optimization) research groups for the good and fun times. The enjoyable hangouts helped alleviate the journey through the PhD program.

Thanks to Intel Corporation, the College of Engineering at Texas A&M University and the National GEM Consortium for their financial support in the form of a Doctoral Fellowship.

I would also like to thank my family for their support throughout all these years. Millions of thanks to my fiancee Brianna Ford. Her support through the past few years has been incommensurable.

Finally, I would like to thank God for his blessings and guidance. I, certainly, will not be at this stage of my life without his support.

DAVID KADJO

iv

# TABLE OF CONTENTS

|                                 | Page                                                                                                                                                                                                                   |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABST                            | RACT                                                                                                                                                                                                                   |

| ACKN                            | IOWLEDGEMENTS                                                                                                                                                                                                          |

| TABL                            | E OF CONTENTS                                                                                                                                                                                                          |

| LIST (                          | OF FIGURES                                                                                                                                                                                                             |

| LIST (                          | OF TABLES                                                                                                                                                                                                              |

| 1. IN'                          | TRODUCTION                                                                                                                                                                                                             |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | 1.1.1Last Level Cache Static Power Reduction21.1.2Branch Prediction Directed Prefetching3Platform Level Energy Optimization71.2.1A CPU Approach71.2.2A CPU-GPU Approach9Thesis Statement10Dissertation Contributions11 |

| 2. LA                           | ST LEVEL CACHE POWER REDUCTION                                                                                                                                                                                         |

| 2.1<br>2.2<br>2.3               | Design162.2.1Cache Size Estimation172.2.2Cache Resizing182.2.3Hardware Implementation23                                                                                                                                |

| 2.4                             |                                                                                                                                                                                                                        |

| 3. BF                           | ETCH FOR CHIP MULTIPROCESSORS                                                                                                                                                                                          |

|    | 3.1 | Background                                                                                     |

|----|-----|------------------------------------------------------------------------------------------------|

|    |     | 3.1.1 Overview                                                                                 |

|    |     | 3.1.2 B-Fetch Microarchitecture                                                                |

|    |     | 3.1.3 Hardware Cost                                                                            |

|    | 3.2 | BFetch                                                                                         |

|    |     | $3.2.1$ Methodology $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 49$ |

|    |     | 3.2.2 Results and Analysis                                                                     |

|    |     | 3.2.3 Sensitivity Analysis                                                                     |

|    | 3.3 | Summary                                                                                        |

| 4. | PLA | TFORM POWER MANAGEMENT                                                                         |

|    | 4.1 | A CPU Power Management                                                                         |

|    |     | 4.1.1 Overview                                                                                 |

|    |     | 4.1.2 Power Models                                                                             |

|    |     | 4.1.3 Power Controller Implementation                                                          |

|    |     | 4.1.4 QoS Controller                                                                           |

|    | 4.2 | CPU-GPU Power Management                                                                       |

|    |     | 4.2.1 Overview                                                                                 |

|    |     | 4.2.2 Frequency Scalability                                                                    |

|    |     | 4.2.3 CPU-GPU-Display Queuing Model                                                            |

|    |     | 4.2.4 State-space Controller Regulating QoS                                                    |

|    |     | 4.2.5 Energy Optimal Frequencies                                                               |

|    |     | 4.2.6 Adding Energy Optimization                                                               |

|    |     | 4.2.7 Implementation                                                                           |

|    | 4.3 | CPU Optimization                                                                               |

|    |     | 4.3.1 Methodology                                                                              |

|    |     | 4.3.2 Results and Analysis                                                                     |

|    |     | 4.3.3 Performance                                                                              |

|    |     | 4.3.4 Power Budgeting                                                                          |

|    | 4.4 | CPU-GPU Optimization                                                                           |

|    |     | 4.4.1 Methodology                                                                              |

|    |     | 4.4.2 Results and Analysis                                                                     |

|    | 4.5 | Summary                                                                                        |

| 5. | PRI | OR WORK                                                                                        |

|    | 5.1 | Cache Power Reduction                                                                          |

|    | 5.2 | Cache Prefetching                                                                              |

|    |     | 5.2.1 Light Weight Prefetchers                                                                 |

|    |     | 5.2.2 Heavy Weight Prefetchers                                                                 |

|    |     | 5.2.3 Branch Directed and Related Techniques                                                   |

|    | 5.3 | Platform Power Management                                                                      |

|    | 5.3.1   | CPU   | -GPU | Opti | miza | tion | <br> |  | • | <br>• • | • • | • | • | • |  | • | • | 97  |

|----|---------|-------|------|------|------|------|------|--|---|---------|-----|---|---|---|--|---|---|-----|

| 6. | CONCLUS | SIONS |      |      |      |      | <br> |  | • | <br>    | •   | • | • | • |  | • | • | 99  |

| RE | FERENCE | S     |      |      |      |      | <br> |  |   | <br>    |     | • |   |   |  |   |   | 101 |

# LIST OF FIGURES

# FIGURE

# Page

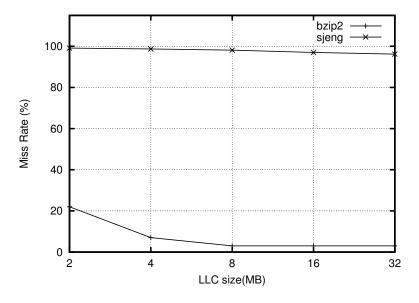

| 1.1  | Last level cache footprints for sjeng and bzip2                                                                           | 4  |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

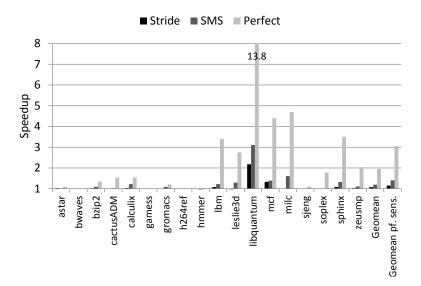

| 1.2  | Speedup comparison between the <i>Stride</i> , <i>SMS</i> , and <i>Perfect</i> Prefetchers.                               | 5  |

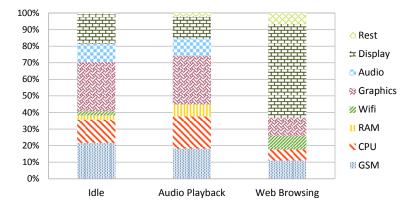

| 1.3  | Power consumption breakdown for a mobile platform under different<br>usage scenarios [8]                                  | 9  |

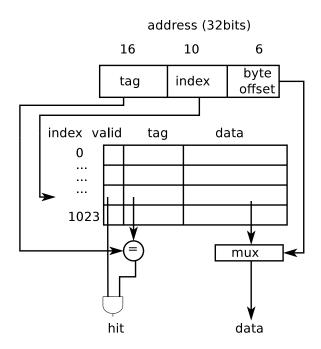

| 2.1  | Accessing a direct mapped cache                                                                                           | 16 |

| 2.2  | High-level block diagram of the set sampler                                                                               | 18 |

| 2.3  | Anatomy of an epoch.                                                                                                      | 19 |

| 2.4  | Shrinking the LLC size.                                                                                                   | 19 |

| 2.5  | Block diagram of temporal locality prediction                                                                             | 21 |

| 2.6  | Conceptual system overview                                                                                                | 24 |

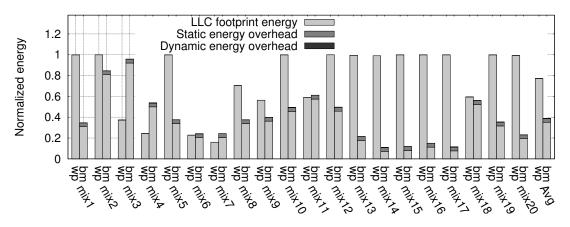

| 2.7  | Energy dissipation for way partitioning "wp" and blocks migration "bm" normalized to the baseline.                        | 27 |

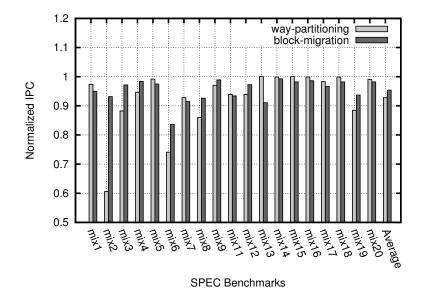

| 2.8  | IPC comparison for blocks migration and way partitioning normalized to the baseline.                                      | 28 |

| 2.9  | Percentage of migrated blocks accessed in the next epoch when the cache is shrunk                                         | 29 |

| 2.10 | Energy dissipation for 2-mix benchmarks using way partitioning "wp" and blocks migrations "bm" normalized to the baseline | 31 |

| 2.11 | IPC for 2-mix benchmarks normalized to the baseline                                                                       | 32 |

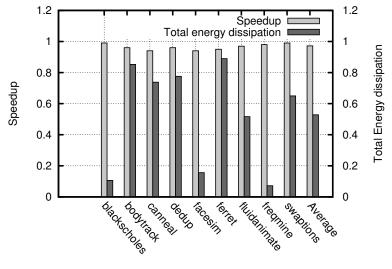

| 2.12 | Speedup over baseline and energy dissipation for multithreaded bench-<br>marks using blocks migrations                    | 33 |

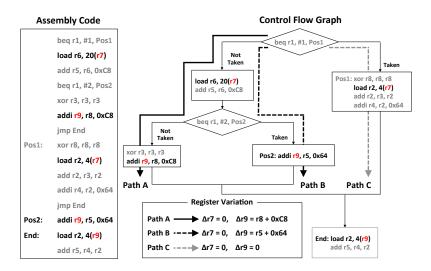

| 3.1  | An assembly code fragment and its control flow graph equivalent                                                           | 36 |

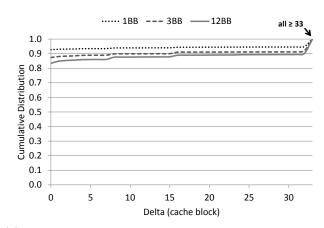

| 3.2  | Cumulative distribution of variation in registers content and effective addresses across execution basic blocks. | 37 |

|------|------------------------------------------------------------------------------------------------------------------|----|

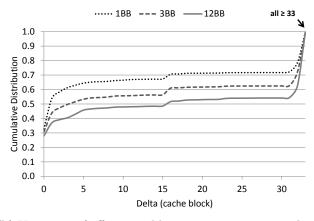

| 3.3  | Overall <i>B-Fetch</i> microarchitecture.                                                                        | 39 |

| 3.4  | Single branch trace cache (BrTC) entry.                                                                          | 40 |

| 3.5  | Single memory history table (MHT) entry                                                                          | 43 |

| 3.6  | An ALPHA assembly fragment with a loop.                                                                          | 44 |

| 3.7  | Consecutive loads off the same source register                                                                   | 46 |

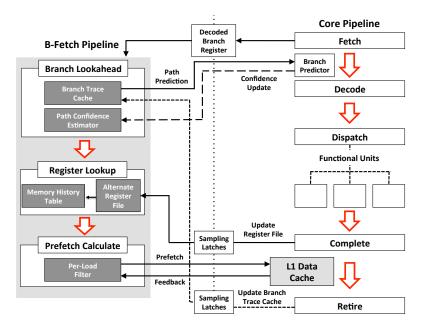

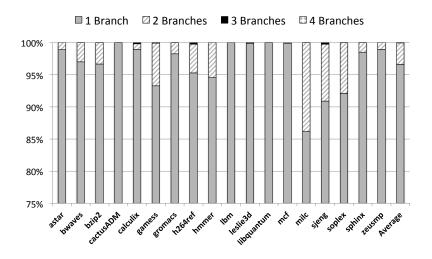

| 3.8  | A breakdown of the number of branch instructions fetched per cycle.                                              | 49 |

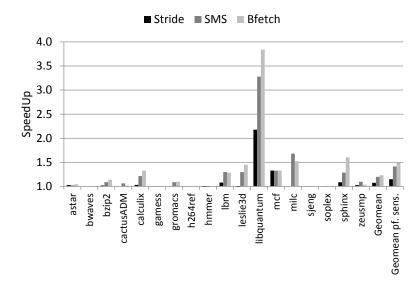

| 3.9  | Single-threaded workload speedups                                                                                | 51 |

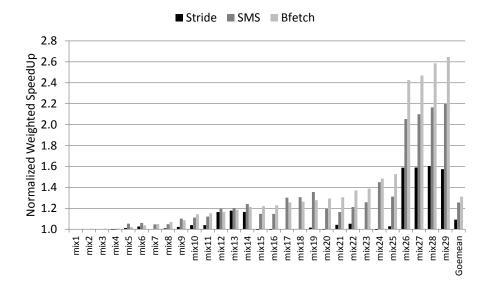

| 3.10 | Normalized weighted speedup for mixes of 2 workloads                                                             | 52 |

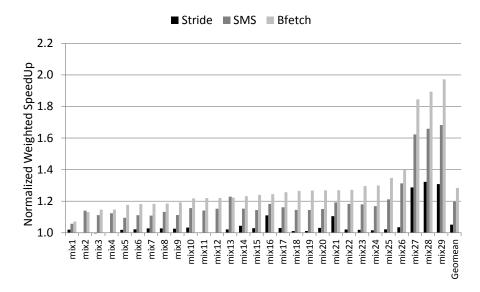

| 3.11 | Normalized weighted speedup for mixes of 4 workloads                                                             | 53 |

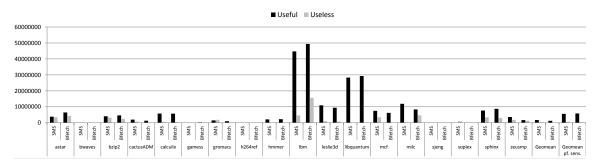

| 3.12 | Number of useful and useless prefetches issued                                                                   | 53 |

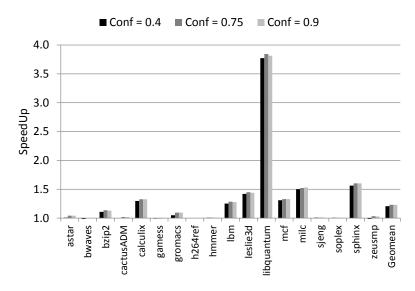

| 3.13 | Branch confidence sensitivity.                                                                                   | 54 |

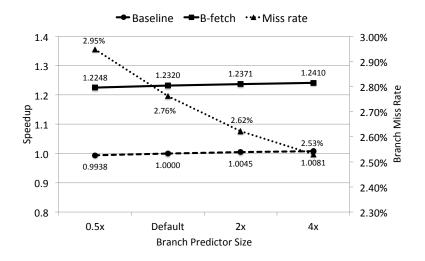

| 3.14 | Branch predictor size sensitivity                                                                                | 55 |

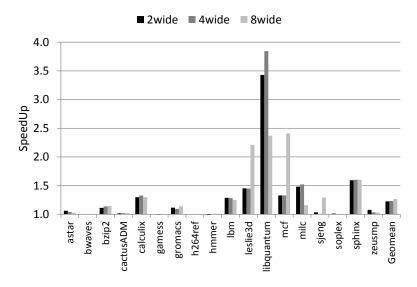

| 3.15 | CPU pipeline width sensitivity.                                                                                  | 56 |

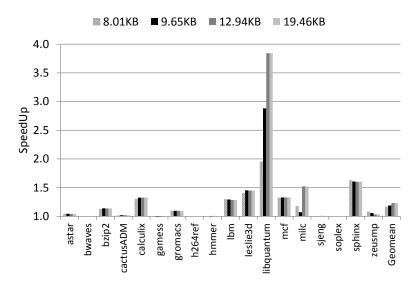

| 3.16 | <i>B</i> - <i>Fetch</i> storage sensitivity                                                                      | 57 |

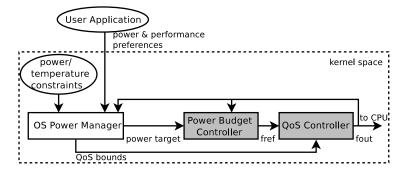

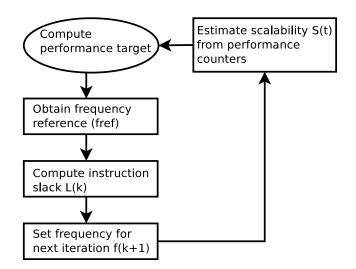

| 4.1  | Overview of the proposed system (added implementation in shaded blocks)                                          | 59 |

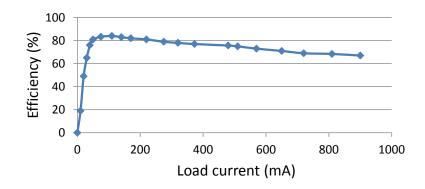

| 4.2  | PMIC efficiency [27]                                                                                             | 61 |

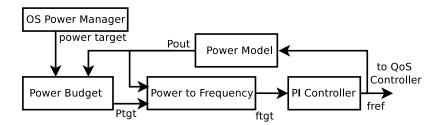

| 4.3  | Design of the power budget controller.                                                                           | 62 |

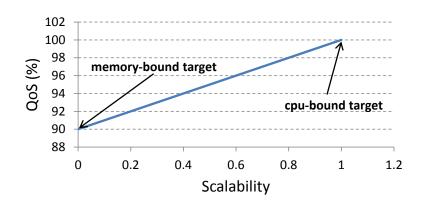

| 4.4  | QoS as a function of the scalability factor.                                                                     | 65 |

| 4.5  | Design of the QoS controller                                                                                     | 66 |

| 4.6  | Closed system control overview                                                                                   | 68 |

| 4.7  | CPU-GPU-Display queuing system                                                                                   | 71 |

| 4.8  | Implementation overview.                                                                                         | 77 |

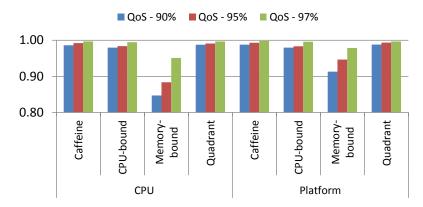

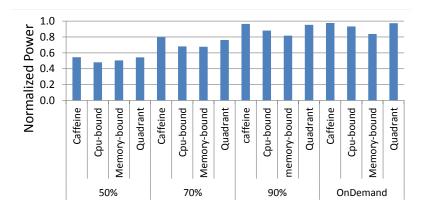

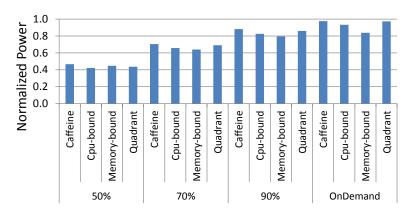

| 4.9  | Energy consumption normalized to the ondemand frequency governor.                     | 80 |

|------|---------------------------------------------------------------------------------------|----|

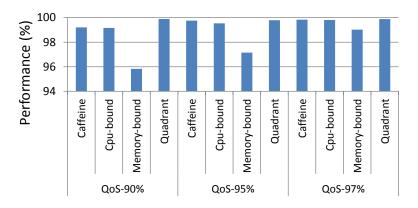

| 4.10 | Application performance relative to max performance                                   | 80 |

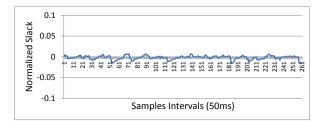

| 4.11 | QoS controller behavior for the $cpu$ -bound workload                                 | 81 |

| 4.12 | Normalized CPU power for the mode that maintains the power at around the target power | 83 |

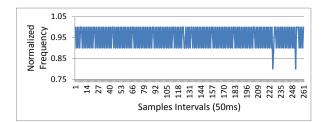

| 4.13 | Normalized CPU power for the mode that maintains the power below target power.        | 85 |

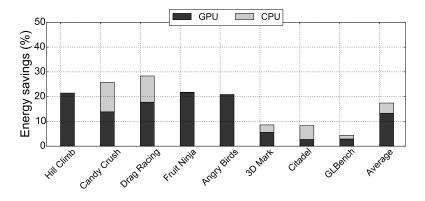

| 4.14 | Energy saving per-frame                                                               | 85 |

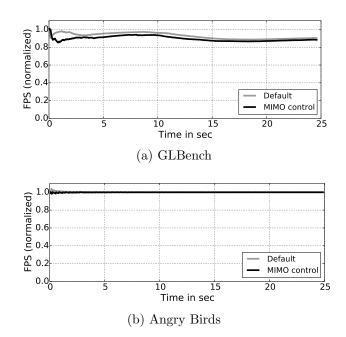

| 4.15 | Frame-rate over time normalized to the target rate                                    | 86 |

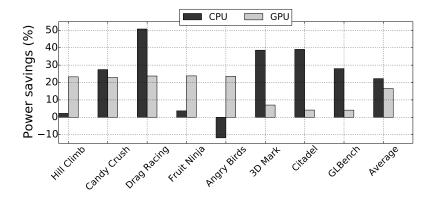

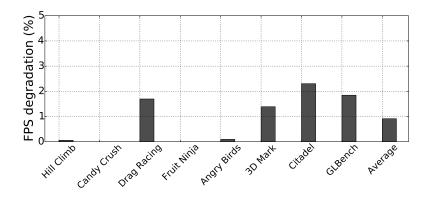

| 4.16 | CPU and GPU power savings                                                             | 87 |

| 4.17 | Performance overhead.                                                                 | 88 |

# LIST OF TABLES

| TABL | Ε                                              | Page |

|------|------------------------------------------------|------|

| 2.1  | Hardware storage overhead.                     | 24   |

| 2.2  | System configuration.                          | 25   |

| 2.3  | Dynamic energy cost of the hardware structures | 26   |

| 2.4  | Cache size estimation error.                   | 30   |

| 3.1  | Hardware storage overhead in KB.               | 48   |

| 4.1  | Baseline configuration.                        | 84   |

#### 1. INTRODUCTION

Power management has become a critical issue for current and future chipmultiprocessors(CMPs), as Moore's law continues providing increasing transistor count. Esmaeilzadeh *et al*, show that a major driver of unusable or dark silicon in future many-core CMPs is increasing leakage power consumption [21]. They also argue that energy consumption must be justified by increased performance to be practical as VLSI scaling continues. Thus, computer architects have focused on building efficient systems. An example of such an efficiency has been the design of better memory subsystems to provide the CPU faster access to larger data sets. To this end, architects have relied on large a memory hierarchy and data prefetching. Given the end of the Dennard scaling, growing cache size comes at an increasing high cost in terms of power/energy consumption. This constraint also impacts the hardware budgets for prefetchers. It becomes necessary to design lightweight prefetchers with high accuracy.

Another example of the drive for more efficient utilization of transistor in computer designs has been the increased integration of platforms components on chip. This integration results in performance improvement due to a reduced communication latencies between components. It also yields better efficiency in terms of power consumption because of the shorter interconnects [39]. Modern MpSoCs consist of many different processing elements (PE) including multiple CPU cores, graphical processing units (GPU), DSP cores and video accelerators. While this rich set of resources enables mobile devices to be used for a wide range of applications, it also elevates the platform power and need for energy efficiency [9, 60, 8, 24].

This dissertation addresses efficiency in MpSoCs through architectural and sys-

tem level approaches. Techniques to increase performance without impacting energy and to reduce energy without impacting performance are proposed.

### 1.1 Microarchitectural Techniques

#### 1.1.1 Last Level Cache Static Power Reduction

The leakage power, to a first order, is linearly proportional to the number of transistors in CMOS circuits. In recent years, architects have dramatically increased the size of the last level cache (LLC), in an attempt to mitigate the large off-chip memory access latencies and bandwidth constraints. Since performance degrades significantly with off-chip memory accesses, the goal in LLC design is to provide enough cache to contain the *worst case* application memory footprint. Thus, the LLC has grown to occupy a large portion of chip die area, as much as 30% in recent Intel CMPs [42]. As such, the leakage power within the LLC has become a significant factor in the overall chip power budget. It is therefore imperative to minimize the leakage consumption within the LLC, without impacting performance. Ideally, one would like the LLC to be minimally sized to application footprint, however, as application footprints vary with application and within an application with program phase, it is impossible to decide at design time the optimum LLC size for all applications at all times. While prior work exists in resizing caches via power gating, it is either overly conservative, leaving energy savings on the table, or imposes a heavy performance burden. We propose a novel LLC power-gating scheme that dramatically reduces energy in the LLC, while leveraging temporal locality aware block migration to mitigate any significant performance impact.

Figure 1.1 illustrates how application footprints vary between applications, it shows the miss rate curve for two applications (bzip2, sjeng) from the SPEC2006 benchmark suite. In the case of bzip2, the miss rate drastically decreases as the

LLC size increases to 8MB, staying constant beyond that point. Thus, its memory footprint can be said to be 8MB. Alternately, *sjeng*'s miss rate is nearly oblivious to the cache size; a 32 MB LLC is not large enough to hold the application memory footprint. A cache of size bigger than an application memory footprint provides little or no performance benefit. Conversely, it dissipates additional energy that affects the overall platform energy as cooling mechanisms are activated to keep the temperature down [4]. When running *bzip2* on a CPU with a LLC size of 32MB, 75% of the cache can be disabled. Because *sjeng*'s miss rate is largely unaffected by the LLC size, nearly all the cache can be disabled.

Previous research ([35, 78, 1]) has proposed methods for reducing the leakage power in caches, however, these methods are not well applicable to LLCs. They require time stamp bookkeeping hardware per cache line, leading to a high hardware overhead due to the low access rate in LLCs. Other methods [58, 2] proposed to shutdown partitions of the cache. These techniques, either do little to reduce the leakage power or have a big performance impact. In general, cache blocks are not ordered by their temporal locality within the sets. Simply shutting down a portion of the cache often leads to performance degradation. The performance impact results from increased LLC misses due to locality lost in the partition being shutdown, exacerbated by the bursts of traffic on the memory bus as the dirty blocks from the partition being shutdown are written back to the main memory.

### 1.1.2 Branch Prediction Directed Prefetching

The current energy constrained environment also impacts hardware budgets for prefetchers. Moreover, in the context of CMPs running multiple concurrent processes, prefetching accuracy is critical to prevent cache pollution effects [20, 73]. Thus, there is a clear need for a light-weight prefetcher with very high accuracy.

Figure 1.1: Last level cache footprints for sjeng and bzip2.

In this work we present a novel, high-accuracy, low-overhead prefetcher for use in chip multiprocessor designs with shared, last-level caches (LLCs). This prefetcher leverages control-flow speculation, together with effective address value speculation to efficiently provide an accurately predicted stream of future memory references.

Prefetching is a well known and deeply studied technique in which a hardware mechanism attempts to fill the cache with useful data ahead of the actual demand load request stream coming from the processor. In effect, a perfect prefetcher could make all memory accesses complete as if they were first level cache hits. Figure 1.2 shows the speedup that might be achieved under such a *Perfect* L1 D-cache prefetcher normalized against the same system without prefetching for a set of SPEC CPU2006 benchmarks. The *Perfect* prefetcher achieves a geometric mean speedup of  $\sim 2X$ versus no prefetching. For comparison, we also show two other current, light-weight prefetchers, *Stride* [14] and *SMS* [63]. We see that while these prefetchers can provide a significant performance gain, there is room for improvement. We note that in

Figure 1.2: Speedup comparison between the *Stride*, *SMS*, and *Perfect* Prefetchers.

the figure, several benchmarks see no gain from the perfect prefetcher, these benchmarks are largely L1 cache resident. To focus on the benefit that can be provided with prefetching, we also show the mean across these *prefetch sensitive* benchmarks, denoted as *geomean pf. sens.*.

Many data prefetching techniques have been proposed over the years, however, most existing prefetchers predict future accesses based on current cache misses. For example, sequential prefetchers prefetch the lines sequentially following the current miss [61], stride prefetchers prefetch lines that exhibit a strided pattern with respect to the current miss [14], and region-based prefetchers prefetch a set of blocks around the miss [63]. These techniques are light-weight, energy-efficient and work well for regular memory accesses, however, they tend to be inaccurate for applications with irregular access patterns. More recent prefetchers attempt to address prefetch accuracy for irregular access patterns [62, 31]. While these methods show significantly improved accuracy, they come at a very high cost in storage overhead, either requiring huge structures to record the memory access patterns or the reservation of large amount of off-chip memory for meta-data storage (and the associated, energy consuming shuttling of large meta-data information on and off chip). Under modern constraints on energy and power consumption, it is critical to design efficient, low-overhead prefetching techniques which can address irregular access patterns.

To improve both efficiency and accuracy, we propose to use control flow speculation to feed a prefetch engine. Control flow, *i.e.*, which basic block of instructions is executed and in what sequence, is determined by the direction of branch instructions contained in the path. Each basic block contains a particular set of loads and stores; so, branch instructions directly determine the access patterns of data and can be used to inform a suitable prefetcher. A challenge with this approach is to determine the effective address of a speculative future load given that the register values it is based on are likely to change before the corresponding memory instruction is executed. Our approach builds on the fact register content varies in a predictable manner across a set of basic blocks, even in the case of irregular control flow. Thus it is possible to stitch together the expected transformations of a register across a sequence of predicted basic blocks leading to a given future load instruction. The effective address of that load can then be predicted accurately based on the current architectural state of the register and those predicted transformations. Unlike prior light-weight prefetchers based on current cache misses, this approach has the added advantage that prefetches can be issued for future loads without waiting for an actual miss to occur. Unlike techniques which speculatively continue execution beyond long latency loads [19, 51], our approach is extremely light-weight, with only a small prefetch engine active during operation, rather than the entire core.

#### 1.2 Platform Level Energy Optimization

As mobile platforms have become mainstream, the computational demands on these devices have reached unprecedented levels. Besides a powerful multiprocessor system-on-chip (MpSoC), mobile platforms host major hardware components such as touch screen displays, modems, cameras and GPS modules. The diversity of hardware resources and applications running on mobile devices results in a large variation in the power consumption profile across different usage scenarios, as illustrated in Figure 1.3.

## 1.2.1 A CPU Approach

Recent empirical data indicates that the CPU no longer dominates the platform power consumption [8, 60]. The major contributors to the power consumption under a typical use case are the CPU, the display, and the power management IC (PMIC) with 30%, 33% and 25% share, respectively [8]. Hence, platform level resource management is necessary to optimize the overall energy consumption. Furthermore, accurate modeling and optimization of platform components is needed due to the nontrivial relation between performance and energy consumption [74, 5, 72, 6, 17, 76].

Traditionally, CPU cores have been the major focus of power management research. Idle power management [49, 3] and dynamic voltage and frequency scaling (DVFS) has been extensively used to minimize power [44, 5, 17, 36, 18]. However, current DVFS policies used in mobile platforms are based on those designed for CPU centric desktops which are not efficient for system level optimization [52]. As a motivational example, we ran a memory intensive workload on a smartphone with Intel<sup>©</sup> Atom<sup>TM</sup> Clovertrail SoC. Reducing the CPU frequency from 2GHz to 1.2GHz results in 12% reduction in total platform power while merely increasing the execution time from 44.10 sec to 45.78 sec. Despite this increase in run-time, our measurements show a platform energy consumption reduction of 9%, which obviously translates to a longer battery life. However, when executing the same workload, the default Android on-demand frequency governor [52], which sets the frequency based on the CPU utilization, maintains the CPU at 2GHz. In other words, this policy fails to detect the poor CPU usage due to the frequent cache misses.

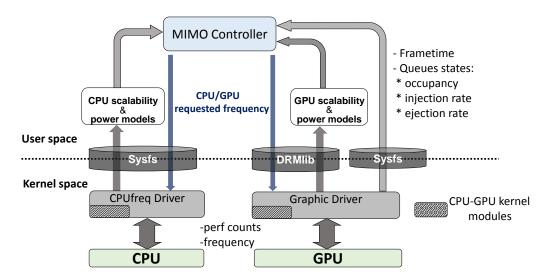

True platform-level power management is possible only when all the platform resources and PEs in the MpSoCs provide hardware support for different sleep and performance states, and these states are exposed to the OS [30]. To date, the CPU cores provide by far the richest set of power states and control knobs exposed at the OS-level. On the other hand, there are very limited number of options to change power states of the other resources such as, GPU and memory at the OS-level. Therefore, we present a general architecture for platform-level power management, but practically illustrate it by focusing on CPU, display and PMIC. We specifically model the impact of PMIC which supplies power to all the components in the platform [27]. Accounting for PMIC efficiency is important since the power dissipated in the PMIC due to DC to DC converters and voltage regulators affect the total platform power.

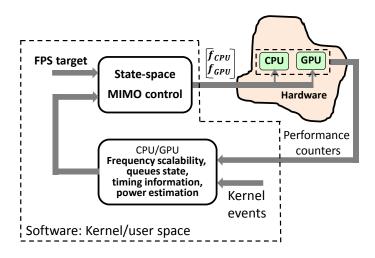

Multiprocessors systems on chip (MpSoCs) for mobile platforms typically contain integrated CPU-GPU cores to provide a better 3D graphic experience. On these platforms, 3D graphic applications are among the most commonly used applications. Therefore, energy optimization for such applications is important. We extend our framework to optimize the energy savings in 3D graphics applications while meetings performance requirements.

Figure 1.3: Power consumption breakdown for a mobile platform under different usage scenarios [8].

## 1.2.2 A CPU-GPU Approach

In typical graphic applications, the GPU works in tandem with the CPU; with the CPU generating tasks for the GPU to produce frames for the display. The target Frame Per Second (FPS) is usually constrained (e.g. 60 FPS). At the same time, applications usually vary in terms of their need for the CPU and GPU computational resources to meet the target FPS. This indicates that running the CPU and GPU at their maximum frequency always may unnecessarily burn significant energy for workloads that do not require aggressive resources to achieve the target FPS. On the other hand, running the CPU and GPU at their minimum frequency may not be sufficient to meet the target FPS. Hence, any energy optimization work geared towards graphic applications needs to correctly understand and model the interaction between the CPU and GPU and set their frequency intelligently to meet the desired Quality of Service target (QoS) while burning minimal energy.

Prior techniques for power management on CPU-GPU heterogeneous systems have mostly focused on discrete GPU cards for high performance computing (HPC) [67, 41, 15]. These techniques exploit the partitioning of workloads into tasks and subsequently mapping them onto either the CPU or the GPU. Pathania *et al.*, recently, proposed a technique to reduce the energy in mobile 3D gaming [53]. Their method, however, relies on an heuristic technique based upon an offline analysis, that determines the CPU-GPU frequencies combinations that generate the desired QoS.

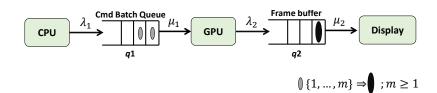

We propose a technique that models the interaction between the CPU and GPU as queuing systems. The CPU generates requests for work and insert them into a request queue. The GPU, then, ejects the requests from the queue and executes the commands that build up the frames. A request, generally, contains all the rendering commands for the GPU. The frames are, then, inserted into a frame queue and sampled by the display controller. The CPU frequency determines the injection rate into the request queue. While, the GPU frequency controls the ejection rate from the request queue and the injection rate into the frame queue. Thus, achieving a target FPS requires the synchronized control of both the GPU and CPU frequencies. This synchronization maintains a certain occupancy in the queues. A detailed illustration of the CPU-GPU interaction is presented in Section 4.2.3. Furthermore, we build run-time power and performance models of both the CPU and GPU based upon the information collected by the hardware performance counters. These counters provide insight into the compute engines' behavior. The power models allow the runtime estimation of the power consumption for the purpose of energy optimization, while the performance models allow estimation of the frequency scalability.

### 1.3 Thesis Statement

This dissertation explores techniques to reduce the efficiency of modern MpSoCs. These techniques can be broken into two basic components. First, we examined micro-architectural technique; We then look at techniques in platform power management to improve efficiency and performance.

#### 1.4 Dissertation Contributions

This dissertation makes the following contributions:

Last Level Cache Static Power Reduction: We propose a novel method that migrates the high temporal locality blocks, data and tag, to the future live partition; thus mitigating the performance impact of oblivious cache bank shutdown via power gating. Our contribution is as follows:

- We migrate, at random, the high temporal locality blocks from the partition to be shutdown to the future live partition, the size of which is estimated based on the application reuse behavior. The migration is done during a transitional period and the blocks locality are computed through a predictor.

- We, further, develop a cache management policy to increase the cache efficiency. This management policy pseudo-partitions the cache with the high locality blocks residing in the future live partition and the low locality blocks in the partition being shutdown. Thus facilitating the cache resizing via power gating.

Our proposed method is independent of the underlying LLC replacement policy. We show that our approach of intelligent block migration provides significant performance improvement when compared to no blocks migration. We found the LLC leakage power to be of orders of magnitude greater than that of the on-die interconnect therefore the LLC leakage is the focus of our work. We evaluate our technique on sets of PARSEC and SPEC2006 benchmarks.

**Branch Directed Prefetching:** We propose *B-Fetch*, a combined control-flow and effective address speculating prefetching scheme. *B-Fetch* leverages the high prediction accuracy of current-generation branch predictors, combined with a novel effective address speculation technique to identify prefetch candidates.

- We demonstrate that future memory instruction effective addresses are predictable based on a speculative control flow path from a simple branch predictor. This speculative control flow path is used to feed our *B*-*Fetch* prefetch engine.

- We propose an effective address value speculation technique based on the current architectural state with learned, per-basic-block variations, to generate effective addresses for the *B-Fetch* prefetch engine.

- We introduce a per-load filtering mechanism to reduce the cache pollution. This technique builds up a confidence estimation for load instructions to determine whether a prefetch candidate is useful or not.

- We show that *B-Fetch* outperforms the best-in-class light-weight prefetcher, Spatial Memory Streaming (*SMS*) [63] by 3.5% for single-threaded workloads (8.5% among prefetch sensitive), and up to 8.9% for multi-application workloads, with 65% less storage overhead than *SMS*.

We evaluate our technique on a set of SPEC CPU2006 benchmarks for both single threaded and multiprogrammed workloads and show performance improvement versus baseline.

**Platform Level Power Management:** We present a general platform power management framework that minimizes the energy consumption while meeting performance and power budgets constraints. We illustrates it using two concrete DVFS algorithms. The first one minimizes the CPU and platform energy while achieving performance guarantees. The performance target is set by a user level application, and expressed as a fraction of the maximum achievable performance which is measured in the number of instructions executed per sampled period. The second one dynamically, adjusts the CPU and GPU frequencies to maintain queue reference occupancy and achieve a QoS target while optimizing for the energy. Both techniques account for the PMIC's energy inefficiency and provide a closed loop control by comparing the achieved power and performance against a reference target. The contributions are as follows:

- We develop closed loop controllers that maximize performance with a power constraint and minimize power with a performance constraint, respectively.

- We develop analytical models to predict power consumption and performance at run-time and use them in closed loop controllers.

- We present a queuing model to represent the interaction between the CPU, GPU, and the display.

We implemented the proposed approaches on an Android mobile tablet based on a Atom processor and show platform energy savings over a series of workloads.

#### 1.5 Dissertation Organization

This dissertation is organized as follows. Chapter 2 presents our technique to reduce the power consumption of the last level cache in CMPs. A data prefetcher to increase the performance of CMPs is proposed in Chapter 3. Chapter 4 presents our approach to increase the platform energy efficiency and performance. the background in memory subsystems and their effect on CPU performance. Chapter 5 reviews previous techniques in cache power reduction and prefetching. It, also, reviews prior work dedicated to energy optimization in SoCs. Finally, chapter 6 concludes our dissertation.

#### 2. LAST LEVEL CACHE POWER REDUCTION\*

This chapter presents our method to reduce the leakage power in last level cache for CMPs.\*We first introduce a background of cache memories. Then, we outline the design of our proposed design. The evaluation along with the analysis of our results are also presented.

### 2.1 Background

Current memory access latencies are of the order of hundreds of processor cycles. To be effective at masking such high latencies, computer architects have leverage larger caches and data prefetchers.

Caches are SRAM memory structures designed to exploit the locality of reference exhibited in programs. They are the temporal and spatial locality. Temporal locality speculates that a referenced memory address will likely be referenced again in the near future. While the spatial locality states that if a memory address is referenced, nearby memory addresses will likely be referenced in the near future. Caches are designed to contain the application working set. In general, an application miss rate decreases with increasing cache capacity; until a point at which the working set fits within the cache. This is illustrated in Figure 1.1. *Bzip2* miss rate decreases until the cache size is 8MB; then remains constant. At that point, increasing the cache size doesn't affect the application miss rate, hence the performance. Of course this trend is dependent on the application; as we observe that *Sjeng* miss rate is nearly oblivious to the cache size. Ideally, one would want the cache size to fit the

<sup>\*</sup>Part of this chapter is reprinted with permission from *Power Gating with Block Migration in Chip-Multiprocessor Last-Level Caches* by David Kadjo, Hyungjun Kim, Paul V. Gratz, Jiang Hu and Raid Ayoub, 2013, The 31st IEEE International Conference on Computer Design, IEEE Computer Society Washington DC, Copyright [2013] by IEEE Computer Society.

application working set. Caches store lines of data or blocks. A typical size is 64 bytes. The blocks are organized into sets. The number of blocks per set is referred to as the cache associativity. A memory request into the cache is split into *tag*, *index* and *byte offset* (shown in Figure 2.1). The *index* selects the set, the *tag* is checked for match against the selected set and the *block offset* specifies the position of the requested data. A cache hit occurs when a valid block matches the tag of the memory request otherwise it is a cache miss. A cache block also contains addition flags bits to indicate whether the block is "valid" and "dirty". Caches are organized as direct mapped, set associative or fully associative. A direct mapped cache has one block per set (1-way associative); that is a memory address occupies one and only one block. A k-way set associative cache is organized in set of k blocks; a memory address can occupy any of the blocks within the set. A fully associative cache a only one set. As a result, a memory address can occupy any of the blocks.

Given the limited size of the cache, a management policy is used to insure the cache its optimum utilization. A cache management policy can be broken into three policies that are: an insertion policy, a promotion policy and a replacement policy. The insertion policy indicates whether an incoming block is placed within the cache. If so, where it is placed. The promotion policy indicates the status of the hit block. The replacement policy indicates the victim block when an incoming block is placed in the cache. The Least Recently Used (LRU) policy is a common policy used for cache management. The LRU policy maintains a "time stamp" of blocks references within a set. Using the LRU policy, an incoming block is placed within the cache, replacing the block that was accessed the furthest in time. When a hit occurs, the block accessed is promoted to the Most Recently Used (MRU). The least recently used block is selected as a victim block when an incoming block is inserted in the cache.

Figure 2.1: Accessing a direct mapped cache.

Cache misses can be classified into four groups that are compulsory, conflict capacity and coherence misses. Compulsory misses occur due to the cache being empty. Every first reference to a memory location results in a miss. Conflict misses occur when multiple memory locations map to the same blocks. Capacity misses occur due the small capacity of the cache; i.e the application working set is larger than the cache size. Coherence misses occur, mainly in CMP contexts, due to the invalidation based coherence protocol when multiple processors write to the same memory location.

#### 2.2 Design

Our proposed technique monitors the application cache footprint and periodically resizes the LLC accordingly. We outline in the following sections the cache size estimation technique and the cache resizing procedures.

#### 2.2.1 Cache Size Estimation

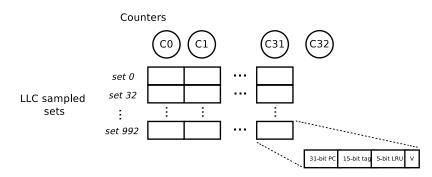

A key problem with dynamically resizing the LLC is quickly identifying the effective cache size for the running application memory footprint. In general, the existence of temporal locality leads to a non-uniform access pattern for the cache's blocks. The LRU (Least Recently Used) algorithm takes advantage of this property to reduce the miss rate. If we construct a histogram that corresponds to the frequency of accessing the different elements in the LRU stack, we observe a monotonic decrease in the frequency distribution where the highest frequency maps to the recently accessed elements. When the cache is underutilized, there is a large variation in the frequency distribution. Hence, the frequency distribution can be used as an indication of the cache utilization by the application [48]. We implement a sampling-based reuse behavior analysis, which decouples from the underlying LLC replacement policy. A set sampler to the LLC is implemented and managed using the LRU replacement policy. This sampler is co-located with the LLC and monitors the LLC traffic to update its sampled tags. The sampler is augmented with counters to keep track of per way hits and total misses as shown in Figure 2.2. These counters allow the construction of the frequency access distribution. A hit to way i causes the corresponding  $lru^{th}$  ranked counter,  $C_{lru}$ , to be incremented, while a miss to the sampler increments the counter  $C_{32}$ . For example, if a block in way 1 is hit and that block is ranked  $7^{th}$  on the LRU stack within its set, the counter  $C_7$  is incremented. Its LRU stack rank is then updated to 0 (Most Recently Used). Equation 2.1 shows the miss rate of a k-way associative partition of the sampler. It is the ratio of the misses to the k-way partition over the total numbers of accesses to the sampler.

$$miss_k = \frac{\sum_{i=k}^{32} C_i}{\sum_{j=0}^{32} C_j} \qquad 1 \le k \le 32$$

(2.1)

Figure 2.2: High-level block diagram of the set sampler.

We empirically determined the set sampling rate to be  $1/32^{th}$  of the LLC as the lowest sampling rate that captures the reuse behavior of the running application with an error less than 10%. As such, the effective cache size can be estimated using the sampler. The sampler associativity is identical to the LLC's. As a result, we estimate the effective cache size for the memory footprint to be the k-way with less than  $\varepsilon$  impact on the miss rate as shown in Equation 2.2.

$$miss_k \le (1+\varepsilon) \times miss_{32} \qquad 0 \le \varepsilon \le 1$$

(2.2)

When multiple programs are running, the sampler evaluates the super set of the applications footprints. Since its primary purpose is to estimate runtime cache footprint, it is unnecessary for the sampler to remain coherent with the actual cache set contents. Furthermore, the sampler has a dual purpose serving as a temporal locality predictor.

#### 2.2.2 Cache Resizing

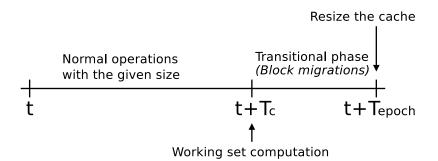

The application execution time is divided into epochs, the anatomy of which is shown in Figure 2.3. Between time t and  $t + T_c$ , the LLC operates using its default replacement policy. At  $t + T_c$ , the effective cache is estimated as per Equation 2.2

Figure 2.3: Anatomy of an epoch.

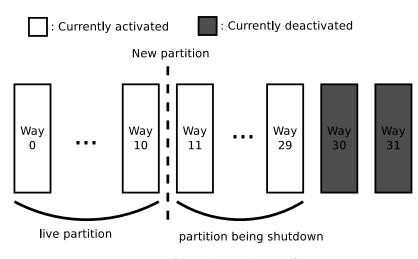

Figure 2.4: Shrinking the LLC size.

using the information gathered by the sampler counters. At time  $t + T_{epoch}$ , the LLC is resized via power-gating. A transitional phase  $(t+T_c, t+T_{epoch})$  is used to mitigate the performance impact of shutting down the LLC partition by migrating the useful data from the partition to be shutdown to the partition which will remain live when the LLC shrinks.

### 2.2.2.1 Temporal Locality Prediction

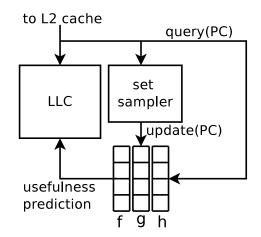

During a cache block's lifetime, it typically sees one or more bursts of accesses, then it is idle until evicted [71]. We implement a trace based predictor, inspired by the work of Khan *et al* [37], to determine the blocks temporal locality. The intuition behind this prediction is that if a sequence of instructions leads to the last access of a cache block, the same sequence on another block will likely have a similar effect on that block. The block diagram of the temporal locality prediction is shown in Figure 2.5. The prediction consists of the sampler and a set of 3 saturating counter arrays or locality counters (f, g and h). Each array consists of 4096 2-bit counters; the arrays are indexed with a different hash function (f(PC), g(PC), h(PC)). A sampler entry encodes the instruction signature (PC) of the instruction that touches a block. When a block is being evicted from the sampler, the indexed counters within the arrays using the corresponding PC are accessed and incremented. Otherwise, the counters are decremented. This phase is referred to as the *update* process. When a request for a block in the LLC is made, the prediction is evaluated and the decision is stored (query process). As such, each block in the LLC is augmented with a bit (*PredictionBit*). This bit is set if the block is predicted not useful and cleared otherwise. The predictor is access in parallel with the LLC, thus it does not incur any performance penalty. We define the *usefulness* of the block as the sum of the indexed counters:

$$U(blk) = f(PC_{blk}) + g(PC_{blk}) + h(PC_{blk})$$

$$(2.3)$$

The usefulness is compared to a threshold  $\tau$  to predict the block temporal locality.

$$blk = \begin{cases} useful & \text{if } U(blk) \ge \tau, \\ not useful & \text{if } U(blk) < \tau \end{cases}$$

(2.4)

A block is predicted useful if its temporal locality is greater or equal to the threshold; otherwise it is predicted not useful. The blocks predicted not useful are

Figure 2.5: Block diagram of temporal locality prediction.

used as victims during the block migration in the transitional phase.

# 2.2.2.2 Procedure and Cache Management

To increase cache efficiency, the amount of time the blocks contain useful data, we develop a cache management policy to be used during the transitional phase. When the LLC size is being reduced (Figure 2.4), the useful blocks from the partition to be shutdown are migrated to the live partition as follows: Upon a hit in the partition to be shutdown; the data is accessed. At the same time, a prediction for the block is made; if the block is predicted to be useful, it is migrated to the live partition, thereby replacing a not useful block (with its *PredictionBit* set). If no such block is found, the victim block is selected using the default cache replacement policy. If the hit block is predicted not useful, its prediction bit is set. On a hit in the live partition, the data is accessed; if the block is predicted to be useful, the prediction bit is set. On a miss, if the incoming block is predicted to be useful it is placed in the live block; otherwise it is placed in the partition to be shutdown, this done as remediation in the case of false negatives. At the end of the transitional phase, the cache is pseudo-partitioned with the high temporal locality blocks mostly

in the live partition and the blocks with low temporal locality in the partition to be shutdown. The cache is then resized at the end of the transitional phase. When the LLC is computed to be expanded, the blocks with the *PredictionBit* set are used as victim blocks to increase the cache efficiency. If no such blocks are found, the default LLC replacement policy is used. The LLC shrinking procedure is outlined in Algorithm 1.

| Algorithm 1: LLC management during the transitional phase when the cache |

|--------------------------------------------------------------------------|

| is being shrunk.                                                         |

| On access to the LLC;                                                    |

| if access is a hit then                                                  |

| Access data;                                                             |

| if hit in live partition then                                            |

| if blk predicted to be not useful then                                   |

| $PredictionBit \leftarrow 1;$                                            |

| end                                                                      |

| else                                                                     |

| if blk predicted to be useful then                                       |

| Migrate blk to live partition, replacing victim blk;                     |

| else                                                                     |

| $PredictionBit \leftarrow 1;$                                            |

| end                                                                      |

| end                                                                      |

| else                                                                     |

| if incoming blk is predicted useful then                                 |

| placed in live part;                                                     |

| else                                                                     |

| placed in part being shutdown;                                           |

| end                                                                      |

| end                                                                      |

When writing back the dirty blocks from the partition to be shutdown, we avoid bursts of writebacks at the end of the epoch by utilizing a writeback policy similar to that proposed by Lee *et al* [43]. We spread the writebacks during the transitional phase, speculatively writing back dirty blocks when the memory bus is idle. No invalidation is sent to higher level caches because our memory hierarchy is non inclusive. The switching latency of the power gate transistor is 2 cycles. It does not impact the application performance. When an additional cache partition is powered up, it is accessed at the end of the transitional period, thousands of cycles later; which is much greater than the switching latency. At the end of the epoch, the sampler counters  $C_i$  are halved to keep track of the program phase.

# 2.2.3 Hardware Implementation

Our design consists of three main hardware components:

- A sampler, co-located with the LLC, encodes the PC of the last instruction that touches a block. A set of counters that captures the application temporal reuse behavior.

- An array of counters to determine the temporal locality of the cache blocks.

- The power gating,  $gated-V_{dd}$ , circuitry used to turn on/off the cache partitions.

The hardware storage overhead cost relative to the LLC is shown in Table 2.1. We assume that the hardware storage is proportional to the area. As such, the area overhead is estimated to be 3.64% of the LLC.

### 2.3 Evaluation

In this section, we discuss the methodology used to evaluate our technique, the energy cost associated and our experimental results.

| Structure              | Per Entry | Per Set    | Total     | Overhead |  |  |  |  |

|------------------------|-----------|------------|-----------|----------|--|--|--|--|

| Sampler                | 52  bits  | 1664  bits | 6.5KB     | 0.3071%  |  |  |  |  |

| Counters               | 32  bits  | 1024 bits  | 1024 bits | 0.0059%  |  |  |  |  |

| Locality counters      | 2 bits    | 6 bits     | 3KB       | 0.1417%  |  |  |  |  |

| Prediction bits        | 1  bit    | 32 bits    | 4KB       | 0.1890%  |  |  |  |  |

| Gated-Vdd circuitry 3% |           |            |           |          |  |  |  |  |

| Total overhead per     | rcentage  |            |           | 3.6437%  |  |  |  |  |

Table 2.1: Hardware storage overhead.

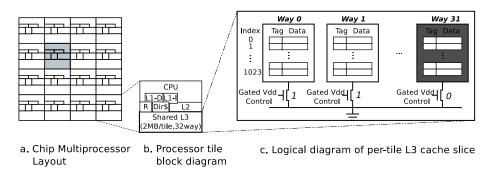

Figure 2.6: Conceptual system overview.

### 2.3.1 Methodology

We modified gem5 [7], a cycle accurate simulator, to accommodate the additional hardware. Our CPU baseline model is a 16-core (4x4) CMP. Each tile consists of a processor, private L1/L2 caches. The LLC is shared among all the cores, with each one having a 2MB slice as shown in Figure 2.6. Our LLC baseline mirrors the Intel Core 7 with 2MB of last level cache per core. We scale up the LLC configuration with cores count. Addresses are interleaved among the slices. Our simulator has a non-inclusive cache hierarchy; its configuration is shown in Table 2.2. We explored a range of configuration parameters and the ones shown in Table 2.2 represent the best setting. These parameters are,  $T_{epoch} = 10$  millions cycles,  $T_c = 0.7 \times T_{epoch}$ ,  $\varepsilon$  = 0.1 and the usefulness threshold  $\tau$  = 8. The default replacement policy for the LLC is LRU.

| Core             | 8-issue out of order, 2GHZ                |

|------------------|-------------------------------------------|

| L1 I-cache       | 32KB, 64B line, 8-way, 2 cycles           |

|                  | latency                                   |

| L1 D-cache       | 32KB, 64B line, 8-way, 2 cycles           |

|                  | latency                                   |

| L2 Private cache | 256KB, $64$ B line, $8$ -way, $10$ cycles |

|                  | latency                                   |

| Last level cache | 2MB/core, 64B size, 32-way, 40            |

|                  | cycles latency                            |

| Cache Coherence  | MOESI                                     |

| Main Memory      | 200 cycles                                |

| $T_{epoch}$      | 10 million cycles                         |

| $T_c$            | 7 million cycles                          |

| ε                | 0.1                                       |

| $\tau$           | 8                                         |

Table 2.2: System configuration.

We use a set of SPEC CPU2006 benchmarks for both single-threaded and multiprogrammed workloads and the PARSEC benchmarks for multithreaded workloads. For the SPEC benchmarks, we fast-forward 10 billion instructions, warm up for an additional 1 billion instructions then run in detailed mode for the next 2 billion instructions. For fair comparison, when running a single-threaded benchmark, we assume only one slice (2MB) of the LLC is available for the workload use. Thus, the results for a single-threaded workload are compared to a CPU baseline of one core and a 2MB LLC. For multiprogrammed workloads, we use the frequency of access (FOA) inter-threads contention model outlined by Chandra *et al* [10] to select the 20 mixes (*mix1 - mix20*) of workloads with the highest cache contention. The statistics are gathered when all of the benchmarks have executed 2 billion instructions. In the case of PARSEC, we run the benchmarks for 2 billion instructions starting from the Region of Interest (ROI), warming up the cache for 1/3 of the ROI. The simulations are performed using the "simlarge" input set with the LLC size of 32MB. We present the performance as the normalized IPC against the IPC achieved with the baseline configuration. In the case of multiprogrammed workloads, we use the normalized system throughput ( $\sum IPC_i / \sum IPC_{iconv}$ ). In the case of multipred workloads, the runtime speedup over the baseline is computed.

| Structure         | Energy Cost (nJ per access) |

|-------------------|-----------------------------|

| Main memory       | 11.99                       |

| Sampler           | 0.009                       |

| Locality counters | 0.00293                     |

| 2MB slice cache   | 0.408                       |

Table 2.3: Dynamic energy cost of the hardware structures.

# 2.3.2 Energy Computation

The proposed technique reduces the leakage energy while incurring minimal extra energy consumption as follows:

- Leakage and dynamic energy due to the sampler and array of counters.

- Leakage energy due to the  $gated-V_{dd}$  circuitry.

- Dynamic energy due to the migration of blocks, data and tag, from the partition being shutdown to the live partition.

- Dynamic energy due to main memory accesses resulting from the writebacks

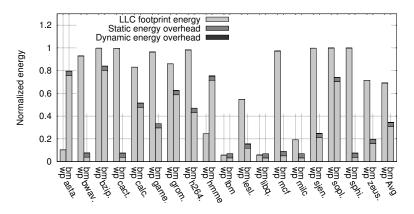

Figure 2.7: Energy dissipation for way partitioning "wp" and blocks migration "bm" normalized to the baseline.

of dirty blocks from the partition being shutdown and the extra misses to the LLC.

In our evaluation, the total energy consumption is computed to be the sum of the leakage energy of the live LLC fraction and the sum of the extra energies listed above. The energy is normalized to the total leakage energy of the LLC in the baseline configuration. The extra dynamic energy due to functional units is ignored because the additional workload execution time is negligible, it less than 2% on average in our experiments. The dynamic energy of the overhead hardware structure is computed as the product of the number of accesses, found through the simulation, and the per-access energy cost, found using CACTI 6.0 [50] configured for 32nm process technology (Table 2.3). The leakage energy of the baseline LLC is estimated to 8.26nJ per cycle per 2MB slice. The leakage energy of the additional hardware is estimated to be 3.64% of the conventional cache as per the discussion in Section 2.2.3.

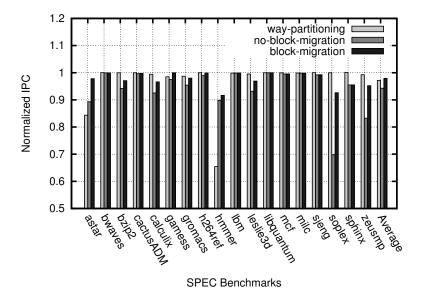

Figure 2.8: IPC comparison for blocks migration and way partitioning normalized to the baseline.

### 2.3.3 Results and Analysis

We present the power and performance results of our "block-migration" method (bm). For comparison, we also evaluate the technique presented by Sato *et al* [58], referred to as *way-partitioning* (wp).

### 2.3.3.1 Single-threaded Workloads

The normalized energy consumption is presented in Figure 2.7. It is broken down into "LLC footprint energy" (the static energy of the active LLC fraction), "static energy overhead" (the leakage overhead due to the additional hardware), and "dynamic energy overhead" (the sum of the dynamic energy due to the extra accesses to the main memory and accesses to the additional hardware and blocks migration). Because Sato *et al* do not estimate the hardware overhead of their "way-partitioning" method, we only present its "LLC footprint energy" thus the comparison is somewhat adverse to "block-migration". The normalized "static energy overhead" is

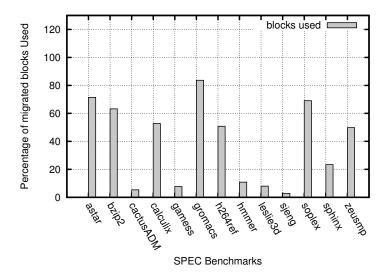

Figure 2.9: Percentage of migrated blocks accessed in the next epoch when the cache is shrunk.

constant across benchmarks at 3.64% while the normalized "dynamic energy overhead" is negligible at 0.032% on average, almost not visible on the charts. Our "block-migration" method achieves an average energy reduction of 66%, versus "waypartitioning" which achieves 30%. *bwaves, cactusADM, lbm, libquantum, milc* either have their memory footprint small enough to fit into the L2 cache or too big to fit into the LLC. As such, our proposed technique shuts down a significant amount of the LLC, 95% for *bwaves*, without performance impact. Not much block migration is performed in those cases; consequently, the performance impact is on par with when no migration is performed (Figure 2.8). "way-partitioning" fails to identify these cases, it allocates 93% of the LLC for *bwaves*. "way-partitioning" locality computation fails to take into account the application overall reuse behavior. Our method shuts down twice as much cache compare to "way-partitioning" with lower performance impact 2.16% versus 2.88% respectively. The energy savings must be examined in conjunction with the performance impact to determine the best trade-off. In cases, such as astar and hmmer, "way-partitioning" saves more energy than "block-migration" but significantly overshoots our performance loss allowance. This is due to the fact that the "way-partitioning" fails to take into account the applications entire reuse behavior when estimating their locality. The performance impact without blocks migration ("no-block-migration") degrades significantly, by 5.69% on average. Some benchmarks such as *soplex* and *zeusmp* suffer a large performance degradation of 30% and 17% respectively without block migration. This is due to the lost of high temporal locality blocks when no migration is performed. The "way-partitioning" allocates a much bigger cache size and therefore has a lower performance performance impact. However, at the cost of a higher energy dissipation.

| Benchmarks | Error (%) |

|------------|-----------|

| astar      | 5.47      |

| bwaves     | 0         |

| bzip2      | 4.29      |

| cactusADM  | 0         |

| calculix   | 8.19      |

| gromacs    | 8.46      |

| h264ref    | 10.91     |

| hmmer      | 5.11      |

| lbm        | 0         |

| leslie3d   | 5.7       |

| libquatum  | 0         |

| mcf        | 0         |

| milc       | 0         |

| sjeng      | 0         |

| soplex     | 18.09     |

| sphinx     | 10.03     |

| zeusmp     | 8.2       |

Table 2.4: Cache size estimation error.

Figure 2.10: Energy dissipation for 2-mix benchmarks using way partitioning "wp" and blocks migrations "bm" normalized to the baseline.

# 2.3.3.2 Impact of Block Migration

We explore the impact of blocks migration for the "cache friendly" workloads, the ones which footprint occupy a significant amount of the LLC. Figure 2.9 shows the percentage of the migrated blocks which are accessed at least once within the next epoch when the cache is shrunk. We observe that indeed, useful data is migrated to the live partition. *astar, bzip2, gromacs* and *soplex* have a higher temporal locality and therefore have a higher percentage of migrated blocks used within the next epoch. These benchmarks show a higher performance degradation when no block migration is performed. *soplex* suffers a performance degradation of 30%.

# 2.3.3.3 Effective Cache Size Prediction

Table 2.4 shows the error of our sampling based cache size computation compared to the exact LLC footprint calculated using a stack distance profiling for each set in the LLC. The results show that our sampling methodology is a reasonably good fit for these benchmarks, though the higher error for *soplex* is also correlated with a higher than average IPC loss on that workload.

Figure 2.11: IPC for 2-mix benchmarks normalized to the baseline.

# 2.3.3.4 Multiprogrammed Workloads

Figure 2.10 shows the energy dissipation for with mixes of two single-threaded workloads (2-mix). To level the playing field, we scale hardware resources with workload count. Hence, we use 2 cores and 2 slices of 2MB LLC (4MB total). The "way-partitioning" shows inferior power savings compared to our technique (23% vs 65%). We observe comparable system throughput across the workload mixtures. On average, "block-migration" achieves 0.95 normalized throughput versus 0.92 for "way-partitioning" (Figure 2.11). We also experimented with 4- and 8-simultaneous single-threaded workloads, these results not included for brevity, and find the lead of "block-migration" increases versus "way-partitioning" with increasing numbers of simultaneous applications.

PARSEC Benchmarks

Figure 2.12: Speedup over baseline and energy dissipation for multithreaded benchmarks using blocks migrations.

### 2.3.3.5 Multithreaded Workloads

The evaluation of our proposed method on multithreaded workloads is illustrated by Figure 2.12. Each multithreaded workload is compiled to generate 16 threads on a  $4 \times 4$  CMP. Our technique shows leakage energy savings of 50% on average at the cost of 2.79% performance impact. *Blackscholes* has a small input set (2MB) therefore a small portion of the LLC remains turned on (6.89%) with almost no performance impact. Alternately, *freqmine* and *facesim* have much larger working sets size (128MB) compared the LLC size (32MB), thus, our technique allocates a small fraction of the LLC (3.5% and 11.93% respectively). Our technique achieves substantial energy savings at yet affordable performance loss. The "way-partitioning" scheme, confining threads to cache partitions, is not applicable to multithreaded workloads.

# 2.4 Summary

This section presented a technique to reduce the static power consumption in last level cache for chip multiprocessor. The proposed technique facilitates power gating in cache by migration the blocks with high temporal locality from the partition to be turned off to the partition to be left powered on. We observed energy saving savings up to 66% with low performance impact of 2.16%. The hardware overhead is estimated to be 3.64%.

#### 3. BFETCH FOR CHIP MULTIPROCESSORS\*

This chapter presents a branch directed, lightweight data prefetcher to improve performance in CMPs.\*A background on prefecthing is provided. The architecture of the prefetcher and details of the proposed design are also presented. In addition, we show evaluation results of our prefetcher compare to current state of the art prefetchers.

## 3.1 Background

A prefetcher must anticipate misses and issue prefetches far ahead of actual execution. This requires accurate prediction of a) the likely memory instructions to be executed, and b) the likely effective addresses of these instructions. The program execution path (*i.e.* which basic blocks are executed and in what sequence) is determined by the direction taken by the relevant control instructions. Memory access behavior can therefore be linked to prior control flow behavior. For example, consider the assembly code in Figure 3.1, consisting of a set of basic blocks and control flow instructions (branches). The basic block executed following each control instruction depends on the direction taken by that control instruction. Data requested in future execution phases and its access patterns are dependent on the branch outcomes encountered along the path and the per-block register transformations along that path. We therefore propose a lookahead mechanism that predicts the likely path of execution starting from the current non-speculative branch and issues prefetches for the memory references down that path.

<sup>\*</sup>Part of this chapter is reprinted with permission from *B-Fetch: Branch Prediction Directed Prefetching for Chip-Multiprocessors* by David Kadjo, Jinchun Kim, Prabal Sharma, Reena Panda, Paul V. Gratz, Daniel A. Jimenez, 2014, The 47th Annual IEEE/ACM International Symposium on Microarchitecture, IEEE Computer Society Washington DC, Copyright [2014] by IEEE Computer Society

Figure 3.1: An assembly code fragment and its control flow graph equivalent.

To accurately predict effective addresses down the predicted path, we leverage the observation that each memory reference always uses a particular register for effective address computation. Unlike previously proposed prefetching approaches that use history based effective address computation techniques, we propose to associate register indices being used by the memory instructions with their preceding control instructions (the entry points of the basic block) and use this correlation to identify prefetch candidate addresses. For example, consider the **Path C** illustrated in Figure 3.1. Relevant memory instructions and their source registers are highlighted in the figure. In **Path C**, both register r7 and r9 do not change their contents. Thus, if we look ahead along the execution path, the effective memory addresses for load instructions can be predicted by adding up static offsets and register values. The lookahead process can be easily performed leveraging support from the branch predictor in the main pipeline. Meanwhile, if the branch is predicted to take **Path A**, the register content of r9 gets changed by the *addi r9, r8, 0xC8* instruction along this path. In this case, if we record the variation of r9 from preceding branch instructions,

(a) Variation of registers content across execution basic block (BB) expressed in granularity of cache block (64B)

(b) Variation of effective addresses across execution basic block (BB) expressed in granularity of cache block (64B)

Figure 3.2: Cumulative distribution of variation in registers content and effective addresses across execution basic blocks.

the effective address can be calculated by adding up current register value, register variation captured in the previous branches, and static offset value. The novelty of *B-Fetch* lies in exploiting branch prediction and predictable register variation to generate the effective memory address.

B-Fetch is based on the premise that register values at the time of effective address generation are correlated in a predictable way from a) their corresponding

values at a time when their preceding branch instructions were executed, and b) the transformations that occur to them over the course of the blocks to that point. Figure 3.2a shows a cumulative distribution of the register variation (delta) across execution basic blocks (BB), for 1 BB, 3 BB and 12 BB. The variation is expressed at the granularity of a cache block (64B). We observe that for a high percentage (92% in case of 1BB) of registers, the variation falls within 64B. Though that percentage decreases for high number of basic blocks, it remains high (89% for 3BB and 82% for 12BB). By contrast, Figure 3.2b shows the variation of the effective addresses across 1 to 12 BB. Unlike the register content, the effective address varies considerably, particularly as the depth increases to 12 BB. Hence prefetchers which rely upon stable or predictable changes in effective address are less likely to be accurate than those that can incorporate current register values into the prefetch effective address calculation.

#### 3.1.1 Overview

*B-Fetch* is a data cache prefetcher that employs two speculative components. It speculates on a) the expected path through at future BBs, and b) the effective addresses of load instructions along that path. The first speculation is directed by a lookahead mechanism that relies on branch prediction to predict the future execution path. For the second, *B-Fetch* records the variation of register contents at earlier branch instructions and exploits this knowledge to predict the effective address. By making use of the variation of register values rather than the effective address history, *B-Fetch* can issue useful prefetches even for instructions that exhibit irregular control flow and data access patterns.

Figure 3.3 illustrates the overall system architecture of a B-Fetch enabled outof-order processor. It shows the main CPU execution pipeline and the additional

Figure 3.3: Overall *B-Fetch* microarchitecture.

hardware for the *B-Fetch* prefetcher. In our baseline design, the main processor has an out-of-order pipeline with a 4-wide issue width. The *B-Fetch* hardware forms a separate, 3-stage prefetch pipeline parallel to the main pipeline. The *B-Fetch* pipeline is connected to the core's Fetch stage via the Decoded Branch Register (DBR). As branch instructions are decoded in the main execution pipeline, the corresponding PCs are placed into the DBR to initiate the prefetching process. After branch PCs and target addresses are fed into the prefetch pipeline, the *B-Fetch* engine starts to predict future execution path, memory instructions, and their effective addresses. The *B-Fetch* pipeline consists of the following stages:

• Branch Lookahead: This stage is responsible for generating the predicted path of program execution starting from the currently decoded branch. This stage also estimates the confidence along that path, stopping when the confidence falls below a given threshold.

- **Register Lookup:** This stage is responsible for capturing and providing information about the registers used to generate effective addresses within a given block.