# IMPROVING THE SIMULATION ENVIRONMENT FOR COMPUTER ARCHITECTURE

#### A Thesis

by

## ALBERTO JAVIER NARANJO CARMONA

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

Chair of Committee, Paul V. Gratz Committee Members, Jiang Hu

Rabinarayan Mahapatra

Head of Department, Chanan Singh

December 2014

Major Subject: Computer Engineering

Copyright 2014 Alberto Javier Naranjo Carmona

#### ABSTRACT

This work presents the efforts to improve the simulation environment for computer architecture research through two major contributions: The addition of a three level cache hierarchy and implementation of a statistical sampling simulation framework.

Full-system and micro-architectural simulation are the primary and most reliable research tools that the computer architecture community has. However, keeping the simulator up to date with the latest industry products is a challenging task, causing a growing time gap between the release of new commercial products and the implementation of their models in the simulators. Another problem architects have to deal with is the performance gap; the time spent on simulating one instruction is several orders of magnitude bigger than the time the real hardware takes to execute the same instruction. This leads to prohibitively long simulation times that, due to the always efficiency-focused industry trend, is also to be increased. As processors get more complex, so do the simulators. The performance improvement achieved by real hardware changes is too small compared to the overhead induced into the simulator while trying to replicate those same changes.

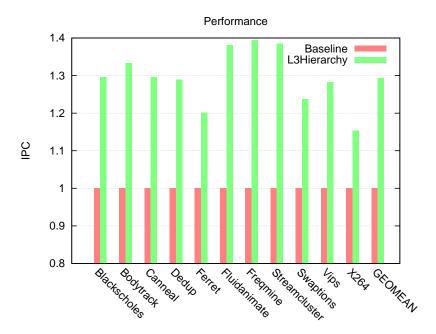

Although a third level (L3) cache hierarchy is a common feature in current processors and its benefits in performance have been known for decades, currently, it is not supported in most full-system simulators. A modern full system simulator was extended to include a third level cache and experiments show that for the PAR-SEC benchmarks, the performance of the system with L3 is  $\approx 30\%$  better than the baseline.

On the other hand the implementation of statistical sampling simulation allows

a greater improvement in simulation performance while statistics theory guarantees that the subset of instructions executed are a representative sample of the benchmark behaviour. The experiments show a measured CPI error of less than 2.5% while achieving simulation time speed-ups of around 3X.

# DEDICATION

To all my family and Miriam.

Without your support I wouldn't have done it, thanks for everything.

## ACKNOWLEDGEMENTS

Special thanks to Dr Paul Gratz, for your patience and always helpful comments. Thanks to all the people in the CAMSIN group, I learned so much next to you all. This work was funded by the Consejo Nacional de Ciencia y Tecnología (CONACYT) - Mexican Council of Science and Technology.

# TABLE OF CONTENTS

|    |      |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page                                  |

|----|------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| AI | BSTR | ACT                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . ii                                  |

| DI | EDIC | ATION                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . iv                                  |

| A( | CKNC | OWLED                                                       | OGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . V                                   |

| TA | ABLE | OF CO                                                       | ONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . vi                                  |

| LI | ST O | F FIGU                                                      | JRES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | viii                                  |

| LI | ST O | F TAB                                                       | LES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . X                                   |

| 1. | INT  | RODU                                                        | CTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 1                                   |

|    | 1.1  | Thesis                                                      | statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 3                                   |

| 2. | BAC  | CKGRO                                                       | UND: CACHE MEMORIES AND STATISTICAL SAMPLING                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5                                     |

|    | 2.1  | 2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7 | memories and coherence Organization and policies of cache memories  Memory hierarchy and its effects in CPU performance Classic coherence problem Cache coherence protocols The MESI protocol Atomic coherence and race conditions Survey on cache coherence verification techniques Cical sampling and confidence intervals Basic properties of confidence intervals Confidence intervals for unknown mean and unknown standard deviation  Confidence intervals for unknown mean and unknown standard deviation | 6 11<br>14 16<br>21 24<br>27 34<br>35 |

| 3. |      |                                                             | NTATION OF A THREE-LEVEL CACHE HIERARCHY IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 40                                  |

|    | 3.1  | Origin 3.1.1 3.1.2                                          | al two-level cache hierarchy in gem5                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 41                                  |

|    |      | 3.1.3  | FSM in L2 49                                          |

|----|------|--------|-------------------------------------------------------|

|    |      | 3.1.4  | Support to atomic operations                          |

|    |      | 3.1.5  | Retaking the concurrent store problem                 |

|    | 3.2  | Extens | sion to three cache levels                            |

|    |      | 3.2.1  | New memory hierarchy                                  |

|    |      | 3.2.2  | New FSM in L1                                         |

|    |      | 3.2.3  | New FSM in L2                                         |

|    |      | 3.2.4  | Locks of states                                       |

|    |      | 3.2.5  | Handling atomic operations with three cache levels 81 |

|    |      | 3.2.6  | Verification of the new cache hierarchy               |

|    |      | 3.2.7  | Experiment design and performance results             |

| 4. | STA  | TISTIC | SAL SAMPLING SIMULATION IN GEM5 89                    |

|    | 4.1  | Survey | on sampling simulation techniques                     |

|    |      | 4.1.1  | Warm-up techniques                                    |

|    |      | 4.1.2  | Sampling simulation for single-threaded programs 93   |

|    |      | 4.1.3  | Sampling simulation for multi-threaded programs 97    |

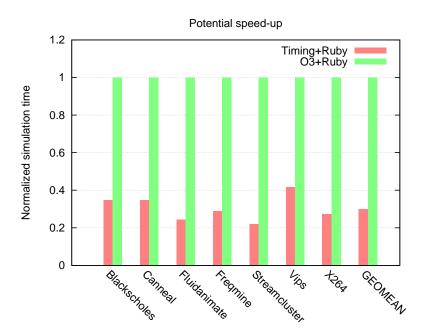

|    | 4.2  | Potent | ial speed-up in gem $5$                               |

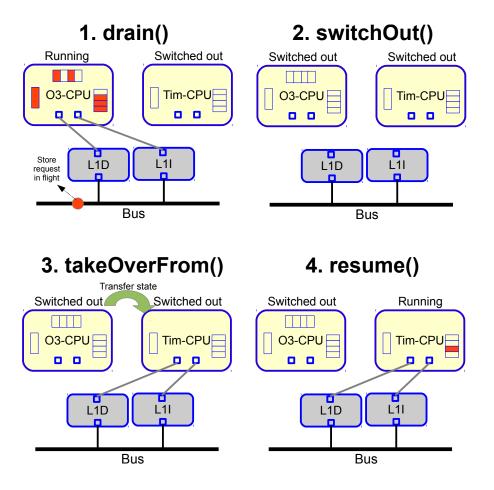

|    | 4.3  | Switch | ing CPU models                                        |

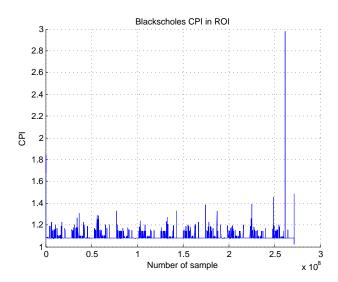

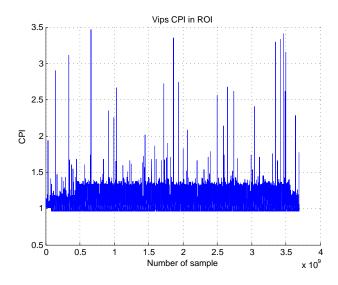

|    | 4.4  | Optim  | al period and sample size                             |

|    | 4.5  | Sample | ing process                                           |

|    | 4.6  | Result | 116                                                   |

| 5. | CON  | NCLUSI | ONS                                                   |

| DΙ | arra | ENCE   | ! 100                                                 |

# LIST OF FIGURES

| FIGUR | FIGURE                                                                    |     |  |

|-------|---------------------------------------------------------------------------|-----|--|

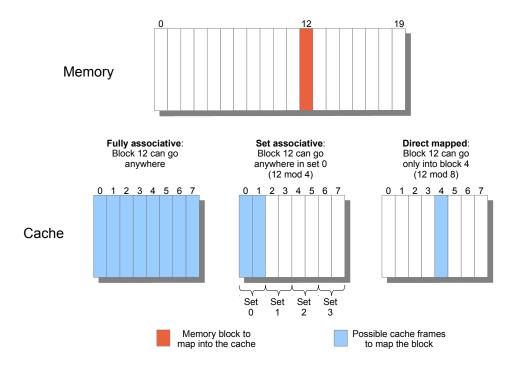

| 2.1   | Example of block cache mapping for different associativities              | 8   |  |

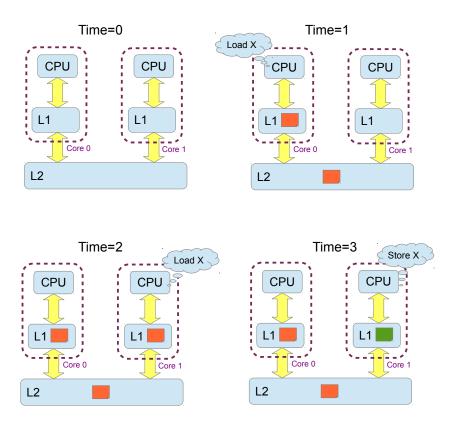

| 2.2   | Classic coherence problem                                                 | 15  |  |

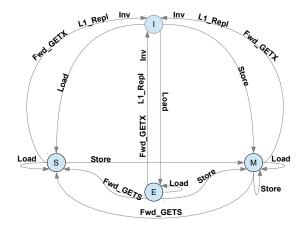

| 2.3   | State diagram of the MESI protocol                                        | 24  |  |

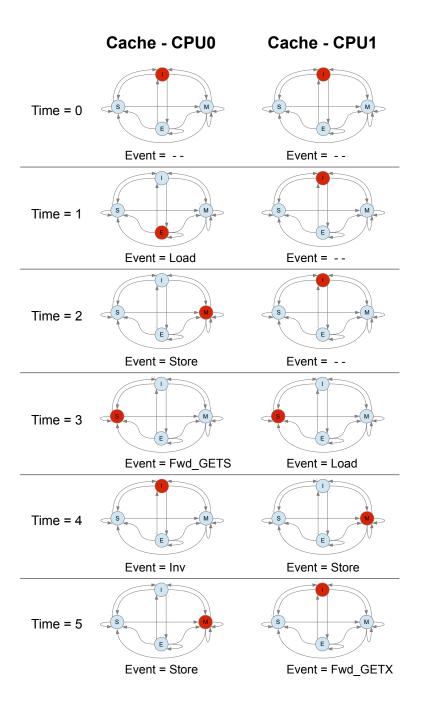

| 2.4   | Example of the operation of the MESI protocol between two caches.         | 25  |  |

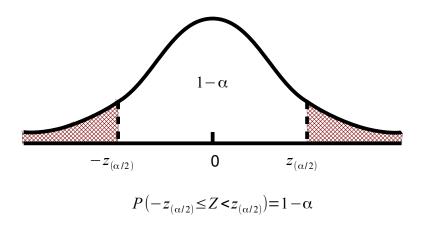

| 2.5   | Probability distribution of observing a value greater than $z_{\alpha/2}$ | 36  |  |

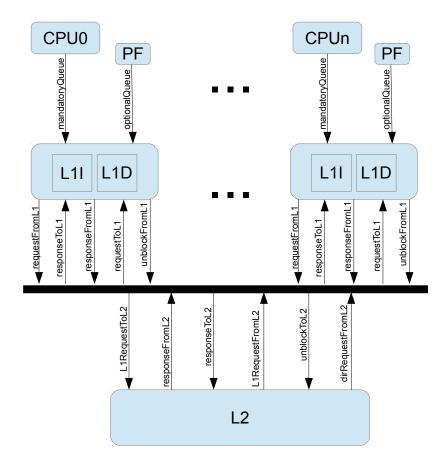

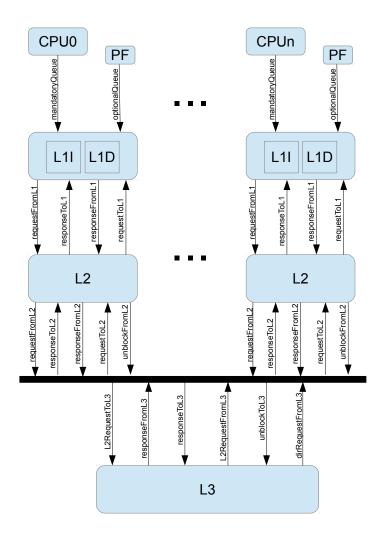

| 3.1   | Original two level cache hierarchy with private L1 and shared L2          | 43  |  |

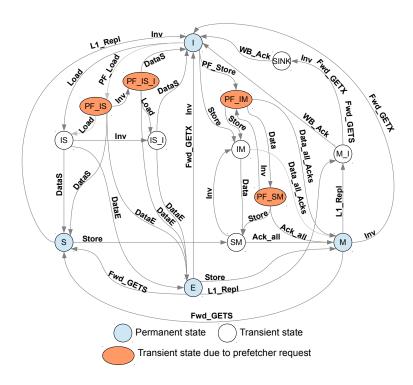

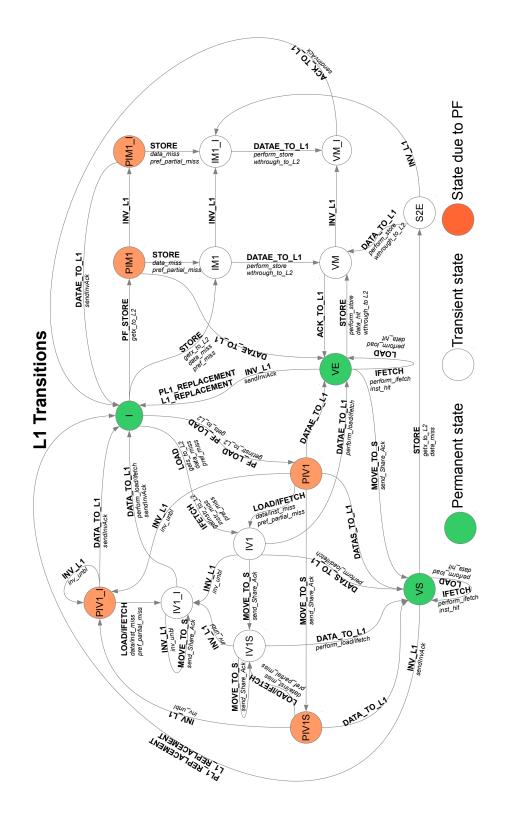

| 3.2   | FSM describing the coherence protocol originally implemented in L1.       | 46  |  |

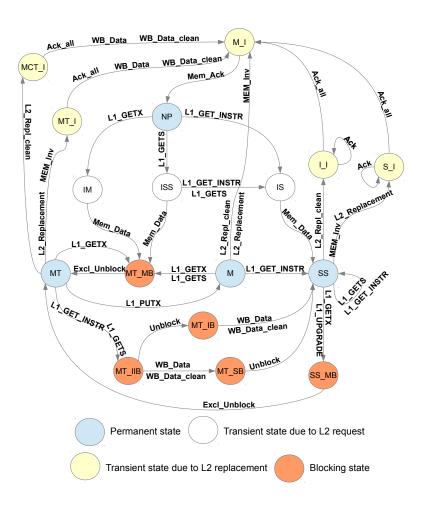

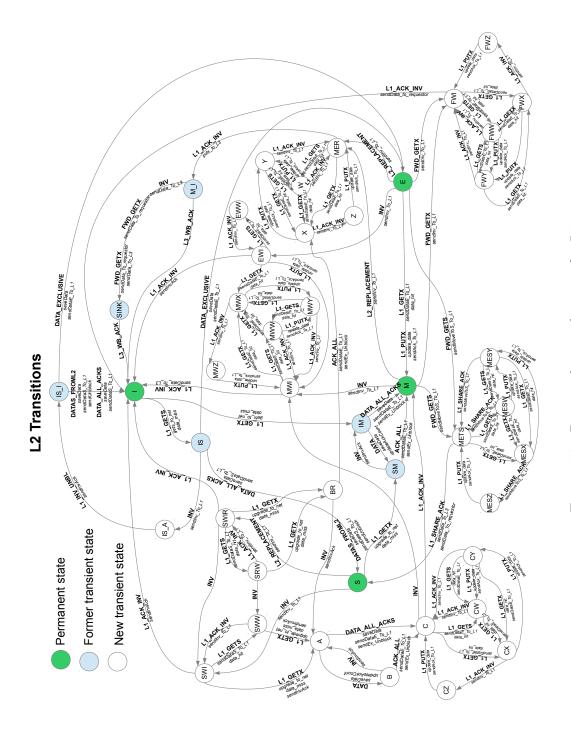

| 3.3   | FSM describing the coherence protocol originally implemented in L2.       | 50  |  |

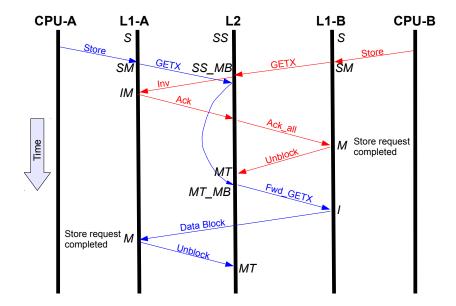

| 3.4   | Example of concurrent store requests                                      | 55  |  |

| 3.5   | Proposed three level cache hierarchy                                      | 59  |  |

| 3.6   | Proposed state diagram for L1                                             | 64  |  |

| 3.7   | Proposed state diagram for L2                                             | 76  |  |

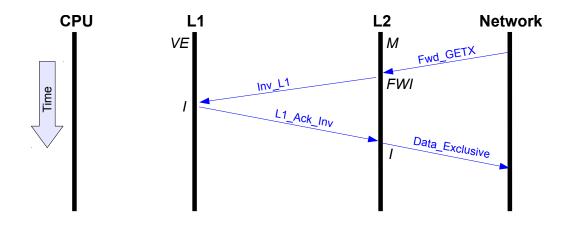

| 3.8   | Communication example between L1 and L2 with no race conditions.          | 79  |  |

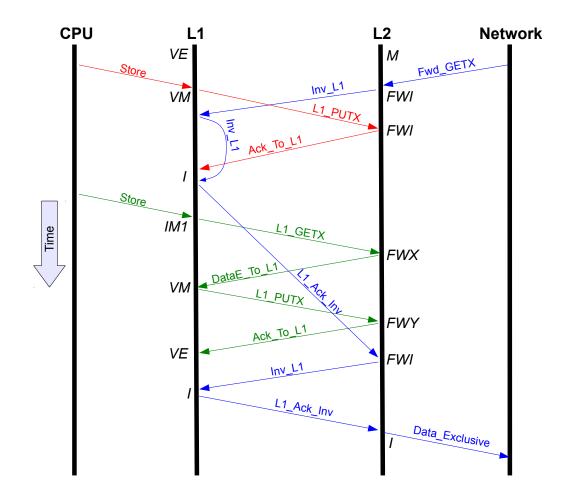

| 3.9   | Communication example between L1 and L2 with race conditions              | 81  |  |

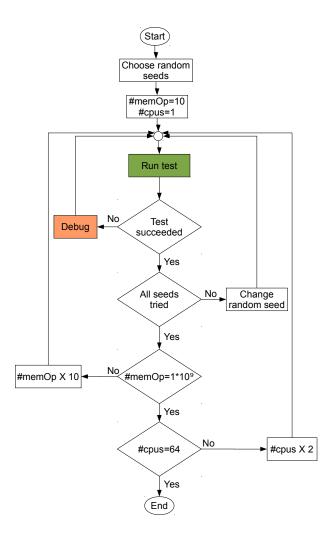

| 3.10  | Algorithm used to debug and verify the new coherence protocol             | 84  |  |

| 3.11  | Performance improvement with the L3 cache hierarchy                       | 86  |  |

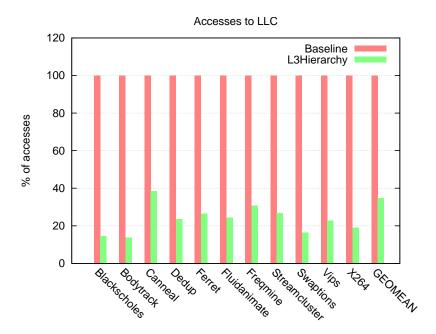

| 3.12  | Reduction of accesses in LLC with the L3 cache hierarchy                  | 87  |  |

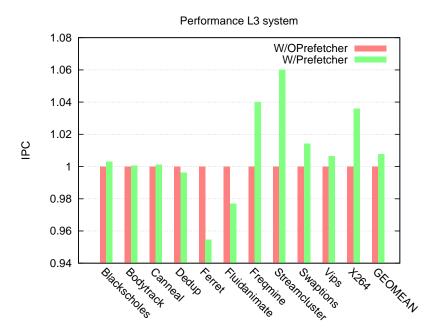

| 3.13  | Performance comparison of a system with or without prefetcher             | 88  |  |

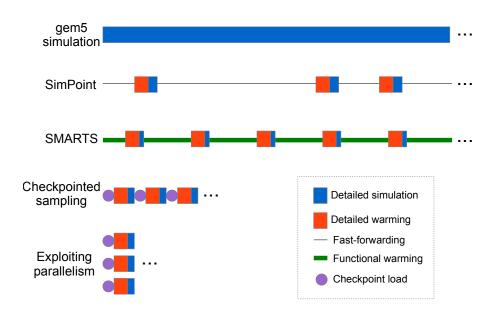

| 4.1   | Sampling techniques for single-threaded programs                          | 96  |  |

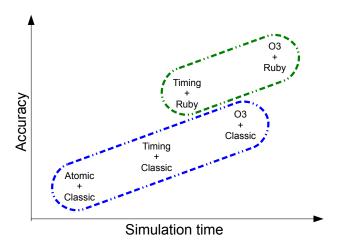

| 4.2   | Summary of all possible combination of models in gem5                     | 103 |  |

| 4.3  | Potential speed-up in the Parsec suite                                      | 106 |

|------|-----------------------------------------------------------------------------|-----|

| 4.4  | Process of switching CPU models                                             | 108 |

| 4.5  | CPI of blackscholes throughout the ROI                                      | 110 |

| 4.6  | CPI of vips throughout the ROI                                              | 110 |

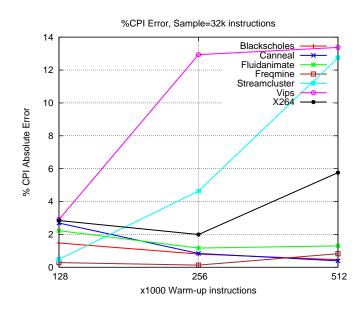

| 4.7  | CPI percentage error for W when U=32k                                       | 111 |

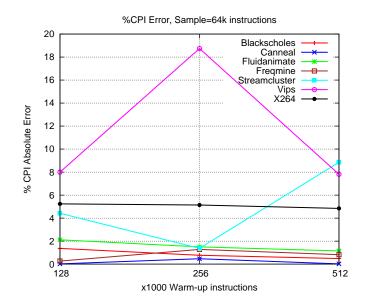

| 4.8  | CPI percentage error for W when U=64k                                       | 112 |

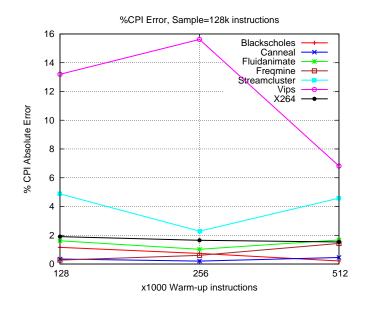

| 4.9  | CPI percentage error for W when U=128k                                      | 112 |

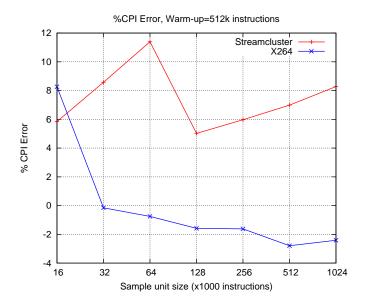

| 4.10 | % CPI error, W=512k                                                         | 113 |

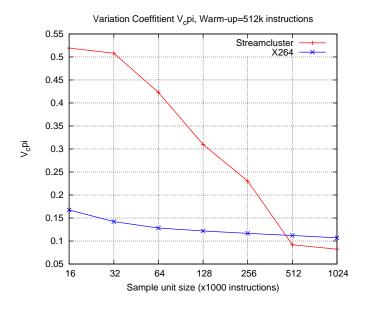

| 4.11 | Variation coefficient, W=512k                                               | 113 |

| 4.12 | Sampled CPI and interval of $\pm$ 5% of the pure detailed CPI               | 117 |

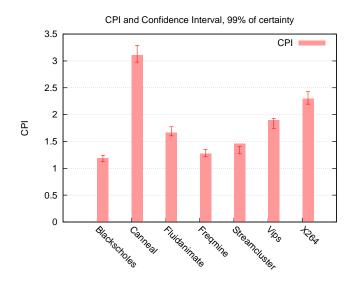

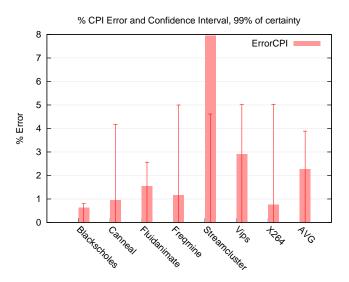

| 4.13 | Percentage CPI error and confidence intervals with confidence level of 99%  | 117 |

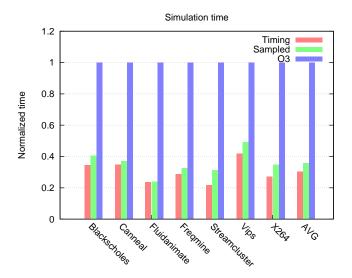

|      | Speed-up of sampling compared with the pure timing and detailed simulations | 118 |

# LIST OF TABLES

| TABLI | E                                                                          | age |

|-------|----------------------------------------------------------------------------|-----|

| 2.1   | Description of states in the MESI protocol                                 | 22  |

| 2.2   | Description of events in the MESI protocol                                 | 23  |

| 2.3   | Description of actions in the MESI protocol                                | 23  |

| 3.1   | Definition of states originally implemented in L1                          | 47  |

| 3.2   | Definition of events originally implemented in L1                          | 48  |

| 3.3   | Definition of states originally implemented in L2                          | 51  |

| 3.4   | Definition of events originally implemented in L2                          | 52  |

| 3.5   | Definition of the proposed events for L1                                   | 61  |

| 3.6   | Definition of the proposed states for L1                                   | 62  |

| 3.7   | Definition of the proposed states for L2                                   | 66  |

| 3.8   | Definition of the proposed events for L2                                   | 77  |

| 3.9   | Specifications for the baseline and proposed hierarchy for the experiment. | 85  |

| 4.1   | Summary of the 1st sampling round                                          | 115 |

| 4.2   | Summary of the 2nd sampling round                                          | 115 |

| 4.3   | Summary of the 3rd sampling round                                          | 116 |

| 4.4   | Percentage of instructions spent in each stage                             | 119 |

| 4.5   | Recommended sampling period for W=256000 and U=64000 instructions          | 119 |

#### 1. INTRODUCTION

Due to the high complexity of modern microprocessors, hardware prototyping is infeasible. The best tools researchers in computer architecture can rely on are simulators that aim to replicate the structure and system performance during the design process. However, modifying and working with the simulators require a deep understanding of the most popular micro-architecture techniques and how they affect other elements inside the system.

Moore's law[25], which allows us to double the amount of switching elements per unit area in a given period, as well as the non-ending trend to find ways to improve performance, have pushed industry to release new upgraded versions of their products with months of difference from the previous ones. Unfortunately, the upgrades are not directly transferred to the simulators field, where researchers expect to have reliable simulators with behaviour close to that seen in real current processors. Implementing those changes takes time and is even harder because industry may not publish in detail their improvements.

All this has led to a huge architectural gap between simulators and real processors. As an example, in order to address the growing disparity of speed between CPU and memory outside the chip known as the "memory wall", computer architects implemented cache memories which are smaller but faster memories inside the CPU chip. Adding more levels of cache memories to the system was a relatively straight forward conclusion; the first processors with three levels (L3) of cache memory appeared in the market in 2001. Up to the date of this writing, the stable version of popular full-system simulators like gem5[5], does not support a memory hierarchy with L3. As a result, there is a difference of 13 years between the architecture implementation

of the simulators and the real CPU's.

As simulators try to approach the state of current processors, they get increasingly more complex. Even running over the most recent processors, the simulated hardware is several orders of magnitude slower than real hardware. Full system simulation (including many CPU's, peripherals and other system components) increases the slowdown up to a factor of 10 to 100. In other words, multi-processor simulation could be a million times slower than real hardware[40]. Furthermore, the benchmarks used to test multi-threaded applications are often longer than their single-threaded counterparts. This speed difference leads to prohibitively long run times (months or even years) for simulating complete benchmark application.

Several approaches to this problem have been proposed[37]. One is to use abbreviated instruction execution streams of benchmarks, but studies concluded that abbreviated execution streams may fail to capture the global variations in program behaviour and performance[21]. Others require a previous analysis of the benchmark trace in order to find repetitive and representative instructions patterns and only execute them once[34]. A different technique runs an initial functional simulation and creates many checkpoints, later, it restores them just to run few instructions and then kill the simulation[41, 43].

Another solution is statistical sampling simulation [42] which uses two different CPU models, one slow and cycle-detailed and other fast and functional. Functional simulators just interpret or execute the instructions of a program. On the other hand, cycle-detailed simulations model the micro-architecture of a design and are used to measure the number of cycles required to execute a program. The idea of sampling simulation is to fast-forward most of the instructions with the fast and functional CPU model, sample few instructions with the cycle-detailed model and then switch back to the functional model to repeat the process. Using sampling theory we can

be certain that the measured parameter is within an interval with a given confidence level.

There is no common agreement about which sampling simulation technique the best, but the involved trade-offs (accuracy, simulation time, disk usage and flexibility) indicate the choice depends on the platform, simulator and benchmarks of interest.

Sampling simulation is not implemented in gem5, to reduce the simulation time, the researcher can either fast-forward until a given instruction and continue the remaining simulation in detailed mode, or switch back and forth between the two modes and simulate exactly one half of instructions in each model. Any of this two cases does not achieve the maximum speed-up or provide statistical support about the certainty of the measured parameter. However, these already added features to the simulator and the low disk space usage requirement made of the statistical sampling simulation the most suitable technique to be implemented in gem5.

#### 1.1 Thesis statement

The aim of this work is to improve simulation framework on two different fronts; the implementation of micro-architecture features present in modern system and the reduction of time spent in simulation. Thus, the statement of this thesis is the following: It is possible to keep increasing the complexity of the simulators and still reduce the simulation time without significant accuracy loss.

One of the contributions of this work is adding a third level cache to gem5 in the most detailed mode which includes creating a new data coherence protocol for chip multiprocessor (CMP) simulation. With this improvement simulations of the memory transactions throughout all the memory hierarchy resemble more closely the behaviour of current designs. In the following chapters I will explain some design, implementation and verification issues that I faced while creating the new coherence

## protocol.

The last contribution of this work is the addition of support to Statistical Sampling Simulation in gem5. In the second part of this work I will explain in detail the theory behind the technique, the process of switching CPU models during runtime, implementation challenges and the results such as the percentage error or the speed-up in run time.

#### 2. BACKGROUND: CACHE MEMORIES AND STATISTICAL SAMPLING

#### 2.1 Cache memories and coherence

An ideal memory system is expected to have infinite capacity, infinite bandwidth, zero latency, non-volatility and zero implementation cost[33]. However, the reality is far from that idealism, the performance of memories has not scaled as fast as the processor performance resulting in one of the biggest challenges in computer architecture known as the *memory wall*.

So far, there is no material or technology capable of satisfying all the aforementioned features, but there do exist some technologies that at least have a good performance in one of those features. Magnetic hard drives offer huge non-volatile storage at low cost but they are ridiculously slow compared with the needs of the processor. The DRAM memory is faster than hard drives, offers higher bandwidth but is expensive, volatile and has less capacity. Finally the SRAM, which should be kept small in order to be as fast as the processor also it is volatile and extremely expensive. With these elements designers have created many memory hierarchies that aim to immediately supply the requested data at almost no cost, however, since all the components inside the hierarchy are not ideal, some clever management needs be done to approach the idealism.

Memory systems exploit an observed attribute of program execution called *locality* of reference which states that programs tend to work only on regions of contiguous blocks of the memory. Specifically the principle of locality can be broken into two concepts.

• Temporal locality: A data block accessed, it is very likely to be accessed again in the near future.

• Spatial locality: When a block is accessed, the contiguous blocks are very likely to be accessed in the near future.

Thus, if we want a close to ideal performance of the memory system, we better get those likely to be accessed blocks near the processor. Cache memories are small fast memories usually implemented in the same die of the processor that quickly supply all the memory requests, exploit the locality of the programs and diminishes the effects of the memory wall.

## 2.1.1 Organization and policies of cache memories

A cache line or cache block is a contiguous series of bytes in memory and is the basic element on which caches operate. The smallest usable block size is the natural word size of the processor because at each access the cache must supply at least that many bytes. If a given cache has block size of 16 bytes and a capacity of 512 bytes, it is composed by 512/16 = 32 blocks. Thus, the  $\log_2 16 = 4$  least significant bits of the address will be used to index to the desired byte inside the block, the remaining higher order bits locate the appropriate block in the cache memory.

At every processor's memory request the caches must quickly determine whether they contain the requested block or not, nevertheless, the look-up latency is not only related to the cache capacity, but also to its internal organization or associativity that determines how blocks are arranged in a cache that contains multiple blocks. Usually, the cache space is divided into sets of blocks where depending on the address, the block is mapped to any available location inside a particular set.

There exist several approaches that play with the number and size of sets, but the simplest one is the  $direct\ mapped$  approach that has as many sets as blocks in the cache. Consider a cache with N blocks, in this case the cache would have N sets, each one containing one block. Thus, this is a many-to-one mapping between

addresses and storage locations in the cache and a particular address can only reside in a single location in the cache. The mapping is determined by the operation (blockaddress)MOD(#ofblocksincache).

Of course, there also exists the other extreme case where for a given cache with N blocks there is only one big set containing all the N blocks. This approach is called fully associative, it does an any-to-any mapping between addresses and available storage locations. Any memory address can reside anywhere inside the cache and all entries must be searched to find the right one.

The last approach, set associative, lies between the previous two. It proposes a set size greater than one but smaller than the total number of block in the cache and does a many to few mapping. In such way, the cache entry is assigned to a specific set resulting from the operation (blockaddress)MOD(#ofsetsincache) and it can reside on any available location inside the set. If there are n blocks in a set, the cache is said to be n-way-set asossiative[33]. Figure 2.1 shows an example of the different approaches implemented in a cache with eight blocks.

On every cache access the address is used to identify the corresponding set, however, inside the set, the block can reside in any storage location and it wouldn't be easy to find the correct. That is why caches have on each block an additional field called *tag* that gives the block address. Hence, the tag of every cache block inside the selected set is checked to see if it matches the block address from the processor. This comparison process is done in parallel in order to save time.

If one of the comparisons succeeds, the requested block is present in the cache and a *hit* has occurred, otherwise, it is a *miss* and the requested block must be brought from lower levels of memory.

An good cache system is expected to show a miss rate close to zero, nevertheless, there are different causes for a miss and not all of them are related to the behaviour

Figure 2.1: Example of block cache mapping for different associativities.

of the program or the capacity of the cache. The categories of the causes of all misses are[19]

- Cold or compulsory: Since the caches are volatile, the very first access to a block cannot be in the cache and must be brought from lower levels. These misses would occur even with infinite sized caches.

- Capacity: Due to insufficient capacity in the cache, the blocks are constantly discarded and later retrieved. A bigger enough cache solves the problem.

- Conflict: A block may be discarded and retrieved if multiple blocks map to the same set and accesses to the different blocks are intermingled. These misses are because of imperfect allocation of entries in the cache. Associativity of the

cache affects the misses by conflict, in particular a full set associative cache would eliminate them all.

• Coherence: This kind off misses is exclusive of multi-core systems. In order to maintain data coherence, before a particular core is allowed to modify a cache entry, the coherence mechanism must ensure that all the copies of the same block in other core's caches are invalidated, that would eventually cause a miss in the other caches. This misses have nothing to do with the cache size or organization, they are due to non idealisms in the coherence mechanism.

When a miss occurs the cache controller must guarantee that there is enough room for the new block before bringing the data from lower memory levels. However, it is very unlikely to have any available spot for the new block, thus, the controller should select a block to be replace with the new data. With the direct mapped caches this selection is trivial because there is only one block per set, but in cache organizations with more than one block per set the controller must evict the block with less chances to be used in the future. Predicting the future and chose the best block is not an easy task, but there exist several techniques like:

- Random: To spread allocation uniformly, candidate blocks are selected by a pseudo-random generator.

- Least recently used: Accesses to blocks are recorded, according to the principle of temporal locality the less likely block to be used is the one that has not been used for the longest time.

- First in, first out: LRU is hard to implement. This technique tries to approximate LRU by identifying the oldest block.

• Least frequently used: Through a period of time the least frequently used block will cause less misses.

Another important aspect of caches worth of analysis is the policies they have to handle writes. If a load/fetch operation misses, the cache controller must allocate (and replace if necessary) a new block in the cache and wait until the data is supplied by lower levels to complete the operation. However, since previous data are not needed for a write, there are two options:

- No-write allocate: This is actually not considered as a miss because the processor does not need to wait if the block is not present in the cache. Instead of allocating the new block in the cache the block is modified only in the lower-level memory. Not recommended in multi-processor systems because can cause race conditions when two different processors modify the same block at the same time.

- Write-allocate: In order to execute the write, the block must be present in the top-level cache. Hence, if it causes a miss, it is treated as a load miss, and once the block is allocated in the top-level cache, the write operation can complete. This approach is more useful in multi-processor systems because when the low level supplies the block for a write, the coherence protocol guarantees that there are no copies in other caches and it avoids race conditions.

The only presence of a cache memory implies the existence of other copies of the blocks in lower levels of the memory hierarchy. When writes to blocks are executed and the blocks in the top-level cache are updated, a mechanism must ensure that the other copies in lower levels will get updated too. There are two policies to handle this situation, one is *write-through* which simply propagates each write through the

cache to he next level. Although its implementation is straight forward, its main drawback is the amount of required bandwidth. After every store, there must be communication between different memory levels, even if that same block will be overwritten in the same operation.

The other policy is write-back which delays updating the copies in lower levels until the block of interest is evicted from the top level. It works under the idea that only the processor needs to get an updated copy of the block at any time, if the latest copy is kept in the highest level of memory, there is no need waste bandwidth and power on updating lower cache levels. However, its implementation is more complex; it requires a dirty bit that indicates when the block has been modified and the version in lower levels is out of date. When the block is to be evicted from the top level, if the dirty bit is set the data is written back to lower levels, otherwise the block is just discarded.

## 2.1.2 Memory hierarchy and its effects in CPU performance

One way to measure how a memory system affects the performance of the CPU is counting the number of cycles the CPU has to stop execution and wait for the memory's response. Assuming a single in-order CPU that stalls whenever a cache miss occurs and whose hits only take one cycle to complete, the amount of cycles the CPU must stall due to cache misses is

$$MemoryStallCycles = NumberOfMisses \times MissPenalty$$

$$= InstructionCount \times \frac{Misses}{Instruction} \times MissPenalty$$

$$= InstructionCount \times \frac{MemoryAccesses}{Instruction} \times MissRate$$

$$\times MissPenalty$$

$$(2.1)$$

The first two terms of equation 2.1 are intrinsic of the program and cannot be

changed with a better design. Nevertheless, as explained before, the miss rate changes with the size and associativity of the caches. Another option architects have to alleviate the impact of misses is to reduce the average miss penalty.

As a thumb rule, the bigger the memory, the bigger the latency. Then, it makes sense to have a small enough first level to match the clock cycle of the fast processor. However, in case of miss the cache controller must forward the request to main memory which has a huge latency. Even with low miss rate, the resulting memory stall cycles can be unacceptable. The average memory access time of the first level (experienced by the processor) is:

$$AvgMemAccessTime = HitTime_{L1} + MissRate_{L1} \times MissPenalty_{L1}$$

(2.2)

Where  $HitTime_{L1}$  is the latency of the first level.

As a simple approximation we can say that the miss penalty of equation 2.2 seen in L1 is constant and is composed by

$$MissPenalty_{L1} = DRAMLatency$$

(2.3)

And equation 2.2 can be rewritten as

$$AvgMemAccessTime = HitTime_{L1} + MissRate_{L1} \times DRAMLatency$$

(2.4)

A simple solution is to add another level (L2) of cache between the original cache (L1) and main memory. L2 must be bigger than L1 so it can supply most of the L1's misses but smaller than main memory so it doesn't have a prohibitively latency. Since now all L1's misses are the L2's accesses and all L2's accesses correspond the

the accesses to main memory, the new L1 and L2 miss penalty are

$$MissPenalty_{L1} = HitTime_{L2} + MissRate_{L2} \times MissPenalty_{L2}$$

(2.5)

$$MissPenalty_{L2} = DRAMLatency$$

(2.6)

Thus, after substituting equations 2.5 and 2.6 in the expression of equation 2.2, the average memory access time with two cache levels is defined by

$$AvgMemAccessTime = HitTime_{L1} + MissRate_{L1} \times MissPenalty_{L1}$$

$$= HitTime_{L1} + MissRate_{L1}$$

$$\times (HitTime_{L2} + MissRate_{L2} \times MissPenalty_{L2}) \quad (2.7)$$

$$= HitTime_{L1} + MissRate_{L1}$$

$$\times (HitTime_{L2} + MissRate_{L2} \times DRAMLatency)$$

If we really expect to see a better memory performance, that is, the average memory access time with two cache levels (eq. 2.7) to be smaller than the access time with only one cache level (eq. 2.4), the following condition must hold

$$AvgMemAccessTime_{WithL1} > AvgMemAccessTime_{WithL2}$$

$$eq. 2.4 > eq. 2.7$$

$$DRAMLatency > HitTime_{L2} + MissRate_{L2} \times DRAMLatency$$

$$DRAMLatency (1 - MissRate_{L2}) > HitTime_{L2}$$

$$(2.8)$$

Equation 2.8 tells us that if both, L2's miss rate and hit time are kept small, it is more likely to improve the performance.

The L2 design is not trivial, in reality there is a compromise between the latency and miss rate. The same analysis applies to determine if even more cache levels would be beneficial to the performance of the system. In practice, the power and silicon area constraints stop us to have many more cache levels.

#### 2.1.3 Classic coherence problem

In the last decade, due to several reasons, the interest of researching on techniques that exploit Thread Level Parallelism has grown among the computer architecture community; commercial multi-processor systems appeared as a consequence. Regarding cache memories, it does not make sense to have one huge shared cache in the first level because its latency would negatively affect the processor performance on every memory operation. The most common solution is to have a small and fast first level cache private for each core.

Every core runs different threads and can have its own address space<sup>1</sup>. However, it is also possible that more than one core operate on the same memory address, which implies that the cores share the block and keep copies from it in their individual private caches.

Caching shared data introduces a new problem, that if not handled properly, the cores may end up seeing two or more different values for the same memory location. Figure 2.2 depicts the process that leads to the *Coherence problem*. Consider a system with two processors (CPU0 & CPU1), each one with its own private L1 cache and both share a common L2 cache. At time=0, both cores are running their own threads and do not share any memory location. Later on at time=1, CPU0 decides to load a new value, so the requested block is brought from main memory, stored in L2 and the private CPU0's L1. Some moments after that, when time=2 the process

<sup>&</sup>lt;sup>1</sup>Set of memory addresses to be accessed.

Figure 2.2: Classic coherence problem.

running in CPU1 requests a read to the same address that CPU0 did before, then the same block is copied from L2 to CPU1's L1. Finally, at time=3 CPU1 does an store and modifies that block, at that moment both cores have different versions of the same data block. If CPU0 reads the block again, it will read the old version of the block and has no way to know that the read value is out of date. That process can keep going indefinitely and each core will read and modify its own copy of the block without being able to determine which version is the right one. This situation violates the coherence of the memory system because it is not clear what value can be returned after a read.

In general, a memory system is coherent if it supports:

- 1. Write propagation: Any change to the memory image made by one processor's write is made visible to all other processors in the system before any of the other processors could load or store that specific location. It must always return the latest written value on each load.

- 2. Write serialization: Two writes to the same memory location by any two processors are seen in the same order by all processors.

A coherent view of the memory is hard requirement for shared-memory multi-core systems. Without it, programs that share memory in two or more cores would behave unpredictably. Designers have developed many protocols that handle properly the coherence problem.

## 2.1.4 Cache coherence protocols

A cache coherence protocol is a set of rules that a memory system must follow after read/write requests in order to have coherence and consistency among multiple data copies, it must also support the principles of write propagation and serialization. To accomplish this, the controller must keep track of the state of any shared data block.

Depending on the kind of action that protocols do to make write visible to other processors, to classes of protocols exist:

• Write-update: These protocols are based on a broadcast write-through policy. Whenever a write in a single processor occurs, all copies of the same block in other caches must be immediately updated to the new value. This is done by broadcasting the new data into the shared bus, hence, all the caches should constantly snoop the bus to be able to detect a write and update their own copy. Write-update protocols worked well for systems with few processors,

nevertheless, as the number of processors increases the communication through a shared bus becomes inefficient to handle the excessive bandwidth demands, leading to their virtual extinction.

• Write-invalidate: With this approach, only a single processor is allowed to write a cache line at any time. Thus, the processor that wishes to write to a cache line must first make sure that its block is the only valid copy among all the cores. Before performing the write, the local processor must check whether or not the cache line is shared with other cores, if so, it sends out messages to invalidate other copies. Subsequent writes from the same processor are streamlined since no check for remote copies is required. Local processor must share (and invalidate if needed) the cache line upon other processor's requests. Finally, the cache block is written back when it gets evicted from the first cache level.

Because coherence protocols are essentially composed of entities (processors, caches and memory controllers) that receive requests (events) from each other and depending on the status of the requested cache line they respond in different ways, a natural way to model them is through Finite State Machines (FSM). In such model, every cache block must be in the state that defines its read/write permissions and better represents its status. After to the arrival of events it may do the transition to another state after performing some specific actions.

The complexity of the protocol increases with the level of detail required to describe the status of the cache block. For example, if the protocol requires to determine whether the block is present on the cache or not, only two states (Invalid and Valid) are needed. If a block is initially in the Invalid state (not present in the cache), a load request from the processor will make the block move to the Valid state

once it is allocated in the cache.

Furthermore, if more detail is needed to know whether other caches have copies of the same block or not, a three-states protocol (Invalid, Exclusive and Shared) is enough. Assuming the Exclusive state has read/write permission and that Shared is a read-only state, this protocol can successfully handle the classic coherence problem. If initially two processors share the same block, both copies must be in the Shared state (S,S). If one of them wishes to write, it must invalidate the other copy and move to the Exclusive state to have read/write permission (E,I). If the second processor now performs a write, the first processor should invalidate its copy and send the latest data to the second one (I,E). Finally, if the first processor wishes to read again the block, there is no need to invalidate the copy, they just share the block (S,S). Note however, that there are combination of states like (S,E) that by definition should never happen and can cause incoherent data.

In write-back systems it is useful to detect if a block has been modified, so the controller can decide whether to write it back to memory or just discard it during a block eviction. That case requires a forth state (Modified). The resulting four-state protocol, known as MESI, its widely known since it was first introduced in 1984. In the subsection 2.1.5 I will explain this protocol in detail.

Coherence protocols require a mechanism able to track the state of each active cache line, the most convenient place to store the state is in the tag array. We can argue that the dirty bit, used to determine if the block has been modified or not, actually is storing the state of the block. Protocols can have different techniques to keep track of the state of each cache block and they can be classified into two big groups: Snooping and directory-based protocols. Here I will explain the main features, advantages and drawbacks of each group.

## 2.1.4.1 Snooping protocols

Snooping protocols where originally conceived for systems with few processors which all their caches are connected to each other through a single shared bus. With this approach every single cache is responsible of tracking the status of all the blocks it contains and of broadcasting to other caches the new data whenever a local modification occurs. Cache controllers must constantly monitor or *snoop* the bus. When other processor broadcasts an update/invalidate message through the bus, the local processor should update/invalidate its own block if it matches with the description of the message. The bus acts as a mutex and avoids race conditions, the processor that gains access to the bus first is allowed to modify the block and other processors must update its copies immediately.

The main drawback of snooping implementations is the poor scalability to systems with many processors, specially in terms of bus bandwidth. For example, if two processors wish to do a write (even on different blocks), one will win the race and the other must wait until the broadcast of the new value is done. After that, the second processor can go ahead and access the bus. In general, if we assume that each processor generates bus transactions at a given rate, the frequency at which the bus must be snooped by other processors is directly proportional to the number of processors in the system. Since each snoop requires at least a local cache lookup, the aggregate bandwidth can quickly become prohibitive.

#### 2.1.4.2 Directory-based protocols

Directory-based protocols are a good alternative to alleviate the bandwidth problem. Since their performance does not rely on broadcasts, they do not need a common shared structure to communicate with other components. Furthermore, that feature makes directory-based protocols more suitable to modern designs like Networks on Chip (NoC's). Unlike snooping protocols where each cache must be aware of all the transactions to update the states, in these protocols a centralized data structure called directory tracks the state of the caches and communicates with them only when it is needed. The information in the directory resides next to each entry of the shared memory and includes the state as well as which caches have copies of the block. In a multi-core system with a shared memory the directory keeps track of the sharing state of the block by attaching to every memory entry a bit vector of size equal to the number of cores, the bits will indicate whether the caches have a copy of the block or not. The storage overhead introduced by the directory structure and bit vector may not scale gracefully for systems with large number of processors[15].

Rather than broadcasting to all the caches, directory-based protocols save bandwidth by sending unicast/multicast messages only to the sharers. On the other hand, the implementation of the directory introduces the problem of indirection. In snooping protocols when two caches needed to communicate, they only had to broadcast the bus; in directory-based protocols, the cache needs to send a message to the directory and if the later determines that it is unable to respond the request (the directory's copy might be out of date due to a write in one cache), it forwards the request to a cache capable of responding. This forced communication with the directory even when it is not really necessary increases the response latency of some memory requests. However, protocols like DiCo\_CMP [32] propose some techniques to avoid indirection, reduce the cache miss access latency and reduce the network traffic.

Another inefficiency of the directory-based protocols occurs when the local cache wants to modify a block shared with many caches. Before proceeding with the store instruction, the local cache must wait for the invalidation acknowledgements from all the sharers, resulting also in higher protocol latencies.

The coherence protocol in the directory is also modelled as a FSM, of course different from the FSM in the caches, with events mainly triggered by the caches requests and states that describe the status of the blocks in the higher level. For example, one state describes that the block is only present in the directory and not in the caches, and other state describes when the block is present in only one cache and probably dirty. In the same way FMSs in top level caches must be synchronized between them, there also should be coherence between the directory and the caches. For example, it is a risk condition when according to the directory, the block is not present in the caches but in reality, it is present and probably modified in one cache.

Future CMP designs with tens or hundred of cores will be constrained by area and power, this constrains make impractical the use of a shared bus and protocols that rely on broadcasts for keeping cache coherence. Apparently, on-chip interconnection networks along with directory-based protocols will dominate in future designs[29].

## 2.1.5 The MESI protocol

The MESI protocol, which is named after the four states it includes, was first presented in 1984 by Papamarcos[27] in the University of Illinois<sup>2</sup>. Due to its simplicity and capability of being used in systems with many cores with good performance, it is usually taken as example for coherence protocols in the literature.

The four states are enough to describe the status of the cache blocks at any time. The Invalid state guarantees no presence of the block in the cache, states Exclusive and Modified guarantee exclusive ownership of the block, and finally, the Shared state guarantees presence but not exclusivity of the block, that is, the block may or may not be the only copy among all the caches. Table 2.1 describes each one of the states.

<sup>&</sup>lt;sup>2</sup>For obvious reasons it it also known as the Illinois protocol.

Table 2.1: Description of states in the MESI protocol.

| State          | Description                                                          |  |

|----------------|----------------------------------------------------------------------|--|

| I              | Invalid: The block is not present in the cache.                      |  |

| S              | Shared: The cache entry is potentially shared with one or more       |  |

|                | caches. The block is clean; it is consistent with the version stored |  |

|                | in the directory.                                                    |  |

| $\overline{E}$ | Exclusive: The cache entry is only present in the local cache.       |  |

|                | The block is clean; it is consistent with the version stored in the  |  |

|                | directory.                                                           |  |

| M              | Modified: The cache entry is only present in the local cache and it  |  |

|                | is dirty. Write-back when the block is evicted from the local cache  |  |

|                | or shared with other caches.                                         |  |

On the other hand, a coherence protocol must react to events that can be originated by a special condition in one of the elements of the cache hierarchy. Depending on the origin of the events, they can be classified as: local reference (due to local CPU's request), remote reference (due to other cache's request) or local capacity eviction (generated inside the local cache). Table 2.2 shows a description of all the events defined in the protocol.

As every FSM, the caches are not just passive entities that receive events and move from one state to another, they are active elements of the protocol that answer to the events depending on the state they are in. A description of the actions they do is shown in table 2.3.

It is worth noting the relationship between the actions done by one cache and the events received from others. For example, if one cache have a read miss, it will issue a GETS request to the interconnection network and other caches will receive that request as a Fwd\_GETS (network read) event.

The last missing thing to complete the description of the protocol is the definition of the transitions between states. Figure 2.3 shows the state diagram of the protocol,

Table 2.2: Description of events in the MESI protocol.

Local reference

| Local reference |                                                            |  |  |  |

|-----------------|------------------------------------------------------------|--|--|--|

| Event           | Description                                                |  |  |  |

| Ifetch          | Local CPU issued an Instruction Fetch request to the       |  |  |  |

|                 | cache.                                                     |  |  |  |

| Load            | Local CPU issued a Load request to the cache.              |  |  |  |

| Store           | Local CPU issued a Store request to the cache.             |  |  |  |

|                 | Remote reference                                           |  |  |  |

| Event           | Description                                                |  |  |  |

| Fwd_GET_INSTR   | Instruction Fetch miss in other cache, local cache must    |  |  |  |

|                 | share the block.                                           |  |  |  |

| Fwd_GETS        | Data Load miss in other cache, local cache must share      |  |  |  |

|                 | the block.                                                 |  |  |  |

| Fwd_GETX        | Store miss in other cache, local cache must invalidate its |  |  |  |

|                 | copy and send the block to the requester.                  |  |  |  |

| INV             | Either the directory or other cache request the local      |  |  |  |

|                 | cache to invalidate its copy of the block.                 |  |  |  |

| Local capacity  |                                                            |  |  |  |

| Event           | Description                                                |  |  |  |

| L1_Replacement  | There is no enough room in the local cache to allocate     |  |  |  |

|                 | a new cache block, it must evict one.                      |  |  |  |

Table 2.3: Description of actions in the MESI protocol.

| Action    | Description                                                    |

|-----------|----------------------------------------------------------------|

| GET_INSTR | Local cache requests an instruction to the directory.          |

| GETS      | Local cache requests a data block without intent to modify it, |

|           | probably because of a load miss.                               |

| GETX      | Local cache requests a data block with intent to modify it,    |

|           | this message implies the invalidation of other copies.         |

| PUTX      | Local cache writes the data back to the shared memory due      |

|           | to eviction of the block.                                      |

the arrows represent the transitions and the labels next to each arrow show the events that can trigger the transition.

In order to better understand the event-action-event relationship and the inter-

Figure 2.3: State diagram of the MESI protocol.

action of the caches in the protocol, lets consider the following example depicted in figure 2.4. Inside figure 2.4, states in red represent the current state of the cache blocks at a given time. Suppose a two-core system with two private caches and a block that is not present in either cache at time 0. At the following time step cache0 receives the Load event from the local CPU, it allocates the requested block, moves to E sends the data to the CPU. Then, at time=2, the CPU performs a store and the cache changes its state to M. When cache1 receives a Load from its local CPU at time=3, it asks cache0 to share the block and both caches change their states to S. Next, the CPU attached to cache1 does a write to the block which invalidates cache0's copy and makes cache1 move to M. Finally, at time=5 cache0 receives a store request, hence it makes cache1 invalidate its copy and send the block to cache0, which moves to M and performs the store.

## 2.1.6 Atomic coherence and race conditions

The coherence protocols explained in this work up to this point have assumed atomic operations, that is, no intervening operations can occur while other operation

Figure 2.4: Example of the operation of the MESI protocol between two caches.

is in progress. For example at time=1 in figure 2.4 cache0 received the Load request, it allocated the block and did a transition from I to E as a single atomic action. However, the reality is not that simple and many things must happen before a transition can finish. In a more realistic exercise, what could happen after cache0 receives the Load request is:

- 1. Cache issues an GETS request to the directory and waits until the directory answers with data.

- 2. The directory receives the GETS request from cache0, supposing the directory does not contain the block, it sends another request to lower memory levels and waits until the block is supplied.

- 3. The directory receives the block from lower memory levels and forwards it to cache0.

- 4. Cacheo receives the requested block, finishes the transition to E and satisfies the local CPU's needs.

If in addition to all the time waiting we also consider the intrinsic network and buffer delays, the time spent from the beginning of the transition to its end is even bigger. This latency is too large to assume that no other events will be triggered before the transition's end. For example, while waiting for the data, the CPU might wish to do a write into the same block, and moments later cache1 might ask cache0 to share the block that has not been loaded and written yet.

Considering non-atomic transitions makes the protocol more real but increases its complexity because it should handle many probable race conditions. Designing for races is hard. Although states dedicated to handle race conditions may represent a considerable proportion of all states, they only represent a small fraction of all

observed transitions in commercial workloads[39]. Because of their relative in infrequency, race conditions have little impact on performance, but they impose design complexity and verification challenges.

## 2.1.7 Survey on cache coherence verification techniques

The coherence protocols verification became an area of interest for researchers as the current systems incorporate more cores and other components in a shared memory scheme. Early coherence protocols based on bus-snooping connected few modules through a time shared bus and hence its low complexity made the verification task relatively easy. Nevertheless, the large amount of cores present in modern CMP's along with the need of higher data bandwidth, have motivated the designers to leave aside the time-shared bus and look towards a more reliable interconnection network. Although more complex due to their intrinsic properties, directory based protocols are a better choice for current (and future) CMPs than snooping protocols.

The more modules coordinated by the protocol, the more likely it is to have corner cases as a result of a rare sequence of events, Then, it is crucial to add auxiliary states to correctly handle the corner cases and avoid the protocol to crash. Although these auxiliary states rarely are visited on normal operation, they do significantly increment the complexity of the protocol and therefore, its verification becomes a challenging problem.

The goal of verification is to ensure that a coherence protocol satisfies all the required specifications, in particular, there are three basic properties to verify that Pong *et al.*[30] define as:

• Data consistency. On each load, the protocol should always return the latest stored value. Consistency is enforced by allowing only one store in progress for each time at any time.

- Complete protocol specification. Protocol incompleteness occurs when possible events or state transitions have been omitted (i.e. a component receives a not specified message in its current state). Since those situations are not specified, the subsequent behaviour of the protocol is unpredictable.

- Absence of deadlock and livelock. A deadlock occurs when the protocol enters a state which does not leave because is waiting for an event that never happens. The protocol is blocked and cannot service other requests until it leaves that state. On the other hand, a livelock occurs when the protocol gets stuck in a loop of transitions without making any useful progress.

Informal protocol verification techniques are based on time-consuming and errorprone procedures. As the complexity of coherence protocols increases, it becomes harder to verify them by simply relying on human reasoning. Simulations are conceptually simple but they only guarantee that the protocol works for a particular sequence of events, they would need to indefinitely run a random sequence to completely verify the protocol.

To successfully verify systems of arbitrary complexity, the biggest issue most of verification techniques must deal with is the *state explosion problem*. In these techniques the protocol is characterized by its state and the verification is based on searching all reachable states exhaustively. Hence, the amount of memory required to manipulate the state information and the verification time grow very fast with the number of processors and the complexity of the protocol mechanisms. With the goal of reducing the size of the state space, the research community has proposed several methods that exploit different features of the cache-based systems like homogeneities, regularities and symmetries.

In the following sections I present a summary of the most relevant and accepted

coherence protocol verification techniques.

### 2.1.7.1 Reachability analysis and state enumeration

The global state of the system is defined as the composition of the states of all its components and the correctness of the protocol is verified on the set of reachable global states. For a given global state, reachable states are found by exhaustively exploring all the possible interactions between entities. If one state fails to preserve the correctness of the protocol it is classified as erroneous, otherwise is permissible.

Conventionally in an exhaustive search algorithm, for each state all its reachable states are added to the working list even if some of them may have been visited previously. Furthermore, a large number of previously visited states are also expanded during the state expansion procedure. This makes the state space grow exponentially with the number of components and the complexity of the protocol. A simple solution is to add a history list that contains all the previously visited states and if the current state is present on the history list it is not expanded or added to the working list.

Even with these assumptions the number of global states is still unmanageable for current coherence protocols, and on the other hand, the agreement between cache states and data copies must also be verified, which means that data values must be modelled along with state transitions.

Several variations have been proposed to overcome the inefficiency and large memory requirement of state enumeration methods, most of them focus on keeping track of only the states on the current expansion path, encoding the state information and using hash tables. However, those techniques are not totally accurate because they do not detect livelocks and several states map to the same hash value<sup>3</sup>[30].

<sup>&</sup>lt;sup>3</sup>An ideal hash function mapping each global state to a unique hash value is not practical.

Other techniques like the Mur $\phi$  Verification System[11, 10] exploit the system symmetries. Mur $\phi$  is composed by a compiler and a high-level programming language for the description of finite-state asynchronous concurrent systems and has been extensively used to verify coherence and communication protocols. A Mur $\phi$  program consists of four parts: declarations, transition rules, start state generation rules, and invariant descriptions (Boolean conditions that have to be true in every reachable state). The compiler generates a C++ program from the FSM which exhaustively generates the reachable states, checks for error conditions and deadlocks.

The Mur $\phi$  verifier works by explicitly generating all the reachable states and storing them in a hash table, it also implements some state reduction techniques such as symmetry reduction, exploitation of reversible rules, and verification of systems with varying numbers of replicated components[20]. However, the state explosion problem is still a big issue, it was shown that even for fairly small models of 3 or 4 processors the reduced state space size is above 107 states [30]. Furthermore, Mur $\phi$  does not guarantee total correctness of the protocol and their developers recommend its use only as a debugging tool.

#### 2.1.7.2 Model checking

A temporal logic is an extension of predicate logic with additional tense operators for expressing properties evolving with time. Model checking is a formal verification technique that expresses properties of the protocol as formulas in temporal logic. In general, after construction of the state graph of the protocol model, the properties specified as temporal logic formulas are evaluated on the graph.

The strength of this technique is based on the expressiveness of temporal logic, which can handle arbitrary temporal formulas, representing both safety (data consistency) and liveness (livelock and deadlock free) properties. However, since model

checking takes the state graph as a model, it also suffers from the state space explosion problem.

Symbolic model checking is a technique to perform model checking without explicitly representing the state graph [23]. It saves great amount of memory by representing the global state graph by Ordered Binary Decision Diagrams (OBDDs); additionally, it composes finite state modules to build the transition relations among global states. As a consequence, unlike the state enumeration methods, the reachable global states are not produced one by one.

Emmerson and Sistla [13] extended the model checking technique by exploiting symmetry. Since states that are permutations of each other are lumped into a single canonical state, the the OBDD size and the state space after transformation can be significantly reduced.

### 2.1.7.3 Symbolic state modelling

Two states are equivalent if they are symmetrically identical in methods with symmetry extension. For example, in a system with three caches, the tuples (shared, shared, invalid) and (shared, invalid, shared) represent a similar condition of the system and hence, should be handled in the same way. In regards of verification of the system, a set of equivalent states can be replaced by one canonical state called symbolic state.

The symbolic state modelling searches the state space exhaustively just like in the traditional state enumeration methods. The difference is that it uses symbolic states and thus, the system is represented by a symbolic state model (SSM). The SSM method groups caches in the same state into a class and the number of caches in the class is symbolically represented by a repetition constructor, in such way, all the equivalent states are pruned out from the reachable states and the states explosion problem is reduced. The abstraction in this model is much more powerful than the symmetric relations obtained from symmetry alone.

Pong et al.[29] discard redundant states under the premise that the protocol correctness in not dependent on the exact number of cached copies, symbolic states only need to keep track of whether the caches have 0, 1 or multiple copies. With this assumption the verification process is independent of the number of caches and consequently is reliable.

### 2.1.7.4 Dynamic verification

Dynamic or runtime verification is not a new concept and avoids the complexity of traditional formal verification techniques, such as model checking and theorem proving. It has been applied to cache coherence to detect at runtime and recover from errors caused by manufacturing faults, soft errors, and design mistakes[6]. However, the existing coherence checkers are susceptible to errors and costly to implement.

Rodrigues et al. present a centralized mechanism for dynamic verification of cache coherency in snoopy bus multicore systems[31]. They propose the addition of a module called Sentry Core (SC) which they claim to be fault-free. The SC has access to the shared bus, monitors all bus transactions and since it is aware of the coherence protocol, by observing the current state of the cache line it knows the next state for any cache line. They show that implementing the SC will incur into a performance degradation of less than 2% in the worst case.

Meixner and Sorin [24] detail the implementation of a framework for the cache coherency dynamic verification in the SPARCv9 architecture. They constructed the Cache Coherence checker around the notion of an epoch, which is a time interval when a processor has permission to read or read and write a given cache block. The rules they used to determine coherence violations are 1) reads and writes are

only performed during appropriate epochs, 2) read-write epochs do not overlap other epochs temporally, and 3) the data value of a block at the beginning of every epoch is equal to the data value at the end of the most recent read-write epoch.

## 2.1.7.5 Other techniques

As mentioned before, great part of the complexity of current coherence protocols is caused by the race conditions that they must handle. Therefore, instead of trying to improve verification techniques, Vantrease *et al.*[39] propose to make the verification feasible by simplifying the protocol and eliminating the race condition.

Mutexes are a natural way to support mutual exclusion in the coherence protocol, i.e. the block's coherence state may not be altered until the mutex has been obtained. However, obtaining access to the mutex is an operation that requires time and hence, is one of the main race condition sources. Vantrease *et al.* propose to use on-chip silicon photonics and implement very low latency mutex which will support simple atomic operations. They advocate a return to atomic protocols and show that an atomic implementation of the protocol is much simpler while imposing less than a 2% performance penalty.

The last coherence protocol verification technique covered in this document is the Random Traffic Generation. It consist on stressing the system with the constant injection of random messages and checking if the response of the system is the right one or not. Every time a new request is injected to the system its message type, expected response and maximum round trip time are registered. The tester (located in the CPU's side of the hierarchy) is constantly checking the status of all injected packets. When a response from one of the originally injected messages gets into the tester, it is checked and compared with the previously registered data. If the received data is the same as expected the transaction is said to be successful and

its data is discarded, otherwise a data consistency error is launched. Furthermore, if the tester detects that one of the injected messages has not came back and exceeds the maximum allowed round trip time, the test stops and a possible deadlock error is displayed.

Assuming a ideal random generator a random test sequence must be run indefinitely in order to enter all reachable states. Although it might be more time consuming than others, this technique is able to find coherence problems, data inconsistencies and deadlock and livelock conditions. Also, the random traffic generation is not exposed to the state explosion problem, the amount of memory and the time spent on each test increase linearly with the number of caches simulated and messages injected to the system respectively. Random traffic generators may stress, but not exhaust, potential race combinations.

### 2.2 Statistical sampling and confidence intervals

In statistics, the goal of sampling is to have an estimate of a population parameter without the need of measuring every element of it. The point estimators involve the use of simple data to calculate a single value and which serves as a "guess" of an unknown population parameters. Some of the most commonly used methods for point estimation include the method of moments and the median-unbiased estimator among others. The discussion and description of point estimators are beyond the scope of this thesis, however it is illustrating to compare them with the interval estimators.

In contrast to point estimation which uses only a single number, interval estimation calculates an interval of probable values of an unknown population parameter. In other words, it outputs an interval in which the parameter of interest is more likely to be and in some cases it also calculates the likelihood of the parameter to be inside the parameter. This chapter introduces and explains the statistical principles of the confidence intervals which will serve in further chapters as the basis of the statistical sampling simulation techniques.

## 2.2.1 Basic properties of confidence intervals

A given confidence interval is always calculated by setting a confidence level before, which is a measurement of the degree confidence of the interval. A confidence level of 95% implies that 95% of the samples of the parameter under interest fall within the interval and only 5% of the samples would be above or below the confidence interval. In other words, the bigger the confidence level the more sure we can be that the estimated population parameter is within the interval. The most common confidence levels used in statistics applications are 90%, 95% and 99%.

Both, the confidence level and confidence interval express the accuracy of the estimation. With a high confidence level, if the resulting interval is small we can argue that the parameter estimation is fairly accurate, however if the interval is big there is uncertainty in the parameter estimation.

In order to introduce the concepts and properties of the confidence intervals lets do first two simple and somewhat unrealistic assumptions:

- The population is normally distributed.

- The population standard deviation  $\sigma$  is known.

Let  $x_1, x_2, \ldots, x_n$  be the random samples of a population with normal distribution, mean  $\mu$  and standard deviation  $\sigma$ . It can be shown that the sample mean  $\bar{x}$  has a normal distribution with expected value  $\mu$  and standard deviation  $\sigma/\sqrt{n}$  [9]. The standardization of  $\bar{x}$  produces the variable

$$Z = \frac{\bar{x} - \mu}{\sigma / \sqrt{n}} \tag{2.9}$$