# MULTILEVEL CONVERTER TOPOLOGIES FOR UTILITY SCALE SOLAR PHOTOVOLTAIC POWER SYSTEMS

#### A Dissertation

by

#### SOMASUNDARAM ESSAKIAPPAN

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

Chair of Committee, Prasad Enjeti Committee Members, Robert S. Balog

Shankar P. Bhattacharyya

Won-jong Kim

Head of Department, Chanan Singh

May 2014

Major Subject: Electrical Engineering

Copyright 2014 Somasundaram Essakiappan

#### **ABSTRACT**

Renewable energy technologies have been growing in their installed capacity rapidly over the past few years. This growth in solar, wind and other technologies is fueled by state incentives, renewable energy mandates, increased fossil fuel prices and environmental consciousness. Utility scale systems form a substantial portion of electricity capacity addition in modern times. This sets the stage for research activity to explore new efficient, compact and alternative power electronic topologies to integrate sources like photovoltaics (PV) to the utility grid, some of which are multilevel topologies.

Multilevel topologies allow for use of lower voltage semiconductor devices than two-level converters. They also produce lower distortion output voltage waveforms. This dissertation proposes a cascaded multilevel converter with medium frequency AC link which reduces the size of DC bus capacitor and also eliminates power imbalance between the three phases. A control strategy which modulates the output voltage magnitude and phase angle of the inverter cells is proposed. This improves differential power processing amongst cells while keeping the voltage and current ratings of the devices low.

A battery energy storage system for the multilevel PV converter has also been proposed. Renewable technologies such as PV and wind suffer from varying degrees of intermittency, depending on the geographical location. With increased installation of these sources, management of intermittency is critical to the stability of the grid. The

proposed battery system is rated at 10% of the plant it is designed to support. Energy is stored and extracted by means of a bidirectional DC-DC converter connected to the PV DC bus. Different battery chemistries available for this application are also discussed.

In this dissertation, the analyses of common mode voltages and currents in various PV topologies are detailed. The grid integration of PV power employs a combination of pulse width modulation (PWM) DC-DC converters and inverters. Due to their fast switching nature a common mode voltage is generated with respect to the ground, inducing a circulating current through the ground capacitance. Common mode voltages lead to increased voltage stress, electromagnetic interference and malfunctioning of ground fault protection systems. Common mode voltages and currents present in high and low power PV systems are analyzed and mitigation strategies such as common mode filter and transformer shielding are proposed to minimize them.

#### **ACKNOWLEDGEMENTS**

I would like to thank my advisor Dr. Prasad Enjeti for his guidance, patience and support throughout my graduate study. His insight helped me in every step of the way, both in my research work at Texas A&M and also in building a career in power electronics and building a professional network. I would also like to thank my dissertation committee members, Dr. Robert S. Balog, Dr. Shankar P. Bhattacharyya and Dr. Won-jong Kim for their insight and guidance. I also thank Dr. Shehab Ahmed and the Qatar National Research Foundation for their support. The Graduate Office of the Department of Electrical and Computer Engineering runs a well-oiled machine and it helped me immensely to navigate through graduate school; for that I thank them, especially Tammy Carda and Jeanie Marshall. I should also acknowledge and thank my professors and teachers from my earlier years in undergraduate university and high school for providing the foundation necessary to accomplish this work.

A large portion of education in graduate school is through discussions, debates and chats over coffees. I would like to acknowledge all current and past students in the research group and in Texas A&M power electronics division, without whom my work would have been infinitely more difficult. I thank (in no particular order) Harish Krishnamoorthy, Mehran Mirjafari, Souhib Harb, Haiyu Zhang, Mohammad Shadmand, Maja Harfman-Todorovic, Mirunalini Chellappan, Anand Balakrishnan, Harsha Patibantla, Joshua Hawke, Vivek Sundaram, Poornima Mazumdar, Dibyendu Rana, Pawan Garg, Jorge Ramos, Jose Sandoval, Michael Daniel, Bahaa Hafez, Ahmed Morsy,

Yateendra Deshpande, Mahshid Amirabadi, Siavash Pakdelian, Hamid Keyhani, Taeyong Kang, Harsh Juneja and all the others in the EPPE research division for making learning and life easier.

I would like to thank my friends Naresh Narayanan, Karthik Raviprakash, Arun Palaniappan, Karthik Tamilarasan, Vijay Sundaram, Shriram Jagannathan for their support and not allowing day-to-day problems interfere with my work.

Finally, I thank my family for playing no small part in my successes - past and future, for believing in me and supporting me; also for being patient when I missed weekly phone calls.

# **TABLE OF CONTENTS**

|      |       | I                                                                | Page |

|------|-------|------------------------------------------------------------------|------|

| ABST | 'RAC' | Γ                                                                | ii   |

| ACKN | NOWI  | LEDGEMENTS                                                       | iv   |

|      |       |                                                                  |      |

| TABL | LE OF | CONTENTS                                                         | vi   |

| LIST | OF FI | GURES                                                            | ix   |

| LIST | OF TA | ABLES                                                            | xvi  |

| 1.   | INTR  | ODUCTION                                                         | 1    |

|      | 1.1.  | Growth of Renewable Power and Photovoltaic Power Installations   | 1    |

|      | 1.2.  | Characteristics of Solar PV Cells and Arrays                     |      |

|      | 1.3.  | Commercial and Utility Scale Solar PV Integration                |      |

|      | 1.4.  | Literature Review                                                |      |

|      |       | 1.4.1. PV Topologies: Two-level Inverter                         | 8    |

|      |       | 1.4.2. PV Multilevel Topologies: Diode-clamped                   |      |

|      |       | 1.4.3. PV Multilevel Topologies: Modular Multilevel              |      |

|      |       | 1.4.4. PV Multilevel Control Techniques                          |      |

|      |       | 1.4.5. PV Battery Energy Storage                                 |      |

|      | 1.5.  | Research Objective                                               |      |

|      | 1.6.  | Outline of Dissertation                                          | 19   |

| 2.   | MED   | IUM FREQUENCY AC LINK CASCADED MULTILEVEL                        |      |

|      | INVE  | ERTER AND ZONAL POWER BALANCER                                   | 21   |

|      | 2.1.  | Introduction                                                     | 21   |

|      | 2.2.  |                                                                  |      |

|      |       | 2.2.1. Zonal Power Balancer under Partial Shading                |      |

|      |       | 2.2.2. DC-AC-AC Converter                                        |      |

|      |       | 2.2.3. Switching Function Generation in Medium Frequency AC Link |      |

|      |       | Converter                                                        | 28   |

|      |       | 2.2.4. Transformer Design                                        |      |

|      |       | 2.2.5. Input Filter Design                                       | 38   |

|      | 2.3.  | Simulation Results                                               |      |

|      | 2.4.  | Experimental Results                                             |      |

|      | 2.5.  | Conclusion                                                       | 46   |

| 3. | CON  | TROL STRATEGY FOR CASCADED MULTILEVEL                            |      |

|----|------|------------------------------------------------------------------|------|

|    | INVI | ERTERS UNDER ASYMMETRIC INSOLATION                               | 47   |

|    | 3.1. | Introduction                                                     | 47   |

|    | 3.2. | Control Theory                                                   |      |

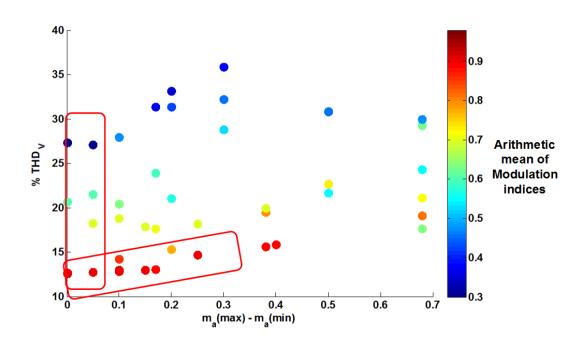

|    |      | 3.2.1. Effect of Modulation Index Control on Output Voltage THD  |      |

|    | 3.3. | Parallel and Cascaded Inverters Control                          |      |

|    | 3.4. | Proposed Control Strategy by Continuous Monitoring               |      |

|    | 3.5. | Multilevel Inverter Modeling and Analysis                        |      |

|    |      | 3.5.1. Average Model of Cascaded Multilevel Inverter             |      |

|    |      | 3.5.2. Output Power – Phase Angle Control Stability Analysis     | 60   |

|    | 3.6. | Operation of Control Algorithm under Changing Insolation         |      |

|    |      | Conditions                                                       |      |

|    | 3.7. | Simulation Results                                               |      |

|    | 3.8. | Conclusion                                                       | 71   |

| 4. | UTII | LITY SCALE BATTERY ENERGY STORAGE SYSTEM FOR                     |      |

|    | MUL  | TILEVEL AC LINK PV INVERTER                                      | 73   |

|    | 4.1. | Introduction                                                     | 73   |

|    | 4.2. | Battery Energy Storage System – Analysis of System Rating        |      |

|    | 4.3. | Proposed Battery Energy Storage System Architecture              |      |

|    |      | 4.3.1. Battery System                                            |      |

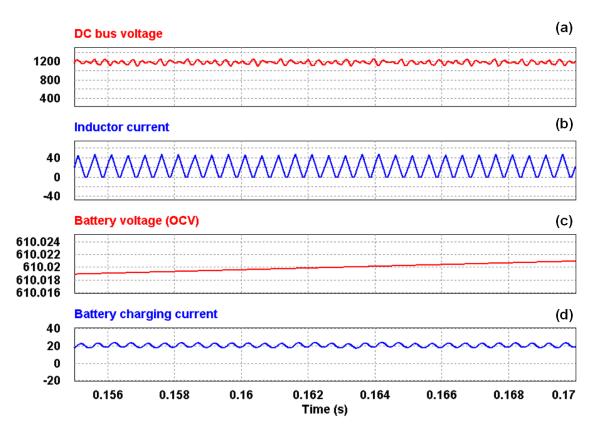

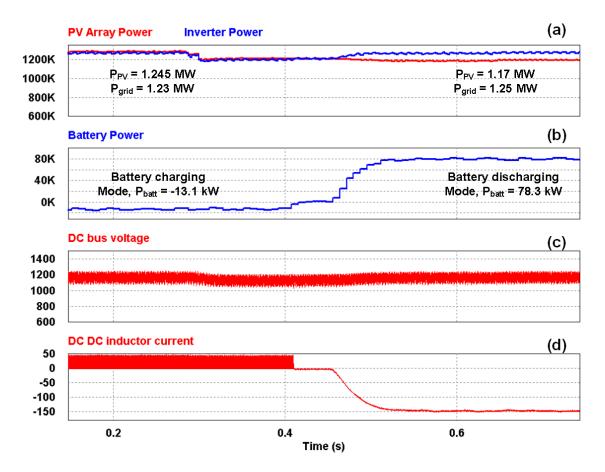

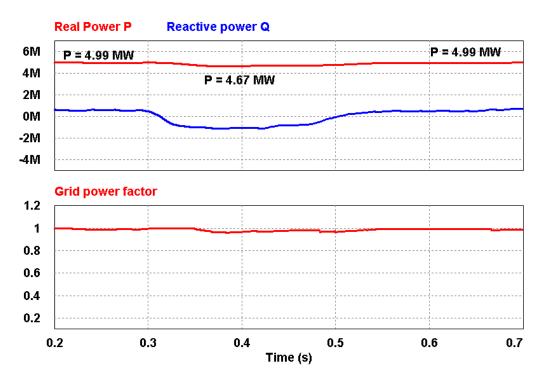

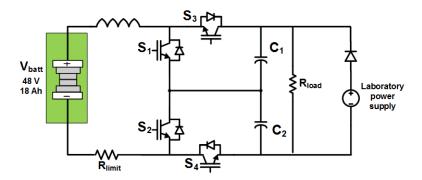

|    |      | 4.3.2. Bidirectional DC-DC Converter: Charging Mode Operation    | 83   |

|    |      | 4.3.3. Bidirectional DC-DC Converter: Discharging Mode Operation | 85   |

|    |      | 4.3.4. DC-DC Converter Modeling                                  | 90   |

|    | 4.4. | Design Example for Utility Scale BESS                            |      |

|    | 4.5. | DC-DC Bidirectional Converter Design and Efficiency Analysis     | 94   |

|    |      | 4.5.1. Inductor Design                                           | 94   |

|    |      | 4.5.2. Capacitor Design                                          | 95   |

|    |      | 4.5.3. Device Ratings                                            |      |

|    |      | 4.5.4. Loss Estimation and Efficiency Analysis                   |      |

|    | 4.6. | Simulation Results                                               |      |

|    | 4.7. | Experimental Results                                             |      |

|    | 4.8. | Summary and Conclusion                                           | .104 |

| 5.  | ANA  | ANALYSIS AND MITIGATION OF COMMON MODE VOLTAGES IN             |     |  |  |  |

|-----|------|----------------------------------------------------------------|-----|--|--|--|

|     | РНО  | TOVOLTAIC POWER SYSTEMS                                        | 106 |  |  |  |

|     | 5.1. | Introduction                                                   | 106 |  |  |  |

|     | 5.2. | Common Mode Capacitances in Photovoltaic Systems               | 106 |  |  |  |

|     | 5.3. | Distributed Ground Capacitances in a Photovoltaic Power System | 108 |  |  |  |

|     | 5.4. | Common Mode Equivalent Circuits of PV System Topologies        | 114 |  |  |  |

|     | 5.5. | Analysis of a Medium Voltage Multi-level Utility Photovoltaic  |     |  |  |  |

|     |      | System                                                         | 123 |  |  |  |

|     | 5.6. | Mitigation of Common Mode Voltages in Multi-level Utility PV   |     |  |  |  |

|     |      | System                                                         | 129 |  |  |  |

|     | 5.7. |                                                                |     |  |  |  |

| 6.  | CON  | ICLUSION AND FUTURE WORK                                       | 135 |  |  |  |

|     | 6.1. | Summary                                                        | 135 |  |  |  |

|     | 6.2. | Future Work                                                    | 136 |  |  |  |

| REF | EREN | CES                                                            | 138 |  |  |  |

# LIST OF FIGURES

|           | ·<br>-                                                                                                      | Page |

|-----------|-------------------------------------------------------------------------------------------------------------|------|

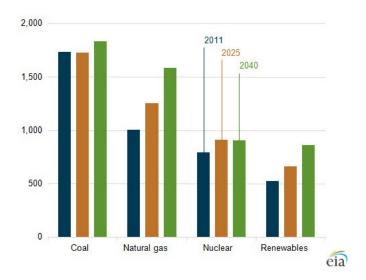

| Fig. 1.1: | Electricity generation by fuel, 2011, 2025 and 2040 (billion kWh) Source: EIA (May 2013) [1]                | 2    |

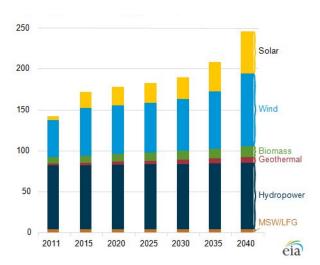

| Fig. 1.2: | Renewable energy sources by installed capacity, 2011-2040 (GW) Source: EIA (May 2013) [1]                   | 2    |

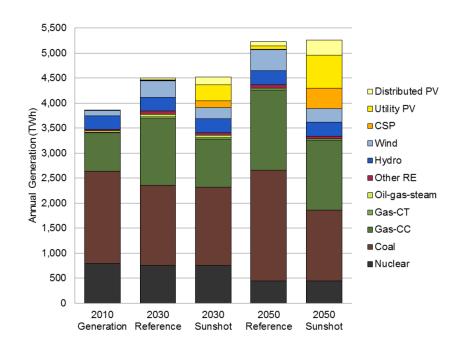

| Fig. 1.3: | U.S. PV installations by market segment, 2030 & 2050 forecasts.  Source: NREL [4]                           | 3    |

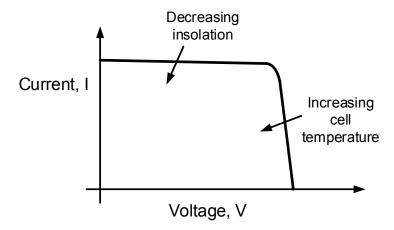

| Fig. 1.4: | The voltage-current characteristics of solar photovoltaic cell                                              | 5    |

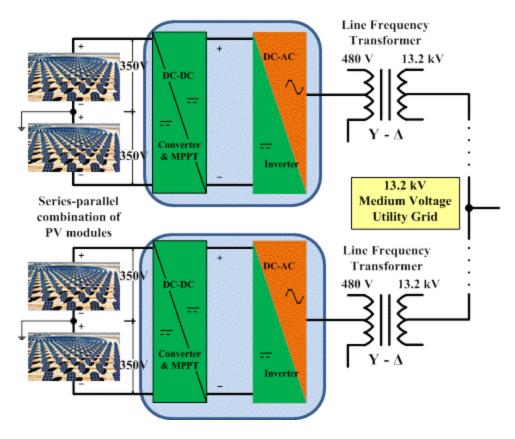

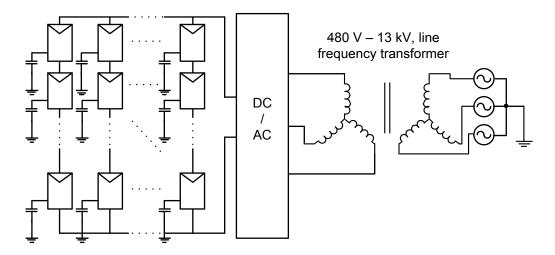

| Fig. 1.5: | Conventional utility scale PV plant interfaced to medium voltage electric grid                              | 9    |

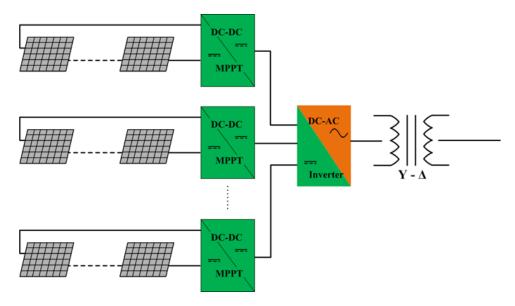

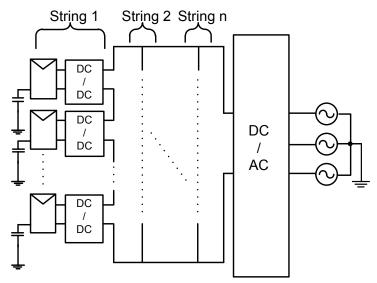

| Fig. 1.6: | String level MPPT converters reduce effects of partial shading and increase energy yield                    | 10   |

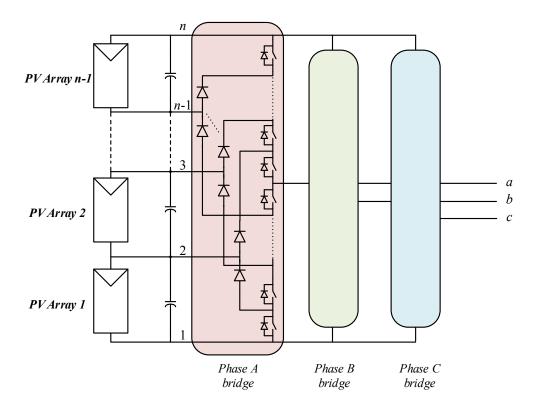

| Fig. 1.7: | Diode clamped <i>n</i> level inverter with individual array MPPT control                                    | 12   |

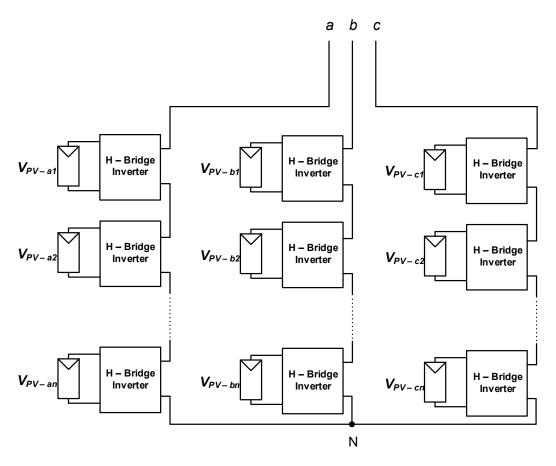

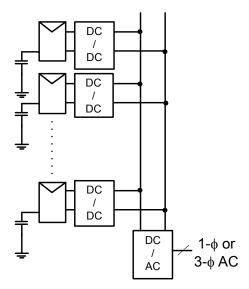

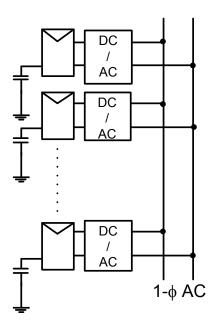

| Fig. 1.8: | Modular cascaded multilevel H-bridge topology for three phase grid integration                              | 13   |

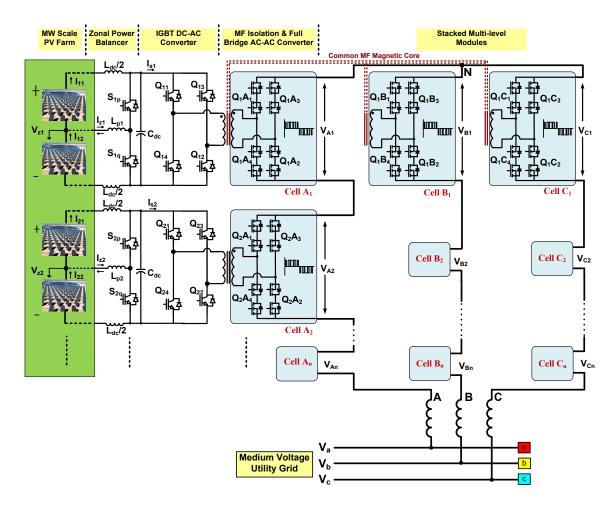

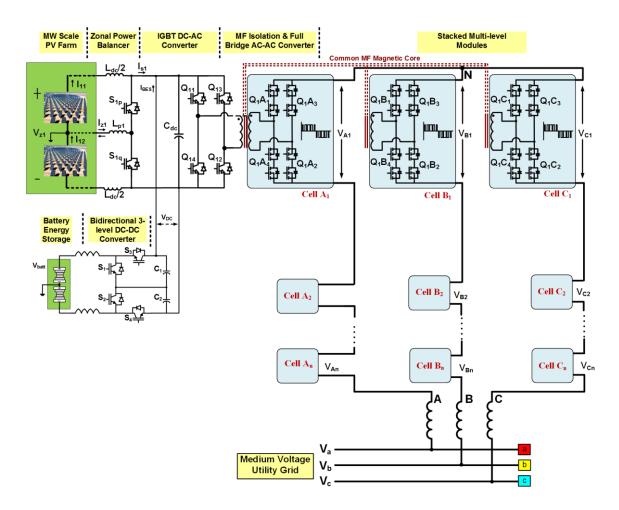

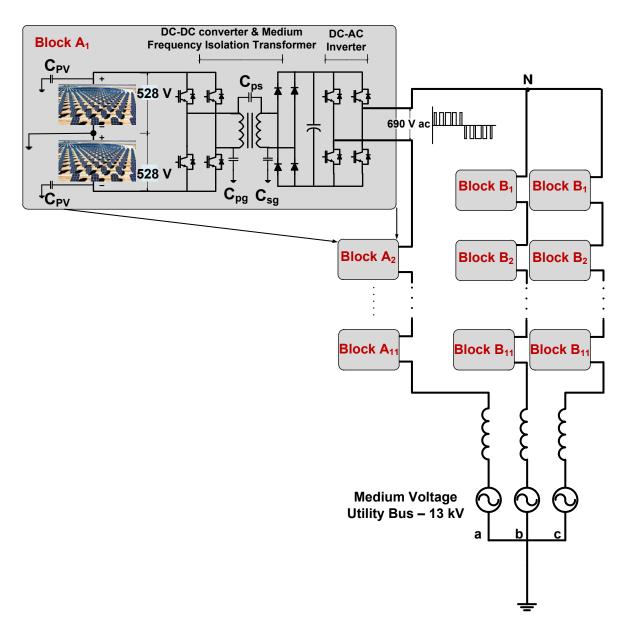

| Fig. 2.1: | Proposed Multi-level DC-AC-AC Converter with MF isolation and Zonal MPPT                                    | 23   |

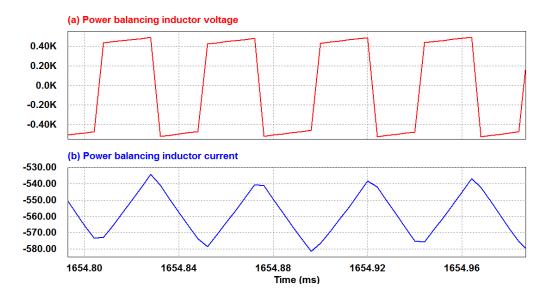

| Fig. 2.2: | (a) Voltage and (b) Current of power balancing inductor                                                     | 26   |

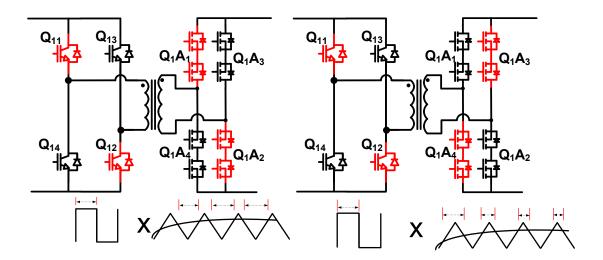

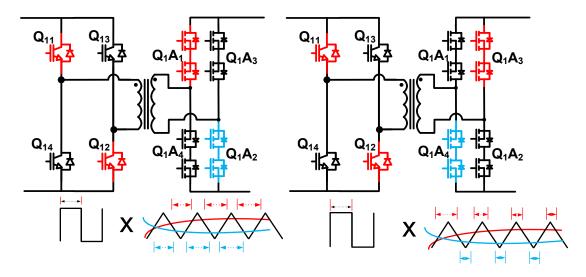

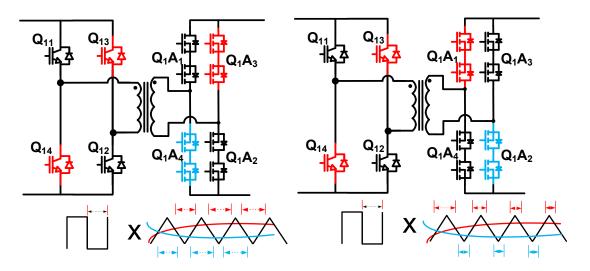

| Fig. 2.3: | PWM switching function generation using bipolar PWM technique for positive square wave voltage              | 30   |

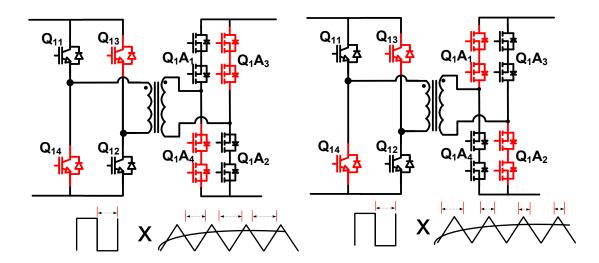

| Fig. 2.4: | PWM switching function generation using bipolar PWM technique for negative square wave voltage              | 31   |

| Fig. 2.5: | PWM switching function generation using unipolar PWM technique for positive square wave voltage             | 33   |

| Fig. 2.6: | PWM switching function generation using unipolar PWM technique for negative square wave voltage             | 33   |

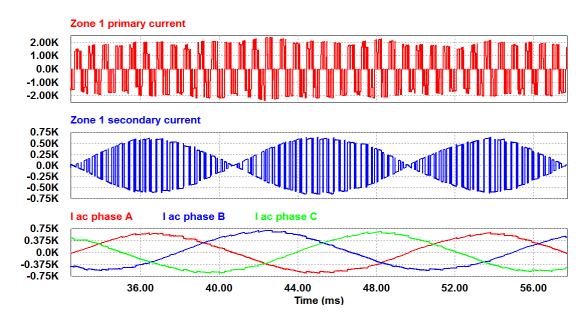

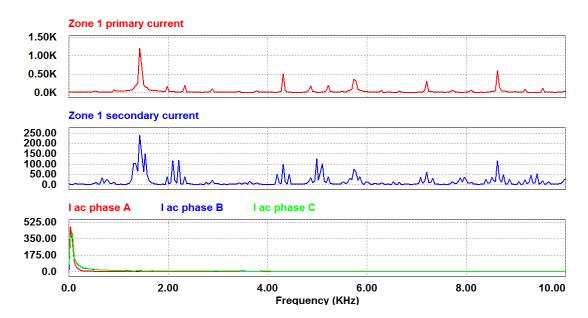

| Fig. 2.7: | Zone 1 transformer primary current, phase-A secondary current and balanced 3-phase load current – waveforms | 36   |

|            |                                                                                                                                                                                                                                                | Page |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 2.8:  | Zone 1 transformer primary current, phase-A secondary current and balanced 3-phase load current - frequency spectrum                                                                                                                           | 36   |

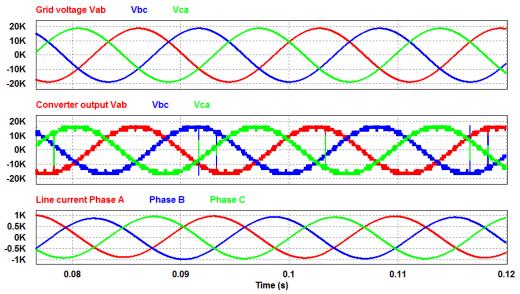

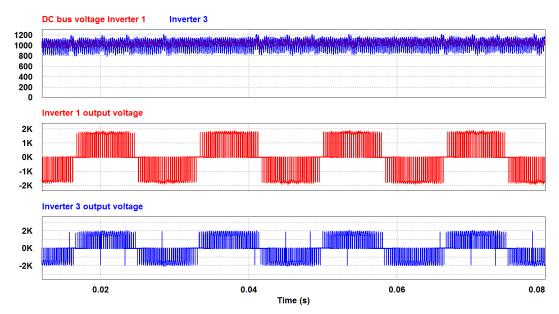

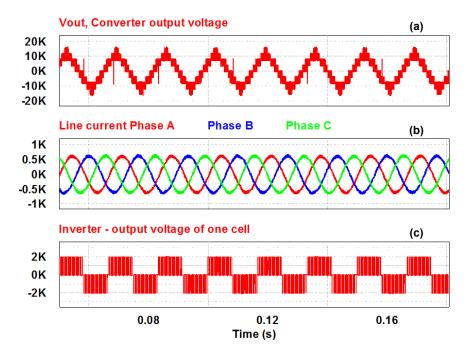

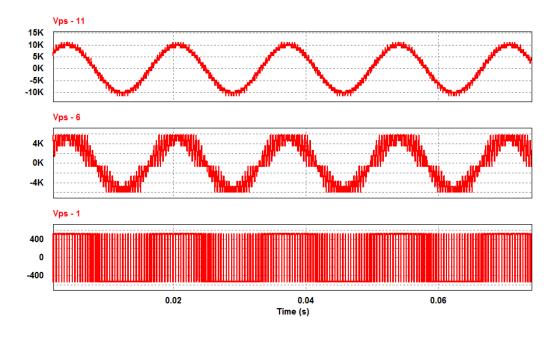

| Fig. 2.9:  | Line currents, converter output voltages and the grid voltage in a multilevel PV system under uniform full insolation                                                                                                                          | 40   |

| Fig. 2.10: | DC bus capacitor voltages in inverter cells 1 and 3 and output voltage of inverter cells 1 and 3, phase A                                                                                                                                      | 40   |

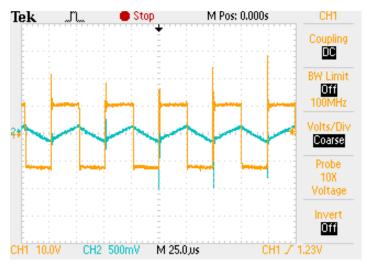

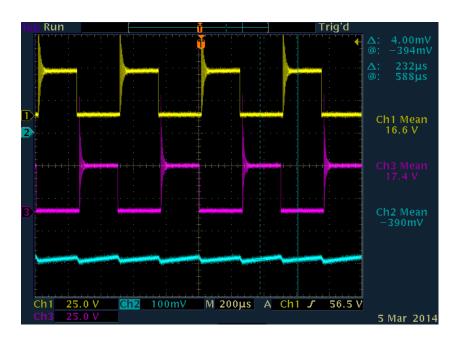

| Fig. 2.11: | Power balancing inductor voltage (Ch 1: 1 div = 10V) and current (Ch 2: 1div = 5A) waveforms under steady state operation. Inductor carries the difference between currents through the two sources.                                           |      |

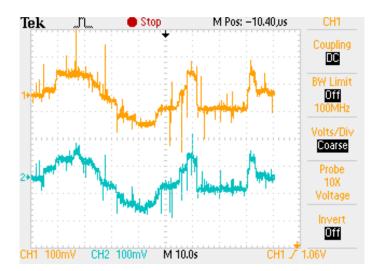

| Fig. 2.12: | Reference tracking performance of the power balancer circuit. Ch 2 is the current reference, the difference in source currents and Ch 1 shows the actual inductor current (1 div = 5A)                                                         | 42   |

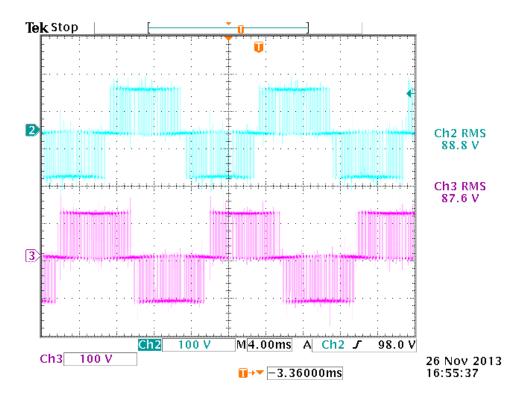

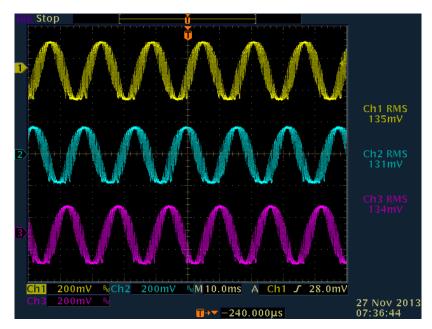

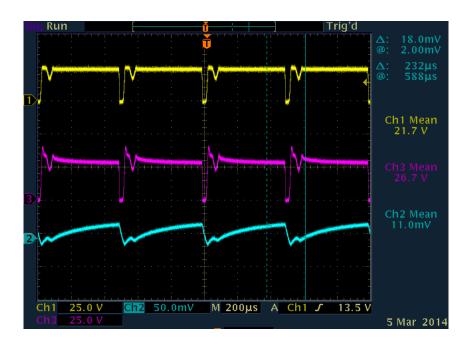

| Fig. 2.13: | Line-line output voltages in one cell of multilevel inverter – $V_{AB}$ (channel 2) and $V_{BC}$ (channel 3)                                                                                                                                   | 44   |

| Fig. 2.14: | Three phase balanced line currents $I_A$ (channel 1), $I_B$ (channel 2) and $I_C$ (channel 3) in one cell of multilevel inverter operation                                                                                                     | 45   |

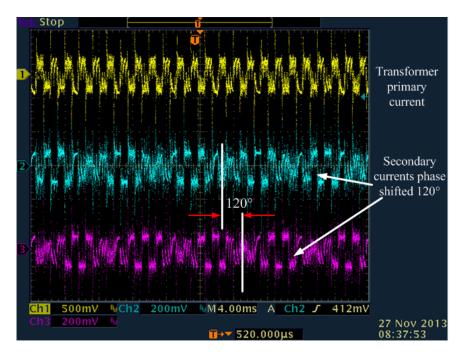

| Fig. 2.15: | Medium frequency transformer primary current (Channel 1), secondary current phase B (Channel 2), phase C (Channel 3). The 120° phase shift in the 120 Hz components in the three phases leads to cancellation of these currents in the primary | 45   |

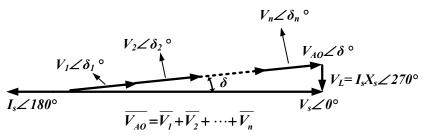

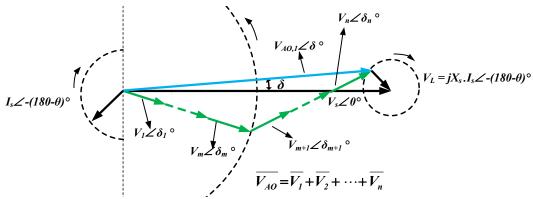

| Fig. 3.1:  | Voltage vectors in a multilevel series connected inverters with fully illuminated PV arrays. The vectors are in phase and of equal magnitude. $V_L$ is voltage across line impedance.                                                          | 50   |

| Fig. 3.2:  | General solution for voltage vectors in a multilevel series connected inverters with <i>m</i> shaded inverters.                                                                                                                                | 51   |

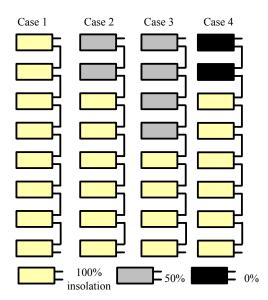

| Fig. 3.3:  | Four cases of insolation pattern for the eight zones in 10 MW design example                                                                                                                                                                   | 51   |

| Fig. 3.4:  | Multilevel inverter output voltage THD for unequal modulation indices amongst cascaded cells                                                                                                                                                   | 53   |

|            |                                                                                                                                                                                                    | Page       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

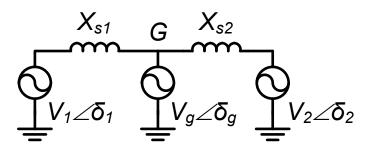

| Fig. 3.5:  | One-line diagram of a parallel-connected two inverter system interfaced with infinite bus G. The phase angle $\delta_g$ of bus G is usually taken as the reference bus, $0^{\circ}$                | 54         |

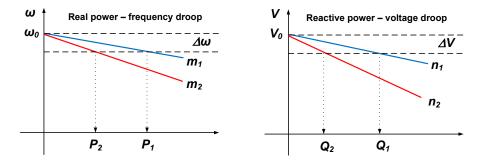

| Fig. 3.6:  | Frequency and voltage droops used in parallel connected inverters for effective power sharing, based on the ratings of the inverters [41, 42]                                                      | 55         |

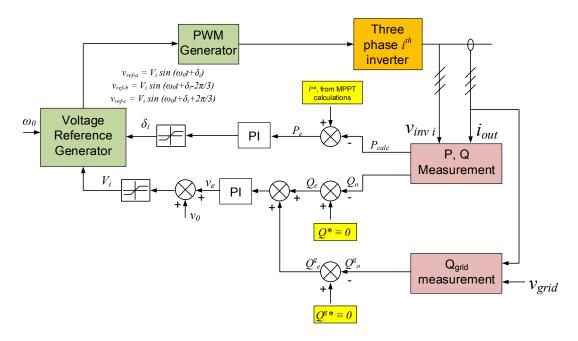

| Fig. 3.7:  | Control algorithm for the operation of one inverter. Phase angle $\delta_i$ and modulation index ma of sinusoidal modulating signals are varied based on real power $P_o$ and reactive power $Q_o$ | 56         |

| Fig. 3.8:  | Three cell cascaded multilevel inverter for analyzing average and small signal model                                                                                                               | 58         |

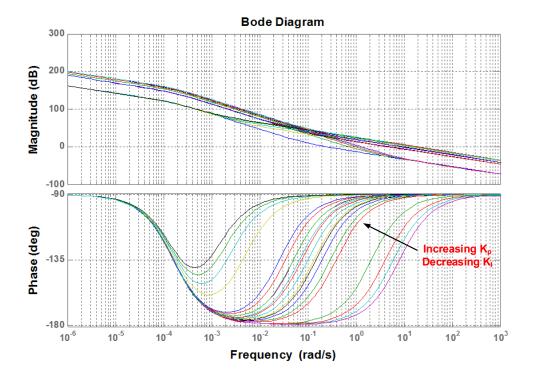

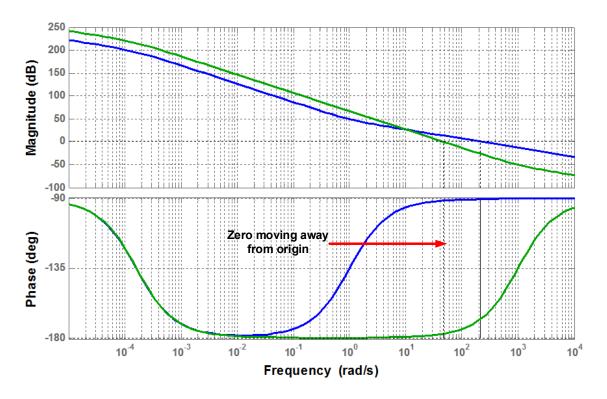

| Fig. 3.9:  | Bode plot of system loop gain for a range of $K_P$ and $K_I$ values                                                                                                                                | 62         |

| Fig. 3.10: | The controller zero is moved away from origin to improve dynamic performance of the cascaded system                                                                                                | 63         |

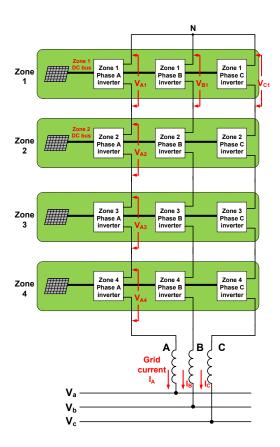

| Fig. 3.11: | Four cascaded three phase inverters with medium frequency transformer isolation interfaced with medium voltage utility grid                                                                        | 66         |

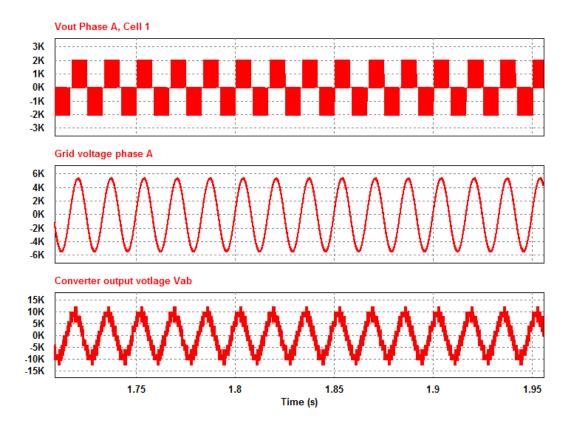

| Fig. 3.12: | Output voltage of one cell of the cascaded inverters, the grid voltage and multilevel inverter overall output voltage and in a PV system under uniform full insolation.                            | 67         |

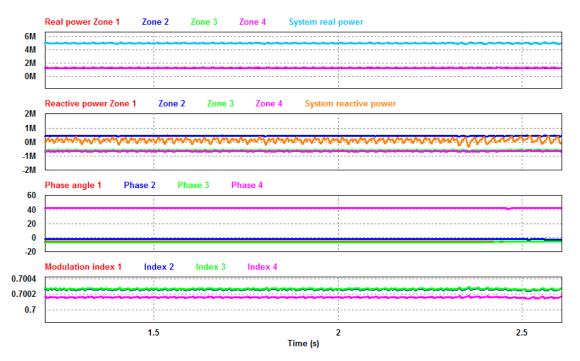

| Fig. 3.13: | Steady state operation of cascaded inverters with equal insolation at 100%                                                                                                                         | 68         |

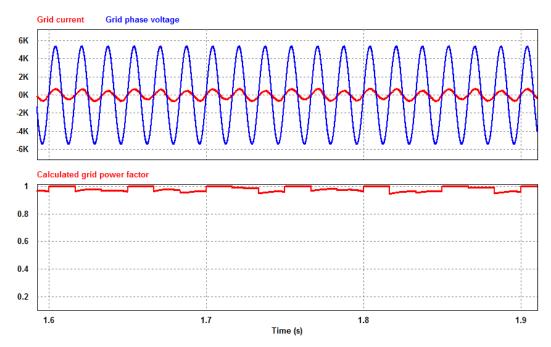

| Fig. 3.14: | Grid phase-neutral voltage and current showing unity power factor operation.                                                                                                                       | 68         |

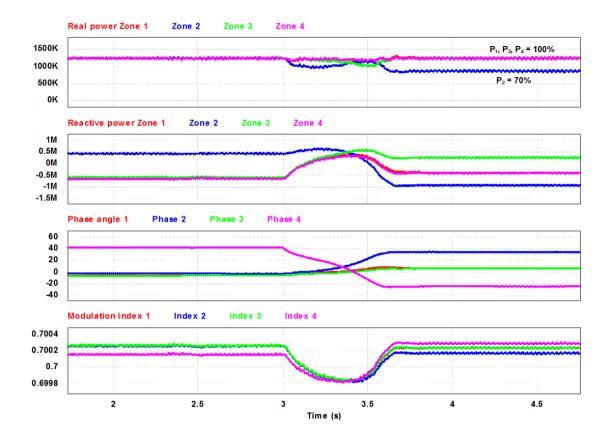

| Fig. 3.15: | Step change in reference power for inverter 2, at $t = 3$ s                                                                                                                                        | 69         |

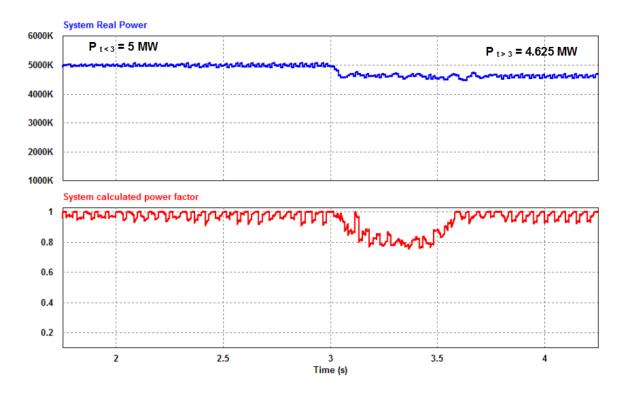

| Fig. 3.16: | System grid real power step response and system power factor                                                                                                                                       | 70         |

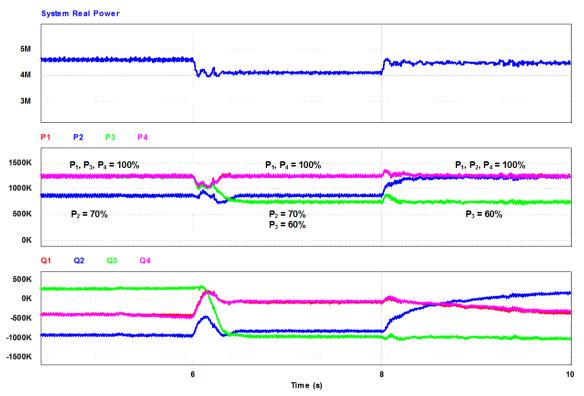

| Fig. 3.17: | Cascaded inverter controller tracking reference power control input                                                                                                                                | 71         |

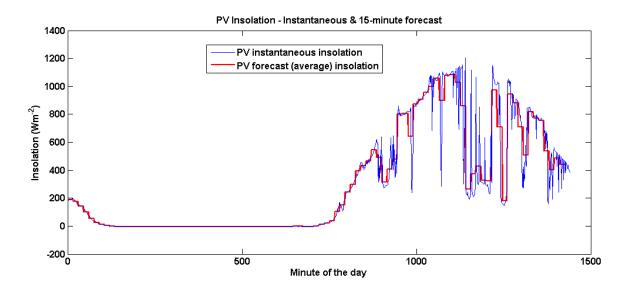

| Fig. 4.1:  | Instantaneous and 15-minute average (forecast) PV insolation data for Boulder, CO on May 17, 2013                                                                                                  | 75         |

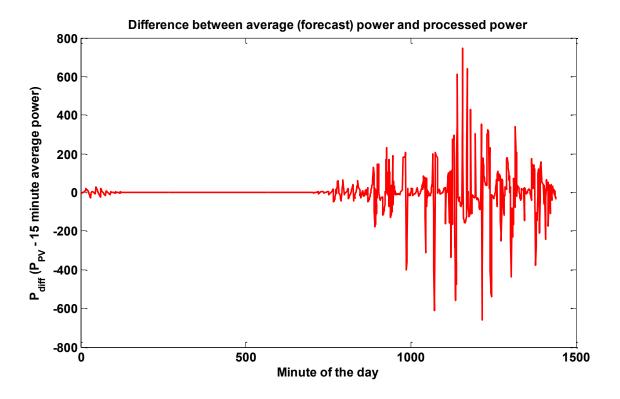

| Fig. 4.2:  | Variations in PV insolation leads to deviation of processed power from average (forecast) power                                                                                                    | 7 <i>6</i> |

|            |                                                                                                                                                                                                                                                  | Page |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

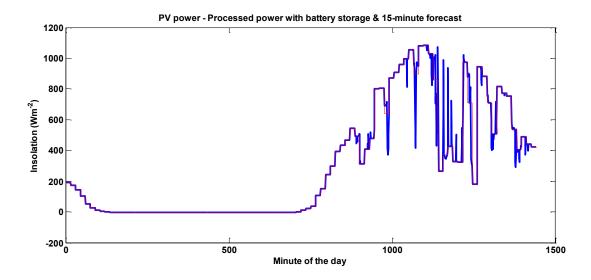

| Fig. 4.3:  | PV processed power with battery storage (blue curve) compared to 15-minute forecast power (red curve)                                                                                                                                            | 77   |

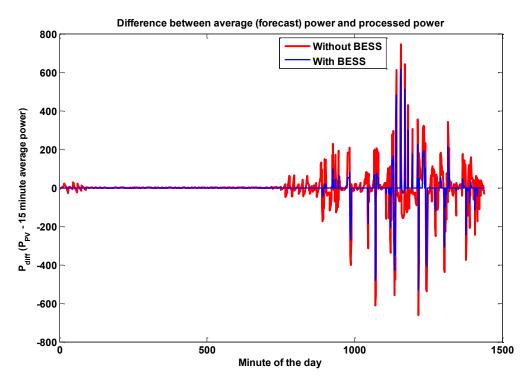

| Fig. 4.4:  | Comparison of error between forecast power and processed power, without BESS and with BESS rated 10%                                                                                                                                             | 77   |

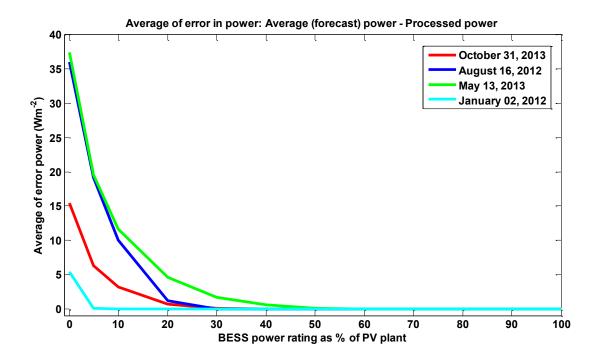

| Fig. 4.5:  | Day-average of deviation in processed power from forecast power, as a function of BESS power rating                                                                                                                                              | 79   |

| Fig. 4.6:  | Overall system diagram of battery energy storage system for utility scale PV plant                                                                                                                                                               | 80   |

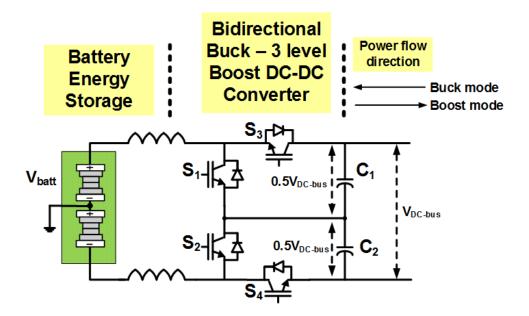

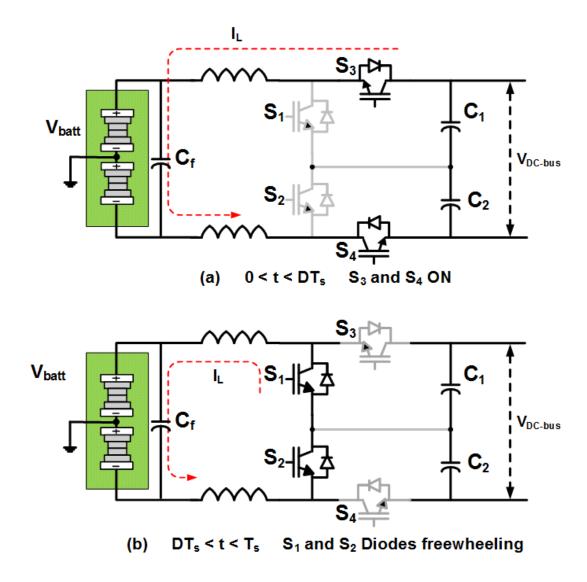

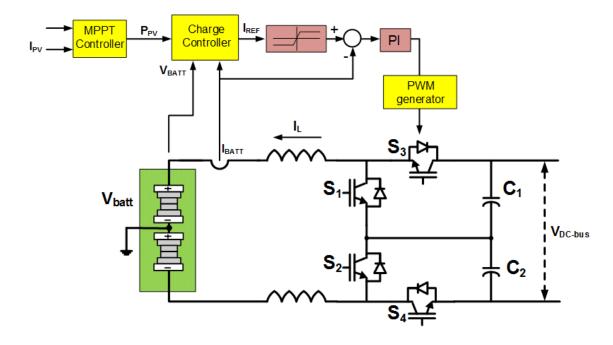

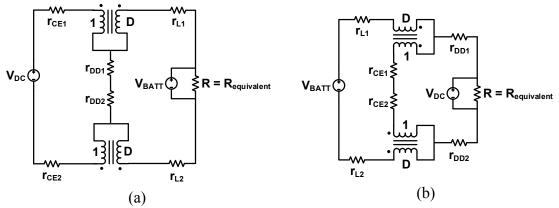

| Fig. 4.7:  | Bidirectional DC-DC converter operating in buck mode for battery charging and 3-level boost mode for battery discharging                                                                                                                         | 81   |

| Fig. 4.8:  | (a) Switches $S_3$ and $S_4$ are ON for $DT_s$ and the inductor current ramps up, supplying current to the battery (b) Switches are turned OFF and the inductor current freewheels through the antiparallel diodes of switches $S_1$ and $S_2$ . | 84   |

| Fig. 4.9:  | Controller for DC-DC converter buck operation during charging mode of the bidirectional converter. The current reference generator senses the open circuit voltage of the battery                                                                | 85   |

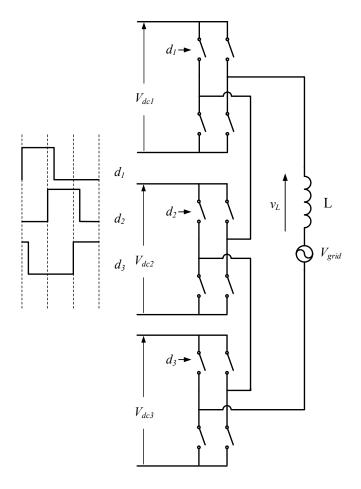

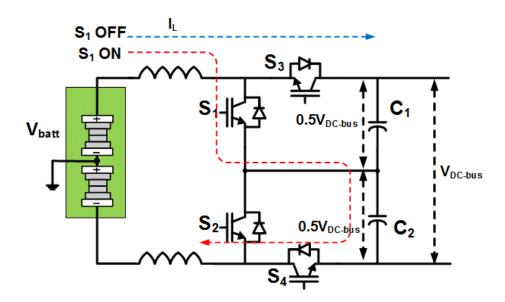

| Fig. 4.10: | Bidirectional DC-DC Converter in battery discharging mode operating as a 3-level boost converter (illustrated for the case that $V_{batt} > 0.5 V_{DC-bus}$ ).                                                                                   |      |

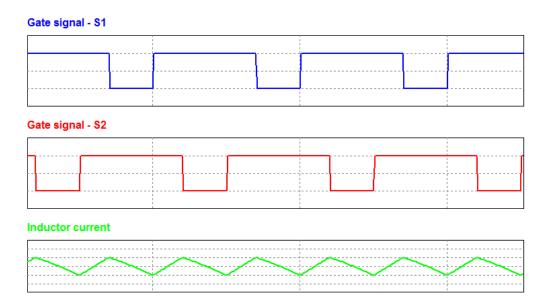

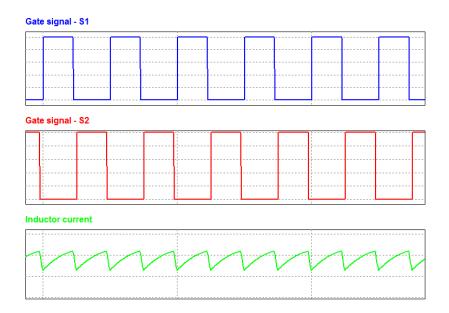

| Fig. 4.11: | Gating signals for top $(S_1)$ and bottom $(S_2)$ IGBTs in the three level DC-DC converter and the inductor current, operation mode 1 $(V_{Batt} < 0.5V_o)$                                                                                      | 87   |

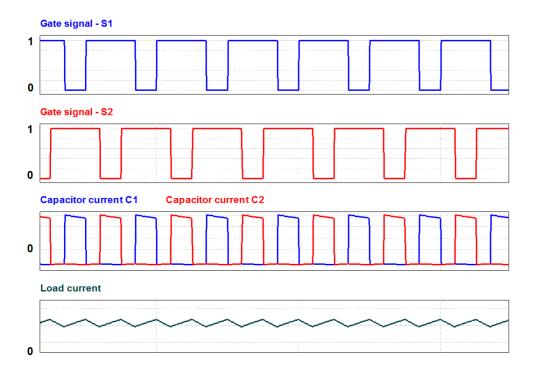

| Fig. 4.12: | Gating signals for top $(S_1)$ and bottom $(S_2)$ IGBTs, the currents through the top capacitor $C_1$ and the bottom capacitor $C_2$ and the load current in the three level DC-DC converter operating in mode 1 $(V_{Batt} < 0.5V_o)$ .         | 88   |

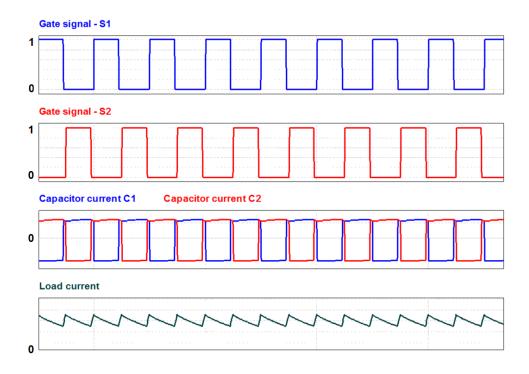

| Fig. 4.13: | Gating signals for top $(S_1)$ and bottom $(S_2)$ IGBTs in the three level DC-DC converter and the inductor current, operation mode 2 $(V_{Batt} > 0.5V_o)$                                                                                      | 89   |

|            |                                                                                                                                                                                                                                                                       | Page     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

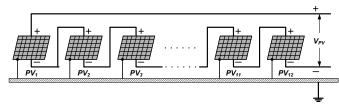

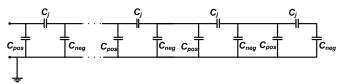

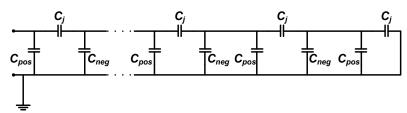

| Fig. 5.3:  | Equivalent circuit of a 12 module PV system with $C_j$ , p-n junction capacitance, $C_{pos}$ , module-to-ground capacitance (positive terminal) and $C_{neg}$ , module-to-ground capacitance (negative terminal)                                                      | 109      |

| Fig. 5.4:  | Equivalent circuit of a 12 module PV system where the negative terminal is shorted to the ground, $C_j$ is the p-n junction capacitance $C_{pos}$ , module-to-ground capacitance (positive terminal) and $C_{neg}$ , module-to-ground capacitance (negative terminal) | 110      |

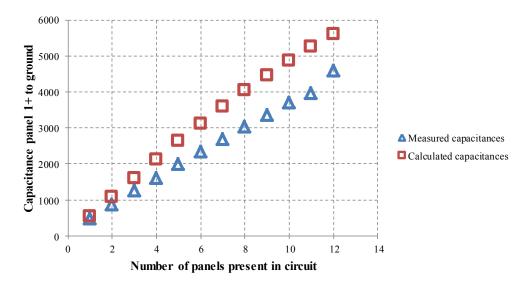

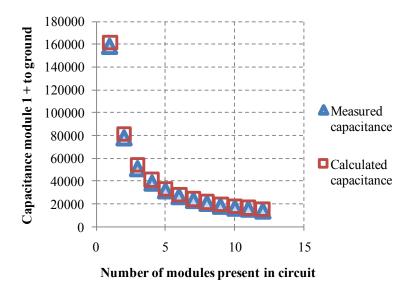

| Fig. 5.5:  | Capacitance to ground at positive terminal of module 1 vs. module index, with the negative terminal floating                                                                                                                                                          | 112      |

| Fig. 5.6:  | Capacitance to ground at positive terminal of module 1 vs. module index, with the negative terminal shorted to the ground                                                                                                                                             | 113      |

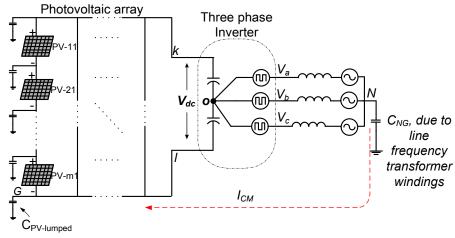

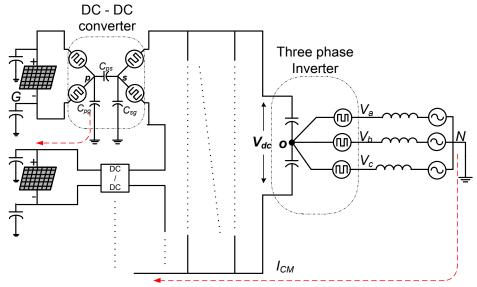

| Fig. 5.7:  | Centralized approach with an array of PV modules connected in series-parallel as shown, with a central inverter and 60 Hz isolation transformer                                                                                                                       | 115      |

| Fig. 5.8:  | An array of per-module DC-DC connected in series-parallel configuration with central inverter                                                                                                                                                                         | 115      |

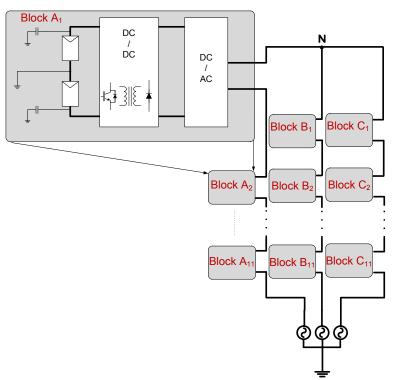

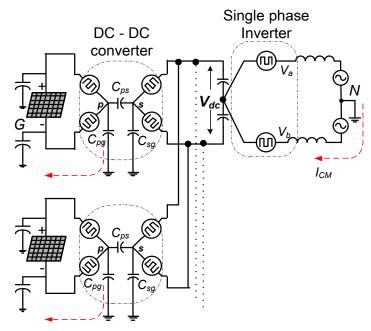

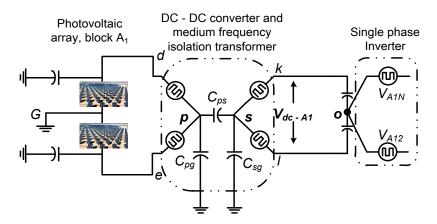

| Fig. 5.9:  | Medium-voltage, multilevel topology built from modular blocks comprised of PV modules connected to a DC-DC converter followed by a single phase inverter.                                                                                                             | 116      |

| Fig. 5.10: | Per-module DC-DC converters arranged in a plug-and-play fashion with one central inverter interfacing to utility                                                                                                                                                      | 117      |

| Fig. 5.11: | Per-module DC-AC micro-inverters connected in parallel to the AC bus, supporting a plug-and-play design and operation of the system                                                                                                                                   | 117      |

| Fig. 5.12: | Common mode equivalent circuit of an array shown in fig. 5.7 with <i>m</i> columns and <i>n</i> rows of PV modules with central inverter interfacing to utility                                                                                                       | 119      |

| Fig. 5.13: | Common mode equivalent circuit of an array shown in fig. 5.8 with <i>m</i> columns and <i>n</i> rows of per-panel DC-DC converters followed by central inverter                                                                                                       | 119      |

| Fig. 5.14: | Common mode equivalent circuit of string shown in fig. 5.10 with perpanel DC-DC converters in plug-and-play configuration                                                                                                                                             | -<br>120 |

|            |                                                                                                                                                                              | Page |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 5.15: | Common mode equivalent circuit of per-panel micro-inverter configuration shown in fig. 5.11.                                                                                 | 120  |

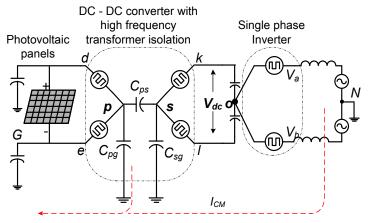

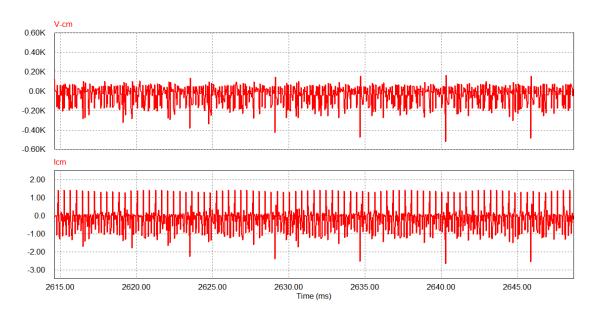

| Fig. 5.16: | Common-mode voltage and current on AC side transformer ground capacitance, $C_{NG}$                                                                                          | 122  |

| Fig. 5.17: | Common mode currents in module-to-ground capacitance of modules 1,10,30 and 40 in a string                                                                                   | 123  |

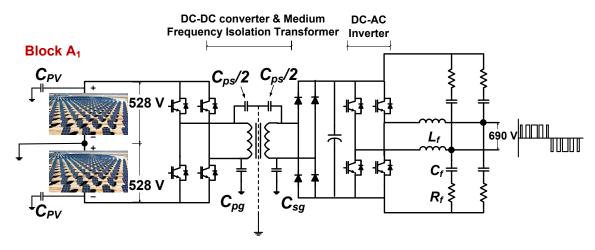

| Fig. 5.18: | Medium voltage 13 kV multilevel three phase system topology with 11 blocks per phase, each block producing 690 V single phase ac                                             | 125  |

| Fig. 5.19: | Common mode equivalent circuit of one block (Block A <sub>1</sub> ) in 13 kV multilevel topology                                                                             | 126  |

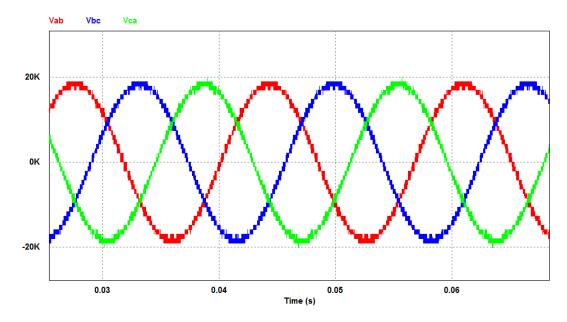

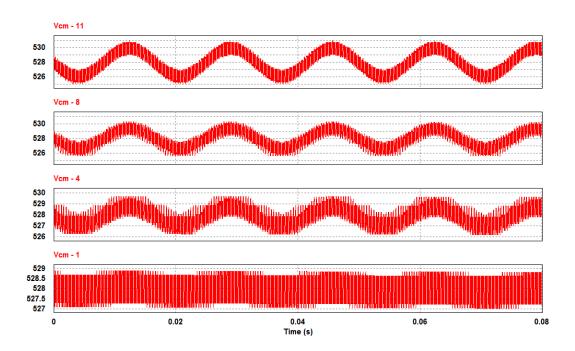

| Fig. 5.20: | Three phase line-line output voltages in a medium voltage level PV system                                                                                                    | 127  |

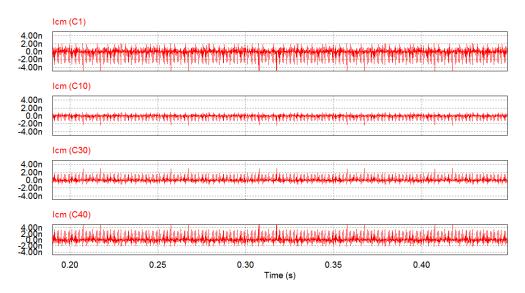

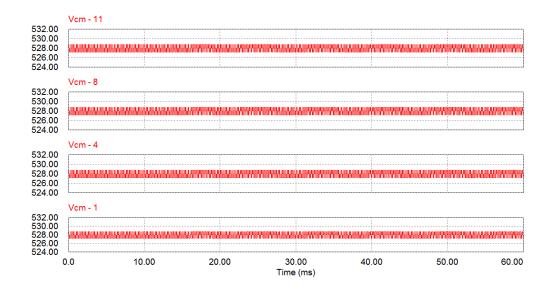

| Fig. 5.21: | Voltages across module to ground common mode capacitances in blocks 1, 4, 8 and 11                                                                                           | 128  |

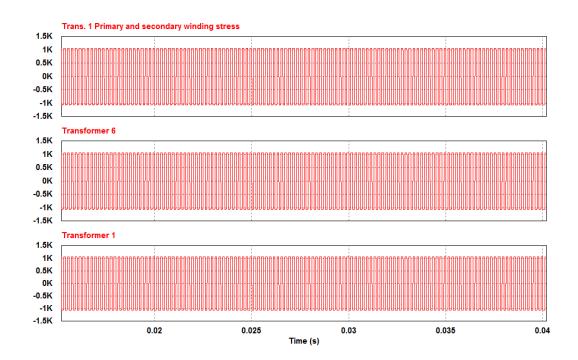

| Fig. 5.22: | Voltage stresses across primary-secondary winding capacitances in medium frequency transformer for blocks 1, 6 and 11                                                        | 128  |

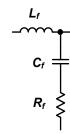

| Fig. 5.23: | L-C-R common mode low pass filter                                                                                                                                            | 130  |

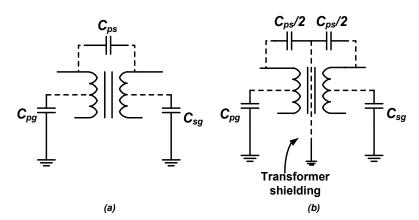

| Fig. 5.24: | Winding capacitances in transformer (a) without any shielding and (b) with transformer shielding                                                                             | 130  |

| Fig. 5.25: | One block in the phase A of multilevel medium voltage (13 kV) photovoltaic system with common mode filter and transformer shielding                                          | 131  |

| Fig. 5.26: | Voltage stresses across primary-to-secondary winding capacitances in medium frequency transformer for blocks 1, 6 and 11, with common mode filters and transformer shielding | 131  |

| Fig. 5.27: | Voltages across module-to-ground common mode capacitances in blocks 1, 4, 8 and 11, with common mode filter and transformer shielding                                        | 132  |

|            |                                                                                                                                                                              |      |

# LIST OF TABLES

|            | P                                                                                                   | age |

|------------|-----------------------------------------------------------------------------------------------------|-----|

| Table 1.1: | Comparison of PV Grid Integration Topologies for 1 MW, Medium Voltage 13.2 kV Grid Integration      | .15 |

| Table 2.1: | Switching Functions for Devices in Primary Side Inverter and Cycloconverter for Bipolar Modulation  | .31 |

| Table 2.2: | Switching Functions for Devices in Primary Side Inverter and Cycloconverter for Unipolar Modulation | .34 |

| Table 2.3: | Cascaded Multilevel PV Inverter System – Specifications                                             | .39 |

| Table 2.4: | MF Transformer Design Specifications                                                                | .43 |

| Table 3.1: | Solutions of Multilevel Inverters Voltage Vectors for Power Sharing – Four Different Cases          | .52 |

| Table 3.2: | Multilevel Inverter for Closed Loop Analysis - Specifications                                       | .65 |

| Table 4.1: | Error between PV Forecast Power and Processed Real Power for Various BESS Ratings                   | .78 |

| Table 4.2: | Comparison of Battery Chemistries                                                                   | .82 |

| Table 4.3: | Specifications for Design Example for Utility Scale Bess Integrated PV                              | .93 |

| Table 5.1: | Calculated and Measured Values of Module 1 Capacitance to Ground                                    | 111 |

| Table 5.2: | Specifications for Centralized Inverter Analysis                                                    | 122 |

| Table 5.3: | System Specifications for Medium Voltage Utility PV System                                          | 124 |

| Table 5.4: | RMS Voltage Stress on Transformer Primary & Secondary Windings                                      | 132 |

#### 1. INTRODUCTION

#### 1.1. Growth of Renewable Power and Photovoltaic Power Installations

The growth in demand for electricity has always been increasing but in recent years the rate of growth has slowed down. Recent figures indicate that the growth has dropped to 0.7% per year [1]. Capacity addition to the grid has kept up with the demand but the sources of generation have varied over decades. Recent capacity additions have come mainly from natural gas power stations and renewable energy sources. Fig 1.1 shows the growth in electricity generation by energy source, which gives the predictions for robust growth in renewable energy installations.

Amongst renewable energy sources, solar and wind power provide most of the growth, as can be seen from fig. 1.2. The steady and rapid growth in solar photovoltaic installation across the United States has been driven by many factors including renewable portfolio standards, decreasing costs of installations and incentives such as feed-in-tariffs or net-metering mandated by governments.

Fig. 1.1: Electricity generation by fuel, 2011, 2025 and 2040 (billion kWh) Source: EIA (May 2013) [1] \*

Fig. 1.2: Renewable energy sources by installed capacity, 2011-2040 (GW) Source: EIA (May 2013) [1] \*

As of 2013 the total capacity of PV installations in the USA stands at 8 GW [2].

Of the 3.3 GW of capacity addition in PV in the year 2012, more than half – 1.7 GW –

<sup>\*</sup> Used with permission from US Energy Information Administration. http://www.eia.gov/about/copyrights\_reuse.cfm

was in the utility sector [2]. With incentives and subsidies from governments and feed-in-tariffs from utilities, grid parity in solar PV sector is said to have been achieved [3]. Also, the cost of installations is projected to reduce by 35% by 2025, adjusted to inflation.

Fig. 1.3: U.S. PV installations by market segment, 2030 & 2050 forecasts. Source: NREL [4] \*

All the aforementioned factors are predicted to contribute to tremendous growth in utility sector PV installations, as seen from fig. 1.3 [4]. The increasing capacity addition of solar PV and installation of larger power stations has led to research and development in high power converter topologies for PV applications, which will be further discussed later in this chapter.

-

<sup>\*</sup> Used with permission from US National Renewable Energy Laboratory

## 1.2. Characteristics of Solar PV Cells and Arrays

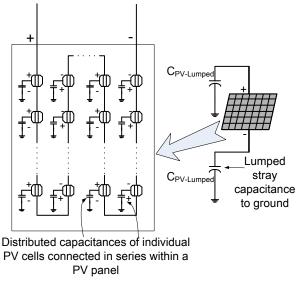

Solar photovoltaic modules are constructed by connecting numerous PV cells in series. There are different types of cell chemistries, the most important of which are Crystalline silicon, Polycrystalline thin film (e.g.: Cadmium telluride), Mono-crystalline thin film (e.g.: Gallium arsenide). A typical commercial solar PV module is rated 250 – 300 W. When light is incident on the surface of the PV cell, some of the light energy is absorbed by the cell to produce electricity. In addition to producing a current the PV cells also generate a small electric field across them which results in output voltage which is typically 0.6 V per cell for a commercial PV module. The voltage-current characteristics of a PV cell and by extension, a PV module are given in fig. 1.4. It can be seen from the figure that PV cells may be characterized as weak current sources since they exhibit the properties of a current source under low voltage and as the voltage increases, the current collapses beyond a "knee point". Also, these properties are dependent on the temperature of the cells and incident solar radiation (insolation), or the amount of solar power incident on a unit area of the module. As the insolation decreases, the current generated by the module decreases and as the temperature increases the voltage generated decreases. These two phenomena are fairly independent.

Fig. 1.4: The voltage-current characteristics of solar photovoltaic cell

In fig. 1.4 it may be seen that beyond a voltage level, the current generated by the PV cell starts to reduce. It is easy to deduce that at this point, both the voltage and the current generated by the cell are at their maximum, which means that the power generated by the cell at this point is the maximum possible for those operating conditions of insolation and temperature. Using power electronic circuits, it is possible to apply this voltage to the PV cell, ensuring that the power generated by the cell is at a maximum. This operation is called Maximum Power Point Tracking (MPPT).

PV modules can be connected in series and parallel combinations to produce desired DC voltage and current ratings. Such combinations are termed PV arrays. The PV arrays have V-I characteristics similar to the cell, appropriately scaled. PV arrays can be connected to power electronic converters so that the PV power may be processed and supplied to the load or the utility grid.

### 1.3. Commercial and Utility Scale Solar PV Integration

Solar PV installations vary in their installed capacity from domestic applications which are in the multi kW range and utility scale plant which are as high as hundreds of MW. This categorization is done mainly based on the size of the installation. Installations on residential rooftops which are below 10 kW are generally grouped into Residential systems. Installations on business buildings and warehouses are usually larger than 10 kW and may be up to megawatts and these installations are known as Commercial systems. Utility systems are much larger, ground-mounted systems which are often greater than 100 MW [5].

The operation of large scale plants has a significant impact on the utility grid. As the capacity of PV installations grows they constitute a growing part of the grid capacity itself. This presents unique challenges, because until few years ago almost all of the grid capacity was conventional synchronous generator based plants, powered by sources such as gas or nuclear power. Problems such as intermittency of solar power pose power electronic design challenges since the stability of the utility grid depends on the regulation of the PV plant as well. The impacts of photovoltaic installations and other distributed sources on the grid, and the design challenges and requirements are reflected upon, in documents such as IEEE 1547 Standards [6] for distributed energy resources. Some examples of the impacts which PV plants could have on the grid and design requirements to minimize the impact are given here (from IEEE 1547).

• Impact on Utility Grid: Power injected into the grid from the distributed resource could completely offset the local load demand of the power system, causing an

increase in bus voltage. If the distributed resource supplies (capacitive operation) or consumes (inductive operation) reactive power, the bus voltage is significantly affected in the local electric power grid. This, in addition to the previous effect, contributes to an increase in bus voltage at the local power system.

- Power Quality DC injection: The distributed resource and its interconnection system shall not inject dc current greater than 0.5% of the full rated output current at the point of common coupling. Any injection of DC current could begin to saturate the cores of distribution transformers, which causes higher values of current spikes in the system.

- Power Quality THD: While supplying balanced linear loads, the THD of line current supplied by the inverters should not exceed 5%. Standards such as IEEE 519 also dictate the permissible amounts of harmonic content for individual harmonic numbers.

- *Islanding Protection:* When the grid voltage collapses and results in an outage, an island of locally energized voltage buses is formed within the grid power system, leading to safety concerns. The interconnection system should detect the formation of this island and cease to energize the local power grid within two seconds.

#### 1.4. Literature Review

The integration of photovoltaic power plants to utility grids has been a topic of research interest for many years. The commonly used topology for utility and commercial power plants is the centralized inverter topology. However, alternative

topologies to maximize power quality and energy harvest have been and continue to be proposed. Research in multilevel topologies has yielded different control strategies to maximize power harvest under partial shading conditions. Also, a lot of research literature has been published on the practical issues in PV integration such as parasitic capacitances, common mode voltages and currents. Another area of recent research interest is energy storage for utility grids, with hybrid power stations gaining attention.

# 1.4.1. PV Topologies: Two-level Inverter

Conventional utility scale PV plants first convert the generated DC voltage to a regulated bus using a DC-DC converter as seen in fig. 1.5, which also performs MPPT. This voltage is fed to an inverter to produce 480 V, 3-phase,  $V_{ac}$ , which is then stepped up to 13.2 kV medium voltage AC using a line frequency transformer.

This system suffers from some disadvantages such as the DC bus voltage being limited due to safety regulations (1000 V in EU and 600 V in USA). This means that the increased current causes higher losses, increased cable sizes and costs. Also, the line frequency transformer used for grid interconnect is bulky in size.

Fig. 1.5: Conventional utility scale PV plant interfaced to medium voltage electric grid

When such a PV inverter system is connected to the PV arrays, maximum power point tracking (MPPT) could be performed by the inverter or the DC-DC converter stage. Since the arrays are connected in series-parallel configuration, the currents carried by the array is limited by the modules which are least illuminated. This in turn reduces the overall power production. The effects of such shading may be mitigated by moving the MPPT DC-DC converter to the string level, as shown in fig. 1.6 or the module level so that each module can produce maximum possible power independently. This leads to an increase in overall energy yield of the PV power system [7].

Fig. 1.6: String level MPPT converters reduce effects of partial shading and increase energy yield

The two-level inverter will need high voltage semiconductor devices for high DC bus applications. Multilevel inverters on the other hand, have better performance than the two-level topology since they produce much better output voltage waveforms and they can operate at a lower switching frequency than two-level inverters. They also can utilize low voltage semiconductor devices which are less expensive and faster in operation.

## 1.4.2. PV Multilevel Topologies: Diode-clamped

Many multilevel topologies have been proposed to improve operational performance and efficiency. Diode clamped topologies were proposed in [8] and [9] which enable individual array MPPT control and provide a better quality output voltage waveform than a full-bridge inverter. Multilevel NPC topologies [10-13] and cascaded

multilevel topologies [14-20] have also been proposed which process power from individual arrays rather than a large field. These topologies can also process unbalanced power amongst phases or the cascaded cells [15, 16, 18]. These proposed topologies still require line frequency transformer isolation and in the case of cascaded multilevel converters, suffer from double frequency power ripple on the DC bus capacitor.

In the diode clamped topology, as shown in fig. 1.7, PV arrays (*n-1* in number) are connected in series and the inverter is an *n*-level inverter with individual array MPPT control [8]. Since this is a multilevel inverter the output current has low distortion and the grid power factor is high. Any DC power imbalances which occur between the arrays are resolved by independent array MPPT control.

Fig. 1.7: Diode clamped *n* level inverter with individual array MPPT control

This system, despite delivering a much superior performance to that of a two-level inverter, suffers from certain deficiencies. The DC bus voltage effectively limits the number of arrays *n* that can be connected in series. Also the system is non-modular and the control is complex. The system still needs a line-frequency transformer to interface with the grid.

## 1.4.3. PV Multilevel Topologies: Modular Multilevel

A modular multilevel topology has cascaded H-bridges as shown in fig. 1.8 to produce a multilevel output waveform [18]. Each H-bridge is connected to a PV array or string. MPPT operation is performed by each H-bridge converter so any power

imbalance between the cells in the multilevel inverter could be resolved. These power imbalances among phases or cells require modulation compensation schemes (zero sequence injection) to produce balanced, equal line-line voltages.

Fig. 1.8: Modular cascaded multilevel H-bridge topology for three phase grid integration

This approach too, has some disadvantages. The DC bus experiences a double frequency power ripple. Even though this is a three phase inverter, the H-bridges operate as if they were single phase, leading to the double frequency ripple. This requires large capacitors on the DC bus. Also, since there is no high frequency transformer isolation,

the maximum possible gain of the inverter is 1. Since modulation compensation schemes could further reduce the magnitude of output voltage, the DC bus voltage needs to be higher than necessary to produce the rated output voltage. Further, the PV modules in this system experience increased common mode voltage problems because of high voltage operation.

These disadvantages notwithstanding, multilevel topologies have been found to be more efficient and have a better performance than two-level inverters [21]. They offer better efficiencies since they enable high voltage operation. They have superior output distortion properties and also reduce common mode voltages and electromagnetic interference problems. Further, the individual switches may be operated at a lower switching frequency to produce a higher switching frequency voltage waveform at the output. These reasons have made high voltage operation and multilevel inverters an attractive option for PV integration. Table 1.1 shows a comparison of PV topologies, two-level and multilevel, to better illustrate the differences between these architectures. In comparing the topologies a DC bus voltage of 800 V is assumed. The inverters are rated 1 MW and the transformer turns ratio is limited to 1:6 for both the line and medium frequency devices. The IGBTs for the 2-level, NPC and diode clamped topologies are 500 A rated and the cascaded topologies have 200 A rated devices.

Table 1.1: Comparison of PV Grid Integration Topologies for 1 MW, Medium Voltage 13.2 kV Grid Integration

| Topology:                        | 2-level                                         | Neutral<br>point<br>clamped | Diode<br>clamped <i>n</i><br>– level    | Cascaded without MF transformer | Cascaded<br>with MF<br>transformer          |

|----------------------------------|-------------------------------------------------|-----------------------------|-----------------------------------------|---------------------------------|---------------------------------------------|

| No. of<br>IGBTs                  | 12 – 18                                         | 36                          | $3\cdot 2^n$                            | 36 (3 levels)                   | 72                                          |

| Device<br>voltage<br>rating      | 1.2 kV                                          | 600 V                       | $\frac{1200}{n}$                        | 1.2 kV                          | 4.16 kV                                     |

| Output<br>quality                | Poor                                            | Good                        | Good, function of <i>n</i>              | Good                            | Good                                        |

| Line<br>frequency<br>transformer | Yes                                             | Yes                         | Yes                                     | Yes                             | No                                          |

| Control                          | Simple                                          | Moderate                    | Complex                                 | Complex                         | Complex                                     |

| Notes                            | High filter requirements, transformer ratio 1:6 | Fault<br>tolerance<br>poor  | Greater<br>MPPT<br>accuracy<br>possible | Transformer ratio 1:6           | Low current rating, reduced cost of cabling |

# 1.4.4. PV Multilevel Control Techniques

Control techniques for multilevel inverter topologies have been studied extensively. Some of the techniques studied for multilevel control are [22]

- a. Voltage oriented control

- b. Voltage direct power control

- c. Virtual flux based control

### d. Virtual flux direct power control

These techniques have also been used and adapted for multilevel inverter based PV systems. Many publications deal with control of PV multilevel for power imbalance amongst the cascaded multilevel cells and amongst the three phases. They consider a single phase inverter cell to be connected exclusively to a PV array. Control techniques proposed often involve a centralized controller which corrects for the phase and cell power imbalance. The output voltages of the individual inverters are controlled by modulation angle correction, thereby introducing a neutral point shift [23]. Feedforward techniques have been proposed to take into account the drift in DC bus voltage while calculating the modulation index [16]. More advanced techniques such as model predictive control have been proposed to predict the switching states as cost functions to control the DC bus voltages [24].

#### 1.4.5. PV Battery Energy Storage

Battery energy storage devices are becoming more prevalent and they provide advantages such as mitigating intermittency effects of renewable energy sources. PV battery systems have been proposed for grid frequency and voltage support using real and reactive power support [25]. Bidirectional isolated DC-DC converters have been proposed for generalized battery energy storage systems using lithium ion batteries [26] and bidirectional DC-DC converters for exclusively DC distribution grids have also been studied [27]. Cascaded multilevel converters for battery charging have also been proposed [28] with battery state-of-charge estimation techniques. However, this

topology is transformerless, which means that some of the batteries operate at an elevated potential on both their terminals.

## 1.5. Research Objective

The objective of this dissertation is to analyze, propose, and design multilevel inverter topologies for utility scale solar photovoltaic applications. Multilevel topologies have been found to be more efficient than two level inverters and provide improved power quality. The proposed multilevel topology will interface MW scale utility photovoltaic power stations with a medium voltage utility grid. The problems discussed in the previous section associated with multilevel topologies such as double frequency power, requirement of line frequency isolation transformer will be addressed. The proposed topology will utilize a medium frequency isolation transformer which increases power density and provides galvanic isolation to the PV modules. The multi output transformer design will eliminate double frequency pulsations on the DC bus capacitor, leading to a reduction of its size. The design and rating analysis of the medium frequency transformer will be done. The multilevel inverter will use a cycloconverter to produce the desired AC output voltage which provides bidirectional capability.

Multilevel inverters employed in photovoltaic power processing face an important issue, viz partial shading or unbalanced insolation amongst the cascaded inverter cells. A control methodology is to be developed which enables different cells of the multilevel inverter to process varying powers. In developing the control method, the well-known and established concepts of real and reactive power flows will be used. The individual cell output voltages magnitude and phase angle will be calculated such that

the powers processed by an individual cell corresponds to the available power from the respective PV array. The analysis behind the control method will be first derived assuming that there is a centralized controller which performs the necessary calculations and generates the modulation indices for the inverter. A design example of a 10 MW PV system interfacing to a medium voltage grid and simulations results will be discussed. A laboratory scaled down prototype inverter will be developed.

The control methodology once derived, will form the basis of developing an independent controller for an individual cell in a multilevel inverter. The control technique will be inspired by droop control techniques employed in the operation of parallel inverters connected to a common voltage bus. Similar to the droop control technique, each inverter will be individually programmed and equipped to control power flow, independent of feedback from other inverters in the system. However, grid voltage zero crossing data will be made available to the individual inverters. The closed loop controller will control modulation index for an inverter cell such that any amount of real power can be processed from the PV arrays, provided the grid voltage has not collapsed.

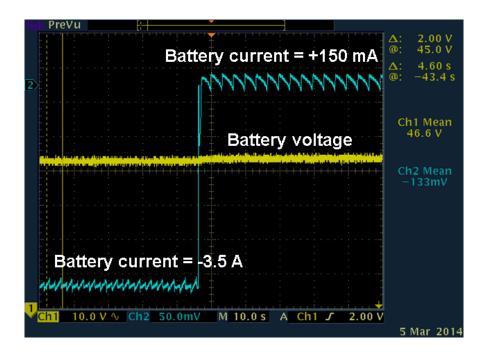

Photovoltaics and other renewable energy sources are often associated with intermittency, which affects the utility grid in ways that could destabilize it. This issue is resolved by a combination of accurate forecasting of renewable availability and reactive power support from inverters using power electronics. However, energy storage systems are becoming more popular in providing support to the grid during intermittency. A battery energy storage system for utility scale PV will be developed in this work. The battery system will be designed to support up to 10% reduction of the PV system. The

design and operation of the bidirectional converter which charges and discharges the battery will be discussed. A study of the design of the battery system and various battery chemistry choices available will also be performed. A design example for the battery energy storage device and simulation results will also be discussed.

Common mode (CM) voltages and currents are an important issue faced by power electronics and electric machine designers. These phenomena lead to problems such as nuisance tripping, deterioration of components and electromagnetic interference (EMI). This work will perform an analysis of PV modules with respect to parasitic capacitances, which influence CM currents in PV modules. CM voltages in various PV inverter topologies including the proposed topology will be characterized and analyzed, along with simulation and experimental results. Techniques to mitigate CM voltages and currents will also be discussed.

#### 1.6. Outline of Dissertation

This dissertation is organized into six chapters. Chapter 1 introduces photovoltaic technology and their growth into an important player in the modern utility grid. The operational characteristics of PV power plants and their impact on the grid are discussed. A literature review of state-of-the-art and research publications on new topologies is done and the research objective is described.

Chapter 2 provides the description of the proposed medium frequency AC link inverter and explains its operation. The design of the inverter and the medium frequency transformer are discussed. The operation of the inverter along with simulation results and prototype experimental results are provided. Chapter 3 develops a control technique

to independently control individual cascaded inverter cells. The chapter first describes the operation of droop control and describes the derivation of cascaded inverter control. Simulation and experimental prototype results are also provided.

Chapter 4 discussed common mode voltages and currents in various PV inverter topologies. Analysis and measurement of parasitic capacitances in a commercial PV system are described. The development of CM voltage and currents and techniques to mitigate them are explained with simulation results.

Chapter 5 is concerned with the development of a battery energy storage system for multilevel PV inverters. Various battery technologies available for this application are discussed. The DC-DC converter used to interface the battery with the grid is explained and analyzed. Simulation results for a 0.1 p.u. battery system are provided for a 5 MW rated PV multilevel system.

Chapter 6 provides a summary of the research work and concludes with recommendations for future research topics.

# 2. MEDIUM FREQUENCY AC LINK CASCADED MULTILEVEL INVERTER AND ZONAL POWER BALANCER\*

### 2.1. Introduction

A commercial large utility solar photovoltaic power station consists of a number of PV arrays, which are large number of PV modules connected in series-parallel configuration. PV modules are connected in series to form a string, specified by the desired PV voltage and a number of strings are connected in parallel, determined by the PV current rating. Each of the PV arrays in the power station is interfaced to a central three phase inverter. As discussed in the previous chapter, multilevel inverter topologies have several advantages such as better power quality, utilization of lower voltage rating devices, etc. The proposed topology is a multi-level DC-AC converter for MW scale applications which has the aforementioned advantages and also improves partial shading operation [29]. The plant is divided into a number of zones as shown in fig. 2.1; the DC voltage from each zone is converted to medium frequency (MF) AC using an IGBT-based full bridge inverter. It is then fed to an MF transformer with 3 secondary windings (one for each phase), stepped-up and then fed to a full bridge AC-AC converter to generate 3-phase AC. The proposed system has the following advantages:

PV field is configured as a center-point grounded system to realize higher voltage DC while preserving the insulation level of individual panels. High DC

\* This chapter is adapted from [29] H. S. Krishnamoorthy, S. Essakiappan, P. N. Enjeti, R. S. Balog, and S. Ahmed, "A new multilevel converter for megawatt scale solar photovoltaic utility integration," in *Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2012, pp.

1431-1438. © 2012 IEEE. Digital Object Identifier: 10.1109/APEC.2012.6166008

- voltage operation reduces the current rating requirement of cables and also improves efficiency.

- A unique current sharing scheme is introduced such that zonal MPPT is achieved.

- Use of medium frequency transformer isolation reduces the size and cost and at the same time, provides galvanic isolation between PV modules of different zones of the plant.

- Multilevel operation allows use of SiC MOSFET devices in the AC-AC converter leading to higher efficiency. Further, the semiconductor devices are utilized more effectively. The reduction in current decreases the cable size and cost [30].

- Due to the modular nature of the approach, it is possible to bypass one zone at a time for maintenance without disconnecting the entire system.

- Harmonic current is reduced on the DC link, which allows the usage of thin film capacitors with smaller sizes and longer life-times. Switching frequency harmonics are also reduced by phase shifted carrier pulse width modulation (PSC-PWM).

- A new control method is proposed for the series connected inverter modules under partial shading. The approach controls each inverter voltage/phase-angle to continuously adjust the power delivered.

Fig. 2.1: Proposed Multi-level DC-AC-AC Converter with MF isolation and Zonal MPPT

# 2.2. Description and Working of Proposed Multilevel Converter

Fig. 2.1 shows the proposed multilevel converter. Inductors-  $L_{p1}$ ,  $L_{p2}$  ...  $L_{pn}$ , along with the switches  $S_{1p}$ ,  $S_{1q}$ ,  $S_{2p}$ , ...  $S_{nq}$  are controlled to function as current choppers which regulate the currents ( $I_{11}$ ,  $I_{12}$  ...,  $I_{n2}$ ) in order that the current through the PV arrays can be different/adjusted to achieve MPPT. The full bridge inverter with switches-  $Q_{11}$ ,  $Q_{12}$ ,  $Q_{13}$ ,  $Q_{14}$ ,  $Q_{21}$ , ...  $Q_{n4}$  are switched at MF and this voltage is applied to the primary of the

MF transformer. The SiC MOSFET based AC-AC converter with bidirectional switches-Q<sub>1</sub>A<sub>1</sub>, Q<sub>1</sub>A<sub>2</sub>, Q<sub>1</sub>A<sub>3</sub>, Q<sub>1</sub>A<sub>4</sub>, Q<sub>1</sub>B<sub>1</sub> ... Q<sub>n</sub>C<sub>4</sub> convert the MF AC to get line frequency AC. The line inductors can induce circulating currents in the transformer secondary at large loads, which can be used to attain ZVS on switches on primary side [31]. When the number of levels is large, the grid-side L-C filters which have to be used in conventional topologies can be eliminated due to the PSC-PWM on AC-AC side [32-35]. Alternatively, the same functionality may be achieved by constructing the AC-AC converter as an indirect matrix converter, which would consist of a controlled rectifier followed immediately by a full bridge inverter without a DC bus capacitor. Another alternative topology would be to use a triple active bridge on the PV side to produce three square wave voltages, which would be applied to three medium frequency single phase transformers. This approach would reduce the device current ratings but increase the number of devices used on the transformer primary side.

Considering a 10 MW solar PV plant divided into n zones of 1 per unit (p.u) power, each generating a maximum  $V_{dc} = 1$  p.u voltage (around 0.5 p.u/array). Assuming that the secondary side SiC MOSFETs are rated for 3.3 kV, the peak voltage that each MOSFET can block after a derating of 50%, is around 1.7 kV. So, the maximum peak-to-peak secondary voltage of transformer can be  $V_{sec} = 1.7*2 = 3.4$  kV, which can be used to generate a maximum sinusoidal output voltage of 1.2 kV rms. In order to interface with a 13.2 kV rms medium voltage utility grid and to allow flexibility in the modulation index ( $m_a$ ) to 0.8, number of zones can be calculated as:

$$n = \frac{(13200/\sqrt{3})}{(m_a * 1200)} \cong 8 \tag{1}$$

So, the base power (1 p.u) is taken as 1.25 MW (10 MW/8) and base voltage (1 p.u) is taken as 1.0 kV. This makes base current as 1250 A and base impedance as 0.8  $\Omega$ .

# 2.2.1. Zonal Power Balancer under Partial Shading

At times of unequal shading within a zone, the current in series connected arrays is limited to that of the least illuminated array. The zonal power balancer eliminates this problem. The currents in the power balancing inductors ( $L_{p1}$ ,  $L_{p2}$ , etc.) are controlled to be equal to the difference in array currents in a zone.

For the design of the power balancer, steady state duty cycle for switching of the IGBT  $S_{np}$  can be written as  $D=V_2/(V_1+V_2)$  and that for  $S_{nq}$  as, D'=I-D. With this, the inductor value can be calculated as:

$$L_p = \frac{D \cdot V_1}{f_{sw} \cdot \Delta I_L} \tag{2}$$

where  $V_I$  and  $V_2$  are the voltages of the two stacks in zone-1 ( $V_I+V_2=V_{zI}$ ).  $f_{sw}$  is the MPPT switching frequency and  $\Delta I_L$  is the maximum allowable ripple current in the inductor.

Same equations apply for other zones as well. In the present context, it is assumed that the voltages  $V_I$  and  $V_2$  can vary from 0.5 p.u to 0.4 p.u each, at the worst condition and the power delivered by each array may vary independently from 0% to 100% capacity during the day. For a switching frequency of 20 kHz and  $\Delta I_L$  of 50 A, L

can be calculated as 240  $\mu$ H. Fig. 2.2 shows the simulated waveforms of current through power balancing inductor (L<sub>p1</sub>) and voltage across the inductor in zone-1 under the condition that the array with voltage  $V_2 = 500$  V delivers 100% power, while the array with voltage  $V_1 = 450$  V delivers only 50% power due to partial shading. It can be seen that the average current through the inductor is -560A, which enables power balancing between the arrays.

Fig. 2.2: (a) Voltage and (b) Current of power balancing inductor

#### 2.2.2. DC-AC-AC Converter

The inversion of PV side DC voltage to line frequency AC is accomplished by the DC-AC-AC medium frequency AC link converter. The primary side voltage is generated by the full bridge inverter and the square wave voltage produced is applied to the AC-AC converter, which produces a sinusoidal PWM voltage on the output side.

The Fourier series expansion of voltage at transformer primary,  $V_{pri}$  can be written as:

$$V_{pri}(t) = \frac{4V_{dc}}{\pi} \cdot \left[ \frac{\sin 1\omega_1 t}{1} + \frac{\sin 3\omega_1 t}{3} + \frac{\sin 5\omega_1 t}{5} + \frac{\sin 7\omega_1 t}{7} + \dots \right]$$

(3)

With PSC-PWM at the secondary side AC-AC converter, switching function can be split into two components (one with a rectifier switch function and another with a sine PWM inverter switch function) and can be written as:

$$S_{acac}(t) = S_{rect}(t) \cdot S_{inv}(t) \tag{4}$$

where

$$S_{rect}(t) = \frac{4}{\pi} \left[ \frac{\sin 1\omega_1 t}{1} + \frac{\sin 3\omega_1 t}{3} + \frac{\sin 5\omega_1 t}{5} + \frac{\sin 7\omega_1 t}{7} + \dots \right]$$

(5)

$$S_{inv}(t) = m_a \left( \sin(2\pi \cdot 60 \cdot t) + \sin(\omega_2 t) + \ldots \right)$$

(6)

$m_a$  is the voltage modulation index,  $\omega_l$  is the IGBT bridge square wave switching frequency and  $\omega_2$  is the AC-AC converter carrier frequency. The carrier frequency can be chosen as  $\omega_2 \approx 4*\omega_l$  to reduce the size of input as well as AC side filters ( $\omega_l$  may be chosen as  $2\pi*1.44$  k rad/s as per MF transformer design). After evaluating the switching functions, the effective output phase voltage can be calculated as:

$$V_{out}(t) = V_{pri}(t) \cdot S_{acac}(t) = \frac{n_2}{n_1} \cdot V_{dc} \cdot S_{inv}(t)$$

(7)

While the MPPT and zonal power balancer take care of shadowing effects between the two arrays in a single zone, power variation between the zones are taken care by regulating the zone output voltages depending on their power transfer capabilities, so that output current of all zones is the same. AC output voltages of the 'n' zones are subject to the condition:

$$\sum_{k=1}^{n} V_k = V_{grid} \tag{8}$$

where  $V_{grid}$  is the phase to neutral grid voltage and  $V_1, V_2... V_n$  are the AC-AC converter output voltage vectors of 'n' zones. Here,  $V_{grid} = 13200/\sqrt{3} = 7,621 \text{V}$  rms. If it is assumed that the phase angle of all zonal voltage vectors are equal under all conditions, the voltage magnitudes have to be varied in order to achieve the current same. But under shading conditions, the voltages will have to vary by large values to compensate for the power from PV arrays. This may lead to overrating of devices, reducing the device utilization. In order to facilitate better device utilization, the phase angles of the voltage vectors also need to be varied along with magnitude.

### 2.2.3. Switching Function Generation in Medium Frequency AC Link Converter

The medium frequency AC link converter may also be called a  $1\phi$  -  $1\phi$  matrix converter or a cycloconverter, since the high frequency voltage of the transformer secondary is converted into line frequency voltage. The switching function of the AC-AC converter is generated similar to a regular single phase inverter but a square wave forms the input to the converter, instead of a constant DC voltage as in the case of an inverter. Hence the switching function includes a rectifying component and a sinusoidal modulation component. The PWM gating signals generated may be through bipolar or unipolar modulation techniques. The carrier waveforms used are triangular since the

symmetrical nature of the pulses generated produces switching frequency harmonics at higher frequencies than sawtooth carriers. The carrier signals used in each of the cascaded cells in a multilevel inverter are phase shifted with respect to a reference cell, known as phase shifted carrier based PWM (PSC-PWM). The amount of phase shift applied to each carrier is dependent on the index of the inverter cell and the total number of cascaded cells. If N inverter cells are cascaded, the phase shift of the  $i^{th}$  cell with respect to the reference cell is  $\frac{2\pi}{N}(i-1)$  if N is odd (symmetrical PWM) and  $\frac{\pi}{N}(i-1)$  if N is even (asymmetrical PWM) [36].

## PWM Bipolar Modulation

The PWM bipolar modulation technique produces output voltage which has two possible states: positive output voltage and negative output voltage, i.e.  $+V_{dc}$  and  $-V_{dc}$ . This technique is simple but the output voltage waveform contains harmonics around  $m_f$ , where  $m_f = \frac{f_{sw}}{f_{line}}$  ( $f_{sw}$  is the carrier frequency). The generation of switching functions for devices in the transformer primary side inverter and the cycloconverter, discussed in the previous section, is discussed below.

Devices  $Q_1A_1$  through  $Q_1A_4$  can be imagined to be the four switches of a single phase inverter. To generate a bipolar output voltage, the modulating signal is compared with the triangular carrier and when the modulating signal is greater,  $Q_1A_1$  and  $Q_1A_2$  are switched on. This is shown in fig. 2.3 and the operation when the modulating signal is less than the carrier can be illustrated similarly. Since the input to the cycloconverter is a square wave and not a constant DC, the sine PWM operation is reversed when the input

voltage is negative. This is pictorially illustrated in fig. 2.4 and the switching functions of all the devices are listed in table 2.1. It is seen that there are four possible switching states for the inverter-cycloconverter combination.

If N inverter cells are cascaded, the output voltage of the cascaded multilevel inverter has switching frequency harmonics around  $f_{sw} \cdot N$ .

Fig. 2.3: PWM switching function generation using bipolar PWM technique for positive square wave voltage

Fig. 2.4: PWM switching function generation using bipolar PWM technique for negative square wave voltage

Table 2.1: Switching Functions for Devices in Primary Side Inverter and Cycloconverter for Bipolar Modulation

| Transformer<br>Voltage    | Primary-sio      | le Inverter      | Cycloconverter      |          |          |          |  |  |  |

|---------------------------|------------------|------------------|---------------------|----------|----------|----------|--|--|--|

|                           | $Q_{11}, Q_{12}$ | $Q_{13}, Q_{14}$ | $Q_1A_1$            | $Q_1A_2$ | $Q_1A_3$ | $Q_1A_4$ |  |  |  |

|                           |                  |                  | $V_{mod} > V_{tri}$ |          |          |          |  |  |  |

| Positive                  | 1                | 0                | 1                   | 1        | 0        | 0        |  |  |  |

| Negative                  | 0                | 1                | 0                   | 0        | 1        | 1        |  |  |  |

| $V_{ m mod} < V_{ m tri}$ |                  |                  |                     |          |          |          |  |  |  |

| Positive                  | 1                | 0                | 0                   | 0        | 1        | 1        |  |  |  |

| Negative                  | 0                | 1                | 1                   | 1        | 0        | 0        |  |  |  |

#### **PWM Unipolar Modulation**

The output voltage of a PWM inverter which uses unipolar modulation has three states:  $+V_{dc}$ , 0 and  $+V_{dc}$ . The modulating signals of the two bridges in a single phase inverter are phase shifted by  $180^{\circ}$  and the switching function for each bridge is independently generated. The switching frequency harmonics of a unipolar modulated inverter are present around  $2m_f$ , where  $m_f = \frac{f_{sw}}{f_{line}}$ . If N inverter cells are cascaded in the multilevel inverter, the output voltage contains switching frequency harmonics around  $f_{sw} \cdot 2N$ . The generation of switching functions is illustrated in fig. 2.5 and fig. 2.6. To generate a unipolar PWM for the cycloconverter, devices  $Q_1A_1$  and  $Q_1A_3$  are imagined to be part of one half-bridge; similar assignment is made to  $Q_1A_2$  and  $Q_1A_4$ . The modulating sinusoidal waveform for the second half bridge is  $180^{\circ}$  phase shifted from that of the first half bridge. All possible switching states in the primary side inverter and cycloconverter are given in table 2.2. There are eight switching states possible for the inverter-cycloconverter combination.

During the switching operation of the cycloconverter, it is possible that voltage spikes may be introduced, since more than one transition are involved in moving from one switching state to another and the current through the leakage inductance of the transformer is interrupted. To prevent this, an appropriate commutation scheme such as the one discussed in [37] may be used.

Fig. 2.5: PWM switching function generation using unipolar PWM technique for positive square wave voltage

Fig. 2.6: PWM switching function generation using unipolar PWM technique for negative square wave voltage

Table 2.2: Switching Functions for Devices in Primary Side Inverter and Cycloconverter for Unipolar Modulation

| Transformer | Primary-si       | de Inverter                       | Cycloconverter                     |                    |                                    |          |  |  |  |

|-------------|------------------|-----------------------------------|------------------------------------|--------------------|------------------------------------|----------|--|--|--|

| Voltage     | ·                |                                   |                                    |                    |                                    |          |  |  |  |

|             | $Q_{11}, Q_{12}$ | Q <sub>13</sub> , Q <sub>14</sub> | $Q_1A_1$                           | $Q_1A_3$           | $Q_1A_4$                           | $Q_1A_2$ |  |  |  |