# FAULT-TOLERANT PARTIAL-RESONANT HIGH-FREQUENCY AC-LINK CONVERTERS AND THEIR APPLICATIONS

## A Dissertation

by

## HAMIDREZA KEYHANI

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Chair of Committee, Hamid A. Toliyat Committee Members, Prasad Enjeti

Shankar Bhattacharyya

Won-Jong Kim

Head of Department, Chanan Singh

May 2014

Major Subject: Electrical Engineering

Copyright 2014 Hamidreza Keyhani

#### **ABSTRACT**

Recently, the demand for high-power-density converters with high efficiency and enhanced reliability has increased considerably. To address this demand, this dissertation introduces several low, medium, and high power converter topologies with high-frequency ac links and soft-switching operation, both with and without galvanic isolation. These converters can be in ac-ac, dc-ac, ac-dc, or dc-dc configurations to transfer power from the utility, energy storage systems, or renewable/alternative energy sources (e.g., photovoltaics, wind, and fuel cells) to stand-alone loads or the utility. The advantages of these topologies include soft switching at turn-on and turn-off of all the semiconductor devices, exclusion of short-life electrolytic capacitors in the link, step-up/down capability, and the use of a smallsized high-frequency transformer for galvanic isolation. The proposed converters are also able to generate output waveforms with arbitrary amplitude and frequency as well as achieving a high input power factor in the ac-ac and ac-dc configurations. Moreover, some of the introduced topologies have fault-tolerance capability, which may allow the converter to run even with one or more faulty switches. In this case, a partial failure will not result in the converter shutdown, and thus system availability is improved.

The high-frequency ac link of the introduced converters is composed of an ac inductor and small ac capacitor. The link inductor is responsible for transferring power, while the link capacitor realizes soft-switching operation. As the link components have low reactive ratings, the converters exhibit fast dynamic responses. The inductor can be replaced by an air-gapped high-frequency transformer to achieve galvanic isolation without the need for any snubber circuits. Due to operation at a high frequency, the link transformer is

substantially smaller in size and lower in weight compared to conventional line-frequency isolation transformers. In this work, the proposed power topologies are explained in detail, and their comprehensive analyses are given to reveal their functioning behavior in various working conditions. Simulation and experimental results at different operating points are also presented to verify the effectiveness of the introduced power converters.

To my beloved wife, Ghazal,

my devoted parents, Nasser and Shokouh,

and my dear siblings, Nazi, Alireza, and Amirreza.

#### **ACKNOWLEDGEMENTS**

I would like to express my gratitude and sincere thanks to my advisor and committee chair, Prof. Hamid A. Toliyat. His insight, deep knowledge, and encouragement guided me throughout the course of this research. His unlimited patience, understanding, and support are beyond my appreciation. I also would like to acknowledge my committee members, Dr. Enjeti, Dr. Bhattacharyya, and Dr. Kim for taking the time serving on my committee and for their valuable advice.

This research was funded in part by project # 08121-2901-01 from RPSEA (Research Partnership to Secure Energy for America) through GE Global Research. Under contract with the Department of Energy's National Energy Technology Laboratory, RPSEA currently manages "Ultra-Deepwater and Unconventional Natural Gas and Other Petroleum Resources Research and Development" program authorized by the U.S. Energy Policy Act of 2005. I would like to thank Dr. Rajib Datta, Dr. Rixin Lai, and Dr. Maja H. Todorovic from GE Global Research for their valued comments and suggestions during the course of the project.

My thanks are also extended to my fellow colleagues at the Advanced Electric Machine and Power Electronics (EMPE) Lab. Special thanks to Matthew Johnson, Vivek M. Sundaram, Yateendra Deshpande, and Jae-Bum Park for their help in this research.

Finally, I am deeply grateful to my father, mother, brothers, and sister for their endless love, support, and encouragement in all my endeavors. Especially, I am greatly indebted to my wife for her love and support. Without her, I could not have completed this study.

# TABLE OF CONTENTS

| F                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ii                         |

| DEDICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                           | iv                         |

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V                          |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                    | vi                         |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IX                         |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                       | xvii                       |

| 1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                          |

| 2. THE ISOLATED SOFT-SWITCHED HIGH-FREQUENCY AC-LINK CONVERTERS AND THEIR APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                               | 5                          |

| <ul> <li>2.1. Introduction</li> <li>2.2. An Isolated Resonant AC-Link Three-phase AC-AC Converter Using a Single High-Frequency Transformer</li> <li>2.2.1. Introduction</li> <li>2.2.2. The Proposed Topology</li> <li>2.2.2.1. The Control Scheme of the Converter</li> <li>2.2.2.2. The Switching Algorithm of the Converter</li> <li>2.2.3. The Converter Analysis and Design</li> <li>2.2.4. Simulation Results</li> <li>2.2.5. Experimental Results</li> </ul> | 6<br>9<br>10<br>11<br>16   |

| 2.3. Single-Stage Multi-String PV Inverter with an Isolated High-Frequency Link and Soft-Switching Operation  2.3.1. Introduction  2.3.2. The Proposed Multi-String PV Inverter  2.3.2.1. The Control Scheme and MPPT Operation  2.3.2.2. The Switching Algorithm of the Proposed Converter  2.3.2.3. The Soft Switching Operation  2.3.4. Experimental Results                                                                                                      | 30<br>33<br>34<br>37<br>42 |

| 3. THE TYPE-I REDUCED-SWITCH RESONANT HIGH-FREQUENCY AC-LINK CONVERTERS                                                                                                                                                                                                                                                                                                                                                                                              | 58                         |

| 3.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 58                         |

| Count.         58           3.2.1. Introduction         58           3.2.2. Topology Description         60           3.2.3. Principle of Operation         61           3.2.4. Analysis and Design         68           3.2.5. Simulation Results         76           3.2.6. Experimental Results         80           3.3. Partial-Resonant Buck-Boost and Flyback DC-DC Converters         84           3.3.1. Introduction         84           3.3.2. The Proposed Resonant DC-DC Converters         86           3.3.3. The Operation of the Proposed DC-DC Converters         88           3.3.3. The Operation of the Proposed DC-DC Converter         93           3.3.5. Experimental Results         100           3.4. Introduction         104           3.4.1. Introduction         104           3.4.2. The Proposed PV Inverter         105           3.4.3. The Principle of Operation         107           3.4.4. The Analysis and Optimal Design of the PV Inverter         110           3.4.5. Experimental Results         112           4. THE TYPE-II REDUCED-SWITCH RESONANT HIGH-FREQUENCY ACLINK CONVERTERS         114           4.1. Introduction         114           4.2.1. Introduction         114           4.2.2. The Proposed AC-AC Resonant Converter                                                             |          | lated ZVS High-Frequency-Link AC-AC Converter with a Reduced Switch |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------------------------------|-----|

| 3.2.2. Topology Description       60         3.2.3. Principle of Operation       61         3.2.4. Analysis and Design       68         3.2.5. Simulation Results       76         3.2.6. Experimental Results       80         3.3. Partial-Resonant Buck-Boost and Flyback DC-DC Converters       84         3.3.1. Introduction       84         3.3.2. The Proposed Resonant DC-DC Converters       86         3.3.3. The Operation of the Proposed DC-DC Converters       88         3.3.4. The Analysis of the DC-DC Converter       93         3.3.5. Experimental Results       100         3.4. A Soft-Switched Highly-Reliable Grid-Tied Inverter for PV Applications       104         3.4.1. Introduction       104         3.4.2. The Proposed PV Inverter       105         3.4.3. The Principle of Operation       107         3.4.4. The Analysis and Optimal Design of the PV Inverter       110         3.4.5. Experimental Results       112         4. THE TYPE-II REDUCED-SWITCH RESONANT HIGH-FREQUENCY ACLINK CONVERTERS       114         4.1. Introduction       114         4.2.1. Introduction       114         4.2.2. The Proposed AC-AC Resonant Converter       115         4.2.3. The Converter's Operation and ZVS in Different Line And Load Conditions       125                                                       | Co       | unt                                                                 | 58  |

| 3.2.3. Principle of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.2.1.   | Introduction                                                        | 58  |

| 3.2.4. Analysis and Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.2.2.   | Topology Description                                                | 60  |

| 3.2.5. Simulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.2.3.   | Principle of Operation                                              | 61  |

| 3.2.5. Simulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.2.4.   | 1 1                                                                 |     |

| 3.2.6. Experimental Results       80         3.3. Partial-Resonant Buck-Boost and Flyback DC-DC Converters       84         3.3.1. Introduction       84         3.3.2. The Proposed Resonant DC-DC Converters       86         3.3.3. The Operation of the Proposed DC-DC Converters       88         3.3.4. The Analysis of the DC-DC Converter       93         3.3.5. Experimental Results       100         3.4. A Soft-Switched Highly-Reliable Grid-Tied Inverter for PV Applications       104         3.4.1. Introduction       104         3.4.2. The Proposed PV Inverter       105         3.4.3. The Principle of Operation       107         3.4.5. Experimental Results       112         4. THE TYPE-II REDUCED-SWITCH RESONANT HIGH-FREQUENCY ACLINK CONVERTERS       114         4.1. Introduction       114         4.2.1. Introduction       114         4.2.2. The Proposed AC-AC Resonant Converter       115         4.2.3. The Converter's Operation and ZVS in Different Line And Load Conditions       123         4.2.4. The Analysis and Design of the Converter       125         4.2.5. Simulation Results       136         4.3. Step-Up/Down Three-Phase Resonant High-Frequency AC-Link Inverters       140         4.3.1. Introduction       140         4.3.2. Topology Description                                    | 3.2.5.   | · · · · · · · · · · · · · · · · · · ·                               |     |

| 3.3. Partial-Resonant Buck-Boost and Flyback DC-DC Converters       .84         3.3.1. Introduction       .84         3.3.2. The Proposed Resonant DC-DC Converters       .86         3.3.3. The Operation of the Proposed DC-DC Converters       .88         3.3.4. The Analysis of the DC-DC Converter       .93         3.3.5. Experimental Results       .100         3.4. A Soft-Switched Highly-Reliable Grid-Tied Inverter for PV Applications       .104         3.4.1. Introduction       .104         3.4.2. The Proposed PV Inverter       .105         3.4.3. The Principle of Operation       .107         3.4.4. The Analysis and Optimal Design of the PV Inverter       .110         3.4.5. Experimental Results       .112         4. THE TYPE-II REDUCED-SWITCH RESONANT HIGH-FREQUENCY ACLINK CONVERTERS       .114         4.1. Introduction       .114         4.2.1. Introduction       .114         4.2.2. The Proposed AC-AC Resonant Converter       .115         4.2.3. The Converter's Operation and ZVS in Different Line And Load Conditions       .123         4.2.4. The Analysis and Design of the Converter       .125         4.2.5. Simulation Results       .136         4.3. Step-Up/Down Three-Phase Resonant High-Frequency AC-Link Inverters       .140         4.3.1. Introduction       .140                    | 3.2.6.   |                                                                     |     |

| 3.3.1.       Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.3. Par | 1                                                                   |     |

| 3.3.2. The Proposed Resonant DC-DC Converters.       86         3.3.3. The Operation of the Proposed DC-DC Converters.       88         3.3.4. The Analysis of the DC-DC Converter.       93         3.3.5. Experimental Results       100         3.4. A Soft-Switched Highly-Reliable Grid-Tied Inverter for PV Applications.       104         3.4.1. Introduction.       104         3.4.2. The Proposed PV Inverter.       105         3.4.3. The Principle of Operation.       107         3.4.4. The Analysis and Optimal Design of the PV Inverter.       110         3.4.5. Experimental Results.       112         4. THE TYPE-II REDUCED-SWITCH RESONANT HIGH-FREQUENCY ACLINK CONVERTERS.       114         4.1. Introduction.       114         4.2. A Soft-Switched Three-Phase AC-AC Converter with a High-Frequency ACLINK.       114         4.2.1. Introduction.       114         4.2.2. The Proposed AC-AC Resonant Converter.       115         4.2.3. The Converter's Operation and ZVS in Different Line And Load Conditions.       123         4.2.4. The Analysis and Design of the Converter.       125         4.2.5. Simulation Results.       132         4.3.1. Introduction.       140         4.3.2. Topology Description.       142         4.3.3. The Operation of the Proposed Converters.       144                   |          |                                                                     |     |

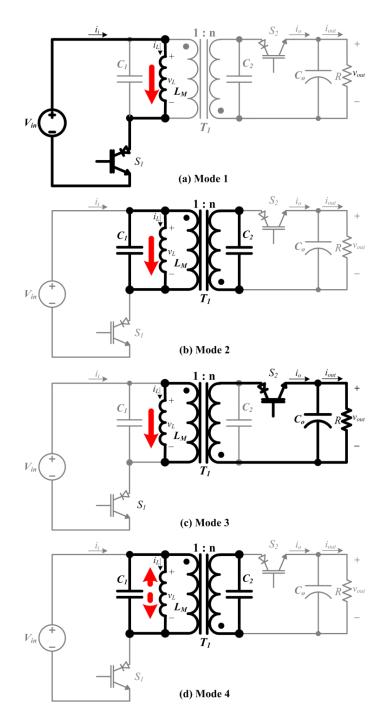

| 3.3.3.       The Operation of the Proposed DC-DC Converters       88         3.3.4.       The Analysis of the DC-DC Converter       93         3.3.5.       Experimental Results       100         3.4.       A Soft-Switched Highly-Reliable Grid-Tied Inverter for PV Applications       104         3.4.1.       Introduction       104         3.4.2.       The Proposed PV Inverter       105         3.4.3.       The Principle of Operation       107         3.4.4.       The Analysis and Optimal Design of the PV Inverter       110         3.4.5.       Experimental Results       112         4.       THE TYPE-II REDUCED-SWITCH RESONANT HIGH-FREQUENCY ACLINK CONVERTERS       114         4.1.       Introduction       114         4.2.       A Soft-Switched Three-Phase AC-AC Converter with a High-Frequency ACLINK       114         4.2.1.       Introduction       114         4.2.2.       The Proposed AC-AC Resonant Converter       115         4.2.3.       The Converter's Operation and ZVS in Different Line And Load Conditions       123         4.2.4.       The Analysis and Design of the Converter       125         4.2.5.       Simulation Results       136         4.3.       Step-Up/Down Three-Phase Resonant High-Frequency AC-Link Inverters                                                                | 3.3.2.   |                                                                     |     |

| 3.3.4. The Analysis of the DC-DC Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.3.   |                                                                     |     |

| 3.3.5.       Experimental Results       100         3.4.       A Soft-Switched Highly-Reliable Grid-Tied Inverter for PV Applications       104         3.4.1.       Introduction       104         3.4.2.       The Proposed PV Inverter       105         3.4.3.       The Principle of Operation       107         3.4.4.       The Analysis and Optimal Design of the PV Inverter       110         3.4.5.       Experimental Results       112         4.       THE TYPE-II REDUCED-SWITCH RESONANT HIGH-FREQUENCY ACLINK CONVERTERS       114         4.1.       Introduction       114         4.2.       A Soft-Switched Three-Phase AC-AC Converter with a High-Frequency ACLINK       114         4.2.1.       Introduction       114         4.2.2.       The Proposed AC-AC Resonant Converter       115         4.2.3.       The Converter's Operation and ZVS in Different Line And Load Conditions       123         4.2.4.       The Analysis and Design of the Converter       125         4.2.5.       Simulation Results       132         4.2.6.       Experimental Results       132         4.3.       Introduction       140         4.3.1.       Introduction       140         4.3.2.       Topology Description       142 </td <td></td> <td></td> <td></td>                                                                    |          |                                                                     |     |

| 3.4. A Soft-Switched Highly-Reliable Grid-Tied Inverter for PV Applications       104         3.4.1 Introduction       104         3.4.2 The Proposed PV Inverter       105         3.4.3 The Principle of Operation       107         3.4.4 The Analysis and Optimal Design of the PV Inverter       110         3.4.5 Experimental Results       112         4. THE TYPE-II REDUCED-SWITCH RESONANT HIGH-FREQUENCY ACLINK CONVERTERS       114         4.1. Introduction       114         4.2. A Soft-Switched Three-Phase AC-AC Converter with a High-Frequency ACLINK       114         4.2.1 Introduction       114         4.2.2 The Proposed AC-AC Resonant Converter       115         4.2.3 The Converter's Operation and ZVS in Different Line And Load Conditions       123         4.2.4 The Analysis and Design of the Converter       125         4.2.5 Simulation Results       132         4.2.6 Experimental Results       136         4.3.1 Introduction       140         4.3.2 Topology Description       142         4.3.3 The Operation of the Proposed Converters       144         4.3.4 Converter Analysis and Optimal Design       149         4.3.5 Simulation Results       155         4.3.6 Experimental Results       155         4.3.6 Experimental Results       155                                                    | 3.3.5.   |                                                                     |     |

| 3.4.1. Introduction       104         3.4.2. The Proposed PV Inverter       105         3.4.3. The Principle of Operation       107         3.4.4. The Analysis and Optimal Design of the PV Inverter       110         3.4.5. Experimental Results       112         4. THE TYPE-II REDUCED-SWITCH RESONANT HIGH-FREQUENCY ACLINK CONVERTERS       114         4.1. Introduction       114         4.2. A Soft-Switched Three-Phase AC-AC Converter with a High-Frequency ACLINK       114         4.2.1. Introduction       114         4.2.2. The Proposed AC-AC Resonant Converter       115         4.2.3. The Converter's Operation and ZVS in Different Line And Load Conditions       123         4.2.4. The Analysis and Design of the Converter       125         4.2.5. Simulation Results       132         4.2.6. Experimental Results       136         4.3.1. Introduction       140         4.3.2. Topology Description       142         4.3.3. The Operation of the Proposed Converters       144         4.3.4. Converter Analysis and Optimal Design       149         4.3.5. Simulation Results       155         4.3.6. Experimental Results       155         4.3.6. Experimental Results       155         4.4.1 Introduction       161         4.4.2. The Proposed M                                                             |          |                                                                     |     |

| 3.4.2. The Proposed PV Inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                                                     |     |

| 3.4.3. The Principle of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |                                                                     |     |

| 3.4.4. The Analysis and Optimal Design of the PV Inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | 1                                                                   |     |

| 3.4.5. Experimental Results       112         4. THE TYPE-II REDUCED-SWITCH RESONANT HIGH-FREQUENCY ACLINK CONVERTERS       114         4.1. Introduction       114         4.2. A Soft-Switched Three-Phase AC-AC Converter with a High-Frequency AC Link       114         4.2.1. Introduction       114         4.2.2. The Proposed AC-AC Resonant Converter       115         4.2.3. The Converter's Operation and ZVS in Different Line And Load Conditions       123         4.2.4. The Analysis and Design of the Converter       125         4.2.5. Simulation Results       132         4.2.6. Experimental Results       136         4.3. Step-Up/Down Three-Phase Resonant High-Frequency AC-Link Inverters       140         4.3.1. Introduction       140         4.3.2. Topology Description       142         4.3.3. The Operation of the Proposed Converters       144         4.3.4. Converter Analysis and Optimal Design       149         4.3.5. Simulation Results       155         4.3.6. Experimental Results       155         4.4. A ZVS Single-Inductor Multi-Input Multi-Output DC-DC Converter with the Step Up/Down Capability       161         4.4.1. Introduction       161         4.4.2. The Proposed MIMO DC-DC Converter       163         4.4.3. The Principle of Operation       165 <td></td> <td></td> <td></td> |          |                                                                     |     |

| 4. THE TYPE-II REDUCED-SWITCH RESONANT HIGH-FREQUENCY ACLINK CONVERTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |                                                                     |     |

| 4.2. A Soft-Switched Three-Phase AC-AC Converter with a High-Frequency AC Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LINK     | CONVERTERS                                                          |     |

| Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                                                     | 114 |

| 4.2.1.Introduction1144.2.2.The Proposed AC-AC Resonant Converter1154.2.3.The Converter's Operation and ZVS in Different Line And Load<br>Conditions1234.2.4.The Analysis and Design of the Converter1254.2.5.Simulation Results1324.2.6.Experimental Results1364.3.Step-Up/Down Three-Phase Resonant High-Frequency AC-Link Inverters1404.3.1.Introduction1404.3.2.Topology Description1424.3.3.The Operation of the Proposed Converters1444.3.4.Converter Analysis and Optimal Design1494.3.5.Simulation Results1554.3.6.Experimental Results1594.4.A ZVS Single-Inductor Multi-Input Multi-Output DC-DC Converter with the<br>Step Up/Down Capability1614.4.1.Introduction1614.4.2.The Proposed MIMO DC-DC Converter1634.4.3.The Principle of Operation165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |                                                                     | 114 |

| 4.2.2. The Proposed AC-AC Resonant Converter1154.2.3. The Converter's Operation and ZVS in Different Line And Load<br>Conditions1234.2.4. The Analysis and Design of the Converter1254.2.5. Simulation Results1324.2.6. Experimental Results1364.3. Step-Up/Down Three-Phase Resonant High-Frequency AC-Link Inverters1404.3.1. Introduction1404.3.2. Topology Description1424.3.3. The Operation of the Proposed Converters1444.3.4. Converter Analysis and Optimal Design1494.3.5. Simulation Results1554.3.6. Experimental Results1594.4. A ZVS Single-Inductor Multi-Input Multi-Output DC-DC Converter with the<br>Step Up/Down Capability1614.4.1. Introduction1614.4.2. The Proposed MIMO DC-DC Converter1634.4.3. The Principle of Operation165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |                                                                     |     |

| 4.2.3. The Converter's Operation and ZVS in Different Line And Load Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |                                                                     |     |

| Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | <u>*</u>                                                            | 113 |

| 4.2.4. The Analysis and Design of the Converter1254.2.5. Simulation Results1324.2.6. Experimental Results1364.3. Step-Up/Down Three-Phase Resonant High-Frequency AC-Link Inverters1404.3.1. Introduction1404.3.2. Topology Description1424.3.3. The Operation of the Proposed Converters1444.3.4. Converter Analysis and Optimal Design1494.3.5. Simulation Results1554.3.6. Experimental Results1594.4. A ZVS Single-Inductor Multi-Input Multi-Output DC-DC Converter with the Step Up/Down Capability1614.4.1. Introduction1614.4.2. The Proposed MIMO DC-DC Converter1634.4.3. The Principle of Operation165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.2.5.   | <u>*</u>                                                            | 123 |

| 4.2.5. Simulation Results1324.2.6. Experimental Results1364.3. Step-Up/Down Three-Phase Resonant High-Frequency AC-Link Inverters1404.3.1. Introduction1404.3.2. Topology Description1424.3.3. The Operation of the Proposed Converters1444.3.4. Converter Analysis and Optimal Design1494.3.5. Simulation Results1554.3.6. Experimental Results1594.4. A ZVS Single-Inductor Multi-Input Multi-Output DC-DC Converter with the<br>Step Up/Down Capability1614.4.1. Introduction1614.4.2. The Proposed MIMO DC-DC Converter1634.4.3. The Principle of Operation165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 424      |                                                                     |     |

| 4.2.6. Experimental Results1364.3. Step-Up/Down Three-Phase Resonant High-Frequency AC-Link Inverters1404.3.1. Introduction1404.3.2. Topology Description1424.3.3. The Operation of the Proposed Converters1444.3.4. Converter Analysis and Optimal Design1494.3.5. Simulation Results1554.3.6. Experimental Results1594.4. A ZVS Single-Inductor Multi-Input Multi-Output DC-DC Converter with the<br>Step Up/Down Capability1614.4.1. Introduction1614.4.2. The Proposed MIMO DC-DC Converter1634.4.3. The Principle of Operation165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |                                                                     |     |

| 4.3. Step-Up/Down Three-Phase Resonant High-Frequency AC-Link Inverters1404.3.1. Introduction1404.3.2. Topology Description1424.3.3. The Operation of the Proposed Converters1444.3.4. Converter Analysis and Optimal Design1494.3.5. Simulation Results1554.3.6. Experimental Results1594.4. A ZVS Single-Inductor Multi-Input Multi-Output DC-DC Converter with the<br>Step Up/Down Capability1614.4.1. Introduction1614.4.2. The Proposed MIMO DC-DC Converter1634.4.3. The Principle of Operation165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                                                                     |     |

| 4.3.1. Introduction1404.3.2. Topology Description1424.3.3. The Operation of the Proposed Converters1444.3.4. Converter Analysis and Optimal Design1494.3.5. Simulation Results1554.3.6. Experimental Results1594.4. A ZVS Single-Inductor Multi-Input Multi-Output DC-DC Converter with the<br>Step Up/Down Capability1614.4.1. Introduction1614.4.2. The Proposed MIMO DC-DC Converter1634.4.3. The Principle of Operation165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |                                                                     |     |

| 4.3.2. Topology Description1424.3.3. The Operation of the Proposed Converters1444.3.4. Converter Analysis and Optimal Design1494.3.5. Simulation Results1554.3.6. Experimental Results1594.4. A ZVS Single-Inductor Multi-Input Multi-Output DC-DC Converter with the<br>Step Up/Down Capability1614.4.1. Introduction1614.4.2. The Proposed MIMO DC-DC Converter1634.4.3. The Principle of Operation165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                                                                     |     |

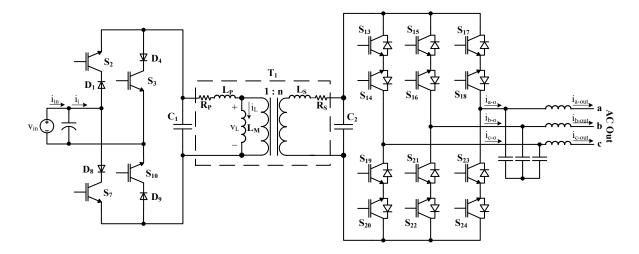

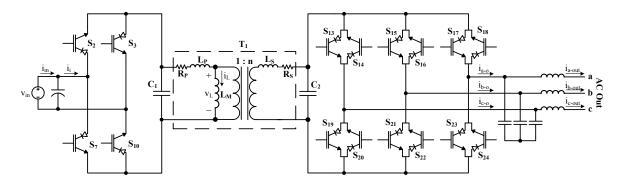

| 4.3.3. The Operation of the Proposed Converters1444.3.4. Converter Analysis and Optimal Design1494.3.5. Simulation Results1554.3.6. Experimental Results1594.4. A ZVS Single-Inductor Multi-Input Multi-Output DC-DC Converter with the<br>Step Up/Down Capability1614.4.1. Introduction1614.4.2. The Proposed MIMO DC-DC Converter1634.4.3. The Principle of Operation165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |                                                                     |     |

| 4.3.4. Converter Analysis and Optimal Design1494.3.5. Simulation Results1554.3.6. Experimental Results1594.4. A ZVS Single-Inductor Multi-Input Multi-Output DC-DC Converter with the<br>Step Up/Down Capability1614.4.1. Introduction1614.4.2. The Proposed MIMO DC-DC Converter1634.4.3. The Principle of Operation165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | 1 65 1                                                              |     |

| 4.3.5. Simulation Results1554.3.6. Experimental Results1594.4. A ZVS Single-Inductor Multi-Input Multi-Output DC-DC Converter with the<br>Step Up/Down Capability1614.4.1. Introduction1614.4.2. The Proposed MIMO DC-DC Converter1634.4.3. The Principle of Operation165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |                                                                     |     |

| 4.3.6. Experimental Results1594.4. A ZVS Single-Inductor Multi-Input Multi-Output DC-DC Converter with the<br>Step Up/Down Capability1614.4.1. Introduction1614.4.2. The Proposed MIMO DC-DC Converter1634.4.3. The Principle of Operation165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |                                                                     |     |

| 4.4. A ZVS Single-Inductor Multi-Input Multi-Output DC-DC Converter with the<br>Step Up/Down Capability1614.4.1. Introduction1614.4.2. The Proposed MIMO DC-DC Converter1634.4.3. The Principle of Operation165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                                                     |     |

| Step Up/Down Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |                                                                     | 109 |

| 4.4.1. Introduction1614.4.2. The Proposed MIMO DC-DC Converter1634.4.3. The Principle of Operation165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |                                                                     | 161 |

| 4.4.2. The Proposed MIMO DC-DC Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                                                                     |     |

| 4.4.3. The Principle of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |                                                                     |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                                                     |     |

| 1, 1, 1, 1. LADCIIIICIIMI ICCUMIU 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.4.4.   |                                                                     |     |

| 5. FAULT-TOLERANCE ABILITY OF THE PROPOSED HIGH-FREQUENCE                     | CY   |

|-------------------------------------------------------------------------------|------|

| AC-LINK CONVERTER                                                             | 172  |

|                                                                               |      |

| 5.1. Introduction                                                             | 172  |

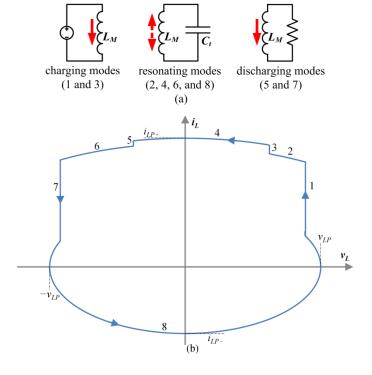

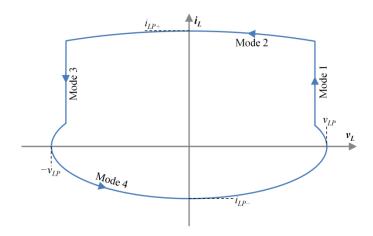

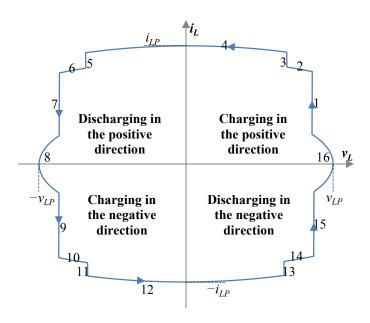

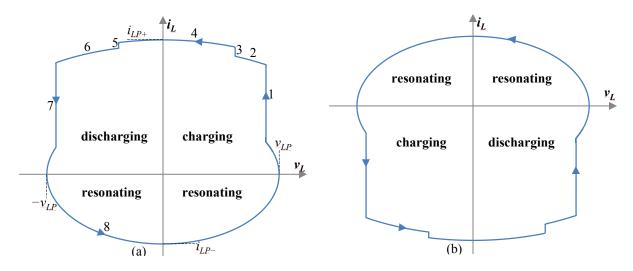

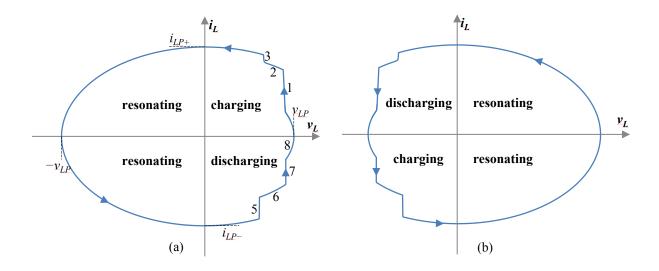

| 5.2. The State-Plane Diagram of the Proposed Original, Type-I, and Type-II So | oft- |

| Switched HFAC-Link Topologies                                                 | 172  |

| 5.3. Categorizing the Switch Faults in the Partial-Resonant High-Frequency AC |      |

| Converter                                                                     | 174  |

| 5.4. Case I: An Input-Side Switch or Load-Side Switch Remains Open            | 177  |

| 5.5. Case II: An Input-Side Switch Remains Closed                             | 181  |

| 5.6. Case III: A Load-Side Switch Remains Closed                              | 182  |

|                                                                               |      |

| 6. CONCLUSIONS AND FUTURE WORK                                                | 185  |

|                                                                               |      |

| REFERENCES                                                                    | 187  |

# LIST OF FIGURES

| Pa                                                                                                                                                                                | age  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

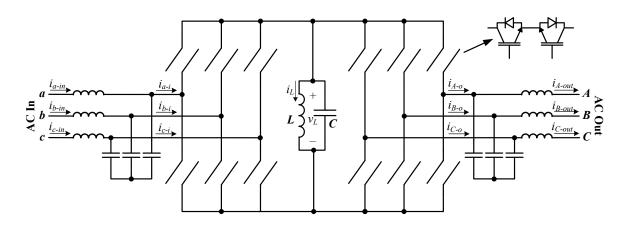

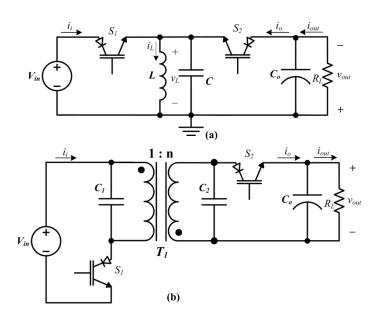

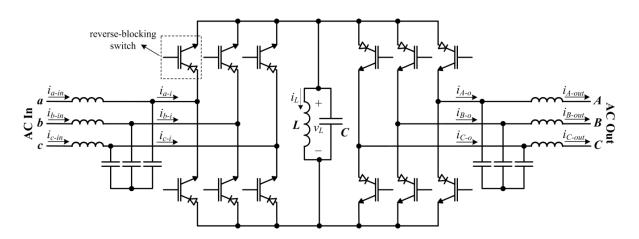

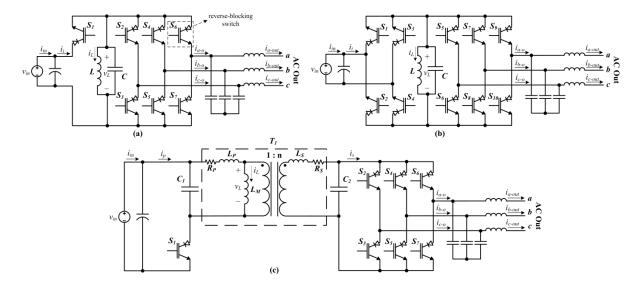

| Fig. 1.1. The basic soft-switched high-frequency ac-link power converter                                                                                                          | 3    |

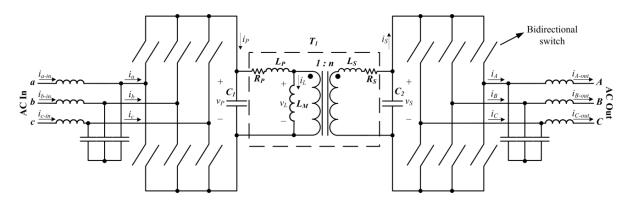

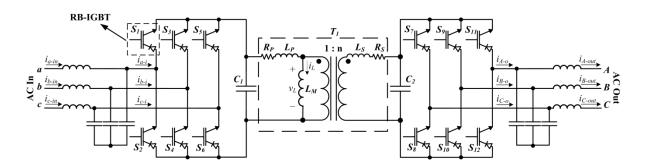

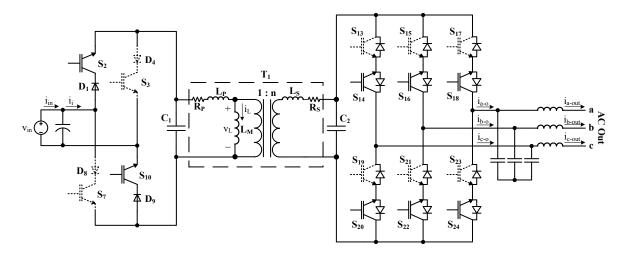

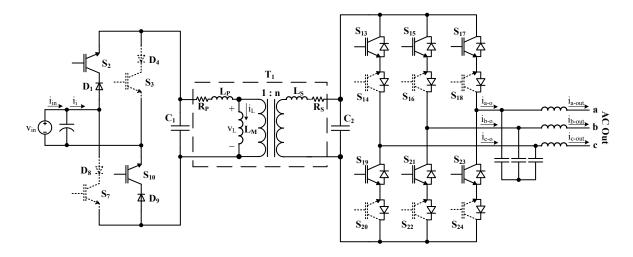

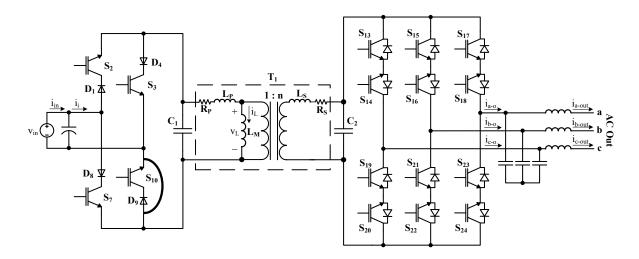

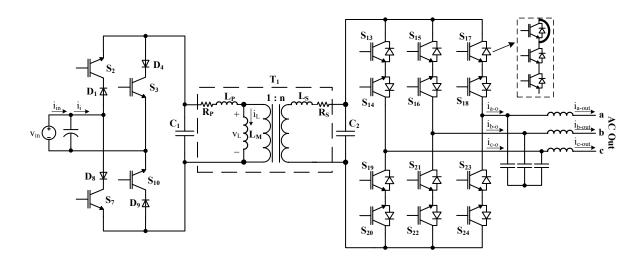

| Fig. 2.1. The isolated parallel-resonant HFAC-link ac-ac converter.                                                                                                               | 9    |

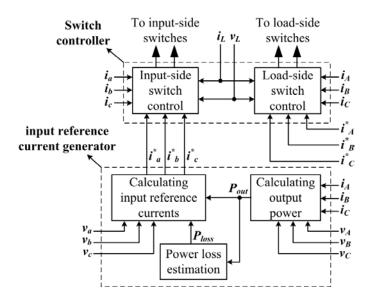

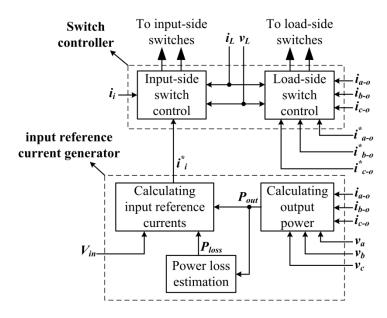

| Fig. 2.2. The control scheme of the proposed converter.                                                                                                                           | . 10 |

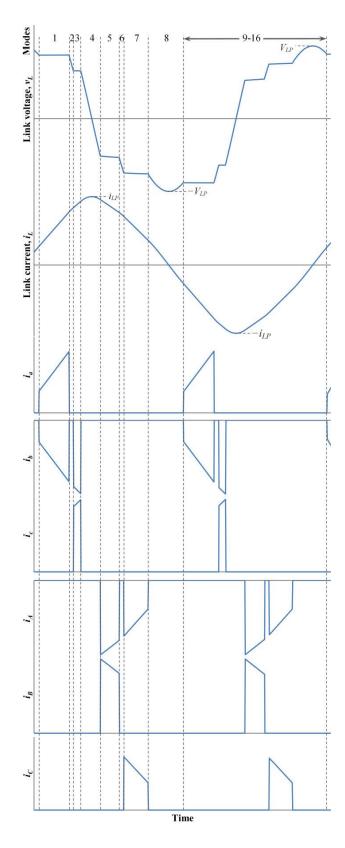

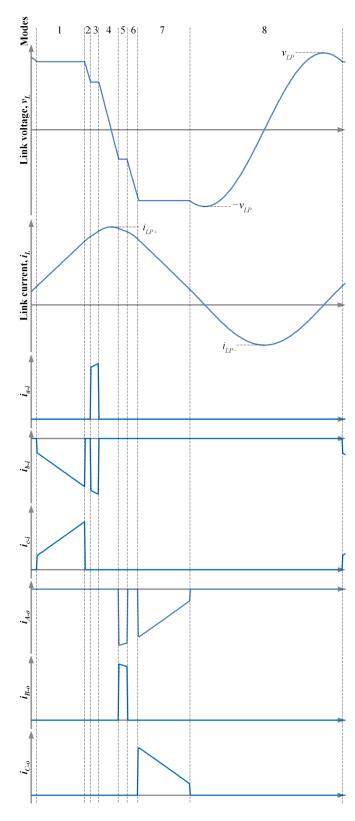

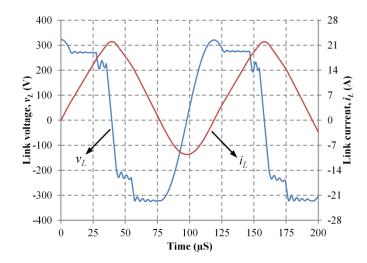

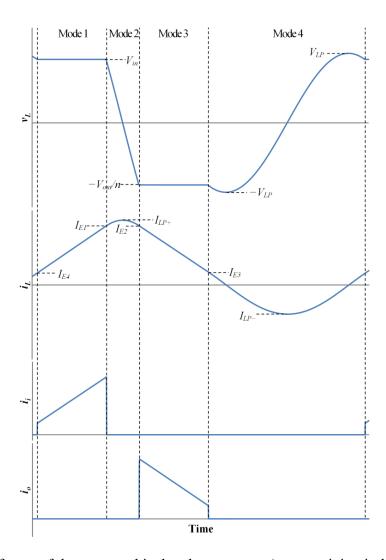

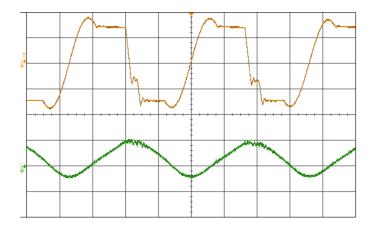

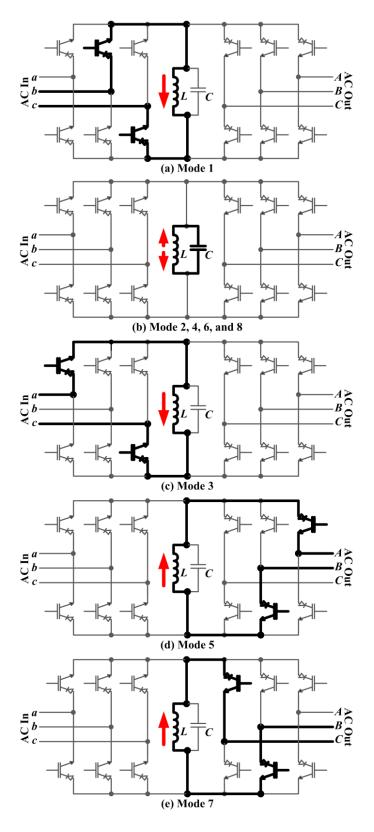

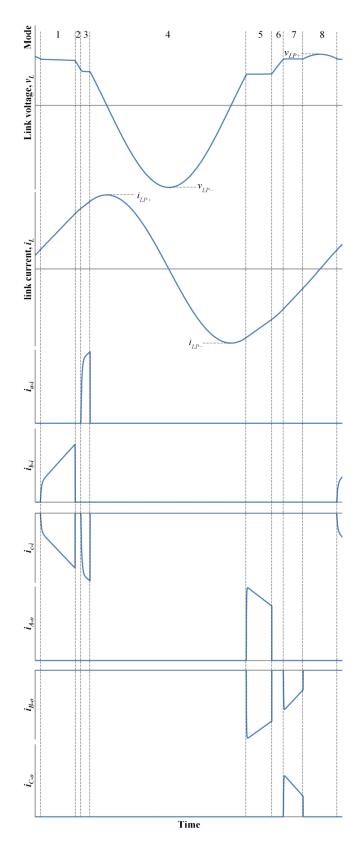

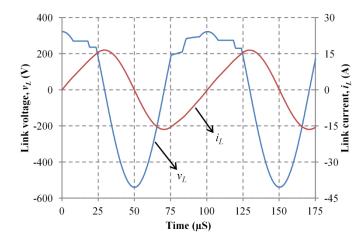

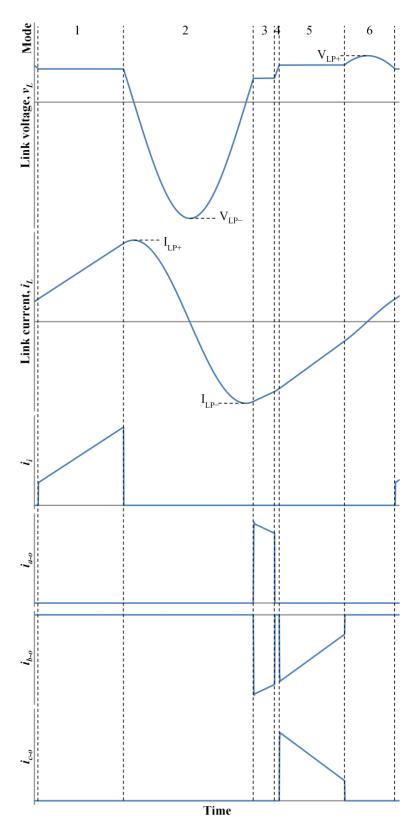

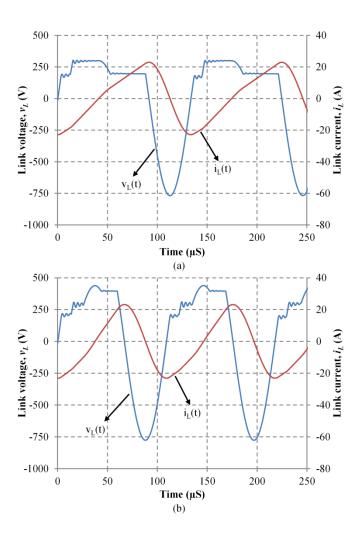

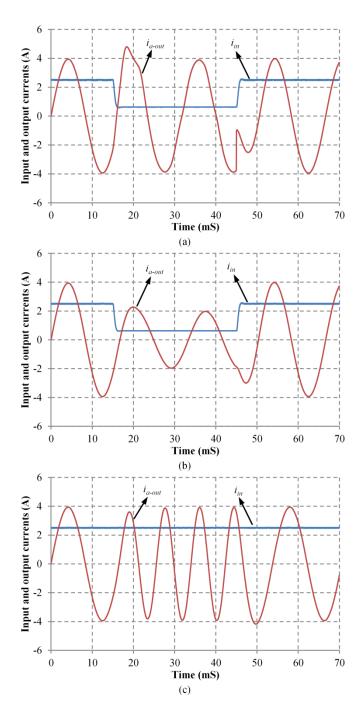

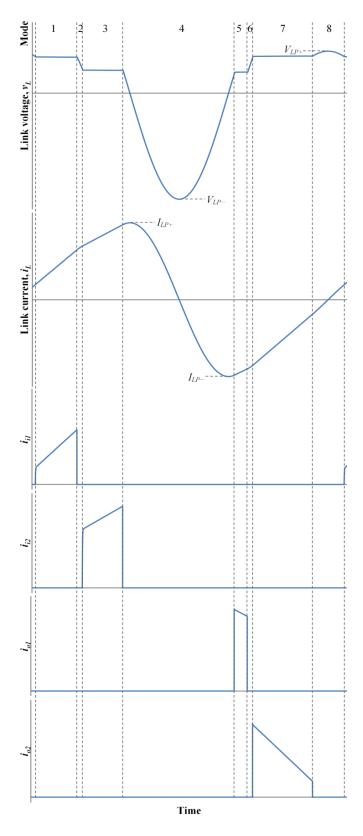

| Fig. 2.3. Typical waveforms of the converter. (a) link voltage, (b) link current, (c-e) input currents, and (f-h) output currents.                                                | . 12 |

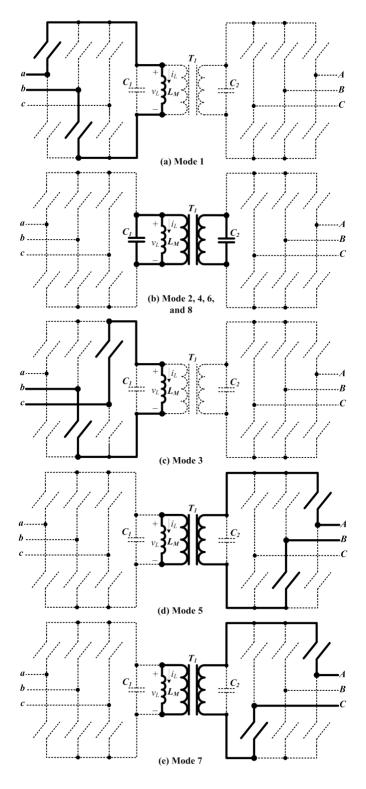

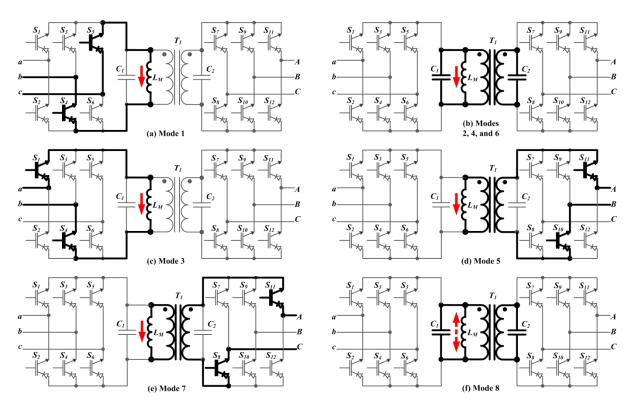

| Fig. 2.4. Typical operating modes of the converter.                                                                                                                               | . 13 |

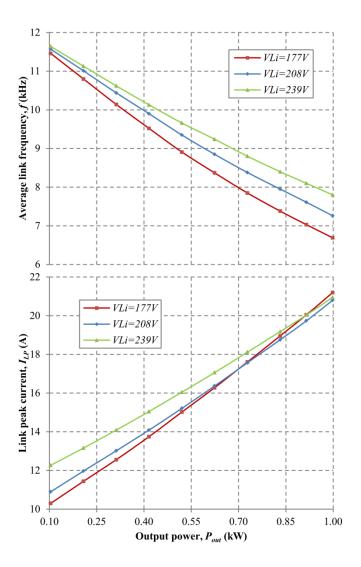

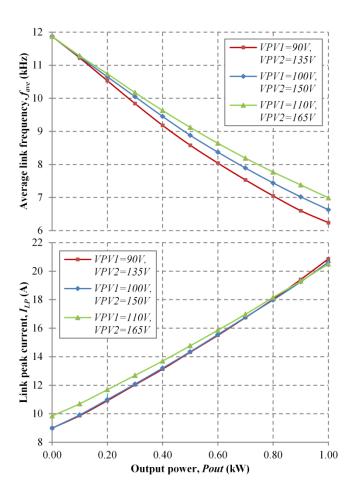

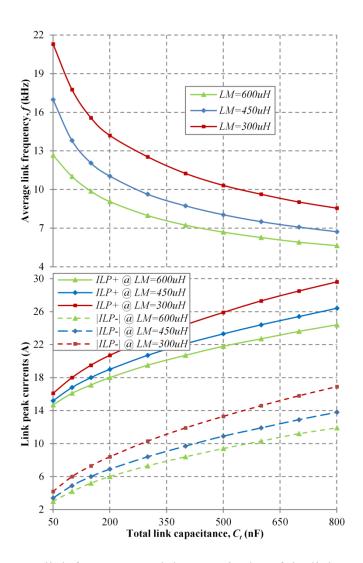

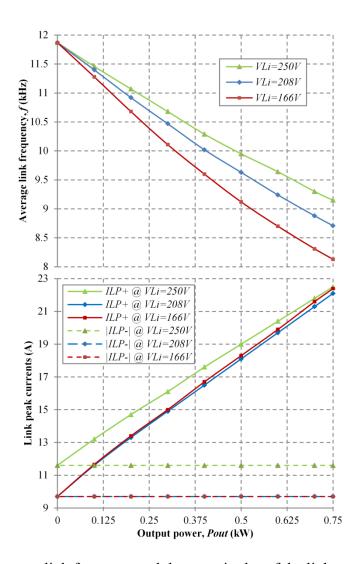

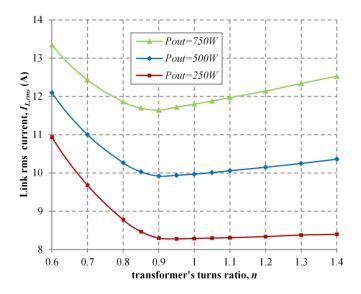

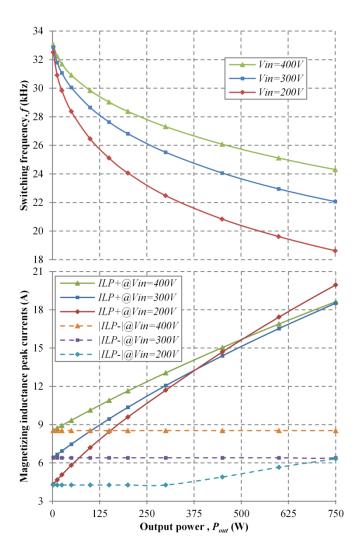

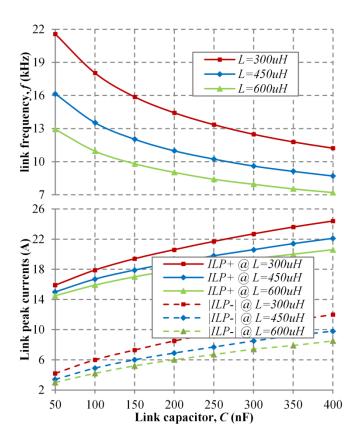

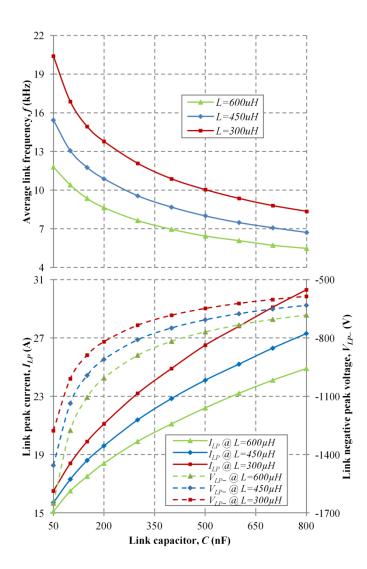

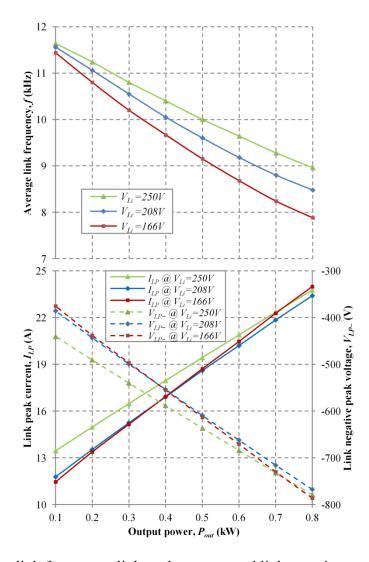

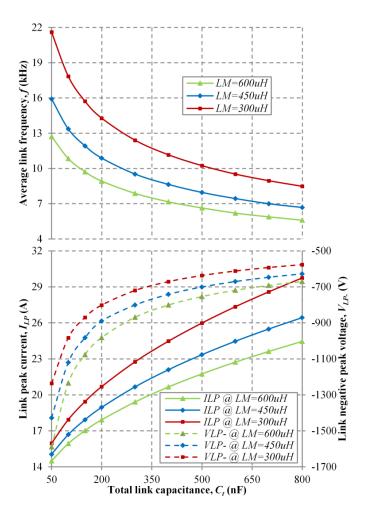

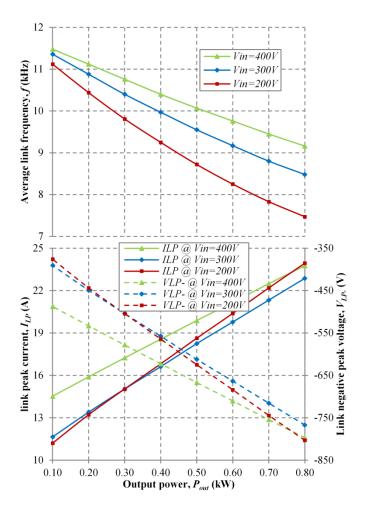

| Fig. 2.5. Average link frequency and link peak current versus output power for various values of the input line voltage, VLo=208V, LM=450µH, C1=C2=200nF, and n=1.                | . 20 |

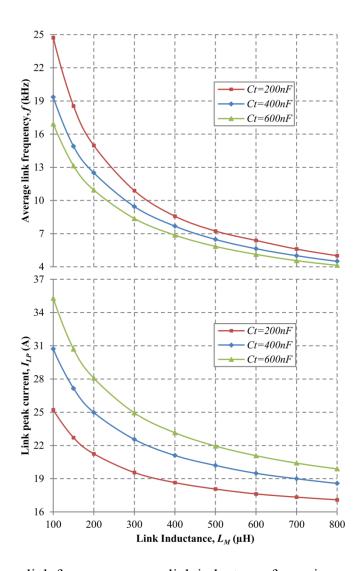

| Fig. 2.6. Average link frequency versus link inductance for various values of the total effective link capacitance, VLi=VLo=208V, Pout=1kW, and n=1                               | . 21 |

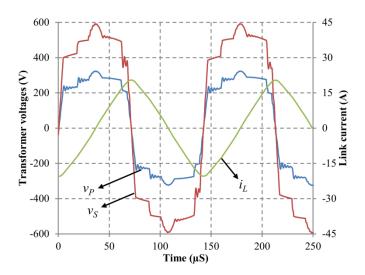

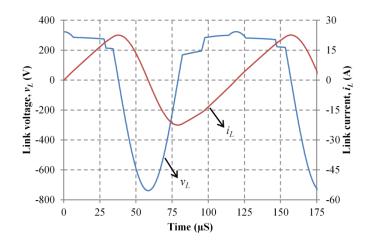

| Fig. 2.7. Simulation results of the proposed converter at 1.25kVA, transformer primary and secondary voltage, and link current.                                                   | . 24 |

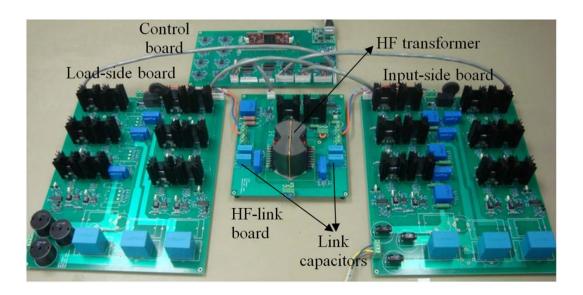

| Fig. 2.8. The 1.25kVA experimental prototype of the introduced converter                                                                                                          | . 24 |

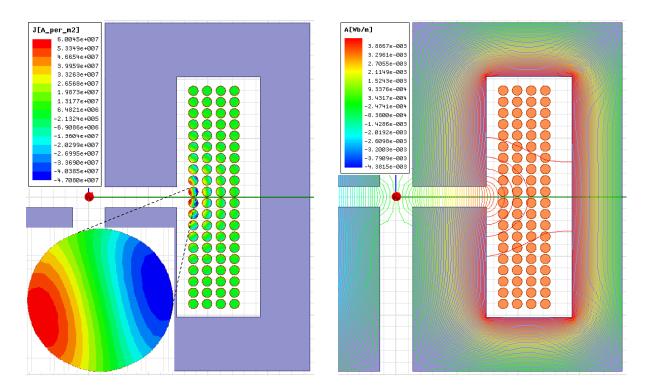

| Fig. 2.9. FEA Analysis of the HF Transformer.                                                                                                                                     | . 27 |

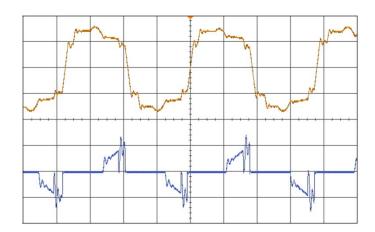

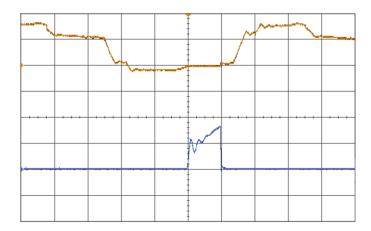

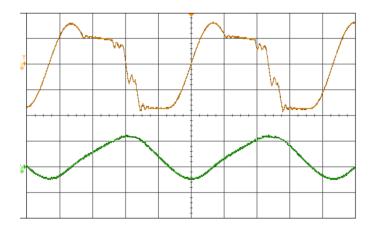

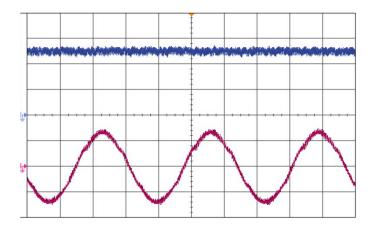

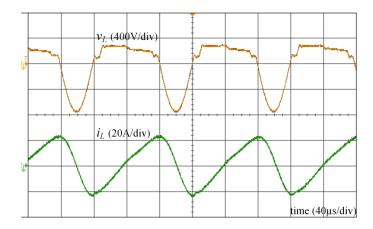

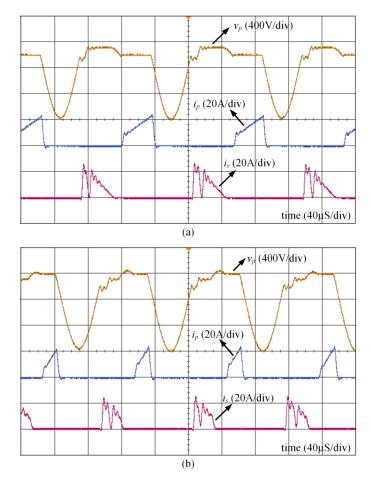

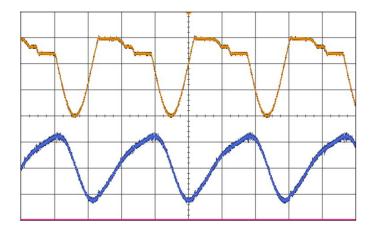

| Fig. 2.10. Experimental results of the converter at 1.25kVA. Top: transformer primary voltage, vp (200V/div), bottom: link input current, ip (20A/div) versus time (40µs/div).    | . 27 |

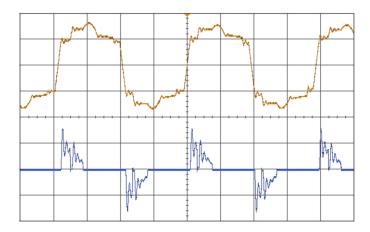

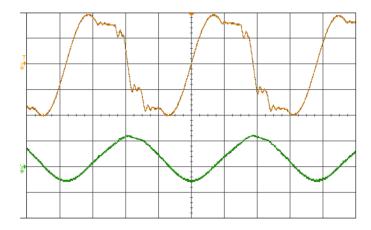

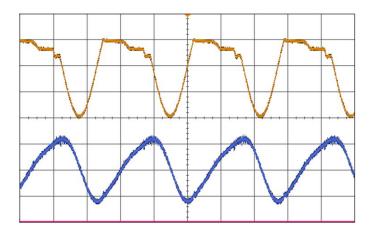

| Fig. 2.11. Experimental results of the converter at 1.25kVA. Top: transformer secondary voltage, vs (400V/div), bottom: link output current, is (20A/div) versus time (40µs/div). | . 28 |

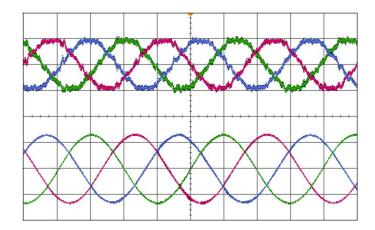

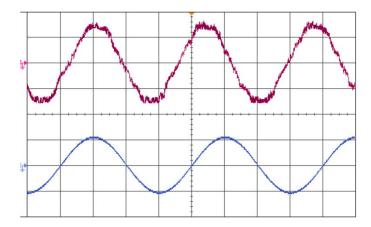

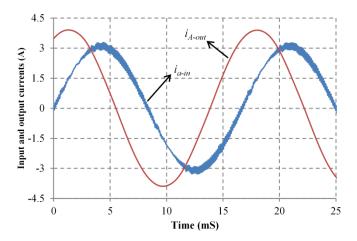

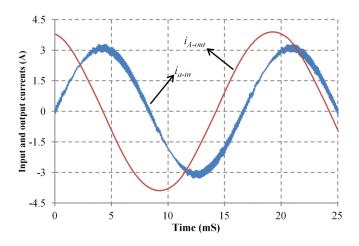

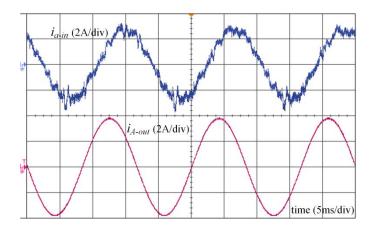

| Fig. 2.12. Experimental results of the converter at 1.25kVA. Top: three-phase input currents (4A/div), bottom: three-phase output current (2A/div) versus time (5ms/div).         | . 28 |

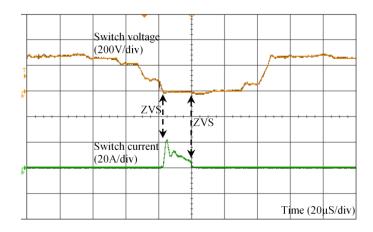

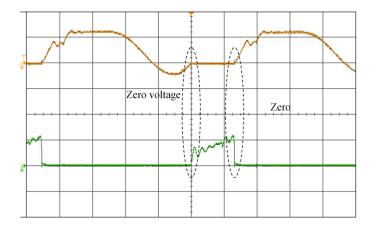

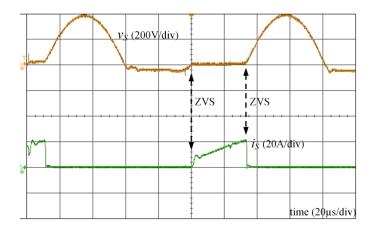

| Fig. 2.13. Experimental results of an input-side switch. Top: switch voltage (200V/div), bottom: switch current (10A/div) versus time (20μS/div)                                  | . 29 |

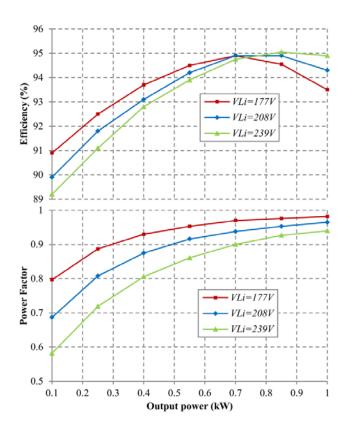

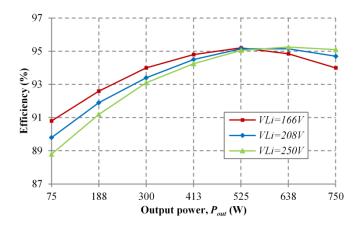

| Fig. 2.14. Efficiency and power factor of the converter prototype versus output power for different values of the input line voltage.                                             | . 30 |

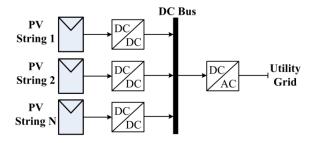

| Fig. | 2.15. | The conventional multi-string configuration.                                                                                                                                                        | 32 |

|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

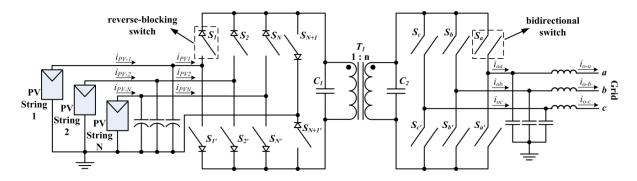

| Fig. | 2.16. | The soft-switched HFAC-link N-string PV inverter.                                                                                                                                                   | 33 |

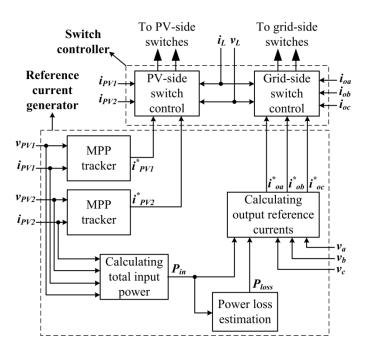

| Fig. | 2.17. | Control scheme of the proposed multi-string PV inverter                                                                                                                                             | 35 |

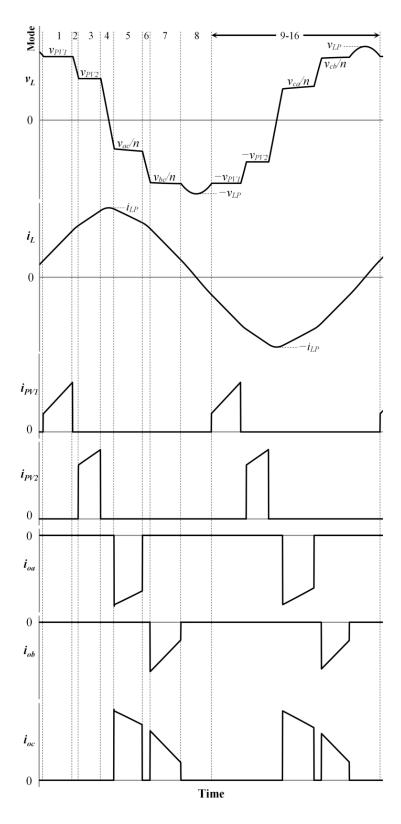

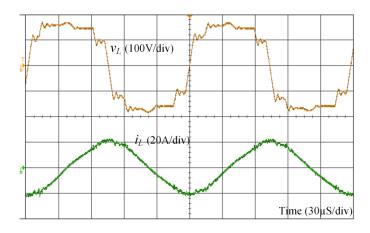

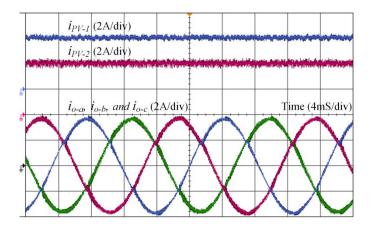

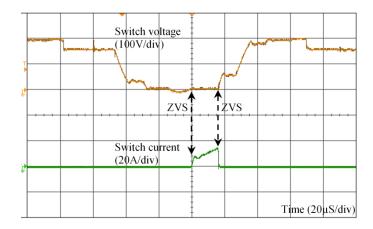

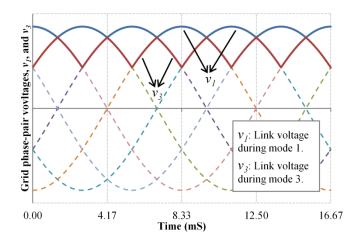

| Fig. | 2.18. | Typical waveforms of the inverter at the instant that vPV1>vPV2, and vcn>0>van>vbn. (a) link voltage, (b) link current, (c-d) unfiltered PV-side currents, and (e-g) unfiltered grid-side currents. | 38 |

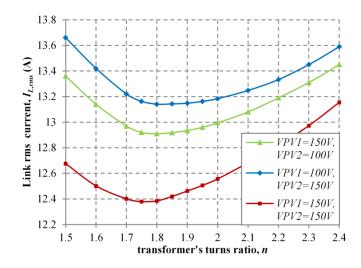

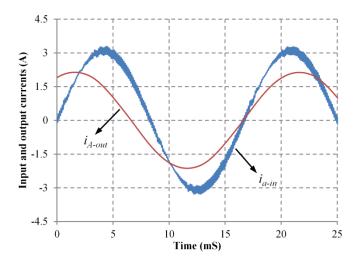

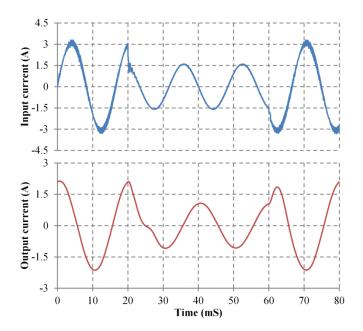

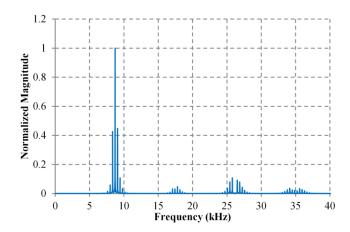

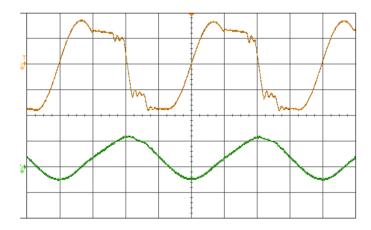

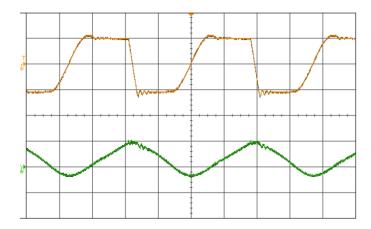

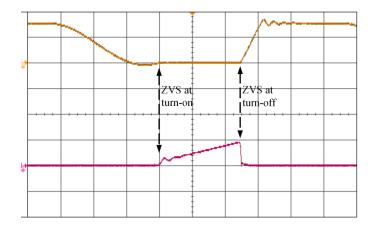

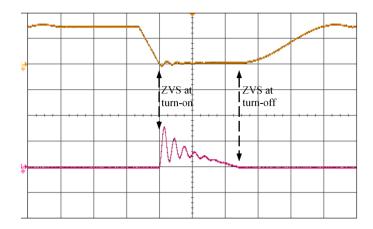

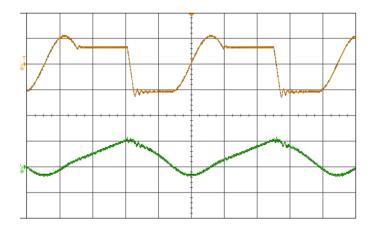

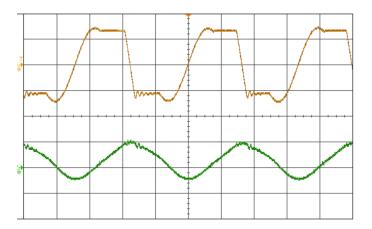

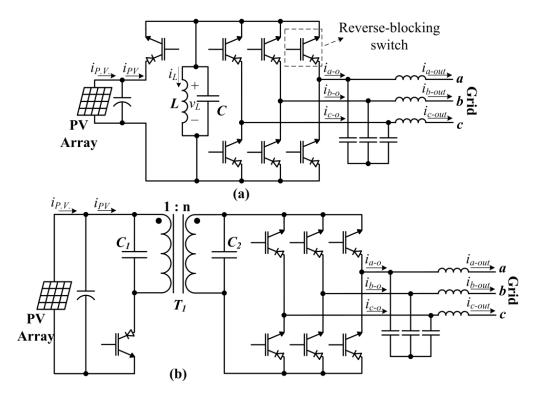

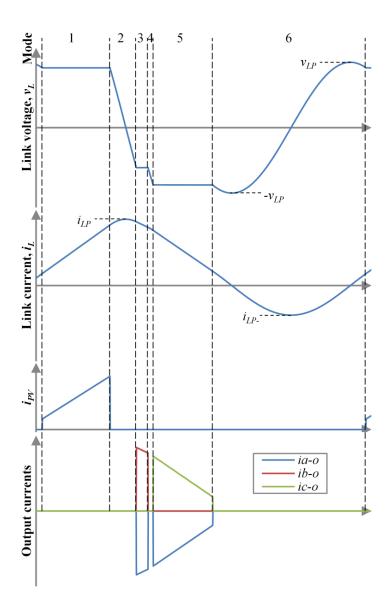

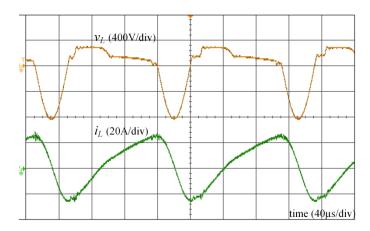

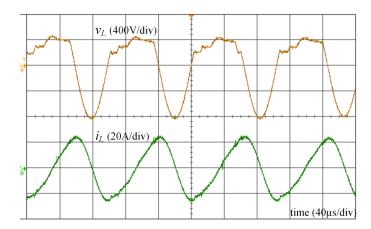

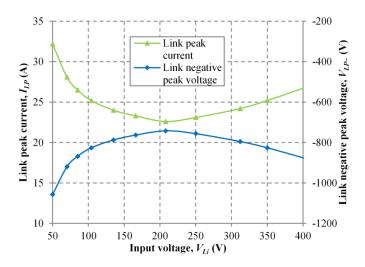

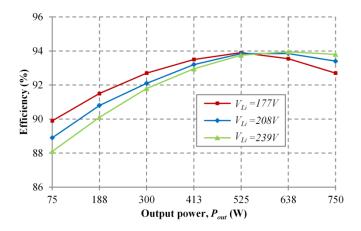

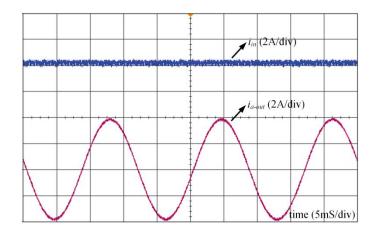

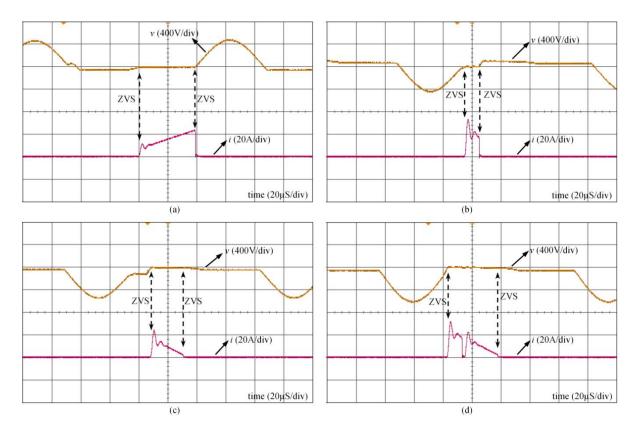

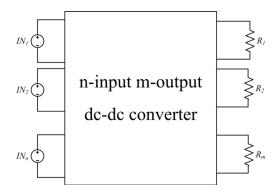

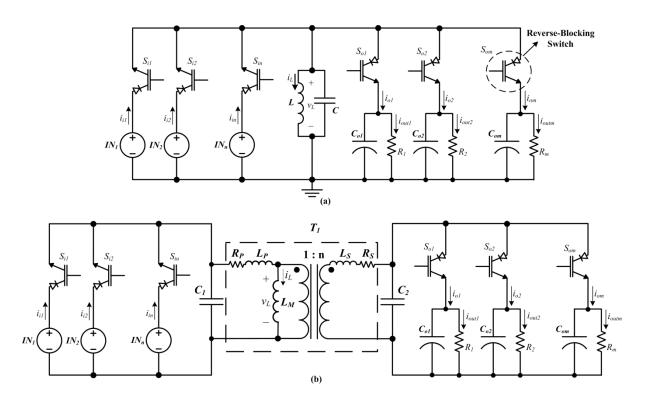

| Fig. | 2.19. | Average link frequency and link peak current versus link inductance for different total link capacitance, VPV1=150V, VPV2=100V, VLo=208V, PPV1=600W, PPV2=400W, and n=1.8.                          | 46 |