# SCALABLE PARALLEL ALGORITHMS FOR MASSIVE SCALE-FREE GRAPHS

A Dissertation

by

# ROGER ALLAN PEARCE

# Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

| Chair of Committee, | Nancy M. Amato       |

|---------------------|----------------------|

| Committee Members,  | Yoonsuck Choe        |

|                     | Lawrence Rauchwerger |

|                     | Marvin L. Adams      |

|                     | Maya Gokhale         |

| Head of Department, | Nancy M. Amato       |

December 2013

Major Subject: Computer Science

Copyright 2013 Roger Allan Pearce

### ABSTRACT

Efficiently storing and processing massive graph data sets is a challenging problem as researchers seek to leverage "Big Data" to answer next-generation scientific questions. New techniques are required to process large scale-free graphs in shared, distributed, and external memory. This dissertation develops new techniques to parallelize the storage, computation, and communication for scale-free graphs with high-degree vertices. Our work facilitates the processing of large real-world graph datasets through the development of parallel algorithms and tools that scale to large computational and memory resources, overcoming challenges not addressed by existing techniques. Our aim is to scale to trillions of edges, and our research is targeted at leadership class supercomputers, clusters with local non-volatile memory, and shared memory systems.

We present three novel techniques to address scaling challenges in processing large scale-free graphs. We apply an asynchronous graph traversal technique using prioritized visitor queues that is capable of tolerating data latencies to the external graph storage media and message passing communication. To accommodate large high-degree vertices, we present an edge list partitioning technique that evenly partitions graphs containing high-degree vertices. Finally, we propose a technique we call distributed delegates that distributes and parallelizes the storage, computation, and communication when processing high-degree vertices. The edges of high-degree vertices are distributed, providing additional opportunities for parallelism not present in existing methods.

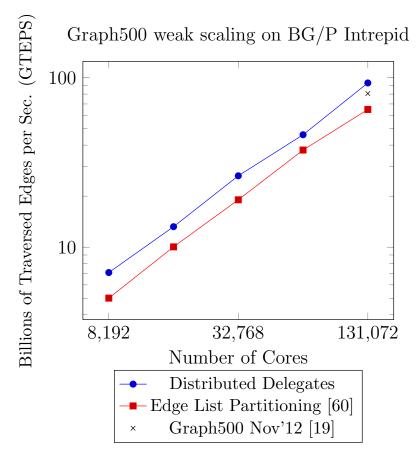

We apply our techniques to multiple graph algorithms: Breadth-First Search, Single Source Shortest Path, Connected Components, K-Core decomposition, Triangle Counting, and Page Rank. Our experimental study of these algorithms demonstrates excellent scalability on supercomputers, clusters with non-volatile memory, and shared memory systems. Our study includes multiple synthetic scale-free graph models, the largest of which has trillion edges, and real-world input graphs. On a supercomputer, we demonstrate scalability up to 131K processors, and improve the best known Graph500 results for IBM BG/P Intrepid by 15%.

# DEDICATION

To my parents, for instilling in me the value of education. To Olga, for your constant support. To Zhanna, for showing me the joys of a child's curiosity.

#### ACKNOWLEDGEMENTS

I feel fortunate to have many supportive people who have helped me throughout this work. I would like to thank my advisor, Dr. Nancy M. Amato, for her continual guidance during my graduate and undergraduate studies. She provided an environment where I could explore many different research interests.

I would like to thank my committee members, Dr. Yoonsuck Choe, Dr. Lawrence Rauchwerger, Dr. Marvin Adams, and Dr. Maya Gokhale, for their guidance and suggestions throughout this work.

I would like to thank many people at Lawrence Livermore National Laboratory, where I was a student intern and Lawrence Scholar. Maya Gokhale provided significant guidance on my research and future career paths. I would also like to thank some of my other collaborators, in particular, Dr. Sasha Ames, Dr. Brian Van Essen, Dr. Scott Lloyd, Dr. Craig Ulmer, Dr. Andy Yoo, and Dr. John May.

I would also like to thank the members of the Parasol Lab. Dr. Jinsuck Kim, Dr. Marco Morales, and Dr. Jyh-Ming Lien, were my graduate student mentors as I was starting my research as an undergrad and graduate student. I would also like to thank some of my other collaborators, in particular, Dr. Sam Rodriquez, Olga Pearce, Dr. Shawna Thomas, Dr. Lydia Tapia, Dr. Nathan Thomas, Dr. Timmie Smith, Aimee Vargas, Dr. Xinyu Tang, Sam Jacobs. These students formed the backbone of a strong research environment, and encouraged open collaboration.

Finally, I would like to thank my family for their constant support.

This work was partially performed under the auspices of the U.S. Department of Energy by Lawrence Livermore National Laboratory under Contract DE-AC52-07NA27344 (LLNL-TH-645698).

# TABLE OF CONTENTS

|    |                                                                             |                                                                                   |                                                                                                                                                                                                                                                                                                                                                                         | Р | age                                                                         |

|----|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------|

| AI | BSTR                                                                        | ACT .                                                                             |                                                                                                                                                                                                                                                                                                                                                                         |   | ii                                                                          |

| Dł | EDIC                                                                        | ATION                                                                             |                                                                                                                                                                                                                                                                                                                                                                         |   | iv                                                                          |

| AC | CKNC                                                                        | OWLED                                                                             | GEMENTS                                                                                                                                                                                                                                                                                                                                                                 |   | v                                                                           |

| TA | ABLE                                                                        | OF CC                                                                             | ONTENTS                                                                                                                                                                                                                                                                                                                                                                 |   | vi                                                                          |

| LI | ST O                                                                        | F FIGU                                                                            | URES                                                                                                                                                                                                                                                                                                                                                                    |   | ix                                                                          |

| LI | ST O                                                                        | F TABI                                                                            | LES                                                                                                                                                                                                                                                                                                                                                                     |   | xi                                                                          |

| 1. | INT                                                                         | RODUC                                                                             | CTION                                                                                                                                                                                                                                                                                                                                                                   |   | 1                                                                           |

|    | $1.1 \\ 1.2$                                                                |                                                                                   | ch Objective and Contributions $\ldots \ldots \ldots$                                                                                                                                                                                                   |   | $\frac{4}{5}$                                                               |

| 2. | PRE                                                                         |                                                                                   | ARIES AND RELATED WORK                                                                                                                                                                                                                                                                                                                                                  |   | 7                                                                           |

|    | <ul> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> </ul> | Graph<br>2.2.1<br>2.2.2<br>Scale-fi<br>2.3.1<br>2.3.2<br>Synthe<br>2.4.1<br>2.4.2 | nology and Graph Representations       .         Partitioning       .         1D Partitioning       .         2D Partitioning       .         ree Graphs       .         Properties       .         Examples       .         scale-Free Models       .         Small World Models       .         sing Large Graphs       .         Multithreaded Shared Memory       . |   | $7 \\ 7 \\ 8 \\ 9 \\ 11 \\ 13 \\ 14 \\ 15 \\ 17 \\ 17 \\ 18 \\ 18 \\ 18 \\$ |

|    | 2.6<br>2.7                                                                  | 2.5.3<br>Challer<br>2.6.1<br>2.6.2<br>Graph<br>2.7.1<br>2.7.2                     | External Memory                                                                                                                                                                                                                                                                                                                                                         |   | 19<br>22<br>25<br>27<br>27<br>28                                            |

|    |                                                                             | 2.7.3                                                                             | Connected Components                                                                                                                                                                                                                                                                                                                                                    |   | 29                                                                          |

|    |              | 2.7.4<br>2.7.5<br>2.7.6 | Triangle Counting                              | 29<br>29<br>29                          |

|----|--------------|-------------------------|------------------------------------------------|-----------------------------------------|

| 3. | ASY          |                         | CONOUS GRAPH TRAVERSAL                         | 31                                      |

|    | $3.1 \\ 3.2$ |                         | chronous Visitor Queue                         | 31<br>32                                |

|    |              | $3.2.2 \\ 3.2.3$        | (SSSP)                                         | 33<br>36<br>37                          |

|    | $3.3 \\ 3.4$ |                         | ithmic Analysis                                | $\frac{39}{39}$                         |

|    | 3.4          | -                       | imental Study                                  | 39<br>41                                |

|    | 0.0          | 3.5.1                   | Graph Types and Sizes                          | 41                                      |

|    |              | 3.5.2                   | Hardware Resources                             | 44                                      |

|    |              | 3.5.3                   | In-Memory Experiments                          | 45                                      |

|    |              | 3.5.4                   | Semi-External Memory Experiments               | 52                                      |

|    | 3.6          | Summ                    | nary                                           | 57                                      |

| 4. | BAI          | LANCE                   | D PARTITIONING WITH HIGH-DEGREE VERTICES       | 59                                      |

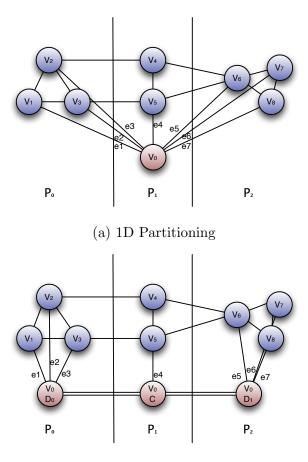

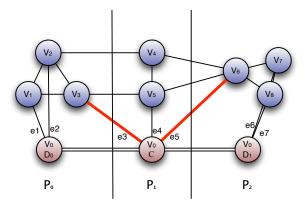

|    | 4.1          | 0                       | List Partitioning                              | 60                                      |

|    | 4.0          | 4.1.1                   | Ghost Vertices                                 | 62<br>62                                |

|    | 4.2          | 4.2.1                   | buted Visitor Queue    Visitor Abstraction     | $\begin{array}{c} 63 \\ 63 \end{array}$ |

|    |              | 4.2.1<br>4.2.2          | Visitor Queue Interface                        | 63                                      |

|    |              | 4.2.3                   | Example Traversal                              | 64                                      |

|    |              | 4.2.4                   | Visitor Queue Design Details                   | 65                                      |

|    | 4.3          | Algori                  | ithms                                          | 68                                      |

|    |              | 4.3.1                   | Breadth-First Search                           | 68                                      |

|    |              | 4.3.2                   | K-Core Decomposition                           | 70                                      |

|    |              | 4.3.3                   | Triangle Counting                              | 71                                      |

|    | 4.4          | Asym                    | ptotic Analysis                                | 72                                      |

|    |              | $4.4.1 \\ 4.4.2$        | Analysis of BFS                                | 74<br>75                                |

|    |              | 4.4.2<br>4.4.3          | Analysis of Triangle Counting                  | 75<br>75                                |

|    | 4.5          | -                       | imental Study                                  | 75                                      |

|    | 1.0          | 4.5.1                   | Experimental Setup                             | 76                                      |

|    |              | 4.5.2                   | Scalability on BG/P Supercomputer              | 76                                      |

|    |              | 4.5.3                   | Scalability of Distributed External Memory BFS | 81                                      |

|    |              | 4.5.4                   | Topological Effects on Performance             | 84                                      |

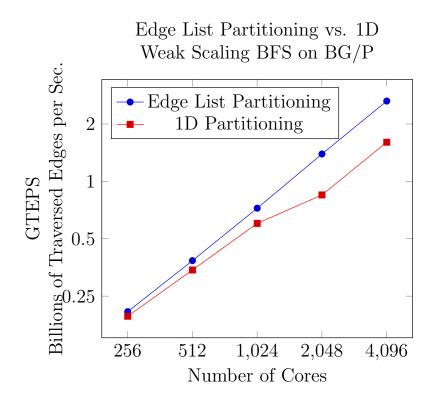

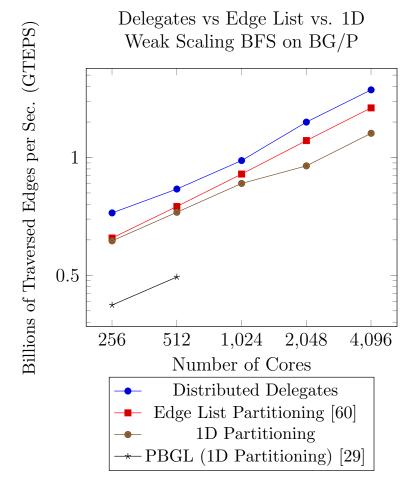

|    |              | 4.5.5                   | Edge List Partitioning vs 1D                   | 86                                      |

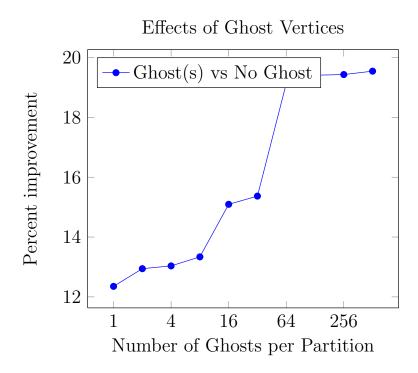

|    |              | 4.5.6                   | Use of Ghost Vertices                          | 87                                      |

|    | 4.6          | Summ                    | nary                                           | 88                                      |

| DIST | ΓRIBU′                                                | TED STORAGE, COMPUTATION, AND COMMUNICATION                                                                                                                                                                                                                                                                                                                                                                |

|------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                                       | DEGREE VERTICES                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.1  | Distrib                                               | outed Delegates                                                                                                                                                                                                                                                                                                                                                                                            |

|      | 5.1.1                                                 | Delegate Partitioning in Visitor Framework                                                                                                                                                                                                                                                                                                                                                                 |

|      | 5.1.2                                                 | Distributed Delegate Partitioning                                                                                                                                                                                                                                                                                                                                                                          |

| 5.2  | Asyncl                                                | hronous Visitor Queue                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 5.2.1                                                 | Visitor Abstraction                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 5.2.2                                                 | Visitor Queue Interface                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 5.2.3                                                 | Controller and Delegate Coordination                                                                                                                                                                                                                                                                                                                                                                       |

|      | 5.2.4                                                 | Routed Point-to-Point Communication                                                                                                                                                                                                                                                                                                                                                                        |

| 5.3  | Visitor                                               | Algorithms                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 5.3.1                                                 | Breadth-First Search & Single Source Shortest Path 100                                                                                                                                                                                                                                                                                                                                                     |

|      | 5.3.2                                                 | PageRank                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 5.3.3                                                 | K-Core Decomposition                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.4  | Asymp                                                 | totic Analysis                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.5  |                                                       | ments                                                                                                                                                                                                                                                                                                                                                                                                      |

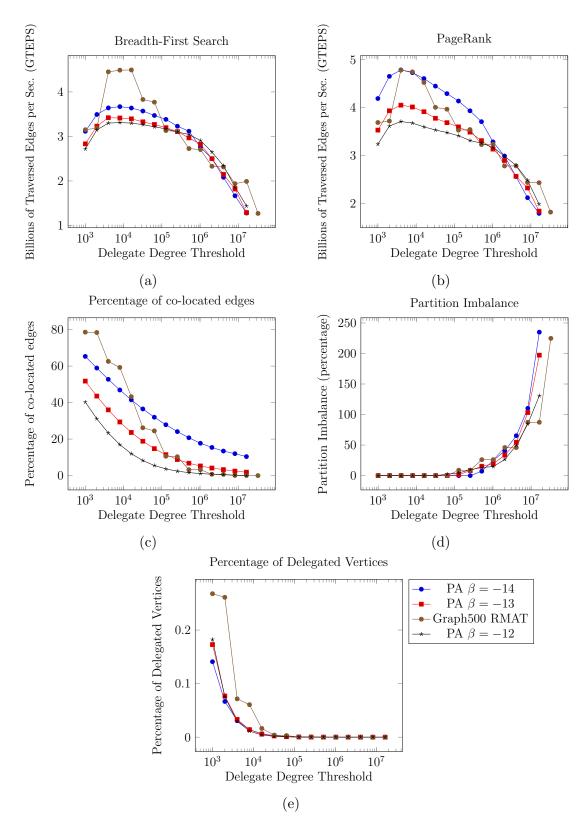

|      | 5.5.1                                                 | Effects of Delegate Degree Threshold                                                                                                                                                                                                                                                                                                                                                                       |

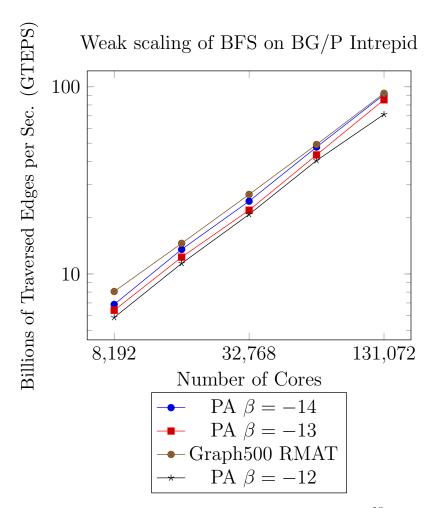

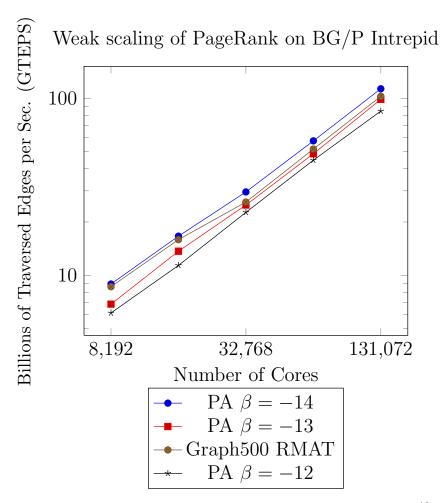

|      | 5.5.2                                                 | Weak Scaling of BFS and PageRank 110                                                                                                                                                                                                                                                                                                                                                                       |

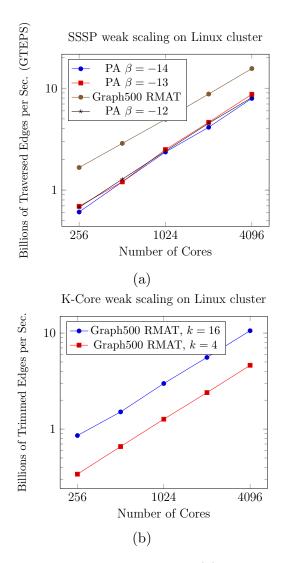

|      | 5.5.3                                                 | Weak Scaling of SSSP and K-Core Decomposition                                                                                                                                                                                                                                                                                                                                                              |

|      | 5.5.4                                                 | Comparison to 1D and Edge Partitioning                                                                                                                                                                                                                                                                                                                                                                     |

|      | 5.5.5                                                 | Comparison to Previous Graph500 Gesults                                                                                                                                                                                                                                                                                                                                                                    |

| 5.6  | Summ                                                  | ary                                                                                                                                                                                                                                                                                                                                                                                                        |

| CON  |                                                       | ION                                                                                                                                                                                                                                                                                                                                                                                                        |

| COP  | ICLU51                                                | $\frac{1}{1}$                                                                                                                                                                                                                                                                                                                                                                                              |

| EFER | ENCES                                                 | 8                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | OF 1<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>CON | $\begin{array}{ccccc} \text{OF HIGH-I} \\ 5.1 & \text{Distrib} \\ & 5.1.1 \\ & 5.1.2 \\ 5.2 & \text{Asyncl} \\ & 5.2.1 \\ & 5.2.1 \\ & 5.2.2 \\ & 5.2.3 \\ & 5.2.4 \\ 5.3 & \text{Visitor} \\ & 5.3.1 \\ & 5.3.2 \\ & 5.3.1 \\ & 5.3.2 \\ & 5.3.3 \\ 5.4 & \text{Asymp} \\ 5.5 & \text{Experi} \\ & 5.5.1 \\ & 5.5.2 \\ & 5.5.3 \\ & 5.5.4 \\ & 5.5.5 \\ 5.6 & \text{Summ} \\ \text{CONCLUSI} \end{array}$ |

# LIST OF FIGURES

# FIGURE

| 2.1  | Illustration of 1D partitioning a graph's adjacency matrix                                                                          | 10 |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Illustration of 2D partitioning a graph's adjacency matrix                                                                          | 12 |

| 2.3  | Vertex degree distributions for a web graph [43] (a) and the Epinions graph [64] (b)                                                | 13 |

| 2.4  | Hub growth for scale-free RMAT and preferential attachment graphs.                                                                  | 16 |

| 2.5  | Multithreaded random read I/O performance for three NAND Flash configurations                                                       | 21 |

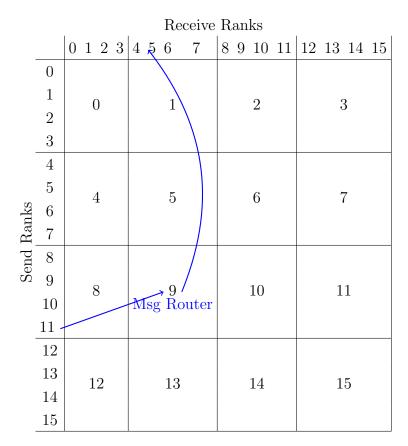

| 2.6  | Illustration of 2D communicator routing of 16 ranks.                                                                                | 24 |

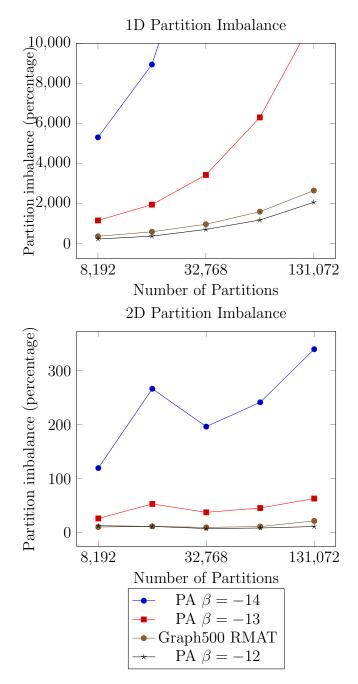

| 2.7  | Weak scaling of partition imbalance for 1D and 2D partitioning; im-<br>balance computed for the distribution of edges per partition | 26 |

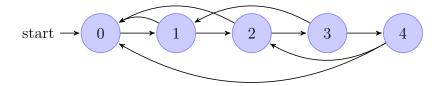

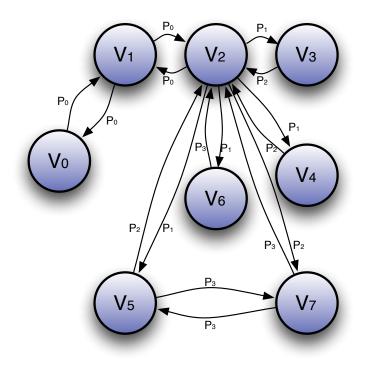

| 3.1  | An example directed graph with poor parallelism for BFS and SSSP.                                                                   | 33 |

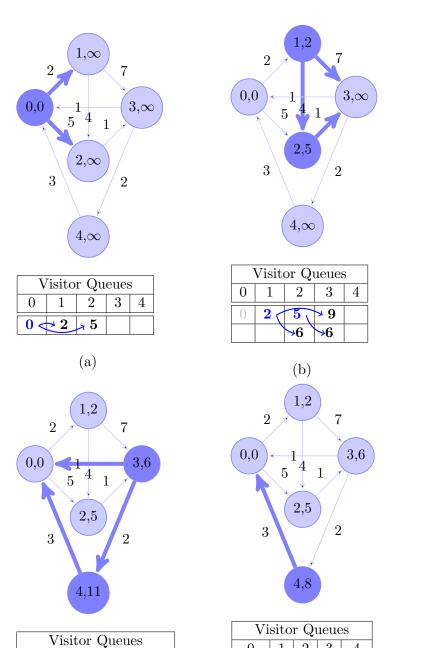

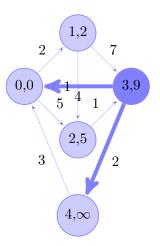

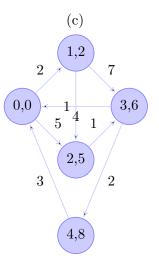

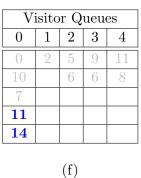

| 3.2  | An example of an asynchronous Single Source Shortest Path (SSSP) traversal of a simple weighted directed graph.                     | 35 |

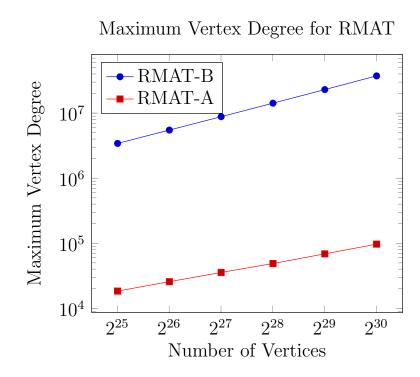

| 3.3  | Maximum Vertex Degree for RMAT-A and RMAT-B graphs                                                                                  | 43 |

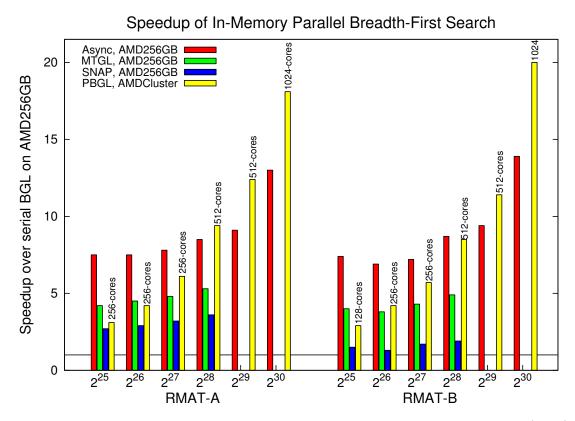

| 3.4  | Performance comparison of In-Memory Breadth First Search (BFS)                                                                      | 47 |

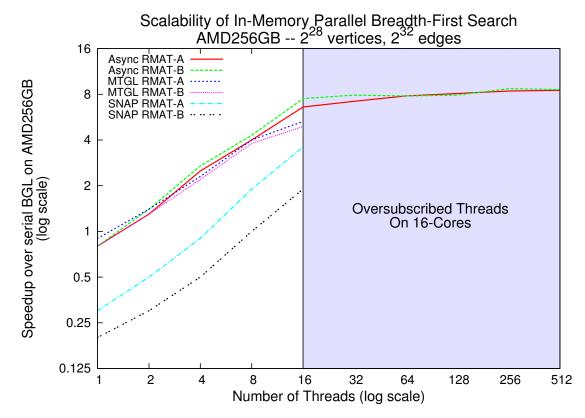

| 3.5  | Scalability of In-Memory Breadth First Search (BFS)                                                                                 | 48 |

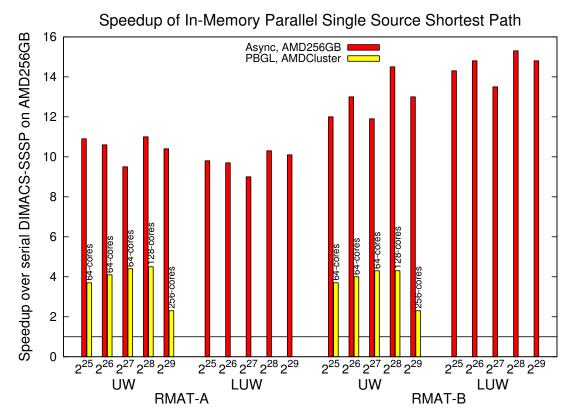

| 3.6  | Performance comparison of In-Memory Singe Source Shortest Path (SSSP)                                                               | 50 |

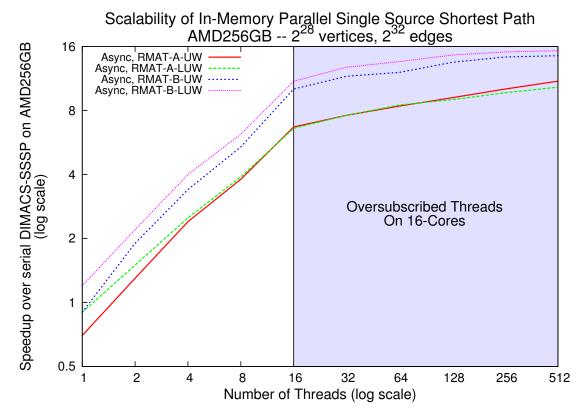

| 3.7  | Scalability of In-Memory Singe Source Shortest Path (SSSP)                                                                          | 51 |

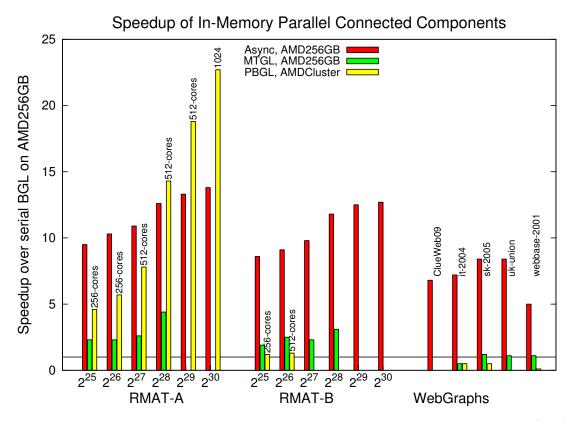

| 3.8  | Performance comparison of In-Memory Connected Components (CC).                                                                      | 52 |

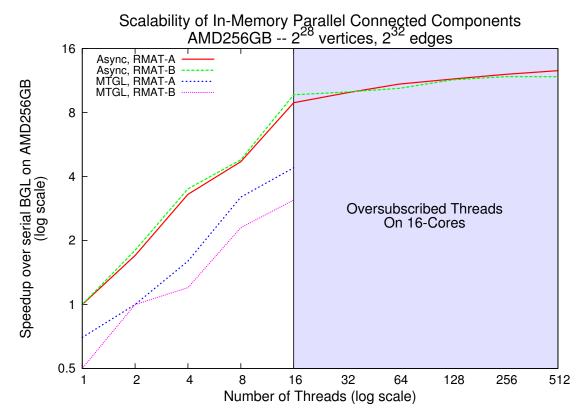

| 3.9  | Scalability of In-Memory Connected Components (CC)                                                                                  | 53 |

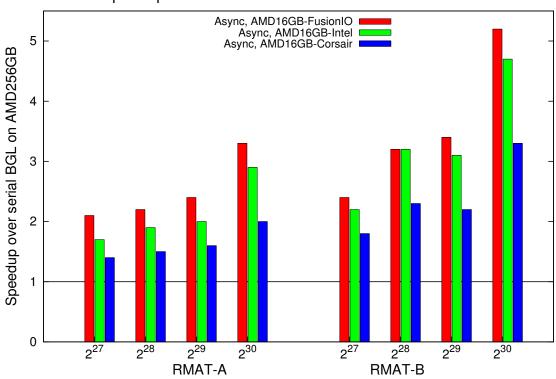

| 3.10 | Performance comparison of Breadth-First Search in Semi-External<br>Memory on three FLASH memory configurations.                     | 55 |

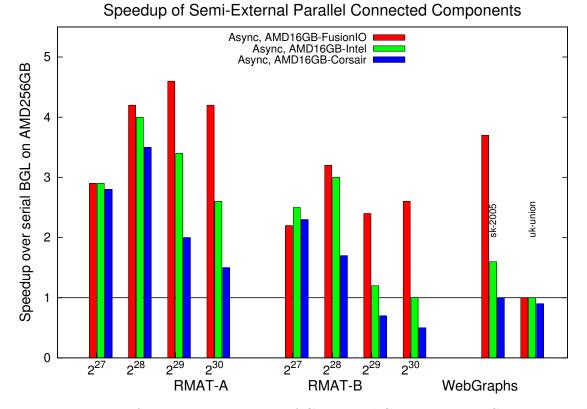

| 3.11 | Performance comparison of Connected Components in Semi-External<br>Memory on three FLASH memory configurations.     | 56  |

|------|---------------------------------------------------------------------------------------------------------------------|-----|

| 4.1  | Example of <i>edge list partitioning</i> for a graph with 8 vertices and 16 directed edges, split into 4 partitions | 61  |

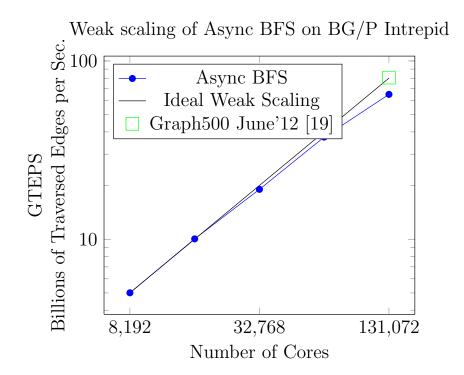

| 4.2  | Weak scaling of Asynchronous BFS on BG/P Intrepid                                                                   | 77  |

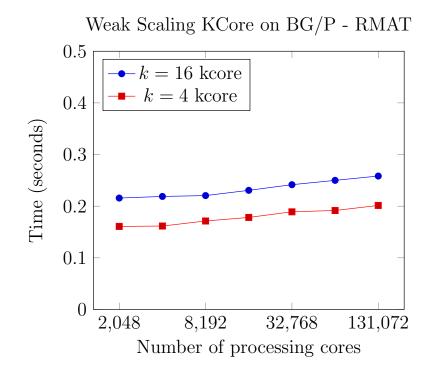

| 4.3  | Weak Scaling of kth-core on BG/P using RMAT graphs                                                                  | 79  |

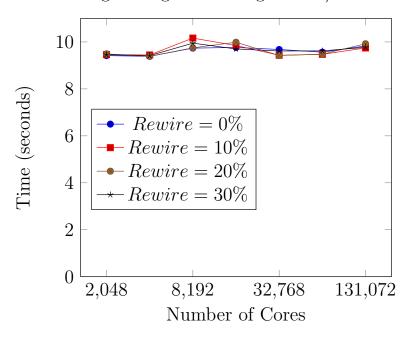

| 4.4  | Weak scaling of triangle counting on BG/P using Small World graphs.                                                 | 80  |

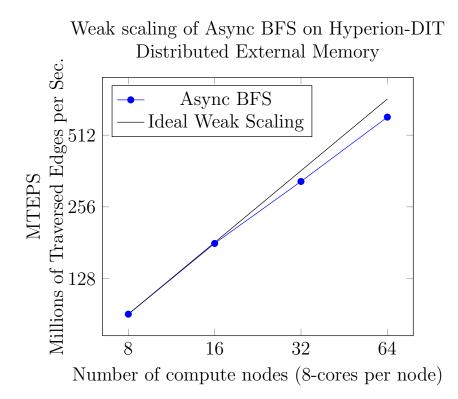

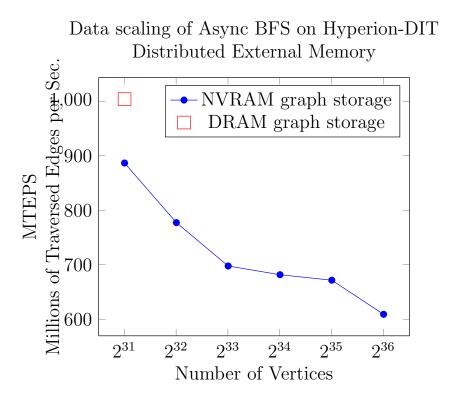

| 4.5  | Weak scaling of distributed external memory BFS on Hyperion-DIT.                                                    | 81  |

| 4.6  | Effects of increasing external memory usage on 64 compute nodes of Hyperion-DIT.                                    | 82  |

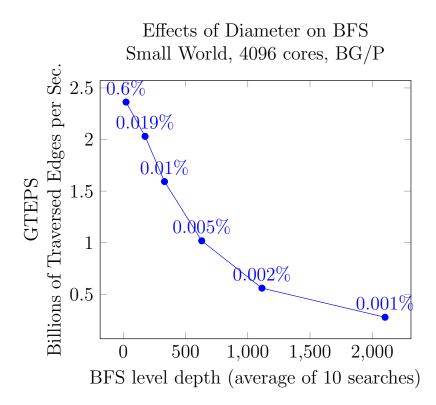

| 4.7  | Effects of diameter on BFS performance                                                                              | 84  |

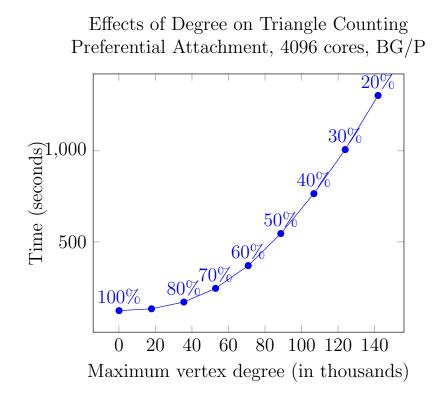

| 4.8  | Effects of vertex degree on Triangle Counting performance                                                           | 85  |

| 4.9  | Comparison of <i>edge list partitioning</i> vs 1D                                                                   | 86  |

| 4.10 | Experiment showing the percent improvement of ghost vertices vs. no ghost vertices                                  | 87  |

| 5.1  | Comparison of 1D partitioning vs. distributed delegates partitioning for the same graph.                            | 90  |

| 5.2  | Illustration of 2D communicator routing of 16 ranks with distributed delegate operations.                           | 99  |

| 5.3  | Effects of delegate degree threshold $(d_{high})$ using 4096 cores on graphs with $2^{30}$ vertices.                | 109 |

| 5.4  | Weak scaling of BFS on BG/P Intrepid                                                                                | 110 |

| 5.5  | Weak scaling of PageRank on BG/P Intrepid                                                                           | 111 |

| 5.6  | Weak scaling of delegate partitioned (a) SSSP and (b) K-Core on Cab<br>Linux cluster at LLNL                        | 113 |

| 5.7  | Comparison of <i>distributed delegates</i> vs. edge list partitioning [60], 1D partitioning, and PBGL [29]          | 114 |

| 5.8  | Weak scaling of delegate partitioned BFS on BG/P Intrepid                                                           | 115 |

# LIST OF TABLES

| TABLE | E                                                                        | Page |

|-------|--------------------------------------------------------------------------|------|

| 2.1   | Graph Data Structures                                                    | 8    |

| 3.1   | Properties of graph datasets used in experiments                         | 42   |

| 3.2   | Graph500 results using NAND Flash in shared-memory                       | 57   |

| 4.1   | Visitor Procedures and State                                             | 64   |

| 4.2   | November 2011 Graph500 results using NAND Flash                          | 83   |

| 5.1   | Delegate Visitor Behaviors                                               | 94   |

| 5.2   | Controller Visitor Commands                                              | 95   |

| 5.3   | Visitor Procedures and State                                             | 95   |

| 5.4   | Comparison of 1D, Edge List Partitioning (ELP) and Distributed Delegates | 107  |

| 5.5   | Analysis Parameters                                                      | 107  |

#### 1. INTRODUCTION

A graph is a powerful tool that can represent a set of objects and their relationships. Graphs are used in a wide range of fields including Computer Science, Biology, Chemistry, and the Social Sciences. These graphs, sometimes known as *networks*, may represent complex relationships between individuals, proteins, chemical compounds, etc. In a graph, relationships are stored using vertices and edges; a vertex may represent an object or concept, and the relationships between them are represented by edges. The power of the graph data structure lies in the ability to encode complex relationships between data and provide a framework to analyze the impact of the relationships.

Efficiently storing and processing large amounts of graph data is a challenging and growing problem as researchers seek to leverage "Big Data" to answer next-generation scientific questions. Many real-world graphs can be classified as *scale-free*, where the distribution of vertex degrees follows a scale-free power-law [6]. The degree of a vertex is the count of the number of edges connecting to the vertex. A power-law vertex degree distribution means that the majority of vertices have small degree, while a select few have a very large degree, with the distribution of the degrees following a power-law distribution. These high-degree vertices are called *hub* vertices. Hubs have the potential to create scaling issues for parallel and distributed algorithms, such as load imbalance and communication bottlenecks, because the processing requirements for a hub are significantly larger than for an average vertex.

This research develops new techniques to distribute and parallelize the storage, computation, and communication of high-degree vertices in scale-free graphs. Our work facilitates the processing of large real-world graph datasets through the development of parallel algorithms and tools that scale to large computational and memory resources, overcoming challenges not addressed by existing techniques. Towards this goal, we begin by identifying key challenges to storing and processing massive scale-free graphs. Many important graph datasets have unstructured and irregular topologies that perform poorly using multi-level memory hierarchies, including external memory. Irregular topologies and high-degree vertices often produce excessive processor to processor, approaching all-to-all, communication when algorithms are parallelized, leading to poor overall performance. These challenges are discussed in depth in Chapter 2.

Many parallel graph algorithms operate on graphs that are partitioned amongst a set of processors, and each processor is assigned a subset of the graph. The graph partitioning problem is to subdivide the vertices and edges of a graph into roughly equal sized groups, while minimizing the number of edges connecting vertices of different groups. The groups or partitions should be of roughly equal size to balance the computation for each processor. Additionally, minimizing the number of edges connecting vertices of different groups reduces the amount of inter-processor communication and coordination required by graph algorithms. Graph partitioning is challenging for many graphs, and is known to be NP-Complete [14]. Without good graph separators, parallel algorithms will require significant communication.

Partitioning many scale-free graphs is difficult, and often not feasible, due to their irregular topology and high-degree vertices. The simplest partitioning is called 1D or row-wise, in which the vertices of the graph are partitioned and all edges adjacent to a vertex, including imbalanced hubs, are assigned to a single partition. For scale-free graphs, the partitions to which high-degree vertices are assigned may contain significantly more edges than the average partition. This edge partition imbalance effects the data storage, computation, and communication costs, because the processors will store and process an uneven number of edges. Current state-ofthe-art partitioning for sparse scale-free graphs into p partitions uses a 2D strategy that partitions high-degree vertices across  $O(\sqrt{p})$  partitions. 2D partitioning also suffers from storage, computation, and communication imbalances.

We address these challenges by providing three novel techniques for processing large scale-free graphs. First, we develop an asynchronous graph traversal technique using visitor queues that is capable of expressing fine-grained parallelism at the individual vertex level. Data latencies associated with the external graph storage media and message passing communication are mitigated by the asynchrony of the computation.

Second, we introduce a new partitioning technique that guarantees balanced partitions containing high-degree vertices. Previous partitioning strategies using 1D and 2D partitioning may produce an imbalanced number of edges per partition for scale-free graphs. Our edge list partitioning approach partitions the graph's edges such that each partition contains an equal number of edges, overcoming the storage balance issues created by high-degree vertices.

Finally, we develop a technique we call distributed delegates to parallelize and distribute the storage, computation, and communication of high-degree vertices. We make a distinction between low and high degree vertices, and distribute the highdegree vertices. The number of edges per partition is balanced, and the large amount of computation and communication for the high-degree vertices is distributed over the processors, leading to significantly improved performance.

Our techniques provide new tools to analyze large scale-free graph datasets on a wide rage of data-intensive computational resources. Our research is targeted at leadership class supercomputers containing significant distributed memory resources, clusters with node-local non-volatile random access memory (NVRAM), and small shared-memory systems containing large NVRAM storage devices. Our work breaks new ground for using NVRAM in the high-performance computing (HPC) environment for data intensive applications. We show that by leveraging distributed NVRAM, significantly larger datasets can be processed with only moderate performance degradation. We show that by exploiting both distributed memory processing and node-local NVRAM, significantly larger datasets can be processed than with either approach in isolation. Further, we demonstrate that our asynchronous approach mitigates the effects of both distributed and external memory latency. The architecture and configuration of NVRAM in supercomputing clusters is an active research topic. To our knowledge, our work is the first to integrate node-local NVRAM with distributed memory at extreme scale for important data intensive problems, helping to inform the design of future architectures.

#### 1.1 Research Objective and Contributions

The research contributions of this dissertation can be summarized as:

- Novel algorithmic techniques to process large scale-free graphs:

- An asynchronous computation model using prioritized visitor queues that tolerates latencies associated with external memory and distributed message passing;

- An edge list partitioning technique that guarantees balanced partitions for scale-free graphs containing high-degree vertices;

- A technique we call distributed delegates to parallelize and distribute the storage, computation, and communication of high-degree vertices;

- The application of these techniques to a variety of parallel graph algorithms

including: Single Source Shortest Path, Connected Components, K-Core decomposition, Triangle Counting, and PageRank;

- Experimental results demonstrate the scalability of algorithms using our techniques on leadership class supercomputers on up to 131K processors;

- Results that show that by leveraging node-local NAND Flash, algorithms using our techniques can process larger datasets with only modest performance degradation over a DRAM-only solution.

Portions of our research were previously published and are currently under review. The asynchronous visitor computation model and an initial evaluation in shared and external memory was published at the *International Conference for High Performance Computing, Networking, Storage and Analysis* (SC) 2010 [59], presented here in Chapter 3. This work led to two external memory experiments featured on the Graph500, including a 7<sup>th</sup> place ranking on the June 2011 list, and was also used as a data-intensive benchmark by Van Essen, et al. [25]. Our technique for partitioning graphs containing high-degree vertices was published at the *International Parallel and Distributed Processing Symposium* (IPDPS) 2013 [60], presented here in Chapter 4. This work led to two distributed-external memory experiments featured on the Graph500 on the June 2012 list. Finally, our approach for parallelizing the storage, computation, and communication of high-degree vertices is under review [58], presented here in Chapter 5.

#### 1.2 Outline

This dissertation describes our asynchronous framework for traversing massive scale-free graphs in shared, distributed and semi-external memories. Chapter 2 describes many of the fundamental properties of real-world graphs, along with previous work that is related to our asynchronous algorithms. Section 2.6 discusses the challenges of processing large scale-free graphs. Chapter 3 introduces our asynchronous visitor computation model and an experimental study using shared-memory and semi-external memory systems. Chapter 4 discusses partitioning graphs containing high-degree hub vertices and an experimental study using distributed-memory systems. Finally, Chapter 5 discusses distributing the storage, computation, and communication of high-degree hub vertices and an experimental study using distributedmemory systems.

## 2. PRELIMINARIES AND RELATED WORK

In this chapter, we cover background topics and related work that will be referred to throughout the remainder of this dissertation. An introduction to graph terminology and representations is discussed in Section 2.1. An overview of graph partitioning is discussed in Section 2.6.1. Scale-free graphs and models of real-world graphs are discussed in Section 2.3. An overview of related work on the parallel processing of graphs is discussed in Section 2.5. The challenges associated with processing scale-free graphs is discussed in Section 2.6. Finally, an introduction to the graph algorithms and analytics that we investigated using our scaling techniques is discussed in Section 2.7.

#### 2.1 Terminology and Graph Representations

A graph G(V, E) is composed of a set of vertices V and a set of edges E, where each edge  $e = (u, v), e \in E$  connects a pair of vertices,  $u, v \in V$ . Vertices and edges may contain weights, or other forms of meta-data. The degree of a vertex is the count of the number of edges connecting to the vertex.

Three common data structures used to represent a graph are an adjacency list, an adjacency matrix, and a compressed sparse row. The features of these structures are shown in Table 2.1.

#### 2.2 Graph Partitioning

Many parallel graph algorithms operate on graphs that have been partitioned amongst a set of processors, and each processor is assigned a subset of the graph. The graph partitioning problem is to subdivide the vertices and edges of a graph into roughly equal sized groups, while minimizing the number of edges connecting

| Name                  | Description                                                                                                         | Storage Cost |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|--------------|

| Adjacency List        | A list of edge targets stored for each                                                                              | O( V  +  E ) |

|                       | source vertex.                                                                                                      |              |

| Adjacency Matrix      | A $ V x V $ matrix where entry                                                                                      | $O( V ^2)$   |

|                       | A $ V x V $ matrix where entry<br>A[i, j] = 1 iff edge $(i, j)$ exists. En-<br>tries may also contain edge weights. |              |

|                       | tries may also contain edge weights.                                                                                |              |

| Compressed Sparse Row | A concatenated array of adjacency                                                                                   | O( V  +  E ) |

| (CSR)                 | lists, with a source vertex look index.                                                                             |              |

Table 2.1: Graph Data Structures

vertices of different groups. The groups or partitions should be of roughly equal size, to balance the cost of computation for each processor. Minimizing the number of edges connecting vertices of different groups reduces the amount of communication and coordination required by the processors. Edges connecting vertices of different partitions are commonly called *cut edges*.

Graph partitioning is challenging for many graphs, and is known to be NP-Complete [14]. Numerous heuristic techniques and libraries have been developed to partitioning graphs approximately. Some of the most successful heuristics are based on hierarchical multilevel techniques, which have been included in libraries such as *Chaco* [34], *Metis* [36], *Party* [52], *Scotch* [62], *KaFFPa* [65], and *Jostle* [76]. Parallel and distributed versions of many of these libraries have also been developed [37, 42, 61, 66, 77].

Currently, there are two approaches to partitioning a graph with the goal of evenly distributing the graph, 1D and 2D. The techniques do not attempt to minimize edge cuts, the number of edges between vertices in different partitions.

# 2.2.1 1D Partitioning

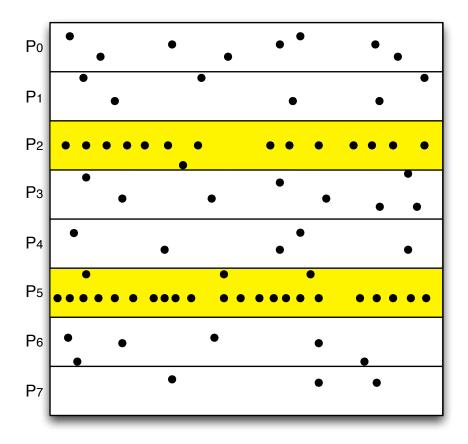

A simple way to partition a graph among p processors is to evenly partition the vertices and their associated adjacency list into p partitions. This style of partitioning is called 1D or *row-wise*, and is illustrated using an adjacency matrix in Figure 2.1. In the figure, high-degree vertices in the graph form dense rows in the adjacency matrix. Because the adjacency lists or rows of high-degree vertices are fully contained by a single partition, the partitions may become significantly imbalanced. In this example, the highlighted partitions  $p_2$  and  $p_5$  contain more edges (non zeros) that the average due to the high-degree vertices contained.

When a graph is 1D partitioned into a set of P partitions, and

$\max_{p_i \in P} \left( \sum_{v \in V_{p_i}} degree(v) \right) > \frac{|E|}{|P|}, \text{ then at least one processor will process more than its fair share of edges.}$

## 2.2.2 2D Partitioning

Recent work using 2D graph partitioning has shown the best results for traditional large scale HPC systems [16, 83, 82]. In 2D partitioning, the graph is partitioned according to a checkerboard pattern of the graph's adjacency matrix, as illustrated in Figure 2.2. The adjacency lists of high-degree vertices are split over  $O(\sqrt{p})$ partitions, which greatly improves the partition balance.

Unfortunately, 2D partitioning has serious disadvantages at scale and with external memory. First, when processing sparse graphs, each 2D block may become hypersparse, i.e., fewer edges than vertices per partition [15]. Specifically, partitions become hypersparse when  $O(\sqrt{p}) > degree(g)$ , where p is the number of distributed partitions and g is the graph. In Figure 2.2, the highlighted partitions  $(p_{13}, p_{14}, p_{15})$ illustrate hypersparse partitions, where there are fewer edges than vertices. For the sparse Graph500 datasets with average degree of 16, this may occur for as low as 256 partitions and is independent of graph size. Second, under weak scaling, the amount of algorithm state (e.g., Breadth-First Search level) stored per partition scales with  $O(\frac{V}{\sqrt{p}})$ , where V is the total number of vertices. This can ultimately hit a scaling

Figure 2.1: Illustration of 1D partitioning a graph's adjacency matrix. High-degree vertices form dense rows that when 1D partitioned row-wise create imbalance. The highlighted partitions  $p_2$  and  $p_5$  contain more edges (non zeros) than average due to the high-degree vertices contained.

wall where the amount of local algorithm state per partition exceeds the capacity of the compute node.

Finally, with respect to our desire to use semi-external memory where the vertex set is stored in in-memory and the edge set is stored in external memory, hypersparse partitions are poor candidates to apply semi-external memory techniques, because the in-memory requirements (proportional to the number of vertices) are larger than the external memory requirements (proportional to the number of edges).

Our partitioning techniques, discussed in Chapters 4 and 5, address the shortcomings of 1D and 2D partitioning for scale-free graphs containing high-degree vertices by creating balanced partitions.

## 2.3 Scale-free Graphs

Many real-world graphs can be classified as *scale-free*, where the distribution of vertex degrees follows a scale-free power-law [6]. A power-law vertex degree distribution means that the majority of vertices have small degree, while a select few have a very large degree, with the distribution of degrees following a power-law distribution. These high-degree vertices are called *hub* vertices, and create multiple scaling issues for parallel algorithms, discussed further in chapter 2.6.

## 2.3.1 Properties

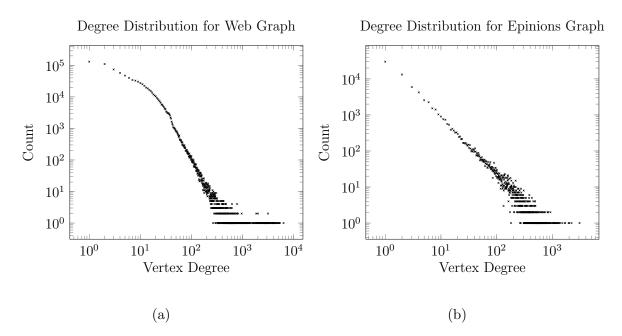

**Power Law.** A common property of many real world graphs is a power law distribution of vertex degree. As an example, Figure 2.3 shows power law distributions of vertex degree for a web graph [43] and the *Epinions* graph [64]. An effect of the power law degree distribution is that while the vast majority of vertices have a low degree, a select few vertices will have a very high degree. These high degree nodes are often referred to as *hub* vertices, and can lead to significant load imbalance for

| •                                     | ●                | • •                   | •                     |

|---------------------------------------|------------------|-----------------------|-----------------------|

| •Po                                   | Pi               | P2                    | P3 •                  |

| • • • • • • • • • • • • • • • • • • • | • •              | • • •                 | • • • •               |

|                                       | •P5              | • P6                  | P7•                   |

| •<br>• <sup>P8</sup>                  | ●<br>₽9<br>●●●●● | ●<br>₽10 <sub>●</sub> | ●<br>P11<br>● ● ● ● ● |

| • • • • • • • • • • • • • • • • • • • | ●<br>₽13         | ●<br>P14<br>●         | • P15<br>•            |

Figure 2.2: Illustration of 2D partitioning a graph's adjacency matrix. The adjacency lists of high-degree vertices are split over  $O(\sqrt{p})$  partitions, which greatly improves the partition balance. Highlighted partitions  $(p_{13}, p_{14}, p_{15})$  illustrate hypersparse partitions, where there are fewer edges than vertices.

Figure 2.3: Vertex degree distributions for a web graph [43] (a) and the Epinions graph [64] (b).

parallel processing, discussed in Section 2.6.1.

**Small Diameter.** Although sparse, many graphs are connected into connected components with small diameters. The diameter of a graph is the longest shortest-path between two vertices. This property leads to a high-level of interconnectedness that has been popularized by the phrase "six degrees of Kevin Bacon."

## 2.3.2 Examples

Examples of scale-free graphs come from many important domains, including the world wide web, social networks and intelligence networks.

World Wide Web (WWW) graph. Graphs that model the structure of the web often consist of vertices representing webpages and directed edges representing the hyperlinks between the webpages. The web graph has been the focus of numerous

studies aimed at detecting community structures and improving applications such as web search [39, 13, 43]. The vertex degree distribution of a web graph is shown in Figure 2.3 (a).

Social Networks. Graphs naturally model the relationships established by social interactions. These interactions could be on-line friendships, call-networks, etc. Zachary [84] performed a now famous social network study in the 1970s, where he constructed a network of friendships among members of a karate club. The network was constructed by direct observation of 34 members' interactions. Modern social networking tools like *Facebook* and *Twitter* have dramatically increased the scale of social network data to hundreds of millions of individuals. These tools and their accompanying social networks have garnered the attention of many social and network scientists [40, 23, 63, 73]. The vertex degree distribution of a social network is shown in Figure 2.3 (b).

Homeland Security. It has been estimated that graphs of interest to the Department of Homeland Security will reach  $10^{15}$  entities [38], providing a significant challenge to analysts who wish to search them. The sheer size of this data dwarfs the main-memory capacities of modern supercomputers, necessitating the use of external memory devices.

## 2.4 Synthetic Graph Models

Throughout this work, we used three synthetic graph generators for our studies. Two of the generators, R-MAT and Preferential Attachment, generate scale-free graphs, while the Watts-Strogatz model generates small world graphs with small diameters. This section describes the models and their parameters used in our experimental studies.

## 2.4.1 Scale-Free Models

Chakrabarti et al. [18] introduced the R-MAT model that generates power law vertex degree distributions. It is based on a recursive matrix model, and uses four parameters,  $\{a, b, c, d\}$  where a+b+c+d = 1, to control how the matrix is recursively subdivided. We follow the Graph500 V1.2 specification for generator parameters [20]. R-MAT has been studied analytically and experimentally [68, 30], and has become the de facto standard scale-free graph generator model in large part due to its scalability to large graph scales. We used the open source RMAT implementation provided by the Boost Graph Library [71].

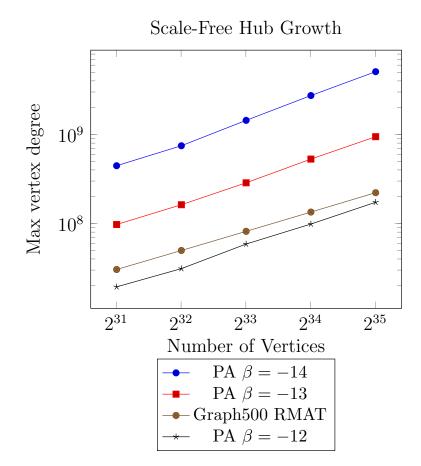

The Barabási-Albert model generates scale-free graphs based on preferential attachment [7]. The model simulates the growth of networks where the probability of a new vertex attaching to an existing vertex is proportional to the vertex's degree. We used a generalized PA model by Móri [54], where the probability of connecting to a vertex of degree d is proportional to  $d + \beta$ , where  $\beta > -16$ . By varying the value of  $\beta$ , we can control the rate in which hubs grow. For our studies, we chose  $\beta$ values of -12, -13, and -14. The  $\beta$  value of -12 was used to roughly match Graph500 RMAT's hub growth, and the  $\beta$  values of -13 and -14 where chosen to increase hub growth and stress the delegate approach. We parallelize the generation of large PA graphs using similar techniques developed by Machta [46].

The growth of the largest hub vertex for the R-MAT and PA graph models is shown in Figure 2.4.

Figure 2.4: Hub growth for scale-free RMAT and preferential attachment graphs.

#### 2.4.2 Small World Models

The Watts-Strogatz [78] model does not generate scale-free graphs, however it models the small world effect of small diameter. The model has a control parameter,  $\beta$ , that interpolates between a ring lattice and an Erdös-Rényi [24] random graph. The interpolating parameter  $\beta$  allows the number of triangles and the graph's diameter to be controlled during experiments.

## 2.5 Processing Large Graphs

Processing of large graphs is receiving increasing attention by the HPC community as datasets quickly grow past the capacity of commodity workstations. Significant challenges arise for traditional HPC solutions because of the nature of these datasets. These challenges can be categorized into unstructured memory access and poor data locality [33, 45].

While graph algorithms have received tremendous attention for the RAM computational model, many realistic datasets are too large to fit in the memory of a single computer. To address this, researchers have explored using Distributed Memory and External Memory. Key challenges in processing large graphs come from the non-contiguous access to the data structure. Distributed Memory approaches suffer from poor load balancing due to the intrinsic nature of power-law distributions, discussed in Section 2.6.1. External Memory approaches suffer the same issues as distributed memory, and in addition, poor data locality and unstructured memory accesses lead to poor performance for which techniques such as prefetching, blocking, and pipelining generally provide little improvement. Some experiments have shown that BFS designed for the RAM computation model runs orders of magnitude slower when forced to use external memory [2].

#### 2.5.1 Distributed Memory

A popular approach to graph processing in HPC has been to use Distributed Memory computer clusters. Such clusters distribute the graph data amongst its processors and memory and process the graph by exchanging messages during computation phases. This approach works well when the graph exhibits nice load balancing properties (regular or uniformly random) [83] but suffers from significant load imbalance when processing power-law graphs [29].

The most common approach for implementing graph algorithms in distributed memory is with the Bulk-Synchronous Parallel (BSP) model [72]. In BSP, processors iteratively work on their local data, and then participate in collective communication operations. This type of approach is susceptible to load imbalance, because each BSP step waits for the slowest processor with the largest load. We avoid BSP in our work, and use an asynchronous approach that can exploit fine-grained parallelism.

Many distributed memory graph libraries have been developed, including the Parallel Boost Graph Library (PBGL), the STAPL Graph Library, and Pregel. PBGL [29] applies the paradigm of generic programming to the domain of graph computations. It supports distributed memory through a bulk-synchronous message passing communication. The STAPL Graph Library [32] provides a framework that abstracts the user from data-distribution and parallelism and supports the expression of asynchronous algorithms. The Pregel graph library [47] provides a vertex-centric visitor model for implementing graph algorithms. The library provides a bulk-synchronous computation model for the vertex visitors.

# 2.5.2 Multithreaded Shared Memory

Massive Multithreaded machines address the challenges of unstructured memory accesses and poor data locality by using little or no memory hierarchy. The Cray XMT has been successful at processing large graph datasets; these specialized supercomputers rely on massive multithreading to mask memory latency without using complex memory caches. The development of the Multithreaded Graph Library (MTGL) for this specialized computing platform has been shown to address many of the issues related to memory latency [9]. Our approach addresses the memory latency issues using commodity hardware and storage devices (NAND Flash) that are relatively slow compared with main memory. Small-world Network Analysis and Partitioning (SNAP) [5] is another parallel graph library for shared memory which utilizes OpenMP for parallelism.

## 2.5.3 External Memory

Many real world graphs are too large to fit into main memory of modern computers, necessitating the use of external storage devices such as disk. Due to the significant difference in access times between main memory and disk, many efficient in-memory algorithms become impractical when using external storage. To analyze the I/O complexity of algorithms using external storage, the Parallel Disk Model (PDM) [75] has been developed. PDM's main parameters are N (problem size), M (size of internal memory), B (block transfer size), D (number of independent disks), and P (number of CPUs). When designing I/O efficient algorithms, the key principles are *locality of reference* and *parallel disk access*. For an in-depth survey of EM Algorithms, see [74].

In this dissertation, we are interested in graphs in a Semi-External Memory (SEM) scenario. A graph is semi-external if there is enough main memory to store algorithmic information about the vertices but not edges. In our SEM work, the full graph structure is stored on the persistent storage device, and the visitor queues and the output of the algorithms are stored in main memory.

Emerging technologies in persistent data storage are changing the way External Memory algorithms are designed. Flash memory is a form of non-volatile random access memory (NVRAM) that has become a commodity product through widespread use in digital cameras, music players, phones, USB drives, etc. An overview of the characteristics and performance of flash memory (namely NAND Flash) with respect to algorithmic research is given in [1, 3]. The key differences from traditional rotating media can be summarized as follows.

- Significantly faster random access time than disk (microseconds instead of 10's of milliseconds).

- Asymmetric read/write performance (writes are more costly than reads).

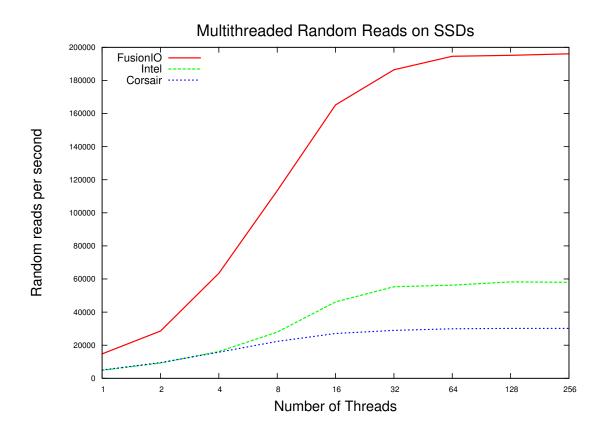

An important characteristic of NAND Flash devices not covered by [1, 3] is the ability to service multiple concurrent I/O requests. To achieve maximum random I/O performance, multiple threads must queue I/O requests. This requires External Memory algorithms to be multithreaded to achieve maximum I/O performance. Figure 2.5 shows the multithreaded random read performance of the three NAND Flash configurations that we test in chapter 3. For all configurations tested, significant improvements in I/O per second (IOPS) are seen as an increasing number of threads issue read requests. The Flash configuration details are discussed in Section 3.4.

In our previous work, we addressed the challenge of achieving DRAM-like performance when some portion of the program state resides in I/O bus-connected NVRAM capable of low latency random access [25]. We identified that high levels of concurrent I/O are required to achieve optimal performance from NVRAM devices (e.g., NAND Flash); this is the underlying motivation for designing highly concurrent asynchronous graph traversals.

Figure 2.5: Multithreaded random read I/O performance for three NAND Flash configurations. Configuration details discussed in Section 3.4.

We also identified that the Linux I/O system software introduces many bottlenecks. This has led many application developers to use the O\_DIRECT I/O flag to bypass Linux's default page cache system. For this work, we implemented a custom *page cache* that resides in user space and provides a POSIX I/O interface. Our custom page cache was designed to support a high level of current I/O requests, both for cache hits and misses, and interfaces with NVRAM using direct I/O. The design of our page cache is not the focus of this work, but was required to optimize performance from the NAND Flash devices used in our studies. **NVRAM in the HPC environment.** Node-local or node-near NVRAM is gaining traction in the HPC environment, often motivated by improving the performance of checkpointing in traditional HPC applications [53]. Our work leverages the NVRAM for data-intensive applications. Examples of HPC systems with NVRAM include:

- Lawrence Livermore Nat. Lab.: Hyperion, Coastal;

- San Diego Supercomp. Center: Trestles, Flash Gordon;

- Tokyo Institute of Technology: TSUBAME2.

The architecture and configuration of NVRAM in supercomputing clusters is an active research topic. To our knowledge, our work is the first to integrate node-local NVRAM with distributed memory at extreme scale for important data intensive problems, helping to inform the design of future architectures.

2.6 Challenges for Processing Large Scale-Free Graphs

In this section, we identify key challenges to storing and processing massive *scale-free* graphs. Many important graph datasets have unstructured and irregular topologies which thrash multi-level memory hierarchies, including external memory. In Section 2.6.1 we describe how irregular topologies can produce dense processor-processor, approaching all-to-all, communication for parallel algorithms, leading to poor overall performance. In Section 2.6.2 we describe how the growth of high-degree vertices provides significant challenges for balancing storage, computation, and communication.

#### 2.6.1 Dense Processor-Processor Communication

Partitioning scale-free graphs into equal sized partitions with minimal edge cuts is difficult, and often not feasible. Many scale-free graphs lack good graph separators, resulting in many cut edges when partitioned. When a graph is partitioned with a large number of cut edges, parallel algorithms will require significant communication. Recent work on partitioning scale-free graphs has developed techniques to partition based on community structure [27, 44, 56]. However, these techniques often do not attempt to create equal sized partitions when attempting to uncover the underlying community structure. As such, these techniques are not well suited for partitioning graphs for the purposes of parallel processing.

For scale-free graphs without good graph separators, parallel algorithms will require significant communication. Specifically, when the parallel partitioned graph contains  $\Omega(|E|^{\alpha})$ , where  $0 < \alpha \leq 1$ , cut edges, a polynomial number of graph edges will require communication between processors if an algorithm requires communication along the edges. Additionally, *dense communication* occurs when  $\Omega(p^{\alpha+1})$  pairs of processors share cut edges, in the worst case creating all-to-all communication.

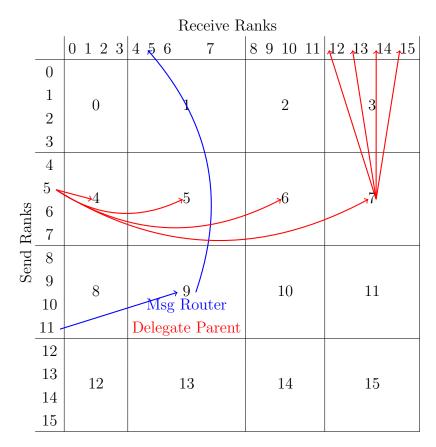

To mitigate the dense processor-processor communication, we apply communication routing and aggregation through a synthetic network. For dense communication patterns, where every process needs to send messages to all p other processes, we route the messages through a topology that partitions the communication. We have experimented with 2D and 3D routing topologies. Figure 2.6 illustrates a 2D routing topology that reduces the number of communicating channels a process requires to  $O(\sqrt{p})$ . This reduction in the number of communicating pairs comes at the expense of message latency because messages require two hops to reach their destination. In addition to reducing the number of communicating pairs, 2D routing increases the amount of message aggregation possible by  $O(\sqrt{p})$ .

Scaling to hundreds of thousands of cores requires additional reductions in communication channels. Our experiments on the IBM BlueGene/P supercomputer use

Figure 2.6: Illustration of 2D communicator routing of 16 ranks. As an example, when *Rank 11* sends to *Rank 5*, the message is first aggregated and routed through *Rank 9*.

a 3D routing topology, that is very similar to the 2D illustrated in Figure 2.6, and is designed to mirror the BG/P 3D torus interconnect topology.

Recent work related to our routed communication has been explored by Willcock [80], where active messages are routed through a synthetic hypercube network to improve dense communication scalability. A key difference to our work is that their approach has been designed for the Bulk Synchronous Parallel (BSP) model and is not suitable for asynchronous graph traversals.

#### 2.6.2 Power-law Degree Distribution

Underlying many of the scaling challenges is the growth of high-degree vertices in the graph as the size of the graph increases. Hub vertices have degrees significantly above average, and lead to imbalances in parallel computation and communication. The hub growth for Graph500 R-MAT and Preferential Attachment scale-free graphs is shown in Figure 2.4. While the average degree is held constant at 16, the number of edges belonging to hubs continues to grow as graph size increases.

For scale-free graphs, 1D partitioning suffers from significant partition imbalance in terms of the number of edges per partition, due to the high-degree vertices in scale-free graphs. 2D partitioning is significantly better than 1D; however, 2D may still create imbalanced partitions. The weak scaling of Graph500 partition imbalance for 1D and 2D block partitioning is shown in Figure 2.7. 1D partition becomes over ten times imbalanced, while 2D is only 20% imbalanced.

Our *edge list partitioning*, discussed in chapter 4, does not suffer from imbalances due to high-degree vertices; it guarantees a balanced number of edges per partition.

Figure 2.7: Weak scaling of partition imbalance for 1D and 2D partitioning; imbalance computed for the distribution of edges per partition. Weak scaled using 262,144 vertices per partition. The number of vertices per partition matches the experiments on BG/P Intrepid shown in Sections 5.5.2 and 5.5.5. Both 1D and 2D partitioning produce imbalanced partitioning, with the increased imbalance when the graph has greater hub size (e.g. PA  $\beta = -14$ ). 2D partitioning is significantly better than 1D for all graphs in our studies, however our distributed delegates partitioning produces perfectly balanced partitions for these weak scaled graphs.

#### 2.7 Graph Algorithms

In this section, we provide an overview of the graph algorithms we explore in this thesis. We focus on six important graph computations that are fundamental to many other areas of graph analysis: Breadth-First Search, Single Source Shortest Path, Connected Components, K-Core decomposition, Triangle Counting, and Page Rank.

### 2.7.1 Breadth-First Search (BFS)

Breadth-First Search (BFS) is a simple traversal that begins from a starting vertex and explores all neighboring vertices in a level-by-level manner. Taking the starting vertex as belonging to level 0, level 1 is filled with all unvisited neighbors of level 0. Level i + 1 is filled with all previously unvisited neighbors of level i; this continues until all neighbors of level i have been visited. BFS runs in O(|V| + |E|)time.

Many parallel versions of BFS are *level synchronous* [8, 5]. This means that all threads of execution working on level i must finish and synchronize before starting to work on level i+1. In some cases, additional work between the level synchronizations is needed to merge the level sets.

BFS is an algorithm that is efficient when computing in-memory, but becomes impractical in external memory. In-memory BFS incurs  $\Omega(n+m)$  I/Os when using external memory, and it has been reported that the in-memory BFS performs orders of magnitude slower when forced to use external memory [2].

For general undirected graphs, Munagala and Ranade [55] improve the worstcase I/O of BFS to O(n + sort(m)) by exploiting the fact that a node in BFS level *i* can only have edges to nodes in level i - 1 or i + 1, removing the need to check all previous BFS levels. The O(n) term in Munagala and Ranade's algorithm is due to non-contiguous access to the adjacency lists, requiring separate access. Mehlhorn and Meyer [50] improved the adjacency list access by pre-processing the graph into subgraphs of low diameter and storing their adjacency lists contiguously, leading to sub-linear I/O complexity.

For general directed graphs, improvements over in-memory BFS and DFS have not been made, their I/O complexity is O((n + m/B)lg(n/B) + sort(m)) [4]. This is considered impractical for general sparse directed graphs. For an in-depth survey of EM graph traversal algorithms, see [4].

## 2.7.2 Single Source Shortest Path (SSSP)

A Single Source Shortest Path (SSSP) algorithm computes the shortest paths in a weighted graph from a single source vertex to every other vertex. In this work, we only address non-negatively weighted graphs. Our approach to Single Source Shortest Path (SSSP) can be viewed as a hybrid between Bellman-Ford [21] and Dijkstra's [22] SSSP. Bellman-Ford *label-correcting* computes SSSP by making |V| - 1 loops over all vertices, *relaxing* the path length of each vertex. Dijkstra's SSSP algorithm also iteratively relaxes vertices, but proceeds in a greedy manner, *relaxing* only the shortest-path vertex at each iteration. Dijkstra's SSSP runs in O(|E| + |V|log(|V|)), and Bellman-Ford runs in O(|V| \* |E|) time.

We show comparisons to a distributed implementation of the  $\Delta$ -stepping SSSP algorithm [51] provided by PBGL [29]. This algorithm proceeds in *bulk-synchronous* steps, where vertices within a *delta* of the shortest path are relaxed together.

Asynchronous algorithms for computing shortest paths in parallel have been previously studied [10, 31]. Our work builds on these techniques to create an asynchronous approach that can overcome load imbalance and data latencies.

### 2.7.3 Connected Components