# SOFT-SWITCHING HIGH-FREQUENCY AC-LINK UNIVERSAL POWER CONVERTERS WITH GALVANIC ISOLATION

## A Dissertation

by

## MAHSHID AMIRABADI

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Chair of Committee, Hamid A. Toliyat Committee Members, Prasad Enjeti

Robert S. Balog

Shankar P. Bhattacharyya

Reza Langari

Head of Department, Chanan Singh

August 2013

Major Subject: Electrical Engineering

"

Eqr {tki j v'4235'O cj uj kf 'Co ktcdcf k

### **ABSTRACT**

In this dissertation the ac-link universal power converters, which are a new class of power converters, are introduced and studied in detail. The inputs and outputs of these converters may be dc, ac, single phase, or multi-phase. Therefore, they can be used in a variety of applications, including photovoltaic power generation, wind power generation, and electric vehicles. In these converters the link current and voltage are both alternating and their frequency can be high, which leads to the elimination of the dc electrolytic capacitors and the bulky low-frequency transformers. Therefore, the ac-link universal power converters are expected to have higher reliability and smaller size. Moreover, these converters are soft switching, which results in negligible switching losses and minimized current and voltage stress over devices.

In the first part of the dissertation, the parallel ac-link universal power converter is studied in detail. This converter is an extension of the buck-boost converter. The series ac-link universal power converter, which is dual of the parallel ac-link universal power converter, is proposed in the second part of this dissertation. This converter is an extension of the Cuk converter. A modified configuration with fewer switches, named sparse ac-link universal power converter is proposed in the third part of this dissertation. The sparse ac-link universal power converters can appear as parallel or series.

The performance of all these configurations is evaluated through simulations and experiments.

# To my parents, Minoo and Mohammad To my husband, Siavash

#### ACKNOWLEDGEMENTS

I would like to express my appreciation to all those who have helped me in completing this dissertation.

My deepest gratitude is to my advisor, Prof. Hamid Toliyat, for his continuous support, immense knowledge, constant encouragement and unlimited patience during this work. He introduced me to this interesting topic, and gave me the freedom to explore on my own and to pursue my ideas, helping me to become an independent researcher. During the most difficult times of my PhD study, he encouraged me and helped me to pass those crucial situations. I could not have imagined having a better advisor. I hope one day I will be able to mentor my students as excellent as he does.

My sincere gratitude also goes to members of my graduate study committee: Prof. Prasad Enjeti, Prof. Robert Balog, Prof. Shankar Bhattacharyya, and Prof. Reza Langari for their valuable time and insightful comments. I am deeply grateful for their guidance and help through the years I spent at Texas A&M University. I am grateful to Prof. Balog for providing me with the opportunity of working with him as his graduate assistant for one semester. This valuable experience truly expanded my vision on real life aspects of power electronics.

I would like to deeply thank Mr. William Alexander, Ideal Power Converters Co., Spicewood, TX for his support and guidance during this project. His intelligence and passion for his work has greatly inspired me. Mr. Alexander's invention has opened many doors to the researchers in the area of power electronics.

I would like to also acknowledge the Electrical and Computer Engineering Department at Texas A&M University for providing me with the highest quality of education and research. I would like to specially thank Prof. Chanan Singh, Prof. Krishna Narayanan, Prof. Costas Georghiades, Prof. Scott L. Miller, Ms. Tammy Carda, Ms. Jeanie Marshal, Ms. Anni Brunker, Ms. Claudia Samford, Ms. Janice Allen, Ms. Eugenia Costea, Mr. Wayne Matous, Mr. Henry Gongora, Mr. Chris Jones, and Mr. Jessie Hernandez for all their help and support.

I am very grateful to the electrical and computer engineering department award committee, especially Prof. Mehrdad Ehsani, for selecting this dissertation as the recipient of the first outstanding dissertation award in this department. This award motivated me further to improve my work.

I would also like to acknowledge Dr. Jeihoon Baek and Samsung Advanced Institute of Technology for supporting my research during the last year of my PhD study. Also I would like to thank the California Energy Commission for financially supporting my research.

My sincere appreciation also goes to Prof. Behbood Zoghi from Engineering Technology and Industrial Distribution department for kindly providing me the opportunity to work with him during spring 2008.

I also thank my current and past colleagues. I am very grateful to Anand Balakrishnan for the great collaboration we had on this project during my first year of PhD studies. I would like to thank Robert Vartanian whose excellent hands-on skills can solve any hardware problem in the lab. Many thanks to Vivek Sundaram, who is always

graciously willing to help others. I am so grateful to Yateendra Deshpandeh for all the collaborations and helpful hints that he has given to me. I am very thankful to Babak Farhangi for all his help throughout the last decade. I greatly thank Jae-Bum Park and Matthew Johnson for being such amazing lab managers and being so supportive whenever I needed their assistance. Many thanks to Esra Ozkentli, whose presence in the lab would remind me how wonderful engineering research labs could be if more women join them. I would also like to thank Dr. Salman Talebi, Anil Kumar Chakali, Dr. Seungdeog Choi, Dr. Nicolas Frank, Behrooz Nikbakhtian, Abdulkadir Bostanchi, Hussain Hussain, Khaled Ali Jaafari, Dr. Mehran Mirjafari, Samantha Castillo, Souhib Harb, Somasundaram Essakiappan, Pawan Garg, Harish Sarma Krishnamoorthy, Dibyendu Rana, and Poornima Mazumdar. Working with them has been a great experience.

Words cannot express my gratitude to my parents, my sister, my brother, and my adorable niece. Their endless love and support has helped me overcome all the hardships. The most difficult part of this journey was leaving home and being far from my family for several years.

A very special acknowledgment goes to my best friend, who happens to be my spouse and also my colleague, Siavash Pakdelian. His endless faith in my ability to accomplish this dissertation was my greatest motivation. Without his love, support, and continuous encouragement none of this would have been possible. He has been with me throughout this long journey, making it much more pleasant.

## TABLE OF CONTENTS

| F                                                                            | Page |

|------------------------------------------------------------------------------|------|

| ABSTRACT                                                                     | ii   |

| DEDICATION                                                                   | iii  |

| ACKNOWLEDGEMENTS                                                             | iv   |

| TABLE OF CONTENTS                                                            |      |

| LIST OF FIGURES                                                              |      |

|                                                                              |      |

| LIST OF TABLES                                                               |      |

| 1. INTRODUCTION                                                              | 1    |

| 2. PARALLEL AC-LINK UNIVERSAL POWER CONVERTER                                | 10   |

| <ul><li>2.1. Introduction</li></ul>                                          |      |

| Background                                                                   |      |

| 2.3. Principles of Operation                                                 |      |

| 2.4. Design Procedure                                                        |      |

| <ul><li>2.5. Analysis</li><li>2.6. Low Voltage Ride Through (LVRT)</li></ul> |      |

| 2.7. Load Power Factor Limitation and an Improved Control Algorithm          |      |

| 2.8. Hybrid Parallel AC-Link Universal Power Converter                       |      |

| 2.8.1. Principles of Operation & Analysis for the Third Power Flow Scenario  |      |

| (PV to the Battery and the Load)                                             |      |

| 2.8.2. Principles of Operation & Analysis for the Fourth Power Flow Scenario | 2    |

| (PV and Battery to the Load)                                                 |      |

| 2.9. Simulation and Experimental Results                                     |      |

| 2.9.1. Low Power Tests                                                       |      |

| 2.9.2. Medium Power Tests                                                    |      |

| 2.10. Summary                                                                | 117  |

| 3. SERIES AC-LINK UNIVERSAL POWER CONVERTER                                  | 119  |

| 3.1. Introduction                                                            | 119  |

|                                                                              | 120  |

|    | 3.3.  | Design Procedure and Analysis                                            | 128 |

|----|-------|--------------------------------------------------------------------------|-----|

|    | 3.4.  | Simulation and Experimental Results                                      | 133 |

|    | 3.4.  | L. DC-DC Configuration                                                   | 133 |

|    |       | 2. DC to Three-Phase AC Configuration                                    |     |

|    |       | 3. AC-AC Configuration                                                   |     |

|    | 3.5.  | Summary                                                                  |     |

| 4. | CDA   | RSE AND ULTRA-SPARSE AC-LINK UNIVERSAL POWER                             |     |

| 4. |       | IVERTERS                                                                 | 146 |

|    | 001   | THE ENGINEERING                                                          | 110 |

|    | 4.1.  | Introduction                                                             | 146 |

|    | 4.2.  | Sparse AC-Link Universal Power Converter                                 |     |

|    | 4.3.  | Ultra-Sparse AC-Link Universal Power Converter                           |     |

|    | 4.4.  | Comparison of the Parallel, Sparse Parallel, and Ultra-Sparse Parallel A |     |

|    |       | Link Universal Power Converters                                          |     |

|    | 4.4.  | I. Efficiency                                                            |     |

|    | 4.4.  | · · · · · · · · · · · · · · · · · · ·                                    |     |

|    | 4.5.  |                                                                          |     |

|    | 4.5.  | 1. DC-AC and AC-DC Sparse Parallel AC-Link Universal Power               |     |

|    |       | Converter                                                                | 170 |

|    | 4.5.  | 2. DC-AC Ultra Sparse Parallel AC-Link Universal Power Converter.        |     |

|    |       | 3. AC-AC Configuration                                                   |     |

|    | 4.6.  | Summary                                                                  |     |

|    |       |                                                                          |     |

| 5. | . SUN | IMARY AND FUTURE WORK                                                    | 188 |

| p  | EEERE | NCES                                                                     | 101 |

## LIST OF FIGURES

|                                                                                                                                                                                                                                                                                                                                                                                                    | Page |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1 Total cost breakdown and the total failures by main components in a PV system                                                                                                                                                                                                                                                                                                             | 2    |

| Figure 2 Total cost breakdown of a wind power generation system and the percentage contribution of different components of a wind power generation system to overall downtime                                                                                                                                                                                                                      | 3    |

| Figure 3 Centralized converter-based PV system                                                                                                                                                                                                                                                                                                                                                     | 5    |

| Figure 4 Multiple-stage conversion systems used in PV applications                                                                                                                                                                                                                                                                                                                                 | 5    |

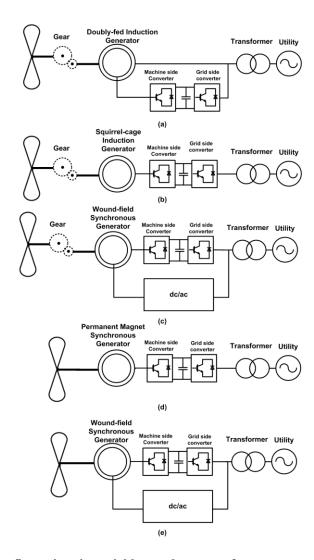

| Figure 5 Wind turbine configurations in variable speed constant frequency systems:  (a) indirect drive using doubly-fed induction generator, (b) indirect drive using squirrel-cage induction generator, (c) indirect drive using wound-field synchronous generator, (d) direct drive using permanent magnet synchronous generator, (e) direct drive using wound-field synchronous generator [10]. | 6    |

| Figure 6 Dc-dc buck-boost converter: (a) configuration, (b) energizing mode (mode 1), (c) de-energizing mode (mode 2), (d) voltage and current waveforms                                                                                                                                                                                                                                           | 12   |

| Figure 7 An alternative representation of the dc-dc buck-boost converter                                                                                                                                                                                                                                                                                                                           | 13   |

| Figure 8 Dc-dc ac-link buck-boost converter: configuration, behavior of the circuit during different modes, and waveforms                                                                                                                                                                                                                                                                          | 15   |

| Figure 9 Bidirectional dc-dc ac-link buck-boost converter                                                                                                                                                                                                                                                                                                                                          | 16   |

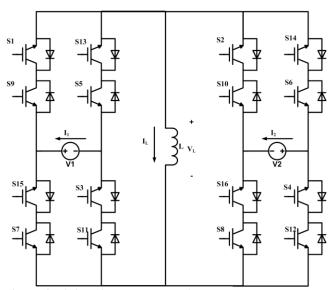

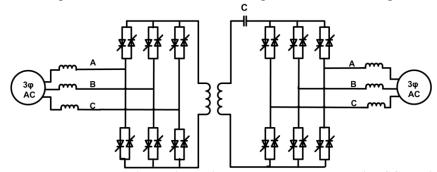

| Figure 10 (a) bidirectional dc-ac ac-link buck-boost converter, (b) bidirectional ac-<br>dc ac-link buck-boost converter, (c) bidirectional ac-ac ac-link buck-boost<br>converter                                                                                                                                                                                                                  |      |

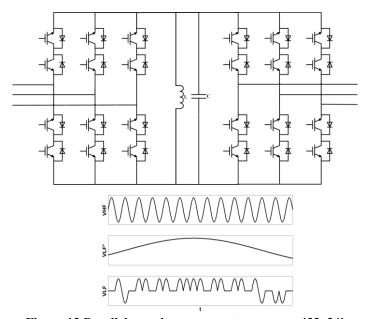

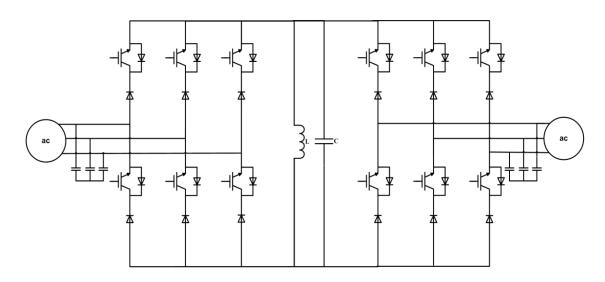

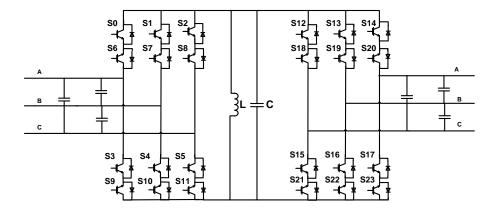

| Figure 11 Soft-switching bidirectional ac-ac ac-link buck-boost converter (ac-ac parallel ac-link universal power converter)                                                                                                                                                                                                                                                                       | 18   |

| Figure 12 Ac-ac dc-link buck-boost converter proposed in [32]                                                                                                                                                                                                                                                                                                                                      | 18   |

| Figure 13 Parallel ac voltage resonant converter [33, 34]                                                                                                                                                                                                                                                                                                                                          | 19   |

| Figure 14 Soft switching ac-ac dc-link buck-boost converter [38]                                                                                                                                                                                                                                                                                                                                   | 20   |

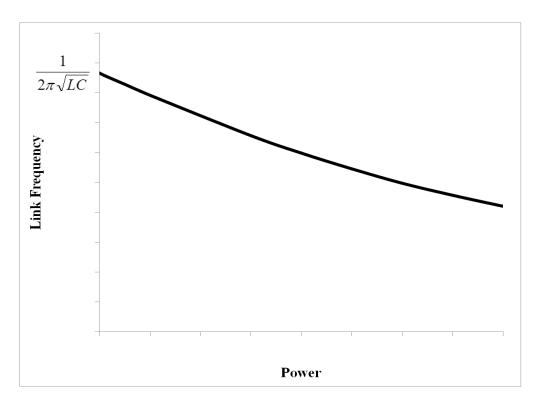

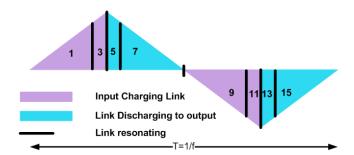

| Figure 15 Circuit behavior in different modes of operation                                                                                                                                                                                                                                                                                                                                         | 25   |

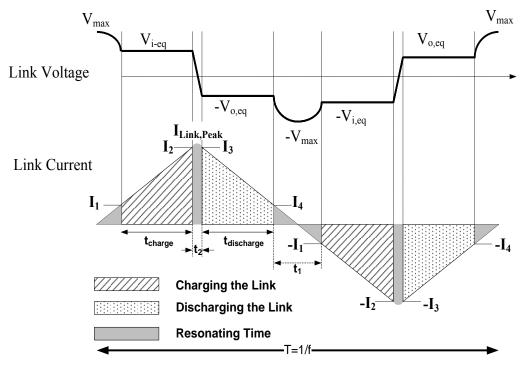

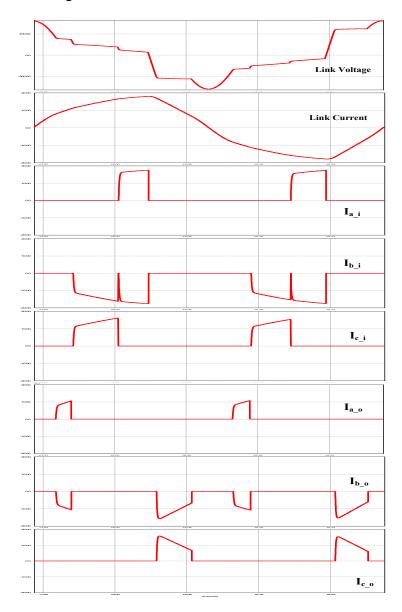

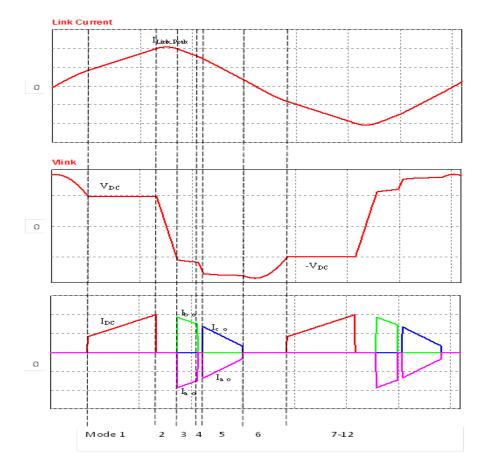

| Figure 16 | Voltage and current waveforms showing the behavior of the circuit during different modes of operation                                                                                         | .31 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

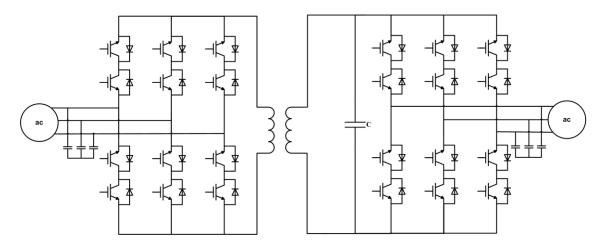

| Figure 17 | Parallel ac-link universal power converter with galvanic isolation                                                                                                                            | .32 |

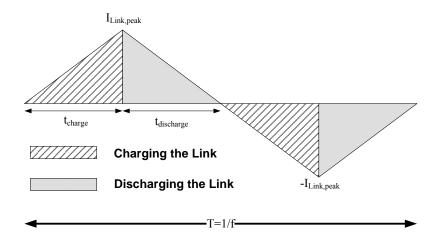

| Figure 18 | Link current when the resonating time is negligible                                                                                                                                           | .34 |

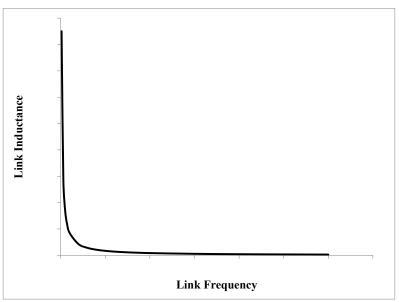

| Figure 19 | Link inductance vs. link frequency                                                                                                                                                            | .35 |

| Figure 20 | Link voltage and current when resonating time is not negligible                                                                                                                               | .39 |

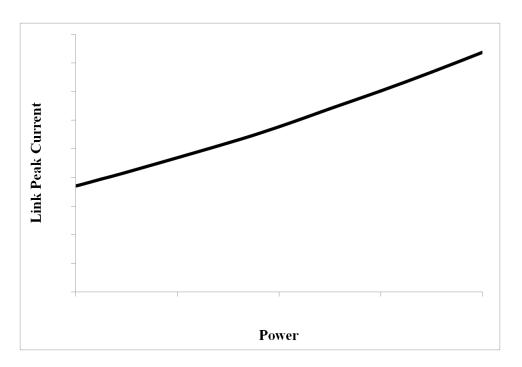

| Figure 21 | Link peak current variations vs. power                                                                                                                                                        | .40 |

| Figure 22 | Link frequency variations vs. power                                                                                                                                                           | .40 |

| Figure 23 | Different modes of operation in the ac-ac parallel ac-link universal converter during a voltage drop                                                                                          | .42 |

| Figure 24 | Link voltage, link current, and unfiltered input/output currents with the improved control algorithm                                                                                          | .46 |

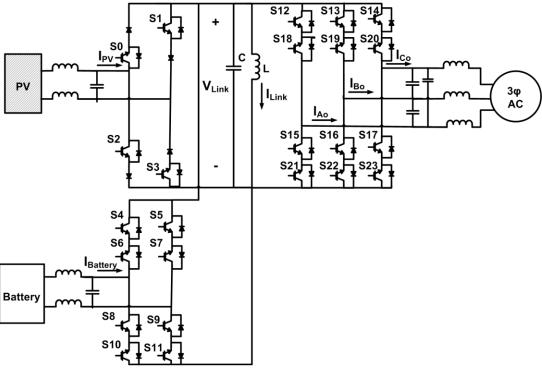

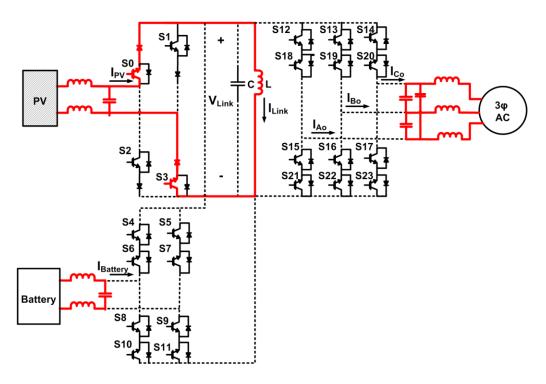

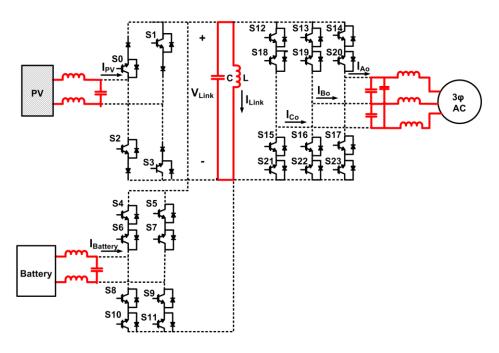

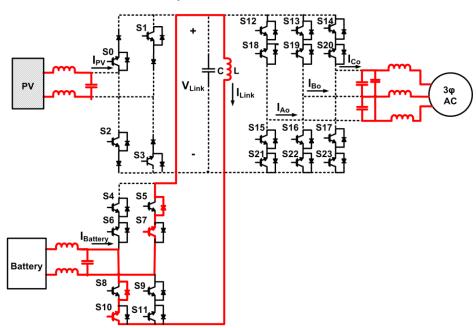

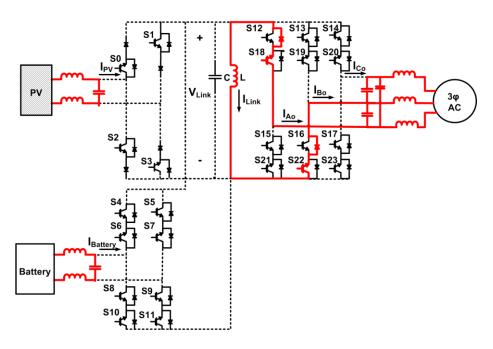

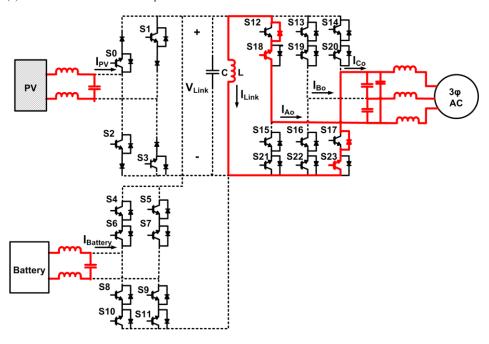

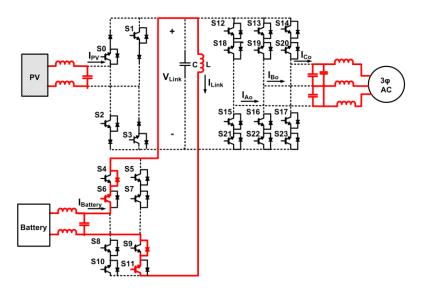

| Figure 25 | Hybrid parallel ac-link universal power converter interfacing PV, battery, and a three-phase load                                                                                             | .50 |

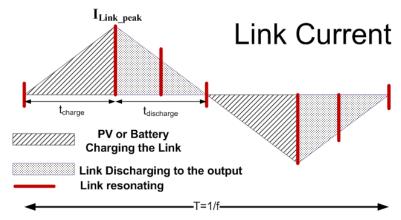

| Figure 26 | Link current of the hybrid inverter during the first and second power-flow scenarios                                                                                                          | .50 |

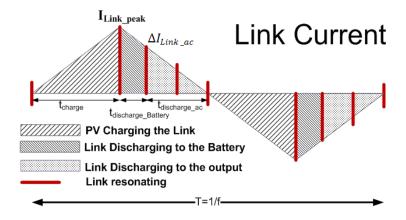

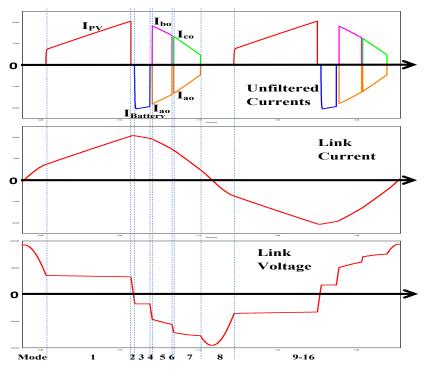

| Figure 27 | Link current of the hybrid inverter during the third power flow                                                                                                                               | .51 |

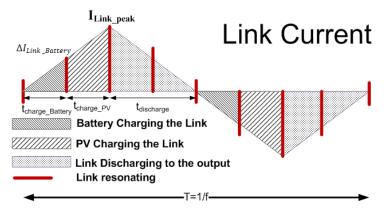

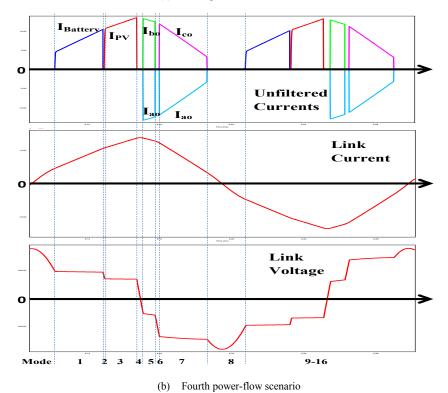

| Figure 28 | Link current of the hybrid inverter during the fourth power-flow scenario                                                                                                                     | .51 |

| Figure 29 | Circuit behavior during different modes of operation                                                                                                                                          | .59 |

| Figure 30 | Current and voltage waveforms                                                                                                                                                                 | .63 |

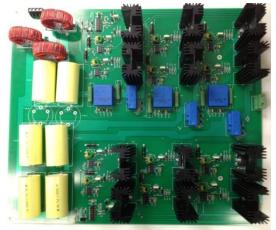

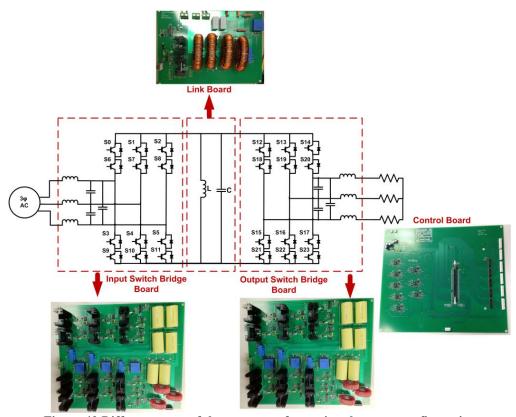

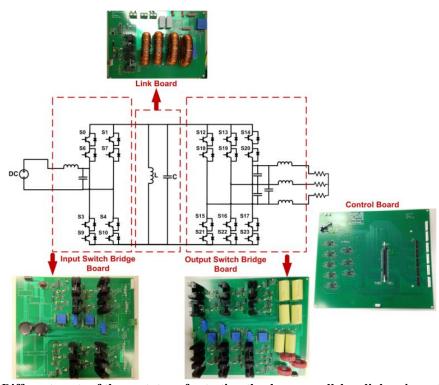

| Figure 31 | Fabricated input/ output switch board                                                                                                                                                         | .65 |

| Figure 32 | Fabricated link board                                                                                                                                                                         | .65 |

| Figure 33 | Fabricated control board                                                                                                                                                                      | .65 |

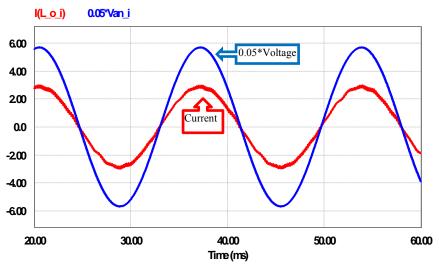

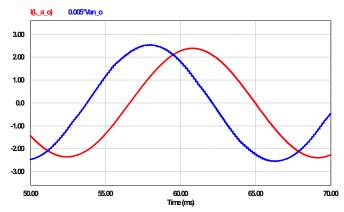

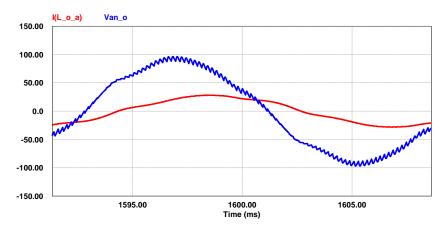

| Figure 34 | The input-side current and scaled voltage in the ac-ac parallel ac-link universal converter when the current is regulated such that the unfiltered current is in-phase with the input voltage | .67 |

| Figure 35 | The input-side current and scaled voltage in the ac-ac parallel ac-link universal converter when the current is regulated such that the filtered current is in-phase with the input voltage | 67 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 36 | The load current and scaled voltage in the ac-ac parallel ac-link universal converter                                                                                                       | 68 |

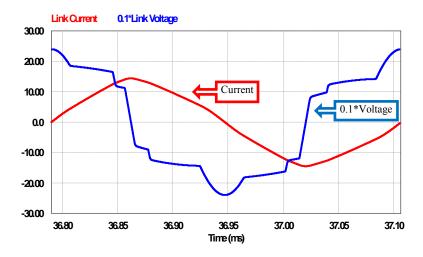

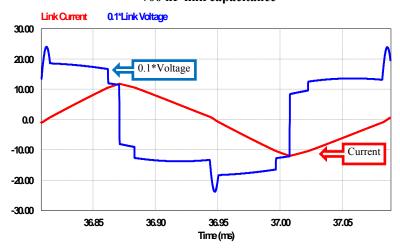

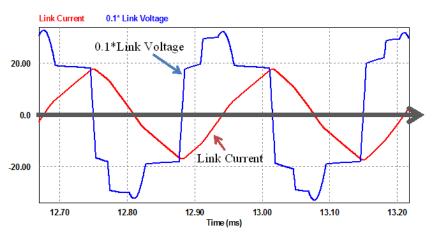

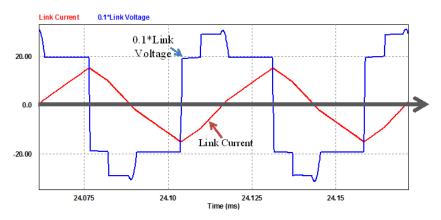

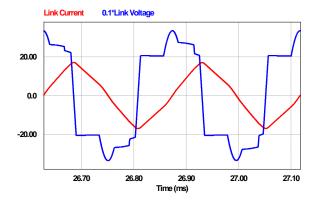

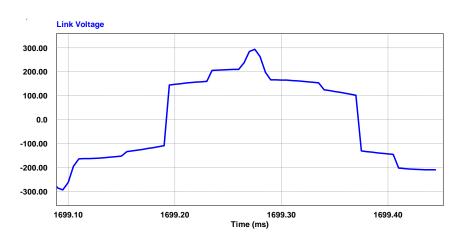

| Figure 37 | The link current and scaled voltage in the ac-ac parallel ac-link universal converter with 700 nF link capacitance                                                                          | 69 |

| Figure 38 | The link current and scaled voltage in the ac-ac parallel ac-link universal converter with 20 nF link capacitance                                                                           | 69 |

| Figure 39 | Fabricated and tested three-phase ac-ac parallel ac-link universal converter                                                                                                                | 69 |

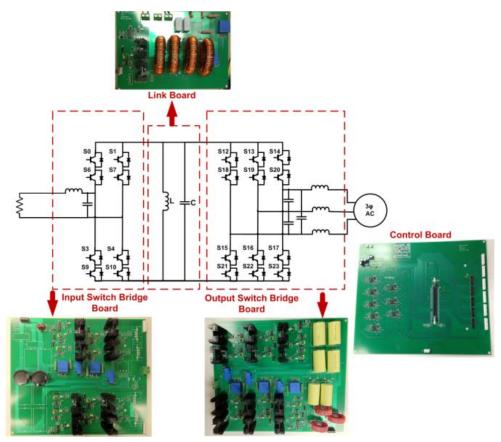

| Figure 40 | Different parts of the prototype for testing the ac-ac configuration                                                                                                                        | 70 |

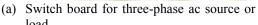

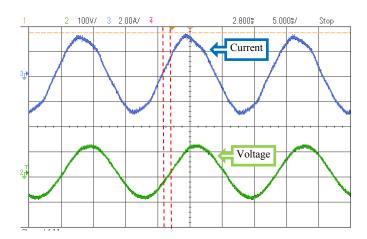

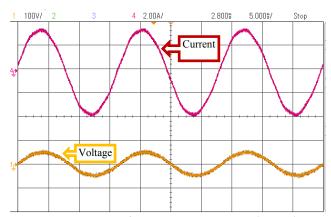

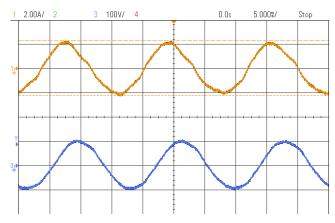

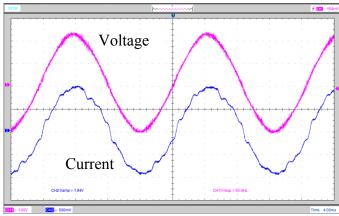

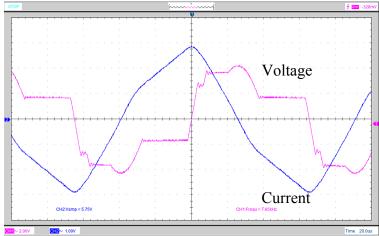

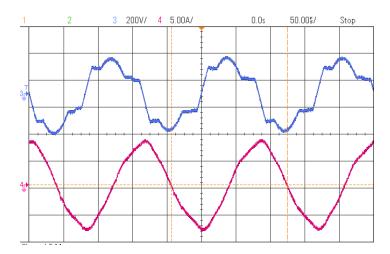

| Figure 41 | The input current and voltage in the ac-ac parallel ac-link universal converter (experimental results)                                                                                      | 70 |

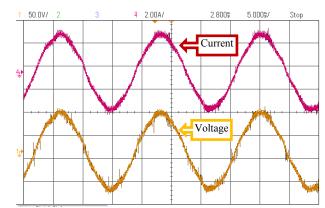

| Figure 42 | The load current and voltage in the ac-ac parallel ac-link universal converter (experimental results)                                                                                       | 71 |

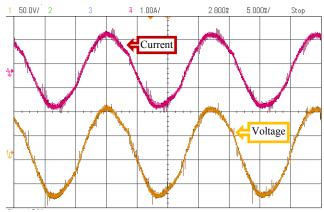

| Figure 43 | The load current and voltage in the ac-ac parallel ac-link universal converter when the output frequency is set at 30 Hz (experimental results)                                             | 72 |

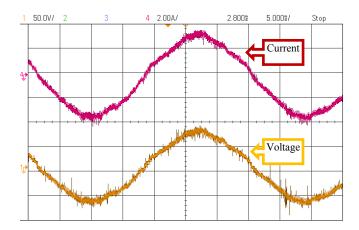

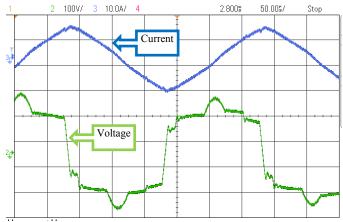

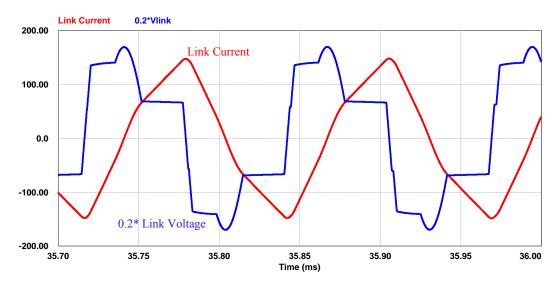

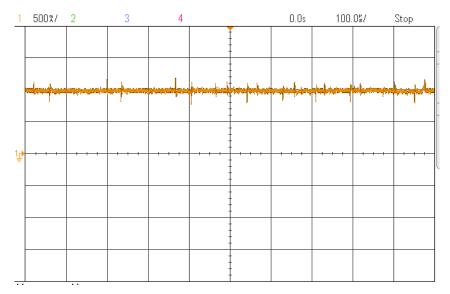

| Figure 44 | The link current and voltage in the ac-ac parallel ac-link universal converter                                                                                                              | 72 |

| Figure 45 | The input current and voltage of the ac-ac parallel ac-link universal converter in step-up operation (Experimental results)                                                                 | 73 |

| Figure 46 | The load current and voltage of the ac-ac parallel ac-link universal converter in step-up operation (Experimental results)                                                                  | 73 |

| Figure 47 | The link current and voltage of the ac-ac parallel ac-link universal converter in step-up operation (Experimental results)                                                                  | 74 |

| Figure 48 | Input current and scaled voltage in the ac-ac parallel ac-link universal converter using the improved control method                                                                        | 75 |

| Figure 49 | Load current and scaled voltage in the ac-ac parallel ac-link universal converter using the improved control method                                                                         | 75 |

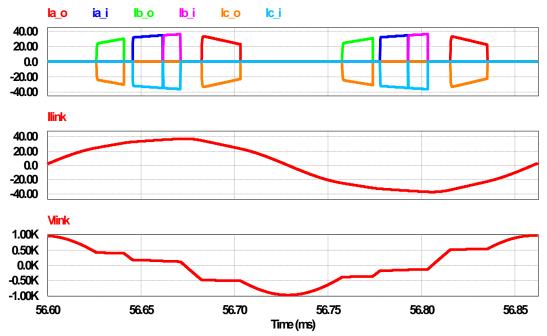

| Figure 50 | Unfiltered phase currents, link current and link voltage in the ac-ac parallel ac-link universal converter using the improved control method         | 76 |

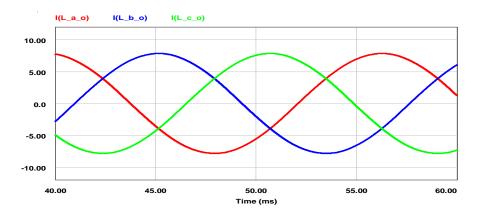

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

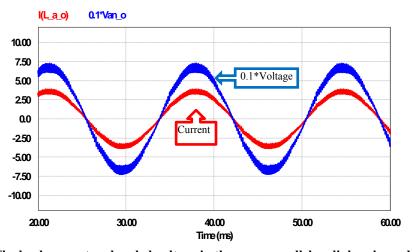

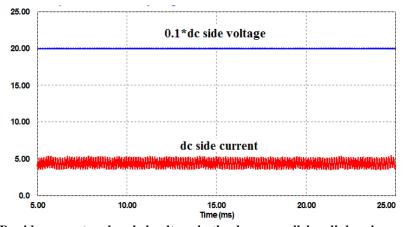

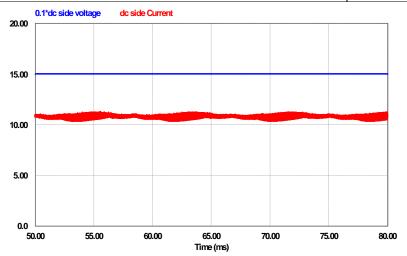

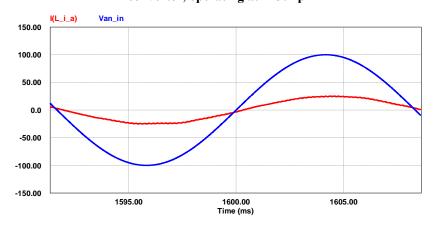

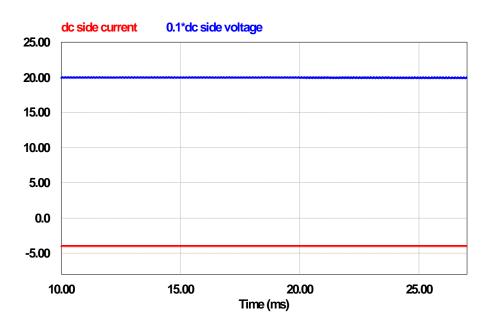

| Figure 51 | Dc side current and scaled voltage in the dc-ac parallel ac-link universal converter                                                                 | 77 |

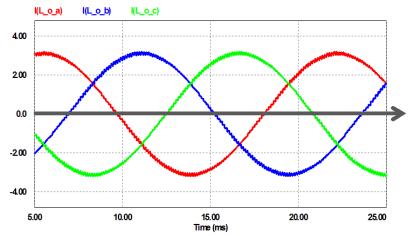

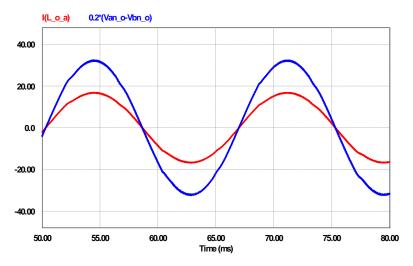

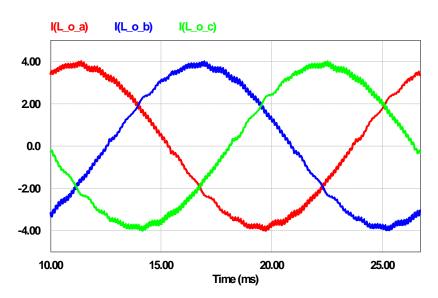

| Figure 52 | Ac-side currents in the dc-ac parallel ac-link universal converter                                                                                   | 77 |

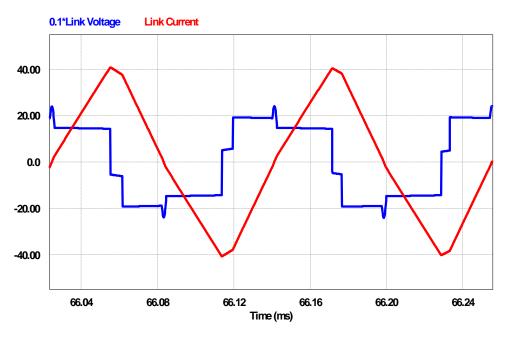

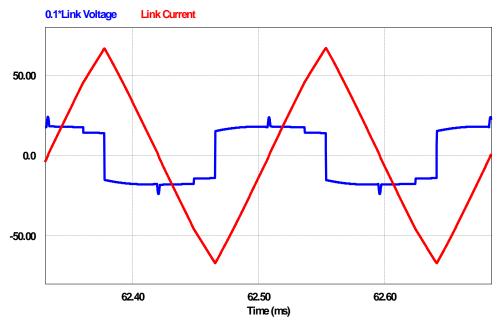

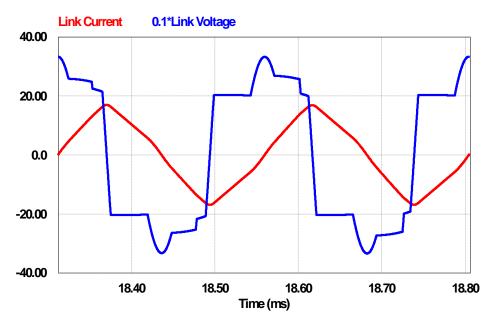

| Figure 53 | Link current and scaled link voltage in the dc-ac parallel ac-link universal converter with 880 $\mu H$ link inductance and 400 nF link capacitance  | 78 |

| Figure 54 | Link current and scaled link voltage in the dc-ac parallel ac-link universal converter with 200 $\mu H$ link inductance and 20 nF link capacitance   | 78 |

| Figure 55 | Different parts of the prototype for testing the dc-ac parallel ac-link universal converter                                                          | 79 |

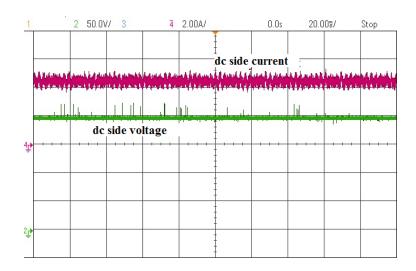

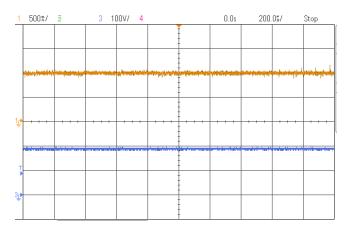

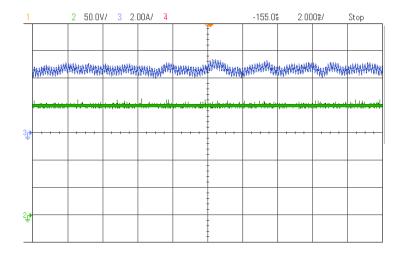

| Figure 56 | Dc-side current (2 A/div) and voltage (50 V/div) in the dc-ac parallel aclink universal converter (experimental results), time scale: 20 ms/div      | 79 |

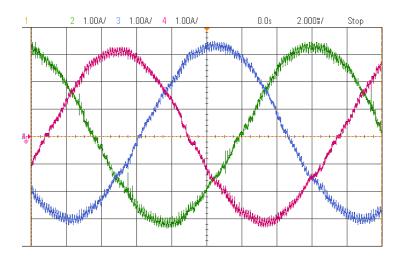

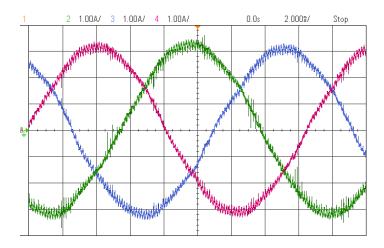

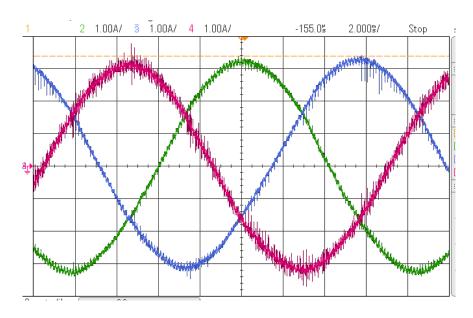

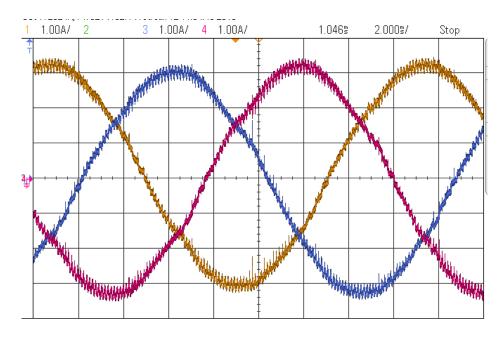

| Figure 57 | Ac side currents (1 A/div) in the dc-ac parallel ac-link universal converter (experimental results), time scale: 2 ms/div                            | 80 |

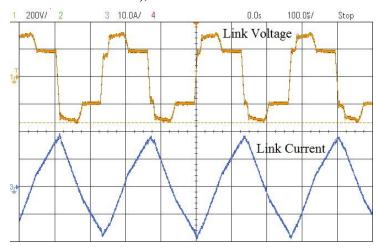

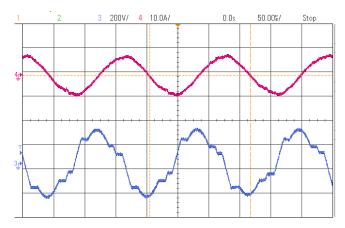

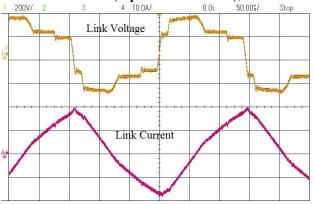

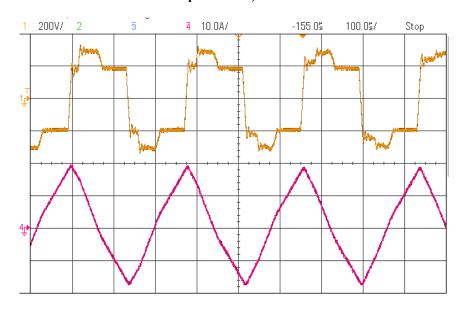

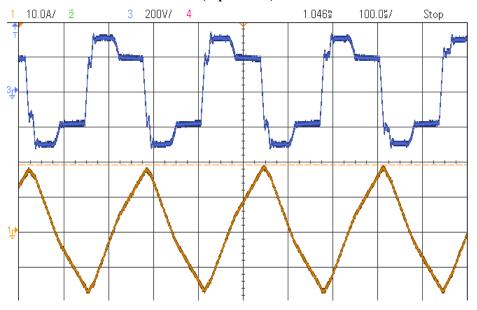

| Figure 58 | Link voltage (200 V/div) and current (10 A/div) in the dc-ac parallel aclink universal converter (experimental results), time scale: 100 $\mu$ s/div | 80 |

| Figure 59 | Ac-side currents in the ac-dc parallel ac-link universal converter                                                                                   | 81 |

| Figure 60 | Dc-side current and scaled voltage in the ac-dc parallel ac-link universal converter                                                                 | 81 |

| Figure 61 | Link current and scaled voltage in the ac-dc parallel ac-link universal converter                                                                    | 81 |

| Figure 62 | Different parts of the tested ac-dc parallel ac-link universal power converter                                                                       | 82 |

| Figure 63 | Ac-side current (top) and voltage (bottom) in the ac-dc parallel ac-link universal converter operating at 200 W (Experiment)                         | 83 |

| Figure 64 | Dc-side current (top) and voltage (bottom) in the ac-dc parallel ac-link universal converter operating at 200 W (Experiment)                         | 83 |

| Figure 65 | Link current (top) and voltage (bottom) in the ac-dc parallel ac-link universal converter operating at 200 W (Experiment)                            | 83 |

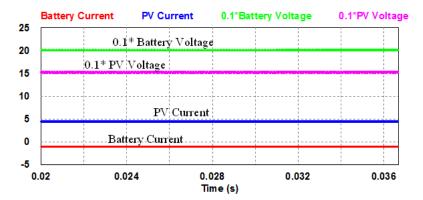

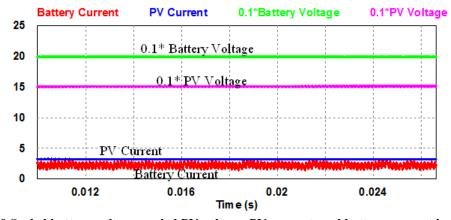

| Figure 66 | Scaled battery voltage, scaled PV voltage, PV current, and battery current in the hybrid parallel ac-link universal converter during the third power-flow scenario                         | .85 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

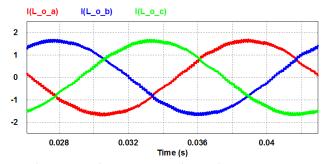

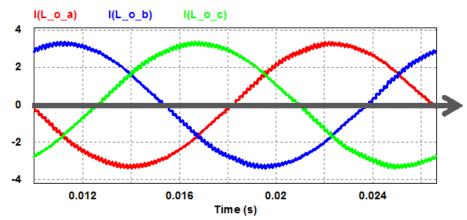

| Figure 67 | Ac-side currents in the hybrid parallel ac-link universal converter during the third power-flow scenario.                                                                                  | .85 |

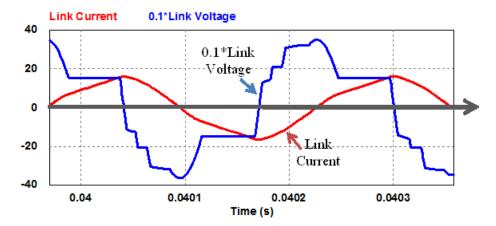

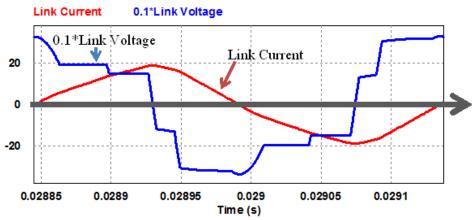

| Figure 68 | Link voltage and current in the hybrid parallel ac-link universal converter during the third power-flow scenario                                                                           | .86 |

| Figure 69 | Ac-side currents in the hybrid parallel ac-link universal converter during the fourth power-flow scenario                                                                                  | .86 |

| Figure 70 | Scaled battery voltage, scaled PV voltage, PV current, and battery current in the hybrid parallel ac-link universal converter during the fourth power-flow scenario                        | .86 |

| Figure 71 | Link voltage and current in the hybrid parallel ac-link universal converter during the fourth power-flow scenario                                                                          | .87 |

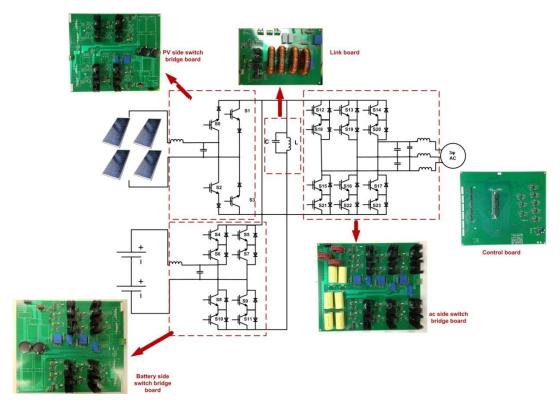

| Figure 72 | Different parts of the tested hybrid parallel ac-link universal converter                                                                                                                  | .88 |

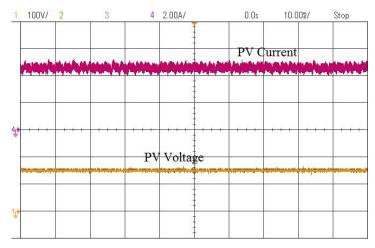

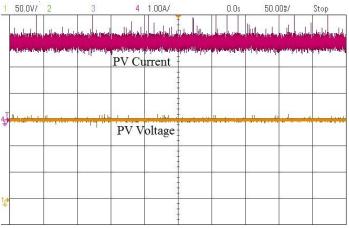

| Figure 73 | PV current (2 A/div) and voltage (100 V/div) in the hybrid parallel ac-link universal converter during the third power-flow scenario (experimental results), time scale: 10 ms/div         | .89 |

| Figure 74 | Battery current (0.5 A/div) and voltage (100 V/div) in the third power flow scenario (experimental results), time scale: 100 $\mu$ s/div                                                   | .89 |

| Figure 75 | Ac-side current (0.5 A/div) in the hybrid parallel ac-link universal converter during the third power-flow scenario (experimental results), time scale: 2 ms/div                           | .89 |

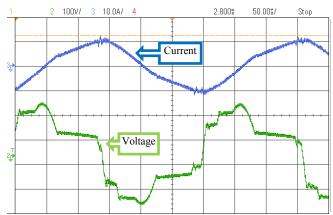

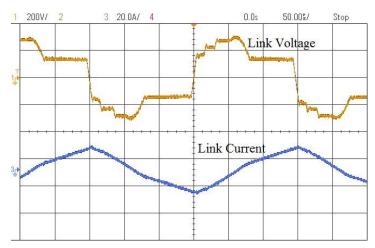

| Figure 76 | Link voltage (200 V/div) and current (20 A/div) in the hybrid parallel aclink universal converter during the third power flow scenario (experimental results), time scale: $50  \mu s/div$ | .90 |

| Figure 77 | PV current (1 A/div) and voltage (50 V/div) in the hybrid parallel ac-link universal converter during the fourth power-flow scenario (experimental results), time scale: 50 ms/div         | .90 |

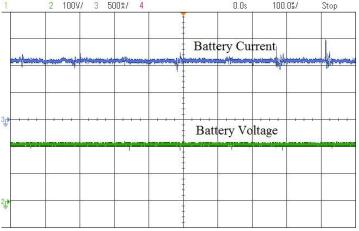

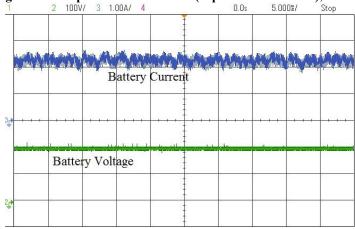

| Figure 78 | Battery current (1 A/div) and voltage (100 V/div) in the hybrid parallel ac-link universal converter during the fourth power-flow scenario (experimental results), time scale: 5 ms/div    | .90 |

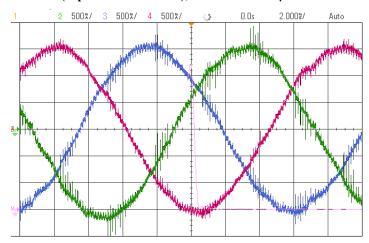

| Figure 79 | Ac-side current (1 A/div) in the hybrid parallel ac-link universal converter during the fourth power flow scenario (experimental results), time scale: 2 ms/div                       | .91 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 80 | Link voltage (200 V/div) and current (10 A/div) in the hybrid parallel aclink universal converter during the fourth power-flow scenario (experimental results), time scale: 50 µs/div | .91 |

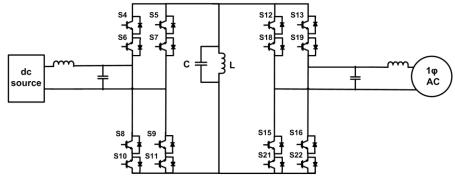

| Figure 81 | Dc to single-phase ac parallel ac-link universal converter (first solution)                                                                                                           | .93 |

| Figure 82 | Dc-side current and scaled voltage in the dc to single-phase ac parallel aclink universal converter (first solution)                                                                  | .93 |

| Figure 83 | Ac-side current and scaled voltage in the dc to single-phase ac parallel aclink universal converter (first solution)                                                                  | .94 |

| Figure 84 | Link current and scaled voltage in the dc to single-phase ac parallel aclink universal converter (first solution)                                                                     | .94 |

| Figure 85 | Link current in the dc to single-phase ac parallel ac-link universal converter (first solution)                                                                                       | .95 |

| Figure 86 | Link current and scaled voltage in the dc to single-phase ac parallel aclink universal converter (first solution) when the load current is close to zero                              | .95 |

| Figure 87 | Current of the dc-side filter capacitor in the dc to single-phase ac parallel ac-link universal converter (first solution)                                                            | .96 |

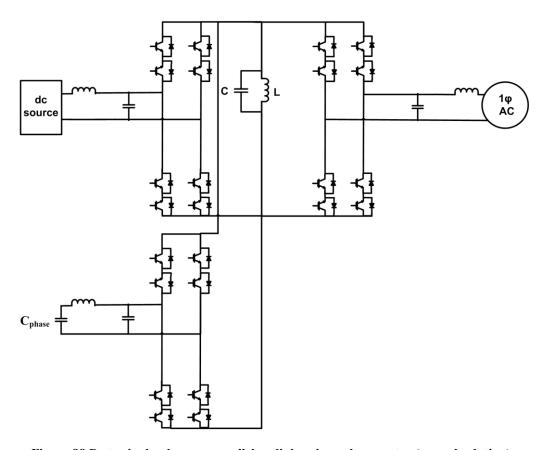

| Figure 88 | Dc to single-phase ac parallel ac-link universal converter (second solution)                                                                                                          | .97 |

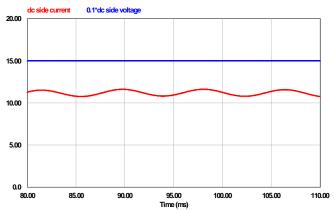

| Figure 89 | Dc-side current and scaled voltage in the dc to single-phase ac parallel aclink universal converter (second solution)                                                                 | .98 |

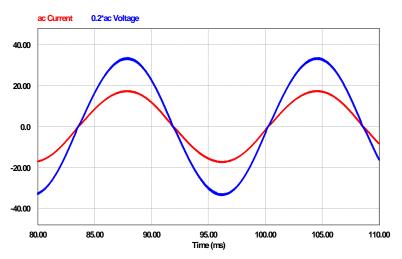

| Figure 90 | Load current and scaled voltage in the dc to single-phase ac parallel aclink universal converter (second solution)                                                                    | .98 |

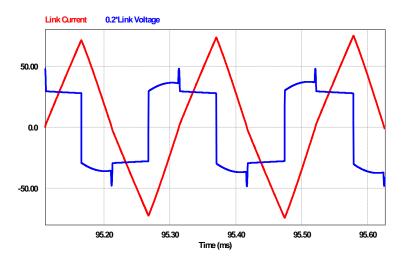

| Figure 91 | Link current and scaled voltage in the dc to single-phase ac parallel aclink universal converter (second solution) when the capacitor acts as a load                                  | .99 |

| Figure 92 | Link current and scaled voltage in the dc to single phase ac parallel aclink universal converter (second solution) when the capacitor acts as a source.                               | 99  |

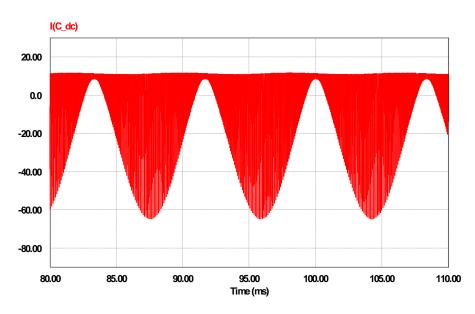

| Figure 93 Capacitor current and scaled voltage in the dc to single-phase ac parallel ac-link universal converter (second solution)                                             | 100 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

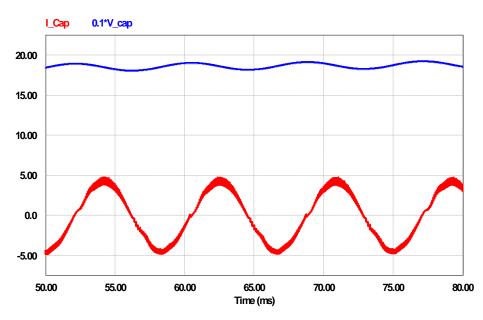

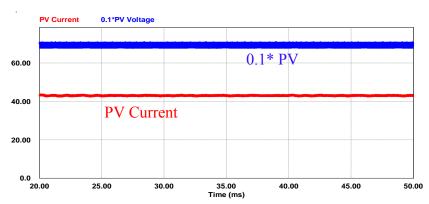

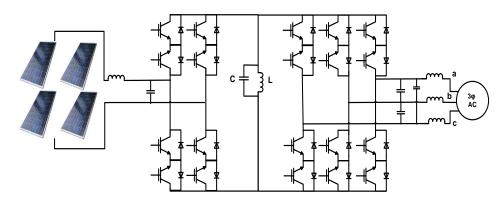

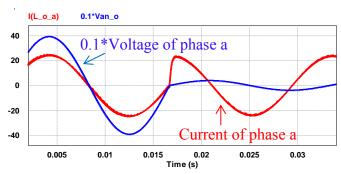

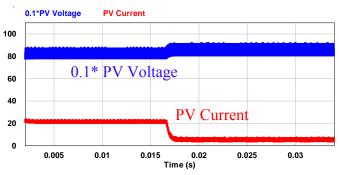

| Figure 94 PV current and scaled voltage in the 30 kW dc-ac parallel ac-link universal power converter at full power                                                            | 103 |

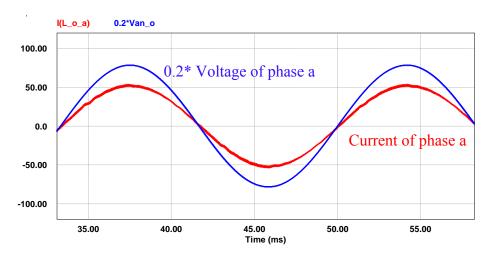

| Figure 95 Ac-side current and scaled voltage in the 30 kW dc-ac parallel ac-link universal power converter at full power                                                       | 104 |

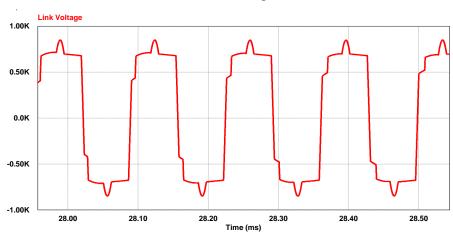

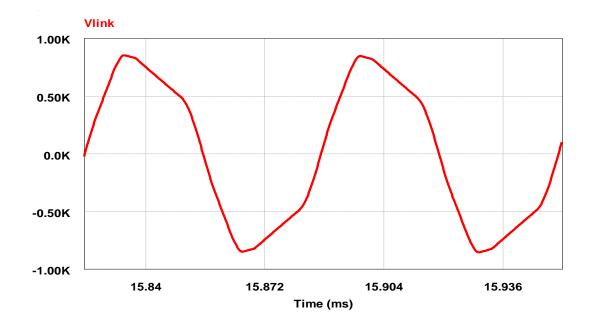

| Figure 96 Link voltage in the 30 kW dc-ac parallel ac-link universal power converter at full power.                                                                            | 104 |

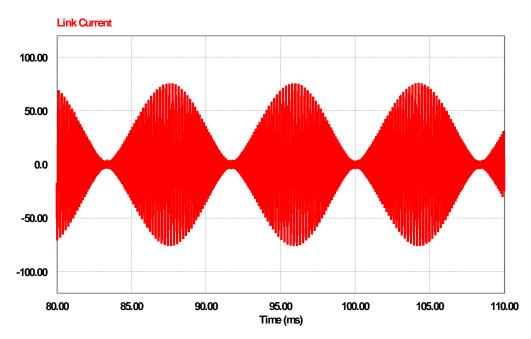

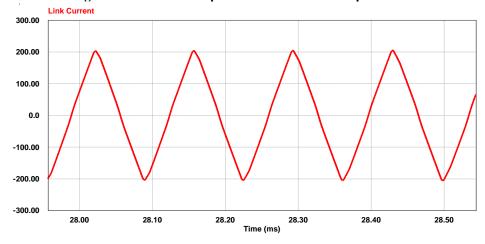

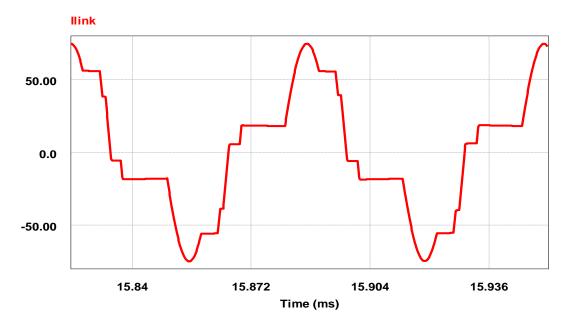

| Figure 97 Link current in the 30 kW dc-ac parallel ac-link universal power converter at full power.                                                                            | 104 |

| Figure 98 Link current and voltage in the dc-ac parallel ac-link universal power converter operating at 15 kW                                                                  | 105 |

| Figure 99 Ac-side current and scaled voltage in the 30 kW dc-ac parallel ac-link universal power converter when the irradiance drops from 850 w/m² to 650 w/m².                | 106 |

| Figure 100 Ac-side current and voltage in the 30 kW dc-ac parallel ac-link universal power converter when the temperature changes from 25 °C to 50 °C                          | 106 |

| Figure 101 Dc-ac parallel ac-link universal power converter in case LVRT feature is needed                                                                                     | 106 |

| Figure 102 Ac-side current and voltage in the 30 kW dc-ac parallel ac-link universal power converter when the ac-side voltage drops to 10% of its nominal value (at t=0.016 s) | 107 |

| Figure 103 PV current and voltage in the 30 kW dc-ac parallel ac-link universal power converter when the ac-side voltage drops to 10% of its nominal value (at t=0.016 s)      | 108 |

| Figure 104 30 kW inverter developed and manufactured by Ideal Power Converters Co.                                                                                             | 108 |

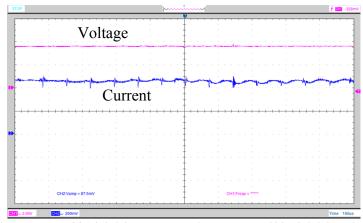

| Figure 105 Dc-side current (20A/division) and dc-side voltage (400V/division) in the 30 kW dc-ac parallel ac-link universal power converter (experiment).                      | 108 |

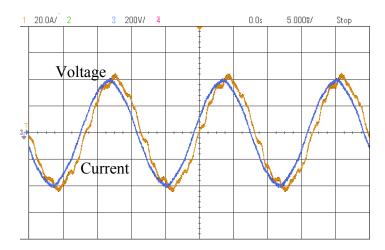

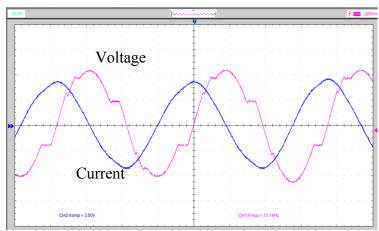

| Figure 106 Ac-side voltage (200V/division) and ac-side current (30A/division) in the 30 kW dc-ac parallel ac-link universal power converter (experiment).                      | 109 |

| Figure 107 | Link current (50A/division) and link voltage (400V/division) in the 30 kW dc-ac parallel ac-link universal power converter at full power (experiment)       | 109  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 108 | Ac-side current (20 A/ division) and voltage (200 V/division) in the 30 kW dc-ac parallel ac-link universal power converter running at 25 kW (experiment)   | 109  |

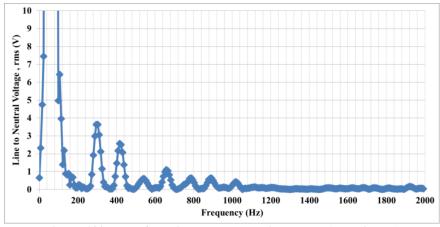

| Figure 109 | FFT of the line to neutral grid voltage (experiment)                                                                                                        | 110  |

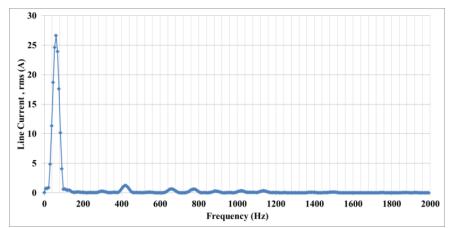

| Figure 110 | FFT of the load current in the dc-ac parallel ac-link universal power converter operating at 25 kW (experiment)                                             | 110  |

| Figure 111 | Link current (50A/division) and link voltage (400V/division) in the dcac parallel ac-link universal power converter operating at 15 kW (experiment)         | 110  |

| Figure 112 | Link current (50A/division) and link voltage (400V/division) in the dcac parallel ac-link universal power converter operating at 3.75 kW (experiment)       | 111  |

| Figure 113 | PV current (5A/division) and PV voltage (200V/division) in the dc-ac parallel ac-link universal power converter operating at 6.2 kW (experiment)            | .111 |

| Figure 114 | Ac-side current (20A/division) and ac-side voltage (200V/division) in the dc-ac parallel ac-link universal power converter operating at 6.2 kW (experiment) | 111  |

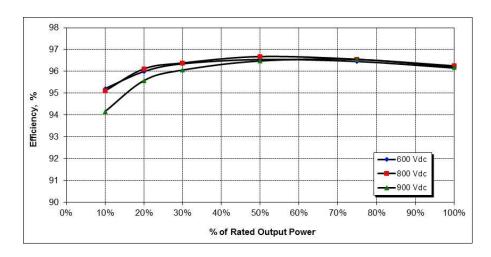

| Figure 115 | CEC Efficiency Curve of the 30 kW dc-ac parallel ac-link universal power converter (experiment) [43]                                                        | 112  |

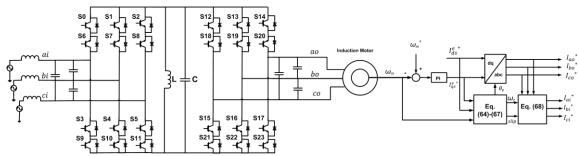

| Figure 116 | Ac-ac parallel ac-link universal converter as a VFD                                                                                                         | 114  |

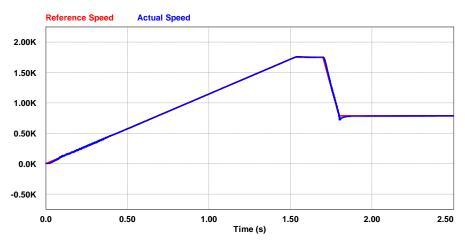

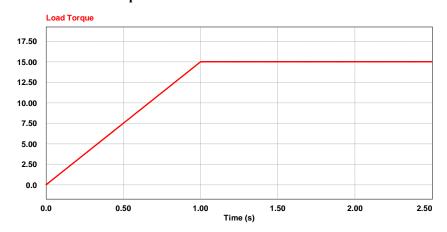

| Figure 117 | The reference speed and the actual speed of the motor (in rpm) derived by the ac-ac parallel ac-link universal converter                                    | 115  |

| Figure 118 | Load torque of the motor derived by the ac-ac parallel ac-link universal converter                                                                          | 115  |

| Figure 119 | Stator current and voltage of the motor derived by the ac-ac parallel ac-<br>link universal converter, operating at 1750 rpm                                | 116  |

| Figure 120 | Input current and voltage in the ac-ac parallel ac-link universal converter.                                                                                | 116  |

| Figure 121 | Stator current and voltage of the motor derived by the ac-ac parallel ac-<br>link universal converter, operating at 780 rpm | 116 |

|------------|-----------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 122 | Link Voltage of the ac-ac parallel ac-link universal converter used as a VFD                                                | 117 |

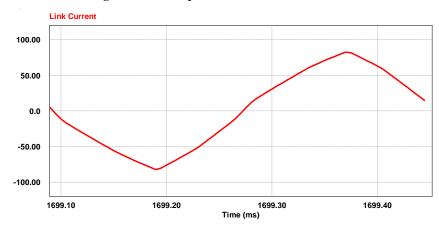

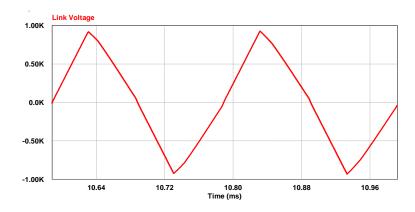

| Figure 123 | Link Current of the ac-ac parallel ac-link universal converter used as a VFD                                                | 117 |

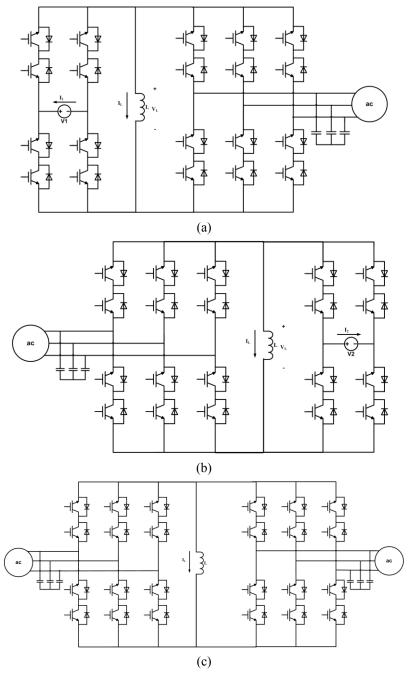

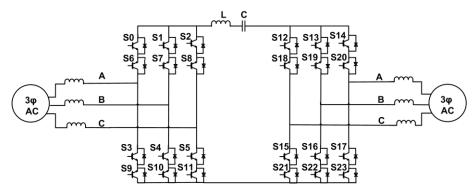

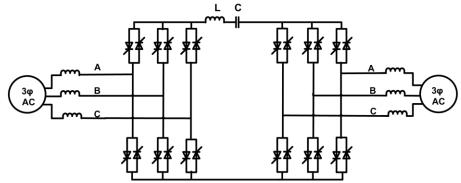

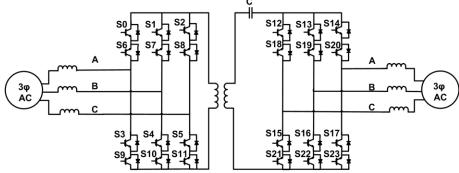

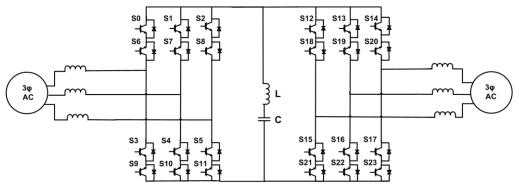

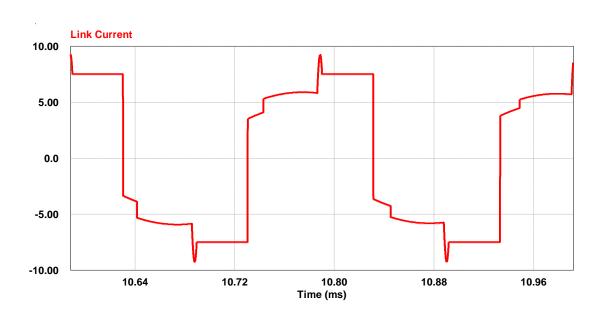

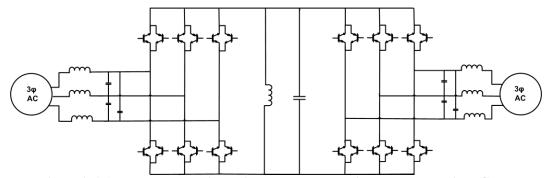

| Figure 124 | Three-phase ac-ac series ac-link universal power converter                                                                  | 121 |

| Figure 125 | Three-phase ac-ac series ac-link universal power converter using SCRs                                                       | 122 |

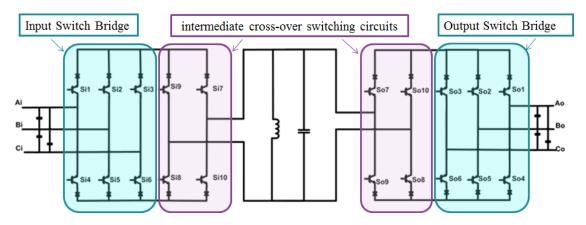

| Figure 126 | Three-phase ac-ac series ac-link universal power converter with galvanic isolation                                          | 122 |

| Figure 127 | Three-phase ac-ac series ac-link universal power converter using SCRs with galvanic isolation                               | 122 |

| Figure 128 | One cycle of the link voltage in the three-phase ac-ac series ac-link universal power converter                             | 122 |

| Figure 129 | Behavior of the series ac-link universal power converter during different modes of operation                                | 125 |

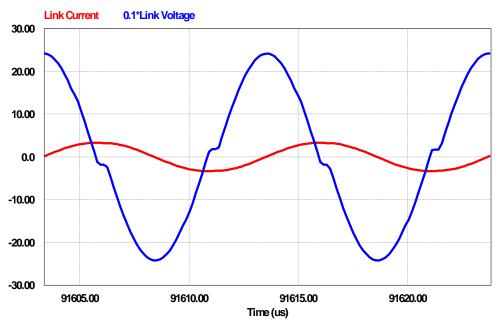

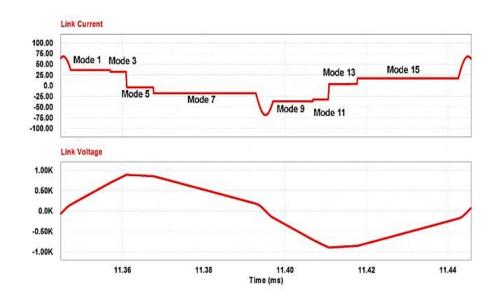

| Figure 130 | Link current and voltage in the series ac-link universal power converter                                                    | 127 |

| Figure 131 | One cycle of the link voltage in the series ac-link universal converter simplified for the design procedure                 | 129 |

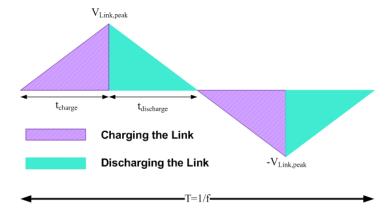

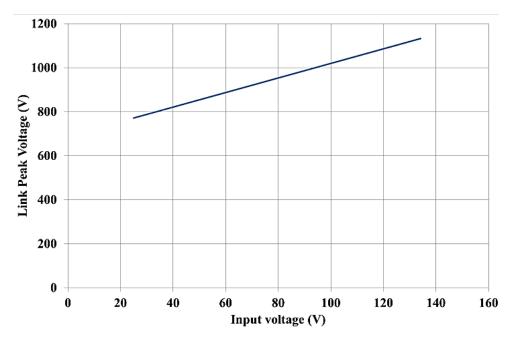

| Figure 132 | Link peak voltage vs. the input voltage in the series ac-link universal converter.                                          | 131 |

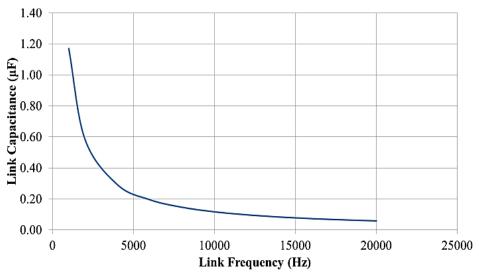

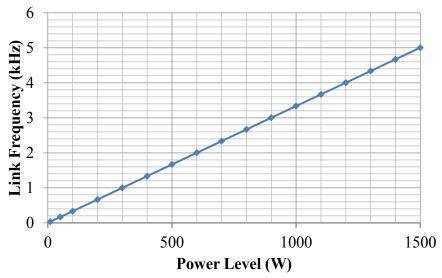

| Figure 133 | Link capacitance vs. the link frequency in the series ac-link universal converter                                           | 131 |

| Figure 134 | Link frequency vs. the power level in the series ac-link universal converter.                                               | 132 |

| Figure 135 | Another form of series ac-link universal power converter                                                                    | 132 |

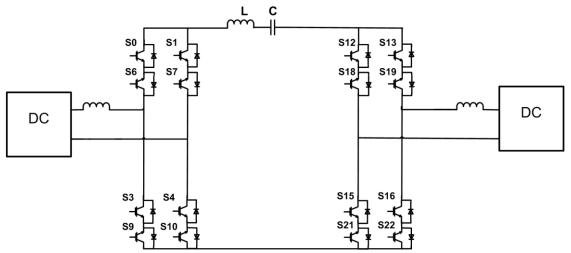

| Figure 136 | Dc-dc series ac-link universal converter                                                                                    | 133 |

| Figure 137 | Input current and scaled voltage in the dc-dc series ac-link universal converter.                                           | 134 |

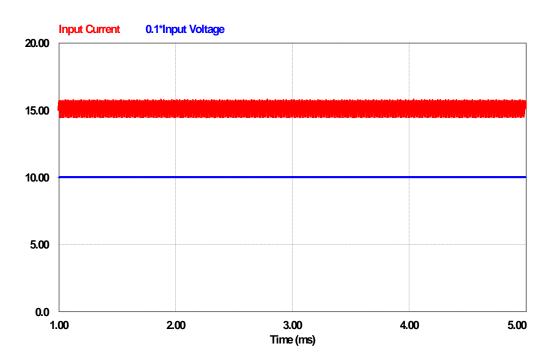

| Figure 138 | Output current and scaled voltage in the dc-dc series ac-link universal converter                                              | 134 |

|------------|--------------------------------------------------------------------------------------------------------------------------------|-----|

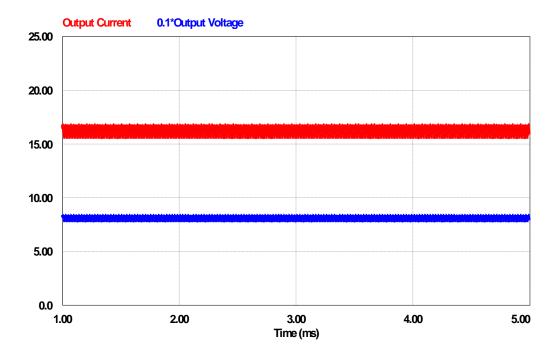

| Figure 139 | Link current and scaled voltage in the dc-dc series ac-link universal converter                                                | 135 |

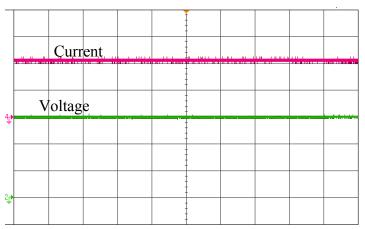

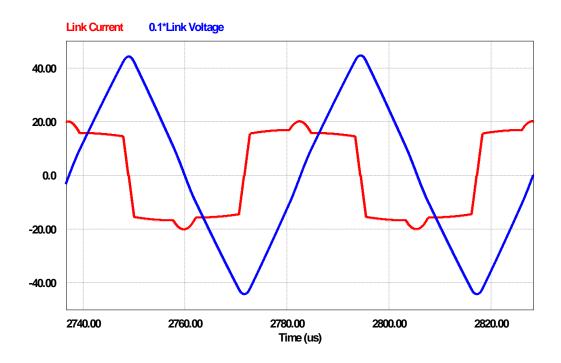

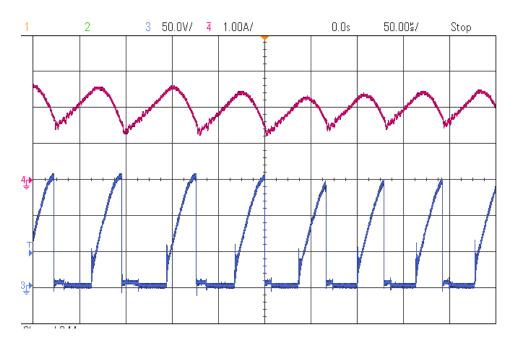

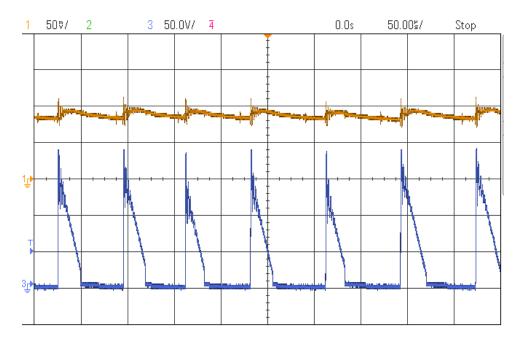

| Figure 140 | Input current (top) and unfiltered voltage (bottom) of the tested dc-dc series ac-link universal power converter (Experiment)  | 136 |

| Figure 141 | Output current (top) and unfiltered voltage (bottom) of the tested dc-dc series ac-link universal power converter (Experiment) | 137 |

| Figure 142 | Link voltage (top) and current (bottom) of the tested dc-dc series ac-link universal power converter (Experiment)              | 137 |

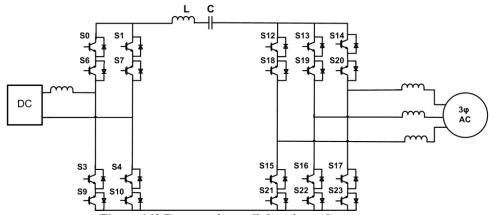

| Figure 143 | Dc-ac series ac-link universal converter                                                                                       | 138 |

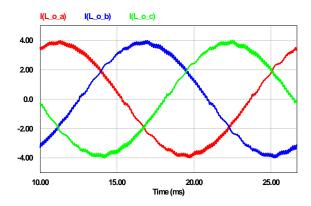

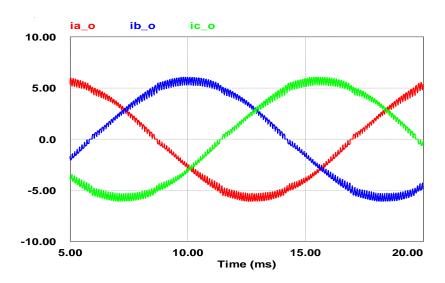

| Figure 144 | Output currents of the simulated 1.5 kW dc-ac series ac-link universal converter.                                              | 139 |

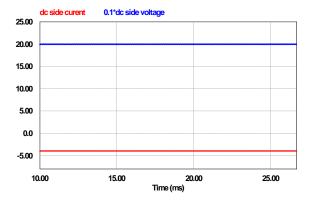

| Figure 145 | Link voltage of the simulated 1.5 kW dc-ac series ac-link universal converter                                                  | 139 |

| Figure 146 | Link current of the simulated 1.5 kW dc-ac series ac-link universal converter.                                                 | 140 |

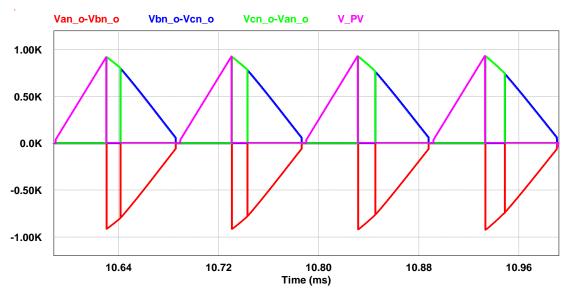

| Figure 147 | Unfiltered line-to-line voltages of the simulated 1.5 kW dc-ac series aclink universal converter                               | 140 |

| Figure 148 | Current and gate command of switch S10 in the simulated 1.5 kW dc-ac series ac-link universal converter                        | 141 |

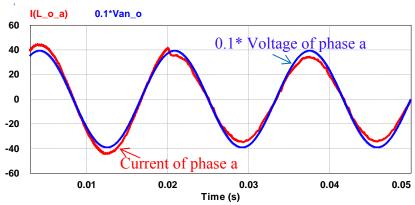

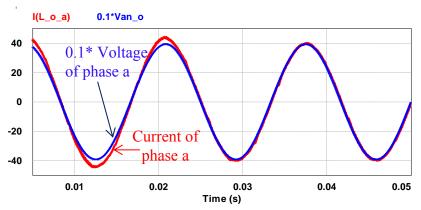

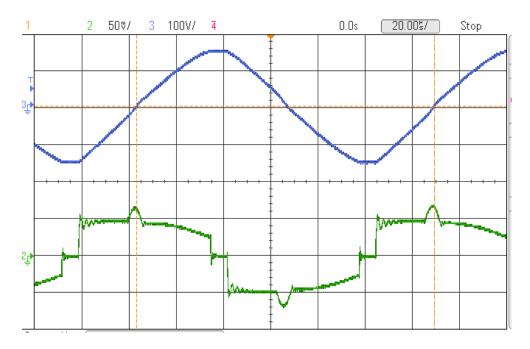

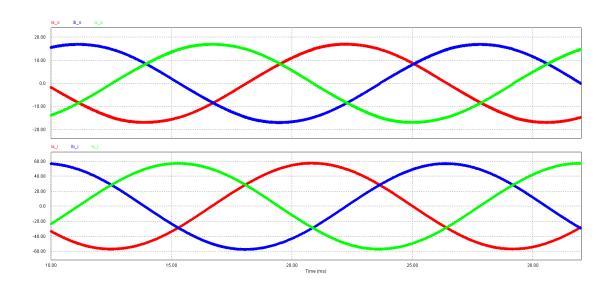

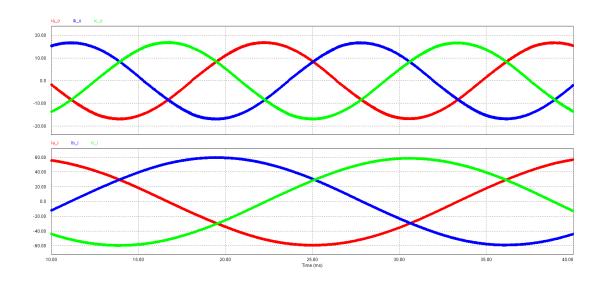

| Figure 149 | Output currents (top) and input currents (bottom) of the ac-ac SEPARC operating at full power                                  | 142 |

| Figure 150 | Link voltage of the ac-ac SEPARC operating at full power                                                                       | 143 |

| Figure 151 | Link current of the ac-ac SEPARC operating at full power                                                                       | 143 |

| Figure 152 | Output currents (top) input currents (bottom) of the ac-ac SEPARC operating at full power when the input frequency is 30 Hz    | 144 |

| Figure 153 | Current (top) and the gate command (bottom) of switch S0 in the ac-ac SEPARC                                                   | 144 |

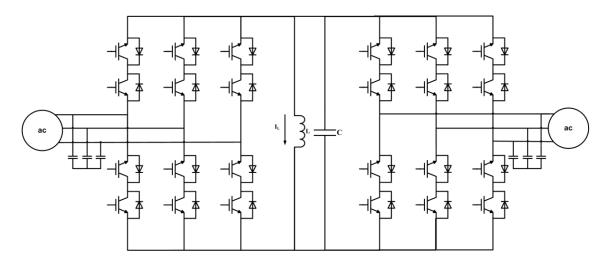

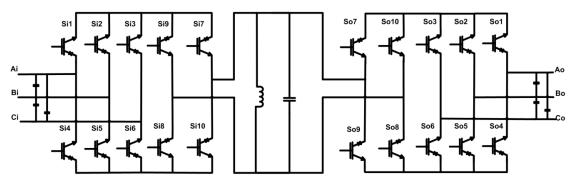

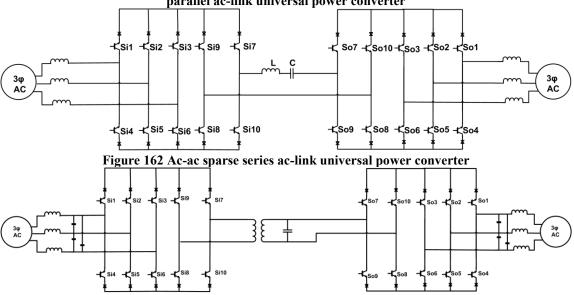

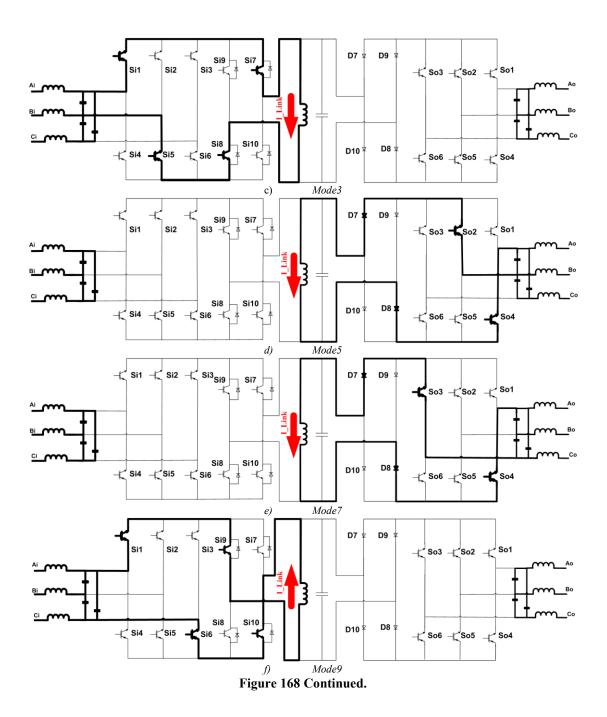

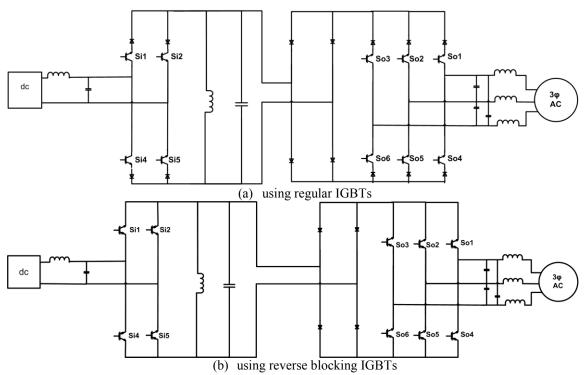

| Figure 154 | Sparse parallel ac-link universal power converter with conventional IGBTs                                                                                                                 | 148 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

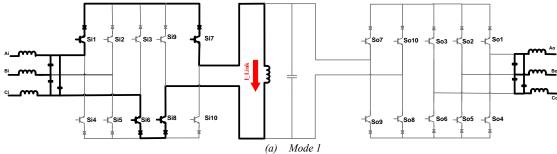

| Figure 155 | Sparse parallel ac-link universal power converter with reverse blocking IGBTs                                                                                                             | 148 |

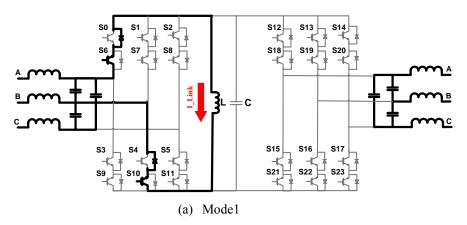

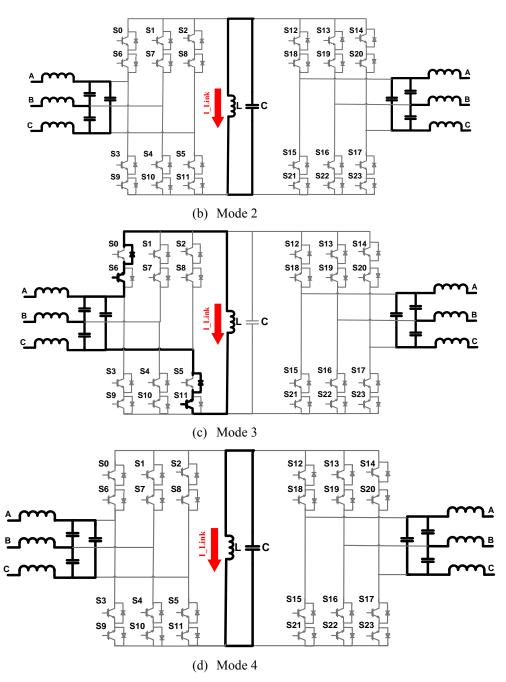

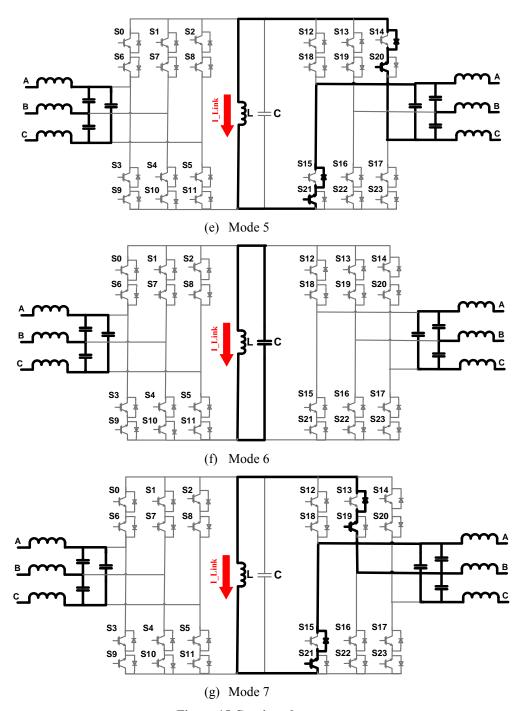

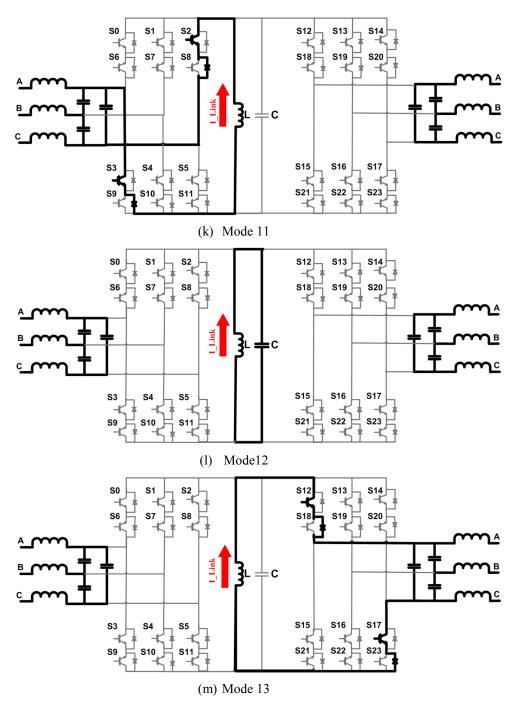

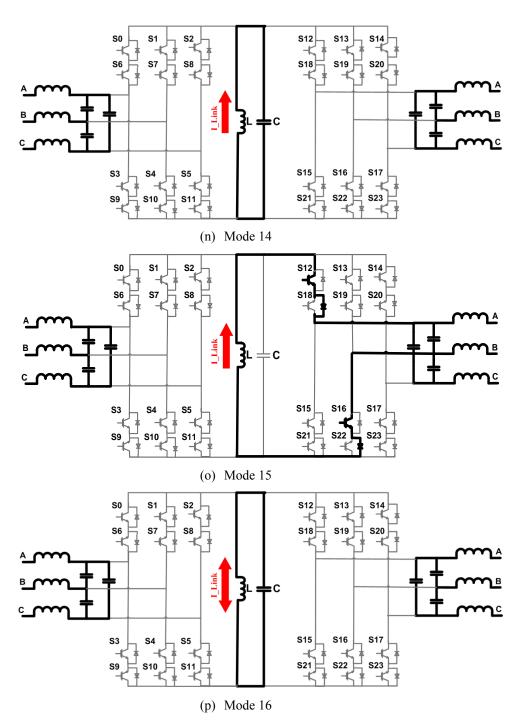

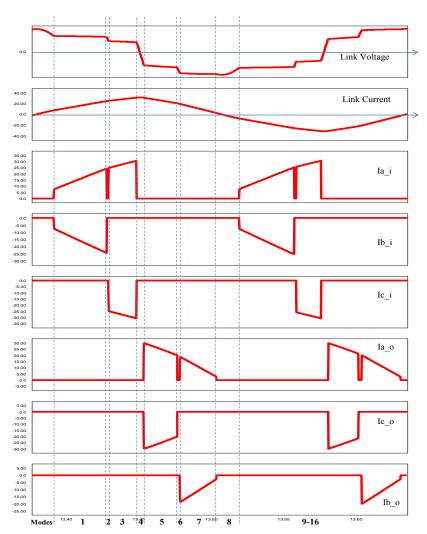

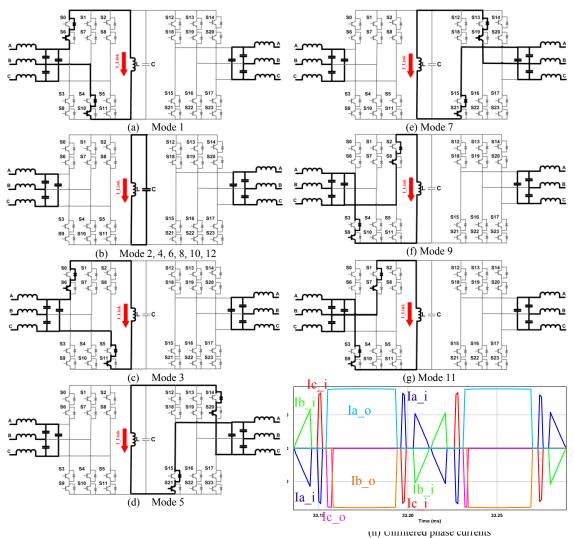

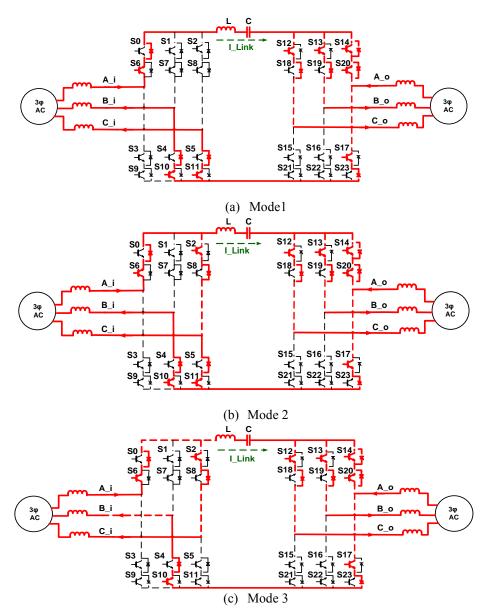

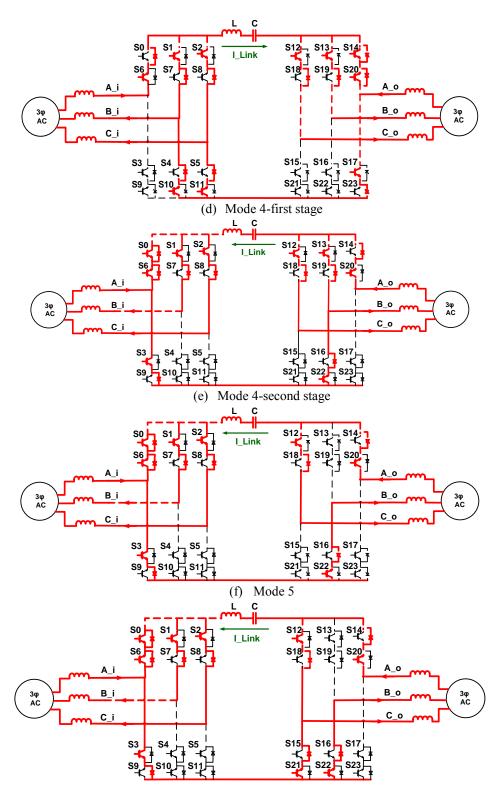

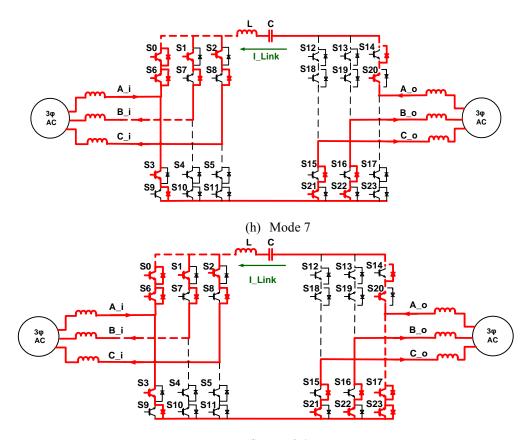

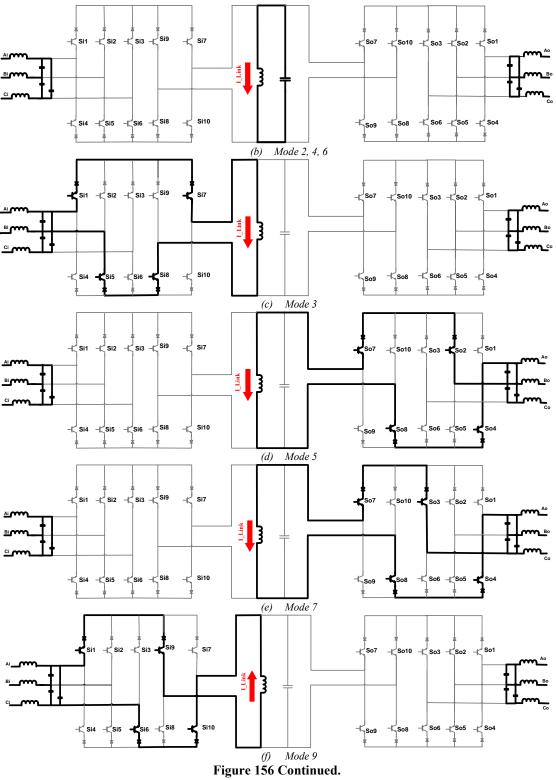

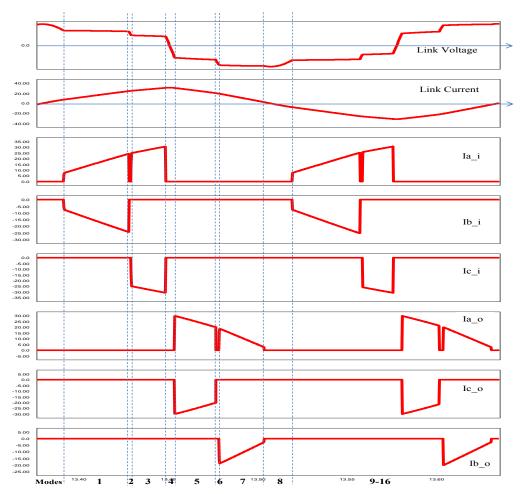

| Figure 156 | Behavior of the ac-ac sparse parallel ac-link universal converter during different modes of operation                                                                                     | 149 |

| Figure 157 | Voltage and current waveforms showing the behavior of the ac-ac sparse parallel ac-link universal converter during different modes of operation                                           | 151 |

| Figure 158 | Dc-ac sparse parallel ac-link universal converter with regular IGBTs                                                                                                                      | 151 |

| Figure 159 | Dc-ac sparse parallel ac-link universal converter with Reverse Blocking IGBTs                                                                                                             | 152 |

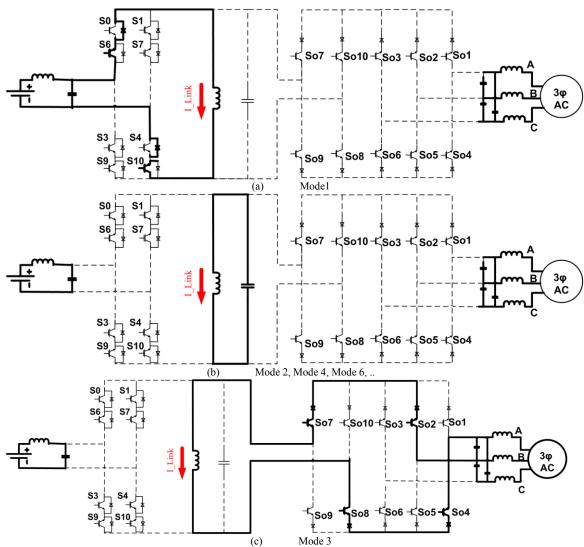

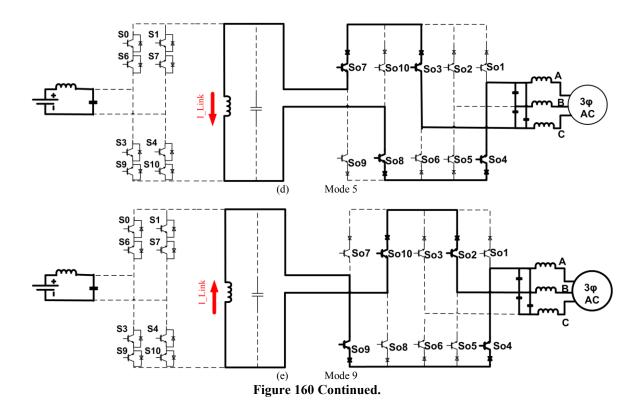

| Figure 160 | Behavior of the dc-ac sparse parallel ac-link universal power converter during different modes of operation                                                                               | 152 |

| Figure 161 | Link current, link voltage and unfiltered input and output currents in the dc-ac sparse parallel ac-link universal power converter                                                        | 154 |

| Figure 162 | Ac-ac sparse series ac-link universal power converter                                                                                                                                     | 154 |

| Figure 163 | Ac-ac sparse parallel ac-link universal converter with galvanic isolation                                                                                                                 | 154 |

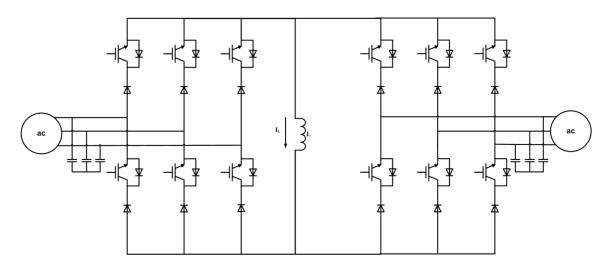

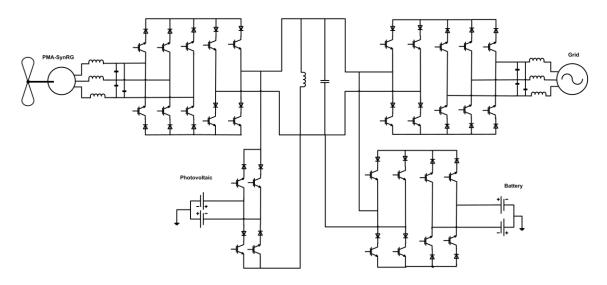

| Figure 164 | An example of the hybrid sparse parallel ac-link universal converter                                                                                                                      | 155 |

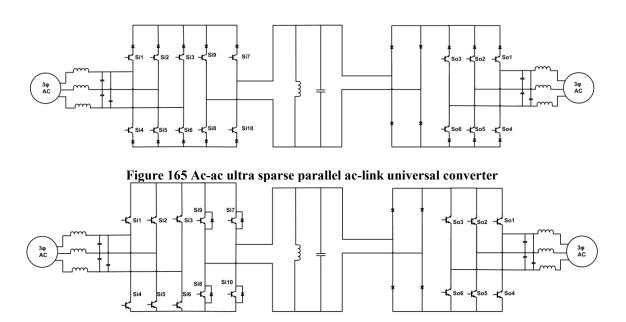

| Figure 165 | Ac-ac ultra sparse parallel ac-link universal converter                                                                                                                                   | 156 |

| Figure 166 | Ac-ac ultra-sparse parallel ac-link universal power converter with reverse-blocking IGBTs at both input and output switch bridges                                                         | 156 |

| Figure 167 | Ac-ac ultra-sparse ac-link universal power converter with reverse-<br>blocking IGBTs at input and output switch bridges and the input-side<br>intermediate cross-over switching circuits. | 156 |

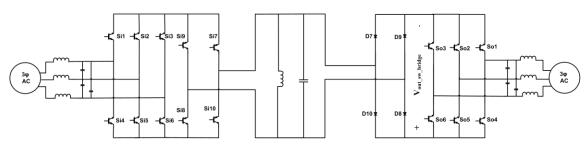

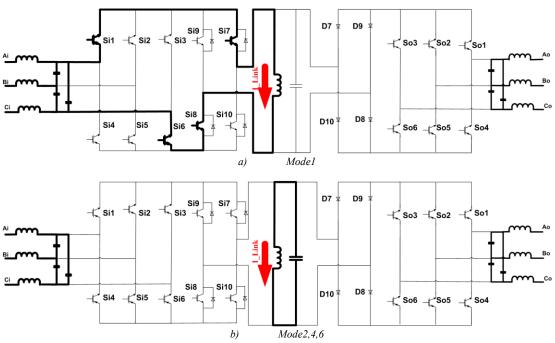

| Figure 168 | Behavior of the ultra-sparse parallel ac-link universal power converter during different modes of operation                                                                               | 157 |

| Figure 169 | Dc-ac ultra-sparse ac-link universal converter                                                                                                                                            | 159 |

| Figure 170 | Ac-ac parallel ac-link universal converter                                                                                                                                                | 163 |

| Figure 171 | Ac-ac parallel ac-link universal converter using reverse blocking IGBTs                                                                                                                   | 163 |

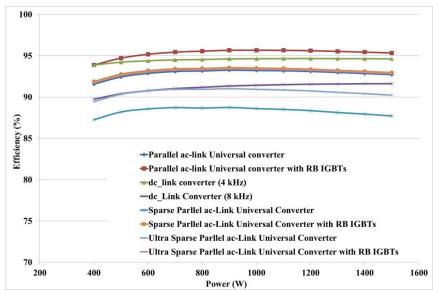

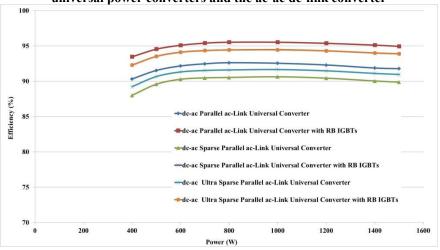

| Figure 172 | Efficiency of the ac-ac parallel, sparse parallel, and ultra-sparse parallel ac-link universal power converters and the ac-ac dc-link converter                                                                                                | 168  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 173 | Efficiency of the dc-ac parallel, sparse parallel, and ultra-sparse parallel ac-link universal power converters                                                                                                                                | 168  |

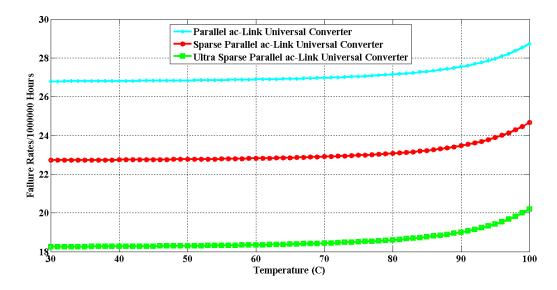

| Figure 174 | Failure rates of different ac-ac configurations                                                                                                                                                                                                | 169  |

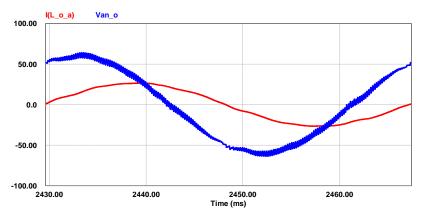

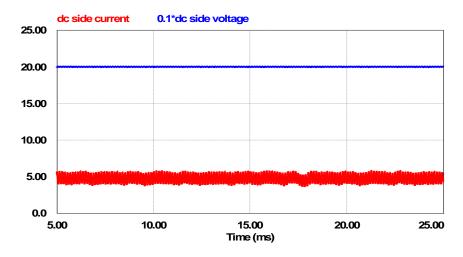

| Figure 175 | Dc-side current and scaled voltage in the dc-ac sparse parallel ac-link universal converter (simulation, dc-ac power flow)                                                                                                                     | 171  |

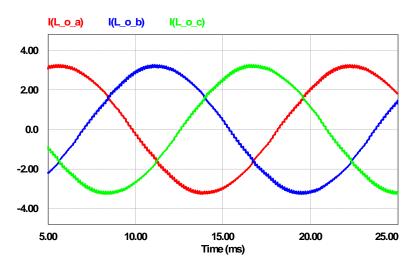

| Figure 176 | Ac-side currents in the dc-ac sparse parallel ac-link universal converter (simulation, dc-ac power flow)                                                                                                                                       | 172  |

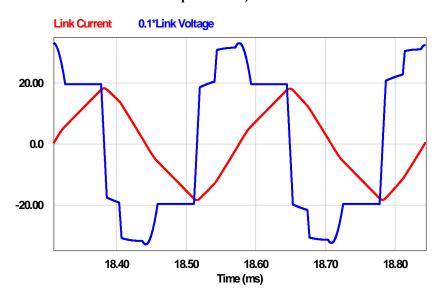

| Figure 177 | Link current and scaled voltage in the dc-ac sparse parallel ac-link universal converter (simulation, dc-ac power flow)                                                                                                                        | 172  |

| Figure 178 | Ac-side currents in the dc-ac sparse parallel ac-link universal converter (simulation, ac-dc power flow)                                                                                                                                       | 173  |

| Figure 179 | Dc-side current and scaled voltage in the dc-ac sparse parallel ac-link universal converter (simulation, ac-dc power flow)                                                                                                                     | 174  |

| Figure 180 | Link current and scaled voltage in the dc-ac sparse parallel ac-link universal converter (simulation, ac-dc power flow)                                                                                                                        | 174  |

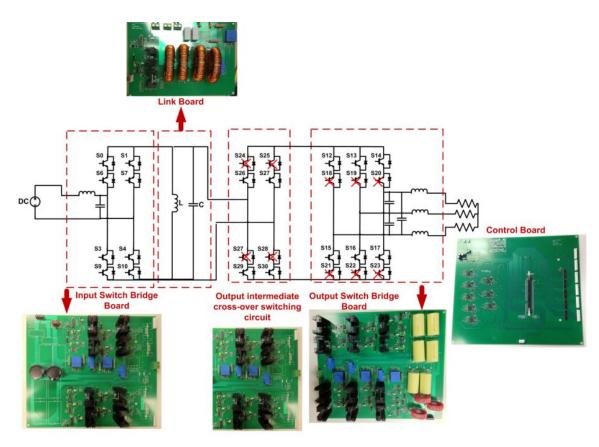

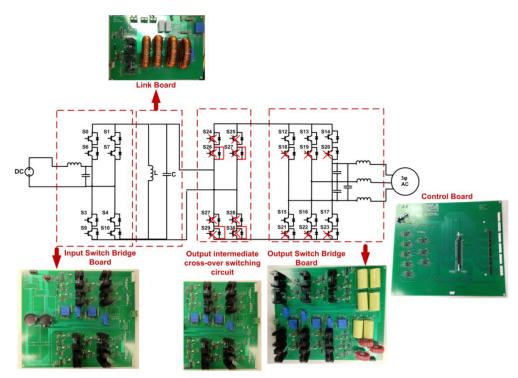

| Figure 181 | Different parts of the prototype for testing the dc-ac sparse parallel aclink universal converter                                                                                                                                              | 175  |

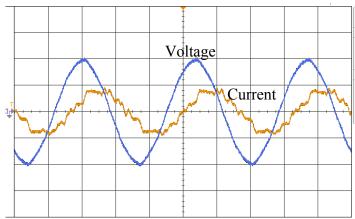

| Figure 182 | Dc-side current and voltage in the dc-ac sparse parallel ac-link universal converter (experiment, dc-ac power flow)                                                                                                                            | 175  |

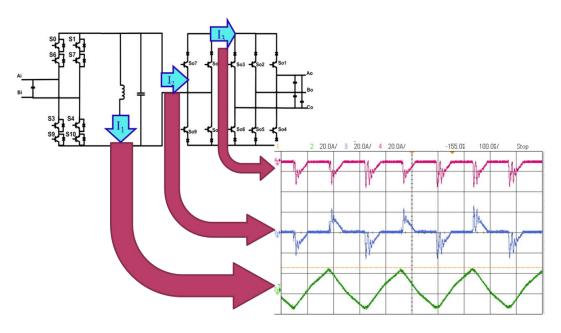

| Figure 183 | Ac-side currents in the dc-ac sparse parallel ac-link universal converter (experiment, dc-ac power flow)                                                                                                                                       | 176  |

| Figure 184 | Link current and voltage in the dc-ac sparse parallel ac-link universal converter (experiment, dc-ac power flow)                                                                                                                               | 176  |

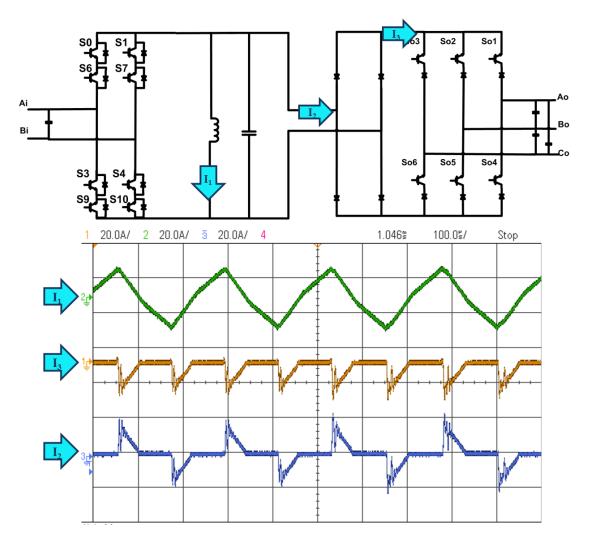

| Figure 185 | Current flowing the ac-side switch bridge (top), current flowing the intermediate cross-over switching circuit (middle), and the link current (bottom) in the dc-ac sparse parallel ac-link universal converter (experiment, dc-ac power flow) | .177 |

| Figure 186 | Link voltage and current in the dc-ac sparse parallel ac-link universal converter (experiment ac-dc power flow)                                                                                                                                | 177  |

| Figure | 187 | Dc-side current in the dc-ac sparse parallel ac-link universal converter (experiment, ac-dc power flow)                                                                                                               | 178 |

|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

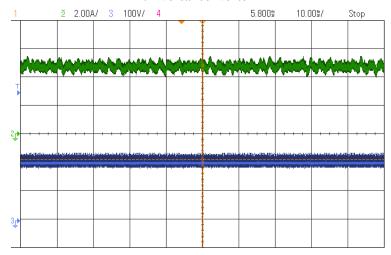

| Figure | 188 | Different parts of the prototype for testing the dc-ac ultra-sparse parallel ac-link universal converter                                                                                                              | 179 |

| Figure | 189 | Dc-side current and voltage in the dc-ac ultra-sparse parallel ac-link universal converter (experiment)                                                                                                               | 179 |

| Figure | 190 | Ac-side currents in the dc-ac ultra-sparse parallel ac-link universal converter (experiment)                                                                                                                          | 180 |

| Figure | 191 | Link current and voltage in the dc-ac ultra-sparse parallel ac-link universal converter (experiment)                                                                                                                  | 180 |

| Figure | 192 | The link current (top), the current flowing the ac-side switch bridge (middle), and current flowing the diode bridge (bottom) in the dc-ac sparse parallel ac-link universal converter (experiment, dc-ac power flow) | 181 |

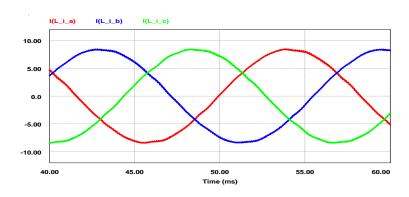

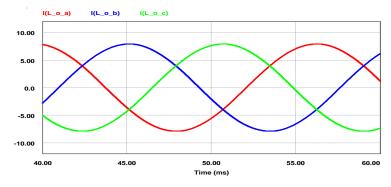

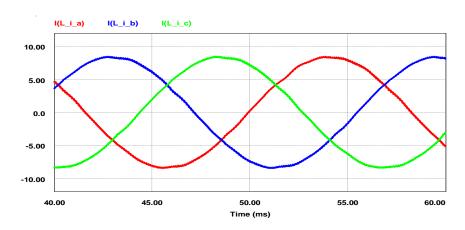

| Figure | 193 | Filtered input currents in the ac-ac parallel ac-link universal converter                                                                                                                                             | 183 |

| Figure | 194 | Filtered output currents in the ac-ac parallel ac-link universal converter                                                                                                                                            | 183 |

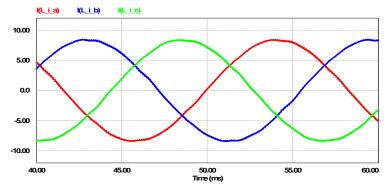

| Figure | 195 | Filtered input currents in the ac-ac sparse parallel ac-link universal converter.                                                                                                                                     | 183 |

| Figure | 196 | Filtered output currents in the ac-ac sparse parallel ac-link universal converter.                                                                                                                                    | 184 |

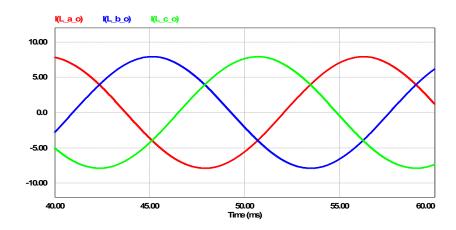

| Figure | 197 | Filtered input currents in the ac-ac ultra-sparse parallel ac-link universal converter.                                                                                                                               | 184 |

| Figure | 198 | Filtered output currents in the ac-ac ultra-sparse parallel ac-link universal converter                                                                                                                               | 184 |

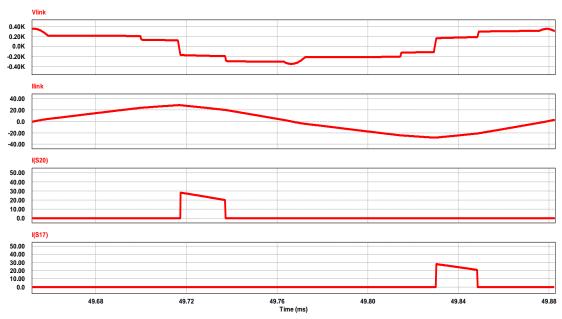

| Figure | 199 | Link voltage, link current, current of switch S20 and current of switch S18 in the ac-ac parallel ac-link universal power converter                                                                                   | 185 |

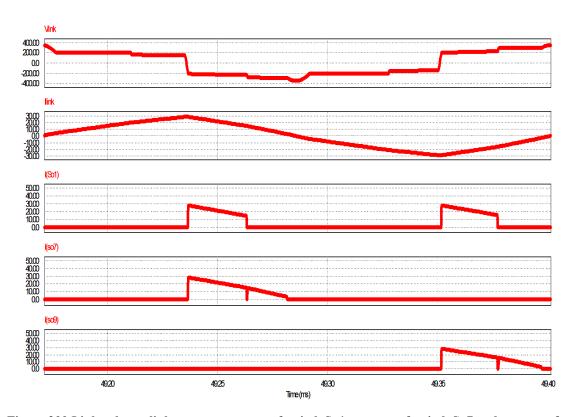

| Figure | 200 | Link voltage, link current, current of switch So1, current of switch So7 and current of switch So9 in the ac-ac sparse parallel ac-link universal power converter                                                     | 185 |

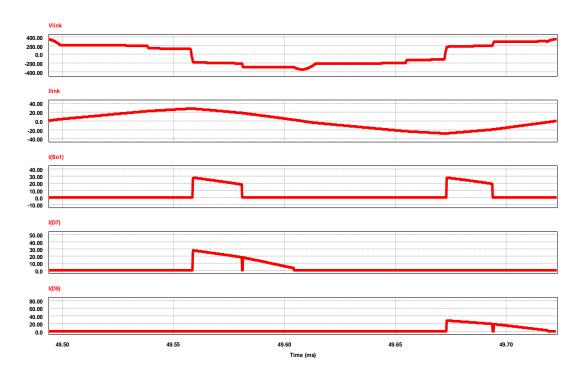

| Figure | 201 | Link voltage, link current, current of switch So1, current of diode D7 and current of diode D9 in the ac-ac ultra-Sparse parallel ac-link universal power converter                                                   | 186 |

## LIST OF TABLES

|                                                                                                                             | Page |

|-----------------------------------------------------------------------------------------------------------------------------|------|

| Table 1 Parameters of the designed, simulated and fabricated ac-ac parallel ac-link universal power converter               | ζ .  |

| Table 2 Comparison of the analysis, simulation and experiment                                                               | 74   |

| Table 3 Parameters of the simulated converter when the improved control method used                                         |      |

| Table 4 Parameters of the simulated and tested dc-ac parallel ac-link universal power converter                             | 77   |

| Table 5 The specifications of the hybrid parallel ac-link universal power converter                                         | 84   |

| Table 6 Summary of the analysis, simulation, and experimental evaluation of the hybrid parallel ac-link universal converter | 92   |

| Table 7 Parameters of the dc-single phase ac converter (first solution)                                                     | 94   |

| Table 8 Parameters of the simulated dc-single phase ac parallel ac-link universal converter (second solution)               | 98   |

| Table 9 Parameters of the 30 kW dc-ac parallel ac-link universal power converter used as a PV inverter                      | 102  |

| Table 10 Parameters of the 30 kW ac-ac parallel ac-link universal converter and the 20 hp induction machine                 |      |

| Table 11 Parameters of the designed and simulated dc-dc series ac-link universal converter                                  | 135  |

| Table 12 Parameters of the tested dc-dc series ac-link universal converter                                                  | 136  |

| Table 13 Parameters of the designed and simulated dc-ac series ac-link universal converter                                  | 138  |

| Table 14 Parameters of the designed and simulated ac-ac SEPARC                                                              | 142  |

| Table 15 Parameters of the ac-ac converters                                                                                 | 168  |

| Table 16 Parameters of the dc-ac converters                                                                                 | 168  |

| Table 17 Parameters of the simulated ac-ac parallel, sparse parallel, and ultra-sparse | ;   |

|----------------------------------------------------------------------------------------|-----|

| parallel ac-link universal converters                                                  | 182 |

#### 1. INTRODUCTION

In this dissertation a new class of power converters, named ac-link universal power converters, is introduced. These converters have several advantages over the other types of converters that make them an excellent candidate for use in renewable energy systems and for use in electric and hybrid-electric vehicles.

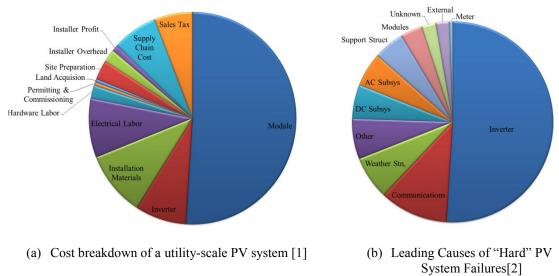

Concerns regarding fossil fuel prices, energy security, and climate change have led to a significant amount of research on renewable energy systems and the methods facilitating their higher penetration. Among these active research areas is power electronics. Power converters are essential components of many systems, including renewable energy systems. In a photovoltaic (PV) system, for instance, inverters account for almost 8% of the total upfront cost, and are responsible for more than 50% of the total failures. The total cost breakdown and the total failures by main components in a PV system are represented in Figure 1 [1, 2]. The high failure rate of the inverters apparently decreases their lifetime. The lifetime of the PV inverters is usually between 5 to 10 years; whereas the lifetime of the PV modules is about 25 years. Therefore, PV inverters need to be replaced two or three times within the lifetime of a PV system. Consequently, the actual cost of a PV system should include periodic inverter replacements [3].

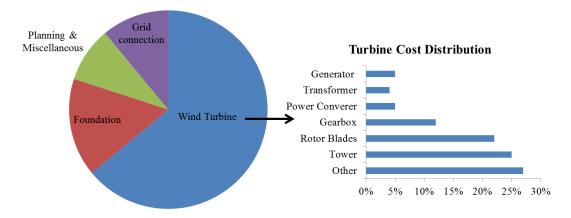

Similarly, in a wind power generation system, converters and transformers account for about 10% of the wind turbine cost; and, from the reliability point of view, power modules in general account for almost 37% of the overall down time. The total

cost breakdown of a wind power generation system and the percentage contribution of different components of a wind power generation system to overall downtime are shown in Figure 2 [4, 5].

Figure 1 Total cost breakdown and the total failures by main components in a PV system

The importance of power electronics in renewable energy systems can be concluded from the above statistics. The addition of power electronics usually adds cost to renewable energy systems, as well as contributing to reliability problems. In this part there will be a brief overview of the power converters employed in wind and PV power generation systems, two of the fastest growing renewable energy technologies. The main problems associated with converters that are employed in these systems are reviewed. Converter problems may hinder the higher penetration of renewable energy systems.

(a) Capital cost breakdown for a typical onshore wind power system and turbine [4]

(b) Percentage contribution to overall failure rate [5]

Figure 2 Total cost breakdown of a wind power generation system and the percentage contribution of different components of a wind power generation system to overall downtime

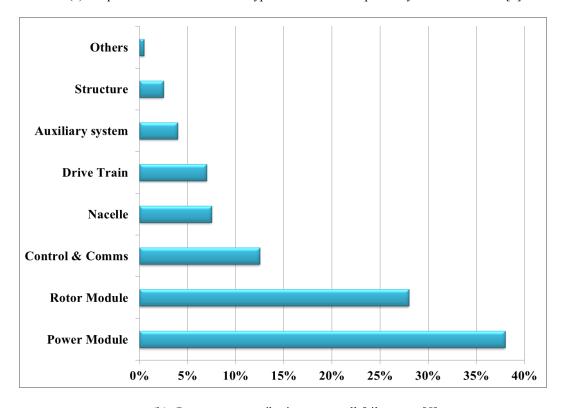

In past designs, a centralized converter-based PV system was the most commonly used type of PV system. As shown in Figure 3, in this system, PV modules

are connected to a three-phase voltage source inverter. The output of the inverter is connected to the grid through a three-phase low-frequency transformer, which steps up the voltage and provides galvanic isolation [6].

Low-frequency transformers are considered poor components mainly because of their large size, which can indirectly add costs to the system. This is because a large transformer requires a bulkier, and consequently, a more expensive foundation. To avoid the need for low-frequency transformers, multiple-stage converters are widely used in PV systems. The most common topology, which is represented in Figure 4, includes a voltage-source inverter and a dc-dc converter. Commonly, the dc-dc converter contains a high-frequency transformer. Despite offering a high boosting capability and galvanic isolation, this converter consists of multiple power processing stages that lower the efficiency of the overall system. Moreover, electrolytic capacitors are required for the dc link. Electrolytic capacitors, which are very sensitive to temperature, might cause severe reliability problems in power converters and an increase of even 10 °C can halve their lifetime. Therefore, PV inverters containing electrolytic capacitors are not expected to provide the same lifetime as the PV modules. Consequently, the actual cost of the PV system involves periodic replacement of the inverter, which increases the levelized cost of energy extracted from the PV system [3, 6-9].

Different configurations of variable speed wind turbine systems are illustrated in Figure 5. As seen in this figure, the bulky low-frequency transformer is an inseparable part of these configurations.

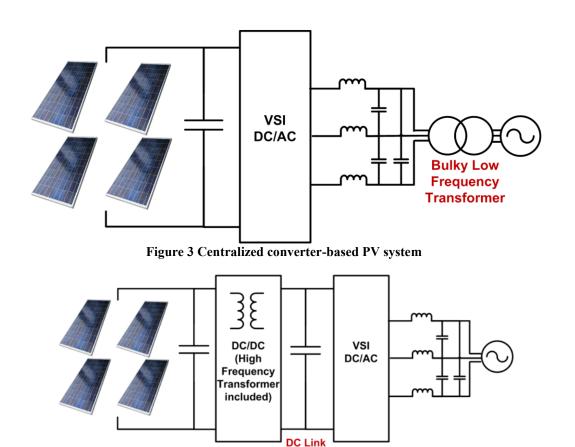

Traditionally, dc-link converters, which are formed by a rectifier and an inverter, are employed in wind power generation systems. In the simplest case, the rectifier can be formed by a diode bridge. To improve the currents, the dc-link converter can be implemented by a pulse-width modulated (PWM) rectifier and a PWM inverter. Regardless of the inverter and the rectifier topologies, a dc electrolytic capacitor, which deteriorates the circuit reliability and lifetime, is an integral part of the dc-link converters. High switching losses and high device stresses are other important limitations of this type of converter [10, 11].

Figure 4 Multiple-stage conversion systems used in PV applications

Figure 5 Wind turbine configurations in variable speed constant frequency systems: (a) indirect drive using doubly-fed induction generator, (b) indirect drive using squirrel-cage induction generator, (c) indirect drive using wound-field synchronous generator, (d) direct drive using permanent magnet synchronous generator, (e) direct drive using wound-field synchronous generator [10].

Considering the aforementioned problems, for the long-term success of renewable energy sector it is essential to support the design of alternative power converters with higher reliability and lower cost.

As an alternative to the currently available converters, ac-link universal power converters were proposed. This category of power converters is described as "universal" because their inputs and outputs can be dc, ac, single-phase, or multi-phase. Therefore, they can be employed in a variety of applications including, but not limited to, PV power generation, battery-utility interfaces, battery chargers, and wind power generation.

In the ac-link universal power converters, the link current and voltage are both alternating and they may have a high frequency; therefore, there is no need for dc electrolytic capacitors at the link. Considering all the problems associated with the electrolytic capacitors, such as temperature dependency, this converter is an excellent alternative to dc-link converters. Moreover, in these converters galvanic isolation can be provided by adding a single-phase high-frequency transformer to the link. Therefore, no low-frequency transformers are employed in ac-link universal power converters. Another merit of these converters is soft switching of the switches that leads to negligible switching losses. Moreover, due to soft switching of the switches, the current and voltage stress over the switches is minimized and there is no need for snubbers in these converters.

The parallel ac-link universal power converter, which was first introduced in [12], is currently available in the market. The dc to three-phase ac parallel ac-link universal power converter has recently been included in the California Energy Commission (CEC) list of approved PV inverters. This converter is an extension of the dc-dc buck-boost converter. Of course, several modifications have been applied to provide the alternating link current and soft switching. In this converter, switches are all

turned on at zero voltage and their turn-off is capacitance buffered. Some of the applications of this converter have been studied in [13-25]. In section 2 the principles of the operation of this converter along with its design and detailed analysis are presented. With the analysis introduced, the performance of the converter can be predicted at any power level. Moreover, the hybrid parallel ac-link universal power converter will be proposed in section 2.

Section 3 of this dissertation proposes the series ac-link universal power converter. Similar to the parallel ac-link universal power converter, the series ac-link universal power converter has several advantages over the other types of converters. In this converter the switches are turned off at zero current and their turn on is soft [26, 27]. The major advantage of this converter over the parallel ac-link universal power converter is that due to the zero current turn off of the switches, silicon controlled rectifiers (SCRs) may be used as well. SCRs have several benefits over the other types of switches: They are available at both high current and high voltage ratings; They have low losses; and, They are inexpensive and reliable. Therefore, they are very popular in high power applications and reliability demanding applications. The series ac-link universal power converter is the dual of a parallel ac-link universal power converter. Therefore, it is in essence an extension of the dc-dc Cuk converter and several modifications have been applied to provide the alternating link voltage and soft switching.

Despite having numerous advantages, both the series and parallel ac-link universal power converters have more switches compared to most of the other

converters. In order to simplify the design and to further increase reliability, the sparse and the ultra-sparse ac-link universal power converters are proposed in section 4 of this dissertation. These converters have all of the advantages of the original configurations, but they use fewer switches [28, 29]. Two patents on the novel topologies presented in this dissertation have been filed [30, 31].

Finally, the main points of this dissertation will be summarized in section 5.

## 2. PARALLEL AC-LINK UNIVERSAL POWER CONVERTER\*

#### 2.1. Introduction

This section introduces the parallel ac-link universal power converters. This converter is an extension of the dc-dc buck-boost converter. By adding the complementary switches and by modifying the switching scheme, the link inductor, which is the main energy storage element in this converter, can have alternating current instead of the direct current. This approach improves the performance of the converter and significantly increases the utilization of the link inductor.

The following section presents a summary of the required steps to form a three-phase ac-ac ac-link buck-boost converter from the conventional dc-dc buck-boost converter. It will be shown that placing a small capacitor in parallel with the link inductor enables the converter to benefit from soft switching, which significantly increases its efficiency. The principles of operation of this soft switching converter, which is called the parallel ac-link universal power converter, are studied in section 2.3.

<sup>\*</sup> Part of this section is reprinted with permission from:

<sup>1. &</sup>quot;High Frequency ac-Link PV Inverter" by M. Amirabadi, A. alakrishnan, H. Toliyat, and W. Alexander, IEEE Transactions on Industrial Electronics, vol. 61, pp. 281-291, 2014. Copyright 2013 by IEEE.

<sup>2. &</sup>quot;Partial resonant AC link converter: A highly reliable variable frequency drive" by M. Amirabadi, H. A. Toliyat, and W. C. Alexander, in Proc. IEEE Industrial Electronics Society Annual Conference (IECON), 2012, pp. 1946-1951. Copyright 2014 by IEEE.

<sup>3. &</sup>quot;A Multi-Port ac Link PV Inverter with Reduced Size and Weight for Stand-alone Application" by M. Amirabadi, H. A. Toliyat, and W. C. Alexander, IEEE Transactions on Industry Applications, 2013, in press. Copyright 2013 by IEEE.

<sup>4. &</sup>quot;Battery-utility interface using soft switched ac link supporting low voltage ride through" by M. Amirabadi, H. A. Toliyat, and W. C. Alexander, in Proc. IEEE Energy Conversion Congress and Exposition Conference (ECCE), 2009, pp. 2606-2613. Copyright 2009 by IEEE.

<sup>5. &</sup>quot;Chapter 5: AC-Link Universal Power Converters: A New Class of Power Converters for Renewable Energy and Transportation" by H. A. Toliyat and M. Amirabadi in "Power Electronics for Renewable Energy Systems, Transportation and Industrial Applications" edited by Haitham Abu-Rub, Marius Malinowski, and Kamal Al-Haddad, 2013, John Wiley & Sons, Ltd., West Sussex, UK. Copyright 2013 by John Wiley & Sons, Ltd.

The design procedures and the analysis of this converter are presented in sections 2.4 and 2.5, respectively. In section 2.6, the low voltage ride-through feature of this converter will be studied and it will be shown that the converter is capable of injecting reactive power in case of a load voltage drop. In section 2.7 it will be shown that the control scheme studied in section 2.3 has certain constraints on the load power factor for providing soft switching. An improved control scheme, which results in soft switching of the switches regardless of the load power factor and the input and output voltage levels, will be proposed in this section. The hybrid parallel ac-link universal power converter is introduced in section 2.8. Some of the applications of the parallel ac-link universal power converter along with the simulation and experimental results are presented in section 2.9, and finally, section 2.10 summarizes this section.

## 2.2. Evolution of the Parallel AC-Link Universal Power Converter and the Background

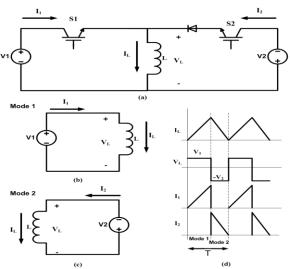

We will start from the most basic configuration; a dc-dc buck-boost converter, as shown in Figure 6. In a buck-boost converter, the link inductor is first charged from the input and then discharged into the output. Clearly, this circuit has two modes of operation: mode 1, charging the link, and mode 2, discharging the link. During mode 1, switch S1 conducts and during mode 2, switch S2 conducts. It is assumed that this buck-boost converter operates at the boundary of continuous and discontinuous conduction modes. Switch S2 must block reverse voltage. Hence, in Figure 6, a diode is placed in series with this insulated-gate bipolar transistor (IGBT). Voltages V1 and V2 are both assumed to be positive. In a conventional buck-boost converter, switch S2 is usually

removed and the diode conducts during mode 2. This converter can also be demonstrated, as represented in Figure 7. Although the bottom diode, switch S3 and switch S4 are unnecessary for this case, they are required for the subsequent steps.

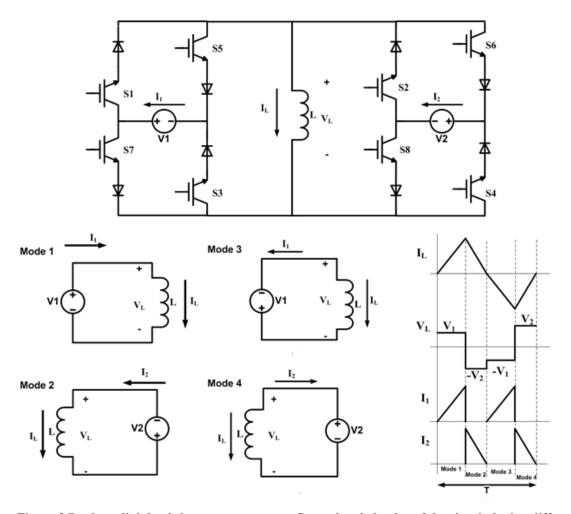

In order to have an alternating inductor current, or in other words, to allow the link inductor to charge and discharge in both positive and negative directions, four other switches should be added, as depicted in Figure 8. The link cycle can then be divided into two half cycles, with the positive link current during the first half cycle and the negative link current during the second half cycle. This configuration results in an alternating link current. This converter has four modes of operation: mode 1, charging the link with positive current; mode 2, discharging the link with positive current; mode 3, charging the link with negative current; and mode 4, discharging the link with negative current. Switches S1, S2, S3, and S4 conduct when the inductor current is positive. Whereas, switches S5, S6, S7, and S8 conduct in the case of a negative link current.

Figure 6 Dc-dc buck-boost converter: (a) configuration, (b) energizing mode (mode 1), (c) deenergizing mode (mode 2), (d) voltage and current waveforms

Figure 7 An alternative representation of the dc-dc buck-boost converter

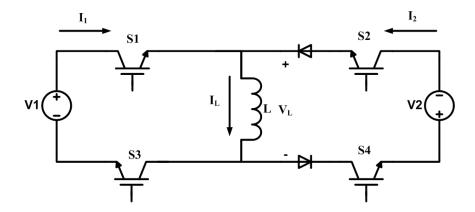

If bidirectional power flow is required, then the number of switches must be doubled, as shown in Figure 9. Switches S1–S8 transfer the power from V1 to V2 and switches S9–S16 are responsible for transferring the power from V2 to V1. The converter shown in Figure 9 is a bidirectional dc-dc ac-link buck-boost converter.

Adding more legs to each side of this converter yields multi-phase bidirectional ac-link converters, such as the dc to multi-phase ac, multi-phase ac to dc, and multi-phase ac to multi-phase ac configurations. The dc to three-phase ac, three-phase ac to dc, and three-phase ac to ac configurations are shown in Figure 10.

The principles of operation of the multi-phase converter are similar to those of the dc-dc converter; however, the main challenge is to determine the contribution of each phase of the multi-phase system to the charging or discharging of the link. Let us consider a three-phase inverter, as shown in Figure 10 (a). As the input of the inverter is dc, the charging of the link in this case is similar to that of the dc-dc converter. However, during the discharging mode, there is one link to be discharged and two phase-pairs to be charged from the link. In order to have lower Total Harmonic Distortion (THD) on the