## ENERGY AND RELIABILITY IN FUTURE NOC INTERCONNECTED CMPS

## A Dissertation

by

## HYUNGJUN KIM

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Chair of Committee, Paul V. Gratz Committee Members, Eun Jung Kim

Henry Pfister Jiang Hu

Daniel A. Jiménez

Head of Department, Chanan Singh

August 2013

Major Subject: Computer Engineering

Copyright 2013 Hyungjun Kim

#### ABSTRACT

In this dissertation, I explore energy and reliability in future NoC (Network-on-Chip) interconnected CMPs(chip multiprocessors) as they have become a first-order constraint in future CMP design.

In the first part, we target the root cause of network energy consumption through techniques that reduce link and router-level *switching activity*. We specifically focus on memory subsystem traffic, as it comprises the bulk of NoC load in a CMP. By transmitting only the flits that contain words that we predicted would be useful using a novel spatial locality predictor, our scheme seeks to reduce network activity. We aim to further lower NoC energy consumption through microarchitectural mechanisms that inhibit datapath switching activity caused by unused words in individual flits. Using simulation-based performance studies and detailed energy models based on synthesized router designs and different link wire types, we show that (a) the prediction mechanism achieves very high accuracy, with an average rate of false-unused prediction of just 2.5%; (b) the combined NoC energy savings enabled by the predictor and microarchitectural support are 36% on average and up to 57% in the best case; and (c) there is no system performance penalty as a result of this technique.

In the second part, we present a method for dynamic voltage/frequency scaling of networks-on-chip and last level caches in CMP designs, where the shared resources form a single voltage/frequency domain. We develop a new technique for monitoring and control and validate it by running PARSEC benchmarks through full system simulations. These techniques reduce energy-delay product by 46% compared to a state-of-the-art prior work.

In the third part, we develop critical path models for HCI- and NBTI-induced

wear assuming stress caused under realistic workload conditions, and apply them onto the interconnect microarchitecture. A key finding from this modeling is that, counter to prevailing wisdom, wearout in the CMP on-chip interconnect is correlated with a lack of load observed in the NoC routers, rather than high load. We then develop a novel wearout-decelerating scheme in which routers under low load have their wearout-sensitive components exercised without significantly impacting the router's cycle time, pipeline depth, area or power consumption. We subsequently show that the proposed design yields a  $13.8\sim65\times$  increase in CMP lifetime.

# DEDICATION

To my wife, Minyoung, and my loving parents

#### ACKNOWLEDGEMENTS

I would like to acknowledge many people without whom this work would not have been possible. First and foremost I would like to thank my advisor, Paul V. Gratz, for his patient support and endless guidance. He always waited for me to make progress by myself while teaching me invaluable knowledge and skills. He has been also patient with my communication skills. He always tried to understand what I was trying to say, and never gave up on any of my trivial idea. I was fortunate to have him as my advisor, and in fact, now, he is my role model as a researcher and as a co-worker.

I was also lucky to meet Eun Jung Kim in my first year in Texas A&M University. She actually was the one who introduced the research field that I ended up focusing on. She taught me the fundamental knowledge of interconnection networks and encouraged me to study in this area. Without her, this work wouldn't exist.

I would like to thank my other committee members, Daniel Jiménez, Jiang Hu, and Henry Pfister for their helpful feedback on my research. Special thanks to Prof. Jiménez for the idea of the spatial locality prediction which became a significant part of this work. I also really enjoyed the work with Prof. Hu and his students, Xi Chen and Zheng Xu, which is essential in this work, as well.

I would also like to thank co-authors, Boris Grot, Pritha Ghoshal, David Kadjo, Vassos Soteriou, and Arseniy Vitkovskiy. Also, I would like to thank the folks from Intel including Ümit Ogras, Raid Ayoub and Michael Kishinevsky who happened to be my mentors while I was interning at Intel. With their feedback and advice, I could expand the area of my research interests taking myself out of my comfort zone, little by little.

Many thanks to the members of CAMSIN group, a research group full of brilliant students and in which Prof. Gratz has fostered an excellent collaborative environment. Special thanks to Ehsan Fatehi, Mark Browning and Jinchun Kim for their dedicated effort, and time they took to setup the infrastructure of experiments for other CAMSIN members.

Thanks to Prof. Eun Jung Kim, again, I was also fortunate to join her group for awhile, and meet Yuho Jin and Lei Wang with whom I wrote my very first research paper. Special thanks to Yuho for teaching me many useful tips and skills required in this area of study, which became the foundation of what I have now in my tool box. I can't forget the days and nights with Lei struggling with our first paper, and the feeling of achievement at the moment it got accepted to be published.

On a more personal note, first, I would like to thank two office mates, Yongoh Lee and Yongtae Kim. They have been the first people with whom I could discuss concerns, and with whom I could share any good and bad news. In fact, they are very supportive not only mentally but also of my research. Also, KATC, Korean Aggies Tennis Club, has been inevitable in my life in College Station. It contributed many memorable moments and stress relief to my five years in College Station.

Finally and most importantly, I would like to thank my family. I don't know how to thank my parents enough for the sacrifices they have made for me. Without your love and support, this journey would not have been possible. I would also like to thank the love of my life, Minyoung. Minyoung's constant love and sense of humor make every day special. I am always excited to be with you for the rest of our lives.

## TABLE OF CONTENTS

|    |              |                                         |                                                   | Page  |

|----|--------------|-----------------------------------------|---------------------------------------------------|-------|

| AI | BSTR         | ACT                                     |                                                   | . ii  |

| DI | EDIC         | ATION                                   |                                                   | . iv  |

| Α( | CKNC         | )WLET                                   | OGEMENTS                                          | . v   |

|    | J111 ( C     | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                                                   | •     |

| TA | ABLE         | OF CO                                   | ONTENTS                                           | . vii |

| LI | ST O         | F FIGU                                  | JRES                                              | . ix  |

| LI | ST O         | F TAB                                   | LES                                               | . xii |

| 1. | INT          | RODU                                    | CTION                                             | . 1   |

|    | 1.1          | Thoris                                  | Statement                                         | . 2   |

|    | $1.1 \\ 1.2$ | Disser                                  | tation Organization                               | . 3   |

| _  |              |                                         |                                                   |       |

| 2. | ENE          | RGY E                                   | EFFICIENCY THROUGH SPATIAL LOCALITY PREDICTION    | )N 4  |

|    | 2.1          | Introd                                  | uction                                            | . 4   |

|    |              | 2.1.1                                   | Motivation                                        | . 4   |

|    |              | 2.1.2                                   | CMP Interconnect                                  | . 5   |

|    |              | 2.1.3                                   | Proposed Technique                                |       |

|    | 2.2          |                                         | round and Related Work                            |       |

|    |              | 2.2.1                                   | Dynamic Power Consumption                         |       |

|    |              | 2.2.2                                   | NoC Power and Energy                              |       |

|    |              | 2.2.3                                   | Spatial Locality and Cache Block Utilization      |       |

|    | 2.3          | Descri                                  |                                                   |       |

|    |              | 2.3.1                                   | Spatial Locality Prediction                       |       |

|    | 2.4          | 2.3.2                                   | Packet Composition                                |       |

|    | 2.4          |                                         |                                                   |       |

|    |              | 2.4.1                                   | Baseline Architecture and Physical Implementation |       |

|    |              | 2.4.2                                   | Simulation Methodology                            | . 27  |

|    | 0.5          | 2.4.3                                   | Energy Consumption                                |       |

|    | 2.5          |                                         |                                                   |       |

|    |              | 2.5.1                                   | Performance                                       |       |

|    |              | 2.5.2 $2.5.3$                           | Predictor Tuning                                  |       |

|    | 26           |                                         | Case Study: Comparison with Smaller Lines         | . 46  |

|    | $\angle .0$  | - СОПСП                                 | 4510115                                           | . 40  |

| 3. | ENE        | ERGY EFFICIENCY THROUGH DVFS                       | 49       |

|----|------------|----------------------------------------------------|----------|

|    | 3.1<br>3.2 | Introduction                                       | 49<br>51 |

|    |            | 3.2.1 Problem Description                          | 51       |

|    |            | 3.2.2 Previous Work                                | 52       |

|    | 3.3        | Throughput-Driven DVFS                             | 54       |

|    | 3.4        | Evaluations                                        | 57       |

|    |            | 3.4.1 Experiment Setup                             | 57       |

|    |            | 3.4.2 Experiment Results                           | 57       |

|    | 3.5        | Conclusions                                        | 60       |

| 4. | WE         | AR-OUT AND LIFETIME IN FUTURE CHIP MULTIPROCESSORS | 61       |

|    | 4.1        | Introduction                                       | 61       |

|    | 4.2        | Background                                         | 65       |

|    |            | 4.2.1 Failure Mechanisms                           | 66       |

|    |            | 4.2.2 Router Microarchitecture                     | 72       |

|    | 4.3        | Router Wear Characterization                       | 75       |

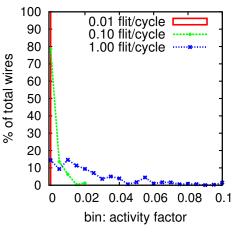

|    |            | 4.3.1 Activity Factor                              | 75       |

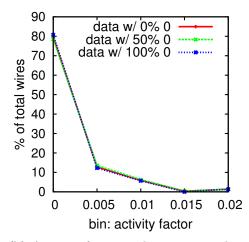

|    |            | 4.3.2 Duty Cycle                                   | 77       |

|    |            | 4.3.3 Workload Characterization                    | 78       |

|    | 4.4        | Path Delay                                         | 82       |

|    | 4.5        | Aging-Preventing Router Microarchitecture          | 84       |

|    |            | 4.5.1 Exercise Logic                               | 84       |

|    |            | 4.5.2 Other Approaches                             | 87       |

|    |            | 4.5.3 NBTI Hardening                               | 88       |

|    | 4.6        | Evaluation                                         | 89       |

|    |            | 4.6.1 Experiment Setup                             | 89       |

|    |            | 4.6.2 Experiment Results                           | 90       |

|    | 4.7        | Related Work                                       | 99       |

|    | 4.8        | Conclusions                                        | 102      |

| 5. | CON        | NCLUSIONS                                          | 103      |

| DI | סקקי       | FNCES                                              | 105      |

## LIST OF FIGURES

| FIGUR | E                                                                                                  | Page |

|-------|----------------------------------------------------------------------------------------------------|------|

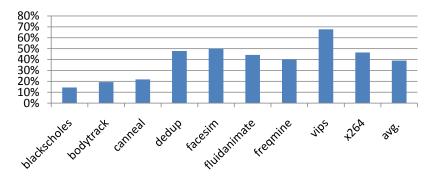

| 2.1   | Percentage of 64-byte block, cache words utilized per block in the PARSEC multithreaded benchmarks | 5    |

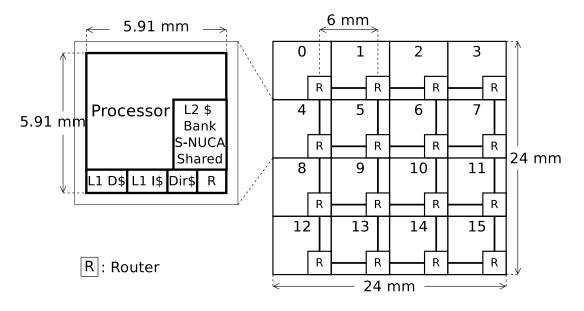

| 2.2   | General CMP architecture                                                                           | 11   |

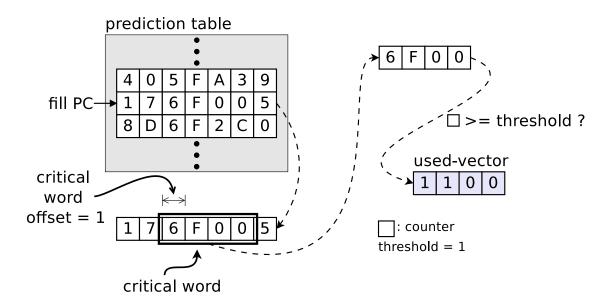

| 2.3   | Prediction example for 4 words/block cache model                                                   | 12   |

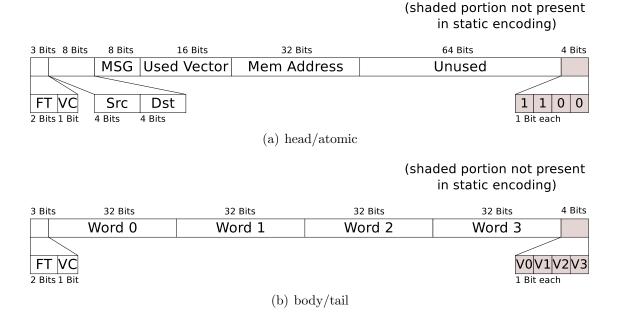

| 2.4   | Flit format for static and dynamic encoding. (Shaded portion not present in static encoding.)      | 18   |

| 2.5   | Read request and corresponding response packets (VC is not shown in this figure.)                  | 20   |

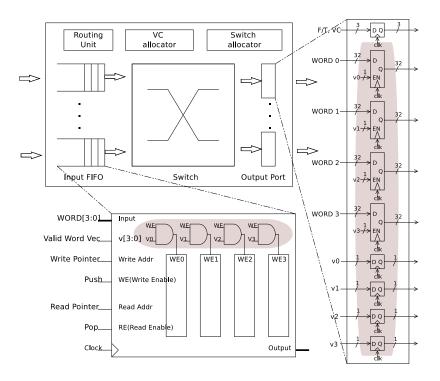

| 2.6   | Dynamic packet compositioning router. (Shaded portion not present in baseline router.)             | 22   |

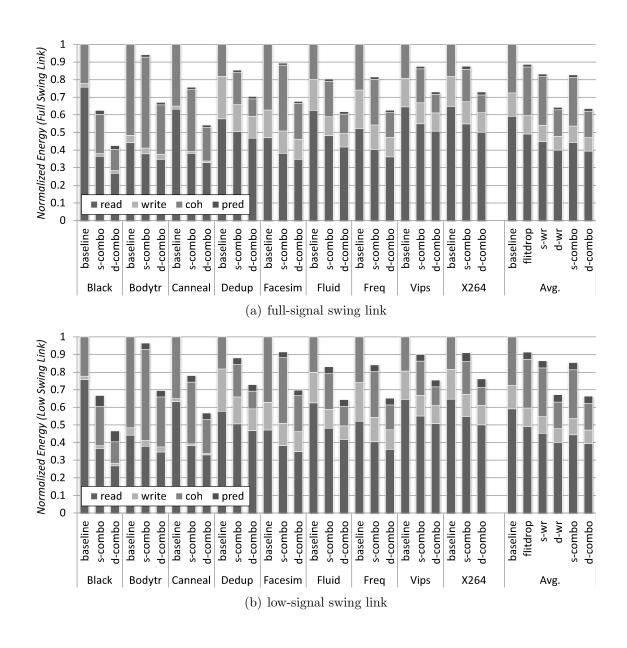

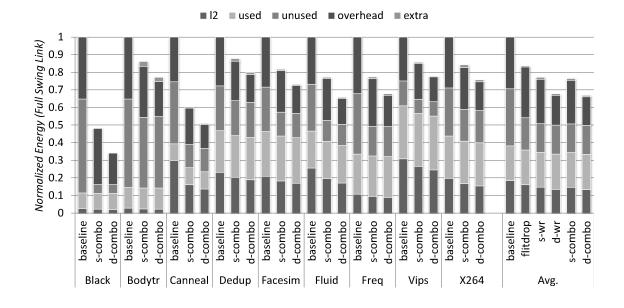

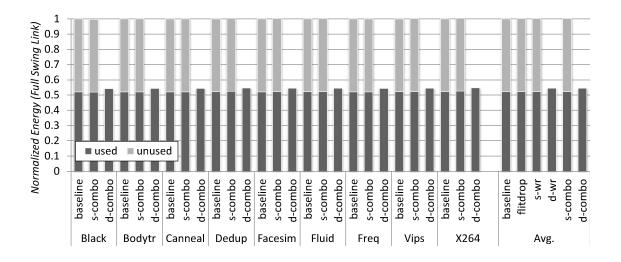

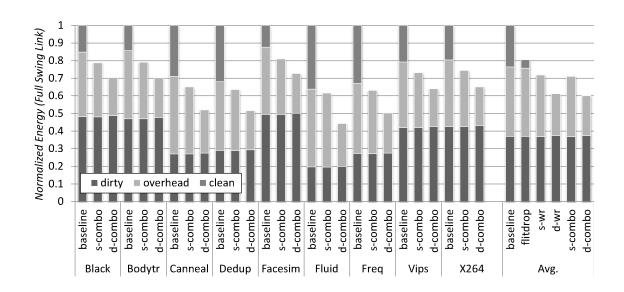

| 2.7   | Dynamic energy breakdown                                                                           | 28   |

| 2.8   | Dynamic energy breakdown for reads                                                                 | 30   |

| 2.9   | Dynamic energy breakdown for coherent packets                                                      | 32   |

| 2.10  | Dynamic energy breakdown for writes                                                                | 34   |

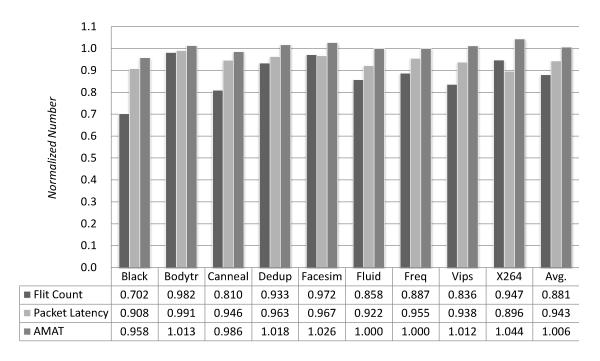

| 2.11  | Flit count, packet latency and AMAT normalized against baseline                                    | 36   |

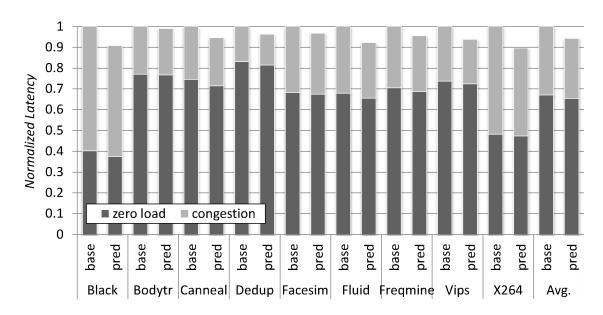

| 2.12  | Packet latency breakdown                                                                           | 37   |

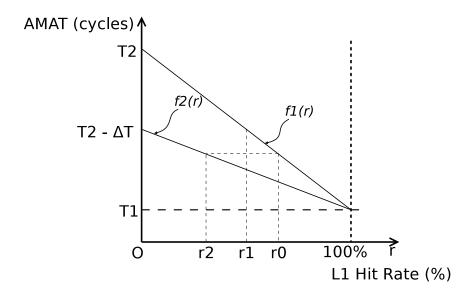

| 2.13  | AMAT graph                                                                                         | 38   |

| 2.14  | Overall system performance                                                                         | 41   |

| 2.15  | Breakdown of predictions outcomes                                                                  | 42   |

| 2.16  | Normalized energy and AMAT for different threshold values                                          | 45   |

| 2.17  | Comparison to a smaller cache line                                                                 | 47   |

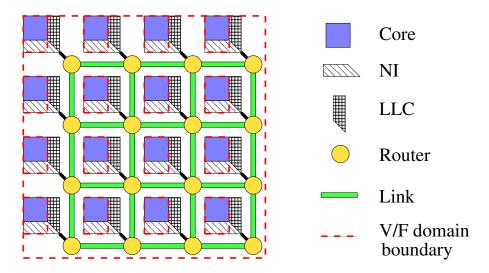

| 3.1   | A multicore processor design where the uncore (NoC+LLC) forms a single V/F domain                  | 51   |

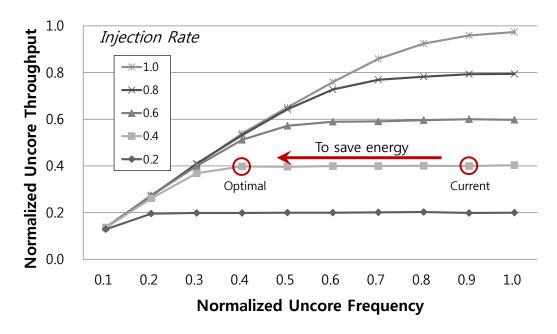

| 3.2  | Throughput vs. uncore frequency                                                                                                                                                                                                                                                                                                                                      | 54 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

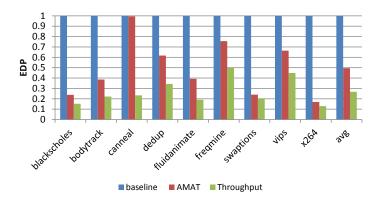

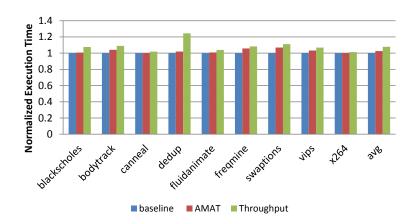

| 3.3  | Energy delay product                                                                                                                                                                                                                                                                                                                                                 | 58 |

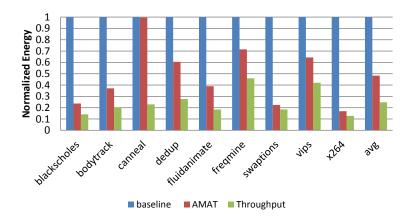

| 3.4  | Energy consumption                                                                                                                                                                                                                                                                                                                                                   | 59 |

| 3.5  | Execution time                                                                                                                                                                                                                                                                                                                                                       | 59 |

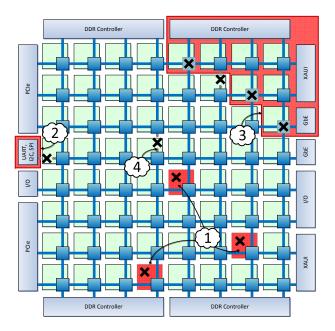

| 4.1  | A 64-core CMP interconnected with an $8 \times 8$ 2D mesh NoC. Components marked with a black $\times$ illustrate wearout failure. The failure scenarios are as follows: (1) failure of cores; (2) peripheral device disconnected from the system due to link failure; (3) network segmentation resulting in a disconnected sub-network; (4) individual link failure | 62 |

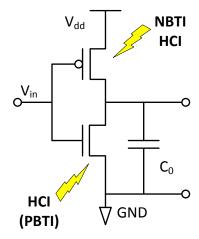

| 4.2  | CMOS inverter                                                                                                                                                                                                                                                                                                                                                        | 67 |

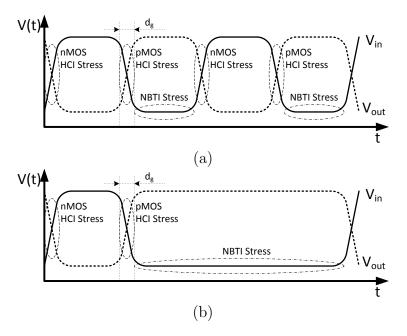

| 4.3  | HCI and NBTI stress time windows for a CMOS inverter: (a) higher switching activity, lower duty cycle; (b) lower switching activity, higher duty cycle                                                                                                                                                                                                               | 68 |

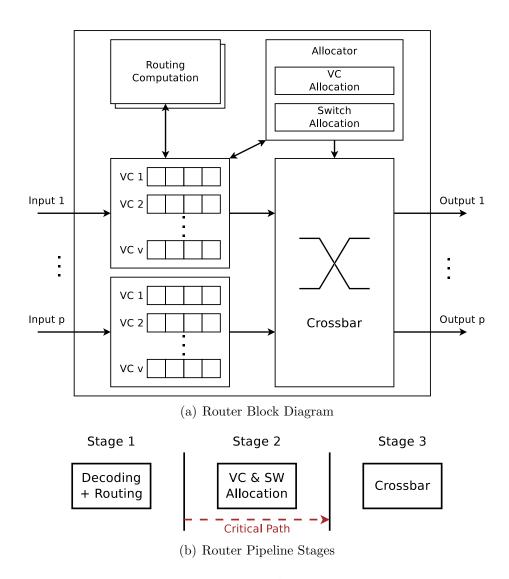

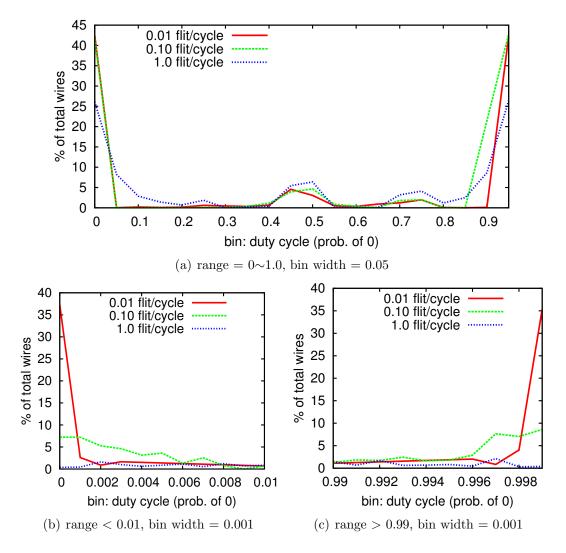

| 4.4  | Baseline router                                                                                                                                                                                                                                                                                                                                                      | 73 |

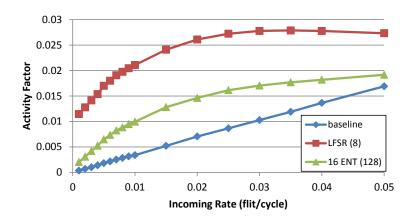

| 4.5  | Sensitivity to the activity factor                                                                                                                                                                                                                                                                                                                                   | 76 |

| 4.6  | Histogram of duty cycle w.r.t incoming rate                                                                                                                                                                                                                                                                                                                          | 79 |

| 4.7  | Average flit incoming rate per router for the entire range of the PAR-SEC benchmark suite (bars) and related range of incoming values (lines)                                                                                                                                                                                                                        | 80 |

| 4.8  | An example circuit path with multiple gates                                                                                                                                                                                                                                                                                                                          | 82 |

| 4.9  | Exercise logic placed onto the critical path so as to improve the duty cycle                                                                                                                                                                                                                                                                                         | 85 |

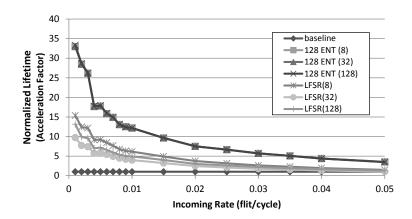

| 4.10 | Normalized lifetime (acceleration factor) for router under a given synthetic incoming rate from $0.001~\rm flits/cycle$ to $.05~\rm flits/cycle$                                                                                                                                                                                                                     | 90 |

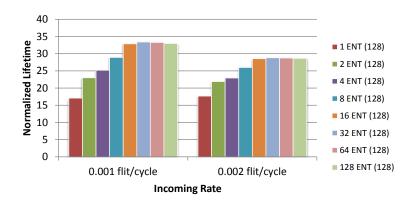

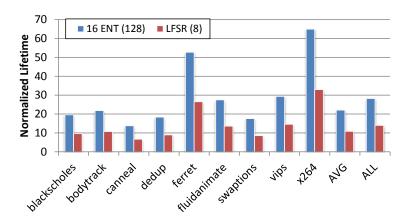

| 4.11 | Normalized lifetime with varying entry numbers under incoming rate of 0.001 flit/cycle and 0.002 flit/cycle                                                                                                                                                                                                                                                          | 92 |

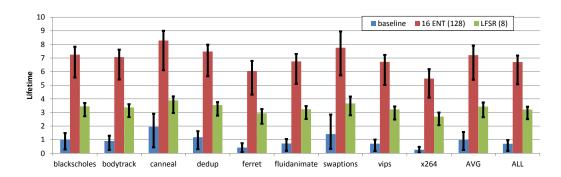

| 4.12 | Relative lifetime expectation                                                                                                                                                                                                                                                                                                                                        | 93 |

| 4.13 | Normalized lifetime of the network using the proposed technique under realistic workload                                                                                                                                                                                                                                                                             | 94 |

| 4.14 | Activity | y tacto | r versus | ınjecti  | on rate | under    | various | bit-width  | route  | r |    |

|------|----------|---------|----------|----------|---------|----------|---------|------------|--------|---|----|

|      | models   |         |          |          |         |          |         |            |        | • | 96 |

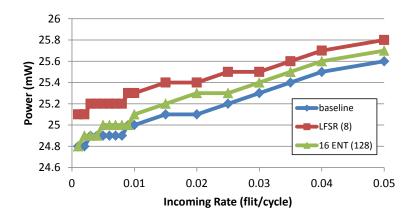

| 4.15 | Router   | power   | consum   | otion ui | nder va | rious bi | t-width | router mod | dels . |   | 97 |

# LIST OF TABLES

| ΓABLΙ | ${f E}$                      | Page |

|-------|------------------------------|------|

| 2.1   | Area and Power               | . 26 |

| 2.2   | Per-Flit Dynamic Energy (pJ) | . 27 |

| 3.1   | Simulation Setup             | . 58 |

| 4.1   | System Setup                 | . 89 |

#### 1. INTRODUCTION

While process technology scaling continues to provide more transistors, the transistor performance and power gains that accompany process scaling have largely ceased [39]. Chip-multiprocessor (CMP) designs achieve greater efficiency than traditional uniprocessors through concurrent parallel execution of multiple programs or threads. Meanwhile, the size of on-chip cache has been increased to overcome the memory wall caused by off-chip memory transactions. The on-chip cache, in general, is shared by multiple cores and divided into multiple slices each of which resides at each core. The increases in size and slice count of this shared cache result in the increases of on-chip communication bandwidth and power consumption. Indeed, the energy consumptions of on-chip communication fabrics and shared, last-level caches (LLCs) have grown to occupy a significant portion of the overall chip power, as much as 30% of total power in recent Intel's single-chip cloud computer [36].

As the core count in chip-multiprocessor (CMP) systems increases, networks-on-chip (NoCs) present a scalable alternative to traditional, bus-based designs for interconnection between processor cores [21]. As in most current VLSI designs, power efficiency has also become a first-order constraint in NoC design. In fact, it is becoming increasingly difficult to ignore the power consumption of NoC. The energy consumed by the NoC itself is as significant as 28% of the per-tile power in the Intel Teraflop chip [35] and 36% of the total chip power in MIT RAW chip [78].

At the same time, with the continuous down-scaling of process technologies, reliability has become an important concern in NoC design [26, 63, 9]. Deep sub-micron CMOS process technology is married by increasing susceptibility to wearout. Prolonged operational stress gives rise to accelerated wearout and failure, due to several

physical failure mechanisms, including Hot Carrier Injection (HCI) and Negative Bias Temperature Instability (NBTI). Each failure mechanism correlates with different usage-based stresses, all of which can eventually generate permanent faults. While the wearout of an individual core in many core CMPs may not necessarily be catastrophic for the entire parallel-processing system, a single fault in the interprocessor Network-on-Chip (NoC) fabric could render the entire chip useless, as it could lead to protocol-level deadlocks, or even partition away vital components such as the memory controller or other critical I/O.

#### 1.1 Thesis Statement

In this dissertation I propose that microarchitectural techniques can be used to address the twin problems of energy-efficiency and reliability in future process technologies. This dissertation describes two designs to improve energy efficiency in the NoCs and LLCs, and a solution to improve reliability of the NoCs.

It has been observed that cache lines fetched to level-1 caches are not fully utilized, and merely 40% of words in the cache lines are actually referenced by processors. A significant portion of NoC dynamic power is consumed by those unused words, which turn out to be predictable. This dissertation proposes a novel spatial locality predictor which speculates those unused words, and a novel packet composition scheme which encodes those words to eliminate bit transition along the NoC datapath.

This dissertation also explores a new Dynamic Voltage and Frequency Scaling (DVFS) scheme to reduce NoC and LLC power consumption. It is necessary to choose a metric on which to base a DVFS control. The metric should be controlled by the frequency level that we adjust and it should reflect the overall system performance. This dissertation proposes to use the throughput of *uncore*, which refers to NoC and LLC together, as the metric of the DVFS policy for uncore system, and proves that

such control results in improved energy efficiency compared to previous schemes.

It also addresses reliability issues in NoC design. Reliability of NoC becomes more important as the current and future chip-multiprocessors rely on it more. The scaling transistor size even accelerates the failure mechanisms, which will impact the critical path of the routers. This dissertation discusses the cause of such failure mechanisms in NoC and introduces a novel wear-resistant NoC router microarchitecture.

## 1.2 Dissertation Organization

This document is organized as follows. Chapter 2 introduces a novel energy reduction technique for the NoCs and LLCs through spatial locality speculation. Chapter 3 includes a new DVFS policy to achieve energy efficient NoCs and LLCs. Chapter 4 describes a new design method for reliable NoCs which mitigates the dominating failure mechanisms efficiently.

#### 2. ENERGY EFFICIENCY THROUGH SPATIAL LOCALITY PREDICTION\*

#### 2.1 Introduction

In this work we present a novel technique to reduce energy consumption for CMP core interconnect leveraging spatial locality speculation to identify unused cache block words. In particular, we propose to predict which words in each cache block fetch will be used and leverage that prediction to reduce dynamic energy consumption in the NoC channels and routers through diminished switching activity.

#### 2.1.1 Motivation

Current CMPs employ cache hierarchies of multiple levels prior to main memory [58, 3]. Caches organize data into *blocks* containing multiple contiguous words in an effort to capture spatial locality and reduce the likelihood of subsequent misses. Unfortunately, applications often do not fully utilize all the words fetched for a given cache block, as recently noted by Pujara et al. [66].

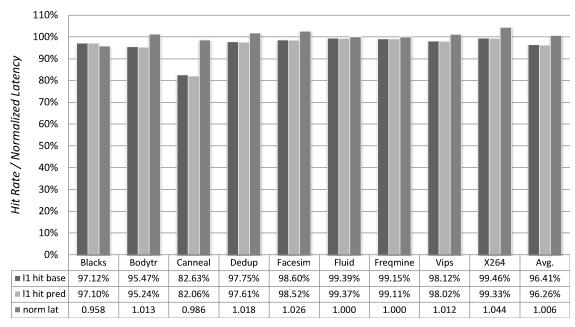

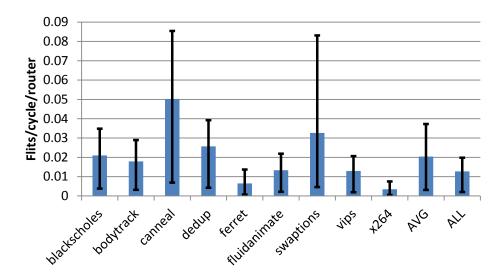

Figure 2.1 shows the percentage of words utilized in the PARSEC multithreaded benchmark suite [10]. On average, 61% of cache block words in the PARSEC suite benchmarks will never be referenced and represent energy wasted in transference through the memory hierarchy<sup>1</sup>. In this work, we focus on the waste associated with traditional approaches to spatial locality, in particular the wasted energy and power caused by large cache blocks containing unused data.

<sup>\*©2012</sup> IEEE. Reprinted, with permission, from Hyungjun Kim, Boris Grot, Paul V Gratz, Daniel Jimenez, NOCS Special Section: Spatial Locality Speculation to Reduce Energy in Chip-Multiprocessor Networks-on-Chip, IEEE Transactions on Computers, 2012

<sup>&</sup>lt;sup>1</sup>Versus 64-byte lines, 32-byte lines reduces unused words to 45%, however it increases AMAT 11% (See Section 2.5.3).

Figure 2.1: Percentage of 64-byte block, cache words utilized per block in the PAR-SEC multithreaded benchmarks.

#### 2.1.2 CMP Interconnect

Networks-on-chip (NoCs) purport to be a scalable interconnect to meet the increasing bandwidth demands of future CMPs [21]. NoCs must be carefully designed to meet many constraints. Energy efficiency, in particular, is a challenge in future NoCs as the energy consumed by the NoC itself is a significant fraction of the total chip power [35, 78]. The NoC packet datapath, consisting of the link, crossbar and FIFOs, consumes a significant portion of interconnect power, 55% of network power in the Intel Teraflop chip [35].

Existing NoCs implement channels with relatively large link bit-widths (>=128 bits) [28, 29], a trend expected to continue as more wire density becomes available in future process technologies. These high-bandwidth link wires reduce the latency of cache block transmission by allowing more words to be transferred in each cycle, minimizing serialization latency for large packets. In some cases, however, not all the words in a flit are useful to the processor. In particular, unused cache block words represent wasted power and energy. We propose to use spatial locality speculation to leverage unused words of the block transfers between the lower and upper cache levels to save energy.

#### 2.1.3 Proposed Technique

The goal of the proposed technique is to reduce dynamic energy in CMP interconnect by leveraging spatial locality speculation on the expected used words in fetched cache blocks in CMP processor memory systems.

The work makes the following contributions:

- A novel intra-cache-block spatial locality predictor, to identify words unlikely to be used before the block is evicted.

- A static packet encoding technique which leverages spatial locality prediction

to reduce the network activity factor, and hence dynamic energy, in the NoC

routers and links. The static encoding requires no modification to the NoC and

minimal additions to the processor caches to achieve significant energy savings

with negligible performance overhead.

- A complementary dynamic packet encoding technique which facilitates additional energy savings in NoC links and routers via light-weight microarchitectural enhancements.

In a 16-core CMP implemented in a 45-nm process technology, the proposed technique achieves an average of  $\sim 35\%$  savings in total dynamic interconnect energy at the cost of less than 1% increase in memory system latency.

The rest of this chapter is organized as follows: Section 4.7 discusses the related work and background in caches, NoCs and power efficiency on-chip to provide the intuition behind our power saving flit-encoding technique. Section 2.3 discusses our proposed technique in detail, including the proposed spatial locality predictor and the proposed packet encoding schemes. Section 4.6 and 2.5 present the experimental setup and the results. Finally, we conclude in Section 4.8.

#### 2.2 Background and Related Work

#### 2.2.1 Dynamic Power Consumption

When a bit is transmitted over interconnect wire or stored in an SRAM cell, dynamic power is consumed as a result of a capacitive load being charged up and also due to transient currents during the momentary short from Vdd to Gnd while transistors are switching. Dynamic power is not consumed in the absence of switching activity. Equation 2.1 shows the dynamic and short-circuit components of power consumption in a CMOS circuit.

$$P = \alpha \cdot C \cdot V^2 \cdot f + t \cdot \alpha \cdot V \cdot I_{short} \cdot f \tag{2.1}$$

In the equation, P is the power consumed, C is the switched capacitance, V is the supplied voltage, and F is the clock frequency.  $\alpha$  represents the activity factor, which is the probability that the capacitive load C is charged in a given cycle. C, V, and F are a function of technology and design parameters. In systems that support dynamic voltage-frequency scaling (DVFS), V and F might be tunable at run time; however, dynamic voltage and frequency adjustments typically cannot be done at a fine spatial or temporal granularity [75]. In this work, we target the activity factor,  $\alpha$ , as it enables dynamic energy reduction at a very fine granularity.

Researchers have recently begun focusing on the energy and power in NoCs, which have been shown to be significant contributors to overall chip power and energy consumption [35, 78, 44, 6].

One effective way to reduce NoC power consumption is to reduce the amount of data sent over the network. To that extent, recent work has focused on compression at the cache and network levels [23, 42] as an effective power-reduction technique. In general, however, compression techniques have overheads in terms of latency for compression and decompression. The technique we present is orthogonal to, and could potentially be used in conjunction with, these loss-less compression techniques to further reduce power. Our work seeks to reduce the amount of data transmitted through identification and removal of useless words; traditional compression could be used to more densely pack the remaining data.

Researchers have also proposed a variety of techniques to reduce interconnect energy consumption through reduced voltage swing [83]. Schinkel et al. propose a scheme which uses a capacitative transmitter to lower the signal swing to 125 mV without the use of an additional low-voltage power supply [72]. In this work we evaluate our prediction and packet encoding techniques for links composed of both full-signal swing as well as low-signal swing wires.

NoC router microarchitectures for low power have also been explored to reduce power in the transmission of data which is much smaller than a flit. Das et al. propose a novel crossbar and arbiter design that supports concurrent transfers of multiple flits on a single link to improve bandwidth utilization. [22].

Finally, static power consumption due to leakage currents is also a significant contributor to total system power. However, researchers have shown that power-gating techniques can be comprehensively applied at the NoC level and are highly effective at reducing leakage power at periods of low network activity [32].

## 2.2.3 Spatial Locality and Cache Block Utilization

Spatial and temporal locality have been studied extensively since caches came into wide use in the early 1980's [33]. Several works in the 1990's and early 2000's focused on indirectly improving spatial locality through compile and run-time program and

data transformations which improve the utilization of cache lines [16, 15, 20, 19]. While these techniques are promising, they either require compiler transformations or program changes and cannot be retrofitted onto existing code. Our proposed approach relies on low-overhead hardware mechanisms and is completely transparent to software.

Hardware techniques to minimize data transfer among caches and main memory have also been explored in the literature. Sectored caches were proposed to reduce the data transmitted for large cache block sizes while keeping overhead minimal [54]. With the sectored cache, only a portion of the block (a sector) is fetched, significantly reducing both the miss time and the bus traffic. The proposed technique builds upon this idea by speculatively fetching, not just the missing sector but sectors (words in this case) which have predicted spatial locality with the miss.

Prefetching is a technique where cache lines expected to be used in the future are fetched prior to their demand request, to improve performance by reducing misses. This may come at the cost of more power spent in the interconnect between caches when inaccurate prefetches lead to unused cache block fetches. Our technique is complementary and can be used to compensate prefetch energy overhead by gating unused words.

Pujara et al. examined the utilization of cache lines and showed that only 57% of words are actually used by the processor and the usage pattern is quite predictable [66]. They leverage this information to lower power in the cache itself by reducing the number of words read from the lower level cache and written to the upper level cache. This mechanism is orthogonal and potentially complementary to our technique, as we focus primarily on achieving lower energy consumption in the interconnect. Youn et al. proposed an architecture that adaptively chooses memory system granularity based on spatial locality and error-tolerance tradeoffs [81]. While

this work focuses on contention for off-chip memory bandwidth, our work targets on-chip interconnect energy consumption by observing spatial locality. Qureshi et al. suggested a method to pack the used words in a part of the cache after evicting it from the normal cache, thus increasing performance and reducing misses [67]. Their work thus focuses on performance rather than energy-efficiency and targets the effectiveness of the second-level cache.

Spatial locality prediction is similar to dead block prediction [50]. A dead block predictor predicts whether a cache block will be used again before it is evicted. The spatial locality predictor introduced in this work can be thought of as a similar device at a finer granularity. The spatial locality predictor, however, takes into account locality relative to the critical word offset, unlike dead block predictors. Chen et al. predicted a spatial pattern using a pattern history table which can be referenced by the pc appended with the critical offset [17]. The number of entries in the pattern history table, as well as the number of indexes increase the memory requirement of the technique. Unlike these schemes, our predictor uses a different mechanism for managing prediction thresholds in the face of mispredictions. Kim et al. proposed spatial locality speculation to reduce energy in the interconnect [47], we present here an extended journal version of this earlier work.

## 2.3 Description

Our goal is to save dynamic energy in the memory system interconnect by eliminating switching activity associated with unused words in cache blocks transferred between the different levels of the on-chip cache hierarchy. To this end we developed a simple, low complexity, spatial locality predictor, which identifies the words expected to be used in each cache block. A used word prediction is made on a L1 cache miss, before generating a request to the L2. This prediction is used to generate the response packet eliding the unused words with the proposed flit encoding schemes described below.

Figure 2.2: General CMP architecture

Figure 2.2 depicts the general, baseline architecture, representing a 16-node NoC-connected CMP. A tile consists of a processor, a portion of the cache hierarchy and a Network Interface Controller (NIC), and is bound to a router in the interconnection

Figure 2.3: Prediction example for 4 words/block cache model

network. Each processor tile contains private L1 instruction and data caches. We assume the L2 is organized as a shared S-NUCA cache [46], each tile containing one bank of the L2. The chip integrates two memory controllers, accessed via the east port of node 7 and west port of node 8. Caches have a 64-byte block size. The NoC link width is 16 bytes, discounting flow-control overheads. Thus, cache-block-bearing packets are five flits long, with one header flit and four data flits. Each data flit contains four 32-bit words, as shown in Figure 2.5(b).

#### 2.3.1 Spatial Locality Prediction

#### 2.3.1.1 Prediction Overview

Our predictor leverages the history of use patterns within cache blocks brought by a certain instruction has been accessed. The intuition behind our predictor is that a given set of instructions may access multiple different memory address regions in a similar manner. In fact, we have observed that patterns of spatial locality are highly correlated to the address of the instruction responsible for filling the cache (the *fill PC*). The literature also shows that a small number of instructions cause the most cache misses [2]. Moreover, a given sequence of memory instructions accesses the same fields of data structures throughout memory [17]. Data structure instances, are unfortunately not aligned to the cache block, this misalignment can be adjusted by using the offset of the word which causes the cache miss (the *critical word offset*) while accessing the prediction table as in [66].

## 2.3.1.2 Predictor Implementation

Our prediction table is composed of rows of four-bit saturating counters where each counter corresponds to a word in the cache block. The table is accessed such that the *fill PC* picks the row of the table, and then n consecutive counters starting from the *critical word offset* are chosen where n is the number of words in a cache block. (Thus, there are 2n-1 counters per row to account for all possible n-1 offsets.) These counters represent the history of word usage in cache blocks brought by a certain memory instruction.

The value of the saturating counter relates to the probability that the corresponding word is used. The lower the counter is, the higher confidence the word will not be used. Initially, all counters are set to their max value, representing a prediction where all words are used. As cache lines are evicted with unused words, counters associated with those unused words are decremented while counters associated with used words are incremented. If a given word counter is equal to or greater than a fixed threshold (configured at design time), then the word is predicted to be used; otherwise, it is predicted not used. We define used-vector as a bit vector which identifies the words predicted used by the predictor in the cache block to be filled. A used-vector of 0xFFFF represents a prediction that all sixteen words will be used

while a used-vector of 0xFF00 signifies that only the first eight words will be used.

Figure 2.3 shows the steps to the prediction. In this example, the number of words in a block is assumed to be 4 and the threshold is 1, for simplicity. In the figure a cache miss occurs on an instruction accessing the second word in a given block ( $critical\ word\ offset=1$ ). The lower-order bits of the fill PC select a row in the prediction table. Among the counters in the row, the selection window of 4 counters, which initially includes the four rightmost counters, moves to the left by the number of the critical word offset. Those selected counters are translated into a predicted used-vector based on the threshold value. The used-vector, 1100, indicates that the first and the second words in this block will be used.

The L1 cache keeps track of the actual used vector while the block is live, as well as the lower-order bits of the fill PC, and the critical word offset. When the block is evicted from the L1, the predictor is updated with the actual used vector; if a word was used, then the corresponding counter is incremented; otherwise, it is decremented. While updating, it finds the corresponding counters with the fill-PC and the critical word offset as it does for prediction. In the event a word is falsely predicted "unused", the counters for the entire row are reset to 0xF to reduce the likelihood of future mispredictions. This form of resetting have been shown to improve confidence over up/down counters for branch predictors [40]; in initial development of the predictor we found a considerable improvement in accuracy using this technique as well. Resetting the counters allows the predictor to quickly react in the event of destructive interference and/or new program phases.

We model a cache with 64B blocks and 4B words. Each row of the predictor is composed of 31 four-bit saturating counters where all counters are initialized to

0xF. The predictor table has 256 rows of  $31 \times 4$  bits each, thus requiring  $\sim 4KB$  of storage. We note, although the "word" size here is 4B, this represents the prediction granularity, it does not preclude use in a 64b (8B) word architecture.

In addition to the 4KB prediction table, our scheme requires extended metadata in each cache tag. In L1, 16 bits (one per word) are necessary to determine which words have been accessed so that we can update the predictor. 8 bits for *fill-PC* and 4 bits for *critical word offset* are required to access the prediction table, as well. We also replace the single valid bit with a vector of 16 bits in L1 and L2 caches. Although, this metadata increases the power per access of the L1 and L2 caches by 0.35% and 0.72%, respectively, we also reduce the number of words read from the lower level caches and written to the upper level cache by  $\sim 30\%$  and also the number of words written back into the lower level cache by  $\sim 40\%$ . Altogether this results an average  $\sim 20\%$  reduction in dynamic energy consumption per cache access. The dynamic energy consumed by the prediction tables is discussed in Section 4.6.

Although not the focus of this work, leakage energy dissipation can be also optimized with the help of spatial locality speculation. Chen et al. achieved 41% of leakage energy reduction with their proposed spatial locality predictor and a circuit level selective sub-blocking technique [17]. We expect a better reduction could be achieved with our technique (as our predictor accuracy is higher), we plan to explore this in a future work on used word prediction for cache power reduction.

## 2.3.1.4 Impact on Performance

When an L1 cache miss is discovered, the predictor supplies a prediction to inform flit composition. The prediction will take two cycles: one for the table access and one for thresholding and shifting. The fastest approach would be to speculatively assume that every cache access will result in a miss and begin the prediction simultaneously with address translation; thus, the latency can be completely hidden. A more energy efficient approach is to begin the prediction as soon as the tag mismatch is discovered and simultaneously with victim selection in the L1 cache. While this approach would add a cycle to the L1 miss time, no time would be added to the more performance critical L1 hit time. The latter approach was used in our experiments. If a word predicted unused actually is used, it is treated as a miss and all words initially predicted as unused are brought into the upper-level cache in order to correct this misprediction. This performance impact of these extra misses is discussed in Section 2.5.1.

On eviction of a L1 cache block, the used-vector and fill PC collected for that block are used to update the predictor. This process is less latency sensitive than prediction since the predictor does not need to be updated immediately to provide good accuracy.

## 2.3.2 Packet Composition

Once we have predicted the application's expected spatial locality to determine the unused words in a missing cache block, we employ a flit encoding technique which leverages unused words to reduce dynamic link and router energy in the interconnect between the L1, directory, L2 cache banks and memory controllers. We propose two complementary means to leverage spatial locality prediction to reduce  $\alpha$ , the activity factor, in the NoC, thereby directly reducing dynamic energy: 1) Remove flits from NoC packets (flit-drop); 2) Keep unused interconnect wires at fixed polarity during packet traversal (word-repeat). For example, if two flits must be transmitted and all the words in the second flit are predicted unused, our flit-drop scheme would discard the unused flit to reduce the number of flits transmitted over the wire. In contrast, our word-repeat scheme would re-transmit the first flit, keeping the wires

at fixed polarity to reduce gate switching. These encoding schemes are also used for writeback packets to include dirty words only.

The packet compositioning may be implemented either "statically", whereby packet encoding occurs at packet generation time, or "dynamically", in which the unused words in each flit are gated within the router FIFOs, crossbars and links to avoid causing bit transitions regardless of the flits which proceed or follow it. We will first discuss the "static" packet compositioning techniques including *flit-drop*, *static-word-repeat* and their combination. We then discuss the "dynamic" packet composition techniques which allow greater reductions in activity factor, at the cost of a small increase in logical complexity in the routers and a slight increase in link bit-width.

## 2.3.2.1 Static Packet Composition

Figure 2.4 depicts the format of cache request and reply packet flits in our design. A packet is composed either of a head flit and a number of body flits (when the packet contains a cache block) or it consists of one atomic flit, as in the case of a request packet or a coherence protocol message. The head/atomic flit contains a used-vector. The head flit also contains source and destination node identifiers, and the physical memory address of the cache block. The remaining bytes in the head/atomic flit are unused. We assume a flow-control overhead of three bits, 1 bit for virtual channel id (VC) and 2 bits for flit type (FT). As each of body/tail flit contains data of four words (16 bytes), a flit is 16 bytes and 3 bits wide including flow control overheads.

Figure 2.5(a) depicts an example of read request (L1 fill). In this example, tile #1 requests a block at address 0x00001200 which resides in the S-NUCA L2 cache bank in tile #8. The used-vector is 1111 1100 0000 1010, indicating the words  $word_0$  -  $word_5$ ,  $word_{12}$  and  $word_{14}$  are predicted used. The corresponding response

Figure 2.4: Flit format for static and dynamic encoding. (Shaded portion not present in static encoding.)

packet must contain at least those words. Since the baseline architecture sends the whole block as it is, the packet contains all of the words from  $word_0$  to  $word_{15}$ , as shown in figure 2.5(b).

Flit-drop: In the *flit-drop* technique, flits which are predicted to contain only unused words are dropped from the packet and only those flits which contain one or more used words are transmitted. The reduction in the number of flits per packet, reduces the number of bit transitions over interconnect wires and therefore the energy consumed. Latency due to packet serialization and NoC bandwidth will also be reduced as well. Although a read request packet may have an arbitrary used-vector, the response packet must contain all flits which have any words predicted used leading to some lost opportunity for packets which have used and unused words intermingled throughout.

Figure 2.5(c) depicts the response packet to the request shown in Figure 2.5(a) for the flit-drop scheme. The first body flit, containing  $word_0$  -  $word_3$ , therefore must be in the packet as all of these words are used. The second body flit, with  $word_4$  -  $word_7$ , also contains all valid words, despite the prediction  $word_6$  and  $word_7$  would not be used. These extra words are overhead in the flit-drop scheme because they are not predicted used but must be sent nevertheless. Although these words waste dynamic power when the prediction is correct, they may reduce the miss-prediction probability.

Static-word-repeat: The static-word-repeat scheme, reduces the activity factor of flits containing unused words by repeating the contents in previous flit in the place of unused words. Flits with fewer used words consume less power because there are fewer bit transitions between flits. Words marked as "used" in the used-vector contain real, valid data. Words marked as "unused" in the used-vector contain repeats of the word in the same location in the previous flit. For instance, if  $word_{4x+1}$  is predicted unused, the NIC places  $word_{4(x-1)+1}$  in its place. As the bit-lines repeat the same bits, there are no transitions on those wires and no dynamic energy consumption. A buffer retaining four words previously fetched by the NIC is placed between the cache and the NIC and helps the NIC in repeating words. An extra mux and logic gates are also necessary in the NIC to encode repeated words.

Figure 2.5(d) depicts the response packet for the request in Figure 2.5(a) using the static-word-repeat scheme. In  $body_1$ ,  $word_6$  and  $word_7$  are unused and, thus, replaced with  $word_2$  and  $word_3$  which are at the same location in the previous flit. All of the words in  $body_2$  are repeated by the words in  $body_1$ , thus it carries virtually nothing but flow-control overhead. We also encode the unused header words, if possible.

| FT   | SRC |     | MSG |         | Mem Address | Unused                       |  |  |

|------|-----|-----|-----|---------|-------------|------------------------------|--|--|

| ATOM | 1   | 8   | REQ | 0xFC0A  | 0x1200      | X                            |  |  |

|      |     | DST | •   | Used Ve | ctor        | 0XFC0A = 1111 1100 0000 1010 |  |  |

#### (a) Request

| HEAD  | 8 1 RESP 0xFFFF |      | 0xFFFF  | 0x1200   | UNUSED 0 | UNUSED 1 |               |         |        |         |         |

|-------|-----------------|------|---------|----------|----------|----------|---------------|---------|--------|---------|---------|

| BODY0 |                 | WORD | 0       | WORD 1   | WORD 2   | WORD 3   |               |         |        |         |         |

| BODY1 | WORD 4          |      |         | WORD 5   | WORD 6   | WORD 7   |               |         |        |         |         |

| BODY2 | WORD 8          |      |         | 2 WORD 8 |          |          | WORD 8 WORD 9 |         | WORD 9 | WORD 10 | WORD 11 |

| TAIL  | WORD 12         |      | WORD 12 |          | 12       | WORD 13  | WORD 14       | WORD 15 |        |         |         |

0xFFFF = 1111 1111 1111 1111

#### (b) Baseline Response

| HEAD  | 8 1 RESP 0xFF0F |  | 8 1 RESP 0xFF0F 0x1200 |   | 0x1200  | UNUSED 0 | UNUSED 1 |  |

|-------|-----------------|--|------------------------|---|---------|----------|----------|--|

| BODY0 | WORD 0          |  |                        | 0 | WORD 1  | WORD 2   | WORD 3   |  |

| BODY1 | WORD 4          |  |                        | 4 | WORD 5  | WORD 6   | WORD 7   |  |

| TAIL  | WORD 12         |  | WORD 12 WORD 13        |   | WORD 14 | WORD 15  |          |  |

0xFF0F = 1111 1111 0000 1111

#### (c) Flit-Drop Response

| HEAD  | 8 1 RESP 0xFC0A |  | 8 1 RESP 0xFC0A |               | 0x1200 | 0x1200   |         | WORD 2 |        | RD 3 |      |

|-------|-----------------|--|-----------------|---------------|--------|----------|---------|--------|--------|------|------|

| BODY0 | WORD 0          |  |                 | 0             | WORD 1 | W        | ORD 2   | WORD 3 |        |      |      |

| BODY1 | WORD 4          |  |                 | 4             | WORD 5 | <u> </u> | W       | ORD 2  | WO     | RD 3 |      |

| BODY2 | WORD 4          |  |                 | WORD 4 WORD 5 |        |          | )       | W      | ORD 2  | WO   | RD 3 |

| TAIL  | WORD 12         |  | WORD 12         |               | WORD 5 |          | WORD 14 |        | WORD 3 |      |      |

0xFC0A = 1111 1100 0000 1010

#### (d) Word-Repeat Response

Figure 2.5: Read request and corresponding response packets (VC is not shown in this figure.)

## 2.3.2.2 Dynamic Packet Composition

The effectiveness of static packet compositioning schemes is reduced in two commonlyoccurring scenarios: (a) when single-flit, atomic packets are being transmitted, and

(b) when flits from multiple packets are interleaved in the channel. In both cases,

repeated words in the flits cannot be statically leveraged to eliminate switching activity in the corresponding parts of the datapath. In response, we propose dynamic

packet composition to reduce NoC switching activity by taking advantage of invalid

words on a flit-by-flit basis. The difference between dynamic and static composition schemes resides primarily in how word-repeat treats unused words. In static composition, the unused portion of a flit is statically set at packet injection by the NIC to minimize inter-flit switching activity, requiring no changes to the router datapath. In dynamic composition, portions of the router datapath are dynamically enabled and disabled based on the validity of each word in the flit. In effect, an invalid word causes the corresponding portion of the datapath to hold its previous value, creating the illusion of word repeat.

To facilitate dynamic composition, the "used-vector" is distributed into each flit as shown in Figure 2.4(b). As a result the link width must be widened by four bits to accommodate the new "valid-word-vector", where each bit indicates whether the corresponding word in that flit is valid. As the figure shows, the head flit's "valid-word-vector" is always set to 1100 because the portion which corresponds to  $Word_2$  and  $Word_3$  of a body/tail flit are always unused.

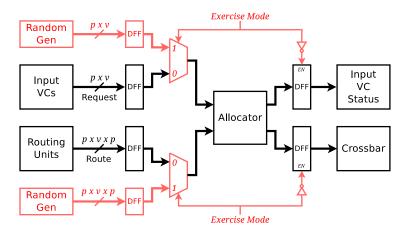

Dynamic packet compositioning requires some modifications to a standard NoC router to enable datapath gating in response to per-flit valid bits. Figure 2.6 depicts the microarchitecture of our dynamic packet compositioning router. Assuming that a whole cycle is required for a flit to traverse a link, latches are required on both sides of each link. The additional logic required for link encoding is shaded in the magnified output port. Plain D-flip-flops are replaced with enable-D-flip-flops to force the repeat of the previous flit's word when the "valid-word-vector" bit for that word is set to zero, indicating that word is not used. Alternately, if the "valid-word-vector" bit for the given word is one, the word is propagated onto the link in the following cycle, as it would in the traditional NoC router. In cases where the link traversal consumes less than a full cycle, this structure could be replaced with a tristate buffer to similar effect.

Figure 2.6: Dynamic packet compositioning router. (Shaded portion not present in baseline router.)

We further augment the router's input FIFO buffers with per-word write enables connected to the "valid-word-vector" as shown in Figure 2.6. In our design, the read and write pointer control logic in the router's input FIFOs remain unmodified; however, the SRAM array storage used to hold the flits is broken into four banks, each one word in width. The "valid-word-vector" bits would gate the valid write enables going to each of word-wide banks, disabling writes associated with unused words in incoming flits, and saving the energy associated with those word writes. The combination of these techniques for dynamic packet composition will reduce the power and energy consumption of the NoC links and router datapath proportional to the reduction in activity factor due to the word-repeat and flit-drop of unused words.

As *flit-drop* and *word-repeat* are complementary, we will also examine their combination in the evaluation section. One alternative technique we explored packs together used words into a minimal size packet. Experimentally we found this approach produces latency and power benefits negligibly different from the combination of *flit-drop* and *word-repeat*, while our technique requires less additional hardware in packet composition, so these results are not presented. These encoding schemes also are used for writebacks by marking clean words as unused.

#### 2.4 Evaluation

## 2.4.1 Baseline Architecture and Physical Implementation

Figure 2.2 depicts the baseline architecture, representing a 16-node NoC-connected CMP. A tile consists of a processor, a portion of the cache hierarchy and a Network Interface Controller (NIC), and is bound to a router in the interconnection network. The baseline architecture employs a  $4\times4$  2D mesh topology with X-Y routing and wormhole flow control. Each router contains 2 VCs and each input buffer is four flits deep. In our baseline configuration we assume the tiles are  $36mm^2$  with 6mm-long links between nodes. Our target technology is 45 nm.

Processor Tiles: Each  $36mm^2$  tile contains an in-order processor core similar to an Intel Atom Z510 ( $26mm^2$ ) [38], a 512KB L2 cache slice ( $4mm^2$ ), two 32KB L1 caches ( $0.65mm^2$  each) and an interconnect router ( $0.078mm^2$ ). The remaining area is devoted to a directory cache and a NIC. Our system is composed of 16 tiles and results in  $576mm^2$ , approximately the size of an IBM Power7 die [43]. We used CACTI 6.0 [59] to estimate cache parameters.

The L1 caches are two-way set-associative with a 2 cycle access latency. The L2 banks are 8-way set-associative with a 15-cycle access time. The 16 L2 banks spread across the chip comprise an 8-MB S-NUCA L2 [46]. Cache lines in both L1 and L2 caches are 64B wide (16 four-byte words), except where otherwise noted. Each node also contains a slice of the directory cache, interleaved the same as the L2. Its latency is 2 cycles. The number of entries in each directory cache is equal to the number of sets in an L2 bank. We assume the latency of the main memory is 100 cycles. The MESI protocol is used by the directory to maintain cache coherence. The predictor's performance is examined with the threshold value of 1 unless stated otherwise. The NoC link width is assumed to be 128 bits wide, discounting flow-control overheads.

NoC Link Wires: NoC links require repeaters to improve delay in the presence of the growing wire RC delays due to diminishing interconnect dimensions [39]. These repeaters are major sources of channel power and area overhead. Equally problematic is their disruptive effect on floorplanning, as large swaths of space must be allocated for each repeater stage. Our analysis shows that a single, energy-optimized 6 mm link in 45 nm technology requires 13 repeater stages and dissipates over 42 mW of power for 128 bits of data at 1 Ghz.

In this work, we consider both full-swing repeated interconnects (full-swing links) and an alternative design that lowers the voltage swing to reduce link power consumption (low-swing links). We adopt a scheme by Schinkel et al. [72] which uses a capacitative transmitter to lower the signal swing to 125 mV without the use of an additional low-voltage power supply. The scheme requires differential wires, doubling the NoC wire requirements. Our analysis shows a  $3.5\times$  energy reduction with low swing links. However, low-swing links are not as static-word-repeat friendly as much as full-swing links are. There is link energy dissipation on low-swing links, even when a bit repeats the bit ahead because of leakage currents and high sense amp power consumption on the receiver side. Thus, the repeated unused-words consume  $\sim 18\%$  of what used-words do. The dynamic encoding technique fully shuts down those portions of link by power gating all components with the "valid-word-vector" bits.

Router Implementation: We synthesized both the baseline router and our dynamic encoding router on a TSMC 45nm library to an operating frequency of 1Ghz. Table 2.1 shows the area and power of the different router designs. Note that the baseline router and the one used in static encoding scheme are identical. The table shows the average power consumed under PARSEC traffic, simulated with the methodology described in Section 2.4.2. The dynamic power for each benchmark is

Table 2.1: Area and Power

|                             | baseline  | static    | dynamic |  |  |

|-----------------------------|-----------|-----------|---------|--|--|

| Area $(mm^2)$               | 0.07      | 0.078     |         |  |  |

| Static Power (mW)           | 0.7       | 0.74      |         |  |  |

| Router with full-swing link |           |           |         |  |  |

| Dynamic Power (mW)          | 1.73      | 1.73 1.28 |         |  |  |

| Total Power (mW)            | 2.45 1.99 |           | 1.67    |  |  |

| Router with low-swing link  |           |           |         |  |  |

| Dynamic Power (mW)          | 0.62 0.46 |           | 0.33    |  |  |

| Total Power (mW)            | 1.34 1.18 |           | 1.08    |  |  |

computed by dividing the total dynamic energy consumption by the execution time, then by the number of routers. Summarizing the data, a router design supporting the proposed dynamic composition technique requires  $\sim 7\%$  more area, while reducing dynamic power by 46% under the loads examined over the baseline at the cost of 4.3% more leakage power.

Table 2.2 shows the dynamic energy consumed by a flit with a given number of words encoded as used, traversing a router and a link, with respect to the three flit composition schemes: baseline(base), static(sta) and dynamic(dyn) encoding. In baseline, a flit always consumes energy as if it carries four used words. In static encoding, as the number of used words decreases, flits consume less energy on routers and full-swing links. Static-encoding reduces NoC energy by minimizing the number of transitions on the wires in the links and in the routers' crossbars. Dynamic-encoding further reduces router energy by gating flit buffer accesses. The four-bit, valid-word-vector in each flit controls the write enable signals of each word buffer, disabling writes associated with unused words. Similarly, it also gates low-swing links, shutting down the transceiver pair on wires associated with the unused words. CACTI 6.0 [59] was used to measure the energy consumption due to accessing the

Table 2.2: Per-Flit Dynamic Energy (pJ)

|   | Router |      | Full Swing Link |       |                      | Low Swing Link |       |       |       |

|---|--------|------|-----------------|-------|----------------------|----------------|-------|-------|-------|

| n | base   | sta  | dyn             | base  | $\operatorname{sta}$ | dyn            | base  | sta   | dyn   |

| 0 |        | 0.73 | 0.34            |       | 0.99                 | 2.30           |       | 0.35  | 0.66  |

| 1 |        | 1.31 | 1.01            |       | 11.52                | 12.83          |       | 3.34  | 3.67  |

| 2 | 3.58   | 1.90 | 2.01            | 43.10 | 22.04                | 23.36          | 12.31 | 6.33  | 6.67  |

| 3 |        | 2.77 | 2.79            |       | 32.57                | 33.89          |       | 9.32  | 9.68  |

| 4 |        | 3.58 | 3.65            |       | 43.10                | 44.41          |       | 12.31 | 12.69 |

n: number of used words

predictor; which is 10.9 pJ per access.

# 2.4.2 Simulation Methodology

We used the M5 full system simulator to generate CMP cache block utilization traces for multi-threaded applications [12]. Details of the system configuration are presented in section 2.4.1. Our workload consists of the PARSEC shared-memory multi-processor benchmarks [10], cross-compiled using the methodology described by Gebhart et. al [27]. All applications in the suite currently supported by M5 were used. Traces were taken from the "region of interest." Each trace contains up to a billion memory operations; fewer if the end of the application was reached. Cycle accurate timing estimation was performed using the *Netrace*, memory system dependence tracking methodology [34].

The total network energy consumption for each benchmark is measured by summing the energy of all L1 and L2 cache fill and spill and coherence packets as they traverse routers and links in the network. In effect, Table 2.2 is consulted whenever a flit with a certain number of used words traverses a router and a link. Note that even for the same flit, the used word number may vary according to the encoding scheme in use. For example, for an atomic flit, n = 4 in static encoding while n = 2 in dynamic. The predictor's energy is also added whenever the predictor is accessed.

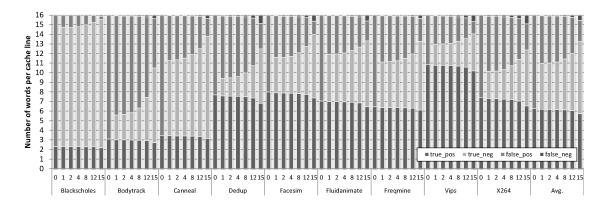

Figure 2.7: Dynamic energy breakdown

## 2.4.3 Energy Consumption

Figure 2.7 shows the breakdown of dynamic energy consumption. For each benchmark, we conducted energy simulations for three configurations, each represented by one stacked bar for that benchmark: 1) baseline - baseline, 2) s-combo - static-word-

repeat and flit-drop combined, and 3) d-combo - dynamic-word-repeat and flit-drop combined. We also show the average energy consumption with pure flit-drop (flit-drop), static-word-repeat (s-wr) and dynamic-word-repeat (d-wr). The bars are normalized against the energy consumed by baseline. Each bar is subdivided into up to four components. The first bar shows the "read" energy, energy consumed by cache fills and the second bar, "write", by writebacks. The third bar, "coh", shows the energy due to the cache coherence packets and the fourth bar, "pred" shows the energy consumed by predictors. The figure shows data for both full-swing and low-swing links.

In the baseline configuration we see that, on average, read communication consumes the most dynamic energy with  $\sim 59\%$  of the total. Coherence traffic consumes the second most with  $\sim 28\%$  of the total energy followed by write communication with  $\sim 13\%$  of the total energy. This breakdown follows the intuition that reads are more frequent than writes. Thus, techniques which only focus on writebacks will miss much potential gain. It is also interesting to note that cache coherence traffic shows a very significant contribution to overall cache interconnect energy. Similarly, work which does not consider atomic packets may miss significant gain.

The figure also shows that among the flit encoding schemes, d-combo shows the greatest improvement with  $\sim 36\%$  dynamic energy savings on average when full-signal swing link is used. If low-signal swing links are used, it becomes  $\sim 34\%$ . The pure dynamic-word-repeat (d-wr) is the second best resulting in additional  $\sim 1\%$  energy consumption. This implies that dropping flits only with flow control bits does not significantly contribute to energy reduction when dynamic- word-repeat is used. However, combining flit-drop is still beneficial to reduce latency. The combined static encoding (s-combo) provides an energy savings of only  $\sim 17\%$  and  $\sim 15\%$  of baseline, under full-swing and low-swing links, respectively. This indicates the

Figure 2.8: Dynamic energy breakdown for reads

significant gains that dynamic encoding provides, primarily in the cache coherence traffic which is predominately made up of single flit packets. We find the predictor merely contributes 1.5% of the total energy when full-signal swing link is used, and 4.1% when low-signal swing link is used.

Table 2.1 shows the average power with either type of links. It reveals that despite the increased static power, the dynamic encoding scheme still outperforms the baseline and the static encoding as well, regardless of link type.

In the following sections we will examine each of the traffic types in detail to gain a deeper understanding of the performance of our proposed technique. As full-swing link and low-swing link show similar trends, only graphs for full-swing links will be shown hereafter.

## 2.4.3.1 Read Energy Discussion

Figure 2.8 shows the breakdown of dynamic energy consumption for reads. Each bar is subdivided into five components and also normalized against baseline. The first bar "12" depicts the energy consumed by L2 cache fills and spills. Although the prediction actually occurs on L1 cache misses, the encoding schemes are also used for the transactions between the L2 and memory controller, based upon used-vector generated on the L1 cache miss the lead to the L2 miss.

The second bar shows the "used" energy, energy consumed by the words which will be referenced by the program, hence "used" bars are nearly equal, with the exception of a slight increase in energy due to router overheads in the dynamic scheme. The third bar, "unused", shows the energy consumed to bring in words which will not be referenced prior to eviction. This also includes the energy consumed by words which result from false-positive predictions, i.e. an incorrect prediction that the word will be used. The fourth bar, "overhead", shows the energy for NoC packet overheads, including header information and flow control bits. The fifth bar, "extra", shows the energy consumed by the packet overhead due extra cache line fills to correct "false-negative" mispredictions. Our goal is to remove, as much as possible, the dynamic datapath energy consumed by unused words denoted by unused and, where possible, the packet overheads in overhead, while minimizing redundant misses due to mispredictions in extra. Unused words consume an average of 33% of total dynamic datapath energy in case of blackscholes (shown as Black in the graphs.)

The d-combo scheme, on average, reduces total dynamic datapath energy by  $\sim 32\%$ . Our prediction mechanism combined with the encoding schemes approximately halves the "unused" portion, on average. In case of Black where the predictor

performs the best, the speculation mechanism removes 90% of the "unused" portion resulting in a 66% energy savings for cache fills when combined dynamic encoding is used. The extra transmission due to mispredictions, shown as "extra" in the stack, contributes less than 1% of energy consumption for cache fills.

# 2.4.3.2 Coherence Energy Discussion

In the simulated system coherence is maintained via the MESI protocol. Coherence protocol messages and responses represent a significant fraction of the network traffic. Those protocol messages are composed primarily of single-flit packets, and contribute  $\sim 28\%$  of total network energy consumption. Figure 2.9 shows the breakdown of dynamic energy consumption for coherence packets. Although these single-flit packets contain  $\sim 50\%$  unused data, as discussed in Section 2.3.2.1, static-encoding can not be used to reduce their energy dissipation. Dynamic-encoding, however, reduce it by up to 45.5%.

Figure 2.9: Dynamic energy breakdown for coherent packets

## 2.4.3.3 Write Energy Discussion

Figure 2.7 shows that writebacks consume an average of 13% of total dynamic energy. Upon dirty line writeback, we find that, on average, 40% of the words in the block are clean, and those words contribute 23% of the total energy consumed by writebacks.

Figure 2.10 shows the dynamic energy breakdown caused by writebacks. The first bar, "dirty", shows the energy consumed by the dirty words in cache lines. The second bar "overhead" shows the energy consumed by NoC packet overheads. The third bar, "clean", includes the link energy consumed by sending clean words in writeback packets. Our goal is to remove the portion of the energy consumption associated with transmitting "clean" words. On average, the s-combo scheme reduces the energy consumption due to writebacks by 29%. Further savings are achieved by d-combo. It encodes not only body/tail flits but also head flits of the writeback packets resulting in a 40% savings. When full swing links are used, it is possible to remove all of energy dissipation due to clean words with the static flit-encoding scheme. However, when static word repeat is used with low swing links, although clean words are encoded to repeat the words in the flit ahead, those words cause energy dissipation due to leakage currents and high sense amp power consumption on the receiver side.

Figure 2.10: Dynamic energy breakdown for writes

## 2.5 Analysis

In this section we analyze the performance impact of the proposed energy reduction technique, explore predictor training and compare against a 32-byte cache line baseline design.

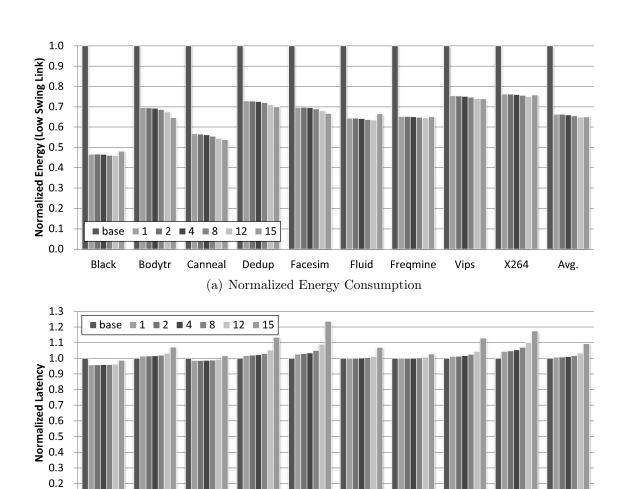

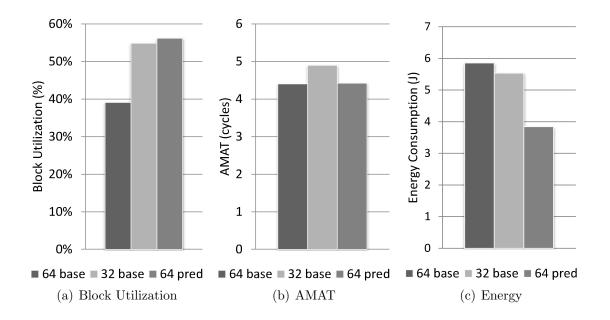

### 2.5.1 Performance