## ANALYSIS AND DESIGN OF NEW HARMONIC MITIGATION APPROACHES

A Dissertation

by

## EDDY CRISTIAN AELOIZA MATUS

## Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Committee Members,

Head of Department,

Prasad Enjeti Hamid Toliyat Aniruddha Datta Ben Zoghi Chanan Singh

December 2012

Major Subject: Electrical Engineering

Copyright 2012 Eddy Cristian Aeloiza Matus

### ABSTRACT

Numerous approaches have been proposed in order to resolve the problems of current harmonics in electrical distribution systems. The rapid development of power semiconductors along with the revolutionary advances on microprocessors consolidated the motor drives industry and with it a massive proliferation of non-linear loads. It was thought that these very same technological advances would trigger an explosive development of harmonic solutions based on power electronics. Moreover, the introduction of the instantaneous active and reactive power theory or the so-called p, q theory which simplifies and gives more robustness to the control strategies of active filters reinforced this idea. Three decades have passed since the first IGBT was introduced in early 1980s, and active harmonic solutions are not the first choice to solve harmonic pollution in electrical distribution systems, mainly due to the high cost and the perception of low reliability. Given this scenario, in this work two main approaches are explored. First, the combination of an asymmetric 18-pulse rectifier with a reduced KVA active harmonic filter to improve the performance under abnormal utility conditions. Second, an interleaved active harmonic filter using multiple inverters connected in parallel at the ac and dc size, which will allow for higher power ratings and power density increase.

The performance issues of the asymmetric 18-pulse rectifier under unbalanced voltage and pre-existing harmonic components are analyzed, as well as the current distortion improvement, achieved when an active power filter is introduced.

On the other hand, the high frequency harmonic cancellation when interleaved inverters are used, the circulation of zero-sequence current and the impact of interleaving on dc bus capacitor are analyzed. Finally, some methods to mitigate the low frequency circulating currents based on eliminating the zero-sequence component, and the introduction of common mode inductors to reduce the high frequency circulating current are studied.

Without a doubt the search for new cost-effective topologies able to reach broader power levels and voltage ranges will continue emerging giving more alternatives to users. Moreover, extensive research on wide band gap devices such as Silicon Carbide (SiC) and Gallium Nitride (GaN), with which it is possible to reach higher voltage breakdown and at least an order-of-magnitude lower switching losses, makes the future more promising for active solutions.

#### ACKNOWLEDGEMENTS

I would like to start this note giving my sincere gratitude to my advisor Dr. Prasad Enjeti for his support, encouragement and technical guidance throughout all these years. Also, to all the members of my committee, Dr. Hamid Toliyat, Dr. Aniruddha Datta and Dr. Ben Zoghi.

I would also like to thanks my parents Angelina and Alejandro, for all their support, encouragement and unconditional love.

To my wife Anna who for many years had to hear the story of finishing a PhD and patiently supported and trusted me, and proofread many of the paragraphs on this work. Also, to my little one Cristian, who patiently understood that, for many weekends, I could not play play-station with him.

Special thanks to Dr. Lucian Asiminoaei, Yamin Durrani, Rajesh Gopinath and Mark Rayner who help me during the implementation of this work.

To Dr. Leonardo Palma and Dr. Oscar Montero for their kindness and help during my arrival at College Station.

Finally, I cannot forget thanking the person who had shaped my professional life and inspired me, Dr. Luis Morán T.

## **TABLE OF CONTENTS**

| ABSTRACT                                                             |                                                                                                                                                                                                                                                                                         | ii                              |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| ACKNOWLE                                                             | EDGEMENTS                                                                                                                                                                                                                                                                               | V                               |

| TABLE OF C                                                           | CONTENTS                                                                                                                                                                                                                                                                                | v                               |

| LIST OF FIG                                                          | URES v                                                                                                                                                                                                                                                                                  | ii                              |

| LIST OF TAI                                                          | BLESxv                                                                                                                                                                                                                                                                                  | ii                              |

| CHAPTER                                                              |                                                                                                                                                                                                                                                                                         |                                 |

| I IN                                                                 | TRODUCTION                                                                                                                                                                                                                                                                              | 1                               |

| 1.<br>1.<br>1.<br>1.<br>1.<br>1.<br>1.                               | 1. Introduction         2. Power quality standards         3. Conventional current harmonic elimination solutions [23]         4. High pass filter [23]         5. Active harmonic filters (AHF)         6. Previous work         7. Research objective         8. Dissertation outline | 5<br>0<br>5<br>6<br>2<br>7      |

| FC<br>2.<br>2.<br>2.<br>2.<br>2.<br>2.<br>2.<br>2.<br>2.<br>2.<br>2. | NALYSIS OF CURRENT HARMONIC ELIMINATION SOLUTION         OR ADJUSTABLE SPEED DRIVES                                                                                                                                                                                                     | 1<br>2<br>5<br>9<br>3<br>4<br>7 |

# CHAPTER

| III    | ASYMMETRIC 18 PULSE RECTIFIER FOR ADJUSTABLE SPEED<br>DRIVE FRONT ENDS | 49      |

|--------|------------------------------------------------------------------------|---------|

|        | <ul> <li>3.1. Introduction</li></ul>                                   | 50<br>y |

|        | voltage disturbances                                                   |         |

| IV     | AN ACTIVE HARMONIC FILTER FOR AN ASYMMETRIC 18-PULS                    | E       |

|        | RECTIFIER FRONT END ADJUSTABLE SPEED DRIVE                             | 68      |

|        | 4.1. Introduction                                                      | 68      |

|        | 4.2. Active harmonic filter (AHF) design considerations                | 70      |

|        | 4.3. Control strategy                                                  |         |

|        | 4.4. Performance of 18-pulse rectifier with AHF                        | 78      |

|        | 4.5. Harmonics of 18-pulse rectifier under unbalanced and distortion   |         |

|        | 4.6. Experimental results                                              | 90      |

|        | 4.7. Conclusions                                                       | 97      |

| V      | AN INTERLEAVED THREE PHASE ACTIVE POWER FILTER WITH                    | I       |

|        | REDUCED SIZE OF PASSIVE COMPONENTS                                     | 99      |

|        | 5.1. Introduction                                                      | 99      |

|        | 5.2. Interleaved inverters for active power filtering                  |         |

|        | 5.3. Current ripple cancellation with interleaved inverters            |         |

|        | 5.4. Linkage inductor considerations                                   |         |

|        | 5.5. Analysis of circulation currents                                  |         |

|        | 5.6. Simulation results                                                |         |

|        | 5.7. Experimental results                                              |         |

|        | 5.8. Conclusions                                                       |         |

| VI     | CONCLUSIONS                                                            | 138     |

|        | 6.1. Conclusions                                                       | 138     |

|        | 6.2. Suggestions for future work                                       | 140     |

| REFERE | NCES                                                                   | 142     |

| APPEND | IX A                                                                   | 158     |

| APPEND | IX B                                                                   | 159     |

## LIST OF FIGURES

| FIGURE   | Page                                                                   |

|----------|------------------------------------------------------------------------|

| Fig. 1.  | Passive harmonic filter equivalent circuit11                           |

| Fig. 2.  | Tuned passive harmonic filter                                          |

| Fig. 3.  | Tuned passive harmonic filter and frequency response characteristic    |

| Fig. 4.  | a) High-pass passive harmonic filter and b) its frequency response     |

|          | characteristic                                                         |

| Fig. 5.  | a) High-pass (modified) passive harmonic filter and b) its frequency   |

|          | response characteristic16                                              |

| Fig. 6.  | Shunt active power filter conceptual circuit                           |

| Fig. 7.  | Conceptual visualization of a series active filter                     |

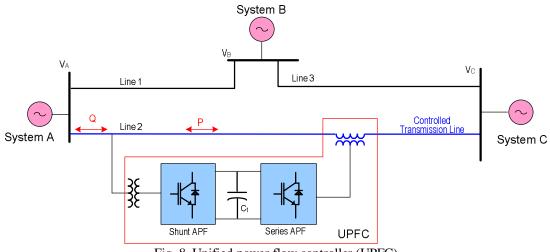

| Fig. 8.  | Unified power flow controller (UPFC)                                   |

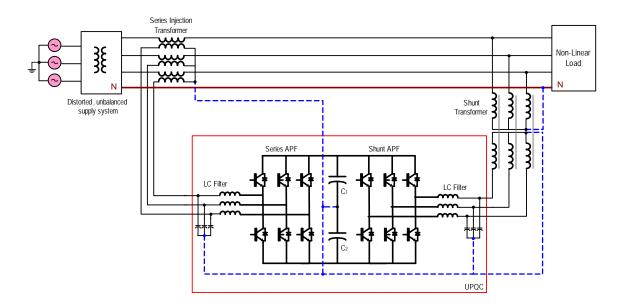

| Fig. 9.  | Unified power quality conditioner                                      |

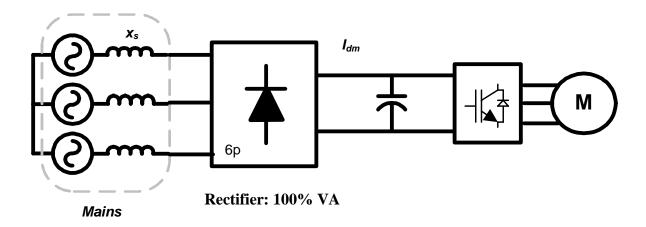

| Fig. 10. | Six pulse rectifier front end adjustable speed drive                   |

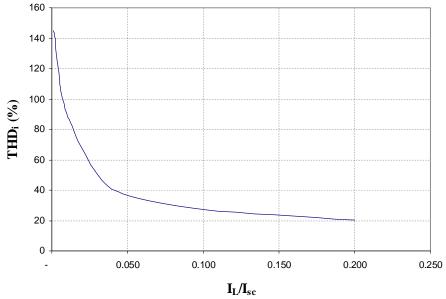

| Fig. 11. | Total harmonic distortion versus load current to short circuit current |

|          | ratio $(I_L/I_{sc})$                                                   |

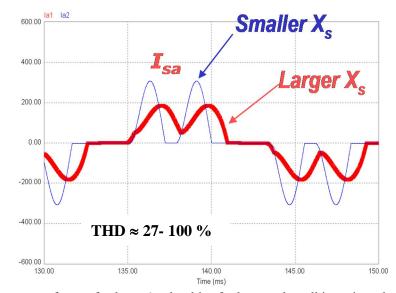

| Fig. 12. | Input current wave forms of voltage 6-pulse drive for large and small  |

|          | input impedance                                                        |

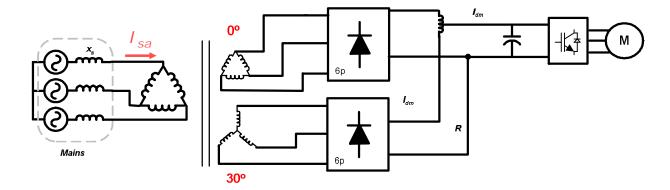

| Fig. 13. | 12-pulse rectifier front end adjustable speed drive                    |

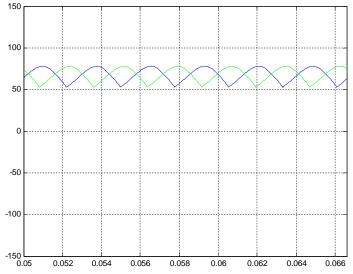

| Fig. 14. | 12-pulse rectifier. 6-pulse rectifier bridges dc output currents       |

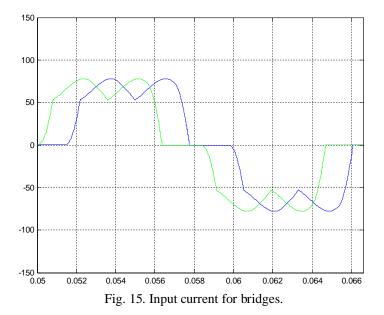

| Fig. 15. | Input current for bridges                                              |

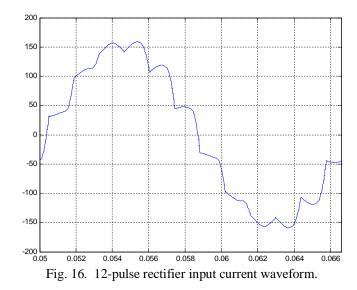

| Fig. 16. | 12-pulse rectifier input current waveform                                       |

|----------|---------------------------------------------------------------------------------|

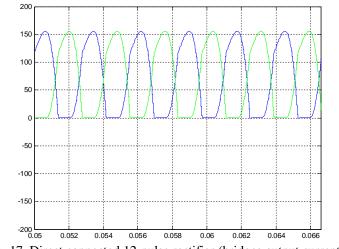

| Fig. 17. | Direct connected 12-pulse rectifier (bridges output currents)                   |

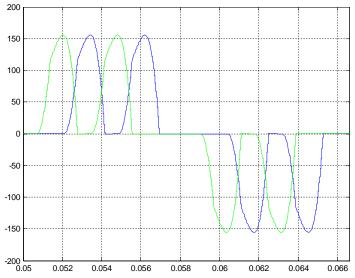

| Fig. 18. | Direct connection 12-pulse rectifier (bridges ac input waveforms)               |

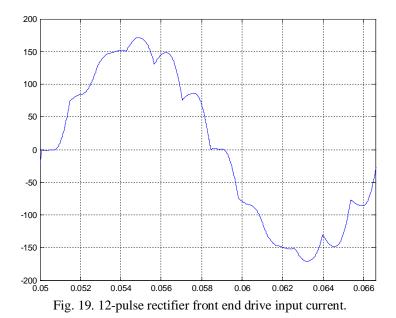

| Fig. 19. | 12-pulse rectifier front end drive input current                                |

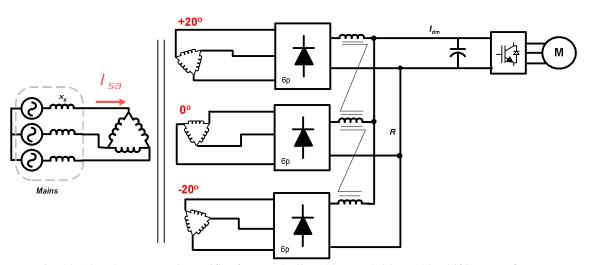

| Fig. 20. | 18-pulse symmetric rectifier front end adjustable speed drive. $\pm 20^{\circ}$ |

|          | shifting transformer                                                            |

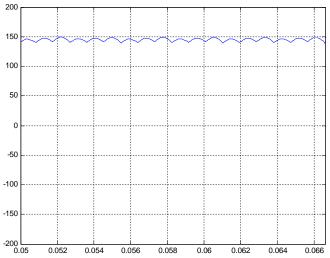

| Fig. 21. | 18-pulse rectifier, output dc current for one 60Hz cycle40                      |

| Fig. 22. | 18-pulse rectifier (direct dc connection), dc output current of each            |

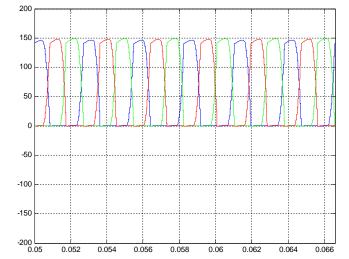

|          | bridge                                                                          |

| Fig. 23. | 18-pulse pulse rectifier, input ac current                                      |

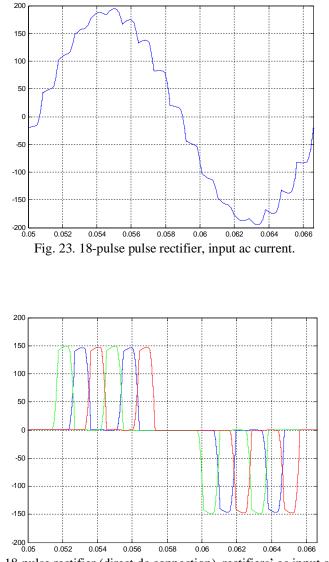

| Fig. 24. | 18-pulse rectifier (direct dc connection), rectifiers' ac input currents41      |

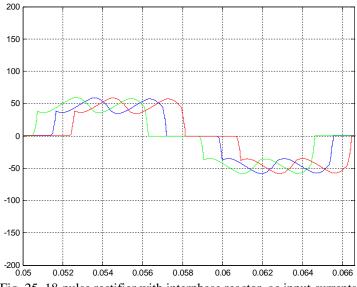

| Fig. 25. | 18-pulse rectifier with interphase reactor, ac input currents                   |

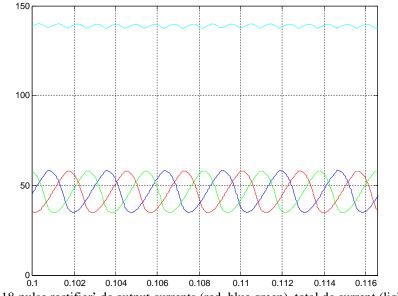

| Fig. 26. | 18-pulse rectifier' dc output currents (red, blue green), total dc current      |

|          | (light blue)                                                                    |

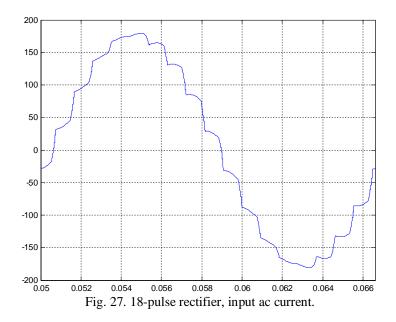

| Fig. 27. | 18-pulse rectifier, input ac current                                            |

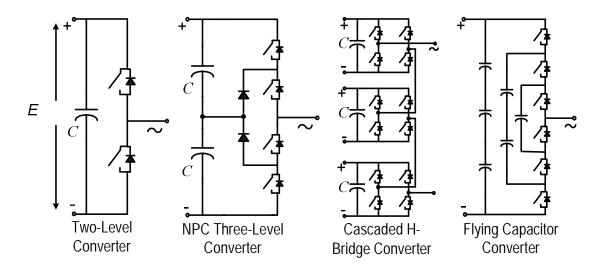

| Fig. 28. | Multilevel converter topologies                                                 |

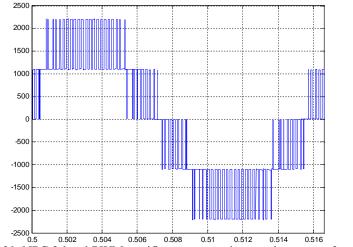

| Fig. 29. | NPC 3-level PWM rectifier, converter input voltage waveform                     |

| Fig. 30. | NPC 3-level PWM rectifier, converter input current waveform                     |

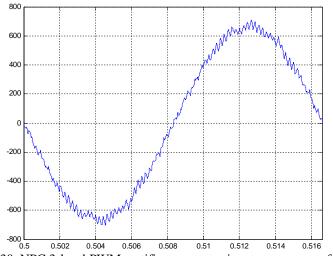

| Fig. 31. | MIRUS lineator harmonic filter [102]48                                          |

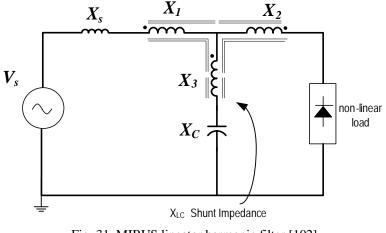

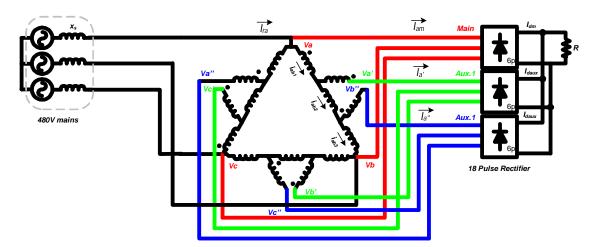

| Fig. 32. | Asymmetric 18-pulse rectifier with resistive load [33]50                        |

Page

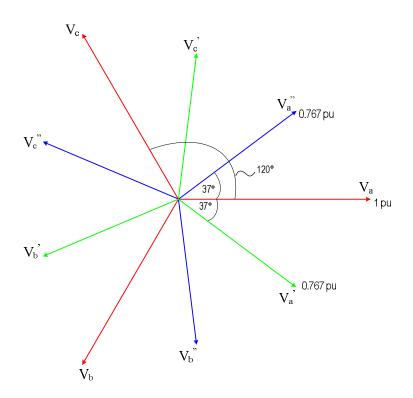

| Phasor diagram of the asymmetric 18-pulse rectifier                                          |

|----------------------------------------------------------------------------------------------|

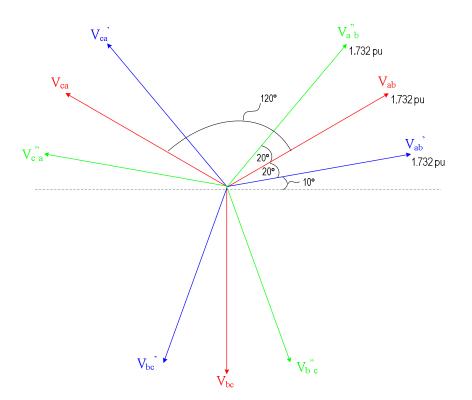

| Phasor diagram of voltage requires for 18-pulse rectification53                              |

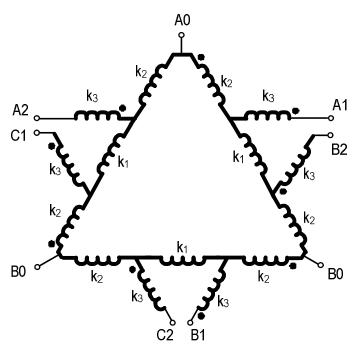

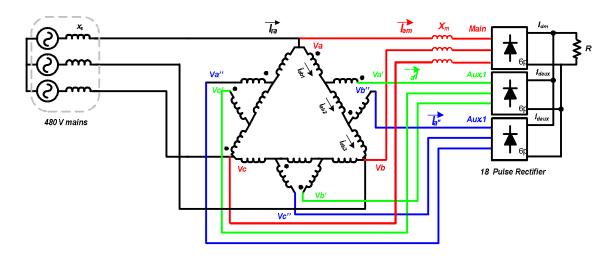

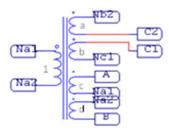

| Autotransformer for asymmetric 18-p rectifier [33]54                                         |

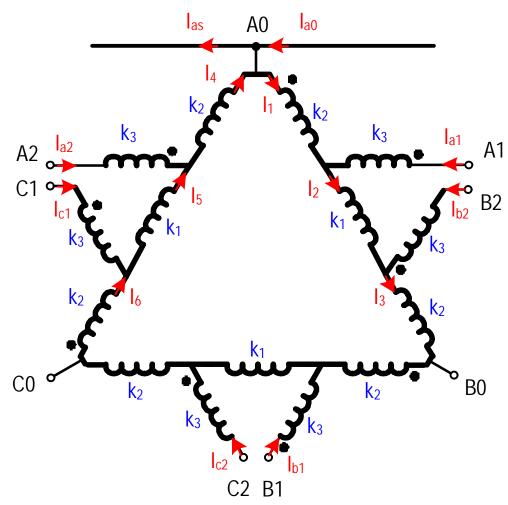

| 18-pulse autotransformer and currents flow detail [33]                                       |

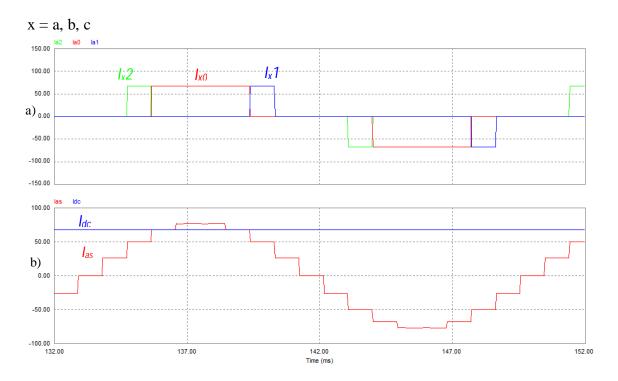

| a) Main and auxiliary rectifiers' current, b) output dc $I_{dc}$ current and                 |

| overall input current <i>I<sub>as</sub></i>                                                  |

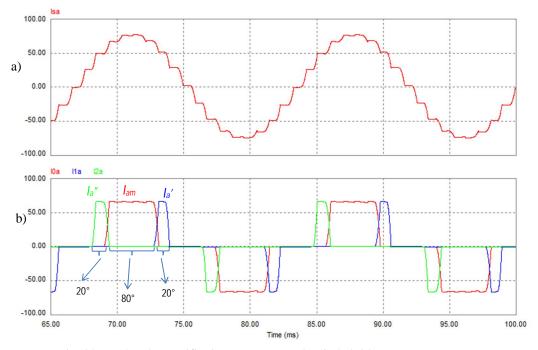

| a) 18-pulse rectifier input current $I_{ra}$ , b) diode bridges currents $I_{am}$ , $I_a$ ', |

| <i>I</i> <sub>a</sub> ".59                                                                   |

| Asymmetric 18-pusle rectifier with balancing reactor X <sub>m</sub> 60                       |

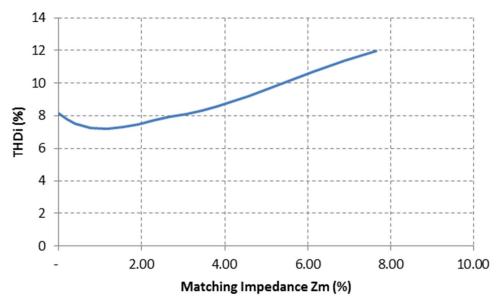

| Asymmetric 18-p rectifier input THDi vs. matching impedance $Z_m$                            |

| (%)61                                                                                        |

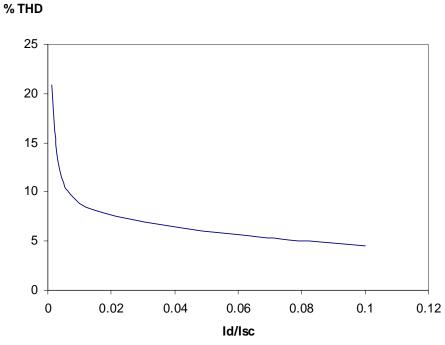

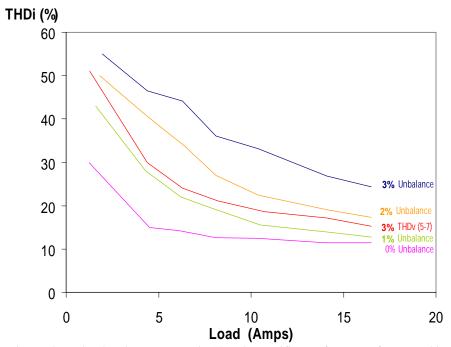

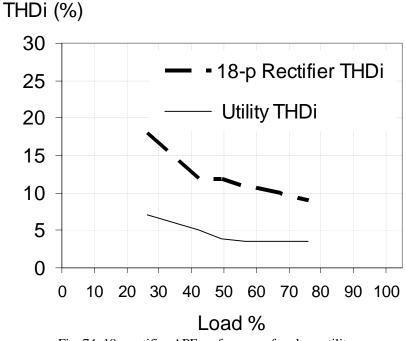

| Asymmetric 18-pulse rectifier input THD <sub>i</sub> vs. $I_d/I_{sc}$ ratio                  |

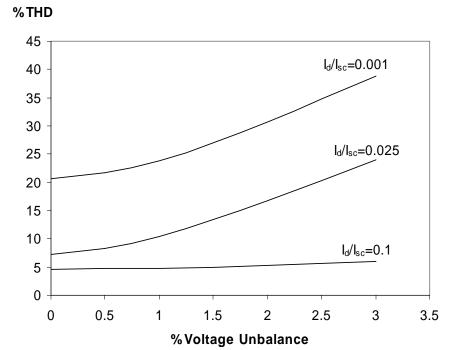

| Asymmetric 18-p rectifier THD <sub>i</sub> vs. % voltage unbalance for different             |

| I <sub>d</sub> /I <sub>sc</sub> rates                                                        |

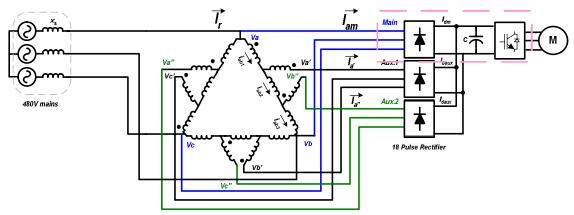

| Asymmetric autotransformer 18 pulse rectifier adjustable speed drive 64                      |

| 18p rectifier input current under clean power supply. a) only resistive                      |

| load in dc bus b) LC filter in dc bus                                                        |

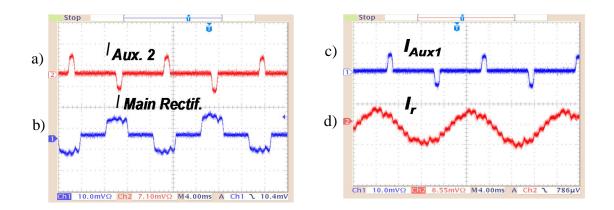

| 18p rectifier currents under clean power supply. a) current  auxiliary                       |

| rectifier-2. b) main rectifier's current c) current auxiliary rectifier-1 d)                 |

|                                                                                              |

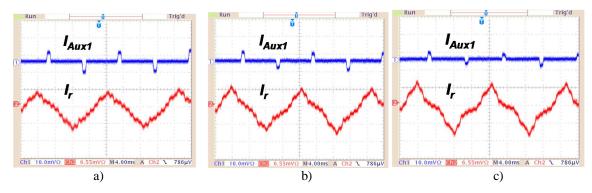

| Fig. 46. | a) 18 pulse rectifier current under 1% input unbalance: auxiliary         |

|----------|---------------------------------------------------------------------------|

|          | rectifier input current (blue) and rectifier's input current (red), b) 18 |

|          | pulse rectifier current under 2% input unbalance: auxiliary rectifier     |

|          | input current (blue) and rectifier's input current (red), c) 18 pulse     |

|          | rectifier current under 3% input unbalance: auxiliary rectifier input     |

|          | current (blue) and rectifier's input current (red)                        |

| Fig. 47. | Experimental results showing asymmetric 18-pulse rectifier                |

|          | performance for several input voltage conditions [40]66                   |

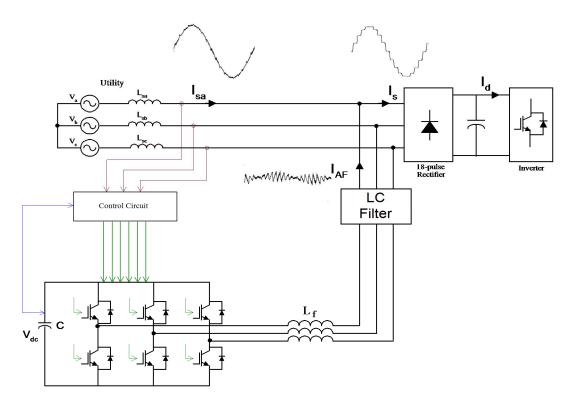

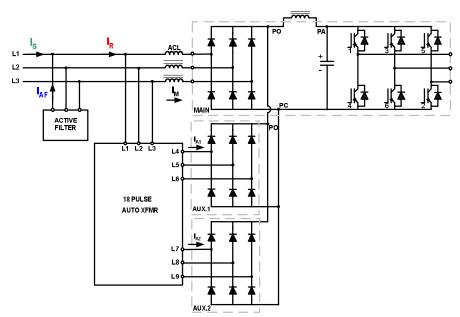

| Fig. 48. | 18-pulse rectifier with active power filter compensation                  |

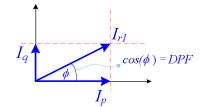

| Fig. 49. | Rectifier's fundamental current phasor diagram74                          |

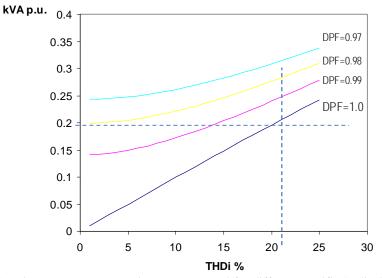

| Fig. 50. | APF kVA rating versus compensating current THDi for different             |

|          | rectifier's displacement power factor (DPF)75                             |

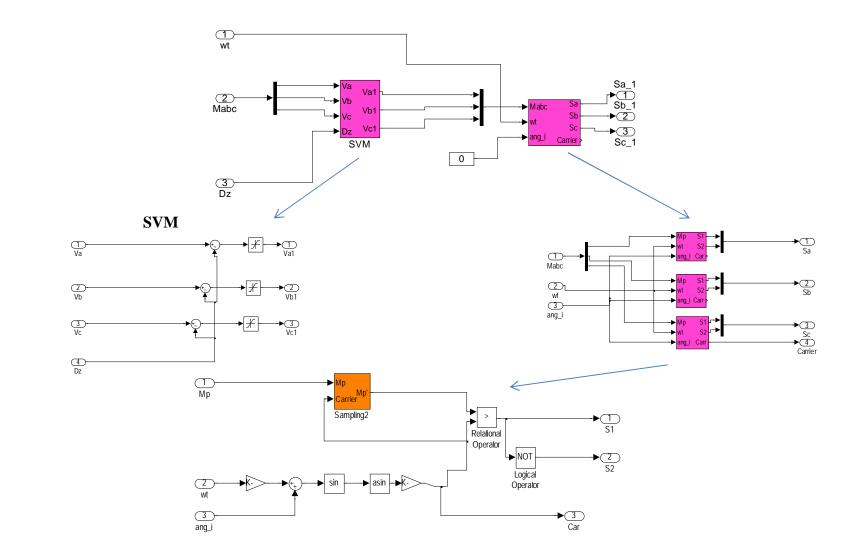

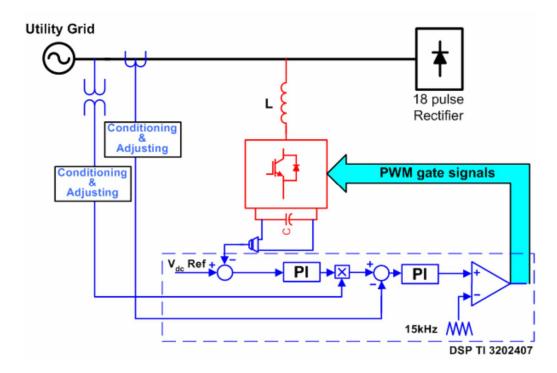

| Fig. 51. | Active Power Filter's control block scheme77                              |

| Fig. 52. | 18-Pulse Autotransformer Rectifier PSIM model79                           |

| Fig. 53. | 18-pulse rectifier PSIM model                                             |

| Fig. 54. | PSIM model – APF IGBT 2-Level converter                                   |

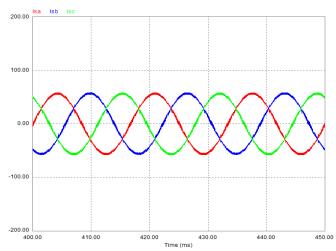

| Fig. 55. | 18-p rectifier w/APF simulation results for ideal input voltage           |

|          | conditions. Total input currents (top). APF's DC bus voltage (bottom) 82  |

| Fig. 56. | 18-p rectifier w/APF simulation results for ideal input voltage           |

|          | conditions. Total input currents in steady state                          |

| Page |

|------|

|------|

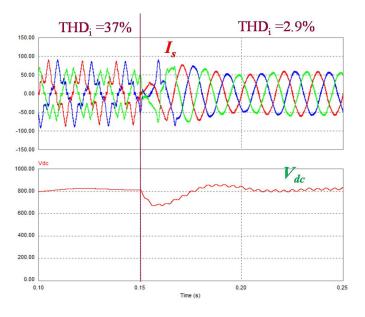

| Fig. 57. | 18-p rectifier w/APF simulation results for 2.5% 5 <sup>th</sup> harmonic voltage |      |

|----------|-----------------------------------------------------------------------------------|------|

|          | distortion. Total input currents (top). APF's DC bus voltage (bottom)             | . 83 |

| Fig. 58. | 18-p rectifier w/APF simulation results for 2.5% 5 <sup>th</sup> harmonic voltage |      |

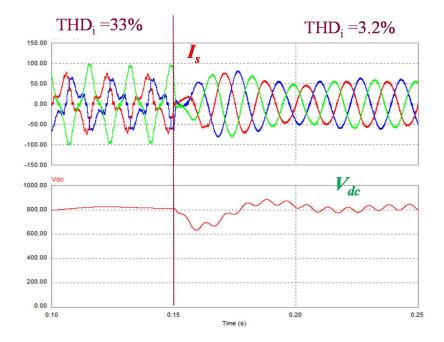

|          | distortion. Total input currents in steady state.                                 | . 84 |

| Fig. 59. | 18-p rectifier w/APF simulation results for 3% input voltage                      |      |

|          | unbalance. Total input currents (top). APF's DC bus voltage (bottom)              | . 85 |

| Fig. 60. | 18-p rectifier w/APF simulation results for 3% input voltage                      |      |

|          | unbalance. Total input currents in steady state.                                  | . 85 |

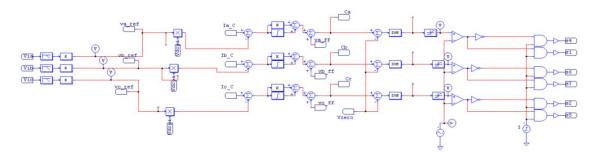

| Fig. 61. | PSIM model - APF's current controllers.                                           | . 86 |

| Fig. 62. | PSIM model – 18-pulse asymmetric rectifier w/APF.                                 | . 87 |

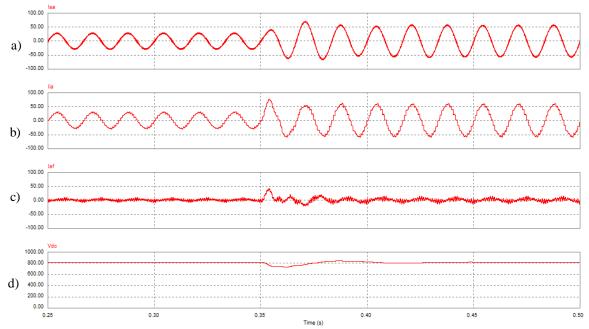

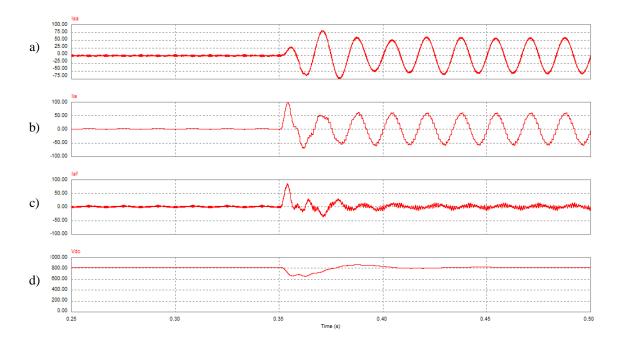

| Fig. 63. | Simulation results for 50% to 100% change in the load operating                   |      |

|          | condition a)Total input current b) Rectifier input current c) APF                 |      |

|          | current d) APF dc link voltage.                                                   | . 88 |

| Fig. 64. | Simulation results for 0% to 100% change in the load operating                    |      |

|          | condition a)Total input current b) Rectifier input current c) APF                 |      |

|          | current d) APF dc link voltage.                                                   | . 89 |

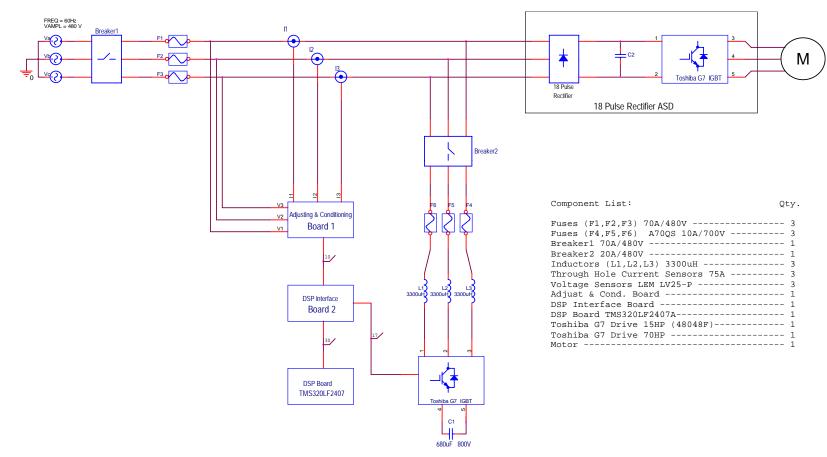

| Fig. 65. | Asymmetric autotransformer 18-pulse rectifier and active filter                   |      |

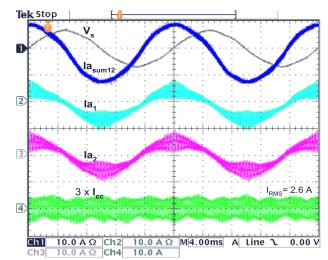

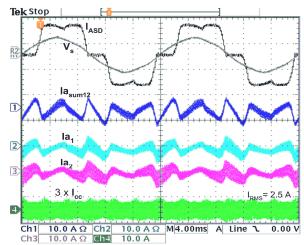

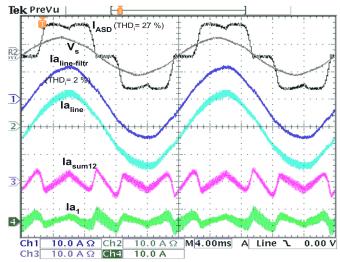

|          | experimental set up                                                               | . 90 |

| Fig. 66. | Active filter starting operation instant.                                         | . 91 |

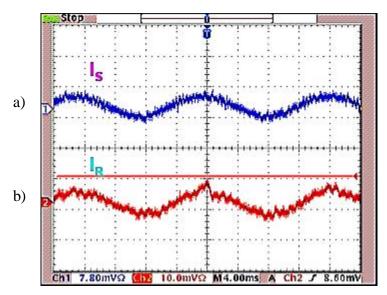

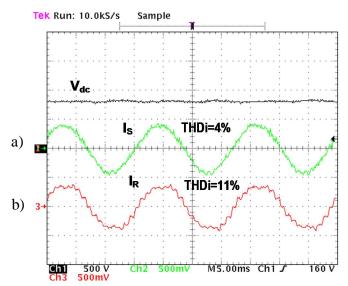

| Fig. 67. | a) Input supply current b)18-P rectifier input current                            | . 92 |

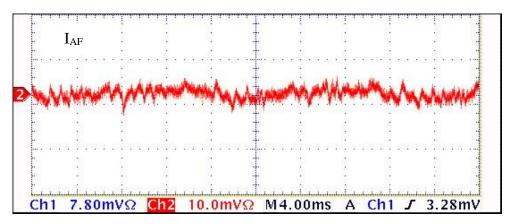

| Fig. 68. | Active Power Filter current                                                                   |

|----------|-----------------------------------------------------------------------------------------------|

| Fig. 69. | APF performance for ideal voltage supply conditions. a) Input supply                          |

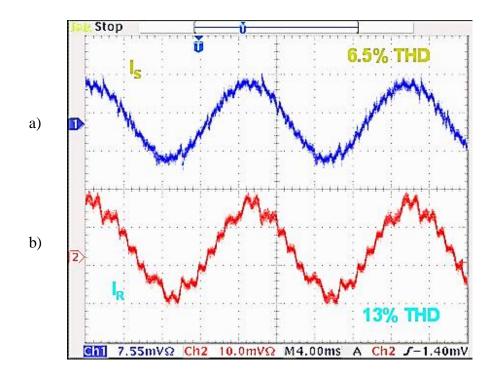

|          | current. b) Rectifier's input current                                                         |

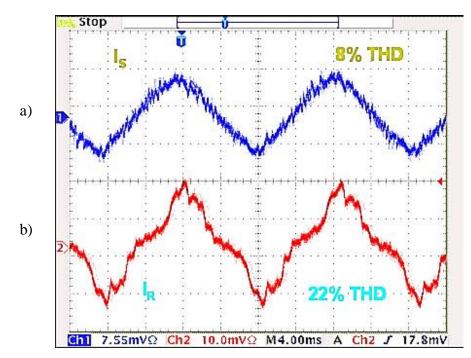

| Fig. 70. | APF performance for 2% voltage unbalance a) Input supply current.                             |

|          | b) Rectifier's input current94                                                                |

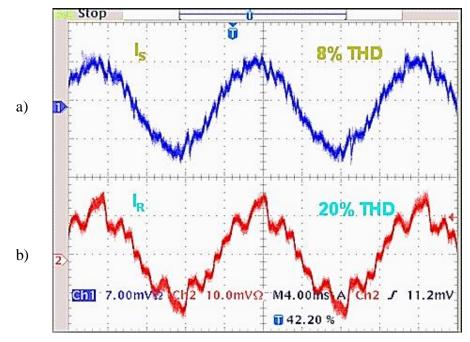

| Fig. 71. | APF performance for voltage harmonic distortion 5th (3%) & 7th                                |

|          | (2%). a) Input supply current. b) Rectifier's input current                                   |

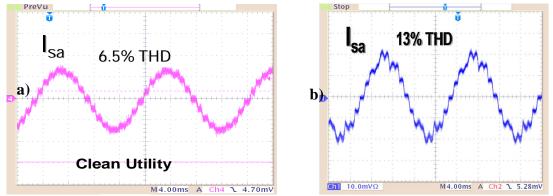

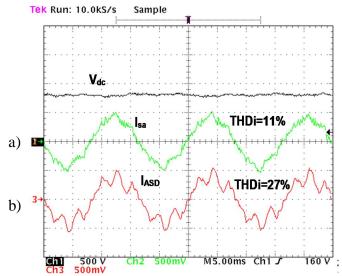

| Fig. 72. | Rectifier-APF's input current for clean utility. a) with active                               |

|          | compensation b) without active compensation                                                   |

| Fig. 73. | Rectifier-APF's input current for distorted utility. a) with active                           |

|          | compensation b) without active compensation                                                   |

| Fig. 74. | 18p rectifier-APF performance for clean utility97                                             |

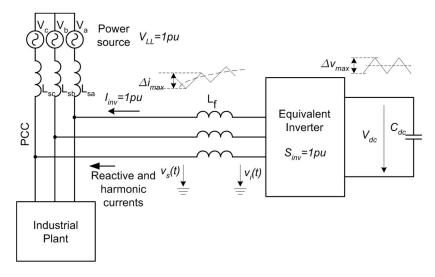

| Fig. 75. | Principle of paralleling multiple power inverters for a shunt active                          |

|          | power filters                                                                                 |

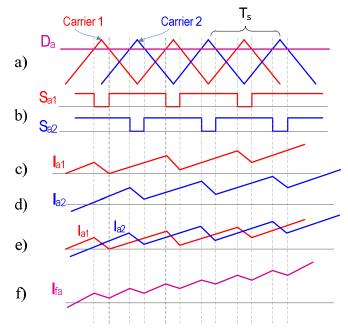

| Fig. 76. | Interleaved Active Power Filter with two inverters                                            |

| Fig. 77. | Conventional parallel active power filter with isolation transformer                          |

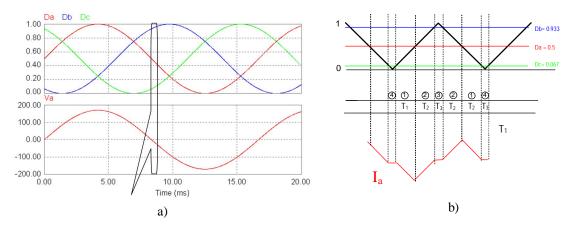

| Fig. 78. | Instantaneous interleaving signals. a) Triangle carriers and modulator                        |

|          | b) Inverter's IGBTs Sa1 and Sa2 gating signals. c) Inverter 1 input                           |

|          | current, $I_{a1}$ . d) Inverter 2 input current $I_{a2}$ . e) Inverter input current $I_{a1}$ |

|          | and $I_{a2}$ . f) Aggregate input current: sum of $I_{a1}$ and $I_{a2}$                       |

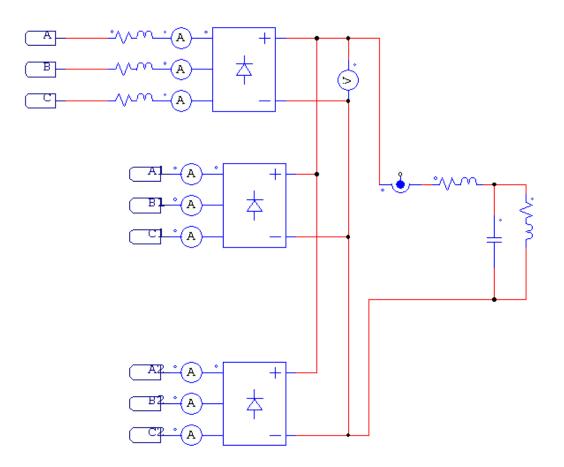

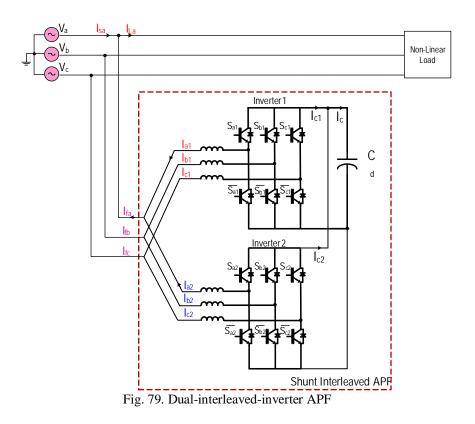

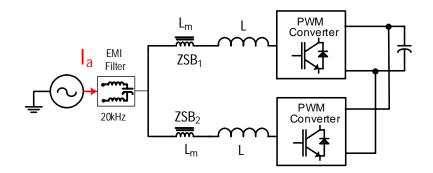

| Fig. 79. | Dual-interleaved-inverter APF                                                         |

|----------|---------------------------------------------------------------------------------------|

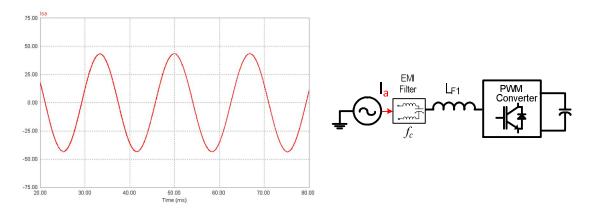

| Fig. 80. | Active power filter compensating reactive power with single inverter 105              |

| Fig. 81. | Active power filter compensating reactive power with two interleaved                  |

|          | inverters                                                                             |

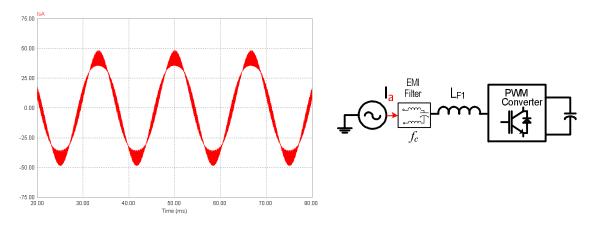

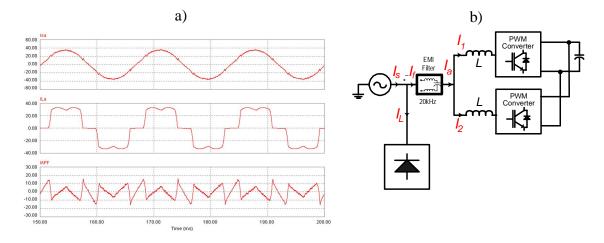

| Fig. 82. | Dual-interleaved-inverter APF structure compensating a six pulse non-                 |

|          | linear load. a) Top to bottom. Source current $I_s$ , load current $I_L$ , APF's      |

|          | current I <sub>f</sub> . b) APF single line diagram                                   |

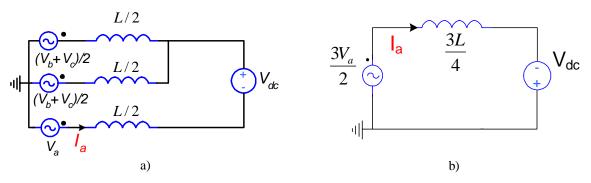

| Fig. 83. | Detail of APF compensating current. a) APF Currents i) Inverter                       |

|          | currents $I_1$ and $I_2$ , ii) Aggregate inverters' current $I_a$ . iii) APF filtered |

|          | current $I_f$ . b) Zoom on Fig. 83.a.i) - inverters' current $I_1$ and $I_2$ 107      |

| Fig. 84. | Illustration of design criteria for the APF108                                        |

| Fig. 85. | Inverter states when the maximum current ripple occurs. Single                        |

|          | inverter case. a) Instantaneous duty cycles and phase-A voltage to                    |

|          | ground. b) Detail of the duty cycles and triangle carrier (top).                      |

|          | Inverter's Phase-A current (bottom)110                                                |

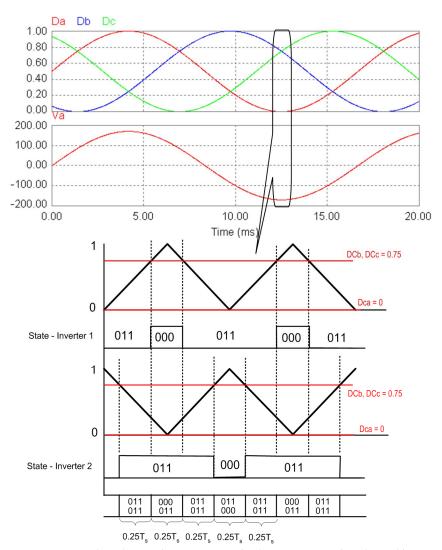

| Fig. 86. | Inverter states when the maximum current ripple occurs. Two                           |

|          | interleaved inverters case                                                            |

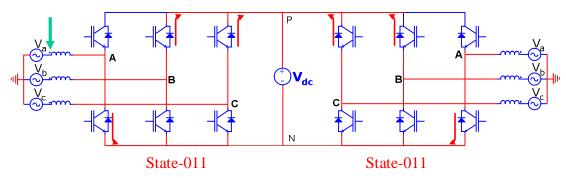

| Fig. 87. | Interleaved inverters model. State 011 on inverter 1 and 2 113                        |

| Fig. 88. | Interleaved inverters equivalent circuit                                              |

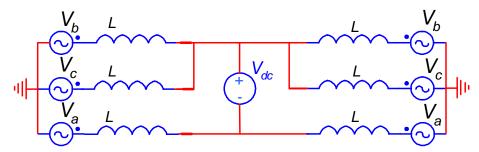

| Fig. 89.  | a) Simplified diagram of the APF with 2 interleaved inverters. b)                  |

|-----------|------------------------------------------------------------------------------------|

|           | Equivalent circuit for the current in phase-a                                      |

| Fig. 90.  | Entire 60Hz cycle for the total APF current. a) Non-interleaved case.              |

|           | b) Interleaved case116                                                             |

| Fig. 91.  | Instant when the maximum current ripple $\Delta i$ occurs. a) Non-                 |

|           | interleaved case b) Interleaved case 116                                           |

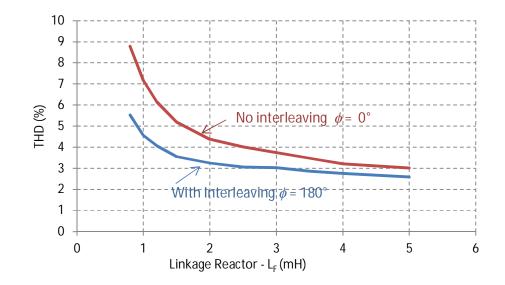

| Fig. 92.  | Input Current THD vs. L <sub>F</sub> with and without interleaving 117             |

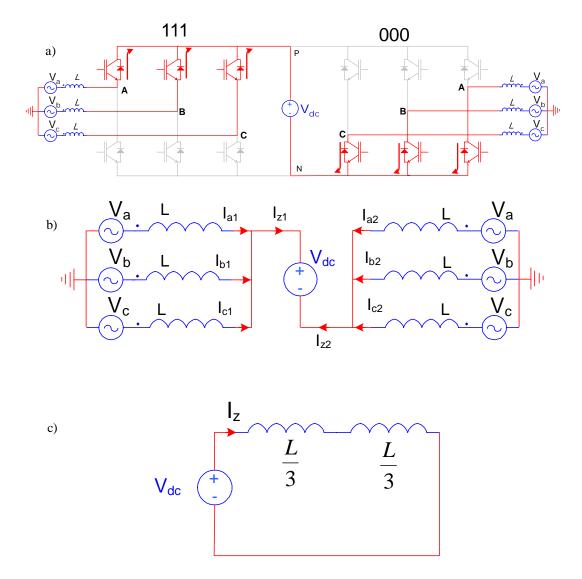

| Fig. 93.  | Equivalent circuit and current path for the zero-sequence current. a)              |

|           | Inverters' zero-sequence current path. b) Inverter equivalent circuit. c)          |

|           | Thevenin's equivalent circuit                                                      |

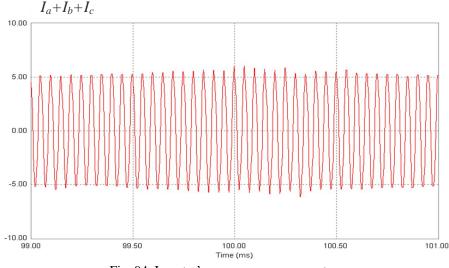

| Fig. 94.  | Inverter's zero-sequence current                                                   |

| Fig. 95.  | Common-mode choke – VAC [103] 121                                                  |

| Fig. 96.  | Interleaved APF with common mode choke (ZBS-zero sequence                          |

|           | blocker)                                                                           |

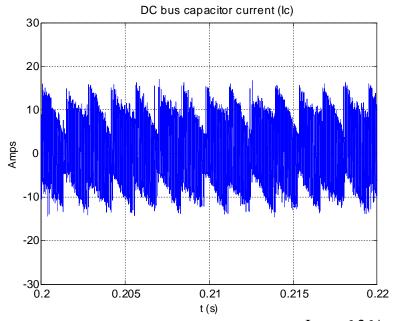

| Fig. 97.  | APF dc bus capacitor current Ic with interleaving. $I_{c_{rms}}$ =6.26A122         |

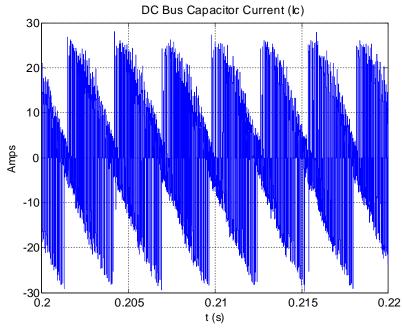

| Fig. 98.  | APF dc bus capacitor current Ic without interleaving. $I_{c_{rms}}=11.39A123$      |

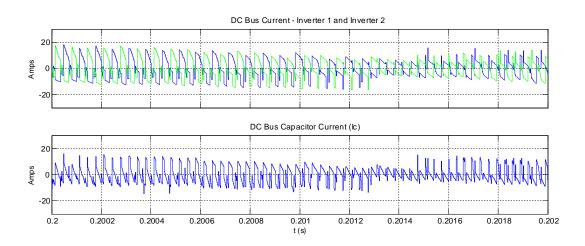

| Fig. 99.  | Inverters dc currents $I_{c1}$ and $I_{c2}$ (top). Dc bus capacitor current Ic 123 |

| Fig. 100. | Harmonic spectrum of dc capacitor current for Single inverter APF ( $f_{sw}$       |

|           | =15 kHz)                                                                           |

Page

| Page |

|------|

|------|

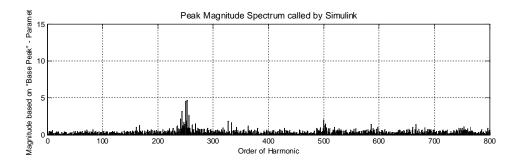

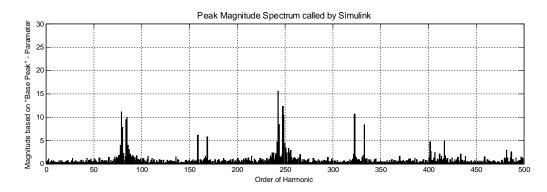

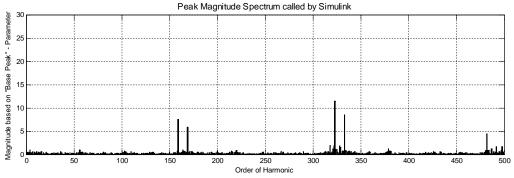

| Fig. 101. | Harmonic spectrum of dc capacitor current for dual-Interleaved-              |

|-----------|------------------------------------------------------------------------------|

|           | inverter structure ( $f_{sw}$ =15 kHz)                                       |

| Fig. 102. | Harmonic spectrum of dc capacitor current for Single inverter APF ( $f_{sw}$ |

|           | =4920Hz). Ic_rms=1 p.u125                                                    |

| Fig. 103. | Harmonic spectrum of dc capacitor current for dual-interleaved-              |

|           | inverter structure ( $f_{sw}$ =4920Hz). Ic_rms=0.5p.u                        |

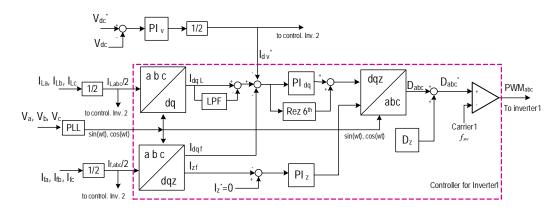

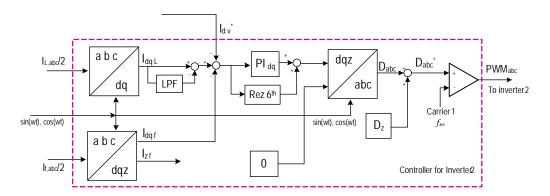

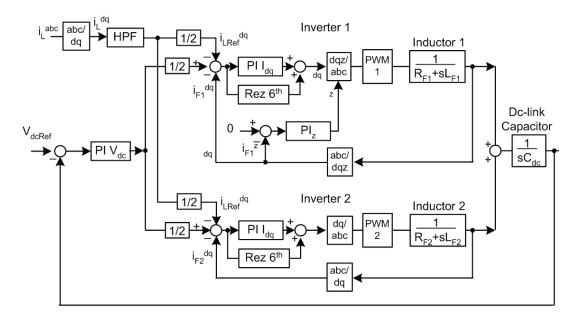

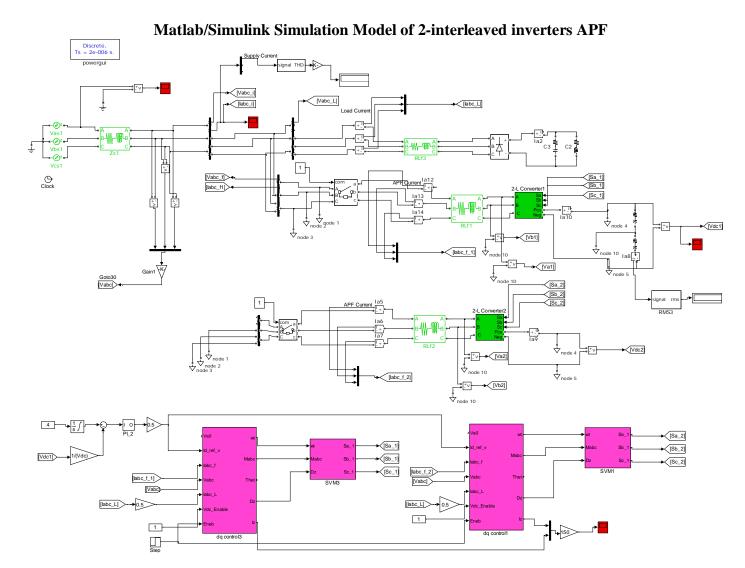

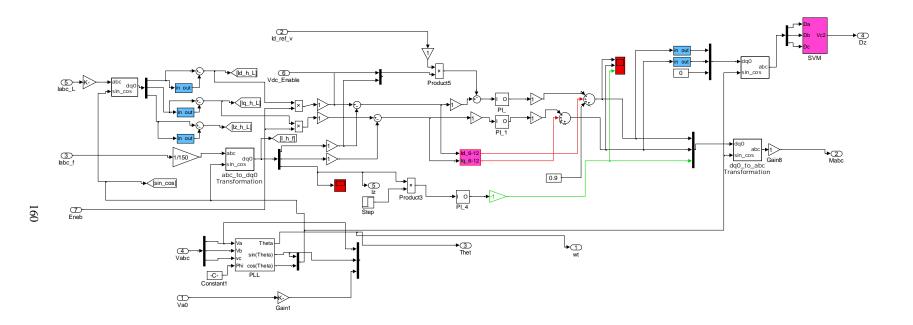

| Fig. 104. | Control block diagram for interleaved inverter 1                             |

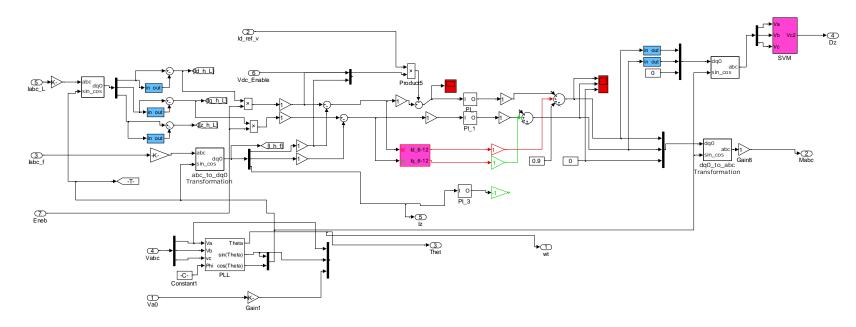

| Fig. 105. | Control block diagram for interleaved inverter 2 126                         |

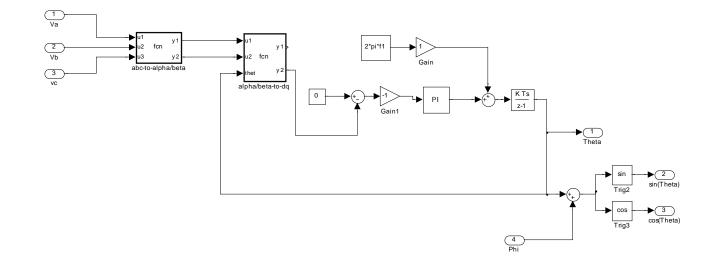

| Fig. 106. | Park's transform                                                             |

| Fig. 107. | Inverse Park's transform                                                     |

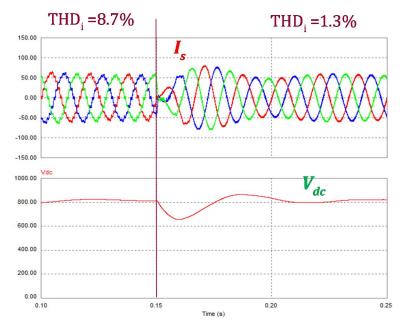

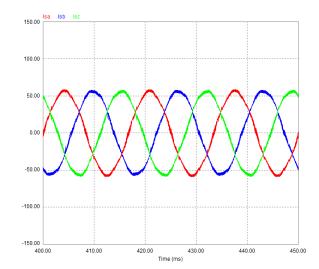

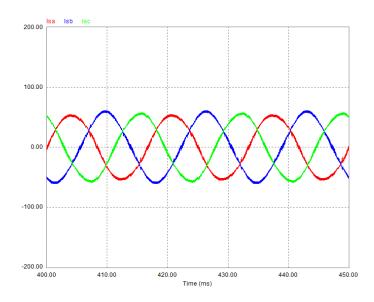

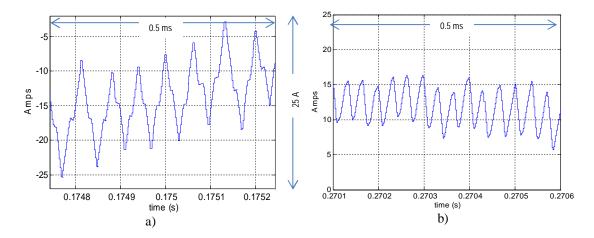

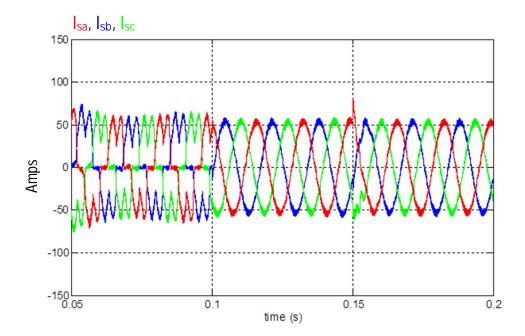

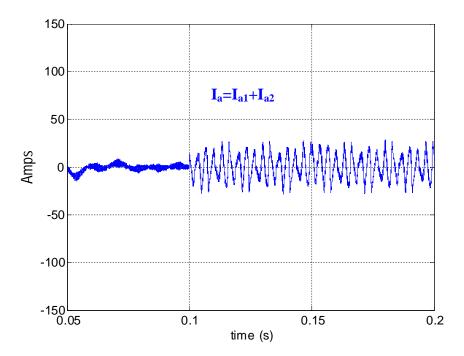

| Fig. 108. | Input current waveforms for APF compensation with two interleaving           |

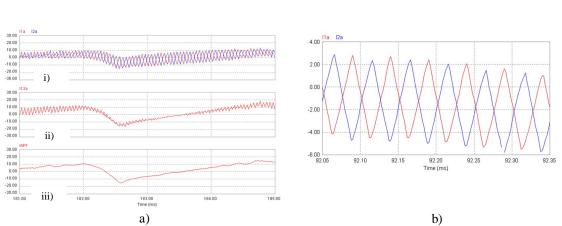

|           | inverters. Compensation starts at 0.1s                                       |

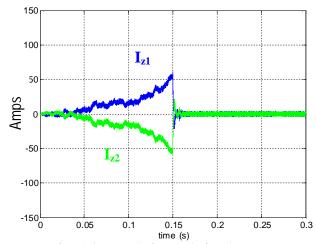

| Fig. 109. | Zero sequence currents of each inverter before and after the zero            |

|           | sequence controller starts (at 0.15s)                                        |

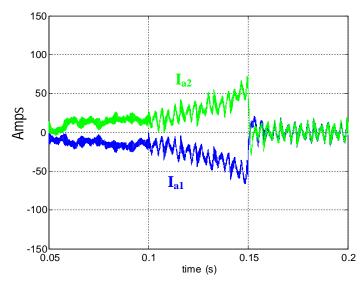

| Fig. 110. | Compensating APF currents ( $I_{f_a1}$ and $I_{f_a2}$ ). Before and after    |

|           | compensation130                                                              |

| Fig. 111. | Interleaved APF's filter total current                                       |

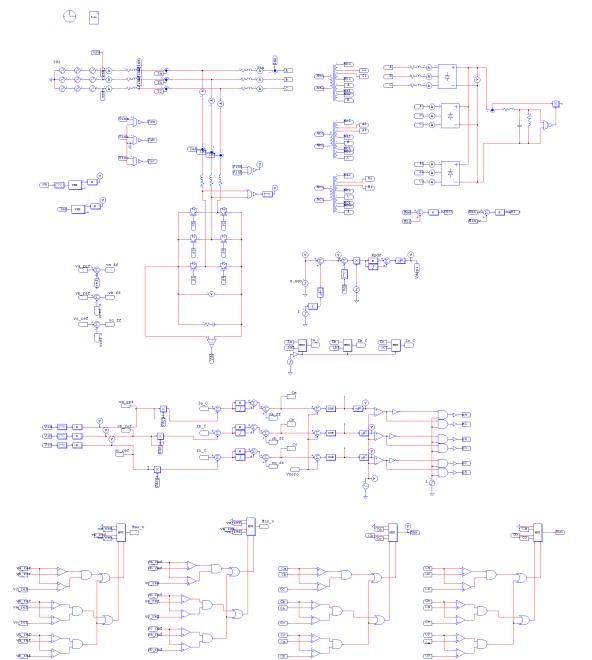

| Fig. 112. | Control scheme for dual interleaved inverters                                |

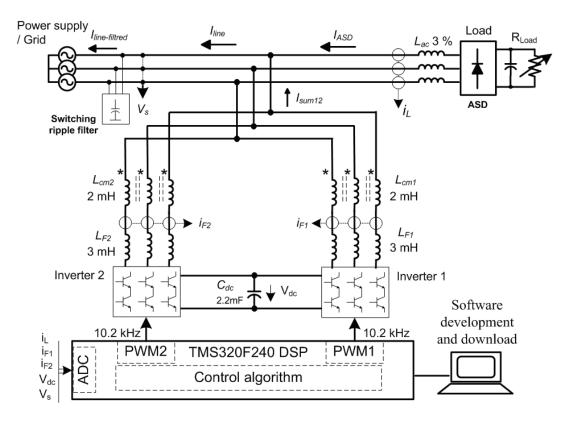

| Fig. 113. | Lab setup for interleaved inverters based APF                                |

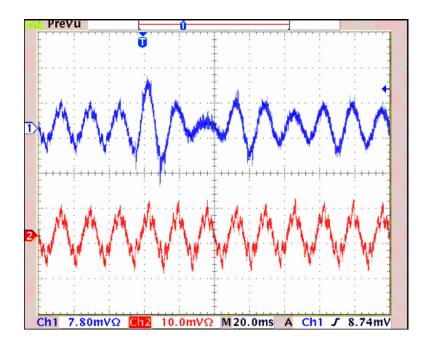

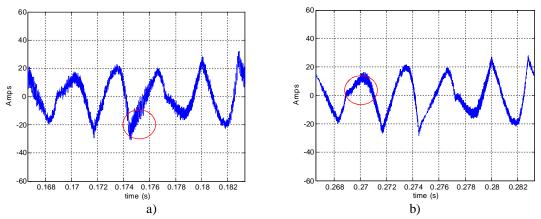

| Fig. 114. | Without a common mode coil. Sinusoidal current reference                     |

# FIGURE

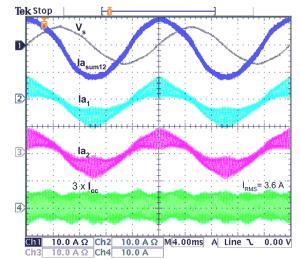

| Fig. 115. | With a common mode. Sinusoidal current reference coil of 2mH        | . 135 |

|-----------|---------------------------------------------------------------------|-------|

| Fig. 116. | APF current for harmonic compensation. With a common mode           |       |

|           | Harmonic current reference coil of 2mH                              | . 135 |

| Fig. 117. | Measured waveforms. APF efficiency of reducing the switching ripple |       |

|           | by interleaving two inverters                                       | . 136 |

## LIST OF TABLES

| TABLI | E                                                                              | Page |

|-------|--------------------------------------------------------------------------------|------|

| Ι     | Low-Voltage Systems Classification and Distortion Limits for 460V              |      |

|       | Systems [67].                                                                  | 6    |

| II    | Voltage distortion Limits for Medium and High Voltage Power                    |      |

|       | Systems [67]                                                                   | 6    |

| III   | Current Distortion Limits for General Distribution Systems (120V               |      |

|       | Through 69,000 V) [68]                                                         | 8    |

| IV    | Voltage Distortion Limits [68]                                                 | 8    |

| V     | Review of IEC 61000-3-4 (First Edition 1998-10) <sup>1</sup> [72]              | 10   |

| VI    | Active Filter Simulation Parameters                                            | 78   |

| VII   | Values of the input parameters used in design.                                 | 108  |

| VIII  | Current ripple $\Delta i$ for each state in a single inverter                  | 110  |

| IX    | Current ripple $\Delta i$ for a single INVERTER evaluated at V <sub>a</sub> =0 | 111  |

| Х     | Single and 2-parallel inverter comparison parameters                           | 115  |

## **CHAPTER I**

### INTRODUCTION

## **1.1. Introduction**

Significant advances on power semiconductors and microprocessors enabled the massive proliferation of motor drives and switching power supplies in the 1980s and early 1990s. Concurrently, harmonics problems raised serious concerns among electrical engineers. Overheating of transformers and cables, failure of capacitor banks due to resonance and interference with telecommunication systems were common symptoms of distributions systems overloaded with current harmonics [1]-[13]. Excessive third harmonic current was also frequently observed on the neutral conductors of commercial buildings as a result of multiple single phase power supplies [14]-[17].

Extensive research has been conducted and multiple approaches to reduce current harmonics have been proposed, developed and commercialized over the years. Ones are based on increasing the tolerance of existing electric devices to withstand harmonics currents such as K-rated transformers, and increased cross section of neutral conductors [18]-[21]. Others are based on eliminating or reducing the circulation of current harmonics. Amongst the latter, are passive tuned filters and power electronics based converters such as multi-pulse rectifiers, active front end converters and active harmonic filters. Passive filters or harmonic traps are cost effective and can provide an acceptable current harmonic cancellation however, they are bulky, heavy, can introduce resonance in the power system and can only be tuned to effectively cancel a single harmonic. Therefore multiple filters have to be installed in order to eliminate more than one harmonic [22].

Multi-pulse rectifiers are based on the principle of harmonic cancellation through phase shifting and are the preferred solution to eliminate harmonics in high power converters in large motor drives, electro-winning rectifiers and HVDC transmission systems [23]-[37]. However, they need bulky phase shifting transformers and are usually used in conjunction with passive filters to eliminate the rest of harmonics that the multipulse rectifier is not able to cancel out [38], [39].

Active solutions - power electronics approaches based on hard switching semiconductors are a viable solution which presents a better alternative when weight and footprint is a constraint. Among them are active front ends (AFE) or active PWM rectifiers [40], active harmonics filter (AHF) or also called active power filters (APF) [41]-[60]. Active power filters are usually classified depending on the way they are connected to the electric system and are divided in shunt APFs and series APFs [60]. Furthermore, hybrid APFs; approaches based on a combination of a passive tuned filter and a reduced KVA APF have been extensively studied [61]-[66].

Hard switching active power filters are practically only used in very special cases, usually at very large horsepower ratings or when size and footprint constrains prohibit the utilization of bulky passive solutions. This is the case of oil offshore platforms, marine vessels and more recently, aircrafts. However, the majority of active power filters on transmission and distribution systems are for reactive power compensation and not for harmonics mitigation. For industrial distribution systems the situation is similar, large rectifying plant for electro-winning or electro-refinery still prefer passive solutions [22]. A similar scenario occurs in compensating harmonics for adjustable speed drives, the preferred solution is either a passive filter or a drive furnished with a multi-pulse diode rectifier.

Moreover, active solutions offer higher flexibility, high performance over a large zone of operating conditions and they guarantee high reliability due to state-of-the-art semiconductors. However, at large horse power rating and at medium voltage the present technology on hard switching devices do not allow operating at high switching frequencies necessary to guarantee the reconstruction of the harmonics to mitigate. This is the main drawback of active solutions which forces the utilization of cutting edge switching devices and complex control strategies which consequentially make them more expensive and in some cases incapable to be a viable solution for very large horse power ratings.

In this work two approaches will be studied, which can serve, in part, to fill the gap for lack of semiconductor devices capable of switching at high switching frequencies with low losses and that guarantee high performance for large APFs. The first one is a combination of an asymmetric 18-pulse rectifier with a reduced KVA active harmonic filter to mitigate harmonics at the front end of adjustable speed drives [37]. The asymmetric 18-pulse rectifier guarantees low harmonic injection for great portion of

operating conditions. It is highly reliable since not active components are present and allows for reduced footprint and lighter weight than conventional 18-pulse rectifiers since a fractionally rated autotransformer is used. However, this topology evidences some drawbacks in the presence of abnormal input voltage conditions such as; voltage unbalance and pre-existing harmonic distortion - the theoretical harmonic injection profile is deteriorated. A shunt APF is proposed in order to operate when abnormal voltage conditions are present and cancel out the current harmonics the 18-pulse rectifier fails to mitigate. A simple control strategy based on forcing the current waveform to track the input voltage waveform is employed.

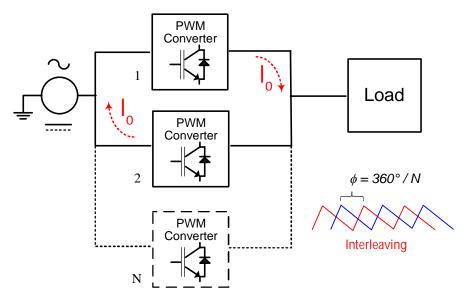

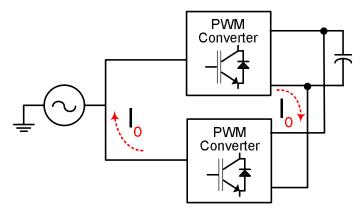

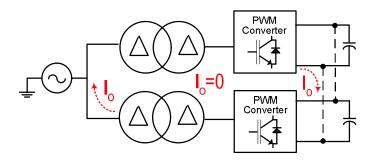

The second approach consists on an APF based on interleaved parallel inverters. The inverters are connected at the ac and dc bus and no isolation transformers are employed as proposed on previous publications. The utilization of interleaved carriers allows for the reduction of semiconductor's switching losses, increase of effective carrier frequency, and reduced size of linkage reactors. The manifestation of low and high frequency (HF) circulating current between the parallel converters will be analyzed. The introduction of common mode inductors is proposed to reduce the HF circulating current and a zero-sequence control loop to mitigate the low frequency circulating current is also proposed [56]-[58].

#### **1.2. Power Quality Standards**

#### **1.2.1 IEEE 519-1981** [67]

In 1981, the institute of electrical and electronics engineers released the "Guide for harmonic control and reactive compensation of static power converters." This guideline intended to help electrical engineers with the application of rapidly emerging adjustable speed drives and power electronics based converters. Even though many large companies, such as metal rolling mills and mining operations had recognized the problems with harmonics and developed mitigation techniques by the utilization of multi-pulse converters, the massive proliferation of small size power converters made the harmonic problem much more complicated to resolve. New users of power converters did not have engineers helping to mitigate harmonics problems. Extensive analysis was necessary to determine whether or not the new converters were going to be a problem. It was impractical and not economical to mitigate the harmonics for each non-linear load. Therefore, the IEEE 519-1981 was designed to help these users with the application of emerging non-linear loads.

However, the harmonics guidelines on IEEE 519-1981 were limited to voltage distortion only (TABLE I and TABLE II) and did not prevent a user from using all power capacity with large harmonics. Even though a user could have been complying with the voltage standard limits, large current harmonics that potentially overheat transformers or cause other system's interference could circulate through the power systems. It was clear the need of a revision to these guidelines where current harmonics limits were a function of the power system ability to withstand the circulation of harmonics. The standard was revised and the well-known IEEE 519-1992 was born.

TABLE I

| Low | LOW-VOLTAGE SYSTEMS CLASSIFICATION AND DISTORTION LIMITS FOR 460V SYSTEMS [67]. |    |        |  |  |  |  |

|-----|---------------------------------------------------------------------------------|----|--------|--|--|--|--|

|     | Class                                                                           | ρ  | DF (%) |  |  |  |  |

|     | Special Application (*)                                                         | 10 | 3      |  |  |  |  |

|     | General System                                                                  | 5  | 5      |  |  |  |  |

|     | Dedicated System                                                                | 2  | 10     |  |  |  |  |

(\*) Special applications are those where the rate of change of voltage of the notch might mistrigger an event.

*DF*= *Voltage Distortion Factor*

$\rho$ = impedance ratio of total impedance to impedance at common point in system.

## TABLE II

VOLTAGE DISTORTION LIMITS FOR MEDIUM AND HIGH VOLTAGE POWER SYSTEMS [67]

| Power System Voltage Level | Dedicated System Converter (*) | General Power System |

|----------------------------|--------------------------------|----------------------|

| Medium Voltage             | 8%                             | 5%                   |

| 2.4 - 69kV                 |                                |                      |

| High Voltage               | 1.5%                           | 1.5%                 |

| 115 kV and above           |                                |                      |

(\*) A dedicated system is one servicing only converters or loads not affected by voltage distortion.

#### **1.2.2 IEEE 519-1992** [68]-[70]

The IEEE 519 -1992 was an update to the 1981 guidelines. It was a significant improvement and it was upgraded to the category of "Recommendation practices and requirements".

The new IEEE-519 standard established the limits for current distortion that customers need to comply with and voltage distortion that the utility company should comply with (TABLE III and TABLE IV). The 1992 revision gave a more comprehensive understanding that the harmonic problem was a responsibility of both users and utility companies.

The standard set the limits for individual current harmonics and for total demand distortion (TDD) for a given short circuit current to load current ratio ( $I_{sc}/I_L$ ). The spirit of standard is that stiffer systems, the ones that feature larger  $I_{sc}/I_L$  ratios, have the ability to withstand larger current harmonics distortion. The concept of TDD or total demand distortion was introduced in order to properly weigh the impact of harmonics on the system. The TDD corresponds to the ratio between the rms value of current harmonics of order higher than two and the maximum fundamental demand load current ( $I_{ML}$ ) sustained for 15 to 30 min. This figure of merit differs from the distortion factor (DF) which quantifies how distorted is the signal from a sine-wave without considering if those harmonic levels are actually a real threat to the system.

$$TDD = \frac{\sqrt{\sum_{h=2}^{\infty} I_h^2}}{I_{ML}}$$

| Individual Harmonic Order (Odd Harmonics) |      |                          |                          |                          |                     |      |

|-------------------------------------------|------|--------------------------|--------------------------|--------------------------|---------------------|------|

| I <sub>sc</sub> / I <sub>L</sub>          | <11  | 11 ≤ <mark>h</mark> ≤ 17 | 17 ≤ <mark>h</mark> ≤ 23 | 23 ≤ <mark>h</mark> ≤ 35 | <mark>h</mark> ≤ 35 | TDD  |

| <20 *                                     | 4.0  | 2.0                      | 1.5                      | 0.6                      | 0.3                 | 5.0  |

| 20-50                                     | 7.0  | 3.5                      | 2.5                      | 1.0                      | 0.5                 | 8.0  |

| 50-100                                    | 10.0 | 4.5                      | 4.0                      | 1.5                      | 0.7                 | 12.0 |

| 100-1000                                  | 12.0 | 5.5                      | 5.0                      | 2.0                      | 1.0                 | 15.0 |

| >1000                                     | 15.0 | 7.0                      | 6.0                      | 2.5                      | 1.4                 | 20.0 |

CURRENT DISTORTION LIMITS FOR GENERAL DISTRIBUTION SYSTEMS (120V THROUGH 69,000 V) [68]

TABLE III

TDD: Total Demand Distortion is the harmonic current distortion in % of the maximum

60 Hz demand load current taken at the PCC (15-30 min).

I<sub>sc</sub>: Maximum Short Circuit Current at PCC.

I<sub>L</sub> : Maximum Demand Load Current (fundamental frequency component) at the PCC.

\* Even harmonics are limited to 25% of the odd harmonic limits above.

Where  $I_{ML}$  is the maximum 60Hz demand load current (15-30 min demand)

| TABLE IV                                                                    |     |     |  |  |  |

|-----------------------------------------------------------------------------|-----|-----|--|--|--|

| VOLTAGE DISTORTION LIMITS [68]                                              |     |     |  |  |  |

| Bus Voltage at PCC Individual Voltage Total Vo<br>Distortion (%) Distortion |     |     |  |  |  |

| 69 kV and below                                                             | 3.0 | 5.0 |  |  |  |

| 69.001 kV through 161 kV                                                    | 1.5 | 2.5 |  |  |  |

| 161.001 kV and above                                                        | 1.0 | 1.5 |  |  |  |

Note: High-voltage systems can have up to 2.0% THD where the cause is an HVDC terminal that will attenuate by the time it is tapped for user.

### **1.2.3 IEC 61000 EMC** [71]-[74]

The main difference between the IEEE 519 standard and Electromagnetic compatibility standard from the International Electromechanical Commission EMC IEC 61000 is the fact that the latter is aimed to limit the harmonic contribution of electrical equipment as oppose to merely electrical system recommendations that mitigates the impact of current harmonics. In that regards, it explicitly applies to electrical manufactures while IEEE 519 means to give recommendations to users on the application of power electronics converters.

The IEC 61000 comprises several standards that limit harmonic contribution:

- **IEC 61000-3-2 (1998-04):** Electromagnetic Compatibility (EMC) Limits for harmonic current emissions (equipment input current up to and including 16 A per phase) [71].

- IEC 61000-3-4 (1998-10): Electromagnetic Compatibility (EMC) Limitation of emission of harmonic currents in low-voltage power supply systems for equipment with rated current greater than 16 A (TABLE V) [72].

- IEC 61000-3-3 (1994-12): Limits Limitation of voltage changes, voltage fluctuations and flicker in public low-voltage supply systems, for equipment with rated current ≤ 16 A per phase and not subject to conditional connection [73].

- IEC 61000-3-5 (1994-12): Limits Limitation of voltage fluctuations and flicker in low-voltage power supply systems for equipment with rated current > 16 A [74]

#### TABLE V

| Harmonic<br>number<br><i>n</i> | Admissible<br>harmonic current<br>In/I1*% |   | Harmonic<br>number<br><i>n</i> | Admissible<br>harmonic current<br>In/I1*% |

|--------------------------------|-------------------------------------------|---|--------------------------------|-------------------------------------------|

| 3                              | 21, 6                                     |   | 21                             | ≤0, 6                                     |

| 5                              | 10, 7                                     |   | 23                             | 0, 9                                      |

| 7                              | 7, 2                                      |   | 25                             | 0, 8                                      |

| 9                              | 3, 8                                      |   | 27                             | ≤0, 6                                     |

| 11                             | 3, 1                                      |   | 29                             | 0, 7                                      |

| 13                             | 2                                         |   | 31                             | 0, 7                                      |

| 15                             | 0, 7                                      |   | 33                             | ≤0, 6                                     |

| 17                             | 1, 2                                      | 1 |                                | •                                         |

| 19                             | 1, 1                                      |   | Even                           | ≤ 8/n or ≤ 0, 6                           |

REVIEW OF IEC 61000-3-4 (FIRST EDITION 1998-10)<sup>1</sup> [72]

Stage 1 current emission values for simplified connection of equipment

h = rated fundamental current; h = harmonic current component

$$R_{sce} = \frac{Short\ Circuit\ VA}{Rated\ VA}$$

### **1.3.** Conventional current harmonic elimination solutions [22]

There are several ways to reduce current harmonics in electrical systems. Without loss of generality, they can be divided in to two main methods. There are ones that aim to reduce the contribution of current harmonics from the non-linear loads by modifying the front end of the equipment with multi-pulse converters or active front ends, and the ones that aim to eliminate or mitigate the propagation of the harmonics upstream from a the point of harmonic source. Among the latter, the most common

<sup>&</sup>lt;sup>1</sup> IEC 61000-3-4 ed.1.0 "Copyright © 1998 IEC Geneva, Switzerland.www.iec.ch"

The author thanks the International Electrotechnical Commission (IEC) for permission to reproduce Information from its International Publication IEC 61000-3-4 ed.1.0 (1998). All such extracts are copyright of IEC, Geneva, Switzerland. All rights reserved. Further information on the IEC is available from <u>www.iec.ch</u>. IEC has no responsibility for the placement and context in which the extracts and contents are reproduced by the author, nor is IEC in any way responsible for the other content or accuracy therein".

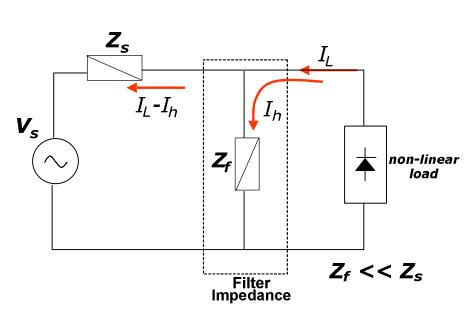

devices are passive filters. The underlying mechanism behind passive filters is to present low impedance for the harmonic to be eliminated. The impedance presented by the filter should be significantly lower than the equivalent impedance of the power source at the frequency to be filtered. Therefore, the current harmonic will circulate between filter and load and it will not propagate to the rest of the electrical system. In other words, the harmonic will be trapped in the filter; that is the reason why passive filters are often referred to as harmonic traps.

Fig. 1 shows a simple equivalent circuit of a passive filter.

Fig. 1. Passive harmonic filter equivalent circuit.

Where;

Zs : Source impedance

Zf: Filter impedance

Other methods to reduce harmonics consist on providing equipment furnished with front ends that inject lower harmonic contents. Multi-pulse rectifiers are well known and they have extensively studied. They work based on the principle of harmonic cancellation. The most command multi-pulse converter is the twelve pulse rectifier. It is typically composed for 2 six-pulse rectifiers and a shifting transformer. The rectifier can be connected in parallel or series connection and the transformer has two secondaries supplying the same voltage but with a phase angle shift of 30°.

## **1.3.1** Tuned passive filter

As mentioned on the previous section, the tuned passive filters (Fig. 2) work based on the principle of providing and alternative branch that would trap the harmonic to be eliminated. The impedance of the filter has to be significantly lower than the source impedance. A tuned harmonic filter is typically composed of an inductor in series with a capacitor. The values of L and C are selected in a way such that the cut-off or resonance frequency of the circuit corresponds to the harmonic frequency to be mitigated.

In general, the impedance of the filter branch can be expressed as:

$$\left|Z_{f}\right| = \left|R_{f} + 2\pi f L_{f} - \frac{1}{2\pi f C_{f}}\right|$$

Making  $Z_f \rightarrow 0$

$$2\pi f_{c} L_{f} - \frac{1}{2\pi f_{c} C_{f}} = 0$$

Therefore, the frequency  $f_c$  at which the tuned filter's impedance is minimum is:

$$f_c = \frac{l}{2\pi \sqrt{L_f C_f}}$$

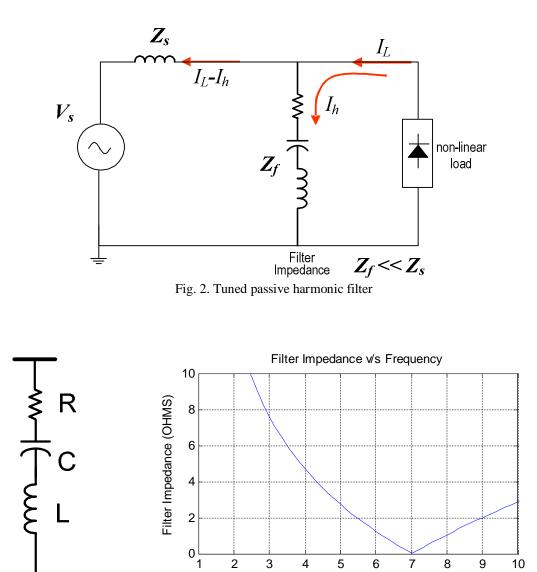

Fig. 3. Tuned passive harmonic filter and frequency response characteristic.

The typical design criterions for tuned passive filters typically consider; the reactive power to compensate displacement power factor (DPF - at 60Hz), resonance frequency equal to 0.95 times the frequency to be eliminated and a quality factor (Q) between 30 and 60. The quality factor Q is a dimensionless figure of merit that characterizes the filter bandwidth relative to its resonance frequency. In other words, it gives an indication of the damping of the filter structure. For a tuned passive filter as shown in Fig. 3, the quality factor is:

$$Q = \frac{1}{R}\sqrt{\frac{L}{C}}$$

The main advantages of tuned passive filters are their simplicity and low cost. However, issues such as resonance, prone to overload, detuning, and the fact that they can only be designed to mitigate a single frequency are a big concern. The effectiveness of the passive filters depends upon presenting an impedance, for a given harmonic, lower than the source's impedance, however, the source impedance can change unexpectedly and modify the response of the filter. They can also serve as a low impedance path for unintended harmonics, resulting in unwanted overloading. On the other hand, the tuned filters depend upon inductor and capacitor values. But the capacitor and inductors are susceptible to parameter tolerance deviations that can detune the filter.

Tuned filters can only be tuned to effectively filter a single harmonic therefore multiple branches must be used when more harmonics want to be filtered.

## 1.4. High pass filter [22]

A high pass filter presents low impedance for frequency above the resonant frequency. The objective is to mitigate more than one harmonic. However, they draw high current at fundamental frequency which increases the resistive losses.

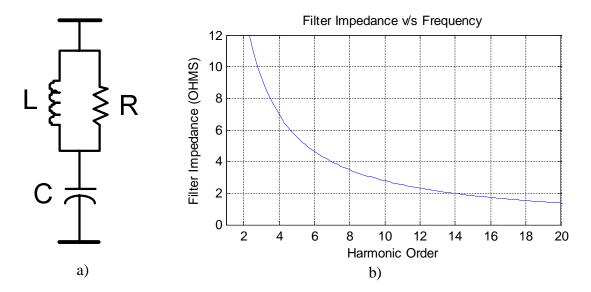

Fig. 4.a shows a high-pass filter equivalent circuit and Fig. 4.b its typical frequency response.

Fig. 4. a) High-pass passive harmonic filter and b) its frequency response characteristic.

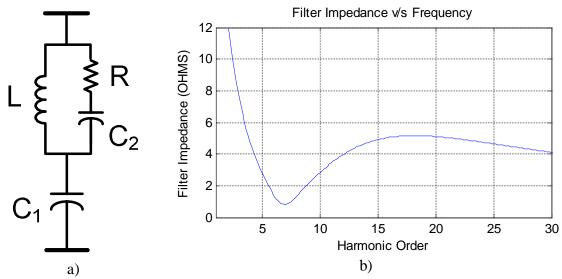

A modification of the high pass filter is the circuit shown in Fig. 5.a, the capacitor C2 reduces the filter's fundamental current which reduces the losses. Fig. 5.b shows its typical frequency response. The filter can be designed to more effectively mitigate a band of harmonics.

Fig. 5. a) High-pass (modified) passive harmonic filter and b) its frequency response characteristic.

### **1.5.** Active harmonic filters (AHF)

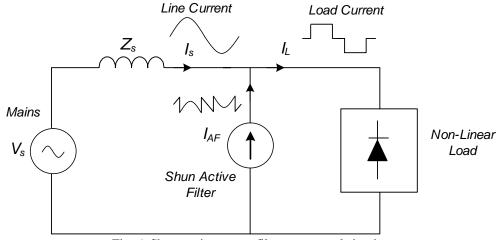

#### **1.5.1 Shunt Active Filter** [42][43][60]

Shunt active harmonic filters (SAHF) are power electronics based devices used as controlled current sources. Modern active filters are microprocessor controlled which gives them high flexibility and versatility. The SAHF would inject a current with the same magnitude of the harmonic to be eliminated but with a perfect 180° phase angle, resulting in the cancellation of the current harmonic and preventing it from circulating to the rest of the electrical system. The main advantage of active filters is the fact that it is possible to cancel a wide range of harmonics with the same device. The active filter can simultaneously inject a current which is composed of several harmonics with different phase angle. Since they are precisely controlled, they can also be selective in the way the generate harmonics, giving the user the option to mitigate a single harmonic or a group them. Graphic human interfaces make them easy to use and monitor their performance. Fig. 6 shows a conceptual single line diagram of a shunt active filter.

Fig. 6. Shunt active power filter conceptual circuit.

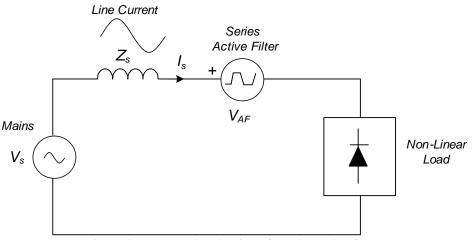

## **1.5.2 Series Active Filter** [60]-[62]

Series active filters (SAF) are power electronics based devices used as controlled voltage sources. They are connected in series with the electrical systems, between the source and the nonlinear load. Series active filters are based on the principle of harmonic isolation by controlling the voltage injected by the filter at the frequency to be eliminated. By increasing the voltage, the SAFs are able to present high impedance for the harmonic currents, resulting on the blocking of the unwanted harmonics and preventing them from flowing to the source. In other words, the SAF can cancel out the virtual equivalent harmonic voltage source imposed by the load. The main drawback of SAFs is the fact that a series injection transformer needs to be used to interface with the system in order to inject the active filter's voltage. This transformer requires a special

design which increases its cost. The transformer must provide very low voltage for line frequency load current circulation. The other practical disadvantage of SAFs hinges on the complexity of the protection system for the active filter converter which must be designed to withstand load's short circuits. During a short circuit event, the high load current will reflect on the secondary of the injection transformer generating dangerous voltages and potentially damaging the active filter converter [62]. Typical protection schemes consider a thyristor based bypass that closes to bypass the converter when the load suffers high current fault conditions and consequently protects the converter from catastrophic failure. Fig. 7 shows a conceptual diagram of a series active filter.

Fig. 7. Conceptual visualization of a series active filter

## **1.5.3 Hybrid Active filters** [60][63]-[66]

In principle, hybrid filters are a combination of a passive filter and an active filter. Typically a hybrid filter consists of a passive tuned (shunt) filter and a series active filter. The addition of the series active filter yields to significantly improvements on the passive filter frequency response, extending the filtering capabilities. The main practical advantage of hybrid active filters is the fact that the KVA rating of the inverter can be a small fraction of the total load kVA (<5%). This is reduces significantly the efforts and cost on power electronics. Low kVA rating inverters with higher current bandwidth can then be used since no large blocks of power need to be handled with power electronics converters.

The series active filter in a hybrid filter can be connected in series with the systems between the source and the passive filter or in series with each branch the shunt passive filters, the latter it is referred to as parallel hybrid active filter.

### **1.5.4** Combination of shunt and series active filters [60] [75]-[79]

Another trend on active harmonic filters consists on a combination of a series active filter and a shunt active power filter. They can be configured to either control active and reactive power flow or mitigate current and voltage harmonics. A very popular configuration is the so called unified power flow controller (UPFC) which was introduced by Gyugi [77] to enable flexible ac transmission systems (FACTS). Another topology is the unified power quality controller (UPQC) which aim to mitigate power quality problems such as current harmonics and voltage disturbances.

## A. The Unified Power Flow Controller (UPFC) [75]-[79]

The unified power flow controller is a combination of a series and a shunt active filter (Fig. 8), and it is typically conceived to provide power control on a meshed power

transmission system. The main advantage of UPFCs is the ability to control reactive power and active power flow. It was initially proposed by Gyugyi and Hingorani and it is considered a key component of the so called flexible ac transmission systems (FACTS), a concept first introduced by the latter author.

The shunt active filter is composed of a PWM inverter which is connected to the system with the objective to control reactive power at the point of common coupling. Dynamic reactive power control can improve the stability of the ac system by increasing the maximum active power that can be transmitted and flatten voltage profile. A series active filter composed of a PWM inverter is connected in series with the load side through a series injection transformer with the objective to provide; power flow by modifying the line effective impedance and damping of sub-synchronous resonance. The dc buses of both inverters are tied together allowing the flow of active power between shunt and series converter as needed. Even though both shunt and series active power must be set equal for both converters in order to guarantee energy balance and maintain rated dc bus voltage. In practice small difference in active power would be allowed to compensate for losses in the converters.

In the case of the unified power flow controller, the active filters are not designed to provide harmonics cancellation rather to control of the fundamental components. However, the topology is still capable of doing so if provided the proper bandwidth.

Fig. 8. Unified power flow controller (UPFC)

## B. The Unified Power Quality Conditioner (UPQC) [60]

The unified power quality controller (Fig. 9) consists also on a combination of a shunt and series active filter; however it is properly designed with the objective to compensate for harmonics components. It constitutes one the most flexible power electronics devices for harmonic compensation. The shunt active filter is in charge of current harmonics cancellation and the series active filter can compensate for voltage harmonics and imbalances of the power supply. The way the UPQC is connected to the electric system is somewhat different than the UPFC. The shunt active filter is connected as close as possible to the non-linear load and the series active filter is connected between the source and the shunt active filter point of common coupling. Even though the topology is suitable to compensate for fundamental reactive power, it is preferable to avoid it and therefore reduce the power rating of the converter.

The typical converter topology is identical to the UPFC consisting of a back-toback two level inverter. Passive LC or RLC filters at both sides are necessary to eliminate high frequency ripple caused by the converter switching frequency.

The series active filter will be responsible for compensating pre-existent voltage harmonic due to non-linear loads upstream of the system. It can also be designed to compensate voltage unbalance by providing the proper fundamental negative-sequence component.

Fig. 9. Unified power quality conditioner.

## **1.6. Previous work**

Multiple has been the efforts in order to mitigate harmonics generated by power electronics converters with minimum demand on extra components such as; additional power electronics converters, transformers or passive LC based filters. It is highly desired that not significant weight, volume and cost is added to the already costly power electronic converters. Choi and Enjeti in [55] proposed a converter front end with reduced kVA 12-pulse rectifier system utilizing an autotransformer and dc side interface reactor; where the autotransformer KVA rating is only 0.18 (p.u.) and the six-pulse rectifiers feature equal current sharing. Also, the same approach is extended to an 18-pulse rectifier system, where the transformer kVA rating is 0.16p.u. In [54] the same authors proposed a 12-pulse rectifier with active interphase reactor where a low kVA rated PWM converter is used to provide near sinusoidal input current.

Kamath in [32], proposed an ASD front end rectification method with autotransformer that is suitable for 18-pulse rectification and is rated at 0.33p.u. It differs from existing schemes by achieving harmonic current reduction without the need for equal diode-bridge current sharing, and eliminating the need for line-impedance matching inductors. The approach employs two extra auxiliary six-pulse rectifiers rated at 0.166p.u each, which significantly reduces the overall power converter kVA rating. This topology is referred to as asymmetric 18-pulse rectifiers, since not all the rectifiers share the current equally. An extensive analysis of similar asymmetric 18-pulse rectifier approach has been done in [33], however, no analysis under abnormal utility supply conditions, such as voltage unbalance and pre-existing harmonic distortion has been provided in this or in previous references. Furthermore, an equivalent asymmetric 18pulse rectifier topology has been patented and commercialized by Toshiba Corp. [34] as a low harmonic adjustable speed drive to comply with the stringent harmonic requirement from the water and waste water market segment or in weak systems. Even though, asymmetric 18-pulse rectifiers present good balance between performance cost and reliability, no significant research is found that analyze their performance under abnormal voltage conditions. The author *et al.* presented in [37] a reduced kVA active power filter to improve the performance of an asymmetric 18-pulse rectifier.

On the other hand, harmonic compensation using active solutions have been studied for decades. The principle of active compensation can be traced back to 1958, when McFarlane and Harris [41] proposed a method to compensate for voltage harmonics generated by non-linearity on the B-H curve in ferromagnetic materials. More than a decade later, Sasaki and Machida in 1971 [42], aiming to eliminate current harmonics in high-voltage DC transmission systems, introduced the modern concept of harmonic compensation in power systems. Their method was based on the principle of the magnetic flux compensation in a transformer core by injecting a compensating current into a tertiary winding. However, in the early 1970's, the hardware technology necessary to implement the compensation principle was not available. During the last three decades, however, remarkable progress on semiconductors with fast switching characteristics and higher current and voltage breakdown levels has been attained. Initially, great success with the development of thyristors and gate turn on devices (GTO) and more recently, multiple generations of insulated gate bipolar transistors (IGBT) are shaping the way active power filter technology is being deployed.

Theoretically, active power filters would compensate the entire unwanted harmonics spectrum, however, to do so converters with infinite bandwidth are necessary. In order to compensate for high order harmonics, the converter needs to accurately reproduce the harmonics with the opposite phase to the harmonic to compensate; therefore high switching frequencies are necessary. Large power converters still cannot commutate at high switching frequencies, due to excessive switching losses. Significant advances such as in GTOs and IGCTs have enabled large power converters however the practical switching frequencies of these devices are still below ~600Hz. The last developments in IGBT like non-punch through and trench gate have increased the reliability of motor drives, however large IGBT based adjustable speed drives can only reach practical switching frequencies of around 2-3kHz. Certainly, not high enough to re-construct 7<sup>th</sup> or higher order harmonics. In addition, semiconductor's technology is also limited by the available current and voltage ratings. In order to cope with high-power requirements, several solutions, such as hybrid topologies [63]-[66], multilevel structures [80]-[86], and paralleled inverters are proposed in the literature [87]-[101].

Akagi *et al.* [88] proposed a parallel structure by using four inverters and solidly connecting the dc side. The reason for adopting this structure is to suppress the harmonics caused by switching operation without increasing the switching frequency, paying attention to practical applications. The ac side includes a power transformer for galvanic isolation. However, an isolation transformer is has a bulky design and suffers of larger power losses since it has to support the nominal current of the APF. Furthermore, the transformer for APF applications is an expensive component; it has to be designed with a high bandwidth according to the maximum compensated harmonic current. On the other hand, removing the transformer and connecting the inverters directly on the ac side, could contribute to circulation currents between the inverters.

Morán, Fernández, *et al.* in [53] proposed a simple and low cost shunt active power filter structure composed of two voltage source inverters in cascade; one GTO based located close to the non-linear load and operating at low switching frequency with the objective to compensate for reactive power and low frequency harmonics. And a second, IGBT based, shunt APF, operating at higher switching frequency and responsible for mitigation of higher order harmonics.

Kim and Enjeti in [30] and [55] proposed a new hybrid APF topology based on two voltage source inverts; one based on IGBTs and another one with lower kVA rating and based on MOSFETs. The former is designed with the ability to support utility fundamental and to compensate reactive power, and the latter designed for lower voltage rating and with the ability to compensate current harmonics. The dc bus of the MOSFET-based inverter is connected from one of the split capacitors of the IGBT based inverter dc bus. In [101] Moran, et al. proposed a shunt APF composed of three voltage source inverters connected in parallel at dc and ac side. Each inverter is operating at different switching frequency so that wider bandwidth can be attained and different semiconductors technology can be used according to their switching speed limitations. However, no analysis or acknowledgement regarding circulating current among the inverter is reported. And Z. Ye, et al. in [96] provides a comprehensive analysis and modeling of circulating currents for two parallel connected PWM rectifiers. However, no application for harmonics mitigation is reported.

#### **1.7. Research Objective**

The main objective of this dissertation is to analyze new cost effective topologies for harmonic mitigation in three-phase high power applications. Traditionally, harmonics mitigation has been done by passive filters and multi-pulse rectifiers. The former have the disadvantage that they are bulky, heavy, and its harmonic attenuation performance is highly dependent on the system impedance and that parallel resonance can occur between the source and filter impedances. Multi-pulse rectifiers have the disadvantage that bulky line frequency transformers specially designed to handle large harmonics are necessary and that passive filters are usually also needed to achieve high performance. To overcome these problems active power filters have emerged as a technically feasibly solution to mitigate harmonics. However when large current needs to be compensated limitations of semiconductor switching losses prohibit the realization of a large current active power filter since the practical switching frequencies cannot reach the bandwidth necessary to reconstruct the harmonics to be compensated. A prospect solution to this problem is the availability of high performance switching devices that can operate at high switching frequencies with low losses, and can withstand large reverse voltages. Extensive research has been done in switching devices made of different materials such as Silicon Carbide and Nitride Gallium; however these devices are still not developed or matured enough to provide a practical solution for large current applications. Therefore alternative power electronics converter topologies could offer a more immediate solution to mitigate harmonics in large current harmonics systems. When searching for new topologies, several key aspects need to be considered for the design which resides in five

main equally weighted pillars: high performance, high power-density, high efficiency, high reliability and low cost.

This work focuses on two topologies to mitigate current harmonics based on these design principles. One topology is based on extending the capabilities of an asymmetric 18-pulse rectifier to mitigate harmonics in motor drives by adding a shunt active power filter conforming a hybrid between a passive and active approach. The asymmetric 18-pulse rectifier provides high reliability and low losses since no active devices are involved in the current rectification process and since the phase-shifting input auto-transformer and active filter, are not rated for full load power.

A second topology based on parallel interleaved inverters is also studied. This topology can enable a modular structure for high current active power filters with reduced size of its passive components. The issues with the parallel connection of the inverters are studied such as the circulation of low and high frequency zero-sequence current. Even though this topology per se is not new, its practical application for active power filters has not been extensively reported.

### **1.8. Dissertation Outline**

In the first chapter of this work is presented an introduction to conventional current harmonic mitigation methods and standards, designed and refined over the years in order to give guidance to engineers on how to operate the electrical systems in the presence of current harmonics. The characteristic of different approaches such as passive and active methods are explored. Among the formers, L-C network based filters and multi-pulse rectifiers among the latters. Chapter II presents the state-of-the-art of harmonic mitigation methods for adjustable speed drives. It is pointed out the influence of the line or source reactance on drives' harmonic performance. The use of tuned L-C harmonic filters and the harmonic cancellation process when multi-pulse front ends are used as well as active front ends with multilevel converter is presented.

Chapter III presents an analysis of a high-power density asymmetric 18-pulse rectifier under abnormal input voltage conditions. It is shown how the current harmonic THD and the harmonic cancellation process are deteriorated when pre-existing voltage harmonic distortion and unbalance is present in the incoming voltage. Extensive experimental data is demonstrated to validate the theoretical analysis. In Chapter IV is introduced a solution to overcome the issues with the high-power density asymmetric 18-pulse rectifier under unbalance or voltage distortion. A reduce kVA active power filter is proposed to compensate the extra current harmonics generated during the abnormal conditions. With the objective to avoid impairing the power density of the approach, the kVA rating of the APF is specified to only 20% of the overall system power rating.

Chapter V presents an analysis of a modular converter structure to achieve high power density and high reliability for active power filters. The approached is based on interleaved parallel two-level converters with direct connection at the dc side and connection through linkage reactors at the ac side. An analysis of the reduction on the linkage reactors and impact of the interleaving approach on the dc bus capacitor is presented as well as the generation of high frequency and low frequency zero-sequence among the converters.

Finally Chapter VI presents the general conclusions and remarks obtained from this work.

#### CHAPTER II

# ANALYSIS OF CURRENT HARMONIC ELIMINATION SOLUTION FOR ADJUSTABLE SPEED DRIVES

# **2.1. Introduction**

The vast proliferation of adjustable speed drives was in great part the result of the realization of significant energy savings; especially for variable torque loads (e.g. pumps, fans) where the demanded power proportional to the cube of shaft seeped. However, these benefits have been overshadowed by the well-known harmonics problems encountered with six diode front end drives. Six pulse rectifiers are a significant source of harmonics which is exacerbated by the utilization of a DC bus capacitor . The total harmonic distortion of the current in adjustable speed drives can vary from a range of 35% to more 100%, depending upon the short circuit to load current ratio ( $I_{sc}/I_L$ ). For stiff or strong systems (large  $I_{sc}/I_L$ ) the current harmonic distortion is higher than for weaker systems (low  $I_{sc}/I_L$ ).

Numerous approaches have been investigated and commercialized over the years in order to reduce current harmonic contribution from adjustable speed drives. One of the most popular approaches, typically found in large drives, is the 12 pulse rectifier which with the help of a phase shifting transformer is able to cancel harmonic components and significantly reduce the total harmonic distortion at the input of the drive system. Other approaches such as 18-pulse rectifiers and larger number of pulses up to 24 and 36 - are common to see for medium voltage applications. For low voltage adjustable speed applications, the typical configuration is a six pulse front end; however, cost limitation and market response usually prohibits the utilization of more costly multi-pulse configurations, for which a specially designed phase-shifting transformer is inherently needed. Therefore, in order to resolve the harmonic problems, passive harmonic filters are available from several manufacturers. In this chapter, a review of the most common alternatives and industrial practices to reduce current harmonics pollution from adjustable speed drives is analyzed.

#### 2.2. Harmonics on 6-pulse front end drives [23][40]